(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2017-184092

(P2017-184092A)

(43) 公開日 平成29年10月5日(2017.10.5)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H04N 1/41</b> (2006.01)  | H04N 1/41  | B 5C159     |

| <b>H04N 19/86</b> (2014.01) | H04N 19/86 | 5C178       |

| <b>G09G 5/02</b> (2006.01)  | G09G 5/02  | 5C182       |

| <b>G09G 5/00</b> (2006.01)  | G09G 5/00  | 520J        |

| <b>G09G 5/36</b> (2006.01)  | G09G 5/00  | 550H        |

審査請求 未請求 請求項の数 8 O L (全 28 頁) 最終頁に続く

|           |                            |            |                                                                                                                                       |

|-----------|----------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2016-70496 (P2016-70496) | (71) 出願人   | 591128453<br>株式会社メガチップス<br>大阪府大阪市淀川区宮原一丁目1番1号                                                                                         |

| (22) 出願日  | 平成28年3月31日 (2016.3.31)     | (74) 代理人   | 100080159<br>弁理士 渡辺 望穂                                                                                                                |

|           |                            | (74) 代理人   | 100090217<br>弁理士 三和 晴子                                                                                                                |

|           |                            | (72) 発明者   | 安藤 潤<br>千葉県千葉市美浜区中瀬1丁目3番地 株式会社メガチップス内                                                                                                 |

|           |                            | F ターム (参考) | 5C159 MA01 MC38 MD03 ME01 PP01<br>PP15 PP16 UA02 UA05 UA31<br>5C178 AC10 AC16 BC21 BC90 CC03<br>CC32 CC54 CC55 CC69 EC04<br>GC06 HC08 |

|           |                            |            | 最終頁に続く                                                                                                                                |

## (54) 【発明の名称】 画像処理装置

## (57) 【要約】

【課題】圧縮伸張後の画像において、階調が階段状に変化したり、擬似乱数によるノイズの偏りによって模様が発生したりするのを防止し、高画質な画像を得ることができる画像処理装置を提供する。

【解決手段】画像処理装置では、第1の乱数シード生成回路が、ラインの番号に対応する第1の乱数シードを生成する。画像圧縮回路が、第1の画像データと、第1の乱数シードと量子化係数に基づいて生成した第1の擬似乱数との加算データを量子化することにより圧縮データを生成する。第2の乱数シード生成回路が、ラインの番号に対応し、かつ、第1の乱数シードと等しい第2の乱数シードを生成する。画像伸張回路が、画像メモリから読み出された圧縮データを量子化係数で逆量子化することにより伸張データを生成し、伸張データから、第2の乱数シードと量子化係数に基づいて生成した第1の擬似乱数と等しい第2の擬似乱数を減算することにより第2の画像データを生成する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1の画像データに対する画像のラインまたはブロック毎に、第1の画像同期信号に基づいて、前記ラインまたはブロックの番号に対応する第1の乱数シードを生成する第1の乱数シード生成回路と、

前記ラインまたはブロックに対応する画素毎に、前記第1の乱数シードに基づいて第1の擬似乱数を生成し、前記第1の画像データと前記第1の擬似乱数との加算データを量子化して符号化することにより圧縮データを生成する画像圧縮回路と、

前記圧縮データを格納する画像メモリと、

第2の画像同期信号を生成する同期信号生成回路と、

前記ラインまたはブロック毎に、前記第2の画像同期信号に基づいて、前記ラインまたはブロックの番号に対応し、かつ、前記第1の乱数シードと等しい第2の乱数シードを生成する第2の乱数シード生成回路と、

前記ラインまたはブロックに対応する画素毎に、前記画像メモリから読み出された圧縮データを復号化して逆量子化することにより伸張データを生成し、前記第2の乱数シードに基づいて前記第1の擬似乱数と等しい第2の擬似乱数を生成し、前記伸張データから前記第2の擬似乱数を減算することにより第2の画像データを生成する画像伸張回路とを備える画像処理装置。

**【請求項 2】**

前記第1の乱数シード生成回路は、

前記ラインまたはブロック毎に、送信側回路から受信した前記第1の画像同期信号に基づいて、前記送信側回路から受信した前記第1の画像データに対応する画像のラインまたはブロックの番号を生成する第1の番号生成回路と、

前記ラインまたはブロック毎に、前記第1の番号生成回路によって生成されたラインまたはブロックの番号を、第1の変換式に基づいて変換することにより前記第1の乱数シードを生成する第1の番号変換回路とを備え、

前記第2の乱数シード生成回路は、

前記ラインまたはブロック毎に、前記第2の画像同期信号に基づいて、前記画像メモリから読み出された圧縮データに対応する画像のラインまたはブロックの番号を生成する第2の番号生成回路と、

前記ラインまたはブロック毎に、前記第2の番号生成回路によって生成されたラインまたはブロックの番号を、前記第1の変換式と等しい第2の変換式に基づいて変換することにより前記第2の乱数シードを生成する第2の番号変換回路とを備える請求項1に記載の画像処理装置。

**【請求項 3】**

前記第1の番号変換回路は、前記第1の番号生成回路によって生成されたラインまたはブロックの番号を、フレーム毎に異なる前記第1の変換式に基づいて変換し、

前記第2の番号変換回路は、前記第2の番号生成回路によって生成されたラインまたはブロックの番号を、前記フレーム毎に前記第1の変換式と等しい第2の変換式に基づいて変換する請求項2に記載の画像処理装置。

**【請求項 4】**

前記第1の乱数シード生成回路は、前記送信側回路から受信した開始ラインまたは開始ブロックの情報に対応する開始ラインまたは開始ブロックから前記第1の乱数シードを生成し、

前記画像圧縮回路は、前記開始ラインまたは前記開始ブロックから前記圧縮データを生成し、

前記画像メモリは、前記開始ラインまたは前記開始ブロックから前記圧縮データを格納する請求項2または3に記載の画像処理装置。

**【請求項 5】**

前記画像圧縮回路は、前記第1の画像データを符号化することにより前記圧縮データを

10

20

30

40

50

生成する符号化回路を備え、

前記符号化回路は、前記ラインまたはブロックに対応する画素毎に、前記第1の乱数シードおよび量子化係数に基づいて前記第1の擬似乱数を生成する第1の擬似乱数生成回路と、

前記画素毎に、前記第1の画像データと前記第1の擬似乱数とを加算することにより前記加算データを生成する第1の加算器と、

前記画素毎に、前記量子化係数を用いて、前記加算データを量子化することにより第1の量子化データを生成する量子化回路と、

前記画素毎に、前記第1の量子化データをエントロピー符号化することにより前記圧縮データを生成するエントロピー符号化回路とを備え、

前記画像伸張回路は、前記画像メモリから読み出された圧縮データを復号化することにより前記伸張データを生成する復号化回路を備え、

前記復号化回路は、前記画素毎に、前記画像メモリから読み出された圧縮データをエントロピー復号化することにより第2の量子化データを生成するエントロピー復号化回路と、

前記画素毎に、前記量子化係数を用いて、前記第2の量子化データを逆量子化することにより前記伸張データを生成する逆量子化回路と、

前記画素毎に、前記第2の乱数シードおよび前記量子化係数に基づいて前記第2の擬似乱数を生成する第2の擬似乱数生成回路と、

前記画素毎に、前記伸張データから前記第2の擬似乱数を減算することにより前記第2の画像データを生成する第1の減算器とを備える請求項2ないし4のいずれか一項に記載の画像処理装置。

#### 【請求項6】

前記符号化回路は、さらに、前記画素毎に、前記量子化回路によって生成された第1の量子化データから、現在の画像よりも前の画像に対応する前記第1の量子化データを減算することにより第1の差分データを生成する第1の予測回路を備え、

前記エントロピー符号化回路は、前記第1の差分データをエントロピー符号化することにより前記圧縮データを生成し、

前記エントロピー復号化回路は、前記画像メモリから読み出された圧縮データをエントロピー復号化することにより第2の差分データを生成し、

前記復号化回路は、さらに、前記画素毎に、前記エントロピー復号化回路によって生成された第2の差分データと、現在の画像よりも前の画像に対応する第2の量子化データとを加算することにより前記第2の量子化データを生成する第2の予測回路を備える請求項5に記載の画像処理装置。

#### 【請求項7】

前記第1の画像データは、RGB色空間の画像データであり、

前記画像圧縮回路は、さらに、前記RGB色空間の第1の画像データを、YUV色空間の第3の画像データとして、第3のY画像データ、第3のU画像データおよび第3のV画像データに変換する色空間変換回路と、

前記量子化係数として、前記第3のY画像データ、第3のU画像データおよび第3のV画像データに対応するY量子化係数、U量子化係数およびV量子化係数を生成する、量子化係数生成回路とを備え、

前記符号化回路は、前記圧縮データとして、前記第3のY画像データ、第3のU画像データおよび第3のV画像データに対応するY圧縮データ、U圧縮データおよびV圧縮データを生成する第1、第2および第3の符号化回路を備え、

前記画像メモリは、前記符号化回路によって生成されたY圧縮データ、U圧縮データおよびV圧縮データと、前記量子化係数生成回路によって生成されたY量子化係数、U量子化係数およびV量子化係数とを格納し、

前記復号化回路は、前記第2の画像データとして、前記画像メモリから読み出されたY圧縮データ、U圧縮データおよびV圧縮データに対応する第2のY画像データ、第2のU画像

10

20

30

40

50

データおよび第2のV画像データを生成する第1、第2および第3の復号化回路を備え、前記画像伸張回路は、さらに、前記復号化回路によって生成されたYUV色空間の第2の画像データを、RGB色空間の第4の画像データに変換する逆色空間変換回路を備える請求項5または6に記載の画像処理装置。

#### 【請求項8】

前記第1の乱数シード生成回路は、前記第1の乱数シードとして、前記第3のY画像データ、第3のU画像データおよび第3のV画像データに対応する第1のY乱数シード、第1のU乱数シードおよび第1のV乱数シードを生成し、

前記量子化係数生成回路は、前記量子化係数として、前記第3のY画像データ、第3のU画像データおよび第3のV画像データに対応するY量子化係数、U量子化係数およびV量子化係数を生成し、

前記第1、第2および第3の符号化回路は、それぞれ、前記第1のY乱数シード、第1のU乱数シードおよび第1のV乱数シードと、前記Y量子化係数、U量子化係数およびV量子化係数とに基づいて、前記第3のY画像データ、第3のU画像データおよび第3のV画像データを符号化することにより前記Y圧縮データ、U圧縮データおよびV圧縮データを生成し、

前記第2の乱数シード生成回路は、前記第2の乱数シードとして、前記画像メモリから読み出されたY圧縮データ、U圧縮データおよびV圧縮データに対応する第2のY乱数シード、第2のU乱数シードおよび第2のV乱数シードを生成し、

前記第1、第2および第3の復号化回路は、それぞれ、第2のY乱数シード、第2のU乱数シードおよび第2のV乱数シードと、前記Y量子化係数、U量子化係数およびV量子化係数に基づいて、前記画像メモリから読み出されたY圧縮データ、U圧縮データおよびV圧縮データを復号化することにより、前記第2の画像データとして、第2のY画像データ、第2のU画像データおよび第2のV画像データを生成する請求項7に記載の画像処理装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、乱数ディザリングによる量子化により画像データを圧縮して画像メモリに格納し、逆量子化により画像メモリに格納した画像データを伸張する画像処理装置に関する。

##### 【背景技術】

##### 【0002】

タブレットPC(Personal Computer:パーソナルコンピュータ)およびノートPC等のように、液晶表示装置を搭載したデバイス内で用いられる画像通信規格として、エンベデットディスプレイポート(Embedded DisplayPort)の規格がある。

##### 【0003】

エンベデットディスプレイポートの規格には、デバイスの消費電力を削減する技術として、PSR(Panel Self Refresh:パネルセルフリフレッシュ)と呼ばれる機能が含まれる。PSRの機能によって画像を表示する場合、通常動作の場合の動画像の表示から、PSRの機能によって静止画像の表示に切り替えられた後に送信側回路が画像データの送信を停止し、液晶表示装置の画像処理装置に含まれる受信側回路が、通常動作の場合に画像メモリに格納した画像データに対応する画像を表示する。

##### 【0004】

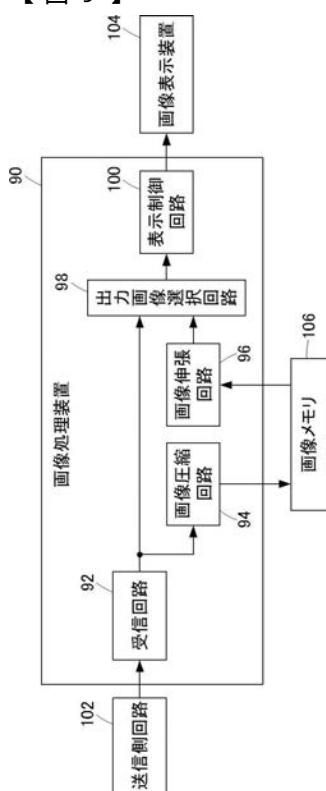

図9は、液晶表示装置の画像処理装置の構成を表す一例のブロック図である。図9に示す画像処理装置90は、受信回路92と、画像圧縮回路94と、画像伸張回路96と、出力画像選択回路98と、表示制御回路100とを備えている。

##### 【0005】

通常動作の場合、送信側回路102から送信される画像データが受信回路92によって受信され、出力画像選択回路98から出力される。そして、表示制御回路100の制御により、出力画像選択回路98から出力される画像データに対応する画像が画像表示装置1

10

20

30

40

50

04に表示される。

#### 【0006】

一方、PSRの機能によって画像を表示する場合、通常動作の場合に受信回路92によって受信された画像データが画像圧縮回路94によって圧縮され、画像メモリ106に格納される。画像の表示タイミングに応じて画像メモリ106から読み出された画像データは画像伸張回路96によって伸張され、出力画像選択回路98から出力される。そして、表示制御回路100の制御により、出力画像選択回路98から出力される画像データに対応する画像が画像表示装置104に表示される。

#### 【0007】

上記のように、PSRの機能によって画像を表示する場合に、画像メモリ106に格納する画像データに対して圧縮処理を適用することにより、画像メモリ106の容量およびバンド幅を低減することができる。一方、動画像の表示から静止画像の表示に切り替えられる際に、表示される画像は非圧縮画像から圧縮画像に切り替えられるため、圧縮処理によって知覚されうる画質の劣化が生じることは好ましくない。

#### 【0008】

また、エンベデットディスプレイポートの規格には、送信側回路が画像全体のうちの更新する矩形領域のみの画像データを送信し直して選択アップデート(Selective Update)を行う、PSR2(Panel Self Refresh 2:パネルセルフリフレッシュ2)と呼ばれる機能がある。PSR2の機能に対応するためには、圧縮伸張処理として、画像の一部のみ、例えば、ライン単位ないしブロック単位で独立して画像データを符号化および復号化することが要求される。

#### 【0009】

また、画像圧縮では、一般に、画像データ間の相関を減らし、圧縮効率を改善する目的で、RGB色空間からYUV色空間等への変換が行われる。

#### 【0010】

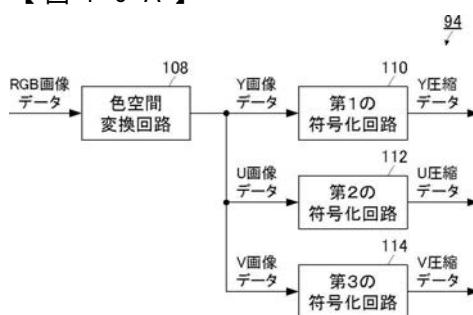

図10Aは、図9に示す画像圧縮回路の構成を表す一例のブロック図である。図10Aに示す画像圧縮回路94は、色空間変換回路108と、符号化回路として、第1、第2および第3の符号化回路110, 112, 114とを備えている。

#### 【0011】

画像圧縮回路では、色空間変換回路108により、RGB色空間の画像データが、YUV色空間の画像データとして、Y画像データ、U画像データおよびV画像データに変換される。そして、第1、第2および第3の符号化回路により、それぞれ、Y画像データ、U画像データおよびV画像データが符号化され、圧縮データとして、それぞれ、Y画像データ、U画像データおよびV画像データに対応するY圧縮データ、U圧縮データおよびV圧縮データが生成される。

#### 【0012】

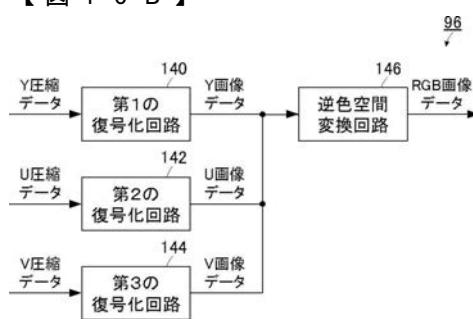

図10Bは、図9に示す画像伸張回路の構成を表す一例のブロック図である。図10Bに示す画像伸張回路96は、復号化回路として、第1、第2および第3の復号化回路140, 142, 144と、逆色空間変換回路146とを備えている。

#### 【0013】

画像伸張回路96では、第1、第2および第3の復号化回路140, 142, 144により、それぞれ、Y圧縮データ、U圧縮データおよびV圧縮データが復号化され、伸張データとして、それぞれ、Y圧縮データ、U圧縮データおよびV圧縮データに対応するY画像データ、U画像データおよびV画像データが生成される。そして、逆色空間変換回路146により、Y画像データ、U画像データおよびV画像データが逆変換されて、YUV色空間の画像データが、RGB色空間の画像データとして生成される。

#### 【0014】

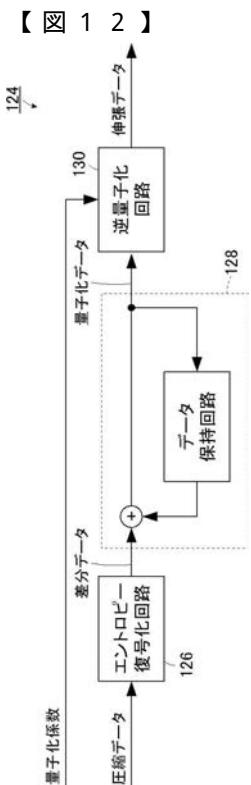

図11は、図10Aに示す符号化回路の構成を表す一例のブロック図である。図11に示す符号化回路116は、量子化回路118と、第1の予測回路120と、エントロピー符号化回路122とを備えている。

10

20

30

40

50

## 【0015】

符号化回路116では、量子化回路118により、量子化係数に基づいて、画像データを量子化することにより量子化データが生成される。続いて、第1の予測回路120により、量子化回路118によって生成された量子化データから、データ保持回路に保持された現在の画像よりも時間的に前の画像に対応する量子化データを減算することにより差分データが生成される。そして、エントロピー符号化回路122により、差分データをエントロピー符号化することにより圧縮データが生成される。

## 【0016】

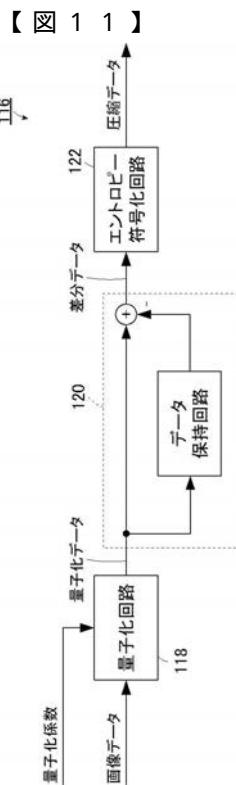

図12は、図10Bに示す復号化回路の構成を表す一例のブロック図である。図12に示す復号化回路124は、エントロピー復号化回路126と、第2の予測回路128と、逆量子化回路130とを備えている。10

## 【0017】

復号化回路124では、エントロピー復号化回路126により、圧縮データをエントロピー復号化することにより差分データが生成される。続いて、第2の予測回路128により、エントロピー復号化回路126によって生成された差分データと、データ保持回路に保持された現在の画像よりも時間的に前の画像に対応する量子化データとを加算することにより量子化データが生成される。そして、逆量子化回路130により、量子化データを逆量子化することにより伸張データが生成される。

## 【0018】

量子化および逆量子化の演算式は、例えば、式(1)および式(2)に示す通りである。20

量子化は、例えば、画像データを丸めて、その下位ビット成分を切り捨てる単純なものとする。

## 【0019】

量子化 : Quant = Floor ((In + Q/2) / Q) ... 式(1)

逆量子化 : DeQuant = Quant \* Q ... 式(2)

ここで、Inは入力データ、Qは量子化係数の値である。

## 【0020】

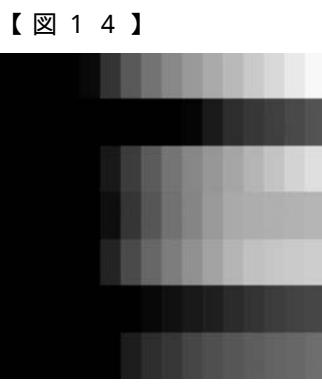

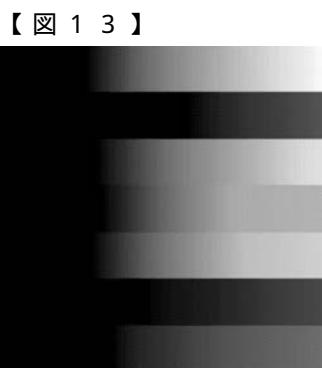

しかし、前述した画像データの下位ビット成分を切り捨てる量子化では、量子化係数の値Qが大きくなると、図13に示すように、圧縮処理前の画像の階調は滑らかに変化しているが、図14に示すように、圧縮伸張後の画像の階調は階段状に変化しており、画質の劣化が明らかである。この理由は、量子化および逆量子化後の値が入力値によって一意に決まることにより、圧縮伸張後の画像では、圧縮処理前の画像の滑らかな階調がつぶれるためである。30

## 【0021】

これに対し、量子化誤差による視覚的な画像の劣化を抑える、ディザリングと呼ばれる技術がある。ディザリングとは、量子化を行う際に、画像データの下位ビット成分を切り捨てて単純に丸めるのではなく、例えば、画像データにおいて、視覚的な誤差が小さくなるように、下位ビット成分の切り捨てまたは切り上げを制御することである。ディザリングの一つに乱数ディザリングがある。

## 【0022】

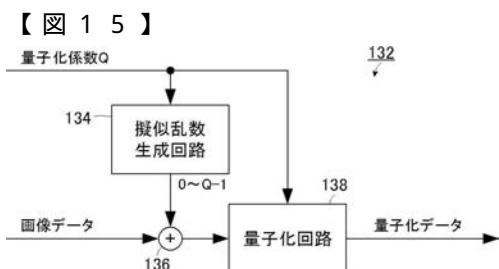

図15は、乱数ディザリング回路の構成を表す一例のブロック図である。図15に示す乱数ディザリング回路132は、擬似乱数生成回路134と、加算器136と、量子化回路138とを備えている。40

## 【0023】

乱数ディザリング回路132では、擬似乱数生成回路134により、量子化係数の値Qに基づいて、0～量子化係数の値Q-1の範囲の擬似乱数が生成される。続いて、加算器136により、画像データと、擬似乱数とを加算することにより加算データが生成される。そして、量子化回路138により、量子化係数に基づいて、加算データを量子化することにより量子化データが生成される。

## 【0024】

量子化および逆量子化の演算式は、例えば、式(3)および式(4)に示す通りである。乱数ディザリング回路132では、画像データの丸め処理の代わりに擬似乱数の加算が行われる。

#### 【0025】

量子化 : Quant = Floor ((In + Rand(Q)) / Q) ... 式(3)

逆量子化 : DeQuant = Quant \* Q ... 式(4)

ここで、Rand(Q)は、擬似乱数生成回路134により、量子化係数の値Qに基づいて生成される擬似乱数である。

#### 【0026】

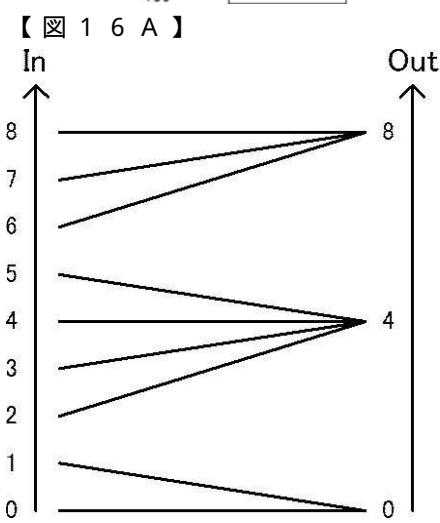

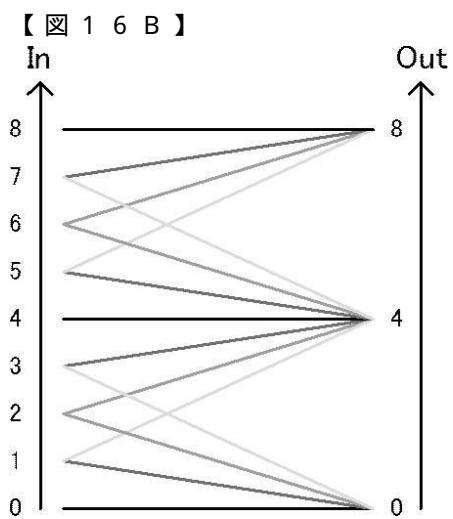

式(1)および式(2)に示すように、画像データの下位ビット成分を切り捨てる単純な量子化では、図16Aに示すように、入力データの値Inに対して出力データの値Outが一意に決まる。図16Aおよび図16Bにおいて、量子化係数の値Q=4である。

10

#### 【0027】

一方、式(3)および式(4)に示すように、乱数ディザリングによる量子化の場合、出力データの値Outは入力データの値Inの近傍の値に確率的に決まり、空間的または時間的に見ると、平均値は保存される。図16Bに示すように、例えば、入力データの値Inが3のとき、出力データの値Outが0に量子化される確率が25%、4に量子化される確率が75%となるようにすると、出力データの値Outの平均値は3となる。この「平均的には可逆となる」性質により画像の見た目の劣化を減らすことができる。

20

#### 【0028】

図17は、従来の乱数ディザリングによる量子化によって圧縮伸張後に得られた画像である。図17に示す画像は、図13に示す画像に対して従来の乱数ディザリングを適用したものであり、図14に示す画像と比べて、階段状の段差が大きく改善されていることが分かる。

20

#### 【0029】

しかしながら、乱数ディザリングによって量子化して得られた画像には、擬似乱数によるノイズが模様のように見えるという問題がある。これは、例えば、図16Bに示すように、入力値が0のときは必ず0に量子化され、入力値が1のときは25% : 75%の確率でディザリングされ、入力値が2のときは50% : 50%の確率でディザリングされるというように、入力値の階調によってディザリングのされ方が異なるためである。そのため、量子化誤差に偏りが生じ、模様のように見える。

30

#### 【0030】

また、本発明に関連性のある先行技術文献として、特許文献1~5がある。

例えば、特許文献1には、乱数を用いてディザリングを行うことにより、擬似輪郭および階調の段差が波打ちとして視認される波打ち現象を解消することが記載されている。

また、特許文献2には、複数のライン間において量子化の方式を切換えることにより、垂直方向のディザリングの効果を得ることが記載されている。

30

#### 【先行技術文献】

#### 【特許文献】

#### 【0031】

40

【特許文献1】特開2013-195784号公報

【特許文献2】特開2003-44847号公報

【特許文献3】特開昭61-161871号公報

【特許文献4】特開平5-219384号公報

【特許文献5】特開2006-50299号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0032】

本発明の目的は、圧縮伸張後の画像において、階調が階段状に変化したり、擬似乱数によるノイズの偏りによって模様が発生したりするのを防止し、高画質な画像を得ることが

50

できる画像処理装置を提供することにある。

【課題を解決するための手段】

【0033】

上記目的を達成するために、本発明は、第1の画像データに対応する画像のラインまたはブロック毎に、第1の画像同期信号に基づいて、前記ラインまたはブロックの番号に対応する第1の乱数シードを生成する第1の乱数シード生成回路と、

前記ラインまたはブロックに対応する画素毎に、前記第1の乱数シードに基づいて第1の擬似乱数を生成し、前記第1の画像データと前記第1の擬似乱数との加算データを量子化して符号化することにより圧縮データを生成する画像圧縮回路と、

前記圧縮データを格納する画像メモリと、

10

第2の画像同期信号を生成する同期信号生成回路と、

前記ラインまたはブロック毎に、前記第2の画像同期信号に基づいて、前記ラインまたはブロックの番号に対応し、かつ、前記第1の乱数シードと等しい第2の乱数シードを生成する第2の乱数シード生成回路と、

前記ラインまたはブロックに対応する画素毎に、前記画像メモリから読み出された圧縮データを復号化して逆量子化することにより伸張データを生成し、前記第2の乱数シードに基づいて前記第1の擬似乱数と等しい第2の擬似乱数を生成し、前記伸張データから前記第2の擬似乱数を減算することにより第2の画像データを生成する画像伸張回路とを備える画像処理装置を提供する。

【0034】

20

また、前記第1の乱数シード生成回路は、

前記ラインまたはブロック毎に、送信側回路から受信した前記第1の画像同期信号に基づいて、前記送信側回路から受信した前記第1の画像データに対応する画像のラインまたはブロックの番号を生成する第1の番号生成回路と、

前記ラインまたはブロック毎に、前記第1の番号生成回路によって生成されたラインまたはブロックの番号を、第1の変換式に基づいて変換することにより前記第1の乱数シードを生成する第1の番号変換回路とを備え、

前記第2の乱数シード生成回路は、

前記ラインまたはブロック毎に、前記第2の画像同期信号に基づいて、前記画像メモリから読み出された圧縮データに対応する画像のラインまたはブロックの番号を生成する第2の番号生成回路と、

30

前記ラインまたはブロック毎に、前記第2の番号生成回路によって生成されたラインまたはブロックの番号を、前記第1の変換式と等しい第2の変換式に基づいて変換することにより前記第2の乱数シードを生成する第2の番号変換回路とを備えることが好ましい。

【0035】

40

また、前記第1の番号変換回路は、前記第1の番号生成回路によって生成されたラインまたはブロックの番号を、フレーム毎に異なる前記第1の変換式に基づいて変換し、

前記第2の番号変換回路は、前記第2の番号生成回路によって生成されたラインまたはブロックの番号を、前記フレーム毎に前記第1の変換式と等しい第2の変換式に基づいて変換することが好ましい。

【0036】

また、前記第1の乱数シード生成回路は、前記送信側回路から受信した開始ラインまたは開始ブロックの情報に対応する開始ラインまたは開始ブロックから前記第1の乱数シードを生成し、

前記画像圧縮回路は、前記開始ラインまたは前記開始ブロックから前記圧縮データを生成し、

前記画像メモリは、前記開始ラインまたは前記開始ブロックから前記圧縮データを格納することが好ましい。

【0037】

50

また、前記画像圧縮回路は、前記第1の画像データを符号化することにより前記圧縮デ

ータを生成する符号化回路を備え、

前記符号化回路は、前記ラインまたはブロックに対応する画素毎に、前記第1の乱数シードおよび量子化係数に基づいて前記第1の擬似乱数を生成する第1の擬似乱数生成回路と、

前記画素毎に、前記第1の画像データと前記第1の擬似乱数とを加算することにより前記加算データを生成する第1の加算器と、

前記画素毎に、前記量子化係数を用いて、前記加算データを量子化することにより第1の量子化データを生成する量子化回路と、

前記画素毎に、前記第1の量子化データをエントロピー符号化することにより前記圧縮データを生成するエントロピー符号化回路とを備え、

前記画像伸張回路は、前記画像メモリから読み出された圧縮データを復号化することにより前記伸張データを生成する復号化回路を備え、

前記復号化回路は、前記画素毎に、前記画像メモリから読み出された圧縮データをエントロピー復号化することにより第2の量子化データを生成するエントロピー復号化回路と、

前記画素毎に、前記量子化係数を用いて、前記第2の量子化データを逆量子化することにより前記伸張データを生成する逆量子化回路と、

前記画素毎に、前記第2の乱数シードおよび前記量子化係数に基づいて前記第2の擬似乱数を生成する第2の擬似乱数生成回路と、

前記画素毎に、前記伸張データから前記第2の擬似乱数を減算することにより前記第2の画像データを生成する第1の減算器とを備えることが好ましい。

#### 【0038】

前記符号化回路は、さらに、前記画素毎に、前記量子化回路によって生成された第1の量子化データから、現在の画像よりも前の画像に対応する前記第1の量子化データを減算することにより第1の差分データを生成する第1の予測回路を備え、

前記エントロピー符号化回路は、前記第1の差分データをエントロピー符号化することにより前記圧縮データを生成し、

前記エントロピー復号化回路は、前記画像メモリから読み出された圧縮データをエントロピー復号化することにより第2の差分データを生成し、

前記復号化回路は、さらに、前記画素毎に、前記エントロピー復号化回路によって生成された第2の差分データと、現在の画像よりも前の画像に対応する第2の量子化データとを加算することにより前記第2の量子化データを生成する第2の予測回路を備えることが好ましい。

#### 【0039】

また、前記第1の画像データは、RGB色空間の画像データであり、

前記画像圧縮回路は、さらに、前記RGB色空間の第1の画像データを、YUV色空間の第3の画像データとして、第3のY画像データ、第3のU画像データおよび第3のV画像データに変換する色空間変換回路と、

前記量子化係数として、前記第3のY画像データ、第3のU画像データおよび第3のV画像データに対応するY量子化係数、U量子化係数およびV量子化係数を生成する、量子化係数生成回路とを備え、

前記符号化回路は、前記圧縮データとして、前記第3のY画像データ、第3のU画像データおよび第3のV画像データに対応するY圧縮データ、U圧縮データおよびV圧縮データを生成する第1、第2および第3の符号化回路を備え、

前記画像メモリは、前記符号化回路によって生成されたY圧縮データ、U圧縮データおよびV圧縮データと、前記量子化係数生成回路によって生成されたY量子化係数、U量子化係数およびV量子化係数とを格納し、

前記復号化回路は、前記第2の画像データとして、前記画像メモリから読み出されたY圧縮データ、U圧縮データおよびV圧縮データに対応する第2のY画像データ、第2のU画像データおよび第2のV画像データを生成する第1、第2および第3の復号化回路を備え、

10

20

30

40

50

前記画像伸張回路は、さらに、前記復号化回路によって生成されたYUV色空間の第2の画像データを、RGB色空間の第4の画像データに変換する逆色空間変換回路を備えることが好ましい。

#### 【0040】

また、前記第1の乱数シード生成回路は、前記第1の乱数シードとして、前記第3のY画像データ、第3のU画像データおよび第3のV画像データに対応する第1のY乱数シード、第1のU乱数シードおよび第1のV乱数シードを生成し、

前記量子化係数生成回路は、前記量子化係数として、前記第3のY画像データ、第3のU画像データおよび第3のV画像データに対応するY量子化係数、U量子化係数およびV量子化係数を生成し、

前記第1、第2および第3の符号化回路は、それぞれ、前記第1のY乱数シード、第1のU乱数シードおよび第1のV乱数シードと、前記Y量子化係数、U量子化係数およびV量子化係数とに基づいて、前記第3のY画像データ、第3のU画像データおよび第3のV画像データを符号化することにより前記Y圧縮データ、U圧縮データおよびV圧縮データを生成し、

前記第2の乱数シード生成回路は、前記第2の乱数シードとして、前記画像メモリから読み出されたY圧縮データ、U圧縮データおよびV圧縮データに対応する第2のY乱数シード、第2のU乱数シードおよび第2のV乱数シードを生成し、

前記第1、第2および第3の復号化回路は、それぞれ、第2のY乱数シード、第2のU乱数シードおよび第2のV乱数シードと、前記Y量子化係数、U量子化係数およびV量子化係数とに基づいて、前記画像メモリから読み出されたY圧縮データ、U圧縮データおよびV圧縮データを復号化することにより、前記第2の画像データとして、第2のY画像データ、第2のU画像データおよび第2のV画像データを生成することが好ましい。

#### 【発明の効果】

#### 【0041】

本発明では、第1および第2の乱数シード生成回路が、画像圧縮回路および画像伸張回路に対してライン毎に、等しい乱数シードを生成し、画像圧縮回路及び画像伸張回路が、乱数シードに基づいて画素毎に擬似乱数を生成する。そして、画像圧縮回路では、画像データと擬似乱数との加算データを量子化係数で量子化することにより圧縮データを生成し、画像伸張回路では、量子化係数で逆量子化後の伸張データから擬似乱数を減算する。これにより、本発明によれば、圧縮伸張後の画像において、階調が階段状に変化したり、擬似乱数によるノイズの偏りによって模様が発生したりするのを防止することができ、従来よりも視覚的に良好な表示品質を得ることができる。

#### 【0042】

また、本発明では、画像同期信号に基づいて、画像の各々のラインまたはブロックの番号に対応する乱数シードを生成する。これにより、本発明によれば、画像圧縮回路16と画像伸張回路24との間で乱数シードを共有するために、例えば、圧縮データに乱数シードを埋め込む必要がないため、圧縮データのデータ量を増やすことなく、画像圧縮回路と画像伸張回路との間で乱数シードを共有することができる。

#### 【図面の簡単な説明】

#### 【0043】

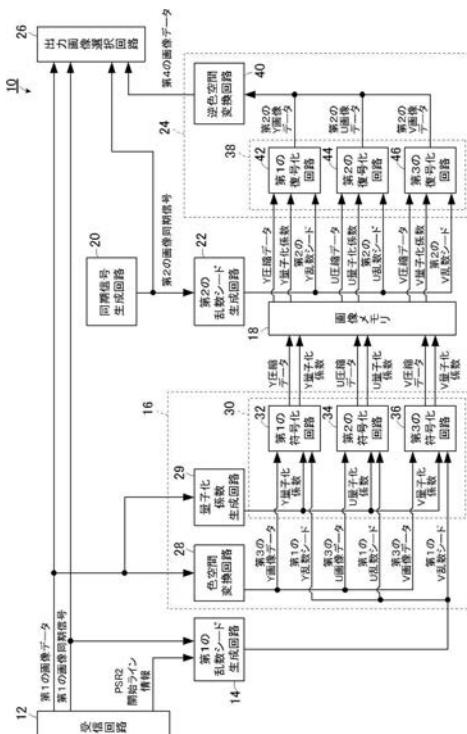

【図1】本発明の画像処理装置の構成を表す一実施形態のブロック図である。

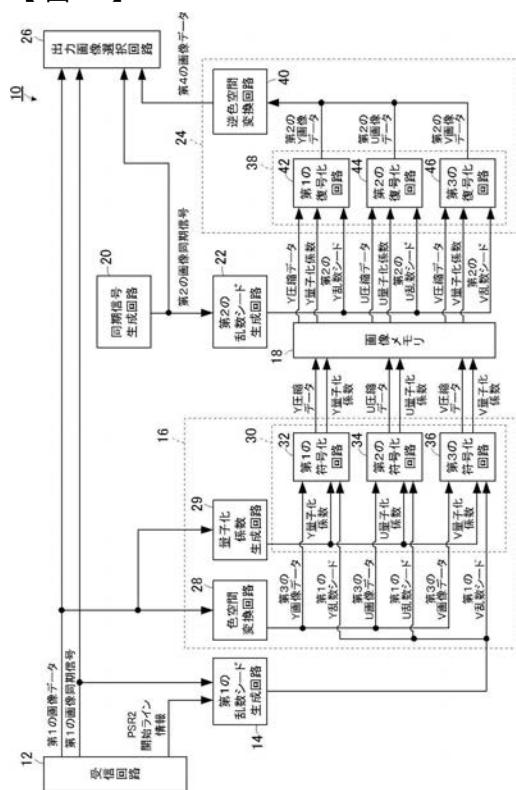

【図2】図1に示す量子化係数生成回路の周辺の構成を表す一例のブロック図である。

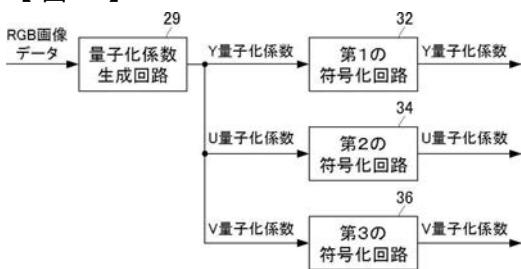

【図3】図1に示す第1の乱数シード生成回路の構成を表す一実施形態のブロック図である。

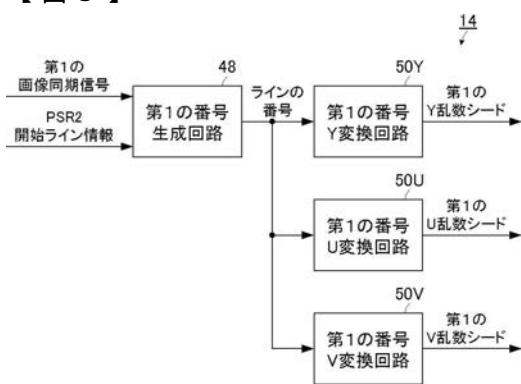

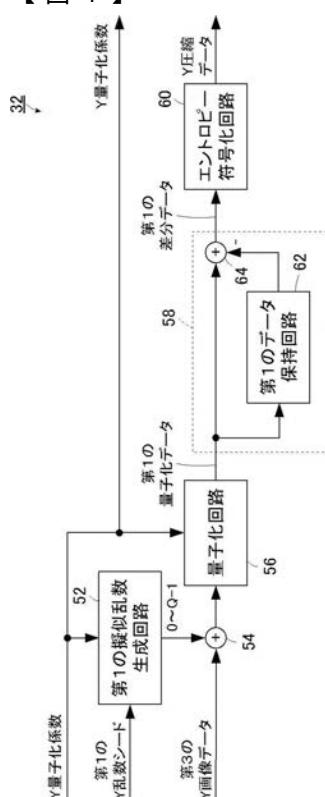

【図4】図1に示す第1の符号化回路の構成を表す一実施形態のブロック図である。

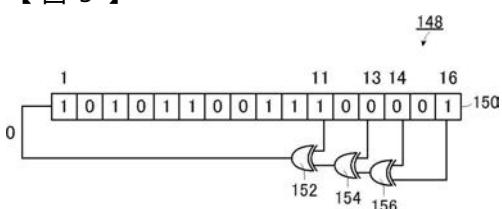

【図5】線形帰還シフトレジスタの構成を表す一例の回路図である。

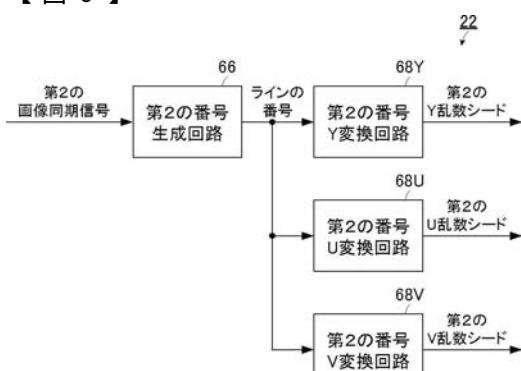

【図6】図1に示す第2の乱数シード生成回路の構成を表す一実施形態のブロック図である。

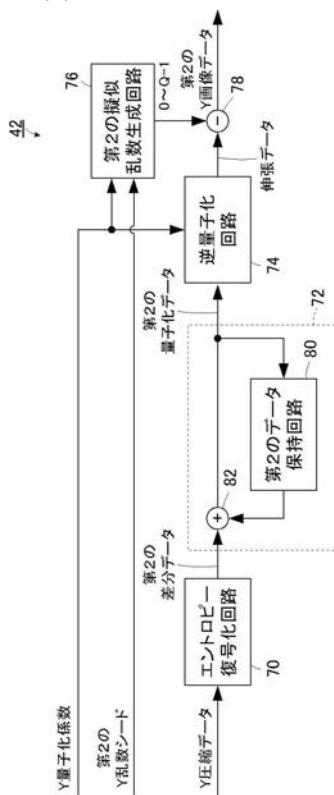

【図7】図1に示す第1の復号化回路の構成を表す一実施形態のブロック図である。

10

20

30

40

50

【図8】本発明の乱数ディザリングによる圧縮伸張後に得られた画像を表す一例である。

【図9】液晶表示装置の画像処理装置の構成を表す一例のブロック図である。

【図10A】図9に示す画像圧縮回路の構成を表す一例のブロック図である。

【図10B】図9に示す画像伸張回路の構成を表す一例のブロック図である。

【図11】図10Aに示す符号化回路の構成を表す一例のブロック図である。

【図12】図10Bに示す復号化回路の構成を表す一例のブロック図である。

【図13】階調が滑らかに変化する、圧縮処理前の画像を表す一例である。

【図14】図13に示す画像に対して、画像データの下位ビット成分を切り捨てる従来の量子化によって得られた圧縮伸張後の画像を表す一例である。

【図15】乱数ディザリング回路の構成を表す一例のブロック図である。 10

【図16A】従来の画像データの下位ビット成分を切り捨てる量子化によって得られた画像データの値を表す一例の概念図である。

【図16B】従来の乱数ディザリングによる量子化によって得られた画像データの値を表す一例の概念図である。

【図17】従来の乱数ディザリングによる量子化によって圧縮伸張後に得られた一例の画像である。

#### 【発明を実施するための形態】

##### 【0044】

以下に、添付の図面に示す好適実施形態に基づいて、本発明の画像処理装置を詳細に説明する。 20

##### 【0045】

図1は、本発明の画像処理装置の構成を表す一実施形態のブロック図である。図1に示す画像処理装置10は、エンベデットディスプレイポートの規格に準拠して、画像出力装置の送信側回路から伝送路を介して送信される画像データを圧縮伸張処理する受信側回路であり、受信回路12と、第1の乱数シード生成回路14と、画像圧縮回路16と、画像メモリ18と、同期信号生成回路20と、第2の乱数シード生成回路22と、画像伸張回路24と、出力画像選択回路26とを備えている。

##### 【0046】

エンベデットディスプレイポートは、GPU(Graphics Processing Unit：グラフィックスプロセッシングユニット)等で生成された、画像出力装置の出力を画像表示装置に接続するためのインターフェイス規格の一つであり、映像信号のインターフェイス規格に関する標準化団体VESA(Video Electronics Standards Association)によって策定されたものである。ディスプレイポートでは、最大4レーンのメインリンク、および、補助チャンネルからなる伝送路によって、送信側回路と受信側回路との間が接続され、画像データ等がパケット化されたシリアルデータが送受信される。 30

##### 【0047】

受信回路12は、送信側回路から送信される第1の画像データ、第1の画像同期信号、PSR2開始ライン情報等を受信する。

##### 【0048】

第1の画像同期信号は、第1の画像データに対応する画像を画像表示装置に表示する場合に、画像の水平方向および垂直方向の表示タイミング等を決定する信号である。 40

PSR2の機能によって画像を表示する場合、更新する矩形領域の位置を表す情報が送信側回路から受信側回路に送信される。PSR2開始ライン情報は、更新する矩形領域の位置を表す情報のうち、更新する矩形領域の開始ラインの番号を表す情報である。

##### 【0049】

続いて、第1の乱数シード生成回路14は、受信回路12によって受信された第1の画像データに対応する画像のライン毎に、同じく受信回路12によって受信された第1の画像同期信号に基づいて、ラインの番号に対応する第1の乱数シードを生成する。

##### 【0050】

本実施形態の場合、第1の乱数シード生成回路14は、第1の乱数シードとして、後述

10

20

30

40

50

する色空間変換回路28によって変換されたYUV色空間の第3のY画像データ、第3のU画像データおよび第3のV画像データに対応する第1のY乱数シード、第1のU乱数シードおよび第1のV乱数シードを生成する。

#### 【0051】

続いて、画像圧縮回路16は、ラインに対応する画素毎に、第1の乱数シード生成回路14によって生成された第1の乱数シードと、量子化係数生成回路によって生成された量子化係数に基づいて第1の擬似乱数を生成し、第3の画像データと第1の擬似乱数との加算データを量子化係数で量子化して符号化することにより圧縮データを生成する。画像圧縮回路16は、色空間変換回路28と、量子化係数生成回路29と、符号化回路30とを備えている。

10

#### 【0052】

色空間変換回路28は、RGB色空間の第1の画像データを、YUV色空間の第3の画像データに変換する。

#### 【0053】

本実施形態の場合、色空間変換回路28は、YUV色空間の第3の画像データとして、RGB色空間の第1の画像データを、第3のY画像データ、第3のU画像データおよび第3のV画像データに変換する。

#### 【0054】

量子化係数生成回路29は、RGB色空間の第1の画像データから、圧縮率を演算し、ラインまたは画素毎にYUVの量子化係数を生成する。

20

#### 【0055】

本実施形態の場合、量子化係数生成回路29は、図2に示すように、YUVの量子化係数として、RGB色空間の第1の画像データから、色空間変換回路28によって変換された第3のY画像データ、第3のU画像データおよび第3のV画像データに対応するY量子化係数、U量子化係数およびV量子化係数を生成する。

#### 【0056】

量子化係数生成回路29によって生成されたY量子化係数、U量子化係数およびV量子化係数は、それぞれ、符号化回路30の第1、第2および第3の符号化回路32，34，36に入力される。また、第1、第2および第3の符号化回路32，34，36に入力されたY量子化係数、U量子化係数およびV量子化係数は、それぞれ、第1、第2および第3の符号化回路32，34，36から出力される。

30

#### 【0057】

なお、図2では、第1、第2および第3の符号化回路32，34，36に対する入出力信号のうち、Y量子化係数、U量子化係数およびV量子化係数のみを図示し、それ以外の信号の図示を省略している。

#### 【0058】

続いて、符号化回路30は、第1の乱数シードと量子化係数に基づいて、色空間変換回路28によって変換されたYUV色空間の第3の画像データを符号化することにより圧縮データを生成する。符号化回路30は、第1、第2および第3の符号化回路32，34，36を備えている。

40

#### 【0059】

第1、第2および第3の符号化回路32，34，36は、それぞれ、第1の乱数シード生成回路14によって生成された第1のY乱数シード、第1のU乱数シードおよび第1のV乱数シードと、量子化係数生成回路29によって生成されたY量子化係数、U量子化係数およびV量子化係数に基づいて、画素毎に、第1の擬似乱数を生成し、色空間変換回路28によって変換された第3のY画像データ、第3のU画像データおよび第3のV画像データと第1の擬似乱数とを加算して加算データを生成し、加算データをY量子化係数、U量子化係数およびV量子化係数で量子化して量子化データを生成し、量子化データから現在の画像よりも時間的に前の画像に対応する量子化データを減算して差分データを生成し、差分データをエントロピー符号化することにより、対応するY圧縮データ、U圧縮データおよびV圧

50

縮データを生成する。

**【0060】**

続いて、画像メモリ18は、符号化回路30によって生成された圧縮データと、量子化係数とを格納する。

**【0061】**

本実施形態の場合、画像メモリ18は、圧縮データとして、それぞれ、第1、第2および第3の符号化回路32，34，36によって生成されたY圧縮データ、U圧縮データおよびV圧縮データと、Y量子化係数、U量子化係数及びV量子化係数とを格納する。

また、画像メモリ18に格納されたY圧縮データ、U圧縮データおよびV圧縮データと、Y量子化係数、U量子化係数及びV量子化係数とは、画像の表示タイミングに応じて順次読み出される。

10

**【0062】**

続いて、同期信号生成回路20は、第2の画像同期信号を生成する。

**【0063】**

第2の画像同期信号は、PSRまたはPSR2の機能によって、画像メモリ18から読み出された圧縮データに対応する画像を画像表示装置に表示する場合に、画像の水平方向および垂直方向の表示タイミング等を決定する信号である。

**【0064】**

続いて、第2の乱数シード生成回路22は、ライン毎に、同期信号生成回路20によって生成された第2の画像同期信号に基づいて、ラインの番号に対応し、かつ、第1の乱数シードと等しい第2の乱数シードを生成する。

20

**【0065】**

本実施形態の場合、第2の乱数シード生成回路22は、第2の乱数シードとして、画像メモリ18から読み出されたY圧縮データ、U圧縮データおよびV圧縮データに対応する第2のY乱数シード、第2のU乱数シードおよび第2のV乱数シードを生成する。

**【0066】**

続いて、画像伸張回路24は、ラインに対応する画素毎に、画像メモリ18から読み出された圧縮データを復号化し、読み出した量子化係数で逆量子化することにより伸張データを生成し、第2の乱数シード生成回路22によって生成された第2の乱数シードと量子化係数とに基づいて第1の擬似乱数と等しい第2の擬似乱数を生成し、伸張データから第2の擬似乱数を減算することにより第2の画像データを生成する。画像伸張回路24は、復号化回路38と、逆色空間変換回路40とを備えている。

30

**【0067】**

復号化回路38は、第2の乱数シードと量子化係数とに基づいて画素毎に第2の擬似乱数を生成し、画像メモリ18から読み出された圧縮データを復号化し、量子化係数で逆量子化することにより伸張データを生成する。復号化回路38は、第1、第2および第3の復号化回路42，44，46を備えている。

**【0068】**

第1、第2および第3の復号化回路42，44，46は、それぞれ、第2の乱数シード生成回路22によって生成された第2のY乱数シード、第2のU乱数シードおよび第2のV乱数シードと、Y量子化係数、U量子化係数及びV量子化係数とに基づいて、画素毎に第2の擬似乱数を生成し、画像メモリ18から読み出されたY圧縮データ、U圧縮データおよびV圧縮データを、それぞれ、エントロピー復号化して差分データを生成し、差分データと現在の画像よりも時間的に前の画像に対応する量子化データとを加算して量子化データを生成し、量子化データを、Y量子化係数、U量子化係数及びV量子化係数に従って逆量子化して、伸張データを生成し、伸張データから第2の擬似乱数を減算することにより、YUV色空間の第2の画像データとして、第2のY画像データ、第2のU画像データおよび第2のV画像データを生成する。

40

**【0069】**

続いて、逆色空間変換回路40は、復号化回路38によって生成されたYUV色空間の第

2の画像データを、RGB色空間の第4の画像データに変換する。

【0070】

本実施形態の場合、逆色空間変換回路40は、第1、第2および第3の復号化回路42, 44, 46によって生成されたYUV色空間の第2のY画像データ、第2のU画像データおよび第2のV画像データを、RGB色空間の第4の画像データに変換する。

【0071】

続いて、出力画像選択回路26は、PSRまたはPSR2の機能によって画像を表示する場合以外の通常動作の場合に、受信回路12によって受信された第1の画像データおよび第1の画像同期信号を出力し、PSRまたはPSR2の機能によって画像を表示する場合に、画像伸張回路24によって生成された第4の画像データ、および、同期信号生成回路20によって生成された第2の画像同期信号を出力する。

10

【0072】

次に、図3は、図1に示す第1の乱数シード生成回路の構成を表す一実施形態のブロック図である。図3に示す第1の乱数シード生成回路14は、第1の番号生成回路48と、第1の番号Y変換回路50Yと、第1の番号U変換回路50Uと、第1の番号V変換回路50Vとを備えている。

【0073】

第1の番号生成回路48は、ライン毎に、受信回路12によって受信された第1の画像同期信号に基づいて、同じく受信回路12によって受信された第1の画像データに対応する画像のラインの番号を生成する。

20

【0074】

第1の番号生成回路48は、PSRの機能によって画像を表示する場合、例えば、第1の画像同期信号に含まれるVsync(Vertical Synchronization Signal: 垂直同期信号)を基準としてラインの番号を0にリセットし、第1の画像同期信号に含まれるDE(Data Enable Signal: データイネーブル信号)を基準としてラインの番号をカウントアップすることにより、画像の各々のラインに対応するラインの番号を生成する。

【0075】

また、PSR2の機能によって画像を表示する場合、例えば、PSR2開始ライン情報に基づいて、ラインの番号として、更新する矩形領域の開始ラインの番号をセットし、DEを基準としてラインの番号をカウントアップすることにより、更新する矩形領域の各々のラインに対応するラインの番号を生成する。

30

【0076】

続いて、第1の番号Y変換回路50Yは、ライン毎に、第1の番号生成回路48によって生成されたラインの番号を、第1の変換式に基づいて変換することにより第1のY乱数シードを生成する。

【0077】

第1の番号Y変換回路50Yは、ライン間において第1のY乱数シードが近い値になることにより、後述する第1の擬似乱数生成回路52によって生成されるライン間の擬似乱数列が相関を持つことを防ぎ、偏りがなく品質のよい擬似乱数列を得る目的で配置される。

第1の変換式は、あらかじめ第1の番号Y変換回路50Yの内部に設定されているものとする。

40

【0078】

第1の番号Y変換回路50Yにおいて使用される第1の変換式の一例を式(5)～式(7)に示す。

【0079】

```

V0 = ((not L) << 8) xor L ... 式(5)

V1 = 0x5a82 * (V0 xor (V0 << 9) xor (V0 << 3)) ... 式(6)

S = (V1 >> 4) and 0xffff ... 式(7)

```

ここで、Lはライン番号、Sは第1のY乱数シード(16ビット)、V0, V1は中間変数であり、notはビット反転、andは論理積、xorは排他的論理和、<<は左ビットシフト、>>は

50

右ビットシフト、\*は乗算を意味する。

#### 【0080】

第1の変換式によって算出された第1のY乱数シードの値を表1に示す。

#### 【0081】

#### 【表1】

| (表1)      |       |       |       |       |       |       |       |       |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

| ラインの番号    | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7     |

| 第1のY乱数シード | 22752 | 37993 | 53234 | 44027 | 51460 | 33421 | 33046 | 56095 |

#### 【0082】

また、第1の変換式を変更することにより、第1の番号Y変換回路50Yによって生成される第1のY乱数シードの値が変化し、乱数ディザリングのパターンを変化させることができる。これを利用して、例えば、第1の番号生成回路48によって生成されたラインの番号を、フレーム毎に異なる第1の変換式に基づいて変換し、フレーム毎に、乱数ディザリングのパターンを変化させることにより、後述する量子化回路56によって生成される第1の量子化データの量子化誤差を時間軸方向に平均化させることもできる。

#### 【0083】

画像の各々のラインの番号に対応する乱数シードを生成する理由は、PSR2の機能によって画像を表示する場合に、ライン単位で独立して画像データの符号化、復号化を行う必要があるためである。ラインの番号に対応する乱数シードを生成することにより、画像圧縮回路16と画像伸張回路24との間で乱数シードを共有するために、例えば、圧縮データに乱数シードを埋め込む必要がないため、圧縮データのデータ量を増やすことなく、画像圧縮回路16と画像伸張回路24との間で乱数シードを共有することができる。

#### 【0084】

第1の番号U変換回路50Uおよび第1の番号V変換回路50Vは、それぞれ、第1のY乱数シードを生成する代わりに、第1のU乱数シードおよび第1のV乱数シードを生成する点を除いて、第1の番号Y変換回路50Yと同様の構成である。

#### 【0085】

次に、図4は、図1に示す第1の符号化回路の構成を表す一実施形態のブロック図である。図4に示す第1の符号化回路32は、第1の擬似乱数生成回路52と、第1の加算器54と、量子化回路56と、第1の予測回路58と、エントロピー符号化回路60とを備えている。

#### 【0086】

第1の擬似乱数生成回路52は、画素毎に、第1の乱数シード生成回路14によって生成された第1のY乱数シードおよびY量子化係数に基づいて、0~Y量子化係数の値Q-1の範囲の第1の擬似乱数を生成する。

#### 【0087】

擬似乱数の生成には、線形帰還シフトレジスタ(LFSR : Linear Feedback Shift Register)を用いる擬似乱数生成方法が用いられる。

#### 【0088】

図5は、線形帰還シフトレジスタの構成を表す一例の回路図である。図5に示す線形帰還シフトレジスタ148は、16ビットのシフトレジスタ150と、3つのEXOR回路152, 154, 156とを備えている。

#### 【0089】

線形帰還シフトレジスタ148では、ライン毎に、第1のY乱数シードの値 $X_0$ がシフトレジスタ150にセットされる。これにより、シフトレジスタ150の初期値が、ライン毎に、第1のY乱数シードの値 $X_0$ にリセットされる。

#### 【0090】

続いて、シフトレジスタ150の左端のビットから1ビット目、2ビット目、...、16ビット目のビットとすると、式(8)に示すように、画素毎に、次に1ビット目のビット

10

20

30

40

50

に入力される新しい値 $X_n[1]$ (nは画素の番号を表す)として、EXOR回路152, 154, 156により、シフトレジスタ150にセットされた第1のY乱数シードの値 $X_0$ のうち、11ビット目のビット、13ビット目のビット、14ビット目のビットおよび16ビット目のビットからなる4ビットの値の排他的論理和が算出される。図5の例の場合、11ビット目のビット、13ビット目のビット、14ビット目のビットおよび16ビット目のビットの値は、それぞれ、1, 0, 0, 1であり、EXOR回路156, 154, 152の出力信号は、それぞれ、1, 1, 0となる。

#### 【0091】

続いて、新しい値 $X_n[1]$ がシフトレジスタ150の1ビット目のビットにセットされるとともに、式(9)に示すように、新しい値 $X_n[1]$ がシフトレジスタ150の1ビット目のビットに入力される前にシフトレジスタ150にセットされていた1ビット目～15ビット目のビットの値が、2ビット目から16ビット目のビットへ1ビットずつシフトされて、2ビット目～16ビット目のビットに新しい値 $X_n[i]$ (iはシフトレジスタ150の2ビット目～16ビット目のビット位置を表す)がセットされる。

#### 【0092】

続いて、式(10)に示すように、シフトレジスタ150にセットされた、 $X_n[1]$ および $X_n[i]$ からなる新しい値 $X_n$ を、Y量子化係数の値Qで除算した結果の余りが乱数Rand(Q)として算出される。

#### 【0093】

これ以後、次のラインの第1のY乱数シードの値が入力されるまで、画素毎に、上記動作が繰り返されて、シフトレジスタ150にセットされた16ビットの値が順次更新され、擬似乱数が生成される。

#### 【0094】

$$X_n[1] = X_{n-1}[16] \text{ xor } X_{n-1}[14] \text{ xor } X_{n-1}[13] \text{ xor } X_{n-1}[11] \dots \text{ 式 (8)}$$

$$X_n[i] = X_{n-1}[i-1] \quad (i=2 \sim 16 \text{ の整数}) \dots \text{ 式 (9)}$$

$$\text{Rand}(Q) = X_n \bmod Q \dots \text{ 式 (10)}$$

ここで、modは、演算結果として除算の余りを出力する演算子である。

#### 【0095】

例えば、第1のY乱数シードの値=44257、Y量子化係数の値Q=8の場合、n番目の画素の処理に使う擬似乱数Rand(Q)は、表2のように生成される。

#### 【0096】

#### 【表2】

| (表2)    |       |       |       |       |       |       |       |       |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| n       | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7     |

| Xn      | 44257 | 22979 | 45959 | 26383 | 52766 | 39996 | 14457 | 28914 |

| Rand(Q) | 1     | 3     | 7     | 7     | 6     | 4     | 1     | 2     |

#### 【0097】

また、本実施形態の場合、量子化係数は、目標とする圧縮率を達成するために必要な値が、画像に基づいて、ラインまたは画素毎に量子化係数生成回路29で生成され、例えば、量子化係数を圧縮データに含めるなどして、画像メモリ18に記憶し符号化回路30と復号化回路38との間で共有されるものとする。

#### 【0098】

続いて、第1の加算器54は、画素毎に、第3のY画像データと、第1の擬似乱数生成回路52によって生成された第1の擬似乱数とを加算することにより加算データを生成する。

#### 【0099】

続いて、量子化回路56は、画素毎に、Y量子化係数を用いて、第1の加算器54によって生成された加算データを量子化することにより第1の量子化データを生成する。

#### 【0100】

続いて、第1の予測回路58は、画素毎に、量子化回路56によって生成された第1の

10

20

30

40

50

量子化データから、現在の画像よりも時間的に前の画像に対応する第1の量子化データを減算することにより第1の差分データを生成する。第1の予測回路58は、第1のデータ保持回路62と、第2の減算器64とを備えている。

#### 【0101】

第1のデータ保持回路62は、画素毎に、現在の画像よりも時間的に前の画像に対応する第1の量子化データを保持する。

#### 【0102】

続いて、第2の減算器64は、画素毎に、量子化回路56によって生成された第1の量子化データから、第1のデータ保持回路62に保持された第1の量子化データを減算することにより第1の差分データを生成する。

10

#### 【0103】

第1の予測回路58は、符号化効率を高める目的で使用される。写真およびCG(Computer Graphics:コンピュータグラフィックス)などの画像データは、一般に、隣り合う画素同士の値が似ている、つまり、相関があるという性質があり、隣り合う画素同士の差分はゼロに近い値に集中する。従って、隣り合う画素同士の画像データの差分を計算し、ゼロに近い値に対して短い符号を割り当てる可変長符号化を行うことにより、データ量を減らすことができる。

#### 【0104】

本実施形態の場合、第1の予測回路58は、時間的に隣り合う画素同士の第1の量子化データの差分を算出する。このように、隣り合う画素同士の第1の量子化データの差分を算出するのは、時間的に次の入力画素を予測する方法の最も簡単な例である。より複雑な予測方法としては、JPEG-LS規格の元とされたLOCO-Iアルゴリズムがある。予測の精度が高ければ、差分はよりゼロ付近に集中し、より短い符号に圧縮することができる。

20

#### 【0105】

続いて、エントロピー符号化回路60は、画素毎に、第1の予測回路58によって生成された第1の差分データをエントロピー符号化することによりY圧縮データを生成する。

#### 【0106】

エントロピー符号化とは、画像データの生起確率に応じて異なる長さの符号を割り当てるにより圧縮を行うものであり、可変長符号化とも呼ばれる。エントロピー符号化の簡単な例として、アルファ符号を例示することができる。アルファ符号における整数nは、式(11)に示すように、「0」のn-1回の繰り返しと、最下位ビットの「1」との合計nビットで表現され、nが小さいほど短い符号長となる。なお、ゴロム符号等のように、より効率的なエントロピー符号化方式を採用してもよい。

30

#### 【0107】

$$(n) = \text{「0」の } n-1 \text{ 回の繰り返し} + \text{「1」} \dots \text{ 式(11)}$$

#### 【0108】

第2および第3の符号化回路34, 36は、それぞれ、第1のY乱数シードの代わりに、第1のU乱数シードおよび第1のV乱数シードを用いる点と、Y量子化係数の代わりに、U量子化係数およびV量子化係数を用いる点と、第3のY画像データの代わりに、第3のU画像データおよび第3のV画像データを用いる点と、Y圧縮データの代わりに、U圧縮データおよびV圧縮データを生成する点とを除いて、第1の符号化回路32と同様の構成である。

40

#### 【0109】

本実施形態の場合、画像データに対して、JPEG( Joint Photographic Experts Group )において行われる周波数領域への変換を行わず、直接、量子化を適用する方式の圧縮処理を行うが、周波数領域への変換を行って量子化してもよい。また、画像データを量子化した後、さらにデータ量を減らすために、予測およびエントロピー符号化を行っているが、予測およびエントロピー符号化を行うことは必須ではない。

#### 【0110】

次に、図6は、図1に示す第2の乱数シード生成回路の構成を表す一実施形態のプロツ

50

ク図である。図6に示す第2の乱数シード生成回路22は、第2の番号生成回路66と、第2の番号Y変換回路68Yと、第2の番号U変換回路68Uと、第2の番号V変換回路68Vとを備えている。

#### 【0111】

第2の番号生成回路66は、ライン毎に、同期信号生成回路20によって生成された第2の画像同期信号に基づいて、画像メモリ18から読み出された圧縮データに対応する画像のラインの番号を生成する。

#### 【0112】

第2の番号生成回路66は、PSRまたはPSR2の機能によって画像を表示する場合に、例えば、第2の画像同期信号に含まれるVsyncを基準としてラインの番号を0にリセットし、第1の画像同期信号に含まれるDEを基準としてラインの番号をカウントアップすることにより、画像の各々のラインに対応するラインの番号を生成する。

10

#### 【0113】

続いて、第2の番号Y変換回路68Yは、ライン毎に、第2の番号生成回路66によって生成されたラインの番号を、第1の変換式と等しい第2の変換式に基づいて変換することにより第2のY乱数シードを生成する。

#### 【0114】

第2の変換式は、あらかじめ第2の番号Y変換回路68Yの内部に設定されているものとする。

第2の番号Y変換回路68Yは、ラインの番号を、第1の変換式と等しい第2の変換式を用いて変換することにより、ライン毎に、第1のY乱数シードと等しい第2のY乱数シードを生成することができる。

20

#### 【0115】

第2の番号U変換回路68Uおよび第2の番号V変換回路68Vは、それぞれ、第2のY乱数シードを生成する代わりに、第2のU乱数シードおよび第2のV乱数シードを生成する点を除いて、第2の番号Y変換回路68Yと同様の構成である。

#### 【0116】

次に、図7は、図1に示す第1の復号化回路の構成を表す一実施形態のプロック図である。図7に示す第1の復号化回路42は、エントロピー復号化回路70と、第2の予測回路72と、逆量子化回路74と、第2の擬似乱数生成回路76と、第1の減算器78とを備えている。

30

#### 【0117】

エントロピー復号化回路70は、画素毎に、画像メモリ18から読み出されたY圧縮データをエントロピー復号化することにより第2の差分データを生成する。

#### 【0118】

続いて、第2の予測回路72は、画素毎に、エントロピー復号化回路70によって生成された第2の差分データと、現在の画像よりも時間的に前の画像に対応する第2の量子化データとを加算することにより第2の量子化データを生成する。第2の予測回路72は、第2のデータ保持回路80と、第2の加算器82とを備えている。

#### 【0119】

第2のデータ保持回路80は、現在の画像よりも時間的に前の画像に対応する第2の量子化データを保持する。

#### 【0120】

続いて、第2の加算器82は、エントロピー復号化回路70によって生成された第2の差分データと、第2の予測回路72に保持された第2の量子化データとを加算することにより第2の量子化データを生成する。

#### 【0121】

本実施形態の場合、第2の予測回路72は、第1の予測回路58に応じて、時間的に隣り合う画素同士の第2の差分データと第2の量子化データとの和を算出する。

#### 【0122】

50

続いて、逆量子化回路74は、画素毎に、Y量子化係数を用いて、第2の予測回路72によって生成された第2の量子化データを逆量子化することにより伸張データを生成する。

#### 【0123】

続いて、第2の擬似乱数生成回路76は、画素毎に、第2の乱数シード生成回路22によって生成された第2のY乱数シードおよびY量子化係数に基づいて、0～Y量子化係数の値Q-1の範囲の第2の擬似乱数を生成する。

#### 【0124】

第2の擬似乱数生成回路76は、第1のY乱数シードと等しい第2のY乱数シードおよびY量子化係数を用いることにより、第1の擬似乱数と等しい第2の擬似乱数を生成することができる。

10

#### 【0125】

続いて、第1の減算器78は、画素毎に、逆量子化回路74によって生成された伸張データから、第2の擬似乱数生成回路76によって生成された第2の擬似乱数を減算することにより、第3のY画像データが圧縮伸張された後の第2のY画像データを生成する。

#### 【0126】

第2および第3の復号化回路44, 46は、それぞれ、Y圧縮データの代わりに、U圧縮データおよびV圧縮データを用いる点と、第2のY乱数シードの代わりに、第2のU乱数シードおよび第2のV乱数シードを用いる点と、Y量子化係数の代わりに、U量子化係数およびV量子化係数を用いる点と、第2のY画像データの代わりに、第2のU画像データおよび第2のV画像データを生成する点を除いて、第1の復号化回路42と同様の構成である。

20

#### 【0127】

次に、画像処理装置10の動作を説明する。

#### 【0128】

通常動作の場合、出力画像選択回路26から、第1の画像データおよび第1の画像同期信号が出力される。

第1の画像データおよび第1の画像同期信号は画像表示装置に供給され、第1の画像同期信号に基づいて、第1の画像データに対応する動画像が画像表示装置に表示される。

#### 【0129】

PSRの機能によって画像を表示する場合、第1の乱数シード生成回路14により、ライン毎に、第1の画像同期信号に基づいて、第1の乱数シードとして、第1のY乱数シード、第1のU乱数シードおよび第1のV乱数シードが生成される。

30

#### 【0130】

第1の乱数シード生成回路14では、第1の番号生成回路48により、ライン毎に、第1の画像同期信号に基づいて、第1の画像データに対応する画像のラインの番号が生成される。

続いて、第1の番号Y変換回路50Y、第1の番号U変換回路50Uおよび第1の番号V変換回路50Vにより、ライン毎に、ラインの番号を、第1の変換式に基づいて変換することにより第1のY乱数シード、第1のU乱数シードおよび第1のV乱数シードが生成される。

40

#### 【0131】

また、色空間変換回路28により、YUV色空間の第3の画像データとして、RGB色空間の第1の画像データが、第3のY画像データ、第3のU画像データおよび第3のV画像データに変換される。

#### 【0132】

また、量子化係数生成回路29により、RGB色空間の第1の画像データから、圧縮率が演算され、YUVの量子化係数が生成される。

#### 【0133】

本実施形態の場合、量子化係数生成回路29は、YUVの量子化係数として、RGB色空間の第1の画像データから、Y量子化係数、U量子化係数およびV量子化係数を生成する。

50

**【 0 1 3 4 】**

続いて、符号化回路30の第1、第2および第3の符号化回路32，34，36により、それぞれ、第1のY乱数シード、第1のU乱数シードおよび第1のV乱数シードと、Y量子化係数、U量子化係数およびV量子化係数に基づいて、第3のY画像データ、第3のU画像データおよび第3のV画像データが符号化され、圧縮データとして、第3のY画像データ、第3のU画像データおよび第3のV画像データに対応するY圧縮データ、U圧縮データおよびV圧縮データが生成される。

**【 0 1 3 5 】**

第1の符号化回路32では、第1の擬似乱数生成回路52により、画素毎に、第1のY乱数シードおよびY量子化係数に基づいて、第1の擬似乱数が生成される。

10

**【 0 1 3 6 】**

続いて、第1の加算器54により、画素毎に、第3のY画像データと第1の擬似乱数とを加算することにより加算データが生成される。

**【 0 1 3 7 】**

続いて、量子化回路56により、画素毎に、Y量子化係数を用いて、加算データを量子化することにより第1の量子化データが生成される。

**【 0 1 3 8 】**

続いて、第1の予測回路58により、画素毎に、第1の量子化データから、現在の画像よりも時間的に前の画像に対応する第1の量子化データを減算することにより第1の差分データが生成される。

20

**【 0 1 3 9 】**

続いて、エントロピー符号化回路60により、画素毎に、第1の差分データをエントロピー符号化することによりY圧縮データが生成される。

**【 0 1 4 0 】**

第2および第3の符号化回路34，36についても同様に動作する。

**【 0 1 4 1 】**

第1、第2および第3の符号化回路32，34，36によって生成されたY圧縮データ、U圧縮データおよびV圧縮データと、Y量子化係数、U量子化係数及びV量子化係数とは、画素毎に、画像メモリ18に格納される。

30

画像メモリ18に格納されたY圧縮データ、U圧縮データおよびV圧縮データと、Y量子化係数、U量子化係数及びV量子化係数とは、画像の表示タイミングに応じて、画素毎に順次読み出される。

**【 0 1 4 2 】**

また、同期信号生成回路20により、第2の画像同期信号が生成される。

**【 0 1 4 3 】**

続いて、第2の乱数シード生成回路22により、ライン毎に、第2の画像同期信号に基づいて、第2の乱数シードとして、第2のY乱数シード、第2のU乱数シードおよび第2のV乱数シードが生成される。

**【 0 1 4 4 】**

第2の乱数シード生成回路22では、第2の番号生成回路66により、ライン毎に、第2の画像同期信号に基づいて、画像メモリ18から読み出された圧縮データに対応する画像のラインの番号が生成される。

40

続いて、第2の番号Y変換回路68Y、第2の番号U変換回路68Uおよび第2の番号V変換回路68Vにより、ライン毎に、ラインの番号を、第1の変換式と等しい第2の変換式に基づいて変換することにより第2のY乱数シード、第2のU乱数シードおよび第2のV乱数シードが生成される。

**【 0 1 4 5 】**

続いて、復号化回路38の第1、第2および第3の復号化回路42，44，46により、それぞれ、第2のY乱数シード、第2のU乱数シードおよび第2のV乱数シードと、Y量子化係数、U量子化係数及びV量子化係数に基づいて、画像メモリ18から読み出されたY

50

圧縮データ、U圧縮データおよびV圧縮データが復号化され、第2の画像データとして、画像メモリ18から読み出されたY圧縮データ、U圧縮データおよびV圧縮データに対応する第2のY画像データ、第2のU画像データおよび第2のV画像データが生成される。

#### 【0146】

第1の復号化回路42では、エントロピー復号化回路70により、画素毎に、画像メモリ18から読み出されたY圧縮データをエントロピー復号化することにより第2の差分データが生成される。

#### 【0147】

続いて、第2の予測回路72により、画素毎に、第2の差分データと、現在の画像よりも前の画像に対応する第2の量子化データとを加算することにより第2の量子化データが生成される。10

#### 【0148】

続いて、逆量子化回路74により、画素毎に、Y量子化係数を用いて、第2の量子化データを逆量子化することにより伸張データが生成される。

#### 【0149】

続いて、第2の擬似乱数生成回路76により、画素毎に、第2のY乱数シードおよびY量子化係数に基づいて第2の擬似乱数が生成される。

#### 【0150】

続いて、第1の減算器78により、画素毎に、伸張データから第2の擬似乱数を減算することにより第2のY画像データが生成される。20

#### 【0151】

第2および第3の復号化回路44, 46についても同様に動作する。

#### 【0152】

続いて、逆色空間変換回路40により、第2のY画像データ、第2のU画像データおよび第2のV画像データ、つまり、YUV色空間の第2の画像データがRGB色空間の第4の画像データに変換される。

#### 【0153】

続いて、出力画像選択回路26から、第4の画像データおよび第2の画像同期信号が出力される。

第4の画像データおよび第2の画像同期信号は画像表示装置に供給され、第2の画像同期信号に基づいて、第4の画像データに対応する静止画像が画像表示装置に表示される。30

#### 【0154】

また、PSR2の機能によって画像を表示する場合、第1の乱数シード生成回路14により、ライン毎に、開始ラインの情報に対応する開始ラインから第1の乱数シードが生成される。この場合、画像圧縮回路16により、開始ラインから圧縮データが生成され、同じく開始ラインから圧縮データが画像メモリ18に格納（アップデート）される。これ以外の動作は、PSRの機能によって画像を表示する場合と同様に動作する。

#### 【0155】

図8は、本発明の乱数ディザリングによる圧縮伸張後に得られた画像を表す一例である。図8に示す画像は、図13に示す画像に対して本発明の乱数ディザリングを適用したものである。図17に示す画像には、ノイズの偏りによる模様が見えるのに対して、図8に示す画像は、ノイズが階調によらず一定であり、図17に示す画像において見える模様が発生していないことが分かる。40

#### 【0156】

上記のように、画像処理装置10では、第1および第2の乱数シード生成回路14, 22が、画像圧縮回路16および画像伸張回路24に対してライン毎に、等しい乱数シードを生成し、画像圧縮回路16および画像伸張回路24が、乱数シードに基づいて画素毎に擬似乱数を生成する。そして、画像圧縮回路16では、画像データと擬似乱数との加算データを量子化係数で量子化することにより圧縮データを生成し、画像伸張回路24では、量子化係数で逆量子化後の伸張データから擬似乱数を減算する。これにより、圧縮伸張後50

の画像において、階調が階段状に変化したり、擬似乱数によるノイズの偏りによって模様が発生したりするのを防止することができ、従来よりも視覚的に良好な表示品質を得ることができる。

#### 【0157】

なお、本発明は、ディスプレイポートの規格に準拠したPSRおよびPSR2の機能によって画像を表示する場合に限らず、送信側回路から受信した画像データを量子化して圧縮し、画像メモリから読み出された画像データを復号化して逆量子化する場合に適用可能である。

。

#### 【0158】

また、画像圧縮では、一般に、画像データの相関を減らし、圧縮効率を改善する目的で、RGB色空間の画像データからYUV色空間等の画像データへの色空間変換が行われた後、画像データの圧縮伸張が行われ、再びYUV色空間等の画像データからRGB色空間の画像データへの逆色空間変換が行われる。しかし、本発明において、色空間変換および逆色空間変換を行うことは必須ではない。

10

#### 【0159】

第3のY画像データ、第3のU画像データおよび第3のV画像データに対して共通の第1の乱数シードを使用してもよいが、第3のY画像データ、第3のU画像データおよび第3のV画像データに対して異なる第1の乱数シードを使用することにより、擬似乱数によるノイズの偏りを、より効果的に解消することができる。同様に、Y圧縮データ、U圧縮データおよびV圧縮データに対して共通の第2の乱数シードを使用してもよい。

20

#### 【0160】

PSR2の機能によって画像を表示する場合に、更新する矩形領域の位置を表す情報のうち、更新する矩形領域の開始ブロックの番号を表す情報を使用してもよい。この場合、各々の構成要素において、高さおよび幅を有するブロック毎に処理が行われる。

#### 【0161】

以上、本発明について詳細に説明したが、本発明は上記実施形態に限定されず、本発明の主旨を逸脱しない範囲において、種々の改良や変更をしてもよいのはもちろんである。

#### 【符号の説明】

#### 【0162】

10 画像処理装置

30

12、92 受信回路

14 第1の乱数シード生成回路

16、94 画像圧縮回路

18、106 画像メモリ

20 同期信号生成回路

22 第2の乱数シード生成回路

24、96 画像伸張回路

26、98 出力画像選択回路

28、108 色空間変換回路

29 量子化係数生成回路

40

30、116 符号化回路

32、110 第1の符号化回路

34、112 第2の符号化回路

36、114 第3の符号化回路

38、124 復号化回路

40、146 逆色空間変換回路

42、140 第1の復号化回路

44、142 第2の復号化回路

46、144 第3の復号化回路

48 第1の番号生成回路

50

|                   |                |    |

|-------------------|----------------|----|

| 5 0 Y             | 第 1 の 番号Y変換回路  |    |

| 5 0 U             | 第 1 の 番号U変換回路  |    |

| 5 0 V             | 第 1 の 番号V変換回路  |    |

| 5 2               | 第 1 の 擬似乱数生成回路 |    |

| 5 4               | 第 1 の 加算器      |    |

| 5 6、1 1 8、1 3 8   | 量子化回路          |    |

| 5 8、1 2 0         | 第 1 の 予測回路     |    |

| 6 0、1 2 2         | エントロピー符号化回路    |    |

| 6 2               | 第 1 の データ保持回路  |    |

| 6 4               | 第 2 の 減算器      | 10 |

| 6 6               | 第 2 の 番号生成回路   |    |

| 6 8 Y             | 第 2 の 番号Y変換回路  |    |

| 6 8 U             | 第 2 の 番号U変換回路  |    |

| 6 8 V             | 第 2 の 番号V変換回路  |    |

| 7 0、1 2 6         | エントロピー復号化回路    |    |

| 7 2、1 2 8         | 第 2 の 予測回路     |    |

| 7 4、1 3 0         | 逆量子化回路         |    |

| 7 6               | 第 2 の 擬似乱数生成回路 |    |

| 7 8               | 第 1 の 減算器      |    |

| 8 0               | 第 2 の データ保持回路  | 20 |

| 8 2               | 第 2 の 加算器      |    |

| 9 0               | 画像処理装置         |    |

| 1 0 0             | 表示制御回路         |    |

| 1 0 2             | 送信側回路          |    |

| 1 0 4             | 画像表示装置         |    |

| 1 3 2             | 乱数ディザリング回路     |    |

| 1 3 4             | 擬似乱数生成回路       |    |

| 1 3 6             | 加算器            |    |

| 1 4 8             | 線形帰還シフトレジスタ    |    |

| 1 5 0             | シフトレジスタ        | 30 |

| 1 5 2、1 5 4、1 5 6 | EXOR回路         |    |

【図1】

【図2】

【図3】

( 4 )

〔 図 5 〕

〔 四 6 〕

【図7】

【図8】

【図9】

【図10A】

【図10B】

---

フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

G 0 9 G 5/36 5 2 0 A

F ターム(参考) 5C182 AA03 AB02 AC03 AC43 BC30 CA11 CA15 CA36 CC21 CC24

DA04 DA22 DA44