(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5219900号

(P5219900)

(45) 発行日 平成25年6月26日(2013.6.26)

(24) 登録日 平成25年3月15日(2013.3.15)

(51) Int.Cl.

H01L 21/314 (2006.01)

H01L 21/316 (2006.01)

F 1

H01L 21/314

H01L 21/316

H01L 21/316M

X

P

請求項の数 18 (全 19 頁)

(21) 出願番号 特願2009-78118 (P2009-78118)

(22) 出願日 平成21年3月27日 (2009.3.27)

(65) 公開番号 特開2009-246365 (P2009-246365A)

(43) 公開日 平成21年10月22日 (2009.10.22)

審査請求日 平成24年3月16日 (2012.3.16)

(31) 優先権主張番号 12/058, 470

(32) 優先日 平成20年3月28日 (2008.3.28)

(33) 優先権主張国 米国(US)

(73) 特許権者 000219967

東京エレクトロン株式会社

東京都港区赤坂五丁目3番1号

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

(72) 発明者 キンバリー ジー レイド

アメリカ合衆国 テキサス州 78737

オースティン 1826 エフエム 1

4338

最終頁に続く

(54) 【発明の名称】原子層堆積(ALD)法及び化学気相成長(CVD)法を用いた高誘電率膜のその場ハイブリッド堆積

## (57) 【特許請求の範囲】

## 【請求項1】

膜のその場ハイブリッド堆積方法であって：

バッチ処理システムの処理チャンバに複数の基板を搬入する手順；

原子層堆積(ALD)法によって前記複数の基板上にhigh-k誘電膜の第1部分を堆積する手順；

該第1部分の堆積後に前記複数の基板を前記処理チャンバから取り出すことなく、化学気相成長(CVD)法によって前記第1部分上に前記high-k誘電膜の第2部分を堆積する手順；

前記複数の基板を前記処理チャンバから取り出す前に前記high-k誘電膜の第1部分と第2部分の後処理を行う手順を有する方法であって、前記後処理は：

(a)ガスが存在しない雰囲気で基板温度を500から1000にして行う高温アニーリング；

(b)酸素含有ガス又は酸素と窒素を含有するガスから選ばれる第4酸化剤の存在下で基板温度を500から1000にして行う高温酸化；又は

(c)非酸化剤ガスの存在下で基板温度を500から1000にして行う高温アニーリング；

(d)前記第1及び第2部分の堆積を交互に繰り返し行う手順であって、前記第1部分の各々は第1厚さを有し、前記第2部分の各々は第2厚さを有する、手順；

のうちの一又は任意の順次実行される組合せから選ばれる、手順；及び、

前記複数の基板を前記処理チャンバから取り出す手順；

を有する方法。

10

20

**【請求項 2】**

前記第1部分を堆積する前に、100 から1000 の基板温度で、酸素含有ガス又は酸素と窒素を含有するガスから選ばれる第1酸化剤によって前記複数の基板を前処理する手順をさらに有する、請求項1に記載の方法。

**【請求項 3】**

前記前処理が、前記第1及び第2部分を堆積するときよりも高い基板温度で実行される、請求項2に記載の方法。

**【請求項 4】**

前記第1酸化剤が、O<sub>2</sub>、O<sub>3</sub>、N<sub>2</sub>O、NO、若しくはH<sub>2</sub>O蒸気、又は上記の混合物から選ばれる、請求項2に記載の方法。 10

**【請求項 5】**

前記第1部分を堆積する手順が複数回の堆積サイクルを実行する手順を有し、各サイクルは前記の処理チャンバ内の複数の基板を第2酸化剤と金属先駆体に曝露し、前記第2酸化剤の曝露と前記金属先駆体の曝露との間には任意のページ手順が存在し、前記第2酸化剤は酸素含有ガス又は酸素と窒素を含有するガスから選ばれる、請求項1に記載の方法。

**【請求項 6】**

前記第2酸化剤が、O<sub>2</sub>、O<sub>3</sub>、N<sub>2</sub>O、NO、若しくはH<sub>2</sub>O蒸気、又は上記の混合物から選ばれる、請求項5に記載の方法。

**【請求項 7】**

前記第2部分を堆積する手順が、前記の処理チャンバ内の複数の基板を第3酸化剤と金属先駆体に同時に曝露する手順を有し、

前記第3酸化剤は酸素含有ガス又は酸素と窒素を含有するガスから選ばれる、請求項1に記載の方法。 20

**【請求項 8】**

前記第3酸化剤が、O<sub>2</sub>、O<sub>3</sub>、N<sub>2</sub>O、NO、若しくはH<sub>2</sub>O蒸気、又は上記の混合物から選ばれる、請求項7に記載の方法。

**【請求項 9】**

前記後処理が、前記第1及び第2部分を堆積するときよりも高い基板温度で実行される、請求項1に記載の方法。 30

**【請求項 10】**

前記第4酸化剤が、O<sub>2</sub>、O<sub>3</sub>、N<sub>2</sub>O、NO、若しくはH<sub>2</sub>O蒸気、又は上記の混合物から選ばれる、請求項1に記載の方法。

**【請求項 11】**

前記第1部分の各々、前記第2部分の各々、又は前記第1及び第2部分の各々は、同一の厚さを有する、請求項1に記載の方法。

**【請求項 12】**

前記第2部分のうちの少なくとも1つは、前記第2部分のうちの他とは異なる第1厚さを有する、請求項1に記載の方法。

**【請求項 13】**

前記第1及び第2部分の堆積は、同一の基板温度で実行される、請求項1に記載の方法。 40

**【請求項 14】**

前記第1及び第2部分の堆積は、それぞれ異なる基板温度で実行される、請求項1に記載の方法。

**【請求項 15】**

膜のその場ハイブリッド堆積方法であって、

当該方法は：

バッチ処理システムの処理チャンバに複数の基板を搬入する手順；

原子層堆積(ALD)法によって前記複数の基板上にhigh-k誘電膜の第1部分を堆積する手順

;

50

該第1部分の堆積後に前記複数の基板を前記処理チャンバから取り出すことなく、化学気相成長(CVD)法によって前記第1部分上に前記high-k誘電膜の第2部分を堆積する手順；

前記第1及び第2部分の堆積を交互に繰り返し行う手順であって、前記第1部分の各々は第1厚さを有し、前記第2部分の各々は第2厚さを有する、手順；

前記複数の基板を前記処理チャンバから取り出す手順；

を有し、

前記第1部分を堆積する手順は第2酸化剤を利用し、

前記第2部分を堆積する手順は前記第2酸化剤とは異なる第3酸化剤を利用し、かつ

前記第2酸化剤と第3酸化剤の各々は、O<sub>2</sub>、O<sub>3</sub>、N<sub>2</sub>O、NO、若しくはH<sub>2</sub>O蒸気、又は上記の混合物から選ばれる、

10

方法。

#### 【請求項 16】

膜のその場ハイブリッド堆積方法であって、

当該方法は：

複数の基板をバッチ処理システムの処理チャンバへ搬入する手順；

500 から1000 の基板温度で、第1酸化剤によって前記の処理チャンバ内の複数の基板を前処理する手順；

該前処理手順後、原子層堆積(ALD)法によって前記複数の基板上にHfO<sub>2</sub>膜の第1部分を堆積する手順であって、前記第1部分を堆積する手順が複数回の堆積サイクルを実行する手順を有し、各サイクルは前記の処理チャンバ内の複数の基板を第2酸化剤と金属先駆体に曝露し、前記第2酸化剤の曝露と前記金属先駆体の曝露との間には任意のページ手順が存在する、手順；

20

化学気相成長(CVD)法によって前記第1部分上に前記HfO<sub>2</sub>膜の第2部分を堆積する手順であって、前記の処理チャンバ内の複数の基板が第3酸化剤と金属先駆体に同時に曝露される、手順；

前記のHfO<sub>2</sub>膜を有する複数の基板を、酸素含有ガス又は酸素と窒素を含有するガスから選ばれる第4酸化剤の存在下で基板温度を500 から1000 にして行う高温酸化によって後処理する手順であって、前記第4酸化剤が、O<sub>2</sub>、O<sub>3</sub>、N<sub>2</sub>O、NO、若しくはH<sub>2</sub>O蒸気、又は上記の混合物から選ばれる、手順；

前記第1及び第2部分の堆積を交互に繰り返し行う手順であって、前記第1部分の各々は第1厚さを有し、前記第2部分の各々は第2厚さを有する、手順；並びに

30

前記複数の基板を前記処理チャンバから取り出す手順；

を有し、

前記前処理手順、前記第1部分を堆積する手順、前記第2部分を堆積する手順、及び後処理手順は、前記複数の基板を前記処理チャンバから取り出すことなく行われる、

方法。

#### 【請求項 17】

前記前処理手順及び前記後処理手順が、前記第1部分を堆積する手順及び前記第2部分を堆積する手順を行うときよりも、高い基板温度で実行される、請求項16に記載の方法。

#### 【請求項 18】

40

前記第1部分を堆積する手順及び前記第2部分を堆積する手順が、それぞれ異なる基板温度で実行される、請求項16に記載の方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0 0 0 1】

本発明はマイクロエレクトロニクスデバイスの高誘電率(high-k)誘電膜の堆積に関し、より詳細には原子層堆積(ALD)法と化学気相成長(CVD)法とを併用したhigh-k誘電膜のその場ハイブリッド堆積に関する。

##### 【背景技術】

##### 【0 0 0 2】

50

半導体産業において、マイクロエレクトロニクスデバイスの最小部位のサイズは、高速で低電力の半導体デバイスという要求を満たすため、ディープサブミクロン領域に入っている。相補型金属-酸化物-半導体(CMOS)デバイスのサイズを縮小することで、ゲート誘電体材料にはサイズ縮小の制約が科される。従来のSiO<sub>2</sub>ゲート誘電体の厚さは物理的限界に接近している。最先端のデバイスは、等価酸化膜厚(EOT)が約1ナノメートル(nm)以下に接近している窒化SiO<sub>2</sub>ゲート誘電体を用いている。このデバイスでは、漏れ電流密度は1mA/cm<sup>2</sup>程度である。デバイスの信頼性の改善、及びそのデバイスの動作中でのゲート誘電体からトランジスタチャネルへの漏れ電流の減少のため、半導体トランジスタ技術は、低EOTを維持したままでゲート誘電層の物理的な厚さを増大させることを許容するhigh-kゲート誘電体材料を用いる。EOTとは、別な誘電体材料から得られるキャパシタンス電圧曲線と同一のものを生じさせるSiO<sub>2</sub>の厚さと定義される。High-k材料は、SiO<sub>2</sub>よりも高い誘電率(k ~ 3.9)を有する誘電材料である。High-k材料とは、SiO<sub>2</sub>の場合のように、基板表面上で成長するというよりは、むしろ基板上に堆積される誘電材料を指す。High-k材料はたとえば金属酸化膜又は金属シリケート膜を有して良い。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許出願第2007/0037412号明細書

【特許文献2】米国特許出願第11/278387号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体デバイスにおいて使用可能なhigh-k誘電体薄膜を形成する複数の方法が開発されてきた。とりわけより確立された手法は、化学気相成長(CVD)法と原子層堆積(ALD)法であるが、これらの手法はそれぞれ、利点と、大容量半導体製造にとって問題となる欠点を有する。基板(ウエハ)汚染の減少に加えさらに、領域間での均一性、ウエハ間での均一性、及び膜全体の均一性という点について、バッチ処理において良好な均一性を実現する必要がある。良好な膜の均一性の必要性に加えて、膜の積層体の高い実効k値及び低いEOTを維持しながら、high-k誘電膜の電気的特性-膜中でのヒステリシスの大きさ、high-k誘電膜と他の材料との界面での欠陥密度、及び漏れ電流が含まれる-を改善させる必要もある。

【課題を解決するための手段】

【0005】

本発明の実施例は、大容量半導体製造を目的とする複数の基板上へのhigh-k誘電膜のその場ハイブリッド堆積方法を供する。当該方法は、化学気相成長(CVD)法と原子層堆積(ALD)法を用いてhigh-k誘電膜を順次堆積する手順を有する。ALDによって堆積されたhigh-k誘電膜部分は、下地の基板又は該基板上の界面層と優れた界面を形成する。そしてCVDによって堆積されたhigh-k誘電膜部分は、CVDの高堆積速度という利点を用いて、高品質のhigh-k誘電膜を費用対効果良く供する。さらにバッチ処理システムは、広い温度範囲にわたって迅速な温度変化(降温又は昇温)をさせることができる。それにより第1及び第2部分の堆積をそれぞれ異なる基板温度で行うことが可能となる。

【0006】

本発明の一の実施例によると、当該方法は、前記バッチ処理システムの処理チャンバに前記複数の基板を搬入する手順、原子層堆積(ALD)法によって前記複数の基板上にhigh-k誘電膜の第1部分を堆積する手順、該第1部分の堆積後に前記複数の基板を前記処理チャンバから取り出すことなく、化学気相成長(CVD)法によって前記第1部分上にhigh-k誘電膜の第2部分を堆積する手順、及び前記複数の基板を前記処理チャンバから取り出す手順を有する。当該方法は、前記high-k誘電膜が所望の厚さを有するまで、前記第1及び第2部分の堆積を交互に繰り返す手順をさらに有して良い。またさらに当該方法は、前記取り出しの前に、前記基板の前処理と前記high-k誘電膜の後処理をその場で行う手順を有して良い。

10

20

30

40

50

**【図面の簡単な説明】****【0007】**

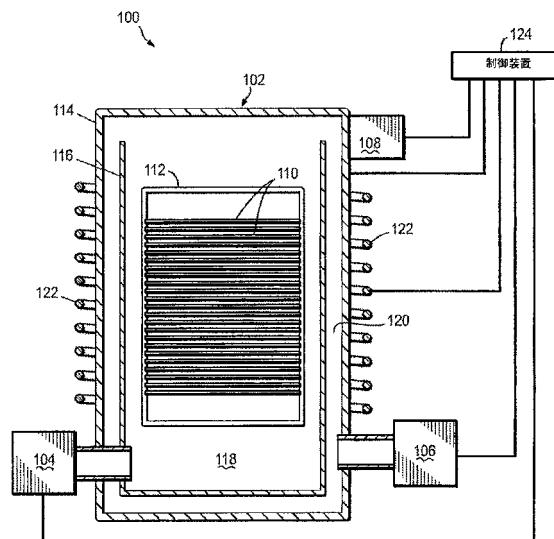

【図1A】本発明の実施例によるバッチ処理システムの単純化されたブロック図を示している。

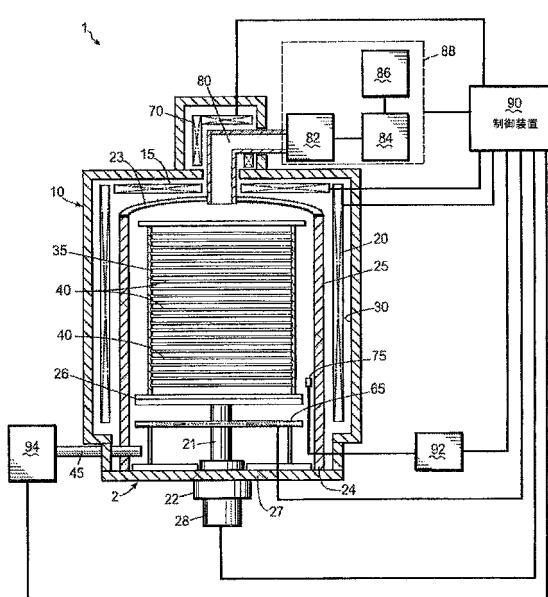

【図1B】本発明の別な実施例によるバッチ処理システムの単純化されたブロック図を示している。

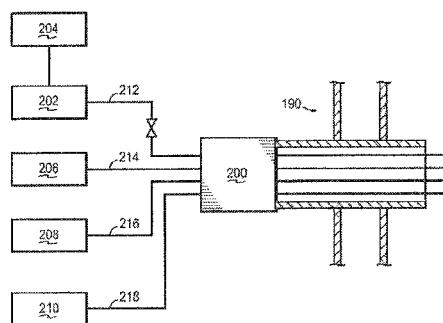

【図2】本発明の実施例による処理チャンバと結合するガス注入システムの単純化されたブロック図を示している。

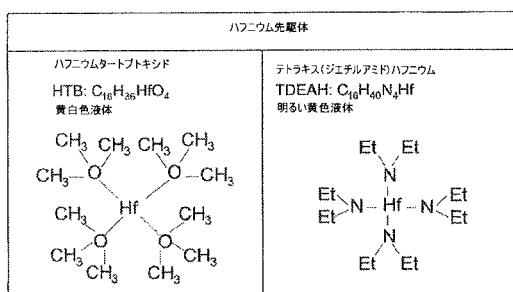

【図3】ハフニウムタートブトキシド(HTB)及びテトラジエチルアミドハフニウム(TDEAH)の化学構造と化学式を表している。

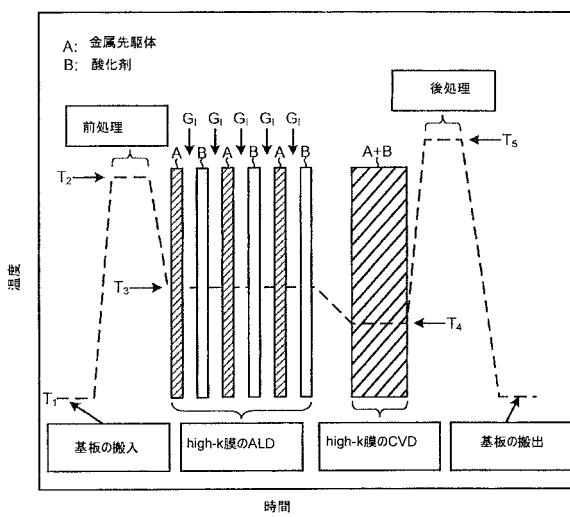

【図4】本発明の実施例によるALDとCVDを併用したhigh-k誘電膜のその場ハイブリッド堆積の時間変化をグラフで表している。

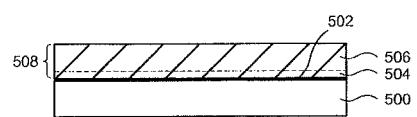

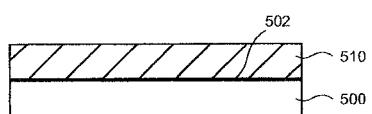

【図5】A-Eは、本発明の実施例による基板上へのhigh-k誘電膜のその場ハイブリッド堆積方法の処理フローを概略的な断面図で表している。

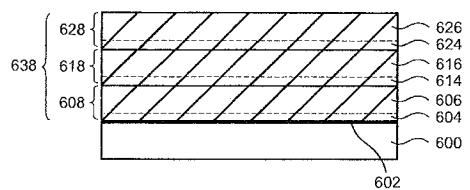

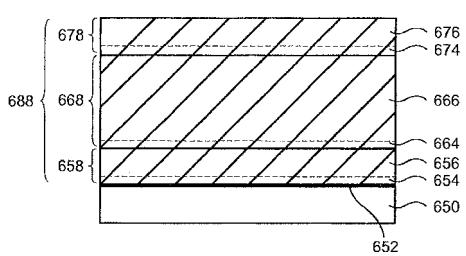

【図6】本発明の実施例による基板上に堆積された追加のhigh-k誘電膜を概略的な断面図で表している。

**【発明を実施するための形態】****【0008】**

本発明のより完全な評価及び本発明に付随する利点の多くは、特に添付の図面と共に検討しながら以降の詳細な説明を参照することですぐに明らかになる。

**【0009】**

半導体デバイスの製造に用いられる、基板上にhigh-k誘電体薄膜を生成する複数の方法がこれまでに開発されてきた。とりわけより確立された手法はCVDである。CVDの変化型であるALDは、均一で等角的な膜の堆積を実現する優れた方法となる可能性があるものとして現れた比較的新しい手法である。ALDは、膜の堆積速度が遅いため、CVDよりも遅い堆積方法である。しかしALDは大抵の場合優れたhigh-k誘電膜特性-たとえば半導体デバイス中で一般的に見られる溝又はピアのような高アスペクト比の特徴部位にわたって膜の等角性が良好であること、並びにhigh-k誘電膜と下地の基板及び/又は他の膜との間での良好な界面に少なくとも部分的に起因して漏れ電流が減少すること-を与える。半導体デバイスでのhigh-k誘電膜の用いる場合の多くでは、膜の堆積速度の低さ故にALDでは長い時間がかかるよう厚さが必要となる。従ってALDは実行するのに非常に費用のかかるものである。さらにCVDプロセスは、たとえ高速な堆積プロセスであるとしても、満足の行くhigh-k誘電膜を供することができない。その理由は、膜の等角性が不十分なこと、並びに下地の基板及び/又は他の膜との良好な界面を形成することができないためである。

**【0010】**

本発明の実施例は、バッチ処理システム内でALDとCVDを1回以上交互に順次用いた複数の基板上へのhigh-k誘電膜のその場ハイブリッド堆積方法を供する。本発明の実施例によると、high-k誘電膜は、金属酸化物、金属酸窒化物、金属シリケート、若しくは金属シリコン酸窒化物、又はこれらの混合物を有して良い。high-k誘電膜はまた、不純物-たとえば炭素又はハロゲン-をも含んで良い。high-k誘電膜はたとえば、ハフニウム含有膜(たとえばHfO<sub>2</sub>、HfON、HfSiO又はHfSiON)、ジルコニウム含有膜(たとえばZrO<sub>2</sub>、ZrON、ZrSiO又はZrSiON)、タンタル含有膜(たとえばTa<sub>2</sub>O<sub>5</sub>)、チタン含有膜(たとえばTiO<sub>2</sub>)、若しくはアルミニウム含有膜(たとえばAl<sub>2</sub>O<sub>3</sub>)、又はこれらの混合物を有して良い。high-k誘電膜はたとえば、深溝キャパシタ内で、又はトランジスタ構造におけるゲート誘電膜の一部として利用されて良い。

**【0011】**

当業者は、様々な実施例は、1つ以上の具体的な詳細がなくても実施可能であり、又は他の置換物及び/又は追加の方法、材料、若しくは構成部品によっても実施可能であることを理解するだろう。他の場合では、周知の構造又は動作は、本発明の様々な実施例の様子を曖昧にしないように、詳細な図示も記載もしていない。同様に説明目的で、本発明を

10

20

30

40

50

より完全に理解してもらうために、具体的な数値及び構成が与えられている。しかし本発明は具体的な詳細が与えられなくても実施可能である。さらに図示された様々な実施例は例示であり、必ずしも正しい縮尺で描かれていないことに留意して欲しい。

#### 【0012】

本明細書で用いられている「(一の)実施例」とは、その実施例に関連づけて記載されている特定の特徴部位、構造、材料、又は特性が、本発明の少なくとも1つの実施例に含まれることを意味し、これらがどの実施例にも存在しているということを意味する訳ではない。よって本明細書の様々な箇所で現れる「(一の)実施例」という語は、必ずしも本発明の同一実施例を指しているわけではない。さらに特定の特徴部位、構造、又は特性は、1つ以上の実施例において適当な方法で組み合わせられて良い。様々な追加の層及び/又は構造が含まれて良く、かつ/又は記載された特徴部位が他の実施例において省略されても良い。

10

#### 【0013】

様々な動作が、本発明を理解するのに最も助けとなるように、複数の独立した動作として記載される。しかし記載の順序は、これらの動作が必ずしも順序に依存することを示唆するように解されてはならない。具体的には、これらの動作は示された順序通りに実行される必要はない。記載された動作は実施例に記載された順序以外の順序で実行されても良い。様々な追加の動作が実行されて良く、かつ/又は記載された動作が追加の実施例において省略されても良い。

#### 【0014】

20

本発明の一の実施例によると、high-k誘電膜を形成する方法は、複数の基板(ウエハ)をバッチ処理システムの処理チャンバ(たとえば処理管)へ搬入する手順、ALDによって前記複数の基板上にhigh-k誘電膜の第1部分を堆積する手順、及びその後に化学気相成長(CVD)法によって前記第1部分上にhigh-k誘電膜の第2部分を堆積する手順を有する。前記複数の基板を前記処理チャンバから取り出す手順を有する。本発明の実施例によると、その場ハイブリッド(ALDの後にCVDが行われる)high-k誘電膜堆積プロセス全体は、処理チャンバから基板を取り出すことなく実行される。これは、多くの一般的な不純物(たとえば大気中に存在する有機材料)がhigh-k誘電膜へ入り込むのを防止、又は少なくとも顕著に減少させ、かつ材料及びそのhigh-k誘電膜の電気的特性の優れた制御を供する。

#### 【0015】

30

本発明の他の実施例によると、high-k誘電膜のその場ハイブリッド堆積プロセスは、基板上にそのhigh-k誘電膜を堆積する前にその基板を前処理する手順、及び/又はその堆積後にそのhigh-k膜を後処理する手順をさらに有して良い。前処理は、基板表面からの不純物の除去及び/又は基板上への酸化物若しくは酸窒化物界面層の形成のために行われて良い。後処理は、high-k誘電膜を圧縮し、かつ/又はhigh-k誘電膜から未反応反応物を除去するために実行される。その後処理はさらに界面層を形成若しくは酸化し、又は酸素空孔を充填し、かつ/若しくはhigh-k誘電膜中の置換酸素を再分配する。

#### 【0016】

図1Aは、本発明の実施例による基板上にhigh-k誘電膜を形成するバッチ処理システムの単純化されたブロック図を示している。バッチ処理システム100は、処理チャンバ102、ガス注入システム104、ヒーター122、真空排気システム106、プロセス監視システム108、及び制御装置124を有する。複数の基板110が、処理チャンバ102内に搬入され、かつウエハポートとも呼ばれる基板ホルダ112を用いて処理されて良い。さらに処理チャンバ102は外部区域114及び内部区域116を有する。本発明の一の実施例では、内部領域116は処理管であって良い。当該バッチ処理システムは広い温度範囲にわたって迅速に温度変化(降温及び昇温)させることができる。温度変化速度は、初期温度と最終温度の温度差の関数であると考えられる。温度変化速度は、広い温度範囲にわたって温度変化させる(たとえば250℃から800℃に変化させる)ときには、たとえば50℃/分程度であって良い。しかし温度変化速度は、初期温度と最終温度の温度差が相対的に小さい(たとえば250℃から300℃に変化する)ときには、最終温度のオーバーシュートを防ぐため、5-20℃/分程度であって

40

50

良い。

### 【0017】

ガス注入システム104は、処理チャンバ102のページ、並びに基板110の準備、洗浄、及び処理を行うため、処理チャンバ102にガスを導入して良い。ガス注入システム104はたとえば、先駆体液体を気化する気化器を含む液体供給システム(LDS)(図示されていない)を有して良い。気化した液体は処理チャンバ102へ流入して良い。その際キャリアガスの助けがあっても良いし、又はその助けがなくても良い。たとえばキャリアガスが用いられるとき、そのガス注入システムはバブリングシステムを有して良い。そのバブリングシステムでは、キャリアガスが先駆体液体を含む容器を介してバブリングされる。

### 【0018】

たとえば本発明の実施例は、ハフニウム(Hf)又はジルコニウム(Zr)含有膜を生成する様々な種類のハフニウム(Hf)又はジルコニウム(Zr)先駆体を利用して良い。たとえば代表例には、 $Hf(O^tBu)_4$ (ハフニウムタートブトキシド、HTB)、 $Hf(NEt_2)_4$ (テトラキス(ジエチルアミド)ハフニウム、TDEAH)、 $Hf(NEtMe)_4$ (テトラキス(エチルメチルアミド)ハフニウム、TEMAH)、 $Hf(NMe_2)_4$ (テトラキス(ジメチルアミド)ハフニウム、TDMAH)、 $Zr(O^tBu)_4$ (ジルコニウムタートブトキシド、ZTB)、 $Zr(NEt_2)_4$ (テトラキス(ジエチルアミド)ジルコニウム、TDEAZ)、 $Zr(NMeEt)_4$ (テトラキス(エチルメチルアミド)ジルコニウム、TDMAZ)、 $Zr(NMeEt)_4$ (テトラキス(エチルメチルアミド)ジルコニウム、TEMAZ)、 $Zr(NMe_2)_4$ (テトラキス(ジメチルアミド)ジルコニウム、TDMAZ)、 $ZrCp_2Me_2$ 、 $Zr(^tBuCp)_2Me_2$ 、及び $Zr(N^iPr)_2$ が含まれる。

### 【0019】

他の実施例は、タンタル(Ta)、チタン(Ti)又はアルミニウム(Al)含有膜を生成する様々な種類のタンタル(Ta)、チタン(Ti)又はアルミニウム(Al)先駆体を利用して良い。”Ta-N”分子内結合を有するTa含有膜の例にはたとえば、TAIMATA、 $Ta(NEt_2)_5(PDEAT)$ 、 $Ta(NMe_2)_5(PDMAT)$ 、 $Ta(NEtMe_2)_5(PEMAT)$ 、( $^tBuN$ ) $Ta(NMe_2)_3(TBTDMT)$ 、( $^tBuN$ ) $Ta(NEt_2)_3(TBTDET)$ 、( $^tBuN$ ) $Ta(NEtMe)_3(TBTEMT)$ 、及び( $^iPrN$ ) $Ta(NEt_2)_3(IPTDET)$ が含まれる。”Ta-C”分子内結合を有するTa含有膜の例にはたとえば、 $Ta(^5-C_5H_5)_2H_3$ 、 $Ta(CH_2)(CH_3)(^5-C_5H_5)_2$ 、 $Ta(^3-C_3H_5)(^5-C_5H_5)_2$ 、 $Ta(CH_3)_3(^5-C_5H_5)_2$ 、 $Ta(CH_3)_4(^5-C_5(CH_3)_5)$ 、又は $Ta(^5-C_5(CH_3)_5)_2H_3$ が含まれる。

### 【0020】

”Ti-N”分子内結合を有するTi含有膜の例にはたとえば、 $Ti(NEt_2)_4(TDEAT)$ 、 $Ti(NMeEt)_4(TEMAT)$ 、 $Ti(NMe_2)_4(TDMAT)$ が含まれる。”Ti-C”分子内結合を有するTi含有膜の例にはたとえば、 $Ti(COCH_3)(^5-C_5H_5)_2Cl$ 、 $Ti(^5-C_5H_5)Cl_2$ 、 $Ti(^5-C_5H_5)Cl_3$ 、 $Ti(^5-C_5H_5)_2Cl_2$ 、 $Ti(^5-C_5(CH_3)_5)Cl_3$ 、 $Ti(CH_3)(^5-C_5H_5)_2Cl$ 、 $Ti(^5-C_9H_7)_2Cl_2$ 、 $Ti(^5-C_5(CH_3)_5)_2Cl$ 、 $Ti(^5-C_5(CH_3)_5)_2Cl_2$ 、 $Ti(^5-C_5H_5)_2(\mu-Cl)_2$ 、 $Ti(^5-C_5H_5)_2(CO)_2$ 、 $Ti(CH_3)_3(^5-C_5H_5)$ 、 $Ti(CH_3)_4$ 、 $Ti(^5-C_5H_5)(^7-C_7H_7)$ 、 $Ti(^5-C_5H_5)(^8-C_8H_8)$ 、 $Ti(C_5H_5)_2(^5-C_5H_5)_2$ 、 $Ti(C_5H_5)_2(-H)_2$ 、 $Ti(^5-C_5(CH_3)_5)_2$ 、 $Ti(^5-C_5(CH_3)_5)_2H_2$ 、及び $Ti(CH_3)_2(^5-C_5(CH_3)_5)_2$ が含まれる。

### 【0021】

本発明の実施例は、high-k誘電膜を形成する様々な種類の希土類先駆体を利用して良い。希土類先駆体の例は特許文献2に記載されている。本発明の実施例によると、high-k誘電膜は、金属酸化物、金属酸窒化物、金属シリケート、若しくは金属シリコン酸窒化物、又はこれらの混合物として希土類金属を有して良い。

### 【0022】

上の記載では、以下のようなリガンド表記が用いられている。 $^tBu$ はタートブチル、 $^iBu$ はイソブチル、Etはエチル、Meはメチル、Cpはシクロペンタジエニル、 $^iPr$ はイソプロピルで、THDは2,2,6,6,-テトラメチル-3,5-ヘプタンジオネットである。

### 【0023】

それに加えて、ガス注入システム104は、Si含有ガス(たとえばシラン( $SiH_4$ ))、酸素及び/又は窒素含有ガスを含む酸化剤(たとえば $O_2$ 、 $O_3$ 、 $N_2O$ 、 $NO$ 、又は $H_2O$ 蒸気)、を処

10

20

30

40

50

理チャンバ102へ流すように備えられて良い。酸化剤ガス源（図示されていない）は、H<sub>2</sub>ガスとO<sub>2</sub>ガスからH<sub>2</sub>O蒸気を生成する水蒸気発生装置(WVG)（図示されていない）を有して良い。WVGの一例は、東京エレクトロン株式会社によって開発された高希釈発火トーチである。その高希釈発火トーチわずかに流れるH<sub>2</sub>ガスとO<sub>2</sub>ガスを燃焼して、処理チャンバの外部でH<sub>2</sub>O蒸気を生成する。さらに上述のガス流は、たとえば不活性ガス（たとえば希ガス又はN<sub>2</sub>）及び/又は水素含有ガスを有して良い。水素含有ガスはH<sub>2</sub>を含んで良い。処理チャンバ102へガスを流す複数のガス供給ラインが備えられて良い。複数の種類のガスが内部区域116によって画定される容積118へ導入されて良い。そして基板110がその複数の種類のガスに曝露されて良い。その後その複数の種類のガスは内部区域116と外部区域114によって画定される容積120へ流れ、かつ真空排気システム106によって処理チャンバ102から排出されて良い。

## 【0024】

基板110は処理チャンバ102へ搬入され、かつ基板ホルダ112を用いて処理されて良い。バッチ処理システム100は、多数の緊密に積層した基板110の処理を可能にする。その結果、基板の処理能力が向上する。基板のバッチサイズはたとえば約100枚以下の基板（ウエハ）であって良い。あるいはその代わりにバッチサイズは約25枚以下の基板であっても良い。処理チャンバ102はたとえば、如何なるサイズの基板-たとえば200mm基板、300mm基板、又はそれ以上のサイズの基板-をも処理して良い。基板110はたとえば、半導体基板（たとえばシリコン又は化合物半導体）、LCD基板、及びガラス基板を有して良い。

## 【0025】

バッチ処理システム100は制御装置124によって制御されて良い。その制御装置124は、バッチ処理システム100からの出力を監視するだけではなく、そのバッチ処理システム100の入力とのやり取りや起動を行うのに十分な制御電圧を発生させることができる。しかも制御装置124は、処理チャンバ102、ガス注入システム104、ヒーター122、プロセス監視システム108、及び真空排気システム106と結合して、これらと情報のやり取りを行って良い。たとえば制御装置124のメモリに記憶されたプログラムは、バッチ処理システム100の上記構成部品を、記憶されたプロセスレシピに従って制御するのに利用されて良い。

## 【0026】

リアルタイムでのプロセス監視は、プロセス監視システム108を用いて実行されて良い。一般的には、プロセス監視システム108は多目的監視システムであり、かつたとえば質量分析計(MS)又はフーリエ変換赤外(FTIR)分光装置を有して良い。プロセス監視システム108は、処理環境中の気体化学種の定性的及び定量的分析を行うことができる。監視可能なプロセスパラメータには、ガス流、ガス圧、気体種の比、及びガス純度が含まれる。これらのパラメータは、これまでのプロセス結果及び堆積されたhigh-k誘電膜の様々な物理的特性と関連づけることができる。

## 【0027】

図1Bは、本発明の別な実施例による基板上にhigh-k誘電膜を形成するバッチ処理システムの単純化されたブロック図を示している。バッチ処理システム1は、処理チャンバ10、排出パイプ80と接続する上端部23を有するプロセス管25、及び円筒形マニホールド2の蓋27と密閉可能な状態で接合する下端部を有する。排出パイプ80は、ガスをプロセス管25から真空排気システム88へ放出することで、処理システム1内を所定の圧力すなわち大気圧未満の圧力に維持する。多段状態（各水平面に垂直な間隔が設けられた状態）で複数の基板（ウエハ）40を保持する基板ホルダ35が、プロセス管25内に設けられている。基板ホルダ35は回転台26上に設けられる。その回転台26は、蓋27を貫通してモーター28によって駆動される回転シャフト21上にマウントされる。回転台26は処理中に回転することで、膜全体の均一性を改善することが可能である。あるいはその代わりに回転台は処理中に静止しても良い。蓋27は、プロセス管25に対して基板ホルダ35を搬入/出すする昇降機22上にマウントされている。蓋27が最上部に位置するとき、蓋27はマニホールド2の開口端部を閉じるように備えられている。

## 【0028】

10

20

30

40

50

複数の種類のガスをプロセス管25へ供給するため、複数のガス供給ラインがマニホールド2の周辺に備えられていて良い。図1Bでは、複数のガス供給ラインのうちの1本のガス供給ライン45しか図示されていない。その1本のガス供給ライン45はガス注入システム94と接続する。円筒形熱反射体30が、プロセス管25を覆うように設けられている。熱反射体30は鏡面仕上げされた内部表面を有する。その内部表面は、主ヒーター20、下部ヒーター65、上部ヒーター15、及び排出パイプ用ヒーター70によって放射される放射熱の熱拡散を抑制する。螺旋状の冷却水路（図示されていない）が、処理チャンバ10の壁内に冷媒の流路として形成される。

#### 【0029】

真空排気システム88は、真空ポンプ86、トラップ84、及び自動圧力制御装置(APC)82を有する。真空ポンプ86はたとえば、毎秒20000リットル（以上）の排気速度を有するドライ真空ポンプを有して良い。処理中、複数のガスが、ガス注入システム94を介して処理チャンバ10へ導入され、かつ処理圧力はAPC82によって調節されて良い。トラップ84は、処理チャンバ10から未反応先駆体材料と副生成物を回収して良い。

10

#### 【0030】

プロセス監視システム92は、リアルタイムでのプロセス監視が可能なセンサ75を有し、かつたとえばMS又はFTIR分光計を有して良い。制御装置90は、マイクロプロセッサ、メモリ、及びデジタルI/Oポートを有する。そのデジタルI/Oポートは、処理システム1からの出力を監視するだけではなく、その処理システム1の入力とのやり取りや起動を行うのに十分な制御電圧を発生させることができる。しかも制御装置90は、ガス注入システム94、モーター28、プロセス監視システム92、ヒーター20、15、65、70、及び真空排気システム88と結合して、これらと情報のやり取りを行って良い。

20

#### 【0031】

図2は、処理チャンバ190と結合するガス注入システム200を図示している。ガス注入システム200と処理チャンバ190は、図1Aのガス注入システム104と処理チャンバ102、又は図1Bのガス注入システム94と処理チャンバ10であって良い。ガス注入システム200は液体供給システム(LDS)202と結合して良い。LDS202は、タートブトキシド(HTB)やテトラ-ジエチレンアミドハフニウム(TDEAH)のような先駆体液体を気化する気化器を有する。図3はHTB又はTDEAHの化学構造及び化学式を表している。気化した液体は、ガス注入システム200を介して処理チャンバ190へ流れて良い。その際キャリアガスの助けがあっても良いし、又はその助けがなくても良い。たとえばキャリアガスが用いられるとき、そのガス注入システムはバプリングシステムを有して良い。そのバプリングシステムでは、キャリアガスが先駆体液体を含む容器を介してバプリングされる。それに加えて、ガス注入システム200はSi含有ガス源206-たとえば $\text{SiCl}_4$ 、 $\text{SiH}_4$ 、又は $\text{Si}_2\text{H}_6$ -と結合して良い。Si含有ガス源206は、Si含有ガスを処理チャンバ190へ供して、Siをhigh-k誘電膜へ組み込む。ガス注入システム200はまた酸化剤ガス源208-たとえば水蒸気発生装置(WVG)又はオゾン発生装置-をも有して良い。ガス注入システム200はSi含有ガス源206-たとえば $\text{SiCl}_4$ 、 $\text{SiH}_4$ 、又は $\text{Si}_2\text{H}_6$ -と結合して良い。ガス注入システム200はN含有ガス源210-たとえば $\text{NH}_3$ -をも有して良い。N含有ガス源210は、N含有ガスを処理チャンバ190へ供して、Nをhigh-k誘電膜へ組み込む。複数の種類のガスを処理チャンバ190へ流すため、複数のガス供給ライン212、214、216、218が備えられて良い。

30

#### 【0032】

図4は、本発明の実施例によるALDとCVDを併用したhigh-k誘電膜のその場ハイブリッド堆積の時間変化をグラフで表している。図5A-5Eは、本発明の実施例による基板上へのhigh-k誘電膜のその場ハイブリッド堆積方法の処理フローを概略的な断面図で表している。時間変化は、任意処理である基板の前処理、前記基板上へのhigh-k誘電膜の第1部分の堆積、CVDによる前記第1部分上への前記high-k誘電膜の第2部分の堆積による前記high-k誘電膜の形成、及び任意処理である前記high-k誘電膜の後処理を表している。本発明の実施例によると、前記前処理及び/又は後処理は、図4及び図5A-5Eに図示されたその場ハイブリッド堆積プロセス全体から省略されても良い。本発明の実施例によると、図4に図示さ

40

50

れた処理工程（つまり前処理、ALD、CVD、及び後処理）はその場で-つまり処理チャンバから基板を取り出すことなく-実行されて良い。

### 【0033】

High-k膜のその場ハイブリッド堆積プロセスは、温度 $T_1$ に維持されたバッチ処理システムの処理チャンバ内で基板ホルダ上に複数-たとえば25又は50枚-の被処理基板を供する手順を有する。たとえば図1Aの処理チャンバ102又は図1Bの処理チャンバ10のような壁の熱い処理チャンバでは、処理チャンバ温度は基板温度（付近）である。処理チャンバへの複数の基板の搬入に続いて、処理チャンバは排気され、任意で不活性ガスによってバージされる。

### 【0034】

High-k膜のその場ハイブリッド堆積プロセスは、基板の搬入及び取り外しにかかる時間を節約できる。その理由は、基板は前処理前に一度の搬入しか必要なく、かつ後処理後も一度の取り出ししか必要としないためである。それに加えてそのプロセスは温度変化についても時間を節約する。その理由は、基板が、手順間で搬送温度にまで冷却される必要がないからである。結局そのプロセスは、各処理手順間での搬送手順を省略することによって、基板搬送の時間を節約する。時間の節約に加えて、そのプロセスは、high-k誘電膜が汚染する機会及び基板とhigh-k誘電膜との間の界面層が汚染する機会を減少させる。

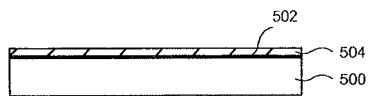

### 【0035】

本発明の一の実施例によると、基板の前処理は、その基板上にhigh-k誘電膜を堆積する前に行われて良い。その前処理が行われることで、図5Aに図示されているように基板500の表面から不純物が除去され、続いて図5Bに図示されているように基板500上に酸化物又は酸窒化物界面層502が形成される。界面層502の厚さは、たとえば約0.4nmから約2nm、又は約0.8nmから約1.5nmであって良い。他の実施例によると、基板500が処理チャンバに搬入されるとき、酸化物又は酸窒化物界面層502が基板500上に存在して良い。他の実施例によると、界面層502は基板500に存在していなくても良い。その前処理は、基板温度を $T_1$ （たとえばほぼ室温）から $T_2$ へ変化させる手順、及び $T_2$ で基板500を所定期間だけ気体の酸化剤に曝露する手順を有して良い。限定ではない例により、その前処理は、約30秒から最大で約30分間、又は約5分から約20分間-たとえば10分間-行われて良い。たとえば酸化剤（酸素及び/又は窒素含有ガス）は、 $O_2$ 、 $O_3$ 、 $N_2O$ 、 $NO$ 、若しくは $H_2O$ 又はこれらの混合物を有して良い。酸化剤は不活性ガス-たとえばAr又は $N_2$ -をさらに有して良い。典型的実施例では、水蒸気発生装置(WVG)が、水蒸気( $H_2O$ )の発生及び処理チャンバへのその水蒸気の（パルス状での）供給に用いられて良い。

### 【0036】

一の実施例では、基板温度 $T_2$ は、前処理中、約200から約1000、約400から約900、又は約500から約850であって良い。典型的実施例では、チャンバ圧力は、約0.01mTorrから約100Torrで、たとえば0.1Torrから約10Torrであって良い。一の典型的な前処理は、約700から約800である基板温度 $T_2$ で基板500をNOに曝露する手順を有する。NO酸化剤の流速は最大約20s<sup>-1</sup>mでたとえば0.1-5s<sup>-1</sup>mであって良い。

### 【0037】

本発明の一の実施例によると、任意手順である前処理後、基板温度は $T_2$ から $T_3$ へ変化し、図5Cに図示されたhigh-k誘電膜の第1部分504が、ALDによって界面層502上に堆積される。他の実施例によると、たとえば前処理が省略されるときには、第1部分504は基板500上に直接堆積されて良い。図4に図示された典型的実施例では、 $T_3$ は $T_2$ よりも低い。代替実施例では、 $T_3$ は $T_2$ 以上であって良い。ALDは、任意手順である前述の前処理と同一の温度及びプロセス条件下で実行されて良い。High-k誘電膜の第1部分504の厚さはたとえば0.5nmから約5nmであって良い。ALDは、等角性の第1部分504の成長速度を、該等角性の第1部分504が下地の界面層502又は基板500との優れた界面特性を有するように供する。

### 【0038】

ALDは平坦面上又は複雑な表面形状にわたり非常に均一な薄膜を堆積する卓抜した能力を示してきた。このような能力の少なくとも一部には、ALDがCVDプロセスほどには流束に

10

20

30

40

50

依存しないことがある。ALDの手法は、化学吸着による反応性先駆体分子（金属先駆体）の飽和分子層又はサブ分子層の形成の原理に基づいている。さらに図4を参照すると、AB層を形成する典型的なALDサイクルは、先駆体すなわち反応物Aを処理チャンバへ流す手順を有する。前記の流す手順は、Aの飽和分子層が基板上に形成されるまでの期間行われる。続いて、先駆体すなわち反応物Aの流れが止まり、そして先駆体すなわち反応物Aは、不活性ガスG<sub>1</sub>を用いて処理チャンバから排気及び/又はバージされる。これに続いて、ある期間先駆体すなわち反応物Aを処理チャンバへ流して、BとAを結合させることで、基板上に層ABを形成する。続いて先駆体すなわち反応物Bの流れが止まり、そして先駆体すなわち反応物Bは、不活性ガスG<sub>2</sub>を用いて処理チャンバから排気及び/又はバージされる。先駆体すなわち反応物Aを導入し、処理チャンバをバージし、先駆体すなわち反応物Bを導入し、かつ処理チャンバをバージするこのプロセスは、所望の厚さを有するAB膜（つまりhigh-k誘電膜の第1部分）を実現するまで、多数回繰り返されて良い。サイクル数、流速、及び曝露時間は、所望のAB膜の厚さに少なくとも部分的に依存すると考えられる。排気及び/又はバージ時間は、プロセス圧力とガス流速のみならず、処理チャンバの容積と設計、及び用いられる化学物質に依存すると考えられる。

#### 【0039】

単なる例として、ALDは、約5-50サイクル-たとえば10-25サイクル-の、酸化剤（たとえばO<sub>2</sub>又はH<sub>2</sub>O）と金属先駆体（たとえばTDEAH）との交互パルス供給を有して良い。酸化剤及び金属先駆体の曝露（又はパルス供給）時間はそれぞれ約5秒から約5分の範囲-たとえば約15秒から約2分-であって良い。HfO<sub>2</sub>を形成する典型的実施例では、酸化剤は、ハフニウム先駆体である限り、2回パルス供給されて良い。排気時間及び/又はバージ時間は、チャンバから過剰な反応物を除去するのに必要な任意の時間-たとえば約10秒から約5分、他の例としては約30秒から約2分-であって良い。

#### 【0040】

ALDによって基板500上にhigh-k誘電膜508の第1部分504を堆積した後、基板温度はT<sub>3</sub>からT<sub>4</sub>へ降温され、かつCVDによって基板温度T<sub>4</sub>で、図5Dに図示されたhigh-k誘電膜508の第2部分506が第1部分504上に堆積される。第1部分504と第2部分506はhigh-k誘電膜508を形成する。CVD処理では、先駆体すなわち反応物AとBはいずれも、所望の厚さを有する第2部分506を堆積するように選ばれた期間、処理チャンバへ流される。第2部分506の厚さはたとえば1nmから約100nmであって良い。図4に図示された典型的実施例では、T<sub>4</sub>はT<sub>3</sub>よりも低い。代替実施例では、T<sub>4</sub>はT<sub>3</sub>以上であって良い。CVDプロセスは、上述のALDと同一又は同様の温度及び圧力条件下で実行されて良い。

#### 【0041】

CVDは、high-k誘電膜508の第1部分504上への第2部分の高成長速度を供する。よってhigh-k誘電膜のその場ハイブリッド堆積プロセスは、ALDによって堆積される第1部分504の優れた等角性及び界面特性と、CVDによって堆積される第2部分506の高堆積速度とを併せ持つ。これにより、最先端の半導体デバイスにおいて、見いだされ又は提案される様々な種類の高品質high-k誘電膜を費用対効果良く形成することが可能となる。High-k誘電膜の全体の厚さは、第1部分504の厚さと第2部分506の厚さを独立に選択することによって選ぶことができる。第2部分506の厚さはALDサイクルの合計数の関数であり、第1部分504の厚さは酸化剤と金属先駆体の合計曝露時間の関数である。

#### 【0042】

本発明の実施例によると、high-k誘電膜のその場ハイブリッド堆積プロセスは、第1組のプロセス条件（たとえばALD基板温度、ALDガス圧、及びALDガス流）を用いてALDを実行する手順、前記プロセス条件を第2組のプロセス条件（たとえばCVD基板温度、CVDガス圧、及びCVDガス流）に調節する手順、及び前記第2組のプロセス条件を用いてCVDを実行する手順を有して良い。バッチ処理システムは、前記プロセス条件を迅速に調節するように備えられている。

#### 【0043】

第2部分506の堆積に続いて、任意手順であるhigh-k誘電膜の後処理が基板温度T<sub>5</sub>で行わ

10

20

30

40

50

れることで、図5Eに図示されている改質されたhigh-k誘電膜が形成される。図4に図示された典型的実施例では、 $T_5$ は $T_4$ よりも高い。代替実施例では、 $T_5$ は $T_4$ 以下であって良い。後処理は、high-k誘電膜508を圧縮し、該high-k誘電膜508から未反応の反応物を除去し、さらに界面層502を酸化し、又は酸素空孔を埋め、かつ/若しくはhigh-k誘電膜508内の置換酸素を再分配する。後処理は、(a)ガスが存在しない雰囲気(つまり高真空条件)で基板温度を約500から約1000にして行う高温アニーリング、(b)酸素及び/若しくは窒素含有ガスから選ばれる第4酸化剤の存在下で基板温度を約500から約1000にして行う高温酸化、又は(c)非酸化剤ガス(たとえばアルゴン(Ar)や窒素(N<sub>2</sub>)のような不活性ガス)の存在下で基板温度を約500から約1000にして行う高温アニーリング、を有して良い。

10

#### 【0044】

後処理は前処理と同一の条件で行われて良いが、これは必須ではなく、他の処理条件が用いられても良い。後処理は、 $T_4$ から $T_5$ への温度を変化させる手順、及び $T_5$ で所定の期間後処理を行う手順を有して良い。一の例では、後処理は、第1期間だけ不活性ガスに曝露し、その後第2期間だけ酸化剤に曝露する手順を有して良い。他の例では、後処理は、第1期間だけ酸化剤に曝露し、その後第2期間だけ不活性ガスに曝露する手順を有して良い。限定ではない例により、その後処理は、約30秒から最大で約30分間、又は約5分から約20分間-たとえば10分間-行われて良い。たとえば酸化剤(酸素及び/又は窒素含有ガス)は、O<sub>2</sub>、O<sub>3</sub>、N<sub>2</sub>O、NO、若しくはH<sub>2</sub>O又はこれらの混合物を有して良い。一の実施例では、基板温度は、後処理中では、約200から約1000、約400から約900、又は約500から約850であって良い。典型的実施例では、チャンバ圧力は、約0.01mTorrから約100Torrで、たとえば0.1Torrから約10Torrであって良い。一の典型的な後処理は、約700から約800の温度でhigh-k誘電膜をNOに曝露する手順を有する。

20

#### 【0045】

本発明の他の実施例によると、その後処理は、第1部分504の堆積前でかつ第2部分506の堆積後に行われて良い。

#### 【0046】

本発明の実施例によると、温度 $T_1$ - $T_5$ は200から1000までの任意の値を有して良いが、それとは異なる温度が選ばれても良い。たとえ任意手順である前処理及び/又は後処理に加えて、ALDとCVDの間で頻繁な温度変化が必要になるとしても、迅速な温度変化能力及び短い温度安定化期間により、高い基板処理能力を得ることができる。処理チャンバの圧力は、任意の前処理、ALD、CVD、及び任意の後処理を通して同一であって良いし、又は変化しても良い。

30

#### 【0047】

図6A及び図6Bは、本発明の実施例による基板上に堆積された追加のhigh-k誘電膜の断面を概略的に図示している。本発明の実施例によると、生成されるhigh-k誘電膜の等角性と電気的特性を良好に制御するため、ALDとCVDは任意の回数だけ交互に繰り返されて良い。一例では、ALDによって堆積される複数の第1膜部分が、CVDによって堆積される相対的に厚い第2膜部分内で、実質的に等間隔に分配されて良い。

#### 【0048】

40

図6Aは、基板600の上に存在する界面層602上の典型的high-k誘電膜638を図示している。High-k誘電膜638は、第1high-k誘電膜608、第2high-k誘電膜618、及び第3high-k誘電膜628を含む。第1high-k誘電膜608は、ALDによって堆積される第1部分604、及びCVDによって堆積される第2部分606を有する。同様に、第2high-k誘電膜618及び第3high-k誘電膜628は、ALDによって堆積される第1部分614と624、及びCVDによって堆積される第2部分616と626を有する。図6Aで概略的に図示されているように、第1部分604, 614, 624は、(実質的に)同一の厚さを有し、かつhigh-k誘電膜638内で実質的に等間隔に分配される。当業者にはすぐに分かるように、ハイブリッドhigh-k誘電膜堆積プロセスは、図6Aに図示されたような3層のhigh-k誘電膜に限定されるものではなく、任意の層数のhigh-k誘電膜が堆積されて良い。一例では、40nmの厚さを有するhigh-k誘電膜が、8回の堆積シーケンスを用い

50

て堆積されて良い。ここで各堆積シーケンスは、ALDによって厚さ1nmのhigh-k誘電膜を堆積し、かつCVDによって厚さ4nmのhigh-k誘電膜を堆積する。

#### 【0049】

同様に図6Bは、基板650の上に存在する界面層652上の別の典型的high-k誘電膜688を図示している。High-k誘電膜688は、第1high-k誘電膜658、第2high-k誘電膜668、及び第3high-k誘電膜678を含む。第1high-k誘電膜658は、ALDによって堆積される第1部分654、及びCVDによって堆積される第2部分656を有する。同様に、第2high-k誘電膜668及び第3high-k誘電膜678は、ALDによって堆積される第1部分664と674、及びCVDによって堆積される第2部分666と676を有する。図6Bで概略的に図示されているように、第1部分654,664,674は、(実質的に)同一の厚さを有するが、第2high-k誘電膜668の第2(CVD)部分666の厚さは、10 対応する第1high-k誘電膜658の第2(CVD)部分656及び第3high-k誘電膜678の第2(CVD)部分676の厚さよりも実質的に厚い。

#### 【0050】

図6A及び図6Bを見ると、当業者は、high-k誘電膜のハイブリッド堆積法が、任意数の第1及び第2部分を有する様々な種類のhigh-k誘電膜の堆積に用いられることをすぐに理解する。ここで第1及び第2部分はそれぞれ任意の所望の厚さを有して良い。当業者にはすぐに分かるように、ハイブリッドhigh-k誘電膜堆積プロセスは、図6Bに図示されたような3層のhigh-k誘電膜に限定されるものではなく、任意の層数のhigh-k誘電膜が堆積されて良い。

#### 【0051】

さらに図6Aと図6Bを参照すると、ALDによってhigh-k誘電膜の一部を堆積することの利点は、high-k誘電膜638と688の全体の漏れ電流の増大に大きく寄与すると考えられる膜の欠陥を阻止すなわち抑制することを含むことができる。従ってhigh-k誘電膜638と688の電気的特性はALDを慎重に用いることによって改善される一方で、そのhigh-k誘電膜のバルク部分はより経済的なCVDによって堆積可能である。20

#### 【0052】

さらに図6Aと図6Bを参照して、本発明の実施例によると、図5A-5Eに記載された後処理が、第1部分604,614と624の堆積後で第2部分606,616と626の堆積前に行われて良い。換言すると、一例では、第1部分604は、第2部分606の堆積前に後処理されて良い。同様に、後処理は、第1部分654,664と674の堆積後で第2部分656,666と676の堆積前に行われて良い。30

#### 【0053】

表1は、CVD、ALD、及びALDに続いてCVDが行われるバッチ処理システム内で基板上にHfO<sub>2</sub>膜を堆積した結果を示している。表1は、堆積方法(酸化剤の種類を含む)、基板温度、合計実行(堆積)時間、EOT、誘電率(k)、フラットバンド電圧シフト( $V_{fb}$ )、界面状態密度( $D_{it}$ )、並びに、2[V]、6[V]、及び8[V]での漏れ電流密度( $J_L$ )を表している。ALDは、275から300の基板温度で、H<sub>2</sub>O酸化剤とTDEAHハフニウム先駆体を交互に曝露する手法を用いた。ここで交互に行われた曝露は、排気及びバージ手順によって分離された。275

のALDプロセスは160回のサイクルを有し、300のALDプロセスは65回のサイクルを有していた。各ALDサイクルは、30秒のH<sub>2</sub>O酸化剤の曝露時間及び90秒のTDEAHの曝露時間を行っていた。30秒のH<sub>2</sub>O酸化剤の曝露及び90秒のTDEAHの曝露後、各ALDサイクルはさらに、1分間のガスバージ、及びそれに続く1分間の排気を行っていた。処理チャンバ圧力はALDプロセス中では0.3Torrであった。H<sub>2</sub>O酸化剤は、水蒸気発生装置内で、流速が0.1l/min@標準状態(slm)のH<sub>2</sub>及び流速が0.1slmのO<sub>2</sub>のガス流を用いることによって生成された。HfO<sub>2</sub>膜の物理的厚さが所望の厚さとなるまで、交互に行われる曝露が行われた。CVDは、235から250の基板温度で、H<sub>2</sub>O酸化剤とTDEAHを同時に曝露する手法を用いた。処理チャンバ圧力はALDプロセス中では0.3Torrであった。O<sub>2</sub>酸化剤のガス流速は0.5slmであった。TDEAH曝露は、TDEAH気化器へのガス流速が1.25slmのN<sub>2</sub>ガスと、該気化器へ同時に供給される0.1立方センチメートル(cc)/minのTDEAH液体を有していた。40

#### 【0054】

表1から分かるように、ALDによるhigh-k誘電膜の堆積は、CVDによる堆積よりもはるか

10

20

30

40

50

に遅かった。この理由の少なくとも一部には、ALDでは、反応ガスH<sub>2</sub>O及びTDEAHと、バージガスを分離する必要があるからである。しかしALDはCVDよりもよく使用されている、すなわちALDよりも好まれている。その理由は、ALDは、CVDと比較して、深溝中及び複雑な表面形状を有する構造上に均一な厚さの薄膜を堆積できるためである。さらにALDによって堆積されるhigh-k誘電膜は通常、すぐれた電気的特性を示す。その理由の少なくとも一部には、ALDによって堆積されるhigh-k誘電膜に存在する欠陥が少ないことがある。ALDとCVDについての表1に示された膜の特性の比較は、ALDによって堆積されたHfO<sub>2</sub>膜は、CVDによって堆積されたHfO<sub>2</sub>膜よりも、高い誘電率(k)、低いヒステリシス(ΔV<sub>fb</sub>)、低い界面状態密度(D<sub>it</sub>)、及び低い漏れ電流密度を示している。しかしCVDの堆積時間はALDの堆積時間よりもはるかに短い。しかもCVDがALDよりも低い基板温度を用いて行われても、CVDの堆積時間はALDの堆積時間よりもはるかに短い。

#### 【0055】

表1はさらに、本発明の実施例によるHfO<sub>2</sub>のその場ハイブリッド堆積の結果を示している。当該その場ハイブリッド堆積は、ALDとCVDによってHfO<sub>2</sub>膜を順次堆積する手順を有していた。ALDは、275 の基板温度で、H<sub>2</sub>O酸化剤とTDEAHハフニウム先駆体を交互に曝露する手法を用いた。ここで交互に行われた曝露は、排気及びバージ手順によって分離された。ALDプロセスは70回のサイクルを有し、そのALDプロセスに続いて40分間のCVDプロセスが行われた。ALDとCVDのプロセス条件については上述した。続いて温度を、5 /minの速度で、275 から235 に変化させた。CVDプロセスは、235 の基板温度で、H<sub>2</sub>O酸化剤とTDEAHを同時に曝露する手法を用いた。

#### 【0056】

表1から分かるように、当該その場ハイブリッド堆積は、ALD単独よりも短い実行時間と、CVD単独よりも改善されたHfO<sub>2</sub>膜の電気的特性との妥協を供する。

#### 【0057】

#### 【表1】

| 堆積法<br>(酸化剤)                                  | 基板温度<br>(°C) | 膜厚<br>(Å) | 合計実行<br>時間<br>(時) | 等価酸<br>化物膜<br>厚(Å) | 誘電率<br>(k) | Δ V <sub>fb</sub><br>(mV) | D <sub>it</sub><br>(10 <sup>-11</sup> eV/cm <sup>2</sup> ) | J <sub>L</sub> (Amps/cm <sup>2</sup> ) |                      |                      |

|-----------------------------------------------|--------------|-----------|-------------------|--------------------|------------|---------------------------|------------------------------------------------------------|----------------------------------------|----------------------|----------------------|

|                                               |              |           |                   |                    |            |                           |                                                            | 2[V]                                   | 6[V]                 | 8[V]                 |

| CVD<br>(O <sub>2</sub> )                      | 250          | 337.7     | 2.6               | 99.6               | 13.2       | 227                       | 3.7                                                        | 1.5x10 <sup>-6</sup>                   | 5.5x10 <sup>-5</sup> | 1.3x10 <sup>-4</sup> |

| CVD<br>(O <sub>2</sub> )                      | 235          | 337       | 3.0               | 105.4              | 12.5       | 238                       | 3.4                                                        | 1.3x10 <sup>-6</sup>                   | 4.8x10 <sup>-5</sup> | 1.1x10 <sup>-4</sup> |

| ALD<br>(H <sub>2</sub> O)                     | 275          | 372.1     | 20.5              | 105.9              | 13.7       | 42                        | 2.7                                                        | 1.4x10 <sup>-6</sup>                   | 4.7x10 <sup>-5</sup> | 1.1x10 <sup>-7</sup> |

| ALD<br>(H <sub>2</sub> O)                     | 300          | 303       | 9.6               | 80                 | 14.7       | 174                       | 3.8                                                        | 2.9x10 <sup>-7</sup>                   | 9.6x10 <sup>-6</sup> | 2.2x10 <sup>-6</sup> |

| ALD/CVD<br>(H <sub>2</sub> O/O <sub>2</sub> ) | 275/235      | 302       | 10.4              | 84.6               | 13.9       | 203                       | 3.1                                                        | 1.6x10 <sup>-7</sup>                   | 7.9x10 <sup>-6</sup> | 4.0x10 <sup>-6</sup> |

大容量半導体製造用のバッチ処理システム内で複数の基板上にhigh-k誘電膜を堆積する複数の実施例が開示されてきた。本発明の実施例の上記記載は、例示及び説明を目的としているに過ぎない。開示された厳密な形態に限定することを意図していない。この説明及び以降の特許請求の範囲は、もっぱら説明目的で用いられていて限定を意図しない語句を含む。

#### 【0058】

たとえ本発明のある典型的実施例のみが詳細に説明されたとしても、当業者は、本発明の上記教示に基づいて、多くの修正型及び変化型が可能であることをすぐに理解する。当業者は、図に示された様々な構成部品についての様々な均等な組合せや置き換えを理解する。従って多くの係る修正型は、本発明の技術的範囲内に含まれるものと解される。

#### 【符号の説明】

10

20

30

40

50

## 【 0 0 5 9 】

|     |            |    |

|-----|------------|----|

| 1   | バッチ処理システム  |    |

| 2   | 円筒形マニホールド  |    |

| 10  | 処理チャンバ     |    |

| 15  | ヒーター       |    |

| 20  | ヒーター       |    |

| 21  | 回転モーター     |    |

| 22  | 昇降機        | 10 |

| 23  | 上端部        |    |

| 25  | プロセス管      |    |

| 26  | 回転台        |    |

| 27  | 蓋          |    |

| 28  | モーター       |    |

| 30  | 熱反射体       |    |

| 35  | 基板ホルダ      |    |

| 40  | 基板         |    |

| 45  | ガス供給ライン    |    |

| 65  | ヒーター       |    |

| 70  | ヒーター       |    |

| 75  | センサ        | 20 |

| 80  | 排出パイプ      |    |

| 82  | 自動圧力制御装置   |    |

| 84  | トラップ       |    |

| 86  | 真空ポンプ      |    |

| 88  | 真空排気システム   |    |

| 90  | 制御装置       |    |

| 92  | プロセス監視システム |    |

| 94  | ガス注入システム   |    |

| 100 | バッチ処理システム  |    |

| 102 | 処理チャンバ     | 30 |

| 104 | ガス注入システム   |    |

| 106 | 真空排気システム   |    |

| 108 | プロセス監視システム |    |

| 110 | 基板         |    |

| 112 | 基板ホルダ      |    |

| 114 | 外側区域       |    |

| 116 | 内側区域       |    |

| 118 | 容積         |    |

| 120 | 容積         |    |

| 122 | ヒーター       | 40 |

| 124 | 制御装置       |    |

| 190 | 処理チャンバ     |    |

| 200 | ガス注入システム   |    |

| 202 | 液体供給システム   |    |

| 204 | バーリングシステム  |    |

| 206 | Si含有ガス源    |    |

| 208 | 酸化ガス源      |    |

| 210 | N含有ガス源     |    |

| 500 | 基板         |    |

| 502 | 界面層        | 50 |

|     |                |    |

|-----|----------------|----|

| 504 | 第1部分           |    |

| 506 | 第2部分           |    |

| 508 | high-k誘電膜      |    |

| 510 | 改質されたhigh-k誘電膜 |    |

| 600 | 基板             |    |

| 602 | 界面層            |    |

| 604 | 第1部分           |    |

| 606 | 第2部分           |    |

| 608 | 第1high-k誘電膜    |    |

| 614 | 第1部分           | 10 |

| 616 | 第2部分           |    |

| 618 | 第2high-k誘電膜    |    |

| 624 | 第1部分           |    |

| 626 | 第2部分           |    |

| 628 | 第3high-k誘電膜    |    |

| 638 | high-k誘電膜      |    |

| 650 | 基板             |    |

| 652 | 界面層            |    |

| 654 | 第1部分           |    |

| 656 | 第2部分           | 20 |

| 658 | 第1high-k誘電膜    |    |

| 664 | 第1部分           |    |

| 666 | 第2部分           |    |

| 668 | 第2high-k誘電膜    |    |

| 674 | 第1部分           |    |

| 676 | 第2部分           |    |

| 678 | 第3high-k誘電膜    |    |

| 688 | high-k誘電膜      |    |

【図1A】

【図1B】

【図2】

【図3】

【図4】

【図5A】

【図5B】

【図 5 C】

【図 5 D】

【図 5 E】

【図 6 A】

【図 6 B】

---

フロントページの続き

(72)発明者 アンソニー ディップ

アメリカ合衆国 テキサス州 78612 シダー・クリーク ベコス・ストリート 147

審査官 萩原 周治

(56)参考文献 特表2004-504496(JP,A)

特開2000-077397(JP,A)

国際公開第2004/107451(WO,A1)

国際公開第2007/131051(WO,A1)

特開2005-011904(JP,A)

特開2004-047660(JP,A)

特開2007-287804(JP,A)

特表2009-509039(JP,A)

特表2009-536459(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/31-21/32

H01L 21/205

C23C 16/00-16/56

H01L 21/336

H01L 21/8229

H01L 21/8239-21/8247

H01L 27/10-27/115

H01L 29/78

H01L 29/788-29/792