(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4611421号

(P4611421)

(45) 発行日 平成23年1月12日(2011.1.12)

(24) 登録日 平成22年10月22日(2010.10.22)

|                      |           |

|----------------------|-----------|

| (51) Int.Cl.         | F 1       |

| HO4B 10/04 (2006.01) | HO4B 9/00 |

| HO4B 10/06 (2006.01) |           |

| HO4B 10/14 (2006.01) |           |

| HO4B 10/26 (2006.01) |           |

| HO4B 10/28 (2006.01) |           |

請求項の数 4 (全 13 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2008-508835 (P2008-508835)  |

| (86) (22) 出願日 | 平成18年2月28日 (2006.2.28)        |

| (65) 公表番号     | 特表2008-539653 (P2008-539653A) |

| (43) 公表日      | 平成20年11月13日 (2008.11.13)      |

| (86) 國際出願番号   | PCT/US2006/007115             |

| (87) 國際公開番号   | W02006/118644                 |

| (87) 國際公開日    | 平成18年11月9日 (2006.11.9)        |

| 審査請求日         | 平成21年2月23日 (2009.2.23)        |

| (31) 優先権主張番号  | 11/118,230                    |

| (32) 優先日      | 平成17年4月28日 (2005.4.28)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 78735 テキサス州<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100116322<br>弁理士 桑垣 衡                                                                                      |

| (72) 発明者  | ミジャスコビック、デジアン<br>アメリカ合衆国 85248 アリゾナ州<br>チャンドラー ダブリュ. スパロー プ<br>レイス 819                                     |

最終頁に続く

(54) 【発明の名称】論理しきい値取得回路および逆ピーク検出器を使用する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基準値を有する基準信号入力と、

第1の差動入力信号と基準信号とに対応して第1の出力信号を生成するように構成された第1の逆ピーク検出器であって、

第1のノードのところで第1の抵抗と結合して、前記第1の差動入力信号を受信する第1のコンデンサと、

前記第1のノードと結合している第1のダイオードと、

前記第1のノードとアースとの間に結合している第1のスイッチと、

第2のノードと前記第1のダイオードの間に結合して、前記基準信号および第1の出力信号を受信するように構成された第1のアンプと、 10

前記第1のノードと第2のノードとの間に結合して、前記基準値より大きい値にシフトした前記第1の差動入力信号のレプリカである前記第1の出力信号を発生するように構成された第1のバッファと、からなる前記第1の逆ピーク検出器と、

第2の差動入力信号と前記基準信号とに対応して、前記基準値より大きい値にシフトした前記第2の差動入力信号のレプリカである第2の出力信号を生成するように構成された第2の逆ピーク検出器と、からなり、

前記第1の出力信号の最小値および前記第2の出力信号の最小値が、前記基準値以上である、回路。

## 【請求項 2】

入力信号を受信するように構成され、また第1の入力信号および第2の入力信号を発生するように構成された差動コンバータと、

前記第1の入力信号および前記第2の入力信号を受信するように構成され、また第1の差動入力信号および第2の差動入力信号を発生するように構成されたアンプと、

をさらに備える請求項1に記載の回路。

【請求項3】

前記第2の逆ピーク検出器が、

第3のノードのところで第2の抵抗と結合して、前記第2の差動入力信号を受信する第2のコンデンサと、

前記第3のノードと結合している第2のダイオードと、

10

前記第3のノードとアースとの間に結合している第2のスイッチと、

前記第4のノードと前記第2のダイオードとの間に結合して、前記基準信号および前記第2の出力信号を受信するように構成された第2のアンプと、

前記第3のノードと前記第4のノードとの間に結合して、前記第2の出力信号を発生するように構成された第2のバッファと、を備え、

前記第2の出力信号の最小値が前記基準値より上に位置する請求項1に記載の回路。

【請求項4】

逆ピーク検出器回路であって、

基準値を有する基準信号入力と、

ノードのところで抵抗と結合して、差動入力信号を受信するように構成されたコンデンサと

20

前記ノードに結合しているダイオードと、

前記ノードとアースとの間に結合しているスイッチと、

前記ノードと第2のノードとの間に結合して、出力信号を発生するように構成されたバッファと、

前記第2のノードと前記ダイオードとの間に結合して前記基準信号および前記出力信号を受信するように構成され、前記出力信号の最小値が前記基準値以上である、アンプと、を備える逆ピーク検出器回路。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は、概して、光通信に関し、特に、論理しきい値を取得する方法に関する。

【背景技術】

【0002】

光ネットワークは、ネットワークを介してデータを送信するために光信号を使用する。光信号は、データを運ぶために使用されるが、光信号は、通常、データを抽出し、処理するために電気信号に変換される。光信号の電気信号への変換は、多くの場合光受信機を使用することにより行われる。光受信機は、光ファイバを介して受信した光信号を電気信号に変換し、この電気信号を増幅して、デジタル・データ・ストリームに変換する。

【0003】

40

バースト・モード受動光ネットワーク(BPON)は、家庭の光送信機から、ハブ/縁石のところに位置する光モジュールに光信号を送信するためにケーブル業界で広く使用されている。光モジュールは通常光受信機を備える。BPON用途で使用される典型的な光信号は155Mbps以上の周波数を有することができる。バースト・モード技術を使用するには、着信信号の高速で正確な処理、および送信機側および光受信機側両方での光パワー・レベルの正確な処理が必要になる。光受信機は、ユーザ・グループ内の各ユーザからの上りトラヒックのバーストの形をしている着信光信号を受信する。各ユーザは、通常、ネットワーク内の異なる地点に位置する。各上りバーストは、通常、500ビットのような固定サイズである。減衰のために、各上りバーストの強度または振幅は、光受信機からユーザまでの距離、上りバーストが移動する光ファイバの長さ、上りバーストを送信する

50

送信機の強度等によりかなり変化する場合がある。例えば、電圧に変換した後、1人のユーザからの上りバーストは1Vの振幅を有する場合があり、一方、他のユーザからの他の上りバーストは1mVの振幅を有する場合がある。各上りバーストは、8ビットのプリアンブル(10101010)を含む。B P O Nシステムにおいては、155M b p sのバースト・モード光受信機は、論理1と論理0とを判別することができるよう、この8ビット・プリアンブル中の上りバーストの論理しきい値を入手しなければならない。論理しきい値とは、論理1と論理0とを判別するために使用する値である。論理しきい値は各上りバーストに対して決定される。次に、光受信機モジュールは、着信信号をスライスして、デジタル出力を生成するためにこの論理しきい値を使用する。

## 【0004】

10

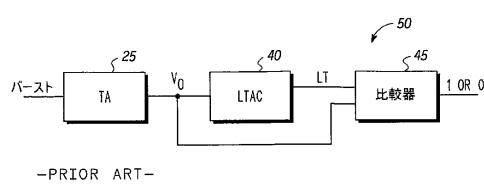

図1は、トランスインピーダンス・アンプ25と、論理しきい値取得回路(L T A C)40と、比較器45とを含む従来の光受信機モジュール50のブロック図である。トランスインピーダンス・アンプ25は、L T A C 40と結合し、また比較器45と結合し、L T A C 40は比較器45と結合している。

## 【0005】

上りバーストは、トランスインピーダンス・アンプ25と結合しているフォトダイオードに入射する。トランスインピーダンス・アンプ25は、フォトダイオードが発生した入力電流信号を、比較的大きな振幅の出力電圧(V<sub>o</sub>)信号に増幅する。トランスインピーダンス・アンプ25は、この出力電圧(V<sub>o</sub>)信号を論理しきい値(L T)を発生するL T A C 40に送信する。L T A C 40は、論理しきい値(L T)を比較器45に送信する。次に、上りバーストが論理1または論理0であるか否かを判定するために、論理しきい値(L T)をトランスインピーダンス・アンプ25からの出力電圧(V<sub>o</sub>)信号と比較するために比較器45を使用する。例えば、上りバーストが論理しきい値より大きい場合には、上りバーストは論理1であると判定され、上りバーストが論理しきい値より小さい場合には、上りバーストは論理0であると判定される。

20

## 【0006】

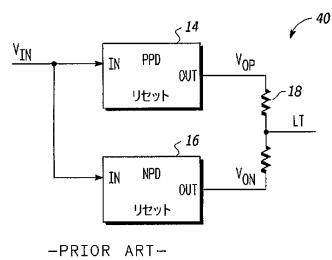

図2は、図1の光受信機モジュール50で使用する従来のL T A C 40の回路図である。論理しきい値取得回路40は、山または正のピーク検出器(P P T)回路14、谷または負のピーク検出器回路(N P D)16および抵抗ストリング18を有する。

## 【0007】

30

P P D回路14は、入力信号(V<sub>i n</sub>)に応じて正の出力電圧(V<sub>o p</sub>)を発生する。N P D回路16は、入力信号(V<sub>i n</sub>)に応じて負の出力電圧(V<sub>o n</sub>)を発生する。それ故、P P D回路14は最大ピーク値を測定し、N P D回路16は上りバーストの最小ピーク値を測定する。

## 【0008】

抵抗ストリング18は、P P D回路14およびN P D回路16の出力間に直列に結合することができる。上りバーストの最大ピーク値(V<sub>o p</sub>)は、抵抗ストリング18の一方の端部のところで受信され、上りバーストの最小ピーク値(V<sub>o n</sub>)は、抵抗ストリング18の他方の端部のところで受信される。平均値は、抵抗ストリング18の中間のところから入手することができる。これにより、上りバーストの最大ピーク値(V<sub>o p</sub>)および上りバーストの最小ピーク値(V<sub>o n</sub>)の平均値(または算術平均)を明示的に決めることができる。この平均値は、論理1と論理0を判別するために使用される論理しきい値である。上りバーストは、論理しきい値と比較され、上りバーストが論理しきい値を超えた場合には、光受信機モジュール50は論理1を受信中であると判定され、入力バーストがしきい値より小さい場合には、光受信機モジュール50は論理0を受信中であると判定する。

40

## 【0009】

あるB P O N用途の場合には、高速および低電力用に設計された光受信機モジュール50を使用したい場合がある。例えば、ある実施態様の場合には、光受信機モジュール50の電源電圧は3ボルトである。上記従来のL T A C 40は、電源のヘッドルームがないた

50

めにこれらの用途に適していない場合がある。さらに、LTAC40は、高い精度で論理しきい値を入手しなければならない。例えば、一実施態様の場合には、LTAC40は、論理しきい値を検出する際に最大誤差が1mVである論理しきい値を入手しなければならない。都合の悪いことに、このような低電力の実施態様の場合、正の出力電圧( $V_{op}$ )および負の出力電圧( $V_{on}$ )は、任意の量だけ相互にオフセットしていて、予め定められた関係を有していない。正の出力電圧( $V_{op}$ )および負の出力電圧( $V_{on}$ )が基準電圧( $V_{ref}$ )に対してどこに位置するのかを正確に判定するのが難しい場合がある。

#### 【0010】

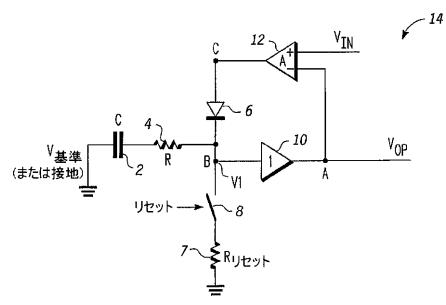

図3は、図2のLTAC40で使用する従来の正のピーク検出器(PPD)回路14の回路図である。PPD回路14は、コンデンサ2と、抵抗4と、ダイオード6と、抵抗7と、リセット・スイッチ8と、バッファ10と、アンプ12とを使用する。抵抗4は、コンデンサ2と第1のノードBとの間に結合している。ダイオード6は、ノードBとノードCとの間に結合し、スイッチ8は、ノードBとアースへの抵抗7との間に結合している。バッファ10は、ノードBとノードAとの間に結合し、アンプ12は、ノードAとノードCのところのダイオード6との間に結合している。

#### 【0011】

コンデンサ2は接地されている。バッファ10は、正の出力電圧( $V_{op}$ )を発生する。アンプ12は、第1の出力電圧( $V_{op}$ )および入力電圧( $V_{in}$ )を受信する。アンプ12は、100~1000の間であってもよい利得Aを有する高利得アンプである。アンプ12は、ダイオード6と結合しているノードBを駆動する。

#### 【0012】

最初に、スイッチ8がオンになっているためにノードBは接地電位になっている。新しい論理しきい値の取得が開始する前に、リセットおよび放電ノードBおよび接地電位へのコンデンサ2を除去するためにリセット・スイッチ8をオフにすることができる。次に、入力電圧( $V_{in}$ )が印加される。ダイオード6は、入力電圧( $V_{in}$ )が正の出力電圧( $V_{op}$ )より大きい場合には、正の電圧に応じてオンになる。入力電圧( $V_{in}$ )がノードBのところの電圧( $V_1$ )よりも小さい場合には、何事も起こらず、正の出力電圧( $V_{op}$ )は同じままである。入力電圧( $V_{in}$ )がノードBのところの電圧( $V_1$ )よりも大きい場合には、正の出力電圧( $V_{op}$ )は、入力電圧( $V_{in}$ )の値に追従するかまたはその値と見なす。例えば、入力電圧( $V_{in}$ )がノードBのところの電圧( $V_1$ )よりも大きい場合には、入力電圧( $V_{in}$ )と $V_1$ との間の差が、アンプ12の利得にほぼ等しい量だけ増幅され、ダイオード6がオンになり、ノードBのより高い電位への充電が開始する。正の出力電圧( $V_{op}$ )は、ノードBのところで電圧( $V_1$ )を追隨し、アンプ12に入力される。入力電圧( $V_{in}$ )が下降を始めると、アンプ12の利得に比例してアンプ12の出力が急速に低減するように、アンプ12が反応する。最終的には、これによりダイオード6をオフにすることができる。次に、ノードBのところの電圧( $V_1$ )が、コンデンサを介してノードBのところに「蓄積」され、もはや入力電圧( $V_{in}$ )に依存しなくなる。

#### 【0013】

谷ピーク検出器16は、アノードおよびカソードが逆になるようにダイオード6を単に反転させるだけで構成することができることを理解されたい。このようにして、ダイオード6は、入力電圧( $V_{in}$ )が負の出力電圧( $V_{on}$ )よりも低い場合には、負の電圧に応じてオンになる。入力電圧( $V_{in}$ )がノードBのところの電圧 $V_1$ よりも低い場合には、負の出力電圧( $V_{on}$ )は、入力電圧( $V_{in}$ )の値に追従するかまたはその値と見なす。入力電圧( $V_{in}$ )がノードBのところの電圧 $V_1$ よりも大きい場合には、何事も起こらず、負の出力電圧( $V_{on}$ )は同じままである。

#### 【0014】

差動信号( $V_{op}$ )および( $V_{on}$ )は、通常、未知の電圧量またはオフセットにより相互に分離またはオフセットしている。そのため、論理しきい値を入手しようとして、正の出力電圧( $V_{op}$ )および負の出力電圧( $V_{on}$ )を単に比較するだけの従来のLT

10

20

30

40

50

Cを使用して論理しきい値を決定するのが難しくなる。大入力信号範囲(1V)に対する要件により、またダイオード6の両端間の電圧降下により、アンプ12内および単一利得バッファ10内においては、このようなピーク検出器を、妥当な精度およびオフセット性能を提供しながら、 $V_{c c} = 3.0V$ で設計することができる。

【発明の開示】

【発明が解決しようとする課題】

【0015】

それ故、低電力光受信機モジュールで正の出力電圧を負の出力電圧と比較するための高精度技術を提供することは望ましいことである。例えば、論理しきい値を明示的に判定しなくてもすむように、どの程度正の出力電圧信号が負の出力電圧信号からオフセットしているかを判定しなくてもよい技術を提供することは望ましいことである。

10

【課題を解決するための手段】

【0016】

さらに、添付の図面および上記技術分野および発明の背景を参照しながら以下の詳細な説明および添付の特許請求の範囲を読めば、本発明の他の望ましい機能および特徴を理解することができるだろう。

【0017】

類似の参照符号が類似の素子を示す添付の図面を参照しながら、以下に本発明について説明する。

【発明を実施するための最良の形態】

20

【0018】

下記の詳細な説明は単に例示としてのものであって、本発明または本発明の適用および使用を制限するものではない。さらに、本発明は、上記技術分野、発明の背景、発明の概要または下記の詳細な説明に記載するすべての明示的または暗黙的理論により制限を受けない。

【0019】

本明細書で使用する場合、「ノード」という用語は、所与の信号、論理レベル、電圧、データ・パターン、電流または量が提示される、任意の内部または外部の基準点、接続点、接合部、信号線、導電性素子等を意味する。さらに、2つ以上のノードを1つの物理的素子により実現することもできる（また、2つ以上の信号を、共通のノードのところで受信または出力した場合でも、多重化、変調または他の方法で区別することができる）。

30

【0020】

以下に一緒に「接続している」、または「結合している」ノードまたは機能について説明する。本明細書で使用する場合、他に別段の指定がない限り、「接続している」という用語は、1つのノード／機能が他のノード／機能と直接または間接に接続していることを意味し、その接続は必ずしも機械的なものでなくてもよいことを意味する。同様に、他に別段の指定がない限り、「結合している」という用語は、1つのノード／機能が他のノード／機能と直接または間接に結合していることを意味し、その結合は必ずしも機械的なものでなくてもよいことを意味する。それ故、図1～図5および図8に示す略図は、素子の例示としての配置を示すが、（回路の機能に悪影響を与えないと仮定して）追加の介入素子、装置、機能または構成要素を実際の実施形態で使用することができる。さらに、本明細書の種々の図面に示す接続線は、種々の素子間の例示としての機能的関係および／または物理的結合を表すためのものである。実際の実施形態においては、多くの代案、または追加の機能的関係または物理的接続を使用することに留意されたい。

40

【0021】

下記の実施形態は、電源のヘッドルームの問題( $V_{c c} = 3.0V$ )を解決しながら、高精度しきい値取得を可能にする。しきい値取得回路は、差動信号の論理しきい値を暗黙のうちに取得するために、正の逆ピーク検出器、および負の逆ピーク検出器を実施するためのものである。「逆」ピーク検出器は、図3の従来のピーク検出器に関して、入力電圧( $V_{in}$ )および基準電圧( $V_{ref}$ )が交換されるピーク検出器である。これらの逆ピ

50

ーク検出器は、「ペデスタル位置決め回路」(PPC)と呼ぶことができる。逆ピーク検出器は、リセット・スイッチと、アンプと、ダイオードと、コンデンサと、バッファとを備える。逆ピーク検出器のリセットが除去されると、リセット・スイッチがオフになる。次に、出力電圧( $V_{out}$ )は、強制的に基準電圧( $V_{ref}$ )と等しくなるか、またはアンプおよびダイオードによりもっと高くなる。これによりコンデンサが、入力電圧( $V_{in}$ )がその最小値である場合に、出力電圧( $V_{out}$ )を基準電圧( $V_{ref}$ )に等しくする値に充電される。取得が終了すると、基準電圧( $V_{ref}$ )を若干低い値にシフトすることにより、逆ピーク検出器が「凍結(frozen)」する。それ故、出力電圧( $V_{out}$ )は、基準電圧( $V_{ref}$ )に等しい「ペデスタル」上に位置する入力電圧( $V_{in}$ )のレプリカである。入力電圧( $V_{in}$ )は、コンデンサにより回路の残りの部分とAC結合しているので、回路パラメータおよび基準電圧( $V_{ref}$ )を、入力電圧( $V_{in}$ )からほとんど独立して選択することができる。これにより、もっと電源のヘッドラムが広くなるので、 $V_{cc} = 3.0\text{ V}$ の電源のところで高い精度を取得することができる。

#### 【0022】

各逆ピーク検出器は、シングル・エンドで、差動入力信号( $V_p, V_n$ )の半体上で動作する。逆ピーク検出器は同一のものであり、逆ピーク検出器が発生し、しきい値取得のために使用する2つの出力電圧( $V_{op}, V_{on}$ )は同じ方法で取得される。それ故、系統的オフセットを除去することができる。取得中、差動入力信号( $V_p, V_n$ )の両方の半体は、基準電圧( $V_{ref}$ )に等しい同じペデスタル上に位置し、出力電圧 $V_{op}$ および $V_{on}$ として逆ピーク検出器の出力のところに現れる。データ・スライシングは、比較器の入力に出力電圧( $V_{op}, V_{on}$ )を直接送ることにより行うことができる。それ故、明示的論理しきい値の値を取得する必要はない。

#### 【0023】

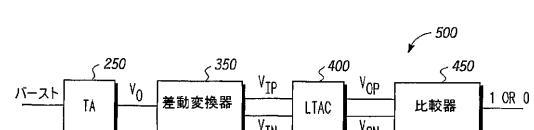

図4は、例示的実施形態による光受信機モジュール500のブロック図である。光受信機モジュール500は、比較器450と、これと結合している論理しきい値取得回路(LTAC)400と、これと結合している差動コンバータ350と、これと結合しているトランスインピーダンス・アンプ250とを備える。

#### 【0024】

トランスインピーダンス・アンプ250は、光の上りバーストを受信し、この光に基づいて出力電圧( $V_o$ )を発生する。

差動コンバータ350は、トランスインピーダンス・アンプ350のシングル・エンドの出力信号( $V_o$ )を受信し、第1の入力電圧( $V_{ip}$ )およびLTAC400に送られる第2の入力電圧( $V_{in}$ )を発生するように構成される。差動信号 $V_{ip}$ は、シングル・エンドの出力信号( $V_o$ )と同一のものであり、差動信号( $V_{in}$ )は、シングル・エンドの出力信号( $V_o$ )の反転したバージョンである。

LTAC400は、第1の出力電圧( $V_{op}$ )および第2の出力電圧( $V_{on}$ )を発生するため、第1の入力電圧( $V_{ip}$ )および第2の入力電圧( $V_{in}$ )を使用する。

#### 【0025】

比較器45は、シングル・エンドの出力信号( $V_o$ )が論理1または論理0を含むか否かを判定するために、第1の出力電圧( $V_{op}$ )および第2の出力電圧( $V_{on}$ )を比較する。一実施形態の場合には、シングル・エンドの出力信号( $V_o$ )は、比較器45が第1の出力電圧( $V_{op}$ )が第2の出力電圧( $V_{on}$ )より大きいと判定した場合には、論理1を含み、比較器45が第1の出力電圧( $V_{op}$ )が第2の出力電圧( $V_{on}$ )より小さいと判定した場合には、論理0を含む。

#### 【0026】

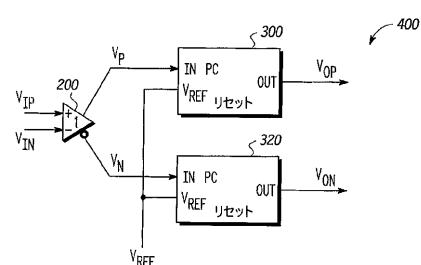

図5は、例示的実施形態による論理しきい値取得回路(LTAC)400の回路図である。LTAC400は、第1の位置決め回路300および第2の位置決め回路320と結合しているアンプ200とを備える。

#### 【0027】

10

20

30

40

50

アンプ200は、差動信号( $V_{ip}$ ,  $V_{in}$ )を受信し、差動信号( $V_{ip}$ ,  $V_{in}$ )から差動信号( $V_p$ )および( $V_n$ )を発生する。差動信号( $V_n$ )は、差動信号( $V_p$ )を反転したものを含み、( $V_p$ )から逆相を有する。差動信号( $V_p$ )上のすべてのノイズは、同じ方法で他の差動入力信号( $V_n$ )に影響を与え、そのためノイズが打ち消される。差動信号( $V_p$ )および( $V_n$ )は、電圧ヘッドルームの点でシングル・エンドの入力信号( $V_n$ )よりももっと広いダイナミック・レンジを提供するのを助ける。何故なら、ダイナミック・レンジは、差動信号( $V_p$ )および( $V_n$ )の間の差をチェックすることにより決定されるからである。

#### 【0028】

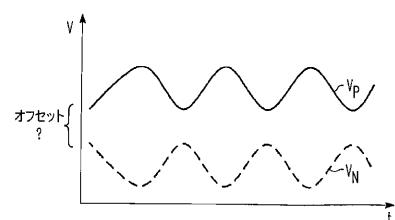

図6は、差動信号 $V_p$ および $V_n$ を示す波形図である。第1の入力電圧( $V_{ip}$ )および第2の入力電圧( $V_{in}$ )に応じるアンプ200は、第1の差動入力信号( $V_p$ )および第2の差動入力信号( $V_n$ )を発生する。10

#### 【0029】

図6に示すように、差動信号( $V_p$ )および( $V_n$ )は、通常、未知の電圧量またはオフセットにより相互に分離またはオフセットしている。これにより、論理しきい値を入手しようとして、( $V_p$ )および( $V_n$ )を単に比較するだけの従来のLTAC40を使用して論理しきい値を決定するのが難しくなる。LTAC40を使用すれば、LTを正確に判定するために、差動信号( $V_p$ )および( $V_n$ )が相互にどの程度オフセットしているかを判定する必要がなくなる。

#### 【0030】

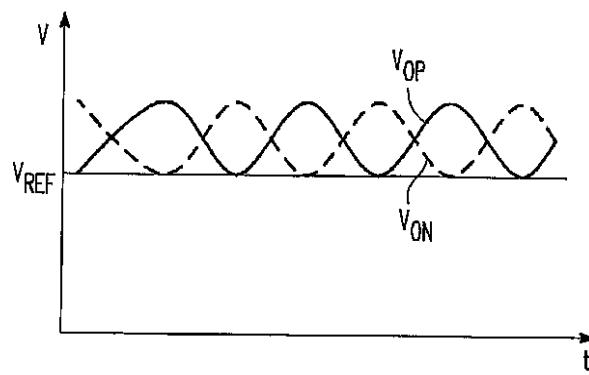

図7は、第1の位置決め回路300および第2の位置決め回路320がそれぞれ発生した差動信号( $V_{op}$ )および( $V_{on}$ )を示す波形図である。20

正の出力電圧( $V_{op}$ )および負の出力電圧( $V_{on}$ )は、正の出力電圧( $V_{op}$ )および負の出力電圧( $V_{on}$ )が相互にオフセットしないように、(x軸上の)共通の基準値を共有する。正の出力電圧( $V_{op}$ )および負の出力電圧( $V_{on}$ )は、両方とも基準電圧( $V_{ref}$ )よりも高い。

#### 【0031】

正の出力電圧( $V_{op}$ )は、正の出力電圧( $V_{op}$ )が基準電圧( $V_{ref}$ )よりも小さくならないように、基準電圧( $V_{ref}$ )より上に位置する。正の出力電圧( $V_{op}$ )は、( $V_p$ )が最小値になった場合に、正の出力電圧( $V_{op}$ )が基準電圧( $V_{ref}$ )にほぼ等しくなるように、基準電圧( $V_{ref}$ )上にシフトした( $V_p$ )のレプリカである。30

#### 【0032】

負の出力電圧( $V_{on}$ )は、負の出力電圧( $V_{on}$ )が基準電圧( $V_{ref}$ )よりも低くならないように、基準電圧( $V_{ref}$ )より上に位置する。負の出力電圧( $V_{on}$ )は、( $V_n$ )が最小値になった場合に、負の出力電圧( $V_{on}$ )が基準電圧( $V_{ref}$ )にほぼ等しくなるように、基準電圧( $V_{ref}$ )上にシフトした( $V_n$ )のレプリカである。

#### 【0033】

一実施形態の場合には、正の差動出力信号( $V_{op}$ )および負の差動出力信号( $V_{on}$ )を、正の差動出力信号( $V_{op}$ )と負の差動出力信号( $V_{on}$ )とを比較する比較器に送ることができる。比較器の出力は、比較器が論理0または論理1を受信しているか否かを判定する。正の差動出力信号( $V_{op}$ )が負の差動出力信号( $V_{on}$ )より大きい場合には、受信機は、論理1を受信中であると見なす。正の差動出力信号( $V_{op}$ )が負の差動出力信号( $V_{on}$ )より小さい場合には、受信機は、論理0を受信中であると見なす。40

#### 【0034】

それ故、LTAC400は、従来のLTAC40の場合のように、オフセットまたは論理しきい値(最大ピーク値と最小ピーク値との間の平均値)を明示的に判定しない。それどころか、図7に示すように、差動信号( $V_p$ ,  $V_n$ )間のオフセットを、その下で正の差動出力信号( $V_{op}$ )および負の差動出力信号( $V_{on}$ )が低減することができない同50

じ (V<sub>ref</sub>) ベデスター上の差動出力信号 (V<sub>op</sub>, V<sub>on</sub>) の 2 つの半体を置くことにより、黙視的に判定することができ、次に、正の差動出力信号 (V<sub>op</sub>) および負の差動出力信号 (V<sub>on</sub>) の 2 つの半体を直接比較する。

#### 【0035】

再度図 5 を参照すると、基準電圧 (V<sub>ref</sub>) 上の共通の軸に沿って第 1 の差動入力電圧 (V<sub>p</sub>) および第 2 の差動入力電圧 (V<sub>n</sub>) を位置決めすることにより、第 1 の差動入力電圧 (V<sub>p</sub>) および第 2 の差動入力電圧 (V<sub>n</sub>) の論理しきい値を暗黙のうちに入手するため、第 1 の位置決め回路 300 および第 2 の位置決め回路 320 を使用することができる。第 1 の位置決め回路 300 は、第 1 の差動入力信号 (V<sub>p</sub>) および基準電圧 V<sub>ref</sub> に応じて第 1 の出力電圧 (V<sub>op</sub>) を発生し、第 2 の位置決め回路 320 は、第 2 の差動入力信号 (V<sub>n</sub>) および基準電圧 (V<sub>ref</sub>) に応じて第 2 の出力電圧 (V<sub>on</sub>) を発生する。第 1 の出力電圧 (V<sub>op</sub>) の最小値および第 2 の出力電圧 (V<sub>on</sub>) の最小値は、基準電圧 (V<sub>ref</sub>) 上の共通の軸に沿って位置する。第 1 の位置決め回路 300 および第 2 の位置決め回路 320 は、1 対の逆ピーク検出器を使用して実施することができる。10

#### 【0036】

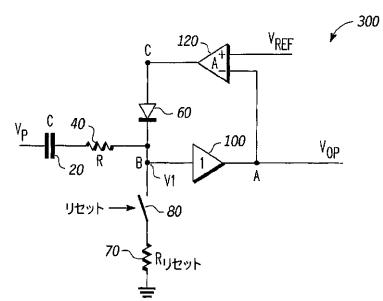

図 8 は、例示的実施形態による正の逆ピーク検出器 300 の回路図である。正の逆ピーク検出器 300 は、コンデンサ 20 と、抵抗 40 と、ダイオード 60 と、抵抗 70 と、スイッチ 80 と、バッファ 100 と、アンプ 120 を備える。負の逆ピーク検出器 320 は、そのアノードおよびカソードが逆になるようにダイオード 60 を単に反転させるだけで実施することができることを理解されたい。20

#### 【0037】

抵抗 40 は、コンデンサ 20 とノード B との間に結合している。ダイオード 60 は、ノード B とノード C との間に結合することができる。リセット・スイッチ 80 は、ノード B とアースへの抵抗 70 との間に結合することができる。アンプ 120 は、ノード A とノード C のところのダイオード 60 との間に結合することができる。バッファ 100 は、ノード B とノード A との間に結合することができる。

#### 【0038】

ノード B のところの電圧 (V<sub>1</sub>) をほぼゼロにするために、正の差動入力信号 (V<sub>p</sub>) バーストが到着する前に、リセット・スイッチ 80 はオフになる。30

コンデンサ 20 は、第 1 の差動入力 (V<sub>p</sub>) を受信する。バッファ 100 が非常に高い入力インピーダンスを有し、ダイオード 60 がオフになっているので、コンデンサ 20 の両端の電圧を変えることはできない。何故なら、電流が流れていらない状態で、コンデンサ 20 の電荷を直ちに変えることはできないし、ダイオード 60 がオフになっていると電流は流れることができないからである。正の差動入力信号 (V<sub>p</sub>) に応じて、ノード B のところの電圧 (V<sub>1</sub>) は、正の差動入力信号 (V<sub>p</sub>) を追隨する。それ故、正の差動入力信号 (V<sub>p</sub>) は、ノード B のところの電圧 (V<sub>1</sub>) が最終的には正の差動入力信号 (V<sub>p</sub>) と等しくなるようにノード B に完全に移行する。第 1 の差動入力信号 (V<sub>p</sub>) に何が起きたにしても、ダイオード 60 は、正の出力電圧 (V<sub>op</sub>) が基準電圧 (V<sub>ref</sub>) より下がるたびに、導通を開始する。正の差動入力電圧 (V<sub>p</sub>) が最小値に等しくなると、ダイオード 60 がオンになり、ノード B のところの電圧 (V<sub>1</sub>) が基準電圧 (V<sub>ref</sub>) に維持または保持されるように、コンデンサ 20 を駆動する。40

#### 【0039】

アンプ 120 は、基準電圧 (V<sub>ref</sub>) およびバッファ 100 が発生した正の出力電圧 (V<sub>op</sub>) を受信し、ダイオード 60 を駆動する信号を発生する。

第 1 の差動入力信号 (V<sub>p</sub>) が低減し始めると、正の出力電圧 (V<sub>op</sub>) と等しいノード B のところの電圧 (V<sub>1</sub>) が基準電圧 (V<sub>ref</sub>) より低くなる。それ故、アンプ 120 の出力が増大し始める。何故なら、ダイオード 60 がオンになると、正の出力電圧 (V<sub>op</sub>) が低減し始めるからである。ダイオード 60 がオンになると、ダイオード 60 がノード B のところの電圧 (V<sub>1</sub>) を強制的に基準電圧 (V<sub>ref</sub>) にしているコンデンサ 20

0を駆動する。正の差動入力電圧( $V_{p}$ )が前の最小値より低くなった時だけ、正の差動入力信号( $V_{p}$ )が回路に影響を与える。それ故、正の逆ピーク検出器回路300は、ノードBのところの電圧( $V_1$ )、それ故、ノードBのところの電圧( $V_1$ )に等しい正の出力電圧( $V_{op}$ )が、基準電圧( $V_{ref}$ )より低くなるのを効果的に防止する。

【0040】

バッファ100は、正の出力電圧( $V_{op}$ )の最小値が基準電圧( $V_{ref}$ )より大きくなるように正の出力電圧( $V_{op}$ )を発生する。正の出力電圧( $V_{op}$ )が基準電圧( $V_{ref}$ )より大きくなるのは、コンデンサ20が、正の出力電圧( $V_{op}$ )が基準電圧( $V_{ref}$ )より低くなることができない値に充電されるからである。要するに、正の出力電圧( $V_{op}$ )は、正の出力電圧( $V_{op}$ )がそれより低減することができない基準電圧( $V_{ref}$ )ペデスタル上に位置する。 10

【0041】

コンデンサ20が第2の差動入力( $V_n$ )を受信し、アンプ12がバッファ100から負の出力電圧( $V_{on}$ )を受信し、負の出力電圧( $V_{on}$ )の最小値が基準電圧( $V_{ref}$ )より大きくなるように、バッファ100が負の出力電圧( $V_{on}$ )を発生するように構成されている点を除けば、逆ピーク検出器回路320の構造は、正のピーク検出器300の構造と同一である。

【0042】

一実施態様は、例えば、基準値を有する基準信号入力と、ノードのところで抵抗と結合し、差動入力信号を受信するように構成されたコンデンサと、ノードに結合しているダイオードと、ノードとアースとの間に結合しているスイッチと、ノードと第2のノードとの間に結合しているバッファと、第2のノードとダイオードとの間に結合しているアンプとを含むことができる逆ピーク検出器回路を提供する。バッファは、出力信号を発生するように構成されている。アンプは、基準信号および出力信号を受信するように構成されている。この場合、出力信号の最小値は基準値以上である。出力信号は、基準信号の値より大きい値にシフトした差動入力信号のレプリカである。 20

【0043】

一実施態様は、第1の出力信号および第2の出力信号を発生するように構成された回路を含む。この回路は、例えば、基準値を有する基準信号入力と、第1の差動入力信号および基準信号に応じて、第1の出力信号を発生するように構成された第1の位置決め回路と、第2の差動入力信号および基準信号に応じて、第2の出力信号を発生するように構成された第2の位置決め回路とを含むことができる。第1の出力信号の最小値および第2の出力信号の最小値は、基準値以上である。 30

【0044】

また、この回路は、入力信号を受信するように構成され、第1の入力信号および第2の入力信号を発生するように構成された差動コンバータと、第1の入力信号および第2の入力信号を受信するように構成され、第1の差動入力信号および第2の差動入力信号を発生するように構成されたアンプと、入力信号が論理1を含むか否かを判定するために、第1の出力信号と第2の出力信号を比較するように構成された比較器とを含むことができる。一実施態様によれば、比較器が第1の出力信号が第2の出力信号より大きいと判定した場合には、入力信号は論理1を含み、この場合、比較器が第1の出力信号が第2の出力信号より小さいと判定した場合には、入力信号は論理0を含む。 40

【0045】

一実施態様によれば、第1の位置決め回路は、第1の逆ピーク検出器を備える。第1の逆ピーク検出器は、例えば、第1のノードのところで第1の抵抗と結合し、第1の差動入力信号を受信する第1のコンデンサと、第1のノードと結合している第1のダイオードと、第1のノードとアースとの間に結合している第1のスイッチと、第2のノードと第1のダイオードとの間に結合し、基準信号および第1の出力信号を受信するように構成された第1のアンプと、第1のノードと第2のノードとの間に結合し、第1の出力信号を発生するように構成された第1のバッファとを備える。第1の出力信号の最小値は、基準値より 50

上に位置する。

【0046】

一実施態様によれば、第1のダイオードは、第1の差動入力信号が最小値に等しくなった場合に、第1のノードのところの電圧が基準値に維持されるようにコンデンサを駆動する。

【0047】

一実施態様によれば、第1の出力信号の最小値が基準値以下にならないように、第1の出力信号の最小値は基準値より大きい。一実施態様によれば、第1の差動入力信号が最小値を有している場合には、第1の出力信号の最小値は、ほぼ基準値に等しい。

【0048】

一実施態様によれば、第1の出力信号は、基準値より大きい値にシフトした第1の差動入力信号のレプリカである。

一実施態様によれば、第2の位置決め回路は、第2の逆ピーク検出器を備える。第2の逆ピーク検出器は、例えば、第3のノードのところで第2の抵抗と結合し、第2の差動入力信号を受信する第2のコンデンサと、第3のノードと結合している第2のダイオードと、第3のノードとアースとの間に結合している第2のスイッチと、第4のノードと第2のダイオードとの間に結合し、基準信号および第2の出力信号を受信するように構成された第2のアンプと、第3のノードと第4のノードとの間に結合し、第2の出力信号を発生するように構成された第2のバッファとを備える。第2の出力信号の最小値は、基準値より上に位置する。

【0049】

一実施態様によれば、第2のダイオードは、第2の差動入力信号が最小値と等しい場合には、第3のノードのところの電圧が基準値に維持されるように、コンデンサを駆動する。一実施態様によれば、第2の出力信号の最小値が、基準値より低くならないように、第2の出力信号の最小値は基準値より大きい。

【0050】

一実施態様によれば、第2の差動入力信号が最小値を有している場合には、第2の出力信号の最小値は基準値にほぼ等しい。

一実施態様によれば、第2の出力信号は、基準値より大きい値にシフトした第2の差動入力信号のレプリカである。

【0051】

一実施態様によれば、第1の出力信号および第2の出力信号が相互にオフセットしないように、第1の出力信号および第2の出力信号は、(×軸上の)共通の基準を共有する。

一実施態様によれば、基準値以上の値のところの共通の軸に沿って第1の差動入力信号および第2の差動入力信号を位置決めすることにより、第1の差動入力信号および第2の差動入力信号の論理しきい値を暗黙のうちに入手するために、第1の位置決め回路および第2の位置決め回路が使用される。

【0052】

上記詳細な説明の中で、少なくとも1つの例示的実施形態を説明してきたが、非常に多くの変形例が存在することを理解されたい。また、1つまたは複数の例示的実施形態は、例示としてのものに過ぎず、如何なる意味でも本発明の範囲、用途または構成を制限するものでないことを理解されたい。それどころか、上記詳細な説明は、当業者に1つまたは複数の例示的実施形態を実施するために便利なロード・マップを提供する。添付の特許請求の範囲およびその合法的な等価物に記載する本発明の範囲から逸脱することなしに、素子の機能および配置を種々に変更することができるることを理解されたい。

【図面の簡単な説明】

【0053】

【図1】従来の光受信機モジュールのブロック図。

【図2】図1の光受信機モジュールで使用する論理しきい値取得回路(LTAC)の回路図。

10

20

30

40

50

- 【図3】図2のLTACで使用する従来の山ピーク検出器の回路図。

- 【図4】例示的実施形態による光受信機モジュールのブロック図。

- 【図5】本発明の例示的実施形態によるLTACの回路図。

- 【図6】差動信号V<sub>p</sub>およびV<sub>n</sub>を示す波形図。

- 【図7】基準電圧(V<sub>ref</sub>)ペデスタル上に位置する差動出力信号V<sub>op</sub>およびV<sub>on</sub>を示す波形図。

- 【図8】例示的実施形態による逆ピーク検出器の回路図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

FIG. 7

---

フロントページの続き

(72)発明者 ジェームズ、フレデリック エイチ .

アメリカ合衆国 85048 アリゾナ州 フェニックス イー. サウスフォーク ドライブ 9

59

審査官 工藤 一光

(56)参考文献 米国特許第05021747(US, A)

特開平07-244091(JP, A)

特開2000-269896(JP, A)

米国特許出願公開第2003/0099307(US, A1)

(58)調査した分野(Int.Cl. , DB名)

H04B10/00-10/28

H04J14/00-14/08

H04L25/00-25/66

H03G3/20-3/34