(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5445895号

(P5445895)

(45) 発行日 平成26年3月19日(2014.3.19)

(24) 登録日 平成26年1月10日(2014.1.10)

|                |           |

|----------------|-----------|

| (51) Int.Cl.   | F 1       |

| HO 1 L 21/336  | (2006.01) |

| HO 1 L 29/78   | (2006.01) |

| HO 1 L 21/8238 | (2006.01) |

| HO 1 L 27/092  | (2006.01) |

| HO 1 L 21/265  | (2006.01) |

| HO 1 L 29/78   | 29/78     |

| HO 1 L 27/092  | 27/08     |

| HO 1 L 21/265  | 21/265    |

| HO 1 L 29/58   | 29/58     |

|                | 3 O 1 S   |

|                | 3 2 1 E   |

|                | H         |

|                | G         |

請求項の数 8 (全 14 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2008-166113 (P2008-166113) |

| (22) 出願日     | 平成20年6月25日 (2008.6.25)       |

| (65) 公開番号    | 特開2009-16824 (P2009-16824A)  |

| (43) 公開日     | 平成21年1月22日 (2009.1.22)       |

| 審査請求日        | 平成23年6月20日 (2011.6.20)       |

| (31) 優先権主張番号 | 10-2007-0064941              |

| (32) 優先日     | 平成19年6月29日 (2007.6.29)       |

| (33) 優先権主張国  | 韓国 (KR)                      |

前置審査

|           |                                                                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 129<br>129, Samsung-ro, Yeon<br>g t o n g - g u, Suwon-si, G<br>yeonggi-do, Republic<br>of Korea |

| (74) 代理人  | 100089037<br>弁理士 渡邊 隆                                                                                                                                                          |

| (74) 代理人  | 100110364<br>弁理士 実広 信哉                                                                                                                                                         |

最終頁に続く

(54) 【発明の名称】半導体素子の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に導電膜パターンを形成する段階と、

前記基板表面及び前記導電膜パターンの表面上に酸化膜を形成する段階と、

不純物の拡散に要求されるエネルギーが上昇するように前記酸化膜を表面処理して拡散

防止膜を形成する段階と、

前記拡散防止膜を通じて前記導電膜パターン両側の基板及び前記導電膜パターンに前記

不純物を注入して、前記基板に不純物領域を形成する段階と、を含み、

前記酸化膜を形成する段階は、O<sub>3</sub> - TEOS 膜を形成する熱的化学気相蒸着工程を含

み、

前記拡散防止膜を形成する段階は、水素、ヘリウム、及びオゾンからなる群より選択さ

れた少なくとも一種のガスから生成されたプラズマを用いるプラズマ処理を含むことを特

徴とする半導体素子の製造方法。

## 【請求項 2】

前記酸化膜は 20 ~ 100 の厚さに形成され、前記不純物は P 型不純物を含むことを

特徴とする請求項 1 に記載の半導体素子の製造方法。

## 【請求項 3】

前記プラズマ処理は、1 ~ 5 分間 300 ~ 700 の温度にて行われることを特徴とす

る請求項 1 に記載の半導体素子の製造方法。

## 【請求項 4】

10

20

前記拡散防止膜上にスペーサ膜を形成する段階と、

前記拡散防止膜をエッチング防止膜に用いて前記スペーサ膜を異方性エッチングすることによって前記導電膜パターンの側壁に位置する拡散防止膜上にスペーサを形成する段階と、を更に含むことを特徴とする請求項1から3の何れか一項に記載の半導体素子の製造方法。

**【請求項5】**

前記スペーサ膜を形成する段階と前記拡散防止膜を形成する段階とは、インサイチュで行われることを特徴とする請求項4に記載の半導体素子の製造方法。

**【請求項6】**

前記酸化膜を形成する段階の前に、前記基板にP型不純物を注入して低濃度不純物領域を形成する段階を更に含むことを特徴とする請求項4に記載の半導体素子の製造方法。 10

**【請求項7】**

前記導電膜パターンの両側に前記低濃度不純物領域の位置を調節するためのオフセットスペーサを形成する段階を更に含むことを特徴とする請求項6に記載の半導体素子の製造方法。

**【請求項8】**

前記不純物領域の形成された基板を熱処理して前記不純物領域にドープされている不純物を活性化させる段階を更に含むことを特徴とする請求項1に記載の半導体素子の製造方法。

**【発明の詳細な説明】**

20

**【技術分野】**

**【0001】**

本発明は半導体素子の製造方法に係り、より詳細には高性能を有するPMOSトランジスタ及びこれを含むCMOSトランジスタの製造方法に関する。

**【背景技術】**

**【0002】**

半導体メモリ素子を構成する基本的な単位素子として電界効果MOSトランジスタ(MOSFET、以下、トランジスタ)がある。前記トランジスタは低電圧で高速動作ができ、小型化、集積化する方向に発展しつつある。

**【0003】**

30

具体的に、前記メモリ素子が高集積化することに応じて素子を形成するためのアクティブ領域の大きさが大幅に減少しつつある。そのため、前記アクティブ領域に形成されるトランジスタのゲートの長さが減少しつつある。このように、トランジスタのゲートの長さが短くなると、チャンネル領域における電界や電位に及ぶソース及びドレインの影響が著しくなり、ゲート電圧によってスイッチング動作を行いにくくなるというショートチャンネル効果が発生する。即ち、前記ゲート長さが短くなることによってチャンネル領域がゲート電圧のみならず、ソース及びドレイン領域の空乏層電荷や電界及び電位分布の影響を大きく受けるようになり、正常的なスイッチング動作が難しくなる。

**【0004】**

また、ドレイン電圧が増加するほどドレインの空乏層が比例して増加してドレイン空乏層がソースに近接する。ゲートの長さが短くなるとドレイン空乏層とソース空乏層とが完全に連結されてしまう。この状態では、ドレイン電界がソース側にまで影響を及ぼしソース近傍の拡散電位を低下させるため、チャンネルが形成されていなくてもソースとドレインとの間に電流が流れようになる。これがパンチスルーやいう現象である。パンチスルーが発生し出すと、飽和領域でもドレイン電流が飽和されず急激に増加するようになる。 40

**【0005】**

このようなショートチャンネル効果はソース/ドレイン領域の接合深さが深いほど、チャンネルドーピングが低いほど深刻になるので、これを減少させるためにソース/ドレインの接合深さを薄く形成しなければならない。このように、ソース/ドレインの接合深さが薄くなることによってソース/ドレイン抵抗が非常に増加する。

50

## 【0006】

また、ショートチャンネル効果を防止するための一方法としてソース／ドレインを L D D (Lightly Doped Drain) 構造に形成することが挙げられる。半導体素子の高集積化が加速化して多用な半導体製造技術が開発されることに応じて、最近では L D D 領域を形成するために前記ゲート電極の両側壁にゲートスペーサを形成している。

## 【0007】

一方、ソース／ドレインの形成は、ソース／ドレイン領域を露出した後、ソース／ドレインイオンをそれぞれドープした後、ドーパントを活性化するために高温の急速熱処理 (Rapid Thermal Process; RTP) を進行する。前記急速熱処理の工程時に前記ソース／ドレイン領域の不純物が基板の下、上、及び側方に拡散する。よって、前記ソース／ドレイン領域間の間隔が更に減少するだけでなく、前記ソース／ドレイン領域の不純物の濃度が更に低くなり前記ソース／ドレイン領域の抵抗が増加する。特に、P型不純物であるホウ素の場合、拡散エネルギーが低くて前記基板の上部に拡散しやすいので、トランジスタの動作特性に悪影響を及ぼす。

10

## 【0008】

一方、前記トランジスタが使用者が希望するレベルのしきい電圧を有するためには、特定の仕事関数を有する物質でゲート電極を形成しなければならない。しかし、ポリシリコンの場合には前記ポリシリコンにドープされる不純物の導電型によって仕事関数を適切に調節することができるので、ゲート電極として広く用いられる。具体的に、PMOSトランジスタの場合、P型不純物であるホウ素をドープしたポリシリコンをゲート電極に用い、N型トランジスタの場合、N型不純物であるリンまたは砒素をドープしたポリシリコンをゲート電極に用いることができる。このように、前記不純物がドープされたポリシリコンをゲート電極に用いる場合には、前記ゲート電極内に不純物が拡散しないようにして前記不純物の濃度が減少しないことが望ましい。前記PMOSトランジスタのゲート電極内の不純物の濃度が減少すると、ゲート空乏現像が著しくなって電気的にゲート酸化膜の厚さが増加するので、動作特性が悪くなる。

20

## 【0009】

しかし、前記ソース／ドレイン領域及びゲート電極内における不純物は工程の進行期間に繰り返して行われる熱工程によって継続的に拡散するので、前記不純物の拡散を減少させることができない。更に、PMOSトランジスタに用いられるホウ素の場合にはN型不純物であるリンや砒素に比べて相対的に更に速く拡散が行われるので、前記不純物の拡散によってPMOSトランジスタの特性が劣化することを防止することが容易でない。

30

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0010】

よって、本発明の目的は、高性能を有するPMOSトランジスタを含む半導体素子の製造方法を提供することにある。

本発明の他の目的は、高性能を有するCMOSトランジスタを含む半導体素子の製造方法を提供することにある。

40

## 【課題を解決するための手段】

## 【0011】

前記の目的を達成するための本発明の一実施例による半導体素子の製造方法によると、基板上に導電膜パターンを形成する。前記基板表面及び前記導電膜パターンの表面上に酸化膜を形成する。不純物の拡散に要求されるエネルギーが上昇するように前記酸化膜を表面処理して拡散防止膜を形成する。その後、前記拡散防止膜を通じて前記導電膜パターン両側の基板及び前記導電膜パターンに前記不純物を注入して、前記基板に不純物領域を形成する。

## 【0012】

前記拡散防止膜を形成する段階は、水素、ヘリウム、窒素、アルゴン、酸素、及びオゾン

50

ンからなる群より選択された少なくとも一種のガスから生成されたプラズマを用いるプラズマ処理を含むことができる。

#### 【0013】

前記拡散防止膜を形成する段階は、紫外線照射を含むことができる。

前記他の目的を達成するための本発明の一実施例による半導体素子の製造方法によると、基板の第1領域及び第2領域にそれぞれ第1ゲート構造物及び第2ゲート構造物を形成する。前記基板、第1ゲート構造物及び第2ゲート構造物の表面上にシリコン酸化膜を形成する。P型不純物の拡散に要求されるエネルギーが上昇するように前記シリコン酸化膜を表面処理して拡散防止膜を形成する。前記第1及び第2ゲート構造物の両側壁に形成された前記拡散防止膜上にスペーサを形成する。前記第1領域に位置するスペーサ両側の基板にN型不純物を注入して、前記基板の第1領域に第1不純物領域を形成する。前記第2領域に位置するスペーサ両側の基板にP型不純物を注入して、前記基板の第2領域に第2不純物領域を形成する段階と、を含む。10

#### 【発明の効果】

#### 【0014】

前記本発明の方法によって半導体素子を形成する場合、前記拡散防止膜によってゲート及びソース／ドレインに含まれているP型不純物の拡散を減少させることができる。よって、前記ゲート及びソース／ドレインに含まれているP型不純物が拡散して、P型不純物の濃度が減少することを防止することができる。このように、前記P型不純物の濃度を維持させることによって、前記ゲートの空乏現像及びソース／ドレインの抵抗増加の問題を減少させることができる。20

#### 【発明を実施するための最良の形態】

#### 【0015】

以下、添付図面を参照して本発明の望ましい実施例を詳細に説明する。

#### 【実施例1】

#### 【0016】

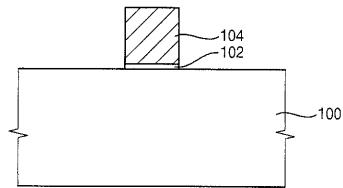

図1乃至図7は、本発明の実施例1によるPMOSトランジスタの製造方法を示す断面図である。

#### 【0017】

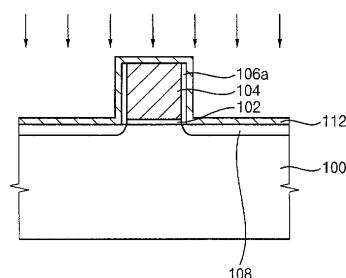

図1を参照すると、前記基板100にゲート酸化膜（図示せず）及びゲート導電膜（図示せず）を順次形成する。前記ゲート酸化膜は、前記基板を熱酸化して形成させたシリコン酸化物で形成することができる。前記ゲート導電膜はP型不純物のドープされたポリシリコン膜で形成することができる。即ち、前記ゲート酸化膜上にポリシリコン膜を形成し、前記ポリシリコン膜に前記P型不純物を注入することで前記ゲート導電膜を形成することができる。ここで、前記P型不純物はホウ素を含む。30

#### 【0018】

本実施例では、前記ゲート導電膜はP型不純物のドープされたポリシリコン膜のみで形成される。しかし、他の実施例では、前記ゲート導電膜は、前記ポリシリコン膜および金属膜の積層された構造を有することもできる。

#### 【0019】

その後、フォトリソグラフィ工程を通じて前記ゲート導電膜及びゲート酸化膜をパターニングすることでゲート酸化膜パターン102及びゲートパターン104を形成する。前記ゲートパターン104を形成するためのマスクとしてフォトレジストパターンを用いることもでき、ハードマスクパターンを用いることもできる。前記パターニング工程を行った後、エッチングマスクに用いられたパターンを除去する。40

#### 【0020】

前記ゲート酸化膜パターン102及びゲートパターン104の形成された基板を熱酸化させることで、前記基板100及びゲートパターン104の表面上に再酸化膜（図示せず）を形成する。前記再酸化膜を形成することで前記ゲートパターン及び基板の表面がキュアリングされる。前記再酸化膜は、5～30の薄い厚さに形成されることが望ましい。50

しかし、前記再酸化膜を形成する工程は工程の単純化のために省略してもよい。

**【0021】**

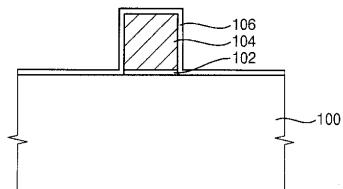

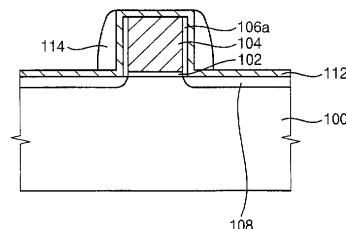

図2を参照すると、前記再酸化膜の形成されている基板100及びゲートパターン104の表面上に第1絶縁膜106を形成する。前記第1絶縁膜106は、後続工程を通じてオフセットスペーサとして提供される。即ち、前記第1絶縁膜の厚さを調節することでソース／ドレインの低濃度のドープ領域の縁部の位置と高濃度のドープ領域の形成位置を調節することができる。前記第1絶縁膜106は、シリコン酸化物を化学気相蒸着法によって10～30の厚さに蒸着して形成することができる。

**【0022】**

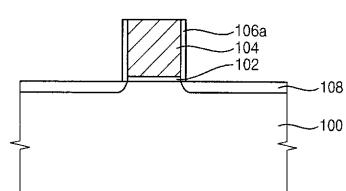

図3を参照すると、前記第1絶縁膜106を異方性エッチングして前記ゲートパターン104の側壁にオフセットスペーサ106aを形成する。前記第1絶縁膜106を異方性エッチングする工程において、前記基板100上に形成されている再酸化膜がともに除去され前記基板100が露出する。

**【0023】**

その後、前記オフセットスペーサ106aの両側に露出した基板に低濃度の不純物をドープして低濃度ソース／ドレイン領域108を形成する。前記オフセットスペーサ106aが具備されることによって前記低濃度ソース／ドレイン領域108が前記ゲートパターン104の下に拡散しすぎることを防止することができる。

**【0024】**

本実施例では、前記再酸化膜及びオフセットスペーサ106aをそれぞれ形成すると説明したが、前記再酸化膜およびオフセットスペーサ106aのうちのいずれかのみ形成することもできる。また、前記再酸化膜及びオフセットスペーサ106aのいずれも形成しないことも可能である。

**【0025】**

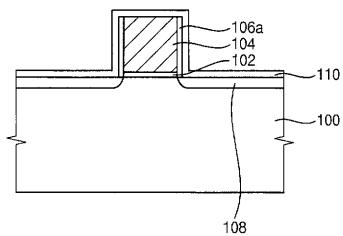

図4を参照すると、前記基板100、オフセットスペーサ106a及び前記ゲートパターン104の表面に沿ってシリコン酸化膜110を形成する。前記シリコン酸化膜110は後続工程でエッチング阻止膜、応力防止のためのパッド膜及び不純物拡散防止膜として用いられる。

**【0026】**

前記シリコン酸化膜は、熱的化学気相蒸着工程によって形成されるO<sub>3</sub>-TEOS膜から形成することができる。これとは違って、プラズマ強化化学気相蒸着工程または高密度化学気相蒸着工程を通じてシリコン酸化膜を形成することもできる。

**【0027】**

前記シリコン酸化膜110を形成する温度が350以下であると化学気相蒸着工程を通じて膜を形成しにくく、前記シリコン酸化膜110を形成する温度が500以上であると、基板100及びゲートパターン104が再結晶化するおそれがあるので望ましくない。そのため、前記シリコン酸化膜110を350～500の温度で形成することが望ましい。

**【0028】**

なお、前記シリコン酸化膜110の厚さが20より薄いと、後続の窒化膜をエッティングするとき、エッチング阻止膜として用いることが容易でなく不純物の拡散防止の効果が減少する。反面、シリコン酸化膜110の厚さが100より厚いと前記シリコン酸化膜110を通じて基板の下に不純物を注入することが容易でない。よって、前記シリコン酸化膜110を、20～100の厚さに形成することが望ましい。

**【0029】**

図5を参照すると、前記シリコン酸化膜110に不活性ガス、酸素、及びオゾンガスのうちの少なくとも一つのガスを用いるプラズマ処理を行って前記シリコン酸化膜110を拡散防止膜112に変換させる。前記プラズマ処理に用いることができる前記不活性ガスの例としては、窒素、ヘリウム、水素、アルゴンなどを挙げることができる。

**【0030】**

10

20

30

40

50

上述のようにシリコン酸化膜110にプラズマ処理を行うと、前記シリコン酸化膜110の膜質が密になり、膜内に含まれている-OH基または-H基が減少する。そのため、前記拡散防止膜112が形成されている場合は、処理前のシリコン酸化膜110が具備されたときに比べてP型不純物が拡散するのに必要なエネルギーが高くなる。よって、前記P型不純物が前記拡散防止膜を通過して基板の上部に拡散することを最小化することができる。

#### 【0031】

具体的には、前記シリコン酸化膜110が熱的化学気相蒸着法によって形成されたO<sub>3</sub>-TEOS膜である場合、前記O<sub>3</sub>-TEOS膜内には-OHが複数含まれている。しかし、前記O<sub>3</sub>-TEOS膜内に不活性ガスを用いるプラズマ処理を行うと、前記O<sub>3</sub>-TEOS膜内の-OH基の含量が非常に減少するようになる。これとは違って、前記O<sub>3</sub>-TEOS膜に酸素またはオゾンを用いるプラズマ処理を行うと、前記O<sub>3</sub>-TEOS膜に酸素結合が強化することによって膜質が密になる。10

#### 【0032】

前記プラズマ処理温度が300以下であると、プラズマ処理による膜の改質効果が減少する。また、前記プラズマ処理温度が700以上であると、非晶質構造を有する基板100及びゲートパターン104が再結晶化するおそれがある。そのため、前記プラズマ処理は300~700の温度で行われることが望ましい。

#### 【0033】

前記プラズマ処理時間が1分以下であると、プラズマ処理による膜の改質効果が減少し、前記プラズマ処理時間が5分以上であると、前記プラズマによって過度に膜が損傷するおそれがあり、工程に所要される時間も過度に長くなつて望ましくない。そのため、前記プラズマ処理時間は1~5分であることが望ましく、前記プラズマ処理温度及び酸化膜の厚さなどによって増減することができる。20

#### 【0034】

図6を参照すると、前記拡散防止膜112上にスペーサ用絶縁膜(図示せず)を形成する。前記スペーサ用絶縁膜は、前記ゲートパターン104の両側の基板100にドープされる高濃度ソース/ドレイン領域の位置を調節する。前記スペーサ用絶縁膜は、前記拡散防止膜112とエッチング選択比を有するシリコン窒化物で構成することができる。

#### 【0035】

具体的には、前記スペーサ用絶縁膜を、プラズマ強化化学気相蒸着(PED-CVD)工程、低圧化学気相蒸着(LPCVD)工程を通じてシリコン窒化膜を蒸着して形成することもできる。前記シリコン窒化膜を蒸着するときの温度が300以下であると膜を蒸着しにくく、前記シリコン窒化膜の蒸着温度が500以上であると、蒸着中に下部膜に非晶質化した領域の再結晶化が発生して応力が加えられるおそれがあるので望ましくない。そのため、前記シリコン窒化膜の蒸着工程は300~500の温度で行われることが望ましい。

#### 【0036】

前記スペーサ用絶縁膜を蒸着する工程でプラズマを用いる場合には、上述の前記シリコン酸化膜110をプラズマ処理する工程と前記スペーサ用絶縁膜の形成工程をInSi<sub>2</sub>(インサイチュ)で行うことができる。例えば、スペーサ用絶縁膜をPE-CVD工程で形成する場合には、上述のプラズマ処理工程を前記PED-CVD工程を行うためのチャンバ内でインサイチュで進行することができる。40

#### 【0037】

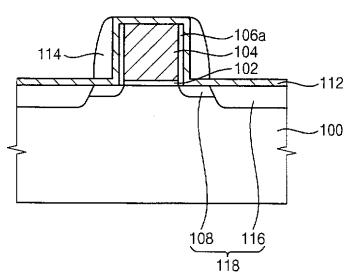

その後、前記スペーサ用絶縁膜を異方性エッチングして前記ゲートパターン104の側壁にスペーサ114を形成する。前記エッチング工程で、前記基板100及びゲートパターン104の上部面に形成された拡散防止膜112をエッチング阻止膜に用いて、前記基板100の表面及びゲートパターン104の上部面に形成された拡散防止膜112が露出するようにする。

#### 【0038】

図7を参照すると、前記拡散防止膜112を通過して前記ゲートパターン104の両側の基板にP型不純物を注入することで高濃度のソース／ドレイン領域116を形成する。前記不純物注入の工程時に前記ゲートパターン104内にもP型不純物が注入される。

#### 【0039】

これによって、低濃度のソース／ドレイン領域108及び高濃度のソース／ドレイン領域116を含むLDD構造のソース／ドレイン領域118が形成される。

#### 【0040】

その後、前記基板を急速熱処理して前記ソース／ドレイン領域118に形成された不純物を活性化する。前記基板の熱処理は900～1200の温度で窒素、アルゴン、及び水素から選択された少なくとも一つのガス雰囲気下で行うことができる。

10

#### 【0041】

図示していないが、前記ソース／ドレイン118領域及びゲートパターン104の上部面に金属シリサイドパターンを形成することができる。

#### 【0042】

このために、前記基板100表面及びゲートパターン104の上部面に形成されている拡散防止膜112を除去する。その後、前記基板100、スペーサ114、ゲートパターン104の表面に沿って金属膜（図示せず）を形成する。前記金属膜として用いることができる金属物質としてコバルトを挙げることができる。前記金属膜を熱処理して前記金属膜とシリコンとを互いに反応させる。これによって、前記ソース／ドレイン領域とゲートパターンの上部の表面に金属シリサイドパターンが形成される。その後、反応しない金属膜を除去する。

20

#### 【0043】

このように、金属シリサイドパターンを形成することで前記ゲートパターンおよびソース／ドレインの抵抗を減少させることができる。しかし、工程を単純化するために前記金属シリサイドパターンを形成する工程を省略することもできる。

#### 【0044】

PMOSトランジスタを形成すると、前記基板を急速熱処理するとき、前記ソース／ドレイン領域及びゲートパターン内に含まれているP型不純物が拡散するおそれがある。しかし、前記ソース／ドレイン領域に該当する基板の表面上に形成されている拡散防止膜によって、前記ソース／ドレイン領域に含まれているP型不純物が基板の上部に拡散することを減少させることができる。また、前記ゲートパターンの側壁及び上部面にも拡散防止膜を具備することで、前記ゲートパターン内に含まれているP型不純物が前記ゲートパターンの上部及び側方を通じて拡散することを減少させることができる。

30

#### 【0045】

その結果、前記ゲートパターン内に含まれた不純物が拡散によって損失することが抑制されるので、前記ゲートパターン内の不純物濃度を十分に高く維持することができる。そのため、前記ゲートパターンに電圧を印加したとき、前記ゲート酸化膜パターンと隣接している前記ゲートパターンの底面におけるゲート空乏が減少し、これによって電気的にゲート酸化膜パターンの厚さが厚くなることを抑制することができる。また、チャンネル領域の電荷密度が増加し、電流の密度もまた増加するようになる。

40

#### 【0046】

前記ソース／ドレイン領域においても基板の上部にP型不純物が拡散することが抑制されるので、不純物の損失を減少させることができる。よって、前記ソース／ドレイン領域内の不純物の濃度を十分に高く維持することができるので、前記ソース／ドレイン領域の抵抗が減少する効果がある。

#### 【実施例2】

#### 【0047】

図8は、本発明の実施例2によるPMOSトランジスタの製造方法を示す断面図である。

#### 【0048】

50

以下で説明する実施例 2 による P M O S トランジスタの製造方法は、シリコン酸化膜を拡散防止膜に転換する方法を除いては実施例 1 と同一である。そのため、重複部分は簡略に説明するかまたは省略する。

#### 【 0 0 4 9 】

まず、実施例 1 の図 1 乃至図 4 を参照して説明したような同一の工程を行う。これによつて、基板 1 0 0 にゲート酸化膜パターン 1 0 2 、ゲートパターン 1 0 4 、再酸化膜、オフセットスペーサ 1 0 6 a 及びシリコン酸化膜を形成する。

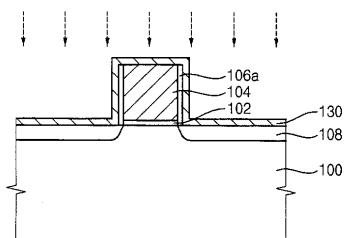

#### 【 0 0 5 0 】

図 7 を参照すると、前記シリコン酸化膜に紫外線光 ( U V l i g h t ) を照射することで前記シリコン酸化膜を改質して拡散防止膜 1 3 0 を形成する。前記紫外線は、1 0 0 ~ 5 0 0 n m の範囲内の波長を有することが望ましく、約 2 0 0 ~ 3 0 0 n m の範囲内の波長を有することが更に望ましい。

10

#### 【 0 0 5 1 】

具体的には、前記シリコン酸化膜に 1 ~ 5 分間紫外線光を照射し、ここで、前記基板 1 0 0 を 4 0 0 ~ 6 0 0 の温度になるようにすることができる。前記紫外線の処理時間が 1 分以下であると膜の改質効果が減少し、5 分以上であると前記紫外線処理によって膜が損傷するおそれがあり、工程に所要される時間も長くなつて望ましくない。

#### 【 0 0 5 2 】

また、前記シリコン酸化膜に紫外線光を照射する工程は、不活性ガスの雰囲気で行うことができる。前記不活性ガスの例としては、窒素、ヘリウム、水素、アルゴンなどが挙げられる。

20

#### 【 0 0 5 3 】

上述のように、膜表面に紫外線光を照射する場合、前記紫外線光のエネルギーが前記膜内の分子結合より高くて前記分子結合を切断するようになる。よつて、前記紫外線処理を行うと、前記シリコン酸化膜 2 2 0 内に含まれている相対的に結合エネルギーの弱い S i - O H 結合、 S i - H 結合、 N - H 結合が減少する。よつて、前記紫外線処理によって形成された拡散防止膜 2 4 0 は、 - O H 基または - H 基がほぼなく、多くは S i - O 結合を有するようになる。

#### 【 0 0 5 4 】

よつて、前記拡散防止膜 1 3 0 の形成されている場合は、処理前のシリコン酸化膜が具備されたときに比べて P 型不純物が拡散するのに必要なエネルギーが高くなる。よつて、前記ドープされた P 型不純物が基板の上部に拡散することを抑制することができる。

30

#### 【 0 0 5 5 】

図示していないが、前記実施例 1 でのように前記シリコン酸化膜をプラズマ処理する工程を更に行なうこともできる。即ち、前記シリコン酸化膜に前記紫外線光を照射する前または前記紫外線光を照射した後に、前記不活性ガス、酸素、及びオゾンガスのうちの少なくとも一つのガスを用いるプラズマ処理を行うこともできる。

#### 【 0 0 5 6 】

その後、図 6 及び図 7 を参照して説明したような同一の工程を行うことによって P M O S トランジスタを形成する。前記工程を通じて形成される P M O S トランジスタも前記ゲートパターン及びソース / ドレイン領域において不純物の拡散が抑制されて良好な動作特性を有する。

40

#### 【 実施例 3 】

#### 【 0 0 5 7 】

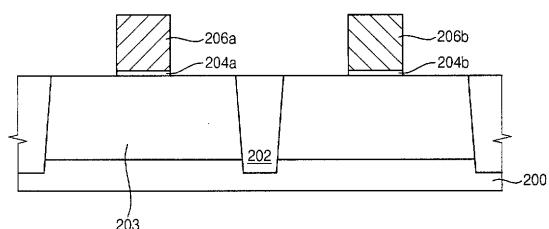

図 9 乃至図 1 2 は、本発明の実施例 3 による C M O S トランジスタの製造方法を示す断面図である。

#### 【 0 0 5 8 】

以下で説明する実施例 3 による C M O S トランジスタの製造方法は、 N M O S トランジスタを形成するための工程が追加されることを除いては実施例 1 と同一である。よつて、重複部分は簡略に説明するかまたは省略する。

50

**【0059】**

図9を参照すると、まず、半導体物質からなる基板200を用意する。前記基板200は、N MOSトランジスタの形成される第1領域とPMOSトランジスタの形成される第2領域とに区分する。

**【0060】**

前記基板200にシャロウトレニチ素子分離工程を行って阻止分離膜パターン202を形成することによって、アクティブ領域及びフィールド領域を画定する。

**【0061】**

その後、N MOS及びPMOSトランジスタそれぞれのチャンネル領域203を形成するため、前記第1領域の基板にP型不純物をドープし、前記第2領域の基板にN型不純物をドープする。

10

**【0062】**

具体的には、前記第1領域の基板200を選択的に露出する第1イオン注入マスクパターン(図示せず)を形成した後、前記第1領域の基板にP型不純物をイオン注入する。その後、前記第1イオン注入マスクパターンを除去する。また、前記第2領域の基板200を選択的に露出する第2イオン注入マスクパターン(図示せず)を形成した後、前記第2領域の基板にN型不純物をイオン注入する。その後、前記第2イオン注入マスクパターンを除去する。前記第1及び第2イオン注入マスクパターンは、フォトレジストを用いて形成することができる。前記P型不純物の例としては、ホウ素、BF<sub>2</sub>などを挙げることができ、前記N型不純物の例としては、砒素、リンなどを挙げることができる。

20

**【0063】**

その後、前記基板200上にゲート酸化膜(図示せず)を形成する。前記ゲート酸化膜は、前記基板200の表面を熱酸化して形成させることができる。

**【0064】**

前記ゲート酸化膜上にゲートで用いるためのポリシリコン膜(図示せず)を形成する。その後、前記第1領域に形成されている前記ポリシリコン膜にはN型不純物を注入し、前記第2領域に形成されている前記ポリシリコン膜にはP型不純物を注入する。このために、前記不純物注入の工程の前に、前記ポリシリコン膜上にイオン注入マスクとしてフォトレジストパターンを形成する工程が行われる。ここで、前記N型不純物はリンまたは砒素を含み、前記P型不純物はホウ素を含む。しかし、現段階において前記ポリシリコン膜に不純物を注入する工程を行わなくても良い。

30

**【0065】**

その後、フォトリソグラフィ工程を通じて前記ポリシリコン膜及びゲート酸化膜をパターニングすることで前記第1領域には第1ゲート酸化膜パターン204a及び第1ゲートパターン206aを形成し、前記第2領域に第2ゲート酸化膜パターン204b及び第2ゲートパターン206bを形成する。

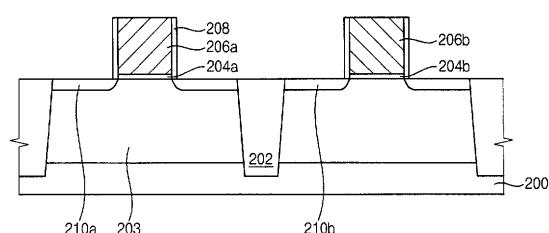

**【0066】**

図10を参照すると、前記図2及び図3を参照して説明したような同一の工程を行うことで、前記第1及び第2ゲートパターン(206a、206b)に再酸化膜(図示せず)及びオフセットスペーサ208を形成する。

40

**【0067】**

その後、前記第1領域の基板を選択的に露出する第3イオン注入マスクパターン(図示せず)を形成した後、前記第1領域の基板にN型不純物をイオン注入する。前記工程を通じて、N MOSトランジスタの低濃度のソース/ドレイン領域210aが形成される。また、前記N型不純物をイオン注入する工程を行うと、前記第1ゲートパターン206a内にもN型不純物がドープされる。その後、前記第3イオン注入マスクパターンを除去する。

**【0068】**

また、前記第2領域の基板200を選択的に露出する第4イオン注入マスクパターン(図示せず)を形成した後、前記第2領域の基板にP型不純物をイオン注入する。前記工程

を通じて、PMOSトランジスタの低濃度ソース／ドレイン領域210bが形成される。また、前記P型不純物をイオン注入工程を行うと、前記第2ゲートパターン206bにもP型不純物がドープされる。その後、前記第4イオン注入マスクパターンを除去する。

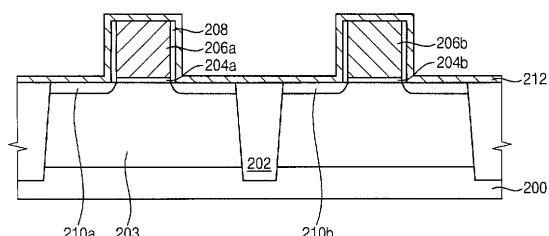

#### 【0069】

図11を参照すると、前記第1及び第2ゲートパターン(206a、206b)、オフセットスペーサ208及び基板200の表面にシリコン酸化膜を形成する。

その後、前記図5を参照して説明したように、前記シリコン酸化膜に不活性ガス、酸素、及びオゾンガスのうち、少なくとも一種のガスを用いるプラズマ処理を行って前記シリコン酸化膜を拡散防止膜212に変換する。前記プラズマ処理の用いることができる前記不活性ガスの例としては、窒素、ヘリウム、水素、アルゴンなどを挙げることができる。

10

#### 【0070】

これとは違って、前記図8を参照して説明したように、前記シリコン酸化膜に紫外線光(UV light)を照射することで、前記シリコン酸化膜を改質して拡散防止膜212を形成することもできる。

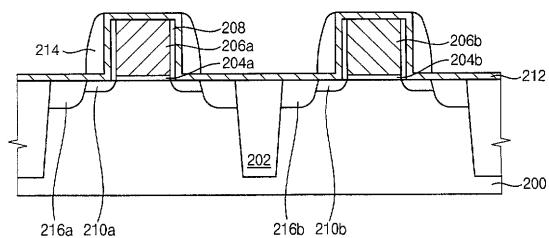

#### 【0071】

図12を参照すると、前記拡散防止膜212上にスペーサ用絶縁膜を形成し、これを異方性エッティングすることでスペーサ214を形成する。

#### 【0072】

その後、前記第1領域の基板を選択的に露出する第5イオン注入マスクパターン(図示せず)を形成した後、前記第1領域の基板にN型不純物をイオン注入する。前記工程を通じて、NMOSトランジスタの高濃度のソース／ドレイン領域216aが形成される。また、前記N型不純物をイオン注入する工程を行うと、前記第1ゲートパターン206aにもN型不純物がドープされる。その後、前記第5イオン注入マスクパターンを除去する。

20

#### 【0073】

また、前記第2領域の基板200を選択的に露出する第6イオン注入マスクパターン(図示せず)を形成した後、前記第2領域の基板にP型不純物をイオン注入する。前記工程を通じて、PMOSトランジスタの高濃度のソース／ドレイン領域216bが形成される。また、前記P型不純物をイオン注入する工程を行うと、前記第2ゲートパターンにもP型不純物がドープされる。その後、前記第6イオン注入マスクパターンを除去する。

#### 【0074】

30

その後、急速熱処理工程を通じて、前記ソース／ドレイン領域に含まれた不純物を活性化させる。

#### 【0075】

前記工程を行うと、LDD構造のソース／ドレイン領域を有するCMOSトランジスタが形成される。前記方法によると、ソース／ドレイン領域及びゲートパターンに含まれている不純物が拡散されることが抑制されるので、高性能を有するCMOSトランジスタを形成することができる。

#### 【0076】

上述したように本発明によると、簡単な工程を通じて不純物の拡散を抑制して高性能を有するトランジスタを形成することができる。具体的には、本発明の方法によって製造されたトランジスタはゲート空乏現像が減少し、ソース／ドレインの抵抗が減少することによって動作電流を増加させて動作速度が速くなる。なお、トランジスタの飽和電流が増加する。これによって、前記トランジスタの動作特性が良好になりかつ信頼性が高くなる。

40

#### 【0077】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有する者であれば本発明の思想と精神から逸脱することなく、本発明を修正または変更できる。

#### 【図面の簡単な説明】

#### 【0078】

【図1】本発明の実施例1によるPMOSトランジスタの製造方法を示す断面図である。

50

【図2】本発明の実施例1によるPMOSトランジスタの製造方法を示す断面図である。

【図3】本発明の実施例1によるPMOSトランジスタの製造方法を示す断面図である。

【図4】本発明の実施例1によるPMOSトランジスタの製造方法を示す断面図である。

【図5】本発明の実施例1によるPMOSトランジスタの製造方法を示す断面図である。

【図6】本発明の実施例1によるPMOSトランジスタの製造方法を示す断面図である。

【図7】本発明の実施例1によるPMOSトランジスタの製造方法を示す断面図である。

【図8】本発明の実施例2による半導体素子の製造方法を説明するための断面図である。

【図9】本発明の実施例3によるCMOSトランジスタの製造方法を示す断面図である。

【図10】本発明の実施例3によるCMOSトランジスタの製造方法を示す断面図である

。

10

【図11】本発明の実施例3によるCMOSトランジスタの製造方法を示す断面図である

。

【図12】本発明の実施例3によるCMOSトランジスタの製造方法を示す断面図である

。

【符号の説明】

【0079】

100、200 基板

102 ゲート酸化膜パターン

104 ゲートパターン

106 第1絶縁膜

20

106a、208 オフセットスペーサ

108、210a、210b 低濃度のソース／ドレイン領域

110、220 シリコン酸化膜

112、130 拡散防止膜

114、214 スペーサ

116、216a、216b 高濃度のソース／ドレイン領域

118 LDD構造のソース／ドレイン領域

203 チャンネル領域

204a 第1ゲート酸化膜パターン

206a 第1ゲートパターン

30

206b 第2ゲートパターン

212 拡散防止膜

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/423 (2006.01)

H 01 L 29/49 (2006.01)

(72)発明者 申 東石

大韓民国京畿道龍仁市器興区書川洞（番地なし） 現代アパート現代ホームタウン108棟601号

(72)発明者 李 周遠

大韓民国京畿道水原市靈通区靈通洞（番地なし） 黃骨マウル豊林アパート234棟1501号

(72)発明者 金 泰均

大韓民国ソウル特別市江西区加陽1洞（番地なし） ドングシンデアパート103棟1302号

審査官 小山 満

(56)参考文献 特開平03-129774 (JP, A)

特開2001-085680 (JP, A)

特開2006-049779 (JP, A)

特開平08-125197 (JP, A)

特開2006-019366 (JP, A)

特開昭63-217655 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 336

H 01 L 21 / 265

H 01 L 21 / 8238

H 01 L 27 / 092

H 01 L 29 / 423

H 01 L 29 / 49

H 01 L 29 / 78