(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5937225号

(P5937225)

(45) 発行日 平成28年6月22日(2016.6.22)

(24) 登録日 平成28年5月20日(2016.5.20)

|                        |                 |

|------------------------|-----------------|

| (51) Int.Cl.           | F 1             |

| HO1L 27/00 (2006.01)   | HO1L 27/00 301W |

| HO1L 21/8238 (2006.01) | HO1L 27/08 321G |

| HO1L 27/092 (2006.01)  | HO1L 27/08 331E |

| HO1L 27/08 (2006.01)   | HO1L 27/06 102A |

| HO1L 21/8234 (2006.01) | HO1L 27/04 A    |

請求項の数 23 (全 13 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-542512 (P2014-542512)  |

| (86) (22) 出願日 | 平成24年11月16日 (2012.11.16)      |

| (65) 公表番号     | 特表2015-503228 (P2015-503228A) |

| (43) 公表日      | 平成27年1月29日 (2015.1.29)        |

| (86) 國際出願番号   | PCT/US2012/065644             |

| (87) 國際公開番号   | W02013/075007                 |

| (87) 國際公開日    | 平成25年5月23日 (2013.5.23)        |

| 審査請求日         | 平成26年6月9日 (2014.6.9)          |

| (31) 優先権主張番号  | 61/560,471                    |

| (32) 優先日      | 平成23年11月16日 (2011.11.16)      |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 13/356,717                    |

| (32) 優先日      | 平成24年1月24日 (2012.1.24)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                        |

|-----------|----------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サン・ディエゴ モアハウス・ドラ<br>イブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                 |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                 |

| (72) 発明者  | 100163522<br>チエンジエ・ズオ<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ドラ<br>イブ・5775         |

最終頁に続く

(54) 【発明の名称】絶縁層および第2の層を有する積層されたチップセットおよびそれを形成する方法

## (57) 【特許請求の範囲】

## 【請求項1】

ガラス、石英またはサファイアのシートと、

第1の絶縁層及び前記第1の絶縁層の第1の側上に形成された少なくとも1つの第1の回路層を備えた第1のシリコンオンインシュレータ(SOI)であって、前記少なくとも1つの第1の回路層が前記第1の絶縁層と前記シートとの間に配置されるように、前記シートに接合される第1のSOIと、

前記シートと前記第1のSOIとの間に配される接着剤層であって、前記第1のSOIの第1の回路層が前記接着剤層を介して前記シートに接合されるようになる接着剤層と、

第2の絶縁層及び少なくとも1つの第2の回路層を備えた第2のSOIであって、前記少なくとも1つの第2の回路層が、前記第2の絶縁層の第1の側上に形成される少なくとも1つの第1の受動回路要素と、前記第2の絶縁層の第2の側上に形成される少なくとも1つの第2の受動回路要素と、を備え、前記少なくとも1つの第1の受動回路要素が、前記第2の絶縁層と前記第1の絶縁層との間に配置され、前記第1の絶縁層の第2の側が、前記少なくとも1つの第2の回路層に結合されるように、前記第1の絶縁層に接続される、第2のSOIと、

を備えるチップセットであって、

前記少なくとも1つの第1の回路層が、複数のCMOSトランジスタを備え、

前記少なくとも1つの第2の回路層が、受動構成部品およびMEMS素子のうちの少なくとも1つを備えるまたは支持する、チップセット。

10

20

**【請求項 2】**

前記少なくとも 1 つの第 1 の回路層が、複数の C M O S トランジスタを備える、請求項 1 に記載のチップセット。

**【請求項 3】**

前記少なくとも 1 つの第 2 の受動回路要素が、少なくとも 1 つの微小電気機械システム ( M E M S ) 素子を備える、請求項 1 に記載のチップセット。

**【請求項 4】**

前記少なくとも 1 つの第 2 の受動回路要素が、少なくとも 1 つのセンサを備える、請求項 1 に記載のチップセット。

**【請求項 5】**

前記第 1 の S O I と前記第 2 の S O I との間に配される第 2 の接着剤層をさらに備え、前記第 1 の絶縁層の第 2 の側が、前記第 2 の接着剤層を介して前記第 2 の回路層に直接接合されるようになる、請求項 1 に記載のチップセット。

**【請求項 6】**

少なくとも 1 つの半導体ダイに集積される、請求項 1 に記載のチップセット。

**【請求項 7】**

セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末 ( P D A ) 、固定ロケーションデータユニット、およびコンピュータからなる群から選択されたデバイスに統合される、請求項 1 に記載のチップセット。

**【請求項 8】**

前記少なくとも 1 つの第 1 の回路層が、複数の相補型 M O S ( C M O S ) トランジスタを備え、

前記少なくとも 1 つの第 2 の回路層が、少なくとも 1 つの受動構成部品または M E M S 素子を備え又は支持し、

前記第 1 の S O I が、前記シートに直接接合され、

前記第 2 の S O I が、前記第 1 の絶縁層に直接接合される、請求項 1 に記載のチップセット。

**【請求項 9】**

第 3 の絶縁層の第 1 の側上に少なくとも 1 つの第 3 の回路層を有する第 3 の S O I を含み、前記第 3 の S O I が、前記少なくとも 1 つの第 3 の回路層が前記第 1 の絶縁層と前記第 2 の絶縁層との間に配置されるように、前記第 1 の S O I に接続される、請求項 1 に記載のチップセット。

**【請求項 10】**

前記少なくとも 1 つの第 3 の回路層が、C M O S トランジスタを備える、請求項 9 に記載のチップセット。

**【請求項 11】**

前記第 2 の S O I が、前記少なくとも 1 つの第 2 の回路層が前記第 2 の絶縁層と前記第 3 の絶縁層との間に配置されるように、前記第 3 の S O I に直接接合される、請求項 9 に記載のチップセット。

**【請求項 12】**

前記少なくとも 1 つの第 1 の回路層が、デジタル回路を含み、前記少なくとも 1 つの第 3 の回路層が、アナログ回路を含む、請求項 9 に記載のチップセット。

**【請求項 13】**

前記少なくとも 1 つの第 1 の回路層が、デジタル回路を含み、前記少なくとも 1 つの第 2 の回路層が、受動デバイスまたは M E M S 素子を含みまたは支持し、前記少なくとも 1 つの第 3 の回路層が、アナログまたは無線周波数 R F 回路を含む、請求項 9 に記載のチップセット。

**【請求項 14】**

前記第 1 の絶縁層の表面積が、前記第 2 の絶縁層の表面積に等しく、前記第 2 の絶縁層

10

20

30

40

50

の前記表面積が、前記第3の絶縁層の表面積に等しい、請求項9に記載のチップセット。

**【請求項15】**

ウエハを支持するための絶縁体シート手段であって、ガラスのシート、石英のシートまたはサファイアのシートを備える絶縁体シート手段と、

第1の絶縁層手段及び前記第1の絶縁層手段の第1の側上に形成される、信号を処理するための少なくとも1つの第1の回路手段を備えた第1のシリコンオンインシュレータ(SOI)であって、前記少なくとも1つの第1の回路手段が前記第1の絶縁層手段と前記絶縁体シート手段との間に配置されるように、前記絶縁体シート手段に接合される、第1のSOIと、

前記絶縁体シート手段と前記第1のSOIとの間に配される接着剤層であって、前記第1のSOIの第1の回路手段が前記接着剤層を介して前記絶縁体シート手段に接合されるようになる接着剤層と、

第2の絶縁層手段及び信号を処理するための少なくとも1つの第2の回路手段を備えた第2のSOIであって、前記少なくとも1つの第2の回路手段が、前記第2の絶縁層手段の第1の側上に形成される少なくとも1つの第1の受動回路要素と、前記第2の絶縁層手段の第2の側上に形成される少なくとも1つの第2の受動回路要素と、を備え、前記少なくとも1つの第1の受動回路要素が、前記第2の絶縁層手段と前記第1の絶縁層手段との間に配置され、前記第1の絶縁層手段の第2の側が、前記少なくとも1つの第2の回路手段に結合されるように、前記第1の絶縁層手段に接続される、第2のSOIと、

を備えるチップセットであって、

前記少なくとも1つの第1の回路手段が、複数のCMOSトランジスタを備え、

前記少なくとも1つの第2の回路手段が、受動回路素子と、微小電気機械システム(MEMS)素子と、センサのうちの少なくとも1つを備えるまたは支持する、チップセット。

**【請求項16】**

前記少なくとも1つの第2の受動回路要素が、少なくとも1つの微小電気機械システム(MEMS)素子又は少なくとも1つのセンサを備える、請求項15に記載のチップセット。

**【請求項17】**

少なくとも1つの半導体ダイに集積された、請求項15に記載のチップセット。

**【請求項18】**

セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定ロケーションデータユニット、およびコンピュータからなる群から選択されたデバイスに統合される、請求項15に記載のチップセット。

**【請求項19】**

前記少なくとも1つの第1の回路手段が、複数のCMOSトランジスタを備え、

前記少なくとも1つの第2の回路手段が、少なくとも1つの受動構成部品または少なくとも1つのMEMS素子を備えまたは支持し、

前記第1のSOIが、前記絶縁体シート手段に直接接合され、

前記第2のSOIが、前記第1の絶縁層手段に直接接合される、

請求項15に記載のチップセット。

**【請求項20】**

前記少なくとも1つの第1の回路層が、複数のCMOSトランジスタを備え、

前記少なくとも1つの第2の回路層が、少なくとも1つの高Q受動部品を備える、請求項1に記載のチップセット。

**【請求項21】**

前記少なくとも1つの第1の回路層が、複数のCMOSトランジスタを備え、

前記少なくとも1つの第2の回路層が、少なくとも1つの半導体バラクタを備える、請求項1に記載のチップセット。

10

20

30

40

50

**【請求項 2 2】**

前記少なくとも 1 つの第 1 の回路層が、複数の C M O S トランジスタを備え、

前記少なくとも 1 つの第 2 の回路層が、少なくとも 1 つの M E M S ベースの同調可能なコンデンサを備える、請求項 1 に記載のチップセット。

**【請求項 2 3】**

前記少なくとも 1 つの第 1 の回路層が、複数の C M O S トランジスタを備え、

前記少なくとも 1 つの第 2 の回路層が、少なくとも 1 つの高性能無線周波数 ( R F ) スイッチを備える、請求項 1 に記載のチップセット。

**【発明の詳細な説明】****【技術分野】**

10

**【0 0 0 1】**

米国特許法 ( 3 5 U . S . C . ) 第 1 1 9 条に基づく優先権主張

本特許出願は、本明細書の譲受人に譲渡された 2 0 1 1 年 1 1 月 1 6 日出願の「 S T A C K E D C M O S C H I P S E T H A V I N G A N I N S U L A T I N G L A Y E R A N D A S E C O N D A R Y L A Y E R A N D M E T H O D O F F O R M I N G S A M E 」という名称の米国仮特許出願第 6 1 / 5 6 0 , 4 7 1 号の優先権を主張する。その仮特許出願を参照により明白に本明細書に組み込む。

**【0 0 0 2】**

本特許出願は、絶縁体に接合された相補型金属酸化膜半導体 ( C M O S ) 層および C M O S 層上に積層された第 2 の層を有するチップセット、およびそれを形成する方法を対象とし、より詳細には、絶縁体に接合された C M O S 層と、受動素子、無線周波数 ( R F ) 回路または微小電気機械システム ( M E M S ) 素子を有する第 2 の層とを含むチップセット、およびそれを形成する方法を対象とする。

20

**【背景技術】****【0 0 0 3】**

セルラーワイヤレスシステムが 2 G から 4 G に進化するのに伴い、多数の帯域をサポートする無線周波数 ( R F ) チップセットに対する需要が増大している。チップセットにこれらの追加帯域を扱う能力を提供することは、さらに送受信機、フィルタ、電力増幅器、受動構成部品およびスイッチをチップセットのフロントエンドに追加することが必要になり得るし、これにより、チップセットの費用および複雑さが増す。携帯電話の R F システムは、しばしば単一の相補型金属酸化膜半導体 ( C M O S ) チップである送受信機と、 R F フロントエンド ( 様々なオンボード構成部品、すなわち、フィルタ、送受共用器、 R F スイッチ、電力増幅器、および受動構成部品を含む ) との主に 2 つの部分からなる。 C M O S 送受信機は、様々な帯域またはモードによって共有されるように設計することができるが ( 一般に多重モード / 多帯域送受信機の設計と呼ばれる ) 、フロントエンド部分、特にフィルタおよび送受共用機は、単に異なる周波数範囲で動作するので、異なる帯域間で共有することができない。より多くの帯域 / モードをサポートするこれらの追加の要素の存在は、性能を高め、サイズと費用を低減しようとするとき、フロントエンドを制限要因にすることがある。

30

**【0 0 0 4】**

従来の多帯域および / または多モード R F チップセットのフロントエンドは、 R F スイッチ、電力増幅器、音響フィルタおよび受動部品、たとえば、誘導子およびコンデンサ、などのデバイスを含むことができる。 C M O S チップ素子は、一般に、連続的に縮小でき、それによって、新技術の進歩とともに費用が低減し、サイズが小さくなるが、フロントエンドは必ずしもそれほど容易に縮小するとは限らない。この状況への 1 つの取組みは、複数のチップ、たとえば、ガリウムヒ素アンテナスイッチ、ガリウムヒ素電力増幅器、 C M O S 制御器、表面弹性波 ( S A W ) フィルタ、集積受動デバイスなどを、単一の積層またはセラミック基板に集積することであった。この取組みは、フロントエンド集積のための「システムインパッケージ」と呼ばれることがある。同調可能なフロントエンドを導入することによってシステムアーキテクチャレベルで多帯域の複雑さの問題に対処すること

40

50

への関心もある。低損失多帯域同調可能システムを実現するためには、半導体バラクタやMEMSベース同調可能コンデンサなどの高Q同調可能受動部品、および高性能RFスイッチを単一の構成に実装する方法を見出さねばならない。フロントエンドの集積は、多帯域および/または多モードRF送受信機チップセットのサイズおよび費用全体を低減するのも有用であり得る。したがって、空間および費用効果のある方法でCMOS構成部品と他のフロントエンド構成部品とを集積したチップセットを提供することが望ましいであろう。

**【発明の概要】**

**【課題を解決するための手段】**

**【0005】**

10

例示的な一実施形態は、ガラス、石英またはサファイアのシートと、第1の基板層の第1の側上に少なくとも1つの第1の回路層を有する第1のウエハとを備えたチップセットを含む。第1のウエハは、少なくとも1つの第1の回路層が第1の基板層とシートとの間に配置されるように、シートに接続される。チップセットは、第2の基板層の第1の側上に少なくとも1つの第2の回路層を有する第2のウエハも含み、第2のウエハは、少なくとも1つの第2の回路層が第2の基板層と第1の基板層との間に配置されるように、第1の基板層に接続される。

**【0006】**

20

別の一実施形態は、第1のシリコン基板と、第1のシリコン基板上の少なくとも1つの第1の回路層とを備える第1のウエハを提供するステップと、少なくとも1つの第1の回路層をガラス、石英またはサファイアのシートに接続し、次いで第1のシリコン基板の一部分を除去するステップとを含む、チップセットを形成する方法である。この方法はまた、第2のシリコン基板と、第2の基板上の少なくとも1つの第2の回路層とを備える第2のウエハを提供するステップと、少なくとも1つの第2の回路層を第1のシリコン基板に接続し、次いで第2のシリコン基板の一部分を除去するステップとを含む。

**【0007】**

30

他の一実施形態は、ウエハを支持するための絶縁体シート手段を有するチップセットと、第1の基板層の第1の側上で信号を処理するための少なくとも1つの第1の回路手段を備えた第1のウエハとを含み、第1のウエハが、少なくとも1つの第1の回路手段が第1の基板層と絶縁体シート手段との間に配置されるように、絶縁体シート手段に接続される。チップセットは、第2の基板層の第1の側上で信号を処理するための少なくとも1つの第2の回路手段を備えた第2のウエハをさらに含み、第2のウエハは、少なくとも1つの第2の回路層が第2の基板層と第1の基板層との間に配置されるように、第1の基板層に接続される。

**【0008】**

40

別の一実施形態は、第1のシリコン基板と、第1のシリコン基板上の少なくとも1つの第1の回路層とを備えた第1のウエハを提供するためのステップと、少なくとも1つの第1の回路層をガラス、石英またはサファイアのシートに接続するためのステップと、次いで第1のシリコン基板の一部分を除去するためのステップと、第2のシリコン基板と、第2の基板上の少なくとも1つの第2の回路層とを備えた第2のウエハを提供するためのステップと、少なくとも1つの第2の回路層を第1のシリコン基板に接続するためのステップと、次いで、第2のシリコン基板の一部分を除去するためのステップと、を含むチップセットを形成する方法である。

**【0009】**

添付の図面は、本発明の諸実施形態の説明を助けるために提示され、諸実施形態の図示のためだけに提供されるものであって、それらの限定のために提供されるものではない。

**【図面の簡単な説明】**

**【0010】**

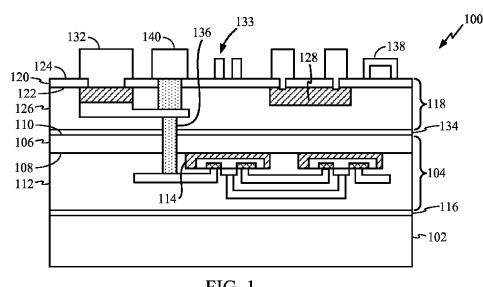

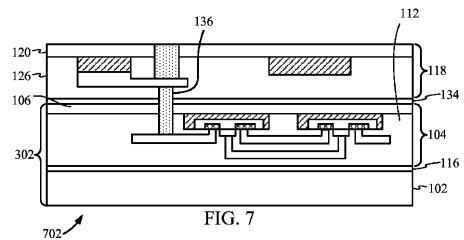

**【図1】**一実施形態による、チップセットの概略的側面図である。

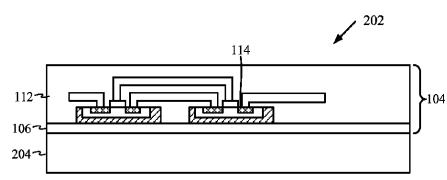

**【図2】**図1のチップセットを製造するための一方法の組立て段階を示す、図1のチップ

50

セットのストック材料および構成部品の概略的側面図である。

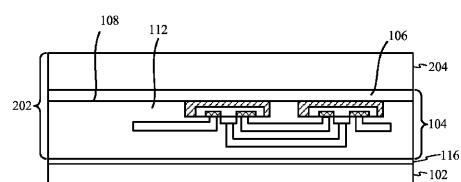

【図3】図1のチップセットを製造するための一方法の組立て段階を示す、図1のチップセットのストック材料および構成部品の概略的側面図である。

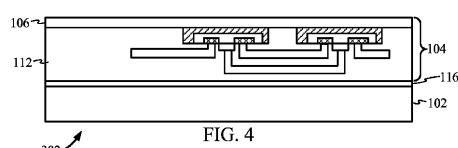

【図4】図1のチップセットを製造するための一方法の組立て段階を示す、図1のチップセットのストック材料および構成部品の概略的側面図である。

【図5】図1のチップセットを製造するための一方法の組立て段階を示す、図1のチップセットのストック材料および構成部品の概略的側面図である。

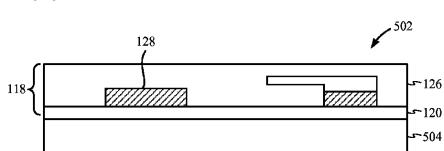

【図6】図1のチップセットを製造するための一方法の組立て段階を示す、図1のチップセットのストック材料および構成部品の概略的側面図である。

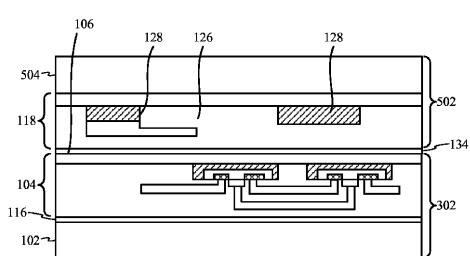

【図7】図1のチップセットを製造するための一方法の組立て段階を示す、図1のチップセットのストック材料および構成部品の概略的側面図である。 10

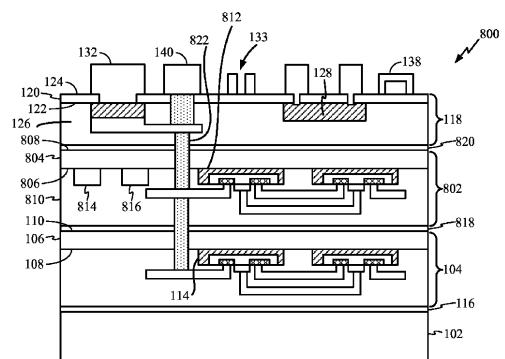

【図8】別の一実施形態による、チップセットの概略的側面図である。

【発明を実施するための形態】

【0011】

本発明の諸態様は、本発明の特定の諸実施形態に向けた次の説明および関連する図面に開示される。代替の諸実施形態は、本発明の範囲を逸脱することなく考案することができる。さらに、本発明の周知の要素については、本発明の関連する詳細を曖昧にしないようするために、詳細に説明しない、または省略するものとする。

【0012】

「例示的な」という用語は、本明細書では「例、事例、または図示として働く」を意味するのに用いる。「例示」として本明細書で説明するいかなる実施形態も、他の諸実施形態より好ましいまたは利点があるとして必ずしも解釈されない。同様に、「本発明の実施形態」という用語は、本発明の実施形態がすべて、論じた特徴、利点、または動作のモードを含む必要はない。 20

【0013】

本明細書で使用する用語は、特定の実施形態のみを説明する目的のものであって、本発明の実施形態を限定することを意図したものではない。本明細書で使用したとき、「1つの(a)」「1つの(an)」および「その(the)」という単数形は、文脈が明確に他の場合を示していない限り、複数形も含むことを意図している。「備える(comprises)」、「備えて(comprising)」「含む(includes)」および／または「含めて(including)」という用語は、本明細書で使用したとき、記述された特徴、整数、ステップ、動作、要素、および／または構成部品の存在を指定するが、1つまたは複数の他の特徴、整数、ステップ、動作、要素、構成部品、および／またはそれらの群の存在または追加を排除しないことがさらに理解される。 30

【0014】

さらに、多くの実施形態について、たとえば、計算デバイスの要素によって実施されるべき一連の動作の観点から説明される。本明細書で説明する様々な動作は、特定の回路(たとえば、特定用途向け集積回路(A S I C))によって、1つまたは複数のプロセッサによって実行されるプログラム命令によって、または両方の組合せによって実施できることが理解される。さらに、本明細書で説明するこれらの一連の動作は、どんな形でもコンピュータ可読記憶媒体内において、実行すると関連するプロセッサに本明細書で説明する機能性を実施する、対応する一組のコンピュータ命令をその中に格納させ、全体を実施するとみなすことができる。したがって、本発明の様々な態様は、いくつかの互いに異なる形で実施することができ、そのすべてが特許請求する主題の範囲内にあることが企図されている。さらに、本明細書で説明する実施形態のそれぞれに対して、対応するそのような任意の実施形態の形について、たとえば、説明した動作を実施する「ように論理的に構成された」として本明細書で説明することができる。 40

【0015】

図1は、一実施形態による、チップセット100を示す。チップセット100は、第1のシリコンオンインシュレータ(SOI)ウェハ104が接合されるガラス、石英または 50

サファイアなどの絶縁体から形成されたシート102を含む。第1のSOIウエハ104は、シート102に対向する第1の側108および第2の側110を有する第1の基板層または第1の絶縁層106を含み、第1のSOIウエハ104は、第1の回路層112も含み、第1の回路層112は、第1の絶縁層106の第1の側108上の複数のCMOSトランジスタ114および関連する配線を含む。これらのCMOSトランジスタ114および他の回路素子(図示せず)は、デジタル信号処理、アプリケーションまたはグラフィックプロセッサ用の回路、および/またはベースバンド信号を渡すための回路を備えることができる。第1のSOIウエハ104は、第1の接着剤層116または他の従来のウエハ接合技術を使用して、第1の回路層112が第1のSOIウエハ104の第1の絶縁層106の第1の側108とシート102の間に配置されるように、シート102に接合される。

#### 【0016】

第2のSOIウエハ118が、第1のSOIウエハ104に接続される。第2のSOIウエハ118は、第1の絶縁層106の第2の側110に対向する第1の側122と第2の側124とを有する第2の基板層または第2の絶縁層120を含む。第2のSOIウエハ118は、第2の回路層126も含み、第2の回路層126は、第2の回路層126内に一部または全体が配置された抵抗器128やコンデンサ132、第2の絶縁層120の第2の側124上に配置された誘導子133やMEMSデバイスまたはセンサ138などの受動要素または「受動部品」を含む。単一の抵抗器128、コンデンサ132、誘導子133、およびMEMSデバイス138は、図1に示される。ただし、第2のSOIウエハ118は、場合によって、これらの構成部品の種類の1つまたは2つを含む、および/またはこれらの個別の構成部品(CMOSトランジスタのような能動回路を含む)の複数のものを含むにすぎないことがある。第2のSOIウエハ118は、第2の接着剤層134を使用して、第2の回路層126が第2の絶縁層120の第1の側122と第1の絶縁層106の第2の側110との間に配置されるように、第1の絶縁層106の第2の側110に接合される。ビア136が、第2の回路層126の素子を第1の回路層112の素子に電気的に接続し、第2の回路層126内または第2の回路層126上および/または第1の回路層112内または第1の回路層112上の素子をチップセット100の外側のデバイスに電気的に接続するために、適切な金属接点140を第2の絶縁層120の第2の側124において接続することができる。

#### 【0017】

類似のチップセットを、サファイア、石英またはガラスなどの純絶縁体から形成されるシート102上の代わりに、高抵抗性シリコン(Si)基板上に埋め込み酸化物を用いて組み立てた場合(SOI CMOS技術における場合のように)、非線形寄生容量が、RF周波数においてSOI基板内の高抵抗性Siと埋め込みSiO<sub>2</sub>との間の界面に生じる。これらの寄生容量によって、RFスイッチおよび電力増幅器には、非線形性および電力処理の問題が生じる。本明細書で説明するように、シート102を使用すると、非線形寄生容量の問題が実質的になくなり、CMOSトランジスタ114や高Q受動部品を備えることができる受動部品などのCMOS素子を、同じチップセット100内に一緒に使用することができになり、SOIウエハ上よりもずっと良い性能が得られる。

#### 【0018】

チップセット100の様々な製造段階を図2~図7に示し、チップセット100内に存在し、図1で論じた素子は、図2~図7では同じ参照番号で識別される。図2は、上に第1の絶縁層106および第1の回路層112が形成された第1のシリコン基板または処理層204を含む第1のストックSOIウエハ202を示す。第1のストックSOIウエハ202は、従来のバルクシリコンCMOSウエハを備えて、費用を低減するのに役立つことができるが、この場合、第1の基板層106は、絶縁体を備えず、代わりに、第1の回路層112の素子のすぐ下に配置されるバルクシリコンの部分であろう。

#### 【0019】

図3は、第1の絶縁層106の第1の側108をシート102に対向させ、反転し、第

10

20

30

40

50

1 の接着剤層 116 によってシート 102 に接合された、第 1 のストック SOI ウエハ 202 を示し、図 4 は、たとえば、化学機械研磨 (CMP) または他の所望の量の第 1 のシリコン処理層 204 を選択的に除去する適切なプロセスにより、第 1 のシリコン処理層 204 の除去によって形成された第 1 の構成部品 302 を示す。図 5 は、上に第 2 の絶縁層 120 および第 2 の回路層 126 が形成された第 2 のシリコン基板または処理層 504 を備える、第 2 のストック SOI ウエハ 502 を示す。図 6 は、反転させ、第 1 の構成部品 302 に取り付け、第 2 のストック SOI ウエハ 502 の第 2 の回路層 126 を第 2 の接着剤層 134 によって第 1 の絶縁層 106 に接合した、第 2 のストック SOI ウエハ 502 を示す。図 7 は、第 2 のストック SOI ウエハ 502 と第 1 の構成部品 302 との組合せを備え、第 2 のストック SOI ウエハ 502 の第 2 のシリコン処理層 504 を CMP または他の適切なプロセスによって除去した、第 2 の構成部品 702 を示す。ビア 136 も、第 2 の構成部品 702 内に形成され、金属接点 140 および他のバックエンドオブザライン (BEOL) の構成部品 (受動部品、MEMS、センサおよびその他を含む) の追加により、図 1 のチップセット 100 がもたらされる。

10

#### 【0020】

図 8 は、第 1 の実施形態に共通の要素と同じ参照符号で識別される、別の一実施形態を示す。図 8 は、シート 102 と、第 1 の SOI ウエハ 104 と、第 2 の SOI ウエハ 118 を含み、第 1 の SOI ウエハ 104 および第 2 の SOI ウエハ 118 は、第 3 の SOI ウエハ 802 によって離隔されている、第 2 のチップセット 800 を示す。第 3 の SOI ウエハ 802 は、第 1 の側 806 および第 2 の側 808 を有する第 3 の基板層または絶縁層 804 と、第 3 の絶縁層 804 の第 1 の側 806 上に複数の回路素子を備える第 3 の回路層 810 とを備えており、回路素子はアナログ回路 814 および / または RF 構成部品 816 を含むことができる。第 3 の SOI ウエハ 802 は、第 3 の SOI ウエハ 802 の第 1 の側 806 が第 1 の SOI ウエハ 104 の第 2 の側 110 に対向するように、第 2 の接着剤層 818 により第 1 の SOI ウエハ 104 の第 2 の側 110 に取り付けられる。第 2 の SOI ウエハ 118 は、第 2 の SOI ウエハ 118 の第 1 の側が第 3 の SOI ウエハ 802 の第 2 の側 808 に対向するように、第 3 の接着剤層 820 によって第 3 の SOI ウエハ 802 の第 2 の側 808 に取り付けられる。第 1 の SOI ウエハ 104、第 2 の SOI ウエハ 118 および第 3 の SOI ウエハ 802 の 3つすべてが、実質的に同じ表面積を有する。ビア 822 が、第 1 の回路層 112、第 2 の回路層 126 および第 3 の回路層 810 の回路構成部品を接続し、金属接点 140 が、第 2 のチップセット 800 の外側の素子との接続部を提供する。この構成により、アナログ回路 814 および / または RF 構成部品 816 をデジタル回路素子 114 およびコンデンサ 132 などの受動部品と同じチップセット内に含めることができ、小型パッケージ内で多くの従来の機能を実施する垂直に集積されたチップセットが提供される。

20

30

#### 【0021】

シート 102 は、ガラス、サファイアまたは石英を備えるとして説明されているが、シート 102 にガラスを使用することは、状況によってとりわけ有益である。まず、ガラスは、一般にサファイアまたは石英より費用が安い。次に、ガラスは、サファイアより誘電率がずっと低く、それによって、基板からの寄生容量が著しく低減する。最後に、ガラスのウエハ / パネルのサイズは、サファイアおよび石英よりずっと大きくすることができ、これにより、より大規模な量産およびより低い単価が可能になる。

40

#### 【0022】

開示された本実施形態のチップセットは、1つまたは複数の半導体ダイに集積することができ、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娯楽ユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末 (PDA)、固定ロケーションデータユニット、およびコンピュータなどのデバイスに統合することができる。

#### 【0023】

本明細書で開示された実施形態に関連して説明した方法、シーケンス、および / またはアルゴリズムは、直接ハードウェアにおいて、プロセッサによって実行されるソフトウェ

50

アモジュールにおいて、またはこの2つの組合せにおいて実施することができる。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で周知の他の任意の形の記憶媒体に常駐することができる。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、および記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。あるいは、記憶媒体は、プロセッサと一緒にすることができる。

## 【0024】

前述の開示により、本発明の例示的な実施形態が示されているが、添付の特許請求の範囲に定義されるように、本発明の範囲を逸脱することなく、本明細書において様々な変更および修正を加えることができることに留意されたい。本明細書に説明する本発明の諸実施形態による方法の特許請求の範囲の諸機能、諸ステップ、および／または諸動作は、任意の特定の順序で実施する必要はない。さらに、本発明の諸要素は、単数で説明しました特許請求することができるが、単数への限定が明示的に記述されていない限り、複数が企図されている。

10

## 【符号の説明】

## 【0025】

|     |                          |    |

|-----|--------------------------|----|

| 100 | チップセット                   |    |

| 102 | シート                      |    |

| 104 | 第1のシリコンオンインシュレータ(SOI)ウエハ | 20 |

| 106 | 第1の基板層または第1の絶縁層          |    |

| 108 | 第1の側                     |    |

| 110 | 第2の側                     |    |

| 112 | 第1の回路層                   |    |

| 114 | C MOSトランジスタ(デジタル回路素子)    |    |

| 116 | 第1の接着剤層                  |    |

| 118 | 第2のSOIウエハ                |    |

| 120 | 第2の基板層または第2の絶縁層          |    |

| 122 | 第1の側                     |    |

| 124 | 第2の側                     | 30 |

| 126 | 第2の回路層                   |    |

| 128 | 抵抗器                      |    |

| 132 | コンデンサ                    |    |

| 133 | 誘導子                      |    |

| 134 | 第2の接着剤層                  |    |

| 136 | ビア                       |    |

| 138 | MEMSデバイス                 |    |

| 140 | 金属接点                     |    |

| 202 | 第1のストックSOIウエハ            |    |

| 204 | 第1のシリコン基板または処理層          | 40 |

| 302 | 第1の構成部品                  |    |

| 502 | 第2のストックSOIウエハ            |    |

| 504 | 第2のシリコン基板または処理層          |    |

| 702 | 第2の構成部品                  |    |

| 800 | 第2のチップセット                |    |

| 802 | 第3のSOIウエハ                |    |

| 804 | 第3の基板層または絶縁層             |    |

| 806 | 第1の側                     |    |

| 808 | 第2の側                     |    |

| 810 | 第3の回路層                   | 50 |

- 8 1 4 アナログ回路

8 1 6 R F 構成部品

8 1 8 第2の接着剤層

8 2 0 第3の接着剤層

8 2 2 ピア

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

【図8】

FIG. 8

## フロントページの続き

| (51)Int.Cl. |         |           | F I     |       |         |

|-------------|---------|-----------|---------|-------|---------|

| H 01 L      | 27/06   | (2006.01) | H 01 L  | 21/02 | B       |

| H 01 L      | 21/822  | (2006.01) | H 01 L  | 27/12 | C       |

| H 01 L      | 27/04   | (2006.01) | H 01 L  | 21/88 | J       |

| H 01 L      | 21/02   | (2006.01) | H 01 L  | 21/88 | T       |

| H 01 L      | 23/52   | (2006.01) | H 01 L  | 29/78 | 6 1 3 A |

| H 01 L      | 27/12   | (2006.01) | H 01 L  | 29/78 | 6 2 7 D |

| H 01 L      | 21/3205 | (2006.01) | H 01 L  | 29/78 | 6 2 6 C |

| H 01 L      | 21/768  | (2006.01) | B 8 1 B | 7/02  |         |

| H 01 L      | 23/522  | (2006.01) | B 8 1 C | 3/00  |         |

| H 01 L      | 29/786  | (2006.01) |         |       |         |

| H 01 L      | 21/336  | (2006.01) |         |       |         |

| B 8 1 B     | 7/02    | (2006.01) |         |       |         |

| B 8 1 C     | 3/00    | (2006.01) |         |       |         |

- (72)発明者 チャンハン・ユン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

- (72)発明者 サン・ジュネ・パク

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

- (72)発明者 チ・シュン・ロ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

- (72)発明者 マリオ・エフ・ヴェレス

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

- (72)発明者 ジョンヘ・キム

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 宇多川 勉

- (56)参考文献 特開2004-349513(JP,A)

特開2009-267098(JP,A)

特開2004-165269(JP,A)

特開2003-100450(JP,A)

米国特許出願公開第2007/0228383(US,A1)

特開2001-102523(JP,A)

## (58)調査した分野(Int.Cl., DB名)

|         |           |

|---------|-----------|

| H 01 L  | 27 / 00   |

| B 8 1 B | 7 / 02    |

| B 8 1 C | 3 / 00    |

| H 01 L  | 21 / 02   |

| H 01 L  | 21 / 3205 |

| H 01 L  | 21 / 336  |

| H 01 L  | 21 / 768  |

H 01 L 21 / 822

H 01 L 21 / 8234

H 01 L 21 / 8238

H 01 L 23 / 52

H 01 L 23 / 522

H 01 L 27 / 04

H 01 L 27 / 06

H 01 L 27 / 08

H 01 L 27 / 092

H 01 L 27 / 12

H 01 L 29 / 786