(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4708723号

(P4708723)

(45) 発行日 平成23年6月22日(2011.6.22)

(24) 登録日 平成23年3月25日(2011.3.25)

(51) Int.Cl.

F 1

|               |           |              |         |

|---------------|-----------|--------------|---------|

| G 11 C 16/02  | (2006.01) | G 11 C 17/00 | 6 1 3   |

| G 11 C 11/401 | (2006.01) | G 11 C 11/34 | 3 6 2 C |

| G 11 C 7/00   | (2006.01) | G 11 C 7/00  | 3 1 2 C |

請求項の数 6 (全 32 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2004-98463 (P2004-98463)    |

| (22) 出願日  | 平成16年3月30日 (2004.3.30)        |

| (65) 公開番号 | 特開2005-285230 (P2005-285230A) |

| (43) 公開日  | 平成17年10月13日 (2005.10.13)      |

| 審査請求日     | 平成19年1月30日 (2007.1.30)        |

|           |                                                        |

|-----------|--------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部 1753 番地 |

| (74) 代理人  | 100088672<br>弁理士 吉竹 英俊                                 |

| (74) 代理人  | 100088845<br>弁理士 有田 貴弘                                 |

| (72) 発明者  | 久保 貴志<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内              |

審査官 堀田 和義

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1及び第2のビット数によって指定される上位及び下位アドレス信号からなるアドレス信号に対応して設けられる複数のメモリセルを有するメモリセルアレイと、

前記上位アドレス信号に基づき、前記メモリセルアレイから所定数のメモリセル情報を読み出す読み出し制御部と、

前記所定数のメモリセル情報それぞれに対しセンスアンプ動作を行い所定ビット数のセンスデータを得るセンスアンプと、

第1のラッチ信号の指示するタイミングで前記所定ビット数のセンスデータをラッチするセンスデータ用ラッチと、

第2のラッチ信号の指示するタイミングで前記センスデータ用ラッチに格納された前記所定ビット数のセンスデータをページデータとしてラッチするページデータ用ラッチとを備え、前記ページデータは前記下位アドレス信号に対応してn個の部分ページデータに分類可能であり、

前記第1及び第2のラッチ信号を出力するページモード制御回路と、

ページモード読み出し期間中において、n回変化する前記下位アドレス信号に基づき、前記n個の部分ページデータを順次ページ選択データとして出力するセレクタ回路とをさらに備え、前記ページ選択データが外部データとして出力され、

前記ページモード制御回路は、

第1のアドレスを規定する前記上位アドレス信号に基づき前記メモリセルアレイから読

10

20

み出された前記所定数のメモリセル情報である第1のメモリセル情報群が、前記センスアンプ及び前記センスデータ用ラッチを介して、前記ページデータとして前記ページデータ用ラッチにラッチされた後、前記上位アドレス信号によって規定される前記第1のアドレスの所定ビットを反転させるビット反転処理を行い前記第1のアドレスに続く第2のアドレスを発生させ、

前記第1のメモリセル情報群に基づく前記ページモード読み出し期間中に、前記第2のアドレスを規定する前記上位アドレス信号に基づき前記メモリセルアレイから読み出された前記所定数のメモリセル情報である第2のメモリセル情報群を、前記センスアンプを介して前記所定ビット数のセンスデータとして前記センスデータ用ラッチに格納させ、

前記第1のメモリセル情報群に関する前記ページモード読み出し期間終了後、前記センスデータ用ラッチに格納された前記第2のメモリセル情報群に基づく前記所定ビット数のセンスデータを、前記ページデータとして前記ページデータ用ラッチにラッチさせることにより、前記第1のメモリセル情報群に基づく前記ページモード読み出し期間後に前記第2のメモリセル情報群に基づくページモード読み出し期間を設定したことを特徴とし、

前記ページモード制御回路は、前記上位アドレス信号のアドレス遷移を検出するアドレス遷移検出部を含み、

前記アドレス遷移検出部は、

前記上位アドレス信号のアドレス遷移を検出して第1のアドレス遷移検出信号を出力する第1のA T D回路と、

前記上位アドレス信号の前記所定ビットに対応する反転処理アドレス信号のアドレス遷移を検出して第2のアドレス遷移検出信号を出力する第2のA T D回路と、

前記第1及び第2のアドレス遷移検出信号のうち一方がアドレス遷移を指示するときアドレス遷移を指示する第3のアドレス遷移検出信号を出力するアドレス遷移信号発生手段と含み、

前記ページモード制御回路は、

前記第3のアドレス遷移検出信号に基づき、前記センスアンプを活性化させるセンス信号及び前記第1のラッチ信号を生成する第1の信号制御回路と、

前記第1のアドレス遷移検出信号と前記第1のラッチ信号とを受け、前記第1のアドレス遷移検出信号に基づき前記第2のラッチ信号を生成し、前記第1のアドレス遷移検出信号がアドレス遷移を指示した後における前記第1のラッチ信号による最初のラッチタイミング指示発生時に、前記ビット反転処理の実行を指示する反転指示信号と前記第2のラッチ信号とを生成する第2の信号制御回路とを含む、

半導体記憶装置。

### 【請求項2】

請求項1記載の半導体記憶装置であって、

前記ページモード制御回路は、

外部アドレス信号の少なくとも一部を前記上位アドレス信号としてラッチし、ラッチ内容に基づく前記上位アドレス信号を前記メモリセルアレイに付与するアドレスラッチ回路を含み、

前記アドレスラッチ回路は、

前記第1のアドレス遷移検出信号がアドレス遷移を指示したとき前記外部アドレス信号における所定ビット対応部分の非反転信号を前記上位アドレス信号の前記所定ビットとしてラッチし、前記反転指示信号が前記ビット反転処理の実行を指示したとき前記所定ビット対応部分の反転信号を前記所定ビットとしてラッチする、

半導体記憶装置。

### 【請求項3】

請求項1あるいは請求項2に記載の半導体記憶装置であって、

前記所定数のメモリセル情報はそれぞれ3値以上の多値情報を含み、

前記センスアンプは、前記所定数のメモリセル情報それぞれに対し第1～第m(2)のセンスアンプ動作を実行することにより、第1～第mの前記所定数のセンスデータを得

10

20

30

40

50

、前記所定ビット数は前記所定数のm倍のビット数を含み、

前記センスデータ用ラッチは第1～第mのセンスデータ用ラッチ部を含み、前記第1～第mのセンスデータ用ラッチ部は前記第1～第mの前記所定数のセンスデータをラッチし、

前記ページデータ用ラッチは第1～第mのページデータ用ラッチ部を含み、前記ページデータは第1～第mのページデータを含み、前記第1～第mのページデータ用ラッチ部は前記第1～第mの前記所定数のセンスデータを前記第1～第mのページデータとしてラッチし、前記第1～第mのページデータはn個の第1～第mの部分ページデータとして分類可能であり、

前記セレクタ回路は第1～第mのセレクタ回路を含み、前記第1～第mのセレクタ回路は、ページモード読み出し期間中において、n回変化する前記下位アドレス信号に基づき、前記n個の第1～第mの部分ページデータを順次第1～第mのページ選択データとして出力し、前記ページ選択データは前記第1～第mのページ選択データを含む、半導体記憶装置。

#### 【請求項4】

請求項1～請求項3のうち、いずれか1項に記載の半導体記憶装置であって、

複数のスペアメモリセルを有するスペアメモリセルアレイと、

前記上位アドレス信号の一部である第1の信号部分及びスペア選択信号に基づき所定のスペア数のスペア情報を読み出すスペア読み出し制御部と、

前記センスアンプと共に制御され、前記所定のスペア数のスペア情報をそれぞれに対しセンスアンプ動作を行い所定スペアビット数のスペアセンスデータを得る置換用センスアンプと、

前記第1のラッチ信号の指示するタイミングで前記所定スペアビット数のスペアセンスデータをラッチ数するスペアセンス用ラッチと、

前記第2のラッチ信号の指示するタイミングで前記スペアセンス用ラッチに格納された前記所定スペアビット数のスペアセンスデータをスペアデータとしてラッチするスペアデータ用ラッチと、

前記第1の信号部分を除き、前記所定ビットを含む前記上位アドレス信号の一部に基づき前記スペア選択信号と冗長置換情報を生成するスペア制御回路とを備え、前記冗長置換情報は前記下位アドレス信号に対応するアドレス置換情報及び冗長置換情報を含み、

前記冗長置換情報の前記アドレス置換情報と前記下位アドレス信号との比較結果に基づき置換実行の有無を判定する置換判定処理を実行し、置換実行時に前記ページ選択データのうち前記冗長置換情報で規定されるビットを前記スペアデータに置き換える置換実行回路をさらに備える、

半導体記憶装置。

#### 【請求項5】

請求項4記載の半導体記憶装置であって、

前記置換実行回路は、冗長置換情報を取り込み制御信号に基づくタイミングで前記冗長置換情報を取り込み、

前記ページモード制御回路は、

前記ビット判定処理に先がけて取り込みを指示する前記冗長置換情報を取り込み制御信号をさらに出力する置換情報制御機能をさらに有する、

半導体記憶装置。

#### 【請求項6】

第1及び第2のビット数によって指定される上位及び下位アドレス信号からなるアドレス信号に対応して設けられる複数のメモリセルを有するメモリセルアレイと、

前記上位アドレス信号に基づき、前記メモリセルアレイから所定数のメモリセル情報を読み出す読み出し制御部と、

前記所定数のメモリセル情報をそれぞれに対しセンスアンプ動作を行い所定ビット数のセンスデータを得るセンスアンプと、

10

20

30

40

50

第1のラッチ信号の指示するタイミングで前記所定ビット数のセンスデータをラッチするセンスデータ用ラッチと、

第2のラッチ信号の指示するタイミングで前記センスデータ用ラッチに格納された前記所定ビット数のセンスデータをページデータとしてラッチするページデータ用ラッチとを備え、前記ページデータは前記下位アドレス信号に対応してn個の部分ページデータに分類可能であり、

前記第1及び第2のラッチ信号を出力するページモード制御回路と、

ページモード読み出し期間中において、n回変化する前記下位アドレス信号に基づき、前記n個の部分ページデータを順次ページ選択データとして出力するセレクタ回路とをさらに備え、前記ページ選択データが外部データとして出力され、

前記ページモード制御回路は、前記上位アドレス信号のアドレス遷移を検出するアドレス遷移検出部を含み、

前記アドレス遷移検出部は、

前記上位アドレス信号のアドレス遷移を検出して第1のアドレス遷移検出信号を出力する第1のATD回路と、

前記上位アドレス信号の所定ビットに対応する反転処理アドレス信号のアドレス遷移を検出して第2のアドレス遷移検出信号を出力する第2のATD回路と、

前記第1及び第2のアドレス遷移検出信号のうち一方がアドレス遷移を指示するときアドレス遷移を指示する第3のアドレス遷移検出信号を出力するアドレス遷移信号発生手段と含み、

前記ページモード制御回路は、

前記第3のアドレス遷移検出信号に基づき、前記センスアンプを活性化させるセンス信号及び前記第1のラッチ信号を生成する第1の信号制御回路と、

前記第1のアドレス遷移検出信号と前記第1のラッチ信号とを受け、前記第1のアドレス遷移検出信号に基づき、前記第2のラッチ信号を生成し、前記第1のアドレス遷移検出信号がアドレス遷移を指示した後における前記第1のラッチ信号による最初のラッチタイミング指示発生時に、前記上位アドレス信号の前記所定ビットを反転させるビット反転処理の実行を指示する反転指示信号と前記第2のラッチ信号とを生成する第2の信号制御回路と、

前記ページモード制御回路は、

外部アドレス信号の少なくとも一部を前記上位アドレス信号としてラッチし、ラッチ内容に基づく前記上位アドレス信号を前記メモリセルアレイに付与するアドレスラッチ回路を含み、

前記アドレスラッチ回路は、

前記第1のアドレス遷移検出信号がアドレス遷移を指示したとき前記外部アドレス信号における所定ビット対応部分の非反転信号を前記上位アドレス信号の前記所定ビットとしてラッチし、前記反転指示信号が前記ビット反転処理の実行を指示したとき前記所定ビット対応部分の反転信号を前記所定ビットとしてラッチする、

半導体記憶装置。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、ページモード読み出し機能を有する半導体記憶装置に関する。

【背景技術】

【0002】

メモリセル自体は“H”，“L”レベルの論理出力機能を有さないDRAM等の半導体記憶装置では、メモリセルに記憶されたデータを検知・増幅して論理値(“H”，“L”)に変換させるセンスアンプ動作が必要となる。このセンスアンプ動作を1ワード単位に行っていたのでは著しくデータアクセスが遅くなることから、複数ワード分のメモリセルに記録されたデータを同時に読み出し(センスアンプ動作を含む)て一旦ラッチに蓄えて

10

20

30

40

50

おき、2回目以降のアクセスに対しては上記ラッチからの読み出し時間でアクセス可能になるページモード読み出し機能が広く使用されている。なお、ページモード読み出し機能を備えた半導体記憶装置として、例えば、特許文献1あるいは特許文献2に開示された半導体記憶装置がある。

#### 【0003】

半導体記憶装置がページモード読み出し機能を有している場合、例えば、16バイト(128ビット(1バイト=8ビット))のデータを一度に処理可能なLSIからのアクセス要求に対して、半導体記憶装置がデータ出力ピンを16本(16ビット分)有している場合、8ワード(128ビット(1ワード=16ビットで換算))分のページモード機能、すなわち、ページ長が8ワードのページモード機能を有しておれば、1度のセンスアンプ動作によって128ビットのデータ読み出しが実現できるため、当該LSIとの間で高速なデータ送信が可能となる。なお、ページモード読み出し機能を有する半導体記憶装置を用いた電子機器としては例えば携帯電話等が考えられる。

10

#### 【0004】

【特許文献1】特開平7-73364号公報

【特許文献2】特開平11-39863号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

しかしながら、ページモードのワード長を長くすることは、同時に活性化するセンスアンプ数を増加させることになり、かつ、一時的にデータを蓄えるラッチの記憶容量も増加されることになるため、ピーク電流の電流値の増大をもたらし、また、トランジスタや配線のレイアウト面積も増大されるという問題点があった。

20

#### 【0006】

この発明は上記問題点を解決するためになされたもので、ピーク電流及びレイアウト面積の増大を最小限に抑えたページモード読み出し機能を有する半導体記憶装置を得ることを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

この発明に係る請求項1記載の半導体記憶装置は、第1及び第2のビット数によって指定される上位及び下位アドレス信号からなるアドレス信号に対応して設けられる複数のメモリセルを有するメモリセルアレイと、前記上位アドレス信号に基づき、前記メモリセルアレイから所定数のメモリセル情報を読み出す読み出し制御部と、前記所定数のメモリセル情報それぞれに対しセンスアンプ動作を行い所定ビット数のセンスデータを得るセンスアンプと、第1のラッチ信号の指示するタイミングで前記所定ビット数のセンスデータをラッチするセンスデータ用ラッチと、第2のラッチ信号の指示するタイミングで前記センスデータ用ラッチに格納された前記所定ビット数のセンスデータをページデータとしてラッチするページデータ用ラッチとを備え、前記ページデータは前記下位アドレス信号に対応してn個の部分ページデータに分類可能であり、前記第1及び第2のラッチ信号を出力するページモード制御回路と、ページモード読み出し期間中ににおいて、n回変化する前記下位アドレス信号に基づき、前記n個の部分ページデータを順次ページ選択データとして出力するセレクタ回路とをさらに備え、前記ページ選択データが外部データとして出力され、前記ページモード制御回路は、第1のアドレスを規定する前記上位アドレス信号に基づき前記メモリセルアレイから読み出された前記所定数のメモリセル情報である第1のメモリセル情報群が、前記センスアンプ及び前記センスデータ用ラッチを介して、前記ページデータとして前記ページデータ用ラッチにラッチされた後、前記上位アドレス信号によって規定される前記第1のアドレスの所定ビットを反転させるビット反転処理を行い前記第1のアドレスに続く第2のアドレスを発生させ、前記第1のメモリセル情報群に基づく前記ページモード読み出し期間中に、前記第2のアドレスを規定する前記上位アドレス信号に基づき前記メモリセルアレイから読み出された前記所定数のメモリセル情報である第

30

40

50

2のメモリセル情報群を、前記センスアンプを介して前記所定ビット数のセンスデータとして前記センスデータ用ラッチに格納させ、前記第1のメモリセル情報群に関する前記ページモード読み出し期間終了後、前記センスデータ用ラッチに格納された前記第2のメモリセル情報群に基づく前記所定ビット数のセンスデータを、前記ページデータとして前記ページデータ用ラッチにラッチさせることにより、前記第1のメモリセル情報群に基づくページモード読み出し期間後に前記第2のメモリセル情報群に基づく前記ページモード読み出し期間を設定しており、前記ページモード制御回路は、前記上位アドレス信号のアドレス遷移を検出するアドレス遷移検出部を含み、前記アドレス遷移検出部は、前記上位アドレス信号のアドレス遷移を検出して第1のアドレス遷移検出信号を出力する第1のA T D回路と、前記上位アドレス信号の前記所定ビットに対応する反転処理アドレス信号のアドレス遷移を検出して第2のアドレス遷移検出信号を出力する第2のA T D回路と、前記第1及び第2のアドレス遷移検出信号のうち一方がアドレス遷移を指示するときアドレス遷移を指示する第3のアドレス遷移検出信号を出力するアドレス遷移信号発生手段と含み、前記ページモード制御回路は、前記第3のアドレス遷移検出信号に基づき、前記センスアンプを活性化させるセンス信号及び前記第1のラッチ信号を生成する第1の信号制御回路と、前記第1のアドレス遷移検出信号と前記第1のラッチ信号とを受け、前記第1のアドレス遷移検出信号に基づき前記第2のラッチ信号を生成し、前記第1のアドレス遷移検出信号がアドレス遷移を指示した後における前記第1のラッチ信号による最初のラッタイング指示発生時に、前記ビット反転処理の実行を指示する反転指示信号と前記第2のラッチ信号とを生成する第2の信号制御回路とを含む。

10

20

#### 【発明の効果】

#### 【0008】

この発明における請求項1記載の半導体記憶装置は、第1のメモリセル情報群に基づく前記ページモード読み出し期間中に、第2のメモリセル情報群を前記センスアンプを介して前記所定ビット数のセンスデータとしてセンスデータ用ラッチに格納させていることにより、第1及び第2のメモリセル情報群によるページモード読み出しを連続的に行える。

#### 【0009】

したがって、連続してページ選択データが読み出せる数であるワード長は、センスアンプ、センスデータ用ラッチ及びページデータ用ラッチに必要な能力に対し2倍となる。

#### 【0010】

30

その結果、ページモード読み出し時のピーク電流及びページモード読み出し機能を実現する回路のレイアウト面積の増大を最小限に抑えた半導体記憶装置を得ることができる。

#### 【発明を実施するための最良の形態】

#### 【0011】

##### <原理>

所定のページ長のページモード読み出し機能を有する半導体記憶装置において、上記ページモード読み出し機能を連続的に複数回動作させることができれば、実質的なページ長を複数倍にするページモード（以下、「シーケンシャルページモード」と呼ぶ）が実現することになり、上述したピーク電流の電流値増大やレイアウト面積増大問題を緩和しつつ高速なデータ転送を確保することが可能となる。しかしながら、本来、外部からのアクセス要求に非同期に動作するページモード読み出し動作時に、内部で自動的にページモード読み出し機能を継続させることは非常に複雑な動作を強いられるため、従来は実現性に乏しかった。特に冗長データとの整合性を実現するのは難しい。このような問題を解消を目指したのが本願発明である。

40

#### 【0012】

また、本発明は、D R A M等の揮発性半導体記憶装置は勿論、不揮発性半導体記憶装置にも適用可能である。例えば、コントロールゲート、フローティングゲートを有するメモリセルトランジスタで構成されるフラッシュメモリにおけるページモード読み出し動作に対しても適用することができる。すなわち、フラッシュメモリのように、複数のビット線のうちYゲートで選択された所定数のビット線に対し、4ワードあるいは8ワード程度の

50

所定数のセンスアンプを設ける構成において、本発明は特に有効である。

【0013】

<実施の形態1>

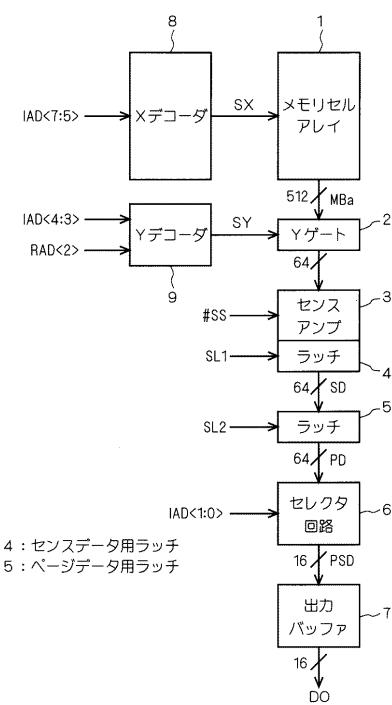

図1はこの発明の実施の形態1である半導体記憶装置のメモリセルアレイ周辺部の構成を示すブロック図である。同図において、内部アドレスIAD<7:5>によってX選択信号SXが選択され、内部アドレスIAD<4:3>及び反転処理アドレスRAD<2>によりY選択信号SYが選択され、64ビットのセンスデータSDが出力され、ページアドレスとして2ビットの内部アドレスIAD<1:0>が用いられる4ワードページの場合が示されている。

【0014】

10

メモリセルアレイ1はマトリクス状に配置された複数のメモリセルを有し、X選択信号SXに基づき、複数のメモリセルのうちより選択されたメモリセルからの記憶データを、総計512本のメインビット線MBaそれぞれに読み出す。

【0015】

Yゲート2はY選択信号SYに基づき、512本のメインビット線MBaのうち64本(所定数)を選択してセンスアンプ3に電気的に接続する。

【0016】

すなわち、内部アドレスIAD<7:3>及び反転処理アドレスRAD<2>からなる上位アドレス信号により、メモリセルアレイ1における64個(所定数)のメモリセル情報がセンスアンプ3に読み出される。なお、反転処理アドレスRAD<2>が上位アドレスにおけるビット反転対象の所定ビットとなる。

20

【0017】

センスアンプ3は、センス信号#SSが“L”のとき活性状態となり、活性状態時にYゲート2より選択された64本のメインビット線MBaに現れる記憶データを検知・增幅するセンスアンプ動作を実行し、64ビット(所定ビット数)構成のセンスデータSDを得る。

【0018】

センスデータ用ラッチ4は、ラッチ信号SL1が“H”的とき活性状態となり、活性状態時にセンスアンプ3により得られた64ビット構成のセンスデータSDとしてラッチする。以降、ラッチ信号SL1が再び“H”になるまでラッチしたセンスデータSDを保持する。したがって、センスアンプ3が非活性状態になっても、センスデータ用ラッチ4にラッチされたセンスデータSDは保持される。

30

【0019】

ページデータ用ラッチ5は、ラッチ信号SL2が“H”的とき活性状態となり、活性状態時にセンスデータ用ラッチ4に格納されたセンスデータSDをページデータPDとしてラッチする。このページデータPDは下位アドレスである内部アドレスIAD<1:0>に対応して4個の1ワード構成の部分ページデータに分類可能である。

【0020】

セレクタ回路6は、内部アドレスIAD<1:0>で選択されるアドレスに基づき、64ビットのページデータPD(4個の部分ページデータ)から、一の部分ページデータを1ワード(16ビット)のページ選択データPSDとして出力する。すなわち、センスアンプ3、センスデータ用ラッチ4、ページデータ用ラッチ5及びセレクタ回路6による従来レベルのハードウェア構成としては、ページ長が4ワード構成のページモード読み出し機能を有している。

40

【0021】

出力バッファ7はページ選択データPSDをバッファリングし、外部データDOとして出力する。

【0022】

Xデコーダ8は内部アドレスIAD<7:5>に基づきX選択信号SXを出力し、Yデコーダ9は内部アドレスIAD<4:3>及び反転処理アドレスRAD<2>に基づきY

50

選択信号 S Y を出力する。したがって、Y ゲート 2、X デコーダ 8 及び Y デコーダ 9 によってメモリセルアレイ 1 から 64 ビットのメモリセル情報を読み出す読み出し制御部が構成される。

【 0 0 2 3 】

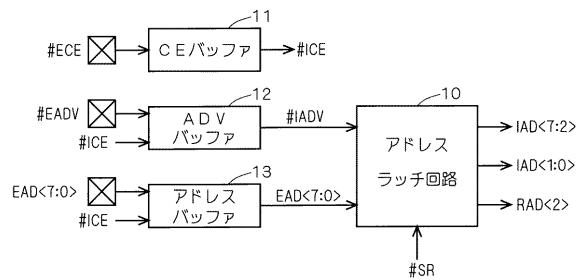

図 2 は内部アドレス I A D < 7 : 5 >、内部アドレス I A D < 4 : 3 > 及び反転処理アドレス R A D < 2 > からなる内部アドレスを供給する内部アドレス供給部の構成を示すブロック図である。

【 0 0 2 4 】

同図において、C E バッファ 1 1 は外部チップイネーブル信号 # E C E をバッファリングして内部チップイネーブル信号 # I C E として出力する。A D V バッファ 1 2 は外部アドレスバリッド (address valid) 信号 # E A D V 及び内部チップイネーブル信号 # I C E をバッファリングして受け内部アドレスバリッド信号 # I A D V として出力する。アドレスバッファ 1 3 は外部アドレス E A D < 7 : 0 > 及び内部チップイネーブル信号 # I C E をバッファリングし外部アドレス E A D < 7 : 0 > をアドレスラッチ回路 1 0 に出力する。

【 0 0 2 5 】

アドレスラッチ回路 1 0 は内部アドレスバリッド信号 # I A D V、外部アドレス E A D < 7 : 0 > 及び内部チップイネーブル信号 # I C E を受け、外部アドレスバリッド信号 # E A D V 及び内部チップイネーブル信号 # I C E が “L” のとき、外部アドレス E A D < 7 : 0 > 及び反転指示信号 # S R に基づき、内部アドレス I A D < 7 : 2 >、内部アドレス I A D < 1 : 0 > 及び反転処理アドレス R A D < 2 > を出力する。

【 0 0 2 6 】

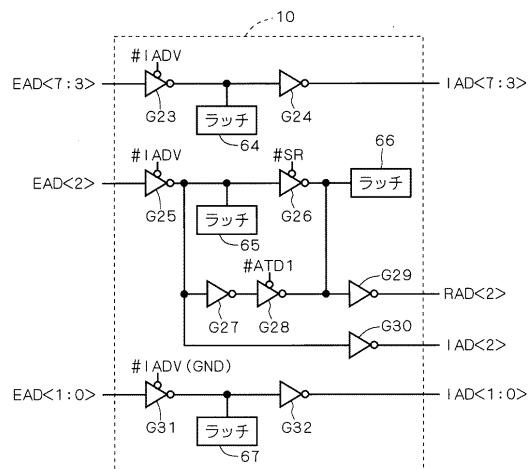

図 3 はアドレスラッチ回路 1 0 の内部構成を示す回路図である。同図に示すように、外部アドレス E A D < 7 : 3 > をインバータ G 2 3 が受け、インバータ G 2 4 の入力がインバータ G 2 3 の出力及びラッチ 6 4 に接続される。そして、インバータ G 2 4 の出力が内部アドレス I A D < 7 : 3 > となる。インバータ G 2 3 は制御入力に内部アドレスバリッド信号 # I A D V を受け、内部アドレスバリッド信号 # I A D V が “L” のときに活性状態となる。

【 0 0 2 7 】

なお、実際には外部アドレス E A D < 7 : 3 > は 5 ビットであるため、インバータ G 2 3、G 2 4 及びラッチ 6 4 も外部アドレス E A D < 7 : 3 > の各アドレス信号 (1 ビット分) に対応して総計 5 つずつ設けられる。本明細書中では、外部アドレス E A D < 7 : 3 > 等の複数ビットの信号を並列に受ける際に、対応する構成が各ビットにおいて同じ場合、便宜上、1 ビット分の構成を代表的に示している場合がある。

【 0 0 2 8 】

外部アドレス E A D < 1 : 0 > をインバータ G 3 1 が受け、インバータ G 3 2 の入力がインバータ G 3 1 の出力及びラッチ 6 7 に接続される。そして、インバータ G 3 2 の出力が内部アドレス I A D < 1 : 0 > となる。インバータ G 3 1 は制御入力に内部アドレスバリッド信号 # I A D V を受け、内部アドレスバリッド信号 # I A D V が “L” のときに活性状態となる。

【 0 0 2 9 】

反転対象ビットである外部アドレス E A D < 2 > をインバータ G 2 5、G 2 7 及び G 3 0 の入力が共通に受ける。インバータ G 2 6 の入力がインバータ G 2 5 の出力及びラッチ 6 5 に接続され、インバータ G 2 6 の出力がラッチ 6 6 及びインバータ G 2 9 の入力に接続される。インバータ G 2 7 ~ G 2 9 は直列に接続され、インバータ G 2 9 の入力はインバータ G 2 6 の出力及びラッチ 6 6 にも接続される。そして、インバータ G 2 9 の出力が反転処理アドレス R A D < 2 > となり、インバータ G 3 0 の出力が内部アドレス I A D < 2 > となる。

【 0 0 3 0 】

このような構成において、アドレスラッチ回路 1 0 は、内部アドレスバリッド信号 # I A D V が “L” のとき、外部アドレス E A D < 7 : 3 > 及び外部アドレス E A D < 1 : 0 >

10

20

30

40

50

>を内部アドレス I A D < 7 : 3 >及び内部アドレス I A D < 1 : 0 >として出力する。

【 0 0 3 1 】

そして、アドレスラッチ回路 10 は、アドレス遷移検出信号 # A T D 1 の “ L ” 立ち下がりをトリガとして、外部アドレス E A D < 2 >を反転処理アドレス R A D < 2 >として出力し、反転指示信号 # S R の “ L ” 立ち下がりをトリガとして外部アドレス E A D < 2 >の反転信号を反転処理アドレス R A D < 2 >として出力する。

【 0 0 3 2 】

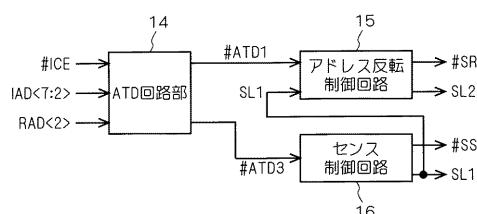

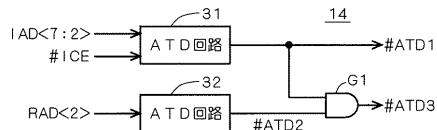

図 4 は図 1 で示したメモリセルアレイ 1 のメモリセルアレイ周辺部に対し各種制御信号を出力するページモード制御回路の主要部の構成を示す回路図である。同図において、A T D 回路部 14 (アドレス遷移検出部) は内部チップイネーブル信号 # I C E 、内部アドレス I A D < 7 : 2 > 及び反転処理アドレス R A D < 2 > を受け、アドレス遷移検出信号 # A T D 1 及び # A T D 3 を出力する。

【 0 0 3 3 】

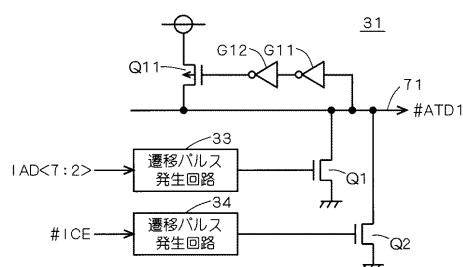

図 5 は A T D 回路部 14 の内部構成を示す回路図である。同図に示すように、A T D 回路 3 1 は内部アドレス I A D < 7 : 2 > 及び内部チップイネーブル信号 # I C E を受け、アドレス遷移検出信号 # A T D 1 を出力し、A T D 回路 3 2 は反転処理アドレス R A D < 2 > を受け、アドレス遷移検出信号 # A T D 2 を出力する。A N D ゲート G 1 はアドレス遷移検出信号 # A T D 1 及びアドレス遷移検出信号 # A T D 2 を受け、アドレス遷移検出信号 # A T D 3 を出力する。

【 0 0 3 4 】

図 6 は A T D 回路 3 1 の内部構成を示す回路図である。同図に示すように、遷移パルス発生回路 3 3 は内部アドレス I A D < 7 : 2 > を受け、内部アドレス I A D < 7 : 2 > のいずれかのアドレス遷移を検出すると “ H ” の遷移パルスを発生する。遷移パルス発生回路 3 4 は内部チップイネーブル信号 # I C E を受け、内部チップイネーブル信号 # I C E のエッジ変化を検出すると “ H ” の遷移パルスを発生する。

【 0 0 3 5 】

N M O S トランジスタ Q 1 及び Q 2 はそれぞれ信号線 7 1 と接地レベル間に介挿され、N M O S トランジスタ Q 1 のゲートが遷移パルス発生回路 3 3 の出力に接続され、N M O S トランジスタ Q 2 のゲートが遷移パルス発生回路 3 4 の出力に接続される。

【 0 0 3 6 】

直列に接続されるインバータ G 1 1 , G 1 2 のインバータ G 1 1 の入力が信号線 7 1 に接続され、P M O S トランジスタ Q 1 1 は信号線 7 1 , 電源 V dd 間に介挿され、P M O S トランジスタ Q 1 1 のゲートがインバータ G 1 2 の出力に接続される。そして、信号線 7 1 より得られる信号がアドレス遷移検出信号 # A T D 1 となる。なお、遷移パルス発生回路 3 3 及び N M O S トランジスタ Q 1 は内部アドレス I A D < 7 : 2 > の各ビットに対応すべく実際にはそれぞれ 6 個設けられる。

【 0 0 3 7 】

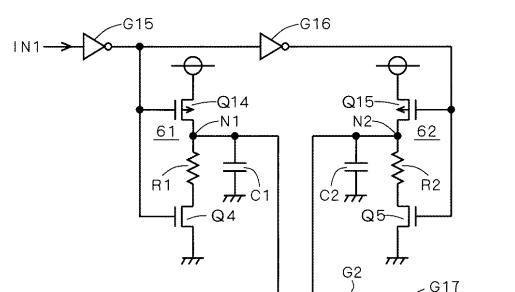

図 7 は遷移パルス発生回路の内部構成を示す回路図である。同図に示す遷移パルス発生回路は、遷移パルス発生回路 3 3 , 3 4 に相当し、遷移パルス発生回路 3 3 の場合、内部アドレス I A D < 7 : 2 > の各アドレスビットを入力信号 I N 1 として受け、出力信号 O U T 1 を出力する 1 ビット分の構成に相当し、遷移パルス発生回路 3 4 の場合、内部チップイネーブル信号 # I C E を入力信号 I N 1 として受け、出力信号 O U T 1 を出力する構成に相当する。

【 0 0 3 8 】

同図に示すように、直列に接続されるインバータ G 1 5 , G 1 6 において、インバータ G 1 5 の入力に入力信号 I N 1 を受ける。N M O S トランジスタ Q 4 , P M O S トランジスタ Q 1 4 , 抵抗 R 1 , 及びキャパシタ C 1 により構成される L 出力遅延インバータ 6 1 において、P M O S トランジスタ Q 1 4 のソースは電源 V dd に接続され、ドレイン ( ノード N 1 ) は抵抗 R 1 の一端及びキャパシタ C 1 の一方電極に接続される。抵抗 R 1 の他端は N M O S トランジスタ Q 4 のドレインに接続され、N M O S トランジスタ Q 4 のソース

10

20

30

40

50

は接地され、キャパシタC1の他方電極は接地される。そして、インバータG15の出力がPMOSトランジスタQ14及びNMOSトランジスタQ4のゲートに共通に接続される。

【0039】

NMOSトランジスタQ5, PMOSトランジスタQ15, 抵抗R2, 及びキャパシタC2により構成されるL出力遅延インバータ62において、PMOSトランジスタQ15のソースは電源Vddに接続され、ドレイン(ノードN2)は抵抗R2の一端及びキャパシタC2の一方電極に接続される。抵抗R2の他端はNMOSトランジスタQ5のドレインに接続され、NMOSトランジスタQ5のソースは接地され、キャパシタC2の他方電極は接地される。そして、インバータG16の出力がPMOSトランジスタQ15及びNMOSトランジスタQ5のゲートに共通に接続される。

10

【0040】

L出力遅延インバータ61は入力(インバータG15の出力)の“H”立ち上がり時は、入力の“L”立ち下がり時に比べて抵抗R1, キャパシタC1の第1のRC時定数で決定される遅延時間分遅れて“L”的反転遅延信号を出力し、L出力遅延インバータ62は入力(インバータG16の出力)の“H”立ち上がり時に、入力が“L”立ち下がり時に比べて抵抗R2, キャパシタC2の第2のRC時定数で決定される遅延時間分遅れて“L”的反転遅延信号を出力する。

【0041】

NANDゲートG2はノードN1, N2を一方入力、他方入力として受け、その出力がインバータG17の入力に接続され、インバータG17の出力が出力信号OUT1となる。

20

【0042】

このような構成の遷移パルス発生回路において、通常は、L出力遅延インバータ61, 62のうち一方の出力が必ず“L”的ため、出力信号OUT1は“L”となっている。

【0043】

そして、入力信号IN1の“H”立ち上がり時において、L出力遅延インバータ61の出力の“L”“H”への変化に対し、L出力遅延インバータ62の出力の“H”“L”への変化が第2のRC時定数分遅れて生じるため、上記第2のRC時定数分の“H”パルスが出力信号OUT1から発生する。

30

【0044】

同様にして、入力信号IN1の“L”立ち下がり時において、L出力遅延インバータ62の出力の“L”“H”への変化に対し、L出力遅延インバータ61の出力における“H”“L”への変化が第1のRC時定数分遅れて生じるため、上記第1のRC時定数分の“H”パルスが出力信号OUT1から発生する。

【0045】

このように、遷移パルス発生回路は、入力信号IN1の“H”立ち上がり及び“L”立ち下がりの信号遷移時に“H”パルスを発生する出力信号OUT1を出力する。

【0046】

図6に戻って、上記構成のATD回路31は、通常は、PMOSトランジスタQ11により、信号線71は“H”に設定されているため、“H”的アドレス遷移検出信号#ATD1を出力する。そして、内部アドレスIAD<7:2>のアドレス遷移時にNMOSトランジスタQ1が、遷移パルス発生回路33からの“H”的遷移パルス発生時間オンするため、アドレス遷移検出信号#ATD1が所定期間“L”に立ち下がり、同様にして内部チップイネーブル信号#ICEの信号遷移時にNMOSトランジスタQ2が、遷移パルス発生回路34の“H”的遷移パルス発生時間オンするため、アドレス遷移検出信号#ATD1が所定期間“L”に立ち下がる。

40

【0047】

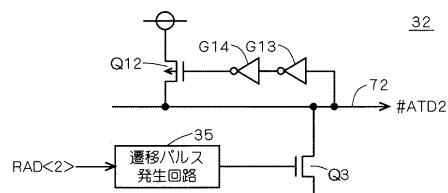

図8はATD回路32の内部構成を示す回路図である。同図に示すように、遷移パルス発生回路35は反転処理アドレスRAD<2>を受け、反転処理アドレスRAD<2>の

50

アドレス遷移を検出すると“H”の遷移パルスを発生する。

【0048】

NMOSトランジスタQ3は信号線72と接地レベル間に介挿され、NMOSトランジスタQ3のゲートが遷移パルス発生回路35の出力に接続される。

【0049】

直列に接続されるインバータG13, G14のインバータG13の入力が信号線72に接続され、PMOSトランジスタQ12は信号線72, 電源Vdd間に介挿され、PMOSトランジスタQ12のゲートがインバータG14の出力に接続される。そして、信号線72より得られる信号がアドレス遷移検出信号#ATD2となる。

【0050】

なお、遷移パルス発生回路35は図7で示した構成を呈しており、遷移パルス発生回路35に入力される反転処理アドレスRAD<2>を入力信号IN1として受け、出力信号OUT1を出力する構成に相当する。

【0051】

このような構成において、ATD回路32は通常は、PMOSトランジスタQ12により、信号線72は“H”に設定されているため、“H”のアドレス遷移検出信号#ATD2を出力する。そして、反転処理アドレスRAD<2>の遷移時にNMOSトランジスタQ3が、遷移パルス発生回路35からの“H”の遷移パルス発生時間オンするため、アド

【0052】

図5に戻って、上述したATD回路31, 32及びANDゲートG1からなるATD回路部14は、内部アドレスIAD<7:2>あるいは内部チップイネーブル信号#ICEの信号遷移時に“L”パルスを発生するアドレス遷移検出信号#ATD1を出力し、内部アドレスIAD<7:2>、内部チップイネーブル信号#ICEあるいは反転処理アドレスRAD<2>の信号遷移時に“L”パルスを発生するアドレス遷移検出信号#ATD3を出力している。

【0053】

図4に戻って、アドレス反転制御回路15(第2の信号制御回路)は、アドレス遷移検出信号#ATD1及びラッチ信号SL1に基づき、反転指示信号#SR及びラッチ信号SL2を出力する。センス制御回路16(第1の信号制御回路)はアドレス遷移検出信号#ATD3に基づきセンス信号#SS及びラッチ信号SL1を出力する。

【0054】

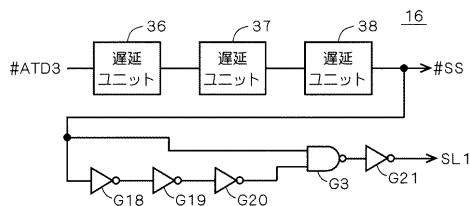

図9はセンス制御回路16の内部構成を示す回路図である。同図に示すように、3段直列に接続される遅延ユニット36～38のうち初段の遅延ユニット36はアドレス遷移検出信号#ATD3を受け、最終段の遅延ユニット38の出力がセンス信号#SSとなる。3段直列に接続されるインバータG18～G20のうち初段のインバータG18がセンス信号#SSを受ける。NANDゲートG3は一方入力にセンス信号#SSを他方入力にインバータG20の出力を受ける。NANDゲートG3の出力はインバータG21を介してラッチ信号SL1として出力される。

【0055】

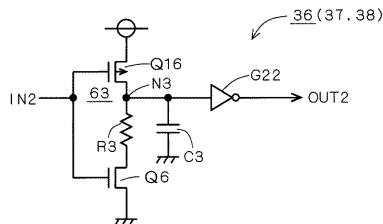

図10は遅延ユニット36(37, 38)の内部構成を示す回路図である。同図に示すように、NMOSトランジスタQ6, PMOSトランジスタQ16, 抵抗R3, 及びキャパシタC3により構成されるL出力遅延インバータ63において、PMOSトランジスタQ16のソースは電源Vddに接続され、ドレイン(ノードN3)は抵抗R3の一端及びキャパシタC3の一方電極に接続される。抵抗R3の他端はNMOSトランジスタQ6のドレインに接続され、NMOSトランジスタQ6のソースは接地され、キャパシタC3の他方電極は接地される。インバータG22の入力がノードN3に接続される。

【0056】

そして、入力信号IN2がPMOSトランジスタQ16及びNMOSトランジスタQ6のゲートに共通に接続され、インバータG22の出力が出力信号OUT2となる。なお、入力信号IN2は遅延ユニット36, 37及び38において、アドレス遷移検出信号#A

10

20

30

40

50

T D 3、遅延ユニット 3 6 の出力信号、及び遅延ユニット 3 7 の出力信号に相当し、出力信号 O U T 2 は遅延ユニット 3 6 の出力信号、遅延ユニット 3 7 の出力信号、遅延ユニット 3 8 の出力信号（センス信号 # S S ）に相当する。

【 0 0 5 7 】

このような構成において、遅延ユニット 3 6 の L 出力遅延インバータ 6 3 は入力信号 I N 2 が“ H ”立ち上がり時に、入力が“ L ”立ち下がり時に比べて抵抗 R 3 , キャパシタ C 3 の第 3 の R C 時定数で決定される遅延時間分遅れて“ L ”の反転遅延信号を出力するため、入力信号 I N 2 から出力信号 O U T 2 への“ H ”立ち上がりの信号伝搬遅延が生じる。一方、入力信号 I N 2 の“ L ”立ち下がり時は、L 出力遅延インバータ 6 3 も速やかに“ H ”の反転信号を出力するため、“ L ”立ち下がりの信号伝搬遅延が生じない。このように、遅延ユニット 3 6 は入力信号 I N 2 の“ H ”立ち上がり時間を所定時間遅延させて出力信号 O U T 2 を出力する。

10

レス遷移検出信号 # A T D 2 が所定期間“ L ”に立ち下がる。

【 0 0 5 8 】

図 9 に戻って、センス信号 # S S は、アドレス遷移検出信号 # A T D 3 の“ L ”立ち下がりをトリガとして速やかに“ L ”に立ち下がり、アドレス遷移検出信号 # A T D 3 の“ H ”立ち上がりをトリガとし、遅延ユニット 3 6 ~ 3 8 による遅延時間後に“ H ”に立ち上がる信号として出力される。

【 0 0 5 9 】

一方、ラッチ信号 S L 1 は、通常は N A N D ゲート G 3 の一方の入力が“ L ”のため“ L ”の信号となり、センス信号 # S S の“ H ”立ち上がり時から所定期間（インバータ G 1 8 ~ G 2 0 の信号伝搬遅延時間）のみ“ H ”パルスを発生する信号となる。

20

【 0 0 6 0 】

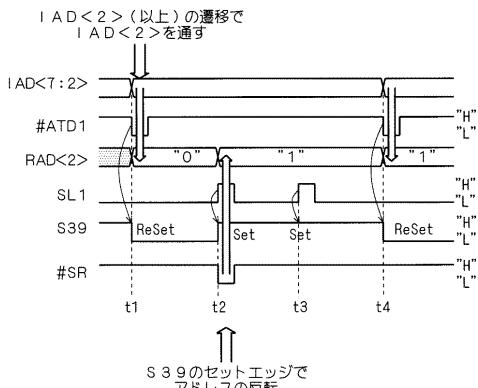

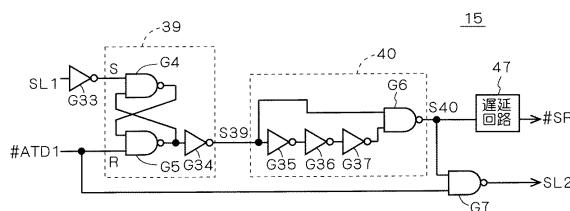

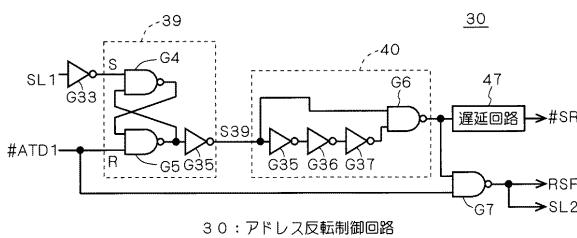

図 1 1 はアドレス反転制御回路 1 5 の内部構成を示す回路図である。同図に示すように、アドレス反転制御回路 1 5 はインバータ G 3 3 、 R S フリップフロップ 3 9 、 1 ショットパルス発生回路 4 0 、 N A N D ゲート G 7 及び遅延回路 4 7 により構成される。

【 0 0 6 1 】

インバータ G 3 3 はラッチ信号 S L 1 を受け、その出力が R S フリップフロップ 3 9 の S (セット) 入力部に入力される。一方、アドレス遷移検出信号 # A T D 1 が R S フリップフロップ 3 9 の R (リセット) 入力部に入力される。

30

【 0 0 6 2 】

R S フリップフロップ 3 9 は N A N D ゲート G 4 , G 5 及びインバータ G 3 4 より構成され、 N A N D ゲート G 4 , G 5 の一方入力がそれぞれ S 入力部、 R 入力部となり、 N A N D ゲート G 4 の出力が N A N D ゲート G 5 の他方入力として帰還し、 N A N D ゲート G 5 の出力が N A N D ゲート G 4 の他方入力として帰還する。インバータ G 3 4 は入力が N A N D ゲート G 5 の出力に接続され、インバータ G 3 4 からの出力信号が F F 出力信号 S 3 9 となる。

【 0 0 6 3 】

このような構成の R S フリップフロップ 3 9 において、ラッチ信号 S L 1 の“ H ”立ち上がりをトリガとして F F 出力信号 S 3 9 が“ H ”にセットされ、アドレス遷移検出信号 # A T D 1 の“ L ”立ち下がりをトリガとして“ L ”にリセットされる。

40

【 0 0 6 4 】

1 ショットパルス発生回路 4 0 は直列に接続されたインバータ G 3 5 ~ G 3 7 及び N A N D ゲート G 6 より構成され、インバータ G 3 5 の入力が F F 出力信号 S 3 9 を受ける。 N A N D ゲート G 6 は一方入力に F F 出力信号 S 3 9 を受け、他方入力がインバータ G 3 7 の出力に接続される。そして、 N A N D ゲート G 6 の出力信号が遅延回路 4 7 を介し反転指示信号 # S R として出力される。なお、アドレス反転制御回路 1 5 では遅延回路 4 7 を介して反転指示信号 # S R を出力する例を示したが、1 ショットパルス発生回路 4 0 の出力をそのまま反転指示信号 # S R として出力させても良い。

【 0 0 6 5 】

NANDゲートG7は一方入力にNANDゲートG6の出力を受け、他方入力にアドレス遷移検出信号#ATD1を受け、その出力をラッチ信号SL2として出力する。

【0066】

このような構成において、1ショットパルス発生回路40から遅延回路47を介して出力される反転指示信号#SRは、通常はNANDゲートG6の一方の入力が“L”的ため“H”的信号となり、FF出力信号S39の“H”立ち上がり時から遅延回路47により遅延時間経過後の所定期間（インバータG35～G37の信号伝搬遅延時間）のみ“L”パルスを発生する信号となる。

【0067】

したがって、アドレス反転制御回路15は、アドレス遷移検出信号#ATD1の“L”立ち下がりによってRSフリップフロップ39がリセットされた後にラッチ信号SL1の最初の“H”立ち上がりによってRSフリップフロップ39がセットされると、1ショットパルス発生回路40から遅延回路47を介して得られる反転指示信号#SRとして、ピット反転処理を指示する“L”的パルスを発生する。10

【0068】

さらに、アドレス反転制御回路15は、1ショットパルス発生回路40の出力信号S40（反転指示信号#SRの遅延前の信号）及びアドレス遷移検出信号#ATD1のうち一方が“L”パルスを発生したとき、ラッチ信号SL2として“L”パルスを発生する。

【0069】

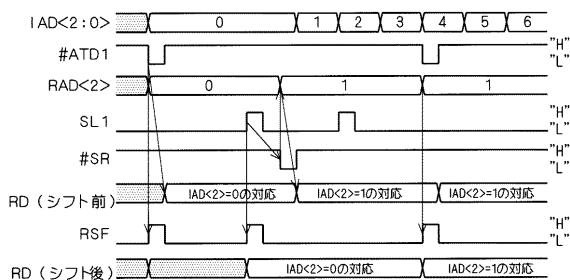

図12はアドレス反転制御回路15及びその周辺回路の動作を示すタイミング図である。20 同図に示すように、時刻t1において、内部アドレスIAD<7:2>のアドレス遷移をATD回路部14が検出すると、アドレス遷移検出信号#ATD1が“L”に立ち下がる。

【0070】

このアドレス遷移検出信号#ATD1の“L”立ち下がりをトリガとして内部アドレスIAD<2>が反転処理アドレスRAD<2>としてアドレスバッファ13より出力される。同時に、アドレス反転制御回路15のRSフリップフロップ39がリセットされ、FF出力信号S39が“L”となる。

【0071】

そして、時刻t1から所定時間経過後の時刻t2にラッチ信号SL1の“H”立ち上がりをトリガとしてRSフリップフロップ39がセットされFF出力信号S39が“H”となり、その結果、反転指示信号#SRが“L”に立ち下がる。なお、図12では説明の都合上、1ショットパルス発生回路40の出力信号S40が遅延回路47を介することなくそのまま反転指示信号#SRとして出力される場合を示している。30

【0072】

この反転指示信号#SRの“L”立ち下がりをトリガとして内部アドレスIAD<2>の反転信号が反転処理アドレスRAD<2>としてアドレスバッファ13より出力される。

【0073】

その後、時刻t2から所定時間経過後の時刻t3にラッチ信号SL1が再び“H”に立ち上がる。しかし、FF出力信号S39が時刻t2から“H”であるため、FF出力信号S39が“H”を維持するに留まるため、反転指示信号#SRが“L”に立ち下がることはない。40

【0074】

その後、時刻t4において、内部アドレスIAD<7:2>のアドレス遷移をATD回路部14が検出すると、アドレス遷移検出信号#ATD1が“L”に立ち下がる。このアドレス遷移検出信号#ATD1の“L”立ち下がりをトリガとして内部アドレスIAD<2>が反転処理アドレスRAD<2>としてアドレスバッファ13より出力される。同時に、アドレス反転制御回路15のRSフリップフロップ39がリセットされ、FF出力信号S39が“L”となる。50

## 【0075】

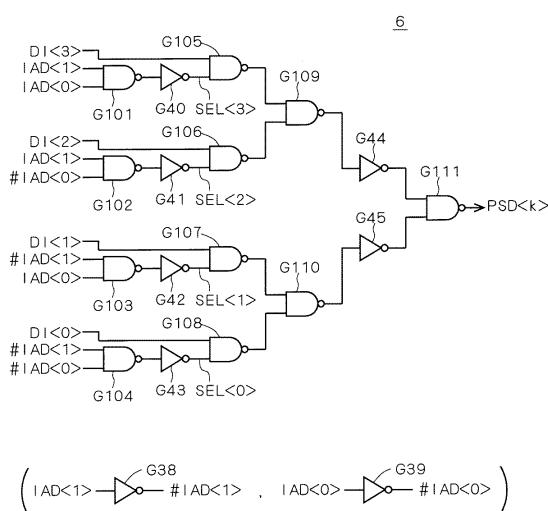

図13は図1のセレクタ回路6の内部構成を示す回路図である。同図において、16ビットのページ選択データPSDのうち、所定ビットPSD<k>（k=0～15のいずれか）に対応し、内部アドレスIAD<1:0>により識別可能なアドレス毎に分類される部分ページデータDI<0>～DI<3>の選択回路を示している。実際には、図13のような構成がページ選択データPSDの16ビット分存在する。ただし、ページ選択データPSDの各ビットにおいて選択信号SEL<3:0>を生成する回路部分（G101～G104, G40～G43）は共有することができる。

## 【0076】

NANDゲートG101は一方入力に内部アドレスIAD<1>を受け、他方入力に内部アドレスIAD<0>を受け、インバータG40はNANDゲートG101の出力を受ける。

10

## 【0077】

NANDゲートG102は一方入力に内部アドレスIAD<1>を受け、他方入力に反転内部アドレス#IAD<0>を受け、インバータG41はNANDゲートG102の出力を受ける。なお、反転内部アドレス#IAD<0>は内部アドレスIAD<0>を受けるインバータG39の出力として得ることができる。

## 【0078】

NANDゲートG103は一方入力に反転内部アドレス#IAD<1>を受け、他方入力に内部アドレスIAD<0>を受け、インバータG42はNANDゲートG103の出力を受ける。なお、反転内部アドレス#IAD<1>は内部アドレスIAD<1>を受けるインバータG38の出力として得ることができる。

20

## 【0079】

NANDゲートG104は一方入力に反転内部アドレス#IAD<1>を受け、他方入力に反転内部アドレス#IAD<0>を受け、インバータG43はNANDゲートG104の出力を受ける。

## 【0080】

NANDゲートG105は一方入力に部分ページデータDI<3>を受け、他方入力にインバータG40の出力信号である選択信号SEL<3>を受ける。

## 【0081】

NANDゲートG106は一方入力に部分ページデータDI<2>を受け、他方入力にインバータG41の出力信号である選択信号SEL<2>を受ける。

30

## 【0082】

NANDゲートG107は一方入力に部分ページデータDI<1>を受け、他方入力にインバータG42の出力信号である選択信号SEL<1>を受ける。

## 【0083】

NANDゲートG108は一方入力に部分ページデータDI<0>を受け、他方入力にインバータG43の出力信号である選択信号SEL<0>を受ける。

## 【0084】

NANDゲートG109は一方入力及び他方入力にNANDゲートG105及びG106の出力が接続され、NANDゲートG110は一方入力及び他方入力にNANDゲートG107及びNANDゲートG108の出力が接続される。NANDゲートG109及びG110の出力がインバータG44及びG45の入力に接続される。

40

## 【0085】

NANDゲートG111は一方入力及び他方入力がインバータG44及びG45の出力に接続され、NANDゲートG111の出力がページ選択データPSD<k>となる。

## 【0086】

このような構成において、内部アドレスIAD<1:0>によって選択信号SEL<3:0>のうちの選択信号のみ“H”となる。ここで、“H”になった選択信号を選択信号SEL<j>（j=0～3のいずれか）とすると、ページ選択データPSD<k>とし

50

て部分ページデータ  $D_I < j >$  が出力される。

【0087】

図14はこの発明の実施の形態1による半導体記憶装置のページモード読み出し動作を示すタイミング図である。以下、同図を参照して実施の形態1のページモード読み出し動作を説明する。

【0088】

まず、時刻  $t_{01}$  で内部チップイネーブル信号 # I C E 及び内部アドレスバリッド信号 # I A D V が “L” に立ち下がり、アドレスバッファ13が活性状態となり、半導体記憶装置が動作状態となる。

【0089】

そして、時刻  $t_{02}$  で、内部アドレス I A D  $< 7 : 2 >$  のアドレス遷移が A T D 回路部 14 によって検出され、アドレス遷移検出信号 # A T D 1 及び # A T D 3 が “L” に立ち下がり、同時にセンス信号 # S S の “L” 立ち下がり、ラッチ信号 S L 2 の “H” 立ち上がりが生じる。

【0090】

このときの内部アドレス I A D  $< 2 >$  を “0” とすると、アドレス遷移検出信号 # A T D 1 の “L” 立ち下がりをトリガとして、内部アドレス I A D  $< 2 >$  が反転処理アドレス R A D  $< 2 >$  としてアドレスラッチ回路 10 から出力される。

【0091】

また、上記動作と並行して、Xデコーダ8は内部アドレス I A D  $< 7 : 5 >$  に基づき X 選択信号 S X を出力し、Yデコーダ9は内部アドレス I A D  $< 4 : 3 >$  及び反転処理アドレス R A D  $< 2 >$  に基づき Y 選択信号 S Y を出力する。そして、メモリセルアレイ1から X 選択信号 S X によって選択されたメモリセルの記憶データが 512ビットのメインビット線 M B a に読み出され、Y選択信号 S Y に基づき Y ゲート2により選択された 64ビットのデータ（第1のメモリセル情報群）がセンスアンプ3に付与される。

【0092】

センスアンプ3はセンス信号 # S S の “L” 立ち下がりにより活性状態となり、センスアンプ動作を行い、時刻  $t_{02}$  から時間 T S 経過後の時刻  $t_{03}$  に付与された 64ビットのデータのセンス結果 (D 0 x x) が現れる。その後、センス信号 # S S が “H” に立ち上がる。

【0093】

その後、時刻  $t_{04}$  にラッチ信号 S L 1 が “H” に立ち上ると、これをトリガとしてラッチ信号 S L 2 の “H” 立ち上がりが生じる。センスアンプ3のセンス結果がセンスデータ S D としてセンスデータ用ラッチ4にラッチされ、センスデータ S D がページデータ P D (D 0 x x) としてページデータ用ラッチ5にラッチされる。

【0094】

その結果、ページデータ用ラッチ5にラッチされたページデータ P D は、セレクタ回路 6 によって、内部アドレス I A D  $< 1 : 0 >$  によって最初に指定されるアドレスに対応するページ選択データ P S D (D 0 0 0) が出力バッファ7を介して外部データ D O として出力される。

【0095】

このように、センスアンプ3によるセンスアンプ動作が必要なため、最初の外部データ D O (D 0 0 0) が得られるのは、時刻  $t_{01}$  ~ 時刻  $t_{04}$  間の時間を要する。

【0096】

その後、ページデータ用ラッチ5にラッチされたページデータ P D は、セレクタ回路 6 により、内部アドレス I A D  $< 1 : 0 >$  によって指定される順に上述した “D 0 0 0” 以降も、“D 0 0 1” “D 0 1 0” “D 0 1 1” の順に選択された後、出力バッファ7により外部データ D O として連続的に出力するページモード読み出し出力が行われる。すなわち、時刻  $t_{04}$  以降、4ワード分のデータが連続して読み出されることになる。

【0097】

10

20

30

40

50

一方、時刻  $t_{04}$  のラッチ信号  $SL_1$  の “H” 立ち上がりから、遅延回路  $4_7$  による遅延時間経過後の時刻  $t_{05}$  に反転指示信号 #  $SR$  の “L” 立ち下がる。この時刻  $t_{05}$ において、アドレスラッチ回路  $1_0$  から、内部アドレス  $IAD < 2 >$  の反転信号が反転処理アドレス  $RAD < 2 >$  として出力させることにより、上位アドレスの所定ビットである反転処理アドレス  $RAD < 2 >$  を “0” から “1” 擬似的（一時的）に反転するビット反転処理が実行される。なお、ここでいう擬似的に反転するとは、時刻  $t_{05}$  ~ 時刻  $t_{08}$  までの一時的な期間において、内部アドレス  $IAD < 2 >$  の “1” を反転させて反転処理アドレス  $RAD < 2 >$  を得ていることを意味する。

#### 【0098】

その結果、反転処理アドレス  $RAD < 2 >$  のアドレス遷移によって変更された  $Y$  選択信号  $SY$  に基づき、 $Y$  ゲート  $2$  により選択された新たな  $64$  ビットのメモリセル情報（第  $2$  のメモリセル情報群）のセンスアンプ  $3$  への付与が速やかに行われる。 10

#### 【0099】

そして、反転処理アドレス  $RAD < 2 >$  のアドレス遷移をトリガとしてアドレス遷移検出信号 #  $ATD_3$  が “L” に立ち下がり、センス信号 #  $SS$  が “L” に立ち下がり、センスアンプ  $3$  が再び活性状態となる。

#### 【0100】

そして、時刻  $t_{05}$  から時間  $T_S$  経過後の時刻  $t_{06}$  に、反転処理アドレス  $RAD < 2 >$  が “1” の場合の（第  $2$  のメモリセル情報群に基づく）新たなセンス結果（ $D_{1xxx}$ ）が現れる。その後、センス信号 #  $SS$  が “H” に立ち上がる。 20

#### 【0101】

時刻  $t_{06}$  から所定時間経過後の時刻  $t_{07}$  において、ラッチ信号  $SL_1$  が “H” に立ち上がり、センスデータ用ラッチ  $4$  にラッチされるセンスデータ  $SD$  が  $D_{0xxx}$ （第  $1$  のメモリセル情報群のデータ）から  $D_{1xxx}$ （第  $2$  のメモリセル情報群のデータ）に変更される。

#### 【0102】

このように、ラッチ信号  $SL_1$  はアドレス遷移検出信号 #  $ATD_3$  の “L” 立ち下がりに応答して、所定時間経過後 “H” となりため、反転処理アドレス  $RAD < 2 >$  のアドレス遷移後のセンスアンプ  $3$  より得られるセンス結果を速やかにラッチすることができる。 30

#### 【0103】

このとき、ラッチ信号  $SL_2$  は反転処理アドレス  $RAD < 2 >$  のアドレス遷移に關係なく “L” を維持するため、ページデータ用ラッチ  $5$  のページデータ  $PD$  が更新されることなく上述したページモード読み出し出力が支障無く行われる。

#### 【0104】

このように、ラッチ信号  $SL_1$  及び  $SL_2$  のラッチタイミングに連動してビット反転処理を実行する反転指示信号 #  $SR$  を生成することにより、時刻  $t_{04}$  以降において、ページデータ用ラッチ  $5$ 、セレクタ回路  $6$  及び出力バッファ  $7$  による前半の  $4$  ワード分のデータ（第  $1$  のメモリセル情報群に基づくデータ）のページモード読み出し動作に並行して、メモリセルアレイ  $1$ 、 $Y$  ゲート  $2$ 、センスアンプ  $3$ 、及びセンスデータ用ラッチ  $4$  による後半の  $4$  ワード分のデータ（第  $2$  のメモリセル情報群に基づくデータ）のセンス動作を行うことができる。 40

#### 【0105】

そして、 $D_{000} \sim D_{003}$  の  $4$  ワード分の外部データ  $D_0$  の出力が終える時刻  $t_{08}$  に内部アドレス  $IAD < 2 >$  がアドレス変化（“0” ~ “1”）する。この時刻  $t_{08}$  時点において、既にセンスデータ用ラッチ  $4$  には次の読み出しだ  $(D_{1xxx})$  がラッチされている。

#### 【0106】

内部アドレス  $IAD < 2 >$  のアドレス遷移検出によるアドレス遷移検出信号 #  $ATD_1$  の “L” 立ち下がりに伴い、反転処理アドレス  $RAD < 2 >$  として内部アドレス  $IAD < 2 >$  が出力されるが、時刻  $t_{05}$  の際に既に反転処理アドレス  $RAD < 2 >$  は “1” とな 50

っているため、結果的に反転処理アドレス R A D < 2 > は “ 1 ” を維持することになる。

【 0 1 0 7 】

このとき、ラッチ信号 S L 2 の “ H ” 立ち上がりが生じるため、センスデータ S D がページデータ用ラッチ 5 にラッチされ、ページデータ P D が更新されるが、前述したように、時刻 t 0 8 には外部データ D O から “ D 0 0 0 ” “ D 0 0 1 ” “ D 0 1 0 ” “ D 0 1 1 ” のデータが既に読み出されているため、ページモード読み出し動作に支障は来さない。

【 0 1 0 8 】

そして、時刻 t 0 8 でページデータ用ラッチ 5 にラッチされたページデータ P D は、セレクタ回路 6 によって、内部アドレス I A D < 1 : 0 > によって指定される順に “ D 1 0 0 ” “ D 1 0 1 ” “ D 1 1 0 ” “ D 1 1 1 ” の順に選択された後、出力バッファ 7 より外部データ D O として連続的に出力するページモード読み出し出力が行われる。すなわち、時刻 t 0 4 から 8 ワードの外部データ D O ( 第 1 及び第 2 のメモリセル情報群に基づくデータ ) が “ D 0 0 0 ” “ D 0 0 1 ” “ D 0 1 0 ” “ D 0 1 1 , “ D 1 0 0 ” “ D 1 0 1 ” “ D 1 1 0 ” “ D 1 1 1 ” の順で連続的に読み出されることになる。

【 0 1 0 9 】

なお、時刻 t 0 8 後の時刻 t 0 9 にラッチ信号 S L 1 及びラッチ信号 S L 2 の “ H ” 立ち上がりにより、センスアンプ 3 によるセンス結果でセンスデータ用ラッチ 4 及びページデータ用ラッチ 5 の内容が更新されるが、センス結果は時刻 t 0 7 時点の内容と同様の ( D 1 x x ) であるため、実質的にはページデータ用ラッチ 5 のラッチ内容に変化はないため、動作に支障を来すことはない。

【 0 1 1 0 】

このように、アドレスラッチ回路 1 0 、 A T D 回路部 1 4 、アドレス反転制御回路 1 5 、及びセンス制御回路 1 6 等から構成されるページモード制御回路によって以下の動作が行われる。

【 0 1 1 1 】

前半 4 ワードのアドレス ( 第 1 のアドレス ) を規定する内部アドレス I A D < 7 : 3 > 及び反転処理アドレス R A D < 2 > に基づきメモリセルアレイ 1 から読み出された第 1 のメモリセル情報群が、センスアンプ 3 及びセンスデータ用ラッチ 4 を介して、ページデータ P D としてページデータ用ラッチ 5 にラッチされた後、反転処理アドレス R A D < 2 > を擬似的に反転させるビット反転処理を行い前半 4 ワードのアドレスに続く後半 4 ワードのアドレス ( 第 2 のアドレス ) をアドレスラッチ回路 1 0 から発生させる。

【 0 1 1 2 】

そして、第 1 のメモリセル情報群に基づくページモード読み出し期間中に、後半 4 ワードのアドレスを規定する上位アドレス信号に基づきメモリセルアレイ 1 から読み出された第 2 のメモリセル情報群を、センスアンプ 3 を介して 6 4 ビット構成のセンスデータ S D としてセンスデータ用ラッチ 4 に格納させる。

【 0 1 1 3 】

その後、上記第 1 のメモリセル情報群に関するページモード読み出し期間終了後、センスデータ用ラッチ 4 に格納された上記第 2 のメモリセル情報群に基づく 6 4 ビット構成のセンスデータ S D を、ページデータ P D としてページデータ用ラッチ 5 にラッチさせることにより、第 1 のメモリセル情報群に基づくページモード読み出し期間後に第 2 のメモリ

【 0 1 1 4 】

その結果、従来レベルのハードウェア構成としては、ページ長が 4 ワード構成のページモード読み出し機能に抑えながら、実質的にはページ長が 8 ワード構成のページモード読み出し動作を実現することができる。

【 0 1 1 5 】

したがって、実施の形態 1 の半導体記憶装置は、同時に活性化するセンスアンプ 3 のビット数及びラッチ 4 , 5 の記憶容量を 4 ワードページ分に抑えながら、8 ワードページ分のページモード読み出し機能を有することになるため、ページモード読み出し時のピーク電流及びページモード読み出し機能を実現する回路のレイアウト面積の増大を最小限に抑

10

20

30

40

50

えることができる。

【0116】

本実施の形態では、前半の4ワード分の外部へのページモード読み出し期間中に、後半の4ワード分のデータを読み出している。後半の4ワード分のセンスデータSDが確定すれば直ちに後半の4ワード分の外部へのページモード読み出し期間に移行することも考えられる。

【0117】

しかしながら、前半の4ワード分の外部へのページモード読み出し動作が確実に行われることを保証するため、前半の4ワード分の外部へのページモード読み出し動作が完了した時刻t08にラッチ信号SL2を“H”にして、後半の4ワード分の外部へのページモード読み出し期間に移行する方が適切である。

【0118】

なお、本実施の形態では、内部アドレスIAD<1:0>の出力順が“00”, “01”, “10”, “11”的場合を示したが、この順は任意である。

【0119】

<実施の形態2>

図15はこの発明の実施の形態2である半導体記憶装置のメモリセルアレイ周辺部の構成を示すブロック図である。同図において、内部アドレスIAD<7:5>によってX選択信号SXが選択され、内部アドレスIAD<4:3>及び反転処理アドレスRAD<2>によりY選択信号SYが選択され、X選択信号SX及びY選択信号SYによって32ビット(所定数)の多値データが読み出され、ページアドレスとして2ビットの内部アドレスIAD<1:0>が用いられる4ワードページの場合が示されている。

【0120】

メモリセルアレイ21はマトリクス状に配置され、各々が4値の多値情報が記憶可能な複数のメモリセルを有し、X選択信号SXに基づき、複数のメモリセルのうちより選択されたメモリセルからの記憶データを、総計256本のメインビット線MBbそれぞれに読み出す。

【0121】

Yゲート22はY選択信号SYに基づき、256本のメインビット線MBbのうち32本(所定数)を選択してセンスアンプ23に電気的に接続する。

【0122】

センスアンプ23は、センス信号#SS2が“L”的とき活性状態となり、活性状態時にYゲート22より選択された、32本のメインビット線MBbに現れる記憶データを検知・増幅するセンスアンプ動作を実行する。センスアンプ動作はセンスアンプ期間中に連続して行う第1及び第2のセンスアンプ動作からなり、センス信号#SS1が“L”的ときに行われる第1のセンスアンプ動作により上記記憶データの上位ビット情報が得られ、センス信号#SS1が“H”的時に行われる第2のセンスアンプ動作により上記記憶データの下位ビット情報が得られる。センスアンプ23より得られた32単位のセンス結果(上位ビット情報あるいは下位ビット情報)はセンスデータ用ラッチ24に付与される。

【0123】

センスデータ用ラッチ24は第1センス用ラッチ部24a及び第2センス用ラッチ部24bにより構成される。第1センス用ラッチ部24aは、ラッチ信号SL11が“H”的とき活性状態となり、活性状態時にセンスアンプ23により増幅された32個の上位ビット情報をセンスデータSD1としてラッチする。第2センス用ラッチ部24bは、ラッチ信号SL12が“H”的とき活性状態となり、活性状態時にセンスアンプ23により増幅された32個の下位ビット情報をセンスデータSD2としてラッチする。したがって、センスデータ用ラッチ24は $32 \times 2 = 64$ ビット(所定ビット数)のセンスデータSD1+SD2をラッチすることになる。

【0124】

以降、第1センス用ラッチ部24a及び第2センス用ラッチ部24bは、それぞれラッ

10

20

30

40

50

チ信号 S L 1 1 及び S L 1 2 が再び “ H ” になるまでラッチしたセンスデータ S D 1 , S D 2 を保持する。したがって、センスアンプ 2 3 が非活性状態になっても、センスデータ用ラッチ 2 4 にラッチされたセンスデータ S D 1 , S D 2 は保持される。

【 0 1 2 5 】

ページデータ用ラッチ 2 5 は、第 1 センス用ラッチ部 2 5 a 及び第 2 センス用ラッチ部 2 5 b により構成され、ラッチ信号 S L 2 0 が “ H ” のとき活性状態となり、活性状態時に、センスデータ用ラッチ 2 4 に格納されたセンスデータ S D 1 及び S D 2 を第 1 及び第 2 のセンス用ラッチ部 2 5 a 及び 2 5 b にラッチする。そして、第 1 センス用ラッチ部 2 5 a にラッチされたデータが第 1 ページデータ P D 1 として出力され、第 2 センス用ラッチ部 2 5 b にラッチされたデータが第 2 ページデータ P D 2 として出力される。第 1 ページデータ P D 1 及び第 2 ページデータ P D 2 はそれぞれ 4 個の部分ページデータに分類可能である。

【 0 1 2 6 】

セレクタ回路 2 6 は第 1 センス用セレクト部 2 6 a 及び第 2 センス用セレクト部 2 6 b から構成され、第 1 センス用セレクト部 2 6 a 及び第 2 センス用セレクト部 2 6 b は、共通に入力される内部アドレス I A D < 1 : 0 > で選択されるアドレスに基づき、ページデータ P D 1 , P D 2 から 8 ビットのページ選択データ P S D 1 , P S D 2 をそれぞれ出力する。すなわち、センスアンプ 2 3 , センスデータ用ラッチ 2 4 、ページデータ用ラッチ 2 5 及びセレクタ回路 2 6 による従来レベルのハードウェア構成としては、ページ長が 4 ワード構成の多値データのページモード読み出し機能を有している。

【 0 1 2 7 】

出力バッファ 2 7 は第 1 センス用バッファ部 2 7 a 及び第 2 センス用バッファ部 2 7 b より構成され、第 1 及び第 2 のセンス用バッファ部 2 7 a 及び 2 7 b は、ページ選択データ P S D 1 及び P S D 2 をバッファリングし、第 1 及び第 2 の外部データ D O 1 及び D O 2 として出力し、第 1 外部データ D O 1 及び第 2 外部データ D O 2 からなる外部データ D O 1 2 が外部データとして最終的に出力される。

【 0 1 2 8 】

X デコーダ 2 8 は実施の形態 1 の X デコーダ 8 同様、内部アドレス I A D < 7 : 5 > に基づき X 選択信号 S X を出力し、Y デコーダ 2 9 は実施の形態 1 の Y デコーダ 9 同様、内部アドレス I A D < 4 : 3 > 及び反転処理アドレス R A D < 2 > に基づき Y 選択信号 S Y を出力する。したがって、Y ゲート 2 2 、X デコーダ 2 8 及び Y デコーダ 2 9 によってメモリセルアレイ 2 1 から 3 2 単位の多値メモリセル情報を読み出す読み出し制御部が構成される。

【 0 1 2 9 】

なお、内部アドレス供給部の構成は、図 2 で示した実施の形態 1 と同様であるため、説明を省略する。

【 0 1 3 0 】

図 1 6 は図 1 5 で示したメモリセルアレイ 2 1 の周辺部に対し各種制御信号を出力するページモード制御回路の主要部の構成を示す回路図である。同図において、A T D 回路部 1 7 は図 4 で示した実施の形態 1 の A T D 回路部 1 4 と同様、内部チップイネーブル信号 # I C E 、内部アドレス I A D < 7 : 2 > 及び反転処理アドレス R A D < 2 > を受け、アドレス遷移検出信号 # A T D 1 及び # A T D 3 を出力する。

【 0 1 3 1 】

センス制御回路 1 9 はアドレス遷移検出信号 # A T D 3 に基づきセンス信号 # S S 1 及び # S S 2 並びにラッチ信号 S L 1 1 及び S L 1 2 を出力する。

セル情報群に基づくページモード読み出し期間を連続的に設定する。

【 0 1 3 2 】

図 1 7 はセンス制御回路 1 9 の内部構成を示す回路図である。同図に示すように、3 段直列に接続される遅延ユニット 4 1 ~ 4 3 のうち初段の遅延ユニット 4 1 はアドレス遷移検出信号 # A T D 3 を受け、最終段の遅延ユニット 4 3 の出力がセンス信号 # S S 1 とな

10

20

30

40

50

る。3段直列に接続されるインバータG46～G48のうち初段のインバータG46がセンス信号#SS1を受ける。NANDゲートG112は一方入力にセンス信号#SS1を他方入力にインバータG48の出力を受ける。NANDゲートG112の出力はインバータG49を介してラッチ信号SL11として出力される。

【0133】

さらに、3段直列に接続される遅延ユニット44～46のうち初段の遅延ユニット44はセンス信号#SS1を受け、最終段の遅延ユニット46の出力がセンス信号#SS2となる。3段直列に接続されるインバータG50～G52のうち初段のインバータG50がセンス信号#SS2を受ける。NANDゲートG113は一方入力にセンス信号#SS2を他方入力にインバータG52の出力を受ける。NANDゲートG113の出力はインバータG53を介してラッチ信号SL12として出力される。なお、遅延ユニット41～46の内部構成は、図10で示した実施の形態1の遅延ユニット36～38の内部構成と同様である。

【0134】

このような構成において、センス信号#SS1及び#SS2は、アドレス遷移検出信号#ATD3の“L”立ち下がりをトリガとして共に速やかに“L”に立ち下がり、アドレス遷移検出信号#ATD3の“H”立ち上がりをトリガとし、遅延ユニット41～43及び遅延ユニット41～46による遅延時間後にそれぞれ“H”に立ち上がる信号として出力される。

【0135】

一方、ラッチ信号SL11及びSL12は、通常はNANDゲートG112及びG113の一方の入力が“L”的ため“L”的信号となり、センス信号#SS1及び#SS2の“H”立ち上がり時から所定期間（インバータG46～G48及びインバータG50～52の信号伝搬遅延時間）のみそれぞれ“H”パルスを発生する信号となる。

【0136】

図16に戻って、アドレス反転制御回路18は、アドレス遷移検出信号#ATD1及びラッチ信号SL12に基づき、反転指示信号#SR及びラッチ信号SL20を出力する。内部構成は、入力信号となるラッチ信号SL1がラッチ信号SL12に置き換わり、出力信号となるラッチ信号SL2がラッチ信号SL20に置き換わった点を除き、図11で示して実施の形態1のアドレス反転制御回路15と同様である。

【0137】

上述したアドレスラッチ回路10（実施の形態1と同じ）、ATD回路部17、アドレス反転制御回路18及びセンス制御回路19等により、実施の形態1と同様なページモード制御が可能なページモード制御回路を構成する。

【0138】

図18はこの発明の実施の形態2による半導体記憶装置のページモード読み出し動作を示すタイミング図である。以下、同図を参照して実施の形態2のページモード読み出し動作を説明する。

【0139】

まず、時刻t11で内部チップイネーブル信号#ICE及び内部アドレスバリッド信号#IADVが“L”に立ち下がり、アドレスバッファ13が活性状態となり、半導体記憶装置が動作状態となる。

【0140】

そして、時刻t12で、内部アドレスIAD<7:2>のアドレス遷移がATD回路部17によって検出され、アドレス遷移検出信号#ATD1及び#ATD3が“L”に立ち下がり、同時にセンス信号#SS2（#SS1）の“L”立ち下がり、ラッチ信号SL20の“H”立ち上がりが生じる。

【0141】

このときの内部アドレスIAD<2>を“0”とすると、アドレス遷移検出信号#ATD1の“L”立ち下がりをトリガとして、内部アドレスIAD<2>が反転処理アドレス

10

20

30

40

50

R A D < 2 > としてアドレスラッチ回路 1 0 から出力される。

【 0 1 4 2 】

また、上記動作と並行して、X デコーダ 2 8 は内部アドレス I A D < 7 : 5 > に基づき X 選択信号 S X を出力し、Y デコーダ 2 9 は内部アドレス I A D < 4 : 3 > 及び反転処理アドレス R A D < 2 > に基づき Y 選択信号 S Y を出力する。そして、メモリセルアレイ 2 1 から X 選択信号 S X によって選択されたメモリセルの記憶データが 2 5 6 ビットのメインビット線 M B b に読み出され、Y 選択信号 S Y に基づき Y ゲート 2 2 により選択された 3 2 単位の多値データがセンスアンプ 2 3 に付与される。

【 0 1 4 3 】

センスアンプ 2 3 はセンス信号 # S S 2 の “ L ” 立ち下がりにより活性状態となり、第 1 のセンスアンプ動作を行い、時刻 t 1 2 から時間 T S 1 経過後の時刻 t 1 3 に、Y ゲート 2 2 より付与された 3 2 単位のデータの上位ビット情報のセンス結果 ( D 0 x x F ) が現れ、このとき、ラッチ信号 S L 1 1 の “ H ” 立ち上がりによりセンス結果が第 1 センスデータ S D 1 としてラッチされる。

【 0 1 4 4 】

時刻 t 1 3 とほぼ同時にセンス信号 # S S 1 が “ H ” に立ち上がり、センスアンプ 2 3 は第 2 のセンスアンプ動作を開始し、時刻 t 1 3 から時間 T S 2 経過後の時刻 t 1 4 に、Y ゲート 2 2 より付与された 3 2 単位のデータの下位ビット情報のセンス結果 ( D 0 x x S ) が現れ、このとき、第 1 ラッチ信号 S L 1 2 の “ H ” 立ち上がりによりセンス結果が第 2 センスデータ S D 2 としてラッチされる。

【 0 1 4 5 】

時刻 t 1 4 にラッチ信号 S L 1 2 が “ H ” に立ち上ると、これをトリガとして反転指示信号 # S R の “ L ” 立ち下がり及びラッチ信号 S L 2 0 の “ H ” 立ち上がりが生じる。その結果、ページデータ用ラッチ 2 5 における第 1 及び第 2 センス用ラッチ部 2 5 a 及び 2 5 b の第 1 及び第 2 のページデータ P D 1 及び P D 2 として、第 1 及び第 2 のセンスデータ S D 1 及び S D 2 がラッチされる。

【 0 1 4 6 】

そして、ページデータ用ラッチ 2 5 にラッチされたページデータ P D 1 及び P D 2 は、セレクタ回路 2 6 によって、内部アドレス I A D < 1 : 0 > によって最初に指定されるアドレスに対応するページ選択データ P S D ( D 0 0 0 ( D 0 0 0 F , D 0 0 0 S ) ) が出力バッファ 2 7 を介して外部データ D O 1 2 として出力される。

【 0 1 4 7 】

このように、センスアンプ 2 3 によるセンスアンプ動作が必要なため、最初の外部データ D O 1 2 ( D 0 0 0 ) が得られるのは、時刻 t 1 1 ~ 時刻 t 1 4 間の時間を要する。

【 0 1 4 8 】

その後、ページデータ用ラッチ 2 5 にラッチされたページデータ P D は、セレクタ回路 2 6 により、内部アドレス I A D < 1 : 0 > によって指定される順に上述した “ D 0 0 0 ” 以降も、“ D 0 0 1 ( D 0 0 1 F , D 0 0 1 S ) ” “ D 0 1 0 ( D 0 1 0 F , D 0 1 0 S ) ” “ D 0 1 1 ( D 0 1 1 F , D 0 1 1 S ) ” の順に選択された後、出力バッファ 2 7 により外部データ D O 1 2 として連続的に出力するページモード読み出し出力が行われる。すなわち、時刻 t 1 4 以降、4 ワード分のデータが連続して読み出されることになる。

【 0 1 4 9 】

一方、時刻 t 1 4 から少し遅れた時刻 t 1 5 において反転指示信号 # S R の “ L ” 立ち下がりにより、内部アドレス I A D < 2 > の反転信号が反転処理アドレス R A D < 2 > として出力されることにより、反転処理アドレス R A D < 2 > が “ 0 ” から “ 1 ” に反転される。

【 0 1 5 0 】

その結果、反転処理アドレス R A D < 2 > のアドレス遷移によって変更された Y 選択信号 S Y に基づき、Y ゲート 2 2 により選択された新たな 3 2 単位の多値データがセンスアンプ 2 3 に付与される。

10

20

30

40

50

## 【0151】

そして、反転処理アドレス R A D < 2 > のアドレス遷移をトリガとしてアドレス遷移検出信号 # A T D 3 が “ L ” に立ち下がり、第 2 のセンス信号 # S S 2 が “ L ” に立ち下がり、センスアンプ 2 3 が再び活性状態となり、第 1 のセンスアンプ動作を開始する。

## 【0152】

そして、時刻 t 1 5 から時間 T S 1 経過後の時刻 t 1 6 に、反転処理アドレス R A D < 2 > が “ 1 ” の場合の新たなセンス結果 ( D 1 x x F ) が現れる。このとき、ラッチ信号 S L 1 1 の “ H ” 立ち上がりによりセンス結果が第 1 センスデータ S D 1 としてラッチされる。すなわち、第 1 センス用ラッチ部 2 4 a にラッチされる第 1 センスデータ S D 1 が D 0 x x F から D 1 x x F に変更される。

10

## 【0153】

時刻 t 1 6 とほぼ同時に、センス信号 # S S 1 が “ H ” に立ち上がり、センスアンプ 2 3 は第 2 のセンスアンプ動作を開始する。センス信号 # S S 1 の “ H ” 立ち上がり後、時間 T S 2 経過後の時刻 t 1 7 に、Y ゲート 2 2 より付与された 3 2 単位のデータの下位ビット情報のセンス結果 ( D 1 x x S ) が現れ、このとき、ラッチ信号 S L 1 2 の “ H ” 立ち上がりによりセンス結果が第 2 センスデータ S D 2 としてラッチされる。すなわち、第 2 センス用ラッチ部 2 4 b にラッチされる第 2 センスデータ S D 2 が D 0 x x S から D 1 x x S に変更される。

## 【0154】

このとき、ラッチ信号 S L 2 0 は “ L ” を維持するため、ページデータ用ラッチ 2 5 のページデータ P D 1 及び P D 2 が更新されることなく上述したページモード読み出し出力が支障無く行われる。

20

## 【0155】

このように、時刻 t 1 4 以降において、ページデータ用ラッチ 2 5、セレクタ回路 2 6 及び出力バッファ 2 7 による前半の 4 ワード分のデータの外部データ D O 1 2 としての出力動作に並行して、メモリセルアレイ 2 1 、Y ゲート 2 2 、センスアンプ 2 3 、及びセンスデータ用ラッチ 2 4 による後半の 4 ワード分のデータのセンス動作が行われる。

## 【0156】

そして、D 0 0 0 ~ D 0 0 3 の 4 ワード分の外部データ D O 1 2 の出力が終える時刻 t 1 8 に内部アドレス I A D < 2 > がアドレス変化 ( “ 0 ” “ 1 ” ) する。この時刻 t 1 8 時点において、既にセンスデータ用ラッチ 2 4 には次の読み出しデータ ( D 1 x x ( D 1 x x F , D 1 x x S ) ) がラッチされている。

30

## 【0157】

内部アドレス I A D < 2 > のアドレス遷移検出によるアドレス遷移検出信号 # A T D 1 の “ L ” 立ち下がりに伴い、反転処理アドレス R A D < 2 > として内部アドレス I A D < 2 > が出力されるが、時刻 t 1 5 の際に既に反転処理アドレス R A D < 2 > は “ 1 ” となっているため、結果的に反転処理アドレス R A D < 2 > は “ 1 ” を維持することになる。

## 【0158】

このとき、ラッチ信号 S L 2 0 の “ H ” 立ち上がりが生じるため、センスデータ S D 1 , S D 2 がページデータ用ラッチ 2 5 にラッチされ、ページデータ P D 1 , P D 2 が更新されるが、前述したように、時刻 t 1 8 には外部データ D O 1 2 から “ D 0 0 0 ” “ D 0 0 1 ” “ D 0 1 0 ” “ D 0 1 1 ” のデータが既に読み出されているため、ページモード読み出し動作に支障は来さない。

40

## 【0159】

そして、時刻 t 1 8 でページデータ用ラッチ 2 5 にラッチされたページデータ P D 1 , P D 2 は、セレクタ回路 2 6 によって、内部アドレス I A D < 1 : 0 > によって指定される順に “ D 1 0 0 ( D 1 0 0 F , D 1 0 0 S ) ” , “ D 1 0 1 ( D 1 0 1 F , D 1 0 1 S ) ” , “ D 1 1 0 ( D 1 1 0 F , D 1 1 0 S ) ” , “ D 1 1 1 ( D 1 1 1 F , D 1 1 1 S ) ” の順に選択された後出力バッファ 2 7 により外部データ D O 1 2 として連続的に出力するページモード読み出し出力が行われる。すなわち、時刻 t 1 4 から 8 ワードの外部デ

50

ータ D O 1 2 が “ D 0 0 0 ” “ D 0 0 1 ” “ D 0 1 0 ” “ D 0 1 1 , “ D 1 0 0 ” “ D 1 0 1 ” “ D 1 1 0 ” “ D 1 1 1 ” の順で連続的に読み出されることになる。

【 0 1 6 0 】

なお、時刻 t 1 8 後の時刻 t 1 9 における第 1 ラッチ信号 S L 1 1 の “ H ” 立ち上がりにより第 1 センス用ラッチ部 2 4 a の内容が更新され、時刻 t 2 0 におけるラッチ信号 S L 1 2 及びラッチ信号 S L 2 0 の “ H ” 立ち上がりにより、第 2 センス用ラッチ部 2 4 b 及びページデータ用ラッチ 2 5 の内容が更新されるが、センス結果は時刻 t 1 7 時点の内容と同様の ( D 1 x x ( D 1 x x F , D 1 x x S ) ) であるため、実質的にはページデータ用ラッチ 2 5 のラッチ内容に変化はないため、動作に支障を来すことはない。

【 0 1 6 1 】

このように、実施の形態 2 の半導体記憶装置は、ラッチ信号 S L 1 2 及びラッチ信号 S L 2 0 の “ H ” 立ち上りによってページデータ用ラッチ 2 5 へのラッチ完了時を基準として、反転指示信号 # S R を “ L ” の活性状態とすることにより、前半のページデータのページモード読み出し機能に支障無く、かつ後半のページデータのセンス動作を実行している。

【 0 1 6 2 】

その結果、実施の形態 2 の半導体記憶装置は、実施の形態 1 と同様、同時に活性化するセンスアンプ 2 3 のビット数及びラッチ 2 4 , 2 5 の記憶容量を 4 ワードページ分に抑えながら、8 ワードページ分のページモード読み出し機能を有することになるため、ページモード読み出し時のピーク電流及びページモード読み出し機能を実現する回路のレイアウト面積の増大を最小限に抑えることができる。

【 0 1 6 3 】

なお、実施の形態 2 では、実施の形態 1 同様、内部アドレス I A D < 1 : 0 > の出力順が “ 0 0 ” , “ 0 1 ” , “ 1 0 ” , “ 1 1 ” の場合を示したが、この順は任意である。

【 0 1 6 4 】

加えて、実施の形態 2 の半導体記憶装置は、3 ビット以上の多値情報を記憶するメモリセルから構成されるメモリセルアレイ 2 1 に対し、上記した効率的なページモード読み出し機能を有するという効果を奏している。

【 0 1 6 5 】

なお、実施の形態 2 では多値情報として 4 値記憶の場合を示したが、3 値、5 値以上の多値記憶に応用することができる。例えば、8 値の場合は各構成部の個数 m を現在の “ 2 ” から “ 3 ” ( ( 2 <sup>3</sup> ) = 8 ) に拡張することにより実現することができる。

【 0 1 6 6 】

＜実施の形態 3 ＞

図 1 9 はこの発明の実施の形態 3 である半導体記憶装置のメモリセルアレイ周辺部の構成を示すブロック図である。同図において、構成要素 1 ~ 9 は実施の形態 1 で示した構成と同様であり、同一符号を付している。

【 0 1 6 7 】

スペアメモリセルアレイ 5 1 は複数のスペアメモリセルを有し、X 選択信号 S X に基づき、複数のスペアメモリセルのうちより選択されたスペアメモリセルからの記憶データ（スペア情報）を、総計 8 本のメインビット線 M B s それぞれに読み出す。

【 0 1 6 8 】

Y ゲート 5 2 はスペア Y 選択信号 S S Y に基づき、8 本のメインビット線 M B s のうち 1 本（所定のスペア数）を選択してセンスアンプ 3 に電気的に接続する。

【 0 1 6 9 】

センスアンプ 5 3 ( 置換用センスアンプ ) は、センス信号 # S S が “ L ” のとき活性状態となり、活性状態時に Y ゲート 5 2 より選択された 1 本のメインビット線 M B s に現れる記憶データを検知・增幅するセンスアンプ動作を実行する。

【 0 1 7 0 】

センスデータ用ラッチ 5 4 ( スペアセンス用ラッチ ) は、ラッチ信号 S L 1 が “ H ” の

10

20

30

40

50

とき活性状態となり、活性状態時にセンスアンプ 53 により増幅された 1 本（所定スペアビット数）のメインビット線 M B s 上の信号をスペアセンスデータ S S D 1 としてラッチする。以降、ラッチ信号 S L 1 が再び“H”になるまでラッチしたスペアセンスデータ S S D 1 を保持する。したがって、センスアンプ 53 が非活性状態になっても、センスデータ用ラッチ 54 にラッチされたスペアセンスデータ S S D 1 は保持される。

【0171】

ページデータ用ラッチ 55（スペアデータ用ラッチ）は、ラッチ信号 S L 2 が“H”的とき活性状態となり、活性状態時にセンスデータ用ラッチ 54 に格納されたスペアセンスデータ S S D 1 をスペアデータ S S D 2 としてラッチする。

【0172】

図 20 はスペア Y 選択信号 S S Y を発生するスペア制御回路 20 の構成を示すブロック図である。同図に示すように、スペア制御回路 20 は内部アドレス I A D < 4 : 3 > 及び反転処理アドレス R A D < 2 > に基づきスペア Y 選択信号 S S Y を決定し出力する。また、スペア Y 選択信号 S S Y より選択されたデータにおける置換情報を示す冗長置換情報 R D を出力する。

【0173】

したがって、X デコーダ 8（実施の形態 1 と同じ）、スペア制御回路 20 及び Y ゲート 52 によりスペアメモリセルアレイ 51 からスペア情報を読み出すスペア読み出し制御部を構成することになる。

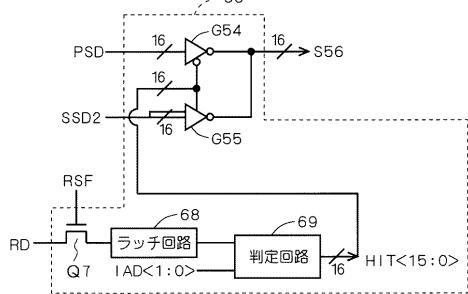

【0174】

スワップ回路 56（置換実行回路）はページ選択データ P S D を受け、冗長置換情報 R D 及び冗長情報シフト信号 R S F（置換情報取り込み制御信号）に規定された指示に従い、置換が必要な場合、ページ選択データ P S D のうちの所定ビットデータを置換用 1 ビットデータであるスペアデータ S S D 2 に置換して、置換済みページ選択データ S 56 を出力する。

【0175】

出力バッファ 7 は置換済みページ選択データ S 56 をバッファリングして外部データ D O として出力する。

【0176】

図 21 はスワップ回路 56 の内部構成を示す回路図である。同図に示すように、インバータ G 54（実際は 16 個あり、代表的に 1 つを示す）は、ページ選択データ P S D を入力し、インバータ G 55（実際は 16 個あり、代表的に 1 つを示す）はスペアデータ S S D 2 を受ける。すなわち、16 個のインバータ G 55 は全て同じスペアデータ S S D 2 を受ける。

【0177】

一方、ラッチ 68 は N M O S トランジスタ Q 7（実際は 6 個あり、代表的に 1 つを示す）を介して冗長置換情報 R D を受ける。冗長置換情報 R D には 2 ビットのアドレス置換情報 R A < 1 : 0 > と 4 ビットの冗長置換情報 R D < 3 : 0 > からなる 6 ビット情報であり、N M O S トランジスタ Q 7 がオン状態時にラッチ 68 に取り込まれる。

【0178】

N M O S トランジスタ Q 7 はゲートに冗長情報シフト信号 R S F を受ける。したがって、冗長情報シフト信号 R S F が“H”的とき冗長置換情報 R D がラッチ 68 に取り込まれる。判定回路 69 はラッチ 68 の出力と内部アドレス I A D < 1 : 0 > とを受け、置換信号 H I T < 15 : 0 > を出力する。

【0179】

置換信号 H I T < 15 : 0 > は、16 個のインバータ G 54 及び G 55 の反転制御入力及び制御入力に付与される。置換信号 H I T < 15 : 0 > は通常、全て“0”であり、置換が必要な際は所定ビットのみ“1”となる。

【0180】

したがって、通常はページ選択データ P S D がそのまま置換済みページ選択データ S 5

10

20

30

40

50

6をして出力され、置換時はページ選択データP S Dのうち置換信号H I T < 1 5 : 0 >の指示する所定ビットがスペアデータS S D 2に置換されて得られるデータが置換済みページ選択データS 5 6として出力される。

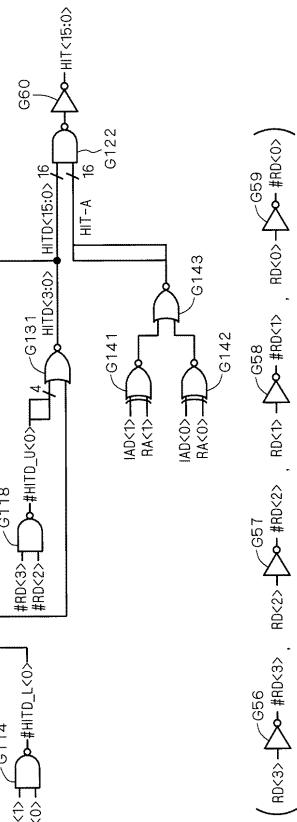

【0181】

図22は判定回路69の内部構成を示す回路図である。同図に示すように、冗長置換情報R D < 3 : 0 >はインバータG 5 6 ~ G 5 9によりそれぞれ反転され、反転冗長置換情報# R D < 3 : 0 >が得られている。

【0182】

N A N DゲートG 1 1 4は一方入力及び他方入力に反転冗長置換情報# R D < 0 >及び反転冗長置換情報# R D < 1 >を受ける。N A N DゲートG 1 1 5は一方入力及び他方入力に冗長置換情報R D < 0 >及び反転冗長置換情報# R D < 1 >を受ける。N A N DゲートG 1 1 6は一方入力及び他方入力に反転冗長置換情報# R D < 0 >及び冗長置換情報R D < 1 >を受ける。N A N DゲートG 1 1 7は一方入力及び他方入力に冗長置換情報R D < 0 >及び冗長置換情報R D < 1 >を受ける。

10

【0183】

N A N DゲートG 1 1 8は一方入力及び他方入力に反転冗長置換情報# R D < 2 >及び反転冗長置換情報# R D < 3 >を受ける。N A N DゲートG 1 1 9は一方入力及び他方入力に冗長置換情報R D < 2 >及び反転冗長置換情報# R D < 3 >を受ける。N A N DゲートG 1 2 0は一方入力及び他方入力に反転冗長置換情報# R D < 2 >及び冗長置換情報R D < 3 >を受ける。N A N DゲートG 1 2 1は一方入力及び他方入力に冗長置換情報R D < 2 >及び冗長置換情報R D < 3 >を受ける。

20

【0184】

N O RゲートG 1 3 1 ~ G 1 3 4は実際には4個存在するが説明の都合上、1ビット代表させて示している。N O RゲートG 1 3 1 ~ G 1 3 4の一方入力にはN A N DゲートG 1 1 4 ~ G 1 1 7の出力であるヒット検出信号# H I T D \_ L < 3 : 0 >が共通に入力される。

【0185】

N O RゲートG 1 3 1の他方入力はN A N DゲートG 1 1 8の出力であるヒット検出信号# H I T D \_ U < 0 >が4ビット分共通に入力され、N O RゲートG 1 3 2の他方入力はN A N DゲートG 1 1 9の出力であるヒット検出信号# H I T D \_ U < 1 >が4ビット分共通に入力され、N O RゲートG 1 3 3の他方入力はN A N DゲートG 1 2 0の出力であるヒット検出信号# H I T D \_ U < 2 >が4ビット分共通に入力され、N O RゲートG 1 3 4の他方入力はN A N DゲートG 1 2 1の出力であるヒット検出信号# H I T D \_ U < 3 >が4ビット分共通に入力される。

30

【0186】

その結果、N O RゲートG 1 3 1 ~ G 1 3 4の出力として、冗長置換情報R D < 3 : 0 >より規定される1ビットのみを“1”とした検出用置換信号H I T D < 1 5 : 0 > ( H I T D < 1 5 : 1 2 > , H I T D < 1 1 : 8 > , H I T D < 7 : 4 > , H I T D < 3 : 0 > )を得ることができる。

40

【0187】

一方、排他的論理和ゲートG 1 4 1は一方入力に内部アドレスI A D < 1 >を受け、他方入力アドレス置換情報R A < 1 >を受け、排他的論理和ゲートG 1 4 2は一方入力に内部アドレスI A D < 0 >を受け、他方入力にアドレス置換情報R A < 0 >を受ける。N O RゲートG 1 4 3は一方入力及び他方入力に排他的論理和ゲートG 1 4 1及びG 1 4 2の出力を受ける。

【0188】

その結果、アドレス置換情報R A < 1 : 0 >と内部アドレスI A D < 1 : 0 >とが完全一致したときのみ“H”的置換アドレス信号H I T \_ AがN O RゲートG 1 4 3から出力される。なお、置換アドレス信号H I T \_ Aは検出用置換信号H I T D < 1 5 : 0 >に対応させるべく16ビットに拡張される。

50

## 【0189】

NANDゲートG122（実際は16個あり、代表的に1つを示す）は検出用置換信号HITD<15:0>及び置換アドレス信号HIT\_Aを受ける。インバータG60（実際は16個あり、代表的に1つを示す）はNANDゲートG122の出力をうける。このインバータG60の出力が置換信号HIT<15:0>となる。

## 【0190】

したがって、置換信号HIT<15:0>は内部アドレスIAD<1:0>がアドレス置換情報RA<1:0>に一致したとき、冗長置換情報RD<3:0>の指示するビットを置換すべく、所定のビットのみが“1”となる。

## 【0191】

図23はスワップ回路56による冗長置換動作を示すタイミング図である。上述したように、スペア制御回路20が反転処理アドレスRAD<2>によってスペアY選択信号SSY及び冗長置換情報RDを生成するため、スワップ回路56において冗長置換情報RDが正しく認識される必要がある。

## 【0192】

このため、冗長置換情報RDの確定後、反転指示信号#SRの“L”立ち下がりより先に冗長情報シフト信号RSFの“H”立ち上がりが生じるようにし、同図に示すように、ラッチ68に格納されるシフト後の冗長置換情報RDが常に、ページ選択データPSDに対応する内容にすることができる。例えば、反転処理アドレスRAD<2>の“1”への変化により冗長置換情報RD（シフト前）の内容は内部アドレスIAD<2>=1対応の内容に変化するが、冗長置換情報RD（シフト後）の内容は次に冗長情報シフト信号RSFが“H”に立ち上がるまで内部アドレスIAD<2>=“0”対応の内容を維持する。したがって、内部アドレスIAD<2:0>の変化が“0”～“3”的期間は内部アドレスIAD<2>=“0”対応の情報がラッチ68にラッチされ続ける。

## 【0193】

図24は実施の形態3で用いられるアドレス反転制御回路の一例を示す回路図である。同図に示すように、NANDゲートG6の出力を遅延回路47を介して得られる信号を反転指示信号#SRとし、ラッチ信号SL2と同じ信号を冗長情報シフト信号RSFとしても出力する。なお、他の構成は図11で示したページモード制御回路におけるアドレス反転制御回路15と同様であるため説明を省略する。

## 【0194】

同図に示すようにアドレス反転制御回路30を構成することにより、図23に示すように、ラッチ信号SL1の“H”立ち上がりと同時に冗長情報シフト信号RSFの“H”立ち上がりが生じ、ラッチ信号SL1の“H”立ち上がりから遅延回路47による遅延時間T47遅れて反転指示信号#SRの“L”立ち下がりを生じさせることができる。

## 【0195】

このように、実施の形態3では、実施の形態1の効率的なページモード読み出し機能を維持した上、さらに冗長置換機能も兼ね備えるという効果を奏する。

## 【0196】

また、アドレス反転制御回路30によって、反転指示信号#SRの“L”立ち下がりに先がけて冗長情報シフト信号RSFの“H”立ち上がりを実現することにより、反転処理アドレスRAD<2>の反転処理が生じても、スワップ回路56のラッチ68には常に正しい内容の冗長置換情報RDがラッチされるため、正確に冗長置換動作を行うことができる。

## 【0197】

なお、実施の形態3では、実施の形態1の構成に冗長データ置換機能を持たせた半導体記憶装置を示したが、同様にして実施の形態2の構成に冗長データ置換機能を持たせても良い。

## 【図面の簡単な説明】

## 【0198】

10

20

30

40

50

【図1】この発明の実施の形態1である半導体記憶装置のメモリセルアレイ周辺部の構成を示すブロック図である。

【図2】実施の形態1の内部アドレス供給部の構成を示すブロック図である。

【図3】図2のアドレスラッチ回路の内部構成を示す回路図である。

【図4】ページモード制御回路の主要部の構成を示す回路図である。

【図5】図4で示したATD回路部の内部構成を示す回路図である。

【図6】図5で示したATD回路(その1)の内部構成を示す回路図である。

【図7】遷移パルス発生回路の内部構成を示す回路図である。

【図8】図5で示したATD回路(その2)の内部構成を示す回路図である。

【図9】図4で示したセンス制御回路の内部構成を示す回路図である。

10

【図10】図9で示した遅延ユニットの内部構成を示す回路図である。

【図11】図4で示したアドレス反転制御回路の内部構成を示す回路図である。

【図12】アドレス反転制御回路及びその周辺回路の動作を示すタイミング図である。

【図13】図1で示したセレクタ回路の内部構成を示す回路図である。

【図14】この発明の実施の形態1による半導体記憶装置のページモード読み出し動作を示すタイミング図である。

【図15】この発明の実施の形態2である半導体記憶装置のメモリセルアレイ周辺部の構成を示すブロック図である。

【図16】ページモード制御回路の主要部の構成を示す回路図である。

【図17】図16で示したセンス制御回路の内部構成を示す回路図である。

20

【図18】この発明の実施の形態2による半導体記憶装置のページモード読み出し動作を示すタイミング図である。

【図19】この発明の実施の形態3である半導体記憶装置のメモリセルアレイ周辺部の構成を示すブロック図である。

【図20】スペアY選択信号を発生するスペア制御回路の構成を示すブロック図である。

【図21】図19で示したスワップ回路の内部構成を示す回路図である。

【図22】図21で示した判定回路の内部構成を示す回路図である。

【図23】スワップ回路による冗長置換動作を示すタイミング図である。

【図24】実施の形態3で用いられるアドレス反転制御回路の一例を示す回路図である。

【符号の説明】

30

【0199】

1, 21 メモリセルアレイ、2, 22, 52 Yゲート、3, 23, 53 センスアンプ、4, 24, 54 センスデータ用ラッチ、5, 25, 55 ページデータ用ラッチ、6, 26 セレクタ回路、7, 27 出力バッファ、8, 28 Xデコーダ、9, 29 Yデコーダ、10 アドレスラッチ回路、11 CEバッファ、12 ADVバッファ、13 アドレスバッファ、14, 17 ATD回路部、15, 18, 30 アドレス反転制御回路、16, 19 センス制御回路、20 スペア制御回路、31, 32 ATD回路、33~35 遷移パルス発生回路、36~38, 41~46 遅延ユニット、47 遅延回路、51 スペアメモリセルアレイ、56 スワップ回路、69 判定回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 12】

【図 11】

【図 13】

【図 14】

【図20】

【図22】

【図21】

【図23】

【図24】

30 : アドレス反転制御回路

---

フロントページの続き

(56)参考文献 特開2004-95030(JP, A)

特開2001-118395(JP, A)

特開平11-96786(JP, A)

特開平5-144255(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 16 / 02