#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

### (19) World Intellectual Property Organization

International Bureau

##

# (10) International Publication Number WO 2010/026446 A1

# (43) International Publication Date 11 March 2010 (11.03.2010)

- (51) International Patent Classification: *H04B* 15/02 (2006.01) *H04L* 25/49 (2006.01)

- (21) International Application Number:

PCT/IB2008/053592

(22) International Filing Date:

4 September 2008 (04.09.2008)

(25) Filing Language:

English

(26) Publication Language:

English

- (71) Applicant (for all designated States except US): FREESCALE SEMICONDUCTOR, INC. [US/US]; 6501 William Cannon Drive West, Austin, Texas 78735 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): O'BRIEN, Michael [IE/IE]; Clonpriest, Youghal, 0 (IE). KELLEHER, Paul [IE/IE]; Rearour, Cork, Aherla (IE). O'KEEFFE, Conor [IE/IE]; 26 Hollygarth,, Cork, Douglas (IE).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ,

EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

of inventorship (Rule 4.17(iv))

#### Published:

with international search report (Art. 21(3))

#### (54) Title: METHOD AND APPARATUS FOR TRANSMITTING DATA

(57) Abstract: A semiconductor device (200) comprising an interface logic module (220) for transmitting data frames across an interface (215), and controller logic module (210) arranged to control a rate at which the interface logic (220) transmits data across the interface (215). Upon receipt of data frames to transmit across the interface (215), the controller logic module (210) is arranged to determine a sequence of data rates with which to transmit sequential data frames across the interface (215), and to configure the transmission of the data frames across the interface (215) according to the determined data rate sequence. The selection of these data rates will be dependent on specific critical RF frequencies where EMI impacts have to be minimised.

WO 2010/026446 A1

Title: METHOD AND APPARATUS FOR TRANSMITTING DATA

#### Description

10

15

20

25

30

35

40

#### 5 Field of the invention

This invention relates to a method and apparatus for transmitting data, and in particular for transmitting data frames across a high speed interface.

#### Background of the invention

High Speed serial interfaces span many standardisation efforts; these include the DigRF/M-PHY interface developed by the Mobile Industry Processor Interface (MIPI) Alliance, Universal Serial Bus (USB) interface, serial Rapid Input Output (sRIO) bus interface, Common Public Radio Interface (CPRI), Open Base Station Architecture Initiative (OBSAI) interfaces, etc. Key requirements for such high speed interfaces include high baud rates with minimal power consumption, low bit error rate and minimal Electromagnetic Interference (EMI). Many electronic products that include high-speed serial interfaces also contain wireless functionality. A mobile telephone device is one such example. Mitigating the effect of high-speed serial communication generated interference, as caused to the receiver or transmitter functionality, is paramount to the effective operation of the wireless functionality.

The MIPI developed M-PHY interface configured in DigRF mode is a high speed interface comprising requirements for EMI that are particularly sensitive, due to the fact that the interface is connecting the radio frequency integrated circuit (RFIC) transceiver device and the baseband processor integrated circuit (BBIC) within a communication device. The RFIC transceiver device in a mobile phone processes the low level signals received from the air-interface. In a DigRF M-PHY interface, there is a requirement for more than 1Gbs on the downlink from the RFIC to the BBIC and greater than 832Mbps on the uplink from the BBIC to the RFIC for some 3GPP LTE (3<sup>rd</sup> Generation Partnership Project Long Term Evolution) use case examples.

The proliferation of embedded clock schemes such as 8b10b coding in serial interfaces to facilitate clock data recovery also has an undesired consequence of shaping the resultant spectrum. The frequency lobes generated are maximally flat across the spectrum with nulls only at the baud frequency. Data streams without embedded clocks encoded tend to have more roll off at higher frequencies such that the RF spectrum exhibits a SINC profile. Typically, the baud rate needed to meet the increased data throughput requirements would be such that data transmitted at these rates would result in a RF spectrum of the data signal that could interfere significantly with critical RF channel frequencies. Furthermore, as the baud rate is increased, the noise impact can become more significant.

One possible solution to this problem is to use more than one data path. In this manner, data may be transmitted at a lower data rate over a plurality of lanes, thus providing the required high data throughput whilst maintaining a low baud rate. However, increasing the number of data paths requires an increase in the number of data pins of the respective integrated circuits and

semiconductor devices. As will be appreciated, increasing the number of pins results in an increase in the power consumption (due to the need to drive each pin) and complexity in terms of synchronising and time controlling the data paths. Furthermore, each additional path increases the composite noise by 3dB. Accordingly, there is a trade-off between the number of data paths, with their inherent power and complexity costs and composite noise increases, and the interference caused by higher baud rates.

PCT/IB2008/053592

#### Summary of the invention

Embodiments of the invention provide a semiconductor device, a wireless communication unit and a method for transmitting data frames across an interface as described in the accompanying claims.

Specific embodiments of the invention are set forth in the dependent claims.

These and other aspects of the invention will be apparent from and elucidated with reference to the embodiments described hereinafter.

15

20

25

30

35

40

10

5

#### Brief description of the drawings

Further details, aspects and embodiments of the invention will be described, by way of example only, with reference to the drawings. Elements in the figures are illustrated for simplicity and clarity and have not necessarily been drawn to scale.

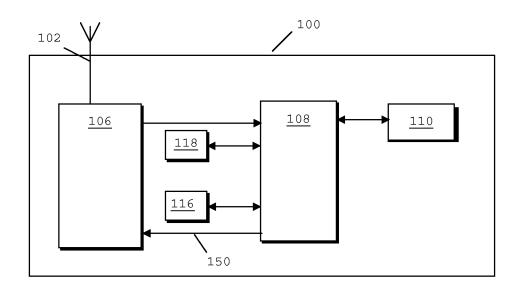

- FIG. 1 illustrates an example of a block diagram of part of an example of a wireless communication unit.

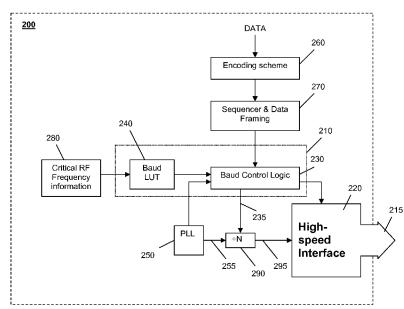

- FIG. 2 illustrates an example of a semiconductor device 200.

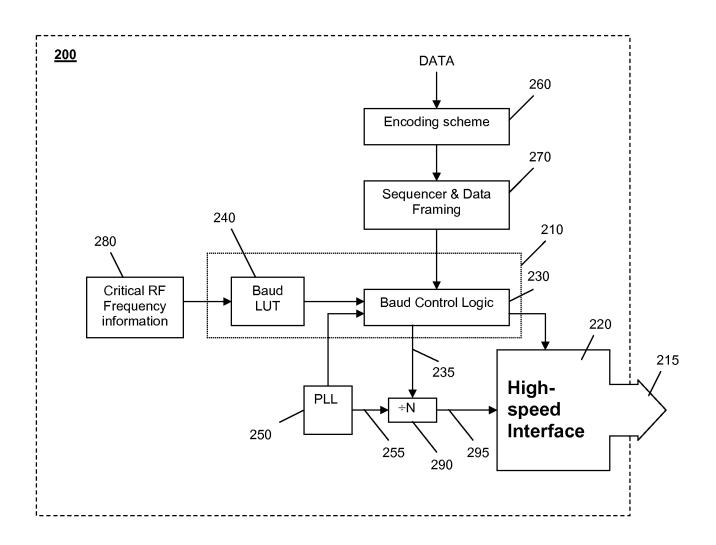

- FIG. 3 illustrates an example of a simplified flowchart of an example of a method for transmitting data frames across an interface.

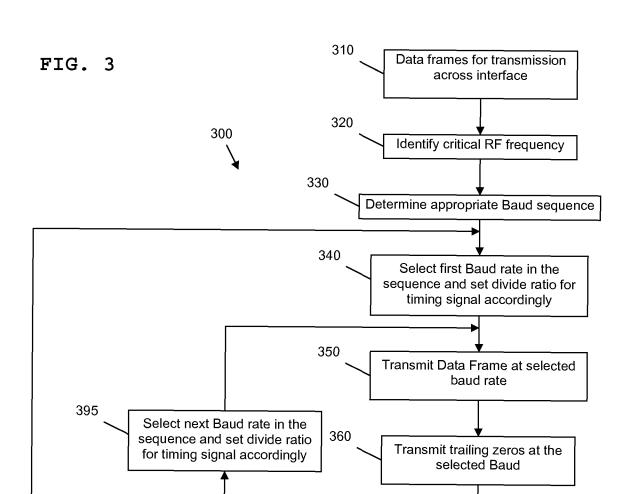

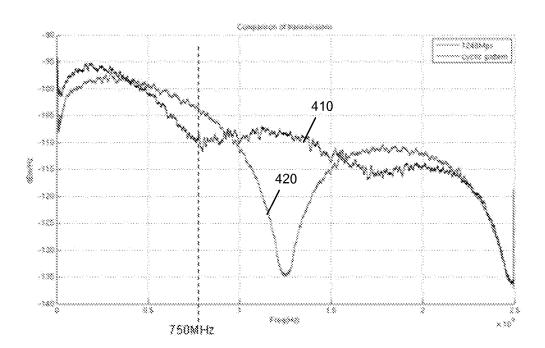

- FIG. 4 illustrates an example of a frequency spectrum comparison for a data signal transmitted across a high speed interface.

#### Detailed description of the preferred embodiments

Referring to FIG. 1, there is illustrated an example of a block diagram of part of an example of a wireless communication unit 100. The wireless communication unit 100, in the context of the illustrated embodiment, comprises a mobile telephone handset comprising an antenna 102. As such, the wireless communication unit 100 contains a variety of well known radio frequency (RF) components or circuits 106, operably coupled to the antenna 102 that will not be described further herein. The wireless communication unit 100 further comprises baseband circuitry, which for the illustrated embodiment is in a form of signal processing logic module 108. An output from the signal processing logic module 108 is provided to a suitable user interface 110 comprising, for example, a display, keypad, loudspeaker and/or microphone.

The signal processing logic module 108 is coupled to a memory element 116 that stores computer-readable code for programming the signal processing logic module 108, for example operating regimes, such as decoding/encoding functions and the like and may be realised in a

WO 2010/026446 PCT/IB2008/053592 - 3 -

variety of technologies such as random access memory (RAM) (volatile), (non-volatile) read only memory (ROM), Flash memory or any combination of these or other memory technologies. A sequencer logic module 118 is typically coupled to the signal processing logic module 108 to control the timing of operations within the wireless communication unit 100.

As previously mentioned to implement the LTE (Long Term Evolution) air interface standards require a net serial data throughput across an uplink interface 150 between the baseband circuitry, comprising signal processing logic module 108, and the RF circuitry 106 of greater than 832MBps, in order to meet the proposed requirements.

5

10

15

20

25

30

35

40

Referring now to FIG. 2, there is illustrated an example of a semiconductor device 200 comprising interface logic module 220 for transmitting data frames across an interface 215, such as a high-speed uplink interface between baseband circuitry and RF circuitry, and controller logic module 210 arranged to control a rate at which the interface logic module 220 transmits data across the interface 215. For the illustrated embodiment, the semiconductor device 220 further comprises encoding logic module 260 and sequencer and framing logic module 270. The encoding logic module 260 is arranged to receive data to be transmitted across the interface 215, and to encode the data, for example using 8bit/10bit encoding. The sequencer and framing logic module 270 sequences the encoded data bits, and divides the sequenced and encoded data bits into frames, for example comprising 256 data bits, for transmission across the interface 215. The data frames are then provided to the controller logic module 210.

Upon receipt of data frames to transmit across the interface 215, the controller logic module 210 is arranged to determine a sequence of data rates with which to transmit sequential data frames across the interface 215, and to configure the transmission of the data frames across the interface 215 according to the determined data rate sequence.

In this manner, sequential data frames may be transmitted across the interface 215 at varying data rates. As a result, the frequency spectrum of the data signal on the interface 215 may be managed, by managing the data rate sequence, thus allowing potential interference to RF signals and the like to also be managed. In particular, interference caused to a critical RF channel frequency due to EMI (electromagnetic interference) from the transmission of data frames across the interface may be reduced by substantially avoiding transmitting data frames at data rates comprising a period similar to that of a critical RF channel frequency, whilst maintaining a high data throughput without transmitting data at significantly high data rates for prolonged periods of time.

For the illustrated example of a embodiment, the controller logic module 210 is arranged to determine the data rate sequence based on a critical frequency, for example a critical RF channel frequency. Accordingly, the controller logic module 210 of FIG. 2 is arranged to receive critical RF frequency information 280. In accordance with some example of a embodiments of the invention, a wireless communication unit, such as the mobile telephone handset 100 of FIG. 1, is capable of operating over a range of RF channels. Thus, the controller logic 210 may be arranged to receive information, for example from a central processing unit (not shown) or the like, identifying the RF receiver channel that the wireless communication unit is currently operating on. Such information may comprise a value representative of an actual frequency of the RF channel, or a value

representative of a channel designation, such as a UMTS (Universal Mobile Telecommunication System) Absolute Radio Frequency Channel Number (UARFCN). In any transceiver, the receiver will only be receiving a minimal subset of frequencies. These frequencies will be known apriori, either by command through an air interface protocol configuration or by the mobile device arbitrarily selecting a frequency of reception. In particular, the transceiver will only be receiving one of these frequencies at any one time. Accordingly, the controller logic module 210 may be arranged to receive information identifying the frequency that is being received.

The controller logic module 210 may be arranged to select a data rate sequence from a set of predetermined data rate sequences, the set of predetermined data rate sequences corresponding to a set of frequencies, such as a set of RF channel frequencies. In particular, for the example of a embodiment illustrated in FIG. 2, the controller logic module 210 comprises baud control logic module 230 arranged, upon receipt of data frames to transmit across the interface 215, to determine a critical frequency from information 280 provided thereto. The controller logic module 210 further identifies a baud rate sequence corresponding to the critical frequency from a lookup table 240, and configures the transmission of the data frames across the interface 215 according to the identified baud rate sequence. Table 1 below illustrates an example of baud rate sequences, comprising baud rates for the transmission of data frames across the interface 215, corresponding to a set of RF frequencies that lookup table 240 may comprise.

| FREQUENCY | BAUD RATE SEQUENCE                              |

|-----------|-------------------------------------------------|

| 750MHz    | [832; 832; 832; 2496; 832; 2496] Mbs            |

| 900MHz    | [832; 2496; 832; 1248; 832; 832; 2496; 832] Mbs |

| 950MHz    | [1248; 832; 832; 1248; 1248; 832] Mbs           |

| 1500MHz   | [1248; 832; 832; 832; 1248; 1248; 1248] Mbs     |

| 1800MHz   | [832; 832; 832; 2496; 832; 2496; 832] Mbs       |

| 2100MHz   | [624; 2496; 2496; 2496] Mbs                     |

20

25

30

5

10

15

#### Table 1

The first column of Table 1 contains a set of RF frequencies, such as those corresponding to RF receiver channels. In alternative embodiments, Table 1 may comprise UMTS Absolute Radio Frequency Channel Numbers (UARFCNs). The second column of Table 1 comprises data rate sequences, which for the illustrated embodiment comprise baud rate sequences. In this manner, when the controller logic module 210 receives critical RF frequency information, for example a value representative of an actual frequency of the critical RF channel or a value representative of a channel designation such as a UARFCN, the baud rate sequence corresponding to that critical RF frequency may be obtained from the lookup table 240. The controller logic module 210 may then reconfigure the baud rate for the transmission of data frames across the interface 215, in accordance with the obtained baud rate sequence.

By way of example, suppose the controller logic module 210 receives information identifying the critical RF channel frequency as, say, 900MHz. The controller logic module 210 may then retrieve the appropriate baud rate sequence from the lookup table 240, for example [832; 2496; 832; 1248; 832; 832; 2496; 832] Mbs. The controller logic module 210 then re-configures the transmission of the data frames across the interface 215 according to this baud rate sequence. Thus, the controller logic module 210 configures the baud rate for the transmission of the first data frame at 832Mbs. After the first data frame has been transmitted, the controller logic module 210 reconfigures the baud rate for the transmission of the second data frame as 2496Mbs. Similarly, after the second data frame has been transmitted, the controller logic 210 reconfigures the baud rate for the third data frame as 832Mbs. In this manner, the controller logic 210 reconfigures the baud rate between each data frame (if required according to the baud rate sequence) until all data frames have been transmitted. If the last baud rate in the sequence is configured before the last data frame to be transmitted, the controller logic module 210 may revert back to the first baud rate in the sequence, and continues to loop through the sequence until all the data frames have been transmitted.

5

10

15

20

25

30

35

40

If the controller logic module 210 subsequently receives information identifying a new critical RF channel frequency, such as, say, 1800, the controller logic module 210 is then able to retrieve the appropriate data rate sequence for the new critical frequency from the lookup table 240, for example [832; 832; 832; 2496; 832; 2496; 832] Mbs. The controller logic module 210 is then able to configure the transmission of data frames across the interface 215 according to this new data rate sequence.

Advantageously, by selecting the data rate sequence from a set of predetermined data rate sequences in this manner, whereby the set of predetermined data rate sequences corresponds generally to a set of critical frequencies, the controller logic module 210 is able to dynamically change the data rate sequence in response to changes in the critical frequency. In this manner, when the wireless communication unit changes frequency channels, the controller logic module 210 is able to dynamically change the data rate sequence accordingly, and thereby manage the frequency spectrum of the data signal being transmitted across the interface.

In accordance with some example of a embodiments of the invention, for ease of implementation and to minimise costs, each data rate within a data rate sequence substantially comprises an integer division of a reference timing signal 255 generated by a Phase Locked Loop (PLL) logic 250. For example, in the case of the data rates within Table 1 above, the PLL logic module 250 may be arranged to generate a reference timing signal 255 comprising a frequency of 2496MHz, which can be divided by integers to produce clock signals comprising the data rate frequencies of 2496MHz, 1248MHz, 832MHz, 624MHz, etc.

Accordingly, for the example of a embodiment illustrated in FIG. 2, the controller logic module 210 is operably coupled to frequency divider logic module 290, which receives the reference timing signal 255 generated by the PLL logic module 250, and divides the reference timing signal 255 by an integer in accordance with a divide ratio 235 from the controller logic module 210. In this manner, the divider logic module 290 generates a data rate signal 295, which

is provided to the interface logic module 220, and which acts as a timing reference for the transmission of data across the interface 215.

Referring now to FIG. 3 there is illustrated an example of a simplified flowchart 300 of an example of a method for transmitting data frames across an interface. For example, the method of FIG. 3 may be implemented within a wireless communication unit, such as the wireless communication unit of FIG. 1. In particular, the method of FIG. 3 may be implemented in the form of computer-readable code for programming a signal processing logic module, such as the signal processing logic module 108.

5

10

15

20

25

30

35

The method starts at step 310 with a receipt (e.g. from an external source) or generation (e.g. internally) of data frames to be transmitted across the interface. A critical RF frequency is then identified, in step 320, followed by a determination of a data rate sequence in step 330. For example, the critical RF frequency identified in step 320 may be used to obtain an appropriate data rate in a form of a baud rate from a lookup table.

Next, in step 340, the first data rate in the data rate sequence is selected and a divide ratio is set for a timing signal according to the first data rate in the data rate sequence. The first data frame is transmitted at the selected data rate, in step 350, followed by the transmission of trailing zeros, if necessary, in step 360. Next, in step 370, it is determined whether the end of the transmission has been reached, e.g. the last data frame has been transmitted. If the end of the transmission has been reached, the method ends at step 380.

However, if the end of the transmission has not been reached, the method moves to step 390, where it is determined whether the end of the data rate sequence has been reached. If the end of the data rate sequence has not been reached, the method moves to step 395 where the next data rate in the sequence is selected, and the divide ratio is set for the timing signal according to the selected data rate in the data rate sequence. The method then loops back to step 350, where the next data frame is transmitted at the selected data rate.

Referring back to step 390, if the end of the data rate sequence has been reached, the method loops back to step 340, where the first data rate in the sequence is selected, and the divide ratio is set for the timing signal according to the first data rate in the data rate sequence. The method then moves on to step 350, where the next data frame is transmitted at the selected data rate.

Referring now to FIG. 4, there is illustrated an example of a frequency spectrum comparison 400 for a data signal transmitted across a high speed interface. The frequency spectrum comparison 400 comprises a first curve 410 representing a frequency spectrum for the data signal transmitted across the interface using a baud rate sequence in accordance with an example of a embodiment of the invention. The frequency spectrum comparison 400 further comprises a second curve 420 representing a frequency spectrum for the data signal transmitted across the interface using a fixed 1248Mbs baud rate.

-7-

In particular, the illustrated curve 410 represents a frequency spectrum for the transmission of data across the interface using the baud rate sequence in Table 1 above corresponding to a critical frequency of 750MHz. Thus, the curve 410 represents the frequency spectrum for the transmission of data across the interface using a cyclic baud rate of: [832; 832; 832; 2496; 832; 832; 2496] Mbs. As can be seen, approximately 7dB of performance improvement at 750MHz is achieved over the fixed baud rate, with poor performance being pushed out to other regions of the spectrum, whilst maintaining the required >832Mbs net data throughput without the need for additional data paths.

5

10

15

20

25

30

Table 2 below illustrates the performance enhancements achieved for each of the baud rate sequences of Table 1 above, in comparison to a fixed 1248MHz baud rate.

| FREQUENCY | BAUD RATE SEQUENCE                              | Performance Enhancement |

|-----------|-------------------------------------------------|-------------------------|

| 750MHz    | [832; 832; 832; 2496; 832; 832; 2496] Mbs       | 7.414dB                 |

| 900MHz    | [832; 2496; 832; 1248; 832; 832; 2496; 832] Mbs | 3.3474dB                |

| 950MHz    | [1248; 832; 832; 1248; 1248; 1248; 832] Mbs     | 2.78dB                  |

| 1500MHz   | [1248; 832; 832; 832; 1248; 1248; 1248] Mbs     | 2.2609dB                |

| 1800MHz   | [832; 832; 832; 2496; 832; 2496; 832] Mbs       | 5.1283dB                |

| 2100MHz   | [624; 2496; 2496; 2496] Mbs                     | 3.9371dB                |

#### Table 2

As can be seen, a performance enhancement is achieved for each of the critical frequencies over the fixed 1248Mbs baud rate, without the need for additional data paths.

Clock data recovery circuits (not shown) may be provided at a downstream side of the interface 215 that determine what baud the data is sent on from the received bit stream. However, it is contemplated that the baud rate sequences may alternatively be pre-programmed into downstream interface logic (not shown).

It will be understood that the method and apparatus for transmitting data frames across an interface, as described above, aim to provide at least one or more of the following:

- (i) Dynamic management of data transfer rates for sequential frames, in order to shape the RF spectrum of the data signal on the interface at critical frequencies;

- (ii) RF spectrum of the data signal on the interface is shaped to reduce interference at RF critical frequencies, and dynamically managing this RF spectrum shaping as a wireless communication unit moves to different RF frequencies; and

- (iii) A low cost implementation leading to improved interface performance leading to a more robust system, where a high data rate interface may be used substantially without degrading receiver performance.

Whilst within example of a embodiments of the invention the interface may comprise a single data lane, it will be understood that the invention may equally be implemented in conjunction with an interface comprising a plurality of data lanes. For example, a single data rate may be applied to all data lanes. Accordingly, the data rate applied concurrently to each data lane will follow the same data rate sequence. Alternatively, a separate data rate sequence may be applied to each individual data lane such.

5

10

15

20

25

30

35

40

In the foregoing specification, the invention has been described with reference to specific examples of embodiments of the invention. It will, however, be evident that various modifications and changes may be made therein without departing from the broader spirit and scope of the invention as set forth in the appended claims. For example, the connections may be any type of connection suitable to transfer signals from or to the respective nodes, units or devices, for example via intermediate devices. Accordingly, unless implied or stated otherwise the connections may for example be direct connections or indirect connections.

The semiconductor substrate described herein can be any semiconductor material or combinations of materials, such as gallium arsenide, silicon germanium, silicon-on-insulator (SOI), silicon, monocrystalline silicon, the like, and combinations of the above.

The conductors as discussed herein may be illustrated or described in reference to being a single conductor, a plurality of conductors, unidirectional conductors, or bidirectional conductors. However, different embodiments may vary the implementation of the conductors. For example, separate unidirectional conductors may be used rather than bidirectional conductors and vice versa. Also, plurality of conductors may be replaced with a single conductor that transfers multiple signals serially or in a time multiplexed manner. Likewise, single conductors carrying multiple signals may be separated out into various different conductors carrying subsets of these signals. Therefore, many options exist for transferring signals.

Because the apparatus implementing the present invention is, for the most part, composed of electronic components and circuits known to those skilled in the art, circuit details will not be explained in any greater extent than that considered necessary as illustrated above, for the understanding and appreciation of the underlying concepts of the present invention and in order not to obfuscate or distract from the teachings of the present invention.

Although the invention has been described with respect to specific conductivity types or polarity of potentials, skilled artisans appreciated that conductivity types and polarities of potentials may be reversed.

Moreover, the terms "front," "back," "top," "bottom," "over," "under" and the like in the description and in the claims, if any, are used for descriptive purposes and not necessarily for describing permanent relative positions. It is understood that the terms so used are interchangeable under appropriate circumstances such that the embodiments of the invention described herein are, for example, capable of operation in other orientations than those illustrated or otherwise described herein.

The term "program," as used herein, is defined as a sequence of instructions designed for execution on a computer system. A program, or computer program, may include a subroutine, a

function, a procedure, an object method, an object implementation, an executable application, an applet, a servlet, a source code, an object code, a shared library/dynamic load library and/or other sequence of instructions designed for execution on a computer system.

5

10

15

20

25

30

35

40

Some of the above embodiments, as applicable, may be implemented using a variety of different information processing systems. For example, although FIG. 1 and the discussion thereof describe an example of a wireless communication unit architecture, this example of a architecture is presented merely to provide a useful reference in discussing various aspects of the invention. Of course, the description of the architecture has been simplified for purposes of discussion, and it is just one of many different types of appropriate architectures that may be used in accordance with the invention. Those skilled in the art will recognize that the boundaries between logic blocks are merely illustrative and that alternative embodiments may merge logic blocks or circuit elements or impose an alternate decomposition of functionality upon various logic blocks or circuit elements.

Thus, it is to be understood that the architectures depicted herein are merely example of a, and that in fact many other architectures can be implemented which achieve the same functionality. In an abstract, but still definite sense, any arrangement of components to achieve the same functionality is effectively "associated" such that the desired functionality is achieved. Hence, any two components herein combined to achieve a particular functionality can be seen as "associated with" each other such that the desired functionality is achieved, irrespective of architectures or intermediary components. Likewise, any two components so associated can also be viewed as being "operably connected," or "operably coupled," to each other to achieve the desired functionality.

Also for example, in one embodiment, the illustrated elements of FIG. 2 comprise logic located on a single integrated circuit or within a same device. Alternatively, system may include any number of separate integrated circuits or separate devices interconnected with each other. Furthermore, logical components may be soft or code representations of physical circuitry or of logical representations convertible into physical circuitry.

Furthermore, those skilled in the art will recognize that boundaries between the functionality of the above described operations are merely illustrative. The functionality of multiple operations may be combined into a single operation, and/or the functionality of a single operation may be distributed in additional operations. Moreover, alternative embodiments may include multiple instances of a particular operation, and the order of operations may be altered in various other embodiments.

All or some of the software described herein may be received or stored in computer readable media such as memory 116. Such computer readable media may be permanently, removably or remotely coupled to the signal processing logic 108. The computer readable media may include, for example and without limitation, any number of the following: magnetic storage media including disk and tape storage media; optical storage media such as compact disk media (e.g., CD-ROM, CD-R, etc.) and digital video disk storage media; nonvolatile memory storage media including semiconductor-based memory units such as FLASH memory, EEPROM, EPROM, ROM; ferromagnetic digital memories; MRAM; volatile storage media including registers, buffers or

WO 2010/026446 PCT/IB2008/053592 - 10 -

caches, main memory, RAM, etc.; and data transmission media including computer networks, point-to-point telecommunication equipment, and carrier wave transmission media, just to name a few.

Also, the invention is not limited to physical devices or units implemented in non-programmable hardware but can also be applied in programmable devices or units able to perform the desired device functions by operating in accordance with suitable program code. Furthermore, the devices may be physically distributed over a number of apparatuses, while functionally operating as a single device. Also, devices functionally forming separate devices may be integrated in a single physical device.

5

10

15

20

25

However, other modifications, variations and alternatives are also possible. The specifications and drawings are, accordingly, to be regarded in an illustrative rather than in a restrictive sense.

In the claims, any reference signs placed between parentheses shall not be construed as limiting the claim. The word 'comprising' does not exclude the presence of other elements or steps then those listed in a claim. Furthermore, Furthermore, the terms "a" or "an," as used herein, are defined as one or more than one. Also, the use of introductory phrases such as "at least one" and "one or more" in the claims should not be construed to imply that the introduction of another claim element by the indefinite articles "a" or "an" limits any particular claim containing such introduced claim element to inventions containing only one such element, even when the same claim includes the introductory phrases "one or more" or "at least one" and indefinite articles such as "a" or "an." The same holds true for the use of definite articles. Unless stated otherwise, terms such as "first" and "second" are used to arbitrarily distinguish between the elements such terms describe. Thus, these terms are not necessarily intended to indicate temporal or other prioritization of such elements. The mere fact that certain measures are recited in mutually different claims does not indicate that a combination of these measures cannot be used to advantage.

#### Claims

A semiconductor device (200) comprising:

an interface logic module (220) for transmitting data frames across an interface (215);

5 and

a controller logic module (210) arranged to control a rate at which the interface logic module (220) transmits data across the interface (215); wherein, upon receipt of data frames to transmit across the interface (215), the controller logic module (210) is arranged to:

determine a sequence of data rates with which to transmit sequential data frames across the interface (215); and

configure the transmission of the data frames across the interface (215) according to the determined data rate sequence.

- 15 2. The semiconductor device (200) of Claim 1 wherein the controller logic (210) is arranged to determine the data rate sequence based on a critical frequency.

- 3. The semiconductor device (200) of Claim 2 wherein the critical frequency comprises a Radio Frequency (RF) channel frequency.

20

10

4. The semiconductor device (200) of Claim 2 or Claim 3 wherein the controller logic module (210) is arranged to select a data rate sequence from a set of predetermined data rate sequences, the set of predetermined data rate sequences corresponding generally to a set of critical frequencies.

25

30

35

40

5. The semiconductor device (200) of Claim 4 wherein, upon receipt of data frames to transmit across the interface (215), the controller logic module (210) is arranged to:

determine a critical frequency;

identify a data rate sequence corresponding to the critical frequency from a lookup table (240); and

configure the transmission of the data frames across the interface (215) according to the identified data rate sequence.

- 6. The semiconductor device (200) of any preceding Claim wherein the control logic module (210) is arranged to reconfigure the data rate for the transmission of data frames across the interface (215) in accordance with the data rate sequence between data frames.

- 7. The semiconductor device (200) of any preceding Claim wherein each data rate within the data rate sequence substantially comprises an integer division of a reference timing signal (255).

WO 2010/026446 PCT/IB2008/053592 - 12 -

- 8. The semiconductor device (200) of Claim 7 wherein the reference timing signal (255) is generated by a Phase Locked Loop (PLL) (250).

- A wireless communication unit (100) comprising a semiconductor device (200)

comprising an interface logic module (220) for transmitting data frames across an interface (215);

and a controller logic module (210) arranged to control a rate at which the interface logic module (220) transmits data across the interface (215);

wherein, upon receipt of data frames to transmit across the interface (215), the controller logic module (210) is arranged to:

- determine a sequence of data rates with which to transmit sequential data frames across the interface (215); and

10

20

25

35

configure the transmission of the data frames across the interface (215) according to the determined data rate sequence.

- 15 10. A method (300) for transmitting data frames across an interface, the method comprising: determining a sequence of data rates with which to transmit sequential data frames across the interface (315); and

- configuring the transmission of the data frames across the interface according to the determined data rate sequence (320).

- 11. A computer-readable storage element comprising executable program code for programming signal processing logic (108), the computer program product comprising program code for:

- determining a sequence of data rates with which to transmit sequential data frames across the interface (315); and

- configuring the transmission of the data frames across the interface according to the determined data rate sequence (320).

- 12. The computer-readable storage element of Claim 11, wherein the computer readable storage medium comprises at least one of a hard disk, a CD-ROM, an optical storage device, a magnetic storage device, a Read Only Memory, ROM, a Programmable Read Only Memory, PROM, an Erasable Programmable Read Only Memory, EPROM, an Electrically Erasable Programmable Read Only Memory, EEPROM, and a Flash memory.

# AMENDED CLAIMS received by the International Bureau on 18 September 2009 (18.09.2009)

A semiconductor device (200) comprising:

an interface logic module (220) for transmitting data frames across an interface (215);

and

a controller logic module (210) arranged to control a rate at which the interface logic module (220) transmits data across the interface (215); wherein, upon receipt of data frames to transmit across the interface (215), the controller logic module (210) is arranged to:

determine a sequence of data rates with which to transmit sequential data frames across the interface (215); and

configure the transmission of the data frames across the interface (215) according to the determined data rate sequence.

- 2. The semiconductor device (200) of Claim 1 wherein the controller logic (210) is arranged to determine the data rate sequence based on a critical frequency.

- 3. The semiconductor device (200) of Claim 2 wherein the critical frequency comprises a Radio Frequency (RF) channel frequency.

- 4. The semiconductor device (200) of Claim 2 or Claim 3 wherein the controller logic module (210) is arranged to select a data rate sequence from a set of predetermined data rate sequences, the set of predetermined data rate sequences corresponding generally to a set of critical frequencies.

- 5. The semiconductor device (200) of Claim 4 wherein, upon receipt of data frames to transmit across the interface (215), the controller logic module (210) is arranged to:

determine a critical frequency;

identify a data rate sequence corresponding to the critical frequency from a lookup table (240); and

configure the transmission of the data frames across the interface (215) according to the identified data rate sequence.

- 6. The semiconductor device (200) of any preceding Claim wherein the control logic module (210) is arranged to reconfigure the data rate for the transmission of data frames across the interface (215) in accordance with the data rate sequence between data frames.

- 7. The semiconductor device (200) of any preceding Claim wherein each data rate within the data rate sequence substantially comprises an integer division of a reference timing signal (255).

- 8. The semiconductor device (200) of Claim 7 wherein the reference timing signal (255) is generated by a Phase Locked Loop (PLL) (250).

- 9. A wireless communication unit (100) comprising a semiconductor device (200) comprising an interface logic module (220) for transmitting data frames across an interface (215); and a controller logic module (210) arranged to control a rate at which the interface logic module (220) transmits data across the interface (215); wherein, upon receipt of data frames to transmit across the interface (215), the controller logic

determine a sequence of data rates with which to transmit sequential data frames across the interface (215); and

module (210) is arranged to:

configure the transmission of the data frames across the interface (215) according to the determined data rate sequence.

10. A method (300) for transmitting data frames across an interface, the method comprising: receiving data frames to transmit across the interface (310);

determining a sequence of data rates with which to transmit sequential data frames across the interface (315); and

configuring the transmission of the data frames across the interface according to the determined data rate sequence (320).

11. A computer-readable storage element comprising executable program code for programming signal processing logic (108), the computer program product comprising program code for:

receiving data frames to transmit across an interface (310); determining a sequence of data rates with which to transmit sequential data frames across the interface (315); and

configuring the transmission of the data frames across the interface according to the determined data rate sequence (320).

12. The computer-readable storage element of Claim 11, wherein the computer readable storage medium comprises at least one of a hard disk, a CD-ROM, an optical storage device, a magnetic storage device, a Read Only Memory, ROM, a Programmable Read Only Memory, PROM, an Erasable Programmable Read Only Memory, EPROM, an Electrically Erasable Programmable Read Only Memory, EEPROM, and a Flash memory.

FIG. 1

FIG. 2

No

End of Baud

sequence?

390

Yes

370

380

End of

transmission

**END**

Yes

No

PCT/IB2008/053592

FIG. 4

#### INTERNATIONAL SEARCH REPORT

International application No PCT/IB2008/053592

A. CLASSIFICATION OF SUBJECT MATTER

INV. H04B15/02 H04L25/49

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H04B H04L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, INSPEC

| Catagamit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Citation of decument with indication, where or an all the                                                                                                         | a valanta no casa na c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Delevent to eleler Me |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Citation of document, with indication, where appropriate, of the                                                                                                  | Relevant to claim No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GB 2 349 006 A (LG PHILIPS LCD [KR]) 18 October 2000 (2000-10-page 11, line 11 - page 12, line 12 - page 18, line 13 - page 18, line 19, line 19, line 5 - line 7 | 1–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |

| <b>A</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | WO 2006/027025 A (FREESCALE SEN<br>INC [US]; O'KEEFFE CONNOR J [IE<br>PAU) 16 March 2006 (2006-03-16)<br>page 16, line 24 - page 17, lir<br>1-3; figures 5,6      | 1–12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | WO 2005/041164 A (PHILIPS INTEL PROPERTY [DE]; KONINKL PHILIPS NV [NL) 6 May 2005 (2005-05-06) abstract; claim 1                                                  | 1-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |

| X Furti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | her documents are listed in the continuation of Box C.                                                                                                            | X See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |

| * Special categories of cited documents:  "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier document but published on or after the international filling date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filling date but later than the priority date claimed |                                                                                                                                                                   | <ul> <li>"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</li> <li>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</li> <li>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</li> <li>"&amp;" document member of the same patent family</li> </ul> |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | actual completion of the international search  8 May 2009                                                                                                         | Date of mailing of the international sea 05/06/2009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rch report            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nailing address of the ISA/ European Patent Office, P.B. 5818 Patentlaan 2 NL – 2280 HV Rijswijk Tel. (+31–70) 340–2040, Fax: (+31–70) 340–3016                   | Authorized officer Lindberg, Per                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |

## INTERNATIONAL SEARCH REPORT

International application No

PCT/IB2008/053592

|           | tion). DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                              |                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                      | Relevant to claim No. |

| A         | FOGG A: "DigRF BASEBAND / RF DIGITAL INTERFACE SPECIFICATION" INTERNET CITATION, [Online] XP002325710 Retrieved from the Internet: URL:http://146.101.169.51/DigRF%20Standard %20v112.pdf> [retrieved on 2004-02-20] the whole document | 1–12                  |

| ,         |                                                                                                                                                                                                                                         |                       |

|           |                                                                                                                                                                                                                                         |                       |

|           |                                                                                                                                                                                                                                         |                       |

|           |                                                                                                                                                                                                                                         |                       |

|           |                                                                                                                                                                                                                                         |                       |

#### INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/IB2008/053592

| Patent document cited in search report |   | Publication Patent family date member(s) |                                  |                                                                                        | Publication<br>date                                                              |

|----------------------------------------|---|------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| GB 2349006                             | A | 18-10-2000                               | DE<br>FR<br>JP<br>JP<br>KR<br>US | 19954240 A1<br>2792101 A1<br>3461783 B2<br>2001007891 A<br>20000065952 A<br>6720943 B1 | 19-10-2000<br>13-10-2000<br>27-10-2003<br>12-01-2001<br>15-11-2000<br>13-04-2004 |

| WO 2006027025                          | A | 16-03-2006                               | AT<br>CN<br>EP<br>JP<br>US       | 422732 T<br>101057411 A<br>1792410 A1<br>2008512884 T<br>2007254599 A1                 | 15-02-2009<br>17-10-2007<br>06-06-2007<br>24-04-2008<br>01-11-2007               |

| WO 2005041164                          | A | 06-05-2005                               | CN<br>JP<br>US                   | 1871635 A<br>2007511118 T<br>2007164883 A1                                             | 29-11-2006<br>26-04-2007<br>19-07-2007                                           |