(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4212552号

(P4212552)

(45) 発行日 平成21年1月21日(2009.1.21)

(24) 登録日 平成20年11月7日(2008.11.7)

(51) Int.Cl.

H01L 29/78 (2006.01)

F 1

H01L 29/78 652 F

H01L 29/78 652 B

H01L 29/78 652 D

H01L 29/78 652 S

H01L 29/78 653 A

請求項の数 5 (全 11 頁)

(21) 出願番号

特願2004-371056 (P2004-371056)

(22) 出願日

平成16年12月22日 (2004.12.22)

(65) 公開番号

特開2006-179664 (P2006-179664A)

(43) 公開日

平成18年7月6日 (2006.7.6)

審査請求日

平成18年2月22日 (2006.2.22)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100077849

弁理士 須山 佐一

(72) 発明者 小野 昇太郎

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72) 発明者 川口 雄介

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の第1の半導体層と、

前記第1の半導体層上に設けられた第2導電型の第2の半導体層と、

前記第2の半導体層を貫通して前記第1の半導体層に達するトレンチと、前記トレンチ内に絶縁膜を介して充填された導電材とを有するトレンチ・ゲートと、

前記第2の半導体層上に前記トレンチ・ゲートの前記導電材と前記絶縁膜を介して隣接形成された第1導電型の第3の半導体領域と、

前記第2の半導体層上に前記第3の半導体領域と前記トレンチ・ゲートに沿って交互に配置されるように隣接形成された第2導電型の第4の半導体領域とを具備し、

10

前記第3の半導体領域および前記第4の半導体領域は、前記トレンチ・ゲートの長手方向に対して傾きを持って配置されていることを特徴とする半導体装置。

## 【請求項 2】

請求項1記載の半導体装置において、

前記第3の半導体領域と前記第4の半導体領域との界面と前記トレンチ・ゲートの長手方向とが成す角度をとしたとき、前記第3の半導体領域と前記第4の半導体領域は前記角度が10~75°の範囲となるように配置されていることを特徴とする半導体装置。

## 【請求項 3】

第1導電型の第1の半導体層と、

前記第1の半導体層上に設けられた第2導電型の第2の半導体層と、

20

前記第2の半導体層を貫通して前記第1の半導体層に達するトレンチと、前記トレンチ内に絶縁膜を介して充填された導電材とを有するトレンチ・ゲートと、

前記第2の半導体層上に前記トレンチ・ゲートの前記導電材と前記絶縁膜を介して隣接形成された第1導電型の第3の半導体領域と、

前記第2の半導体層上に前記第3の半導体領域と前記トレンチ・ゲートに沿って交互に配置されるように隣接形成された第2導電型の第4の半導体領域とを具備し、

前記第4の半導体領域は、実効素子領域における前記第4の半導体領域の占める割合が、駆動電圧が印加されるゲート信号入力端子領域に近い領域より遠い領域の方が大きくなるように形成されていることを特徴とする半導体装置。

【請求項4】

10

第1導電型の第1の半導体層と、

前記第1の半導体層上に設けられた第2導電型の第2の半導体層と、

前記第2の半導体層を貫通して前記第1の半導体層に達するトレンチと、前記トレンチ内に絶縁膜を介して充填された導電材とを有するトレンチ・ゲートと、

前記第2の半導体層上に前記トレンチ・ゲートの前記導電材と前記絶縁膜を介して隣接形成された第1導電型の第3の半導体領域と、

前記第2の半導体層上に前記第3の半導体領域と前記トレンチ・ゲートに沿って交互に配置されるように隣接形成された第2導電型の第4の半導体領域とを具備し、

前記第3の半導体領域および前記第4の半導体領域は少なくとも一部が前記トレンチ・ゲートの長手方向に対して傾きを持って配置されており、かつ前記第4の半導体領域は実効素子領域における前記第4の半導体領域の占める割合が、駆動電圧が印加されるゲート信号入力端子領域に近い領域より遠い領域の方が大きくなるように形成されていることを特徴とする半導体装置。

20

【請求項5】

請求項3または請求項4記載の半導体装置において、

前記第3の半導体領域が前記トレンチ・ゲートと接する部分の長さをL1、前記第4の半導体領域が前記トレンチ・ゲートと接する部分の長さをL2、これらの長さ比をL2/L1としたとき、前記第4の半導体領域は前記入力端子領域に近い領域から前記入力端子領域から遠い領域に向けて、前記長さ比L2/L1が連続的に増加するように形成されていることを特徴とする半導体装置。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置に係り、特に縦型MOS (Metal-Oxide-Semiconductor) ゲート構造を有する半導体装置に関する。

【背景技術】

【0002】

半導体上方にトレンチ (trench: 溝) を形成し、これを用いたトレンチ・ゲート構造は、IGBT (Insulated Gate Bipolar Transistor) やMOS-FET (Metal Oxide Semiconductor - Field Effect Transistor) 等の半導体素子に応用されており、特に電力用途等に有利な構造である。例えば、トレンチ・ゲート構造を有するMOSFETはスイッチング速度が速く、また電流容量が大きく、数10V~300V程度の耐圧が得られるため、携帯型端末やパーソナル・コンピュータ等のスイッチング電源等に利用されつつある。

40

【0003】

このようなトレンチ・ゲート構造を有するパワー半導体装置について、nチャネル型トレンチMOSFETを一例として説明する。トレンチMOSFETにおいて、例えばn型ドリフト層とp型ベース層とが積層形成された半導体ウェーハに、p型ベース層を貫通してn型ドリフト層に達するトレンチが形成される。トレンチ内にはゲート絶縁膜を介してゲート電極材が形成され、これらによりトレンチ・ゲートが構成される。n型ドリフト層の裏面側にはn<sup>+</sup>型ドレイン領域を介してドレイン電極が形成される。

50

## 【0004】

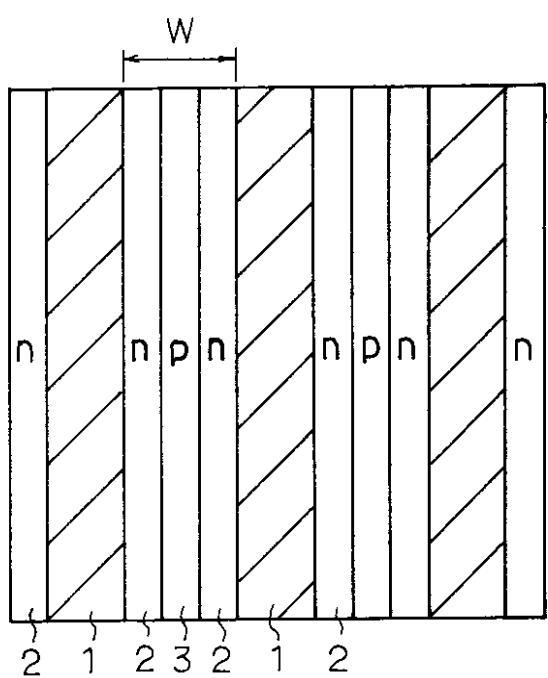

一方、p型ベース層の上にはn<sup>+</sup>型ソース領域とこれに隣接して形成されたp<sup>+</sup>型領域とが設けられる。さらに、これらの上部にはソース電極が形成される。従来のMOSFETにおいては、例えば図8に示すように、トレンチ・ゲート1に隣接させたn<sup>+</sup>型ソース領域2をそれぞれトレンチの形成方向（奥行き方向）に沿って形成し、さらにこれらn<sup>+</sup>型ソース領域2間にp<sup>+</sup>型領域3を形成した構造が一般的に採用されている（例えば特許文献1の図6参照）。しかし、このような構造ではトレンチ間隔がn<sup>+</sup>型ソース領域2とp<sup>+</sup>型領域3の幅に規制されることから、トレンチ間隔の狭小化に限界がある。

## 【0005】

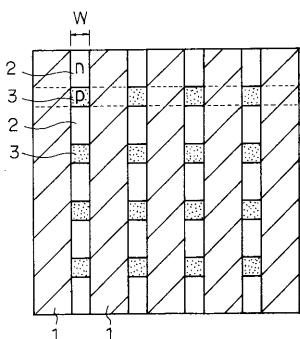

一方、微細化技術の進歩に伴って、トレンチ間距離Wは1μm以下とすることが可能になつてている。そこで、例えば図9に示すように、トレンチ・ゲート1間にn<sup>+</sup>型ソース領域2とp<sup>+</sup>型領域3とをトレンチの形成方向に沿って交互に隣接配置した構造、言い換えるとトレンチ・ゲート1と、交互に配置したn<sup>+</sup>型ソース領域2およびp<sup>+</sup>型領域3とを直交させた構造が提案されている。例えば、特許文献2には上記したような素子上部構造を適用したIGBTが記載されている。また、特許文献3にはトレンチ・ゲートに沿ったソース領域からインジエクタ領域までの長さが、これらの間の最短距離より長くなるようにトレンチ・ゲートを配置した素子構造が記載されている。

## 【0006】

上述したような素子上部構造（図9）を適用したパワーMOSFETにおいては、ゲート電極材に所定の電圧を印加すると、p型ベース層のうちのゲート絶縁膜に隣接した領域に反転層が形成され、ソース電極とドレイン電極との間でオン状態が形成される。このようなパワーMOSFETではトレンチ間隔を微細化することによって、素子実効面積に占める電流通路（チャネル）の割合を増加させることができる。従って、パワーMOSFETのオン状態での抵抗を低減することが可能となる。

【特許文献1】特許第3329707号公報

【特許文献2】特許第2950688号公報

【特許文献3】特開平9-116139号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0007】

しかしながら、図9に示したn<sup>+</sup>型ソース領域2とp<sup>+</sup>型領域3の配置構造において、オン抵抗を低減するためにはトレンチ・ゲート1間の素子領域に対するn<sup>+</sup>型ソース領域2が占める割合を大きくする必要がある。このときの最も大きな問題点としてはアバランシェ破壊が挙げられる。これは、インダクタンス負荷駆動直後にパワーMOSFETがオンからオフに移行する際に生じるブレイクダウン電流によって、任意のセルにおけるp型ベース層で大きく電圧降下が発生することに起因する。

## 【0008】

すなわち、n<sup>+</sup>型ソース領域/p型ベース層/n型ドリフト層からなる寄生n-p-nバイポーラトランジスタがオンすると大電流が流れる。この寄生バイポーラトランジスタが動作したセルは、動作しないセルと比較して耐圧が低下するため、電流はこのセルに集中して流れることになり、デバイス破壊に至る。図9に示した素子上部構造において、n<sup>+</sup>型ソース領域2の幅を広くするということは、チャネル近傍でブレイクダウンが生じた際に、p型ベース層を流れるホール電流がp<sup>+</sup>型領域3に流れ込むまでの道のりに高い抵抗が配置されていることに等しい。この抵抗が大きいと寄生n-p-nバイポーラトランジスタがオンしやすくなり、その結果としてアバランシェ破壊に至りやすい。

## 【0009】

本発明はこのような課題に対処するためになされたものであって、縦型MOSゲート構造（トレンチ・ゲート構造）を有する半導体装置の素子上部構造に基づくオン抵抗の低減効果を阻害することなく、アバランシェ耐量を高めることを可能にした半導体装置を提供することを目的としている。

10

20

30

40

50

**【課題を解決するための手段】****【0010】**

本発明の一態様に係る半導体装置は、第1導電型の第1の半導体層と、前記第1の半導体層上に設けられた第2導電型の第2の半導体層と、前記第2の半導体層を貫通して前記第1の半導体層に達するトレンチと、前記トレンチ内に絶縁膜を介して充填された導電材とを有するトレンチ・ゲートと、前記第2の半導体層上に前記トレンチ・ゲートの前記導電材と前記絶縁膜を介して隣接形成された第1導電型の第3の半導体領域と、前記第2の半導体層上に前記第3の半導体領域と前記トレンチ・ゲートに沿って交互に配置されるように隣接形成された第2導電型の第4の半導体領域とを具備し、前記第3の半導体領域および前記第4の半導体領域は、前記トレンチ・ゲートの長手方向に対して傾きを持って交差するように配置されていることを特徴している。

**【0011】**

本発明の他の態様に係る半導体装置は、第1導電型の第1の半導体層と、前記第1の半導体層上に設けられた第2導電型の第2の半導体層と、前記第2の半導体層を貫通して前記第1の半導体層に達するトレンチと、前記トレンチ内に絶縁膜を介して充填された導電材とを有するトレンチ・ゲートと、前記第2の半導体層上に前記トレンチ・ゲートの前記導電材と前記絶縁膜を介して隣接形成された第1導電型の第3の半導体領域と、前記第2の半導体層上に前記第3の半導体領域と前記トレンチ・ゲートに沿って交互に配置されるように隣接形成された第2導電型の第4の半導体領域とを具備し、前記第4の半導体領域は、実効素子領域における前記第4の半導体領域の占める割合が、駆動電圧が印加されるゲート信号入力端子領域に近い領域より遠い領域の方が大きくなるように形成されていることを特徴としている。

**【0012】**

本発明のさらに他の態様に係る半導体装置は、第1導電型の第1の半導体層と、前記第1の半導体層上に設けられた第2導電型の第2の半導体層と、前記第2の半導体層を貫通して前記第1の半導体層に達するトレンチと、前記トレンチ内に絶縁膜を介して充填された導電材とを有するトレンチ・ゲートと、前記第2の半導体層上に前記トレンチ・ゲートの前記導電材と前記絶縁膜を介して隣接形成された第1導電型の第3の半導体領域と、前記第2の半導体層上に前記第3の半導体領域と前記トレンチ・ゲートに沿って交互に配置されるように隣接形成された第2導電型の第4の半導体領域とを具備し、前記第3の半導体領域および前記第4の半導体領域は少なくとも一部が前記トレンチ・ゲートの長手方向に対して傾きを持って交差するように配置されており、かつ前記第4の半導体領域は実効素子領域における前記第4の半導体領域の占める割合が、駆動電圧が印加されるゲート信号入力端子領域に近い領域より遠い領域の方が大きくなるように形成されていることを特徴としている。

**【発明の効果】****【0013】**

本発明の一態様に係る半導体装置は、第3の半導体領域および第4の半導体領域をトレンチ・ゲートの長手方向に対して傾きを持って交差させているため、ブレイクダウン電流に対する第3の半導体領域直下のもぐり抵抗を低減することができる。これによって、寄生n-p-nバイポーラトランジスタの駆動が抑制されることから、オン抵抗の低減効果を阻害することなく、アバランシェ耐量を高めることができる。

**【0014】**

本発明の他の態様に係る半導体装置は、実効素子領域における第4の半導体領域の占める割合をゲート信号入力端子領域に近い領域より遠い領域の方が大きくなるように設定しているため、オン抵抗の低減効果を損なうことなく、オフタイミングのずれ等により電流が集中しやすい領域（ゲート信号入力端子領域から遠い領域）のアバランシェ耐量を高めることができる。

**【0015】**

本発明のさらに他の態様に係る半導体装置によれば、寄生n-p-nバイポーラトランジス

10

20

30

40

50

タの駆動を抑制すると共に、電流集中に対する耐性を高めることによって、オン抵抗の低減効果を損なうことなく、アバランシェ耐量を高めることが可能となる。

#### 【発明を実施するための最良の形態】

##### 【0016】

以下、本発明を実施するための形態について、図面を参照して説明する。なお、以下では本発明の実施形態を図面に基づいて述べるが、それらの図面は図解のみの目的のために提供されるものであり、本発明はそれらの図面に限定するものではない。

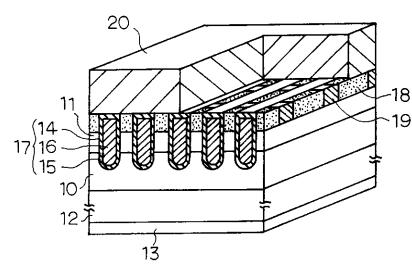

##### 【0017】

まず図1を参照して、本発明の実施形態による半導体装置の基本構造について述べる。図1は本発明の半導体装置を適用したnチャネル型トレンチMOSFETの要部基本構造を一部断面で示す斜視図である。なお、図1は半導体ウェーハ上に並列形成された複数の素子単位のうちの一部を抜き出して斜め上方から眺めた斜視図であって、MOSFET表面の配置を理解しやすいようにソース電極の一部を取り除いた状態を示している。

##### 【0018】

図1において、10はn型ドリフト層であり、このn型ドリフト層10上にはp型ベース層11が積層形成されている。n型ドリフト層10の下側にはn<sup>+</sup>型ドレイン領域12が存在しており、その裏面側にはドレイン電極13が形成されている。なお、これらの構造は、例えばn<sup>+</sup>型半導体ウェーハ(12)上にn<sup>-</sup>型層(n型ドリフト層10)とp型層(p型ベース層11)とを順に積層形成することにより作製される。

##### 【0019】

上記したn型ドリフト層10やp型ベース層11を有する半導体ウェーハの表面側には、p型ベース層11を貫通してn型ドリフト層10に達するトレンチ14が形成されている。トレンチ14内には、その内壁面に形成されたゲート絶縁膜15を介してゲート電極材16が充填されており、これらによりトレンチ・ゲート17が構成されている。ゲート電極材17には、例えばポリシリコンのような導電材が用いられる。

##### 【0020】

一方、p型ベース層11上にはn<sup>+</sup>型ソース領域18とp<sup>+</sup>型領域19とが形成されている。これらn<sup>+</sup>型ソース領域18とp<sup>+</sup>型領域19は、トレンチ・ゲート17間の素子領域内に形成されており、さらにトレンチ・ゲート17の長手方向(トレンチ14の形成方向/図中奥行き方向)に沿って交互に隣接して配置されている。n<sup>+</sup>型ソース領域18はトレンチ・ゲート17のゲート電極材16とゲート絶縁膜15を介して隣接している。さらに、n<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19の上部には、これらと接続するソース電極20が形成されている。

##### 【0021】

上述したトレンチ・ゲート17は、例えば以下のようにして作製される。まず、素子上面に一方向のトレンチ14を並行に形成する。トレンチ14の内壁面にゲート絶縁膜15を形成した後、ゲート電極材16を充填し、さらにゲート電極材16の上部もゲート絶縁膜15で覆うことによって、トレンチ・ゲート17を作製する。次いで、p型ベース層11上にトレンチ・ゲート17と交差するように、n<sup>+</sup>型ソース領域18となる領域とp<sup>+</sup>型領域19となる領域を、それぞれストライプ状に交互に隣接させて形成する。なお、各ストライプ領域はトレンチ・ゲート17で分断されることで、トレンチ・ゲート17間の素子領域に交互に隣接形成されたn<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19となる。

##### 【0022】

このような素子構造を有するパワーMOSFETにおいて、ゲート電極材16に所定の電圧を印加すると、p型ベース層11のうちのゲート絶縁膜15に隣接した領域に反転層が形成され、ソース電極20とドレイン電極13との間でオン状態が形成される。また、パワーMOSFETのオンからオフへの移行時にチャネル近傍でブレイクダウンが生じた際に、p型ベース層11を流れるホール電流はp<sup>+</sup>型領域19に流れ込む。

##### 【0023】

本発明の半導体装置を適用した第1の実施形態によるパワーMOSFETは、上述した

10

20

30

40

50

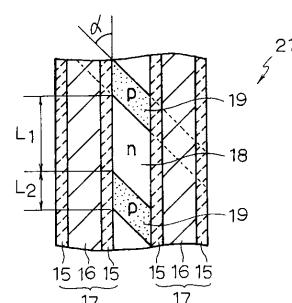

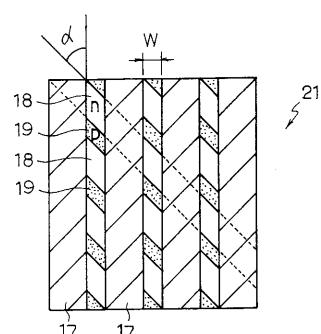

基本構造(図1に示したトレンチ・ゲート構造を有するMOSFETの基本構造)を有し、かつ図2および図3に示すように、n<sup>+</sup>型ソース領域18とp<sup>+</sup>型領域19とがトレンチ・ゲート17の長手方向に対して傾きを持って交差するように配置されている。図2は第1の実施形態によるパワーMOSFET21の素子上部構造(ソース電極20を取り除いた部分の構造)を示す平面図であり、図3はパワーMOSFET21のトレンチ・ゲート17とn<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19とが存在する部分を平面方向(横方向)に切断した要部拡大断面図である。

#### 【0024】

すなわち、トレンチ・ゲート17はn<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19の形成方向に対して角度 $\theta$ を持って交差するように配置されている。n<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19の形成方向とは、上述したようにトレンチ14を形成する前の状態における各ストライプ領域の形成方向を示すものであり、このn<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19の形成方向に対してトレンチ・ゲート17の長手方向(トレンチ14の形成方向)は角度 $\theta$ で示される傾きを持って交差している。言い換えると、n<sup>+</sup>型ソース領域18とp<sup>+</sup>型領域19との界面は、トレンチ・ゲート17の長手方向に対して角度 $\theta$ だけ傾いた状態で配置されている。

#### 【0025】

上記したように、n<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19をトレンチ・ゲート17の長手方向に対して傾きを持って交差するように配置することによって、n<sup>+</sup>型ソース領域18の下部に位置するp型ベース層11の各部からp<sup>+</sup>型領域19までの距離を短縮することができる。このp型ベース層11からp<sup>+</sup>型領域19までの距離の短縮は、チャネル近傍で生じたブレイクダウン電流に対するn<sup>+</sup>型ソース領域18直下のもぐり抵抗が低減されることを意味する。このように、n<sup>+</sup>型ソース領域18直下のもぐり抵抗を低減することで、前述した寄生n-p-nバイポーラトランジスタの駆動に基づく電流集中が低減されることから、寄生n-p-nバイポーラトランジスタの駆動に起因するアバランシェ破壊の発生を抑制することが可能となる。

#### 【0026】

このようなn<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19の斜め配置に基づくアバランシェ耐量の向上効果は、図3に示すn<sup>+</sup>型ソース領域18の基準長さ(トレンチ・ゲート17と接する部分の長さ)L<sub>1</sub>とp<sup>+</sup>型領域19の基準長さ(トレンチ・ゲート17と接する部分の長さ)L<sub>2</sub>との比率を、従来の直交構造と同一とした上で実現される。従って、トレンチ間距離Wを一定とした場合、トレンチ・ゲート17間の素子領域に対してn<sup>+</sup>型ソース領域18が占める割合を維持してオン抵抗の低減を図った上で、アバランシェ耐量を高めることができる。これによって、トレンチ・ゲート構造を有するパワーMOSFET21の実用性や信頼性等を向上させることが可能となる。なお、L<sub>1</sub>とL<sub>2</sub>との比率は任意に設定可能であり、例えばL<sub>1</sub> : L<sub>2</sub> = 2 : 1 ~ 5 : 1の範囲とされる。

#### 【0027】

上述したn<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19の形成方向とトレンチ・ゲート17の長手方向とが成す角度 $\theta$ は、従来の直交構造に対してもぐり抵抗の低減効果が得られる範囲で任意に設定可能である。半導体製造技術におけるマスクアライメントの精度は±1°以下であるため、このようなアライメント精度を超える範囲で角度 $\theta$ を設定することができる。ただし、角度 $\theta$ が大きすぎると従来の直交構造と比較した場合のアバランシェ耐量の向上効果が不十分となるため、角度 $\theta$ は75°以下とすることが好ましい。一方、角度 $\theta$ が小さすぎると各領域18、19の形状が不安定になり、特性の低下等を招くおそれがあるため、角度 $\theta$ は10°以上とすることが好ましい。

#### 【0028】

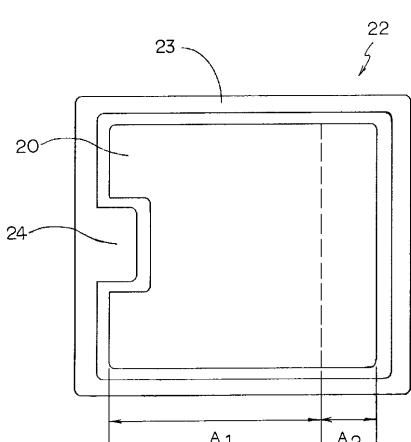

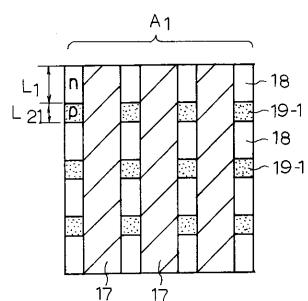

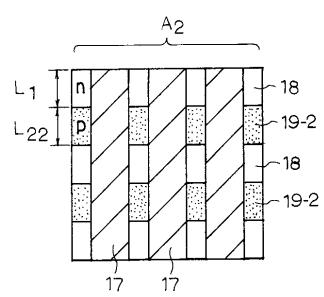

次に、本発明の第2の実施形態による半導体装置について説明する。本発明の半導体装置を適用した第2の実施形態によるパワーMOSFETは、上述した基本構造(図1に示したトレンチ・ゲート構造を有するMOSFETの基本構造)を有し、かつ図4ないし図6に示すように、実効素子領域におけるp<sup>+</sup>型領域19の占める割合に基づいて複数の領

10

20

30

40

50

域  $A_1$ 、 $A_2$  が設定されている。図 4 は第 2 の実施形態によるパワー MOSFET 2 2 の平面図である。図 4 において、2 3 はゲート電極、2 4 は駆動電圧が印加されるゲート信号入力端子領域である。すなわち、ゲート電極 2 3 には領域 2 4 に接続された外部端子からゲート信号が入力され、パワー MOSFET 2 2 のオン・オフ動作が制御される。

#### 【0029】

ここで、アバランシェ破壊に至る原因は、前述した寄生  $n-p-n$  バイポーラトランジスタの駆動に起因する場合に加えて、パワー MOSFET のゲートが不均一にオフすることに起因する場合が考えられる。つまり、ゲートがオンしている状態ではチャネルに電流が流れているが、ゲート信号入力端子領域 2 4 にオフの信号が入ったとき、ゲート信号入力端子領域 2 4 に近いセルと遠いセルとではオフのタイミングにずれが生じる場合がある。これはメタル層とポリシリコン等の導電材からなるゲート電位のネットワークが、ゲート信号入力端子領域 2 4 から遠い部分でゲート抵抗の増加により遅延が生じるためである。

10

#### 【0030】

インダクタンス負荷駆動直後のオンからオフへの過渡状態において、ゲート抵抗の増加に基づく遅延が生じると、オフしているセルとオンしているセルとが同時に存在することとなる。この場合、遅れてオフしたセルにブレイクダウン電流が集中し、アバランシェ破壊に至りやすい。このような理由でゲート信号入力端子領域 2 4 から遠いセルでは電流集中が生じやすい。ゲート信号入力端子領域 2 4 からの距離に基づくオフ時の電流集中を抑制してアバランシェ破壊を防ぐためには、ゲート電位のネットワークの抵抗を低減し、パワー MOSFET 全体を均一にオン・オフさせることが考えられる。

20

#### 【0031】

ここで、第 2 の実施形態によるパワー MOSFET (トレンチ・ゲート構造を有する MOSFET) においては、ゲート信号入力端子領域 2 4 からの距離に基づいて実効素子領域における  $p^+$  型領域 1 9 の占める割合を設定している。すなわち、実効素子領域における  $p^+$  型領域 1 9 の占める割合が、ゲート信号入力端子領域 2 4 に近い領域  $A_1$  より遠い領域  $A_2$  の方が大きくなるように設定されている。このように、 $p^+$  型領域 1 9 の占める割合を大きくすることによって、アバランシェ耐量を高めることができる。従って、ゲート信号入力端子領域 2 4 から遠い領域  $A_2$ 、すなわちオフタイミングに遅れが生じやすい領域  $A_2$ において、オフタイミングの遅れによるブレイクダウン電流の集中が生じたとしても、領域  $A_2$  でのアバランシェ破壊を抑制することが可能となる。

30

#### 【0032】

トレンチ間距離  $W$  を一定とした場合、ゲート信号入力端子領域 2 4 に近い領域  $A_1$  はオン抵抗の低減効果が得られるように、 $n^+$  型ソース領域 1 8 の基準長さ (トレンチ・ゲート 1 7 と接する部分の長さ)  $L_1$  と  $p^+$  型領域 1 9-1 の基準長さ (トレンチ・ゲート 1 7 と接する部分の長さ)  $L_{21}$  との比率の設定されている。一方、ゲート信号入力端子領域 2 4 から遠い領域  $A_2$  はアバランシェ耐量を高めるように、 $n^+$  型ソース領域 1 8 の基準長さ  $L_1$  と  $p^+$  型領域 1 9-2 の基準長さ  $L_{22}$  との比率の設定されている。

#### 【0033】

具体的には、 $n^+$  型ソース領域 1 8 の基準長さ  $L_1$  を一定とした場合、領域  $A_2$  の  $p^+$  型領域 1 9-2 の基準長さ  $L_{22}$  は領域  $A_1$  の  $p^+$  型領域 1 9-1 の基準長さより長く設定されている。これによって、ゲート信号入力端子領域 2 4 から遠い領域  $A_2$  における  $p^+$  型領域 1 9 の占める割合を、ゲート信号入力端子領域 2 4 に近い領域  $A_1$  のそれより大きくすることができる。また、 $p^+$  型領域 1 9 の基準長さ  $L_2$  を一定とし、 $n^+$  型ソース領域 1 8 の基準長さ  $L_1$  を変化させることによっても同様な効果が得られる。

40

#### 【0034】

このように、領域  $A_2$  における  $p^+$  型領域 1 9 の割合を領域  $A_1$  のそれより大きくすることによって、オフタイミングのずれによる電流集中に対するアバランシェ耐量を高めることができる。また、素子領域全体の大半を占める領域  $A_1$  はスイッチングが早く、かつ  $n^+$  型ソース領域 1 8 が占める割合を大きくすることで、オン抵抗の低減を図ることができる。従って、オン抵抗の低減を図った上で、パワー MOSFET 2 2 全体としてのアバラン

50

シェ耐量を高めることが可能となる。これはトレンチ・ゲート構造を有するパワーMOSFETの実用性や信頼性等の向上に大きく寄与するものである。

#### 【0035】

ここで、領域A<sub>2</sub>におけるn<sup>+</sup>型ソース領域18の基準長さL<sub>1</sub>とp<sup>+</sup>型領域19-2の基準長さL<sub>22</sub>との比率は、上記した条件を満足させることができ可能な範囲内で、目的とするオン抵抗とアバランシェ耐量との兼合いに基づいて任意に設定可能である。例えば、領域A<sub>2</sub>におけるL<sub>1</sub>とL<sub>21</sub>との比率をL<sub>1</sub> : L<sub>21</sub> = 2 : 1 ~ 5 : 1とした場合、領域A<sub>2</sub>におけるL<sub>1</sub>とL<sub>22</sub>との比率はL<sub>1</sub> : L<sub>22</sub> = 2 : 1 ~ 1 : 2とすることが好ましい。また、領域A<sub>2</sub>の設定範囲についても同様であり、目的とするオン抵抗とアバランシェ耐量との兼合いに基づいて任意に設定可能である。これらオン抵抗とアバランシェ耐量のバランスを考慮すると、領域A<sub>2</sub>の面積は素子領域全体の5~30%の範囲とすることが好ましい。10

#### 【0036】

なお、実効素子領域におけるp<sup>+</sup>型領域19の占める割合が異なる領域は、図4に示したように2箇所の領域（領域A<sub>1</sub>と領域A<sub>2</sub>）に限られるものではなく、例えば3箇所もしくはそれ以上の領域を設定することも可能である。この場合、p<sup>+</sup>型領域19の占める割合はゲート信号入力端子領域24からの距離に基づいて徐々に増加させることができよい。さらに、p<sup>+</sup>型領域19の占める割合は、ゲート信号入力端子領域24に近い部分から遠い部分に向けて連続的に変化させることも可能である。

#### 【0037】

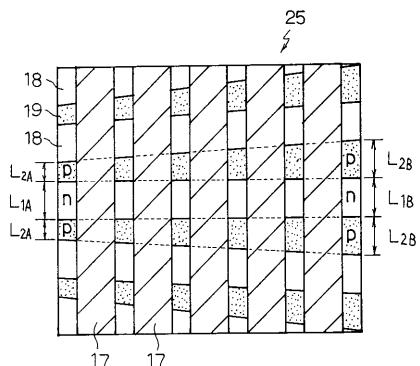

次に、本発明の第3の実施形態による半導体装置について説明する。本発明の半導体装置を適用した第3の実施形態によるパワーMOSFETは、前述した基本構造（図1に示したトレンチ・ゲート構造を有するMOSFETの基本構造）を有し、かつ図7に示す素子上部構造を有している。図7は図2と同様に、第3の実施形態によるパワーMOSFET25の素子上部構造（ソース電極20を取り除いた部分の構造）を示す平面図である。20

#### 【0038】

図7に示すパワーMOSFET25の素子上部構造において、n<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19の形成方向は、実効素子領域におけるp<sup>+</sup>型領域19の占める割合がゲート信号入力端子領域に近い領域（図中左側端部領域）より遠い領域（図中右端部領域）の方が大きくなるように、トレンチ・ゲート17の長手方向（トレンチ14の形成方向）に対して少なくとも一部が傾きを持っている。すなわち、n<sup>+</sup>型ソース領域18の基準長さL<sub>1</sub>とp<sup>+</sup>型領域19の基準長さL<sub>2</sub>との比率（L<sub>2</sub> / L<sub>1</sub>）は、ゲート信号入力端子領域に近い領域（L<sub>2A</sub> / L<sub>1A</sub>）から遠い領域（L<sub>2B</sub> / L<sub>1B</sub>）に向けて連続的に増加している。30これによって、第2の実施形態と同様にオフタイミングのずれによる電流集中に対するアバランシェ耐量を高めることができる。

#### 【0039】

さらに、n<sup>+</sup>型ソース領域18およびp<sup>+</sup>型領域19の形成方向とトレンチ・ゲート17の長手方向とが傾きを持って配置されていることから、n<sup>+</sup>型ソース領域18とp<sup>+</sup>型領域19との界面の少なくとも一部はトレンチ・ゲート17の長手方向に対して傾いた状態で配置されている。これによって、第1の実施形態と同様にチャネル近傍で生じたブレイクダウン電流に対するn<sup>+</sup>型ソース領域18直下のもぐり抵抗が低減されることから、寄生n-p-nバイポーラトランジスタの駆動を抑制することができる。40

#### 【0040】

このように、第3の実施形態によるパワーMOSFET25においては、オフタイミングのずれによる電流集中に対するアバランシェ耐量の向上と寄生n-p-nバイポーラトランジスタの駆動に基づく電流集中の緩和を共に実現することができる。これによって、パワーMOSFET25のオン抵抗の低減を図った上で、アバランシェ破壊の発生をより効果的に抑制することが可能となる。なお、パワーMOSFET25におけるL<sub>1</sub>とL<sub>2</sub>との比率や各領域18、19の形成角度等の具体的な条件は、第1および第2の実施形態と同様とすることが好ましい。

#### 【図面の簡単な説明】

## 【0041】

【図1】本発明の実施形態によるパワーMOSFETの要部基本構造を一部断面で示す斜視図である。

【図2】本発明の第1の実施形態によるパワーMOSFETの素子上部構造を示す平面図である。

【図3】本発明の第1の実施形態によるパワーMOSFETの要部を拡大して示す断面図である。

【図4】本発明の第2の実施形態によるパワーMOSFETの平面図である。

【図5】図4に示すパワーMOSFETのゲート信号入力端子領域に近い領域の素子上部構造を示す平面図である。 10

【図6】図4に示すパワーMOSFETのゲート信号入力端子領域から遠い領域の素子上部構造を示す平面図である。

【図7】本発明の第3の実施形態によるパワーMOSFETの素子上部構造を示す平面図である。

【図8】従来のパワーMOSFETの素子上部構造の一例を示す平面図である。

【図9】従来のパワーMOSFETの素子上部構造の他の例を示す平面図である。

## 【符号の説明】

## 【0042】

10 ... n型ドリフト層、 11 ... p型ベース層、 12 ... n<sup>+</sup>型ドレイン領域、 13 ... ドレン電極、 14 ... トレンチ、 15 ... ゲート絶縁膜、 16 ... ゲート電極材、 17 ... トレンチ・ゲート、 18 ... n<sup>+</sup>型ソース領域、 19 ... p<sup>+</sup>型領域、 20 ... ソース電極、 21、 22、 25 ... パワーMOSFET、 23 ... ゲート電極、 24 ... ゲート信号入力端子領域。 20

【図1】

【図3】

【図2】

【図4】

【 图 5 】

【 图 6 】

【 四 7 】

【 四 8 】

【 四 9 】

---

フロントページの続き

(72)発明者 山口 好広

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 松木 宏文

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

(72)発明者 荒井 清孝

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝 マイクロエレクトロニクスセンター内

審査官 小野田 誠

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78