(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6666258号

(P6666258)

(45) 発行日 令和2年3月13日(2020.3.13)

(24) 登録日 令和2年2月25日(2020.2.25)

(51) Int.Cl.

F 1

H02M 1/08 (2006.01)

H03K 17/082 (2006.01)H02M 1/08

H03K 17/082

A

請求項の数 19 (全 21 頁)

(21) 出願番号 特願2016-558712 (P2016-558712)

(86) (22) 出願日 平成27年7月9日(2015.7.9)

(65) 公表番号 特表2017-521982 (P2017-521982A)

(43) 公表日 平成29年8月3日(2017.8.3)

(86) 國際出願番号 PCT/EP2015/065712

(87) 國際公開番号 WO2016/005501

(87) 國際公開日 平成28年1月14日(2016.1.14)

審査請求日 平成30年6月25日(2018.6.25)

(31) 優先権主張番号 62/022,304

(32) 優先日 平成26年7月9日(2014.7.9)

(33) 優先権主張国・地域又は機関

米国(US)

(31) 優先権主張番号 14/744,862

(32) 優先日 平成27年6月19日(2015.6.19)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 516046879

パワー インテグレーションズ スイッツ

ランド ゲーエムペーハー

Power Integrations

Switzerland GmbH

スイス 2504 ビール-ビエンヌ ヨ

ハン-レンフェル-シュトラッセ 15

(74) 代理人 100100181

弁理士 阿部 正博

(74) 復代理人 100125818

弁理士 立原 聰

(72) 発明者 タールハイム ヤン

スイス ビール-ビエンヌ ツェーハー-

2504 ローレンヴェグ 65

最終頁に続く

(54) 【発明の名称】動的タイミングでの多ステージゲートオフ切り替え

## (57) 【特許請求の範囲】

## 【請求項 1】

電力半導体スイッチをオフに切り替える回路であって、

前記電力半導体スイッチの制御端子への前記電力半導体スイッチをオフに切り替える信号をスイッチングするように接続されたオフ切り替えトランジスタと、

オフ切り替え中に前記電力半導体スイッチの前記制御端子における電圧を制御するフィードバック制御ループと、

を備え、

前記フィードバック制御ループが、

前記電力半導体スイッチの前記制御端子の前記電圧の測定結果をフィードバックするフィードバック経路と、

制御端子基準電圧生成器であって、前記制御端子基準電圧生成器が、前記電力半導体スイッチを通る電流の伝導における異常の検出を示す異常信号に応答した時間依存基準電圧を生成するように構成されており、および、前記制御端子基準電圧生成器が、通常動作中における固定の基準電圧を生成するように構成されている、前記制御端子基準電圧生成器と、

前記制御端子の前記電圧と前記時間依存基準電圧との間の差分を表すエラー信号を生成するエラー増幅器と、

前記オフ切り替えトランジスタによる前記電力半導体スイッチの前記制御端子への前記電力半導体スイッチをオフに切り替える前記信号の前記スイッチングを制御するために

前記エラー信号を前方に伝達する転送経路と、

を含み、

前記電力半導体スイッチをオフに切り替える回路が、

前記電力半導体スイッチの前記制御端子の前記電圧が前記電力半導体スイッチのミラープラトーの近傍の電圧レベル未満であることを検出することと、前記電力半導体スイッチの前記制御端子の前記電圧が前記電力半導体スイッチの前記ミラープラトーの前記近傍の前記電圧レベル未満であることを示す信号を出力することを行いうように接続されたミラープラトー検出回路をさらに備え、

前記制御端子基準電圧生成器は、前記電力半導体スイッチの前記制御端子の前記電圧が前記ミラープラトーの前記近傍の前記電圧レベル未満であることを示す前記信号に応答して、前記時間依存基準電圧の時間変化率を増加させる、

電力半導体スイッチをオフに切り替える回路。

【請求項 2】

前記ミラープラトー検出回路が、前記電力半導体スイッチの前記制御端子への電流を検出するように接続された制御端子電流検出回路を備える、

請求項 1 に記載の回路。

【請求項 3】

前記ミラープラトー検出回路が、前記オフ切り替えトランジスタの制御入力を使用して、前記電力半導体スイッチの前記制御端子の前記電圧が前記電力半導体スイッチの前記ミラープラトーの前記近傍における前記電圧レベル未満であることを検出する、

請求項 1 に記載の回路。

【請求項 4】

前記制御端子基準電圧生成器が、

前記時間依存基準電圧を、前記電力半導体スイッチがオンである第 1 の値から、前記電力半導体スイッチのミラープラトーの近傍における第 2 の値に変化させる第 1 の回路と、

前記時間依存基準電圧を、前記電力半導体スイッチの前記ミラープラトーの前記近傍における第 3 の値から、前記電力半導体スイッチがオフである第 4 の値に変化させる第 2 の回路と、

を備える、

請求項 1 から請求項 3 のいずれか一項に記載の回路。

【請求項 5】

前記第 1 の回路は、前記第 2 の回路が前記時間依存基準電圧を変化させる時間変化率未満の時間変化率で、前記時間依存基準電圧を変化させる、

請求項 4 に記載の回路。

【請求項 6】

前記第 1 の回路が、400 ナノ秒から 4000 ナノ秒の間に、前記第 1 の値から前記第 2 の値まで前記時間依存基準電圧を変化させる、

請求項 4 または請求項 5 に記載の回路。

【請求項 7】

前記第 2 の回路が、100 ナノ秒から 2000 ナノ秒の間に、前記第 3 の値から前記第 4 の値まで前記時間依存基準電圧を変化させる、

請求項 4 または請求項 5 に記載の回路。

【請求項 8】

前記第 2 の回路が、10 ナノ秒から 100 ナノ秒の間に、前記第 3 の値から前記第 4 の値まで前記時間依存基準電圧を変化させる、

請求項 4 または請求項 5 に記載の回路。

【請求項 9】

前記第 2 の値が、前記電力半導体スイッチの前記ミラープラトーを上回っており、

前記第 3 の値が、前記電力半導体スイッチの前記ミラープラトー未満である、

10

20

30

40

50

請求項 4 から請求項 6 のいずれか一項に記載の回路。

【請求項 1 0】

前記制御端子基準電圧生成器が、前記時間依存基準電圧を前記第 2 の値と前記第 3 の値との間で一定に保持する回路を備える、

請求項 4 から請求項 6 のいずれか一項に記載の回路。

【請求項 1 1】

前記電力半導体スイッチを通る前記電流の伝導における前記異常の検出に応答して、前記異常信号を出力するように接続された異常検出回路をさらに備え、

前記制御端子基準電圧生成器が、前記異常信号に応答して、前記電力半導体スイッチが開いているときの前記固定の基準電圧の値から前記時間依存基準電圧を変化させ始める、

請求項 1 から請求項 1 0 のいずれか一項に記載の回路。

【請求項 1 2】

前記異常検出回路が、前記電力半導体スイッチのコレクタ・エミッタ電圧を検出する回路を備える、

請求項 1 1 に記載の回路。

【請求項 1 3】

前記電力半導体スイッチをオフに切り替える前記信号が、電流であり、

前記回路が、オフ切り替えゲート抵抗器をさらに備える、

請求項 1 から請求項 1 2 のいずれか一項に記載の回路。

【請求項 1 4】

前記電力半導体スイッチが、IGBT である、

請求項 1 から請求項 1 3 のいずれか一項に記載の回路。

【請求項 1 5】

前記オフ切り替えトランジスタが、N MOSトランジスタである、

請求項 1 から請求項 1 4 のいずれか一項に記載の回路。

【請求項 1 6】

半導体スイッチのオフ切り替え回路であって、

可変抵抗を有する要素であって、

当該要素が、前記半導体スイッチの制御入力に接続されている、

当該要素と、

前記半導体スイッチの制御入力電圧または制御入力電流におけるミラープラトーの終端を検出するように設計された検出回路と、

前記半導体スイッチを通る電流の伝導における異常の検出を示す異常信号に応答して、前記半導体スイッチの前記制御入力に現れる電圧が前記ミラープラトーの前記終端後に所定の速度で低減されるように、前記可変抵抗を有する前記要素の抵抗値を制御するように設計された制御回路であって、前記所定の速度が、前記半導体スイッチの制御端子に現れる信号の閉ループ制御により設定される、当該制御回路と、

を備える、半導体スイッチのオフ切り替え回路。

【請求項 1 7】

前記ミラープラトーの前記終端が、前記可変抵抗を有する前記要素の制御入力における電圧に基づいて検出される、

請求項 1 6 に記載のオフ切り替え回路。

【請求項 1 8】

前記ミラープラトーの前記終端は、前記可変抵抗を有する前記要素の前記制御入力における前記電圧が所定の信号レベル未満に立ち下がったときに検出される、

請求項 1 7 に記載のオフ切り替え回路。

【請求項 1 9】

前記所定の信号レベルが、前記可変抵抗を有する前記要素の予定ゲート閾値電圧の 50 % から 150 % の範囲にある、

請求項 1 8 に記載のオフ切り替え回路。

10

20

30

40

50

**【発明の詳細な説明】****【技術分野】****【0001】**

(関連出願の相互参照)

本出願は、発明の名称を「動的タイミングでの多ステージゲートオフ切り替え」とする2014年7月09日に出願された米国仮特許出願第62/022,304号の優先権を主張する。

**【0002】**

本出願は、発明の名称を「動的タイミングでの多ステージゲートオフ切り替え」とする2015年6月19日に出願された米国特許出願第14/744,862号の優先権を主張する。

10

**【0003】**

本発明は、半導体スイッチのオフ切り替え回路と、半導体スイッチのオフ切り替え回路とアクティブクランプ回路とを備えるシステムと、半導体スイッチをオフに切り替える方法に関する。

**【背景技術】****【0004】**

短絡状態及び/または過電流状態が発生した場合に半導体スイッチ(及び、特に電力半導体スイッチ)をオフに切り替えるいくつかの方法がよく知られている。一例において、半導体スイッチの制御入力(例えば、ゲート端子)は、第1の抵抗と第2の抵抗とに接続され得、第1の抵抗は、通常動作中、半導体スイッチの制御入力を基準電位(例えば、半導体スイッチのエミッタ電圧)に接続することにより、半導体スイッチをオフに切り替えるように配置されている。短絡及び/または過電流状態が発生すると、より大きな第2の抵抗が、この時点で、半導体スイッチの制御入力と基準電位との間に接続され得る。その結果、半導体スイッチの制御入力を放電する電流が低減する。半導体スイッチの制御入力における電圧が、通常動作中より低速で低減される。従って、半導体スイッチの出力における負荷に加わる寄生インダクタンスによって定まる、半導体スイッチ内の危険な過電圧状態をもたらし得る過度に急激なオフ切り替え動作を防止することができる。

20

**【発明の概要】****【0005】**

30

半導体スイッチの第1のオフ切り替え回路は、可変抵抗を有する要素であって、当該要素が、半導体スイッチの制御入力に接続されている、当該要素と、制御入力基準信号を生成する回路と、半導体スイッチをオフに切り替えるため閉制御ループ内で制御入力基準信号に応答して可変抵抗を有する要素の抵抗を調節するように設計された制御回路とを備える。

**【0006】**

閉制御ループ内の可変抵抗を有する要素の調整は、様々な異なる半導体スイッチで満足のゆく結果を達成する動的オフ切り替え回路を提供することを可能にする。半導体スイッチの制御入力(例えば、ゲート入力を通る)を通る電流は、可変抵抗を有する要素の調節された抵抗を介して調節され得るので、オフ切り替え回路は、それぞれの半導体スイッチに動的に適合することが可能である。従来の引用文献でのいくつかのオフ切り替え回路において、制御入力電圧の満足のゆく波形を確実にするため、異なる半導体スイッチに対して異なる構成要素を使用する必要がある。例えば、上記の例において、異なる種類の半導体スイッチに対して異なる寸法の抵抗を使用することが示され得る。この適合が発生しない場合、短絡状態がより長く続くこと(抵抗が必要より大きい場合)、または、半導体スイッチの出力における負荷にかかる電圧が十分に低減されないことが発生し得る。他のより複雑なオフ切り替え回路は、より多くの、及び/または、高価な構成要素を必要とする。

40

**【0007】**

半導体スイッチの第2のオフ切り替え回路は、可変抵抗を有する要素であって、が半導

50

体スイッチの制御入力に接続されている、当該要素と、半導体スイッチの制御入力電圧または対応する制御入力電流におけるミラープラトーの終端を検出するように設計された検出回路と、半導体スイッチの制御入力に現れる電圧がミラープラトーの終端の後、所定の速度で低減されるような方法で、可変抵抗を有する要素の抵抗値を制御するように設計された制御回路と、を備える。

【0008】

半導体スイッチのオフ切り替え波形をミラープラトーの終端の検出に結び付けることにより、第2のオフ切り替え回路は、同様に異なる半導体スイッチに動的に適合され得る。ミラープラトー（すなわち、半導体スイッチの制御入力と半導体スイッチのソース、エミッタまたはカソード入力との間の電圧が実質的に一定に留まるように、制御入力を通る全電流が制御入力と半導体スイッチのドレイン入力、コレクタ入力またはアノード入力との間の寄生容量の充電に実質的に寄与する領域）は、異なる半導体スイッチに対して（多くの場合、幅広い温度と工程パラメータに対してさえ）、同様の電圧範囲内であり得る。例えば、多くのIGBTにおいて、ミラープラトーは、9.5ボルトから11.5ボルトの間であり得る。さらに、ミラープラトーの終端は、短絡及び/または過電流が発生した場合に半導体スイッチのドレイン電流、コレクタ電流またはアノード電流が、安全なレベルまで低減される時間を示し得、その一方で、オフ切り替え動作の継続は、半導体スイッチの出力にかかる高い過電圧をもたらさない場合があり得る。従って、半導体スイッチのオフ切り替え特性における変化に対する有益な動的スイッチング点が選択され得る。

【0009】

第1の実施形態において、半導体スイッチのオフ切り替え回路は、可変抵抗を有する要素であって、当該要素が半導体スイッチの制御入力に接続されている、当該要素と、制御入力基準信号を生成する回路と、半導体スイッチをオフに切り替えるため閉制御ループ内で制御入力基準信号に応答して可変抵抗を有する要素の抵抗を調節するように設計された制御回路と、を含む。

【0010】

このオフ切り替え回路は、以下の特徴の1つ以上をもち得る。例えば、可変抵抗を有する要素は、半導体スイッチである。さらなる例において、可変抵抗を有する要素は、MOSFET半導体スイッチである。さらに、可変抵抗を有する要素の可変抵抗は、半導体スイッチのドレイン、アノードまたはコレクタ端子とソース、カソードまたはエミッタ端子との間に形成されている。さらに、可変抵抗を有する要素は、さらなる抵抗半導体スイッチの制御入力と基準電位との間に直列に接続されている。例えば、制御入力基準信号は、第1の速度での第1の低減と、実質的に一定の信号レベルである領域と、第2の速度での第2の低減とを伴う。他の例として、第2の速度は、第1の速度より大きい。さらに、第1速度と第2の速度とは、時間的に変化する。さらなる例において、オフ切り替え回路は、半導体スイッチの制御入力電圧または制御入力電流におけるミラープラトーの終端を検出するように設計された検出回路をさらに含み、制御入力基準信号を生成する回路は、所定の速度でのミラープラトーの終端の検出に応答して、制御入力基準信号のレベルを低減するように設計されている。さらに、ミラープラトーの終端は、可変抵抗を有する要素の制御入力における電圧に基づいて検出される。さらに、ミラープラトーの終端は、可変抵抗を有する要素の制御入力における電圧が、所定の信号レベル未満に立ち下がったときに検出される。例えば、所定の信号レベルは、可変抵抗を有する要素の予定ゲート閾値電圧の50%から150%の範囲にある。他の例において、所定の信号レベルは、0.3から2ボルトの範囲にある。さらに、所定の信号レベルは、可変抵抗を有する要素と同じ技術に基づいて、基準電流によって、及び第2の要素によって決定される。場合によっては、第2の要素の面積またはゲート幅は、可変抵抗を有する要素の領域またはゲート幅のK倍であり、基準電流は、ミラープラトーの終端に対して設計されている可変抵抗を有する要素の出力電流の閾値のK倍であるように選択される。例えば、基準電流は、可変抵抗を有する第2の要素の制御入力、特にゲートと、可変抵抗を有する第2の要素の出力、特にドレインとに接続されている。さらに、基準電流は、100マイクロアンペア未満であるよ

10

20

30

40

50

うに選択され、Kは、1%未満であるように選択される。場合によっては、ミラープラト

ーの終端に達する前における制御入力基準信号のレベルは、実質的に一定であり、ミラープラト

ーの終端の検出に応答して、制御入力基準信号の信号レベルは、所定の速度で低減

される。さらに、オフ切り替え回路は、半導体スイッチの制御入力における電圧を検出する

回路をさらに備える。他の例と同様に、制御回路は、制御入力基準信号と半導体スイッ

チの制御入力における電圧とに応答して、可変抵抗を有する要素の抵抗を調節するよう

に設計されている。さらに、制御回路は、制御入力基準信号を半導体スイッチの制御入力

における電圧と比較するため第1の比較回路を備える。例えば、第1の比較回路の出力に応

答して、可変抵抗を有する要素に対する制御信号を生成する回路である。例えば、制御信

号を生成する回路は、第1の比較回路の出力と半導体スイッチの異常状態を示す異常信号

との比較に応答して、可変抵抗を有する要素に対する制御信号を生成するように設計され

た第2の比較回路を備える。さらに、オフ切り替え回路は、半導体スイッチの異常状態を

示す異常信号を受信するように設計されている。さらに、半導体スイッチの異常状態は、

短絡状態及び/または過電流状態である。他の例において、半導体スイッチは、電力半導

体スイッチである。さらなる例として、電力半導体スイッチは、IGBT、IEGT、パ

ワーMOSFET、または電力バイポーラトランジスタである。場合によっては、オフ切

り替え回路は、アクティブクランプ回路をさらに備える。例えば、ミラープラト

ーの終端は、可変抵抗を有する要素にかかる電圧に基づいて検出される。さらに、ミラープラト

ーの終端は、半導体スイッチの制御入力における電流に基づいて検出される。さらに、ミラ

ープラトーの終端は、半導体スイッチにかかる電圧に基づいて検出される。場合によ

りは、ミラープラトーの終端は、半導体スイッチを通る有用電流に基づいて検出される。例

えば、制御回路は、制御入力基準信号と、可変抵抗を有する要素にかかる電圧、半導体ス

イッチの制御入力における電流、半導体スイッチにかかる電圧、または半導体スイッチを

通る有用電流とにに基づいて、可変抵抗を有する要素の抵抗を検出するように設計され

ている。他の例において、制御入力基準信号を生成する回路は、2つ以上の電流源とキャパシ

タンスとを備え、キャパシタンスは、異常が発生した場合に2つ以上の電流源から放電さ

れるように配置されている。さらに、キャパシタンスは、半導体スイッチのオン切り替え

動作後、所定の電圧に接続される。さらに、2つ以上の電流源のうちの第1のものは、ミ

ラープラトーの終端が検出された時点の後、キャパシタンスを放電するように設計され

ている。場合によっては、2つ以上の電流源のうちの第2のものは、キャパシタンスに閾値

電圧がかかる時点までキャパシタンスを放電するように設計されている。例えば、オフ切

り替え回路は、無効化信号に応答して、制御回路が制御入力基準信号に応答して可変抵抗

を有する要素の抵抗を調節することを防止する、無効化回路をさらに備える。

#### 【0011】

第2の実施形態において、オフ切り替えシステムは、第1の実施形態のオフ切り替え回

路の1つと、オフ切り替え回路の1つ以上の特徴と、半導体スイッチの出力電圧を所定の

閾値電圧未満に維持するために必要な程度まで、半導体スイッチの駆動回路の出力電圧を能動的

に増加させるように設計されたアクティブクランプ回路と、選択信号に応答して、異常が発

生した場合に半導体スイッチをオフに切り替えるためオフ切り替え回路とアクティブクラン

プ回路とのいずれかを有効化する選択回路と、を含む。

#### 【0012】

オフ切り替えシステムは、以下の特徴の1つ以上をもち得る。例えば、アクティブクラ

ンプ回路の出力は、可変抵抗を有する要素の制御入力に接続されている。さらに、アクテ

ィブクランプ回路は、可変抵抗を有する要素の制御入力と半導体スイッチのソース入力、

コレクタ入力またはカソード入力との間の電圧が、所定の閾値電圧に近づいたとき、可変

抵抗を有する要素の制御入力における電圧を低減する。さらに、オフ切り替えシステムは、

アクティブクランプ回路が有効化された場合に、可変抵抗を有する要素の制御入力に対

する制御入力基準信号の結合が防止されるように設計されている。

#### 【0013】

第3の実施形態において、半導体スイッチのオフ切り替え回路は、可変抵抗を有する要

10

20

30

40

50

素であって、当該要素が半導体スイッチの制御入力に接続されている、当該要素と、半導体スイッチの制御入力電圧または制御入力電流におけるミラープラトーの終端を検出するように設計された検出回路と、半導体スイッチの制御入力に現れる電圧が、ミラープラトーの終端後に所定の速度で低減されるような方法で可変抵抗を有する要素の抵抗値を制御するように設計された制御回路とを含む。

【0014】

オフ切り替え回路は、以下の特徴の1つ以上をもち得る。例えば、ミラープラトーの終端は、可変抵抗を有する要素の制御入力における電圧に基づいて検出される。場合によつては、ミラープラトーの終端は、可変抵抗を有する要素の制御入力における電圧が所定の信号レベル未満に立ち下がったときに検出される。さらに、所定の信号レベルは、可変抵抗を有する要素の予定ゲート閾値電圧の50%から150%の範囲にある。さらに、所定の信号レベルは、0.3から2ボルトの間である。例えば、ミラープラトーの終端に達する前における制御入力基準信号のレベルは、実質的に一定であり、ミラープラトーの終端の検出に応答して、制御入力基準信号の信号レベルは低減される。

10

【0015】

第4の実施形態において、半導体スイッチをオフに切り替える方法は、制御入力基準信号を生成することと、可変抵抗を有する要素の抵抗を調節することとを含み、閉制御ループ内で制御入力基準信号に応答してその要素が半導体スイッチの制御入力に接続される。

【0016】

第5の実施形態において、電力スイッチを制御するためにスイッチ制御装置において使用する駆動回路は、オン信号を受信するように接続されたオン状態駆動装置であって、オン状態駆動装置が、オン信号に応答して、第1の制御信号を出力して電力スイッチをオンに切り替え、第1の制御信号が、高閾値に実質的に等しい、当該オン状態駆動装置と、オフ信号を受信するように接続されたオフ状態駆動装置であって、当該オフ状態駆動装置が、オフ信号に応答して、第1の制御信号を出力して電力スイッチをオフに切り替え、第1の制御信号が低閾値に実質的に等しい、当該オフ状態駆動装置と、第1の制御信号を受信するように接続されたソフト遮断回路であって、当該ソフト遮断回路が、異常状態に応答して、閉ループにおいて第1の制御信号を調節し、当該ソフト遮断回路が、ある期間にわたって第1の制御信号を高閾値から中閾値まで低減した後、第1の制御信号を低閾値まで低減し、その期間が、電力スイッチのミラープラトーの終端に応答して、終わる。当該ソフト遮断回路と、を含む。

20

【0017】

駆動回路は、以下の特徴の1つ以上をもち得る。例えば、ソフト遮断回路は、オフ信号が第1の閾値に達したときに、電力スイッチのミラープラトーの終端を検出する。他の例において、オフ状態駆動装置は、トランジスタをさらに含み、ソフト遮断回路は、トランジスタのゲート電流またはゲート電圧を表すゲート信号を受信して、トランジスタのゲート信号が第1の閾値に達したときに、電力スイッチのミラープラトーの終端を検出するように接続されている。電力スイッチのミラープラトーの終端は、空白時間の後、トランジスタのゲート信号が第1の閾値に達したときに検出される。さらに、遮断回路は、第1の制御信号と基準信号とを受信するように接続された増幅器を含み、基準信号は、ある期間にわたって高閾値から中閾値まで低減した後、異常状態と電力スイッチのミラープラトーの終端とに応答して、低閾値まで低減する。場合によつては、電力スイッチのミラープラトーの終端は、空白時間の後、トランジスタのゲート信号が第1の閾値に達したときに検出され、空白時間は、基準信号が中閾値に実質的に等しいときに終わり得る。例えば、異常状態がない場合、基準信号は、その期間にわたって中閾値に実質的に等しくない。他の例として、駆動回路は、アクティブクランプ信号を受信し得、ソフト遮断回路は、アクティブクランプ信号が第1の閾値と第2の閾値との間である場合、無効化される。アクティブクランプ信号は、第1の制御信号が電力スイッチをオフに切り替える前、別の電流を含む。さらに、異常状態は、電力スイッチにおける過電流状態であり得る。

30

【0018】

40

50

第6の実施形態において、電力半導体スイッチをオフに切り替える回路は、電力半導体スイッチの制御端子に対する電力半導体スイッチをオフに切り替える信号をスイッチングするように接続されたオフ切り替えトランジスタと、フィードバック制御ループのオフ切り替え中、電力半導体スイッチの制御端子における電圧を制御するフィードバック制御ループと、を含む。フィードバック制御ループは、電力半導体スイッチの制御端子の電圧の測定結果をフィードバックするフィードバック経路と、時間依存基準電圧を生成する制御端子基準電圧生成器と、制御端子の電圧と時間依存基準電圧との間の差分を表すエラー信号を生成するエラー増幅器と、オフ切り替えトランジスタにより電力半導体スイッチの制御端子に対する電力半導体スイッチをオフに切り替える信号のスイッチングを制御するためエラー信号を前方に伝達する転送経路と、を含む。

10

#### 【0019】

回路は、以下の特徴の1つ以上をもち得る。例えば、回路は、電力半導体スイッチの制御端子の電圧が電力半導体スイッチのミラープラター近傍における電圧レベル未満であることを検出して、それを示す信号を出力するように接続されたミラープラター検出回路をさらに含む。他の例として、制御端子基準電圧生成器は、電力半導体スイッチの制御端子がミラープラター近傍における電圧レベル未満であることを示す信号に応答して、時間依存基準電圧の時間変化率を増加させる。場合によっては、ミラープラター検出回路は、電力半導体スイッチの制御端子への電流を検出するように接続された制御端子電流検出回路を備える。さらに、ミラープラター検出回路は、電力半導体スイッチの制御端子を基準電圧と比較するように接続された電圧比較器を備える。さらに、制御端子基準電圧生成器は、時間依存基準電圧を、電力半導体スイッチがオンである第1の値から電力半導体スイッチのミラープラター近傍における第2の値まで変化させる第1の回路と、時間依存基準電圧を、電力半導体スイッチのミラーエンジニア近傍における第3の値から電力半導体スイッチがオフである第4の値まで変化させる第2の回路と、を含む。例えば、第1の回路は、第2の回路が基準電圧を変化させる時間変化率未満である時間変化率で、時間依存基準電圧を変化させる。他の例として、第1の回路は、第1の値から第2の値まで、400ナノ秒から4000ナノ秒の間で時間依存基準電圧を変化させる。場合によっては、第2の回路は、第3の値から第4の値まで、100ナノ秒から2000ナノ秒の間で時間依存基準電圧を変化させる。他の例において、第2の回路は、第3の値から第4の値まで、10ナノ秒から100ナノ秒の間で時間依存基準電圧を変化させる。さらに、第2の値は、電力半導体スイッチのミラープラターを上回っており、第3の値は、電力半導体スイッチのミラープラター未満である。さらに、制御端子基準電圧生成器は、時間依存基準電圧を第2の値と第3の値との間で一定に保持する回路を備える。いくつかの例において、異常検出回路は、電力半導体スイッチを通る電流の伝導における異常の検出に応答して異常信号を出力するように接続されており、制御端子基準電圧生成器は、異常信号に応答して、基準電圧を電力半導体スイッチが開いている値から変化させ始める。他の例として、異常検出回路は、電力半導体スイッチのコレクタ・エミッタ電圧を検出する回路を備える。さらに、電力半導体スイッチをオフに切り替える信号は、電流であり、回路は、オフ切り替えゲート抵抗器をさらに備える。さらに、電力半導体スイッチは、IGBTである。場合によっては、オフ切り替えトランジスタは、NMOSトランジスタである。

20

30

40

#### 【0020】

本発明の非限定的かつ非網羅的で例示的な実施形態について、以下の図を参照しながら説明しており、異なる図における同じ参照符号は、そうでないという指定がない限り、同じ構成要素に関する。

#### 【図面の簡単な説明】

#### 【0021】

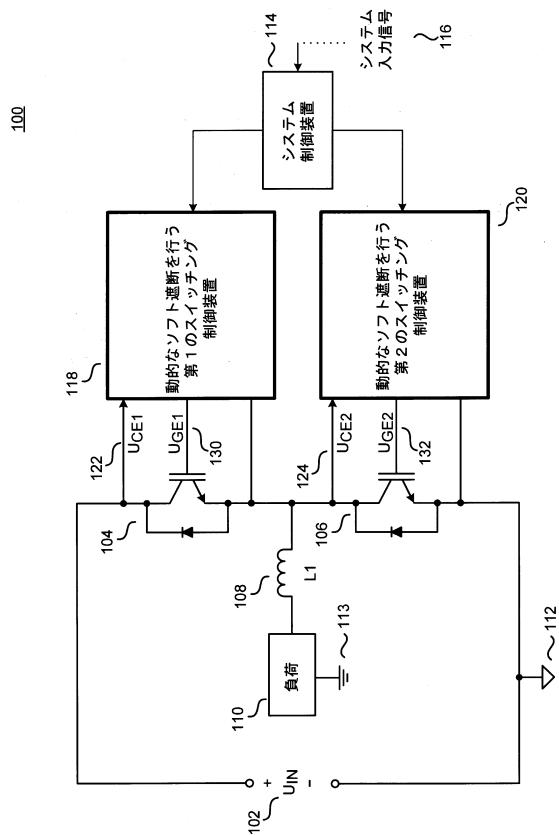

【図1A】図1Aは、消費装置に電気エネルギーを提供する例示的な装置を示し、本装置は、本明細書で説明するオフ切り替え回路をもつ半導体スイッチの制御回路を有する。

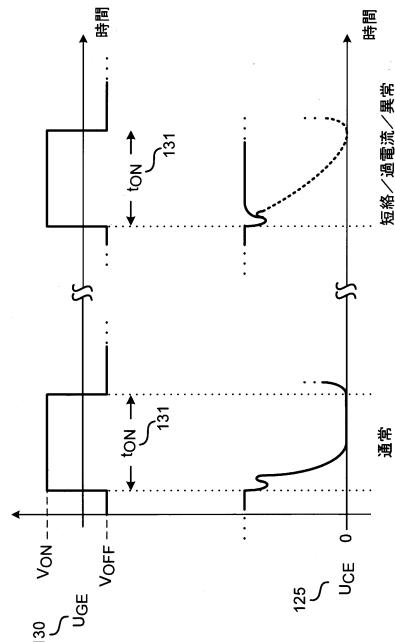

【図1B】図1Bは、例示的な、半導体スイッチの制御端子にかかる電圧の信号波形と、通常動作中における、または短絡が発生した場合における半導体スイッチにかかる電圧の

50

信号波形を示す。

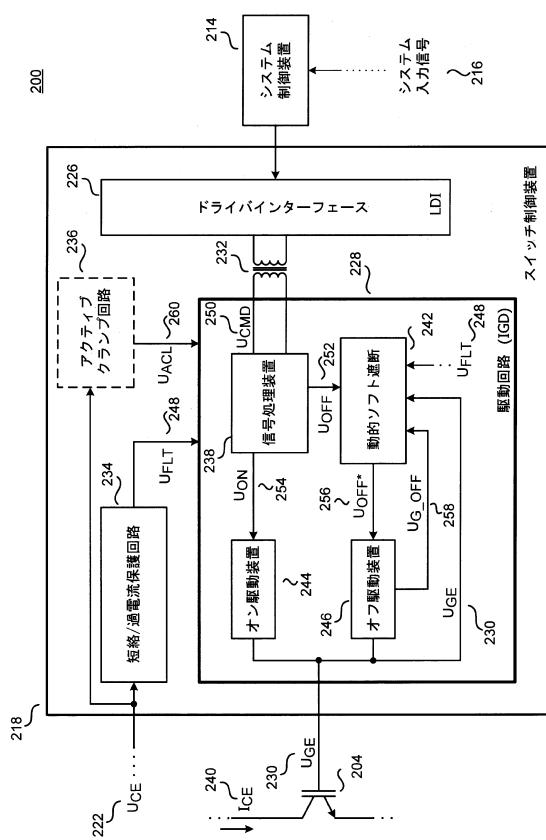

【図2】図2は、本明細書で説明するオフ切り替え回路とアクティブクランプ回路とを有する半導体スイッチの例示的な制御回路を示す。

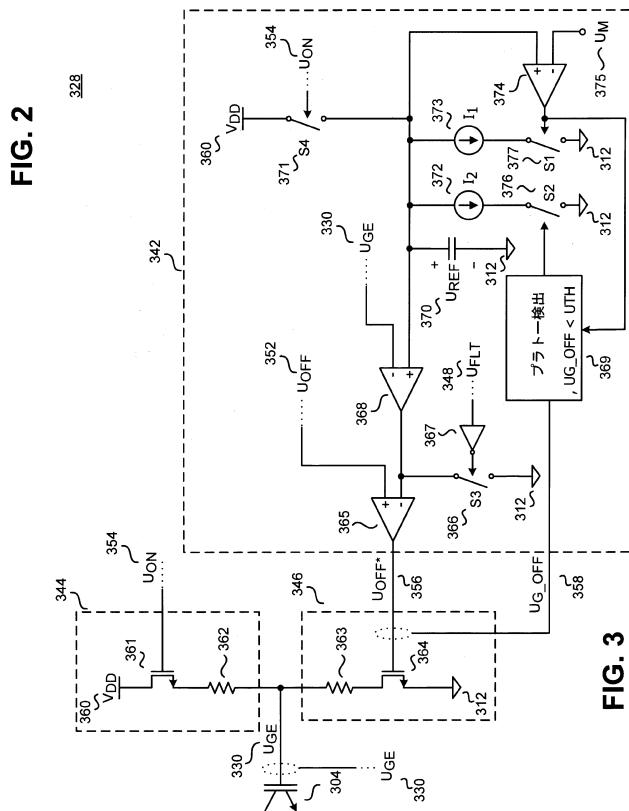

【図3】図3は、例示的なオフ切り替え回路を示す。

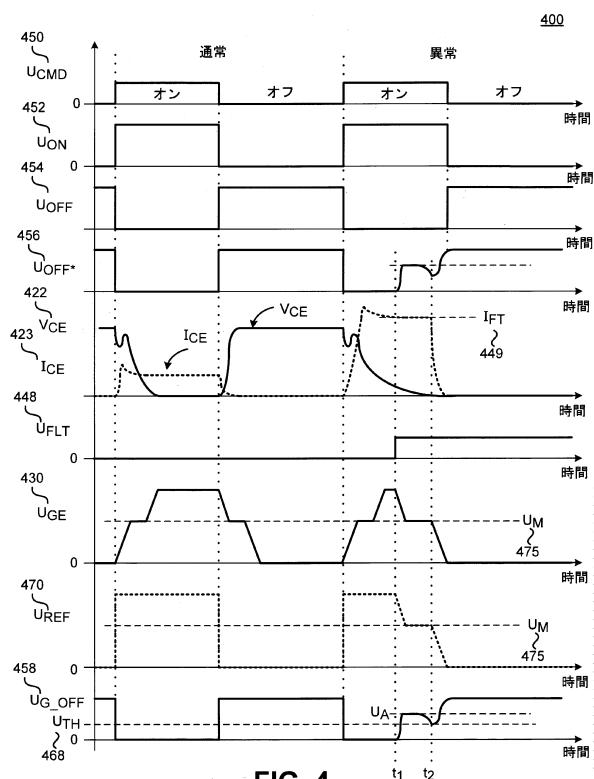

【図4】図4は、本明細書で説明するオフ切り替え回路をもつ半導体スイッチの制御回路を有するシステムにおける例示的な信号波形を示す。

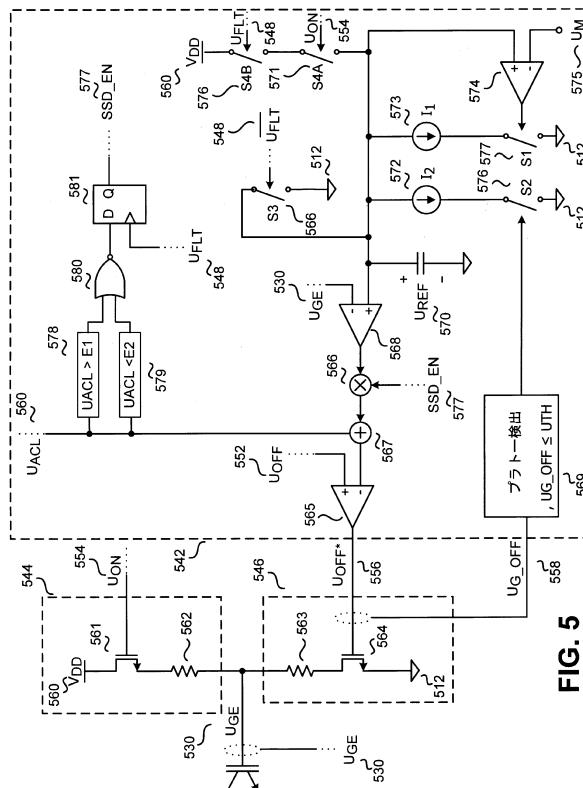

【図5】図5は、アクティブクランプ回路と組み合わせた例示的なオフ切り替え回路を示す。

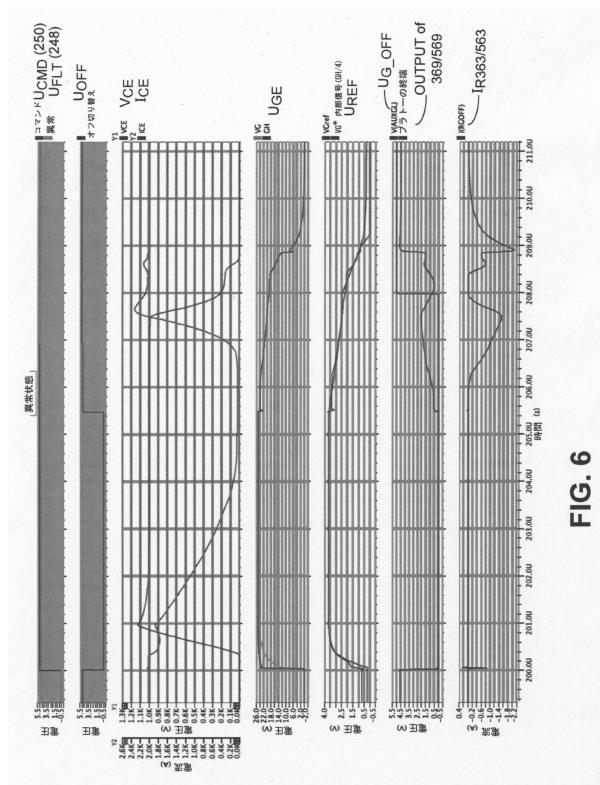

【図6】図6は、例示的なオフ切り替え回路におけるシミュレーションした信号波形を示す。

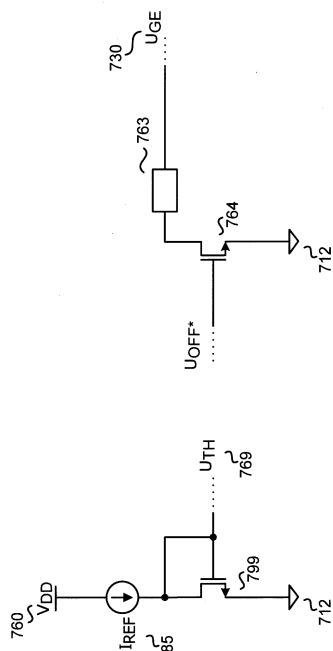

【図7】図7は、ミラープラトーネの終端を検出する回路内の閾値電圧を生成する例示的な回路を示す。

【発明を実施するための形態】

【0022】

以下の説明では、本発明を深く理解できるように多くの詳細事項について説明する。しかし、本発明を実施する際に特定の詳細事項が必要とは限らないことが当業者には明らかである。本発明の理解を不必要に妨げないように、よく知られた装置と方法とについては、別の位置で詳細には説明していない。

【0023】

本説明における、「実装例 (an implementation)」、「構成 (a configuration)」、「例 (an example)」または「例 (example)」という言及は、本実施形態との関連で説明する特定の特徴、構造または性質が本発明の少なくとも1つの実施形態に含まれることを意味する。従って、本説明中の様々な位置における「一実装例において (in one implementation)」、「一実施形態において (in one embodiment)」、「一例 (one example)」または「一例において (in one example)」という語句は、必ずしもすべてが同じ実施形態または同じ例に関するわけではない。

【0024】

加えて、1つ以上の実施形態または例において、特定の特徴、構造または性質は、あらゆる所望の適切な組み合わせ及び/または部分的組み合わせで組み合わされ得る。特定の特徴、構造または性質は、集積回路、電子回路、論理回路または説明されている機能を提供する他の適切な構成要素に含まれ得る。さらに、当業者に対する説明を目的として図面を使用するということと、図面が必ずしも正確な寸法で示されているわけではないことを述べておく。

【0025】

図1Aは、消費装置110に電気エネルギーを提供する装置100（電力変換装置とも呼ばれる）を示し、本装置は、本明細書で説明するオフ切り替え回路をもつ半導体スイッチの制御回路を有する。しかし、エネルギーの流れは、また、逆方向を向き得る。この場合、要素110は、発電装置である。他の装置において、要素110は、消費装置と発電装置との両方として様々な動作状態で動作し得る。以下の説明において、エネルギーを提供する装置についてのみ説明し、ここには、上述の例のすべてを含む（エネルギーは、異なる出力において提供され得る）。装置は、互いに接続された2つの電力半導体スイッチ104、106を備える。加えて、装置100は、直流入力電圧102（U<sub>IN</sub>）を受信し得る。装置は、電力半導体スイッチ104、106を制御することにより、電気エネルギーを入力から、消費装置110が接続されている出力まで（または、逆方向に）伝達するように設計されている。この場合、電気エネルギーを提供する装置は、電圧レベル、電流レベルまたはその2つの変数の組み合わせを制御し得、これらは、消費装置に出力される。図1Aに示す例において、電力半導体スイッチ104、106は、IGBTである。

【0026】

以下の説明では、IGBTの例を使用して装置と方法とを説明する。しかし、本明細書

で説明するオフ切り替え装置は、IGBTと共に使用するものに限定されない。その代わり、それらは、他の電力半導体スイッチと組み合わせても使用され得る。例えば、金属酸化膜半導体電界効果トランジスタ(MOSFET: metal-oxide-semiconductor field-effect transistor)、バイポーラトランジスタ(BJT: bipolar transistor)、注入促進ゲートトランジスタ(IGBT: injection-enhancement gate transistor)及びゲートターンオフサイリスタ(GTO: gate turn-off thyristor)は、本明細書で説明するオフ切り替え装置と共に使用され得る。本明細書で説明するオフ切り替え装置は、窒化ガリウム(GaN)半導体または炭化ケイ素(SiC)半導体を基材とする電力半導体スイッチと共に使用されてもよい。

10

#### 【0027】

スイッチオフ状態における電力半導体スイッチの最大公称コレクタ・エミッタ電圧、アノード・カソード電圧またはドレイン・ソース電圧は、500Vを上回る、好ましくは、2kVを上回る値であり得る。

#### 【0028】

加えて、本明細書で説明するオフ切り替え装置は、電力半導体スイッチと共に使用するものに限定されない。従って、他の半導体スイッチが、本明細書で説明するオフ切り替え装置と共に使用されてもよい。本明細書で言及する効果と利点とは、また、他の半導体スイッチをもつシステムにおいて少なくとも部分的に発生する。

#### 【0029】

以下、IGBTについて説明するので、電力半導体スイッチの端子は、「コレクタ」、「ゲート」及び「エミッタ」と呼ばれる。しかし、既に説明したとおり、装置と方法とはIGBTに限定されない。不必要に長い説明とならないように、本明細書における「エミッタ」という名称は、「ソース」または「カソード」と表記する対応する電力半導体スイッチの端子をさらに含む。同様に、本明細書における「コレクタ」という用語は、「ドレイン」または「アノード」と表記する端子も含み、「ゲート」という用語は、「ベース」と表記する対応する電力半導体スイッチの端子を表す。以下の説明では、「コレクタ・エミッタ電圧」という用語は、「ドレイン・ソース電圧」と「カソード・アノード電圧」とをさらに含み、「コレクタ電圧」という用語と「エミッタ電圧」という用語とは、それぞれ、「ドレイン電圧」または「アノード電圧」と「ソース電圧」または「カソード電圧」とをさらに含む。

20

#### 【0030】

電力半導体スイッチ104、106は、各々、第1の制御回路118と第2の制御回路120により制御される。制御回路は、第1のIGBTと第2のIGBTとのスイッチング時間を制御するため第1のゲート・エミッタドライバ信号130( $U_{GE1}$ )と第2のゲート・エミッタドライバ信号132( $U_{GE2}$ )とを提供する。さらに、制御回路118と制御回路120との両方は、任意選択的に、システム制御装置114により制御される。システム制御装置114は、システム入力信号116を受信する入力を有し得る。図1Aに示す例において、ハーフブリッジ構成をとる2つの電力半導体スイッチ104、106を示す。しかし、オフ切り替え装置は、他の形態でも使用され得る。例えば、制御回路の、または電力半導体スイッチにかかる電圧の波形を検出する装置を有する単一の電力半導体スイッチ(例えば、単一のIGBT)が接続され得る。他の例において、6つの電力半導体スイッチまたは12個の電力半導体スイッチを有する三相システムにおいて、電力半導体スイッチの各々は、電力半導体スイッチにかかる電圧の波形を検出する装置を有し得る。

30

#### 【0031】

ゲート・エミッタドライバ信号の出力に加えて、制御回路118、120は、電力半導体スイッチ104、106にかかる電圧を表す信号を受信する。信号は、電圧信号または電流信号であり得る。図1Aに示す例において、各制御回路118、120は、各場合において、コレクタ・エミッタ電圧を表した、コレクタ・エミッタ電圧信号122、124

40

50

( $U_{CE1}$ 、 $U_{CE2}$ ) と表される 1 つの信号をもつ。

【0032】

図 1 A は、別々の制御回路として制御回路 118、120 を示す。しかし、2 つの制御回路 118、120 は、また、単一の回路に一体化され得る。この場合、単一の制御回路が、2 つの電力半導体スイッチ 104、106 を制御する。さらに、第 2 のゲート・エミッタドライバ信号 132 ( $U_{GE2}$ ) は、第 1 のゲート・エミッタドライバ信号 130 ( $U_{GE1}$ ) を反転させたものであり得る。

【0033】

2 つの制御回路 118、120 は、本明細書で説明するオフ切り替え装置の 1 つを備える。短絡状態及び／または過電流状態の成立に応答して、それぞれの電力半導体スイッチ 104、106 が、本明細書で説明するオフ切り替え装置の支援によりオフに切り替えられ得る。

【0034】

図 1 B は、例示的な、半導体スイッチの制御端子にかかる電圧の信号波形と、通常動作中と短絡が発生した場合とにおいて半導体スイッチにかかる電圧の信号波形とを示す。ゲート端子とエミッタ端子との間の電圧 130 ( $U_{GE}$ ) の信号波形を、図 1 B の上半分に示す。電圧 130 ( $U_{GE}$ ) は、第 1 の信号レベル ( $V_{ON}$ ) と第 2 の異なる信号レベル ( $V_{OFF}$ ) として示されている。ゲート端子が、第 1 の信号レベル ( $V_{ON}$ ) にあるとき（期間  $t_{ON} 131$  にわたって）、半導体スイッチがオンに切り替えられる。半導体スイッチがオンに切り替えられるときの、通常時（左側）と、例示的な短絡事象及び／または過電流事象（右側）との場合における、半導体スイッチにかかるコレクタ・エミッタ電圧 125 の信号波形を、図 1 B の下半分に示す。示した短絡事象において、コレクタ・エミッタ電圧 125 は、オン切り替え後、比較的低い値まで急激には低減しない（しかし、コレクタ・エミッタ電圧が他の特徴的な波形をとることを想定した、さらに別の短絡事例がある）。これにより、半導体スイッチや負荷に損傷をもたらし得る。従って、半導体スイッチは、急速にオフに切り替えられなければならない。しかし、これが過度に急速に発生した場合、負荷に過電圧が発生し得る。これを防ぐため、本明細書で説明するオフ切り替え回路が使用され得る。

【0035】

図 2 は、本明細書で説明するオフ切り替え回路 242 と（任意選択的な）アクティブクランプ回路 236 とを備える半導体スイッチの例示的な制御回路 218 を示す。制御回路は、システム制御装置 214 から制御コマンドを受信する（制御コマンドは、システム入力信号 216 に応答して生成される）。ドライバインターフェース 226 において、これらの制御コマンドが制御信号 250 ( $U_{CMD}$ ) に変換され、制御信号 250 は、絶縁変圧器 232 を介して駆動回路 228 に送信される。駆動回路 228 は、絶縁変圧器 232 を介して受信された制御信号 250 ( $U_{CMD}$ ) に応答して、半導体スイッチ 204 を制御する。この目的のため、駆動回路 228 は、半導体スイッチ 204 の制御入力に（例えば、ゲート入力に）接続されている。

【0036】

図 2 に示す例示的な駆動回路 228 は、半導体スイッチのオン状態用の駆動装置 244 とオフ状態用の駆動装置 246 とを有する。駆動装置 244、246 は、各々、半導体スイッチ 204 のドライバ信号 230 ( $U_{GE}$ ) を生成する。2 つの駆動装置 244、246 は、ドライバ信号処理装置 238 を介して制御され、ドライバ信号処理装置 238 は、絶縁変圧器 232 から制御信号 250 ( $U_{CMD}$ ) を受信（して、それらを、それぞれの駆動装置 244、246 に対するオン信号 254 ( $U_{ON}$ ) とオフ信号 258 ( $U_{OFF}$ ) とに変換）する。

【0037】

本明細書で説明するオフ切り替え回路 242 は、ドライバ信号処理装置 238 とオフ状態用の駆動装置 246 との間に接続されている。オフ切り替え回路 242 は、短絡事象及び／または過電流事象においてオフ切り替え動作を確実なものにでき、その場合において

10

20

30

40

50

、オフ切り替え動作中、半導体スイッチを通るスイッチ電流 240（この例では、コレクタ・エミッタ電流  $I_{CE}$ ）の減少は、通常動作中ほどには急激ではない（「ソフト遮断」と呼ばれる）。その結果、半導体スイッチの出力にかかる危険な過電圧の発生を防止することが可能である。図3と図4と図5とを参照して、様々なオフ切り替え回路の性質に関する詳細について説明する。

#### 【0038】

オフ切り替え回路 242 は、オフ状態用の駆動装置 246 に対するオフ信号 252（ $U_{OFF}$ ）と、短絡事象及び／または過電流事象の存在を示す異常信号 248 と、半導体スイッチ 230 の制御端子に現れる信号（例えば、ゲート・エミッタ電圧  $U_{GE}$ ）とを受信する。これらの信号に基づいて、オフ切り替え回路 242 は、半導体スイッチ 204 のオフ切り替え動作を動的に制御し得る。一例において、半導体スイッチ 230 の制御端子に現れる信号の波形は、半導体スイッチ 204 をオフに切り替えるため閉制御ループ内で調節され得る。図2に示す例において、調整は、変更されたオフ信号 256（ $U_{OFF*}$ ）の生成を含み、変更されたオフ信号 256 は、オフ切り替え回路 242 からオフ状態用の駆動装置 246 に送信され得る。この変更されたオフ信号 256（ $U_{OFF*}$ ）は、一例において、オフ状態用の駆動装置 246 における可変抵抗を有する要素の可変抵抗を変化させて、その結果、半導体スイッチ 230 の制御端子に現れる信号の波形（例えばゲート・エミッタ電圧  $U_{GE}$ ）に影響を与える。言い換えると、変更されたオフ信号 256（ $U_{OFF*}$ ）は、制御ループの操作された変数であり得る。図2に示す例において、半導体スイッチ 230 の制御端子に現れる信号（例えば、ゲート・エミッタ電圧  $U_{GE}$ ）は、制御ループのフィードバックパラメータである。しかし、フィードバックパラメータとして、他のパラメータが使用されてもよい。

#### 【0039】

加えて、または代替的に、オフ状態用の駆動装置 246 は、半導体スイッチ 230 の制御入力に現れる電圧（例えば、ゲート・エミッタ電圧  $U_{GE}$ ）が、ミラープラートの終端後に所定の速度で低減されるように制御され得る。この方法で、動的オフ切り替え回路 242 は、様々な半導体スイッチに対する適切な「ソフト遮断」を確実なものにできる。一例において、半導体スイッチ 204 の制御入力電圧または制御入力電流におけるミラープラートの終端は、オフ状態用の駆動装置 246 における可変抵抗を有する要素の制御入力における電圧の波形 258（ $U_{G_OFF}$ ）に基づいて検出され得る。

#### 【0040】

制御回路 218 は、異常信号 248（ $U_{FLT}$ ）を生成する短絡及び／または過電圧検出回路 234 を含む。一例において、短絡及び／または過電圧保護回路 234 は、半導体スイッチ 204 のコレクタ・エミッタ電圧 222（ $U_{CE}$ ）を監視し得る。図1Bを参照して説明したように、コレクタ・エミッタ電圧 222（ $U_{CE}$ ）は、短絡事象及び／または過電流事象における特徴的な波形をとり得、短絡及び／または過電圧保護回路 234 が、この特徴的な波形を検出し得る。

#### 【0041】

任意選択的に、制御回路 218 は、アクティブクランプ回路 236 を備え得る。これは、異常が発生した場合に、「ソフト遮断」のための第2の回路を提供し得、第2の回路は、オフ切り替え回路 242 の代替例として使用され得る。

#### 【0042】

図2を参照して、本明細書で説明するオフ切り替え回路 242 とアクティブクランプ回路 236 とを有する半導体スイッチの例示的な制御回路について説明してきたので、図3を参照して、例示的なオフ切り替え回路について説明する。

#### 【0043】

図3は、オン状態用の駆動装置 344 とオフ状態用の駆動装置 346 とオフ切り替え回路 342 と半導体スイッチ 304 とを示す。駆動装置 344、346 は、各々可変抵抗を有する要素 361、364 を（図3に示す例において、N MOS半導体スイッチとして）含む（が、可変抵抗を有する他のスイッチング可能な半導体スイッチまたは他の要素が使

10

20

30

40

50

用されてもよい)。可変抵抗を有する要素 361、364 は、各々、任意選択的な抵抗 362、363 と直列に接続されている。

【0044】

オン状態用の駆動装置 344 の可変抵抗を有する要素 361 (と抵抗 362 と) は、半導体スイッチ 304 の制御入力 (図 3 に示す例におけるゲート入力) と第 1 の基準電位 360 ( $V_{DD}$ ) との間に接続されている。加えて、可変抵抗を有する要素 361 は、可変抵抗を有する要素 361 の制御端子 (例えば、NMOS 361 のゲート入力) において制御回路のオン信号 354 ( $U_{ON}$ ) を受信し得るように配置されている。従って、半導体スイッチがオンに切り替えられることが意図されている場合、半導体スイッチをオンに切り替えるのに十分高い電位 (例えば、図 3 における第 1 の基準電位 360  $V_{DD}$ ) に半導体スイッチ 304 の制御入力 (例えば、IGBT 304 のゲート端子) が接続されるように、可変抵抗を有する要素 361 の抵抗が低減される (例えば、NMOS 半導体スイッチ 361 がオンに切り替えられる)。

【0045】

同様に、オフ状態用の駆動装置 346 の可変抵抗を有する要素 364 (と抵抗 363 と) は、半導体スイッチ 304 の制御入力 (図 3 に示す例における IGBT のゲート入力) と第 2 の基準電位 312 との間に接続されている。加えて、可変抵抗を有する要素 364 は、制御端子 364 (NMOS 364 のゲート端子として示されている) において、制御回路の変更されたオフ信号 356 ( $U_{OFF*}$ ) を受信し得るように配置されている。従って、半導体スイッチ 304 がスイッチオフされることが目標とされる場合、半導体スイッチがスイッチオフされるのに十分低い電位 (例えば、第 2 の基準電位 312) に半導体スイッチ 304 の制御入力 (IGBT 304 のゲート端子) が接続されるように、可変抵抗を有する要素 364 の抵抗が低減される (例えば、NMOS 半導体スイッチ 364 がオンに切り替えられる)。制御端子 (IGBT のゲート端子) をすぐに第 2 の基準電位まで引くことによる半導体スイッチ 304 のスイッチオフは、半導体スイッチ 304 のコレクタ・エミッタ電流の比較的急速な低減をもたらす。しかし、短絡事象が存在する場合、寄生結合により、コレクタ・エミッタ電流の急速な低減は、危険となり得る過電圧の生成をもたらし得る。その影響を防ぐため、短絡事象及び / または過電流事象でオフ切り替え回路 342 が使用されて、ソフト遮断を実装し得る。

【0046】

図 3 に示す例において、スイッチ 366 (S3) は、異常があるとき (例えば、対応する検出回路が異常を特定したとき) にスイッチ 366 (S3) が開くように、異常信号 348 ( $U_{FLT}$ ) により制御される。その結果、異常がある場合、オフ切り替え回路 342 により (元の) オフ信号 352 ( $U_{OFF}$ ) が変更される。その一方で、通常動作中、スイッチ S3 366 が閉じて、オフ切り替え回路 342 がオフ状態用の駆動装置 346 の可変抵抗を有する要素 364 に影響を与えないように、固定の基準電位 312 に接続される。

【0047】

オフ切り替え回路 342 は、制御入力基準信号 370 ( $U_{REF}$ ) を生成する回路と、半導体スイッチの制御入力電圧または対応する制御入力電流におけるミラーブラートーの終端を検出するように設計された検出回路 369 と、制御入力基準信号 370 ( $U_{REF}$ ) を半導体スイッチの制御入力における電圧 330 ( $U_{GE}$ ) と比較するための第 1 の比較回路 368 とを含む。

【0048】

まず、制御入力基準信号 370 ( $U_{REF}$ ) を生成する回路について説明する。この回路は、キャパシタンスを含み、基準信号 370 ( $U_{REF}$ ) は、キャパシタンスにかかる電圧によって形成される。図 3 に示す例において、キャパシタンスは、2 つの電流源 372、373 ( $I_1, I_2$ ) に接続され得、第 1 の速度または第 2 の速度で基準信号 370 ( $U_{REF}$ ) の信号レベルを低減するため電流源 372、373 ( $I_1, I_2$ ) を通して放電され得る。第 1 速度と第 2 の速度とは、電流源 372、373 ( $I_1, I_2$ ) とキャ

パシタンスとの値に比例し得る。まず、キャパシタンスの第1の端子は、オン信号354( $U_{ON}$ )に応答して半導体スイッチ304がオンに切り替わると、所定の基準電位360( $V_{DD}$ )に接続され得る。これは、図3に示す例において、オン状態において半導体スイッチ304の制御入力が接続される第1の基準電位360に対応する。キャパシタンスの第2の端子が、低いほうの電位(これは、図3に示す例において、オフ状態において半導体スイッチ304の制御入力が接続される第2の基準電位312に対応する)にあるので、半導体スイッチ304のオン状態中、キャパシタンスが所定の電圧に充電され、その結果、オン切り替えの開始直前は静的である。その結果、制御入力基準信号370( $U_{REF}$ )が、所定の基準電位360( $V_{DD}$ )に対応する所定の信号レベルにおいて「開始」される。

10

## 【0049】

第1の電流源373は、スイッチ377(S1)を介して第2の基準電位312に接続されている。スイッチ377(S1)が閉じると、第1の電流源373が、キャパシタンスを第1の速度(電流 $I_1$ に対応)で放電する。スイッチ377(S1)の制御回路は、短絡事象及び/または過電流事象が検出された時点から(または、短絡事象及び/または過電流事象の検出から所定の期間後に)、半導体スイッチ304の制御入力における電圧330が半導体スイッチのミラープラトーに対応する電圧(信号 $U_M$ 375として示されている)に達する時点まで、スイッチ377(S1)が閉状態に維持されるように設計され得る。従って、この期間において、キャパシタンスが第1の速度で放電される。

20

## 【0050】

図3に示す例において、スイッチ377(S1)の制御回路は、キャパシタンスにかかる電圧(すなわち、基準信号370( $U_{REF}$ ))を閾値375( $U_M$ )と比較する比較回路374を含む。この閾値375( $U_M$ )は、半導体スイッチのミラープラトーに対応する電圧を反映するように選択され得る。多くのIGBTにおいて、この電圧は、9.5ボルトから11.5ボルトの間であり得る。基準信号370( $U_{REF}$ )の信号レベルが閾値375( $U_M$ )に達すると、スイッチ377(S1)が閉く。キャパシタンスは、これ以降、電流源373により放電されない。これは、基準信号370( $U_{REF}$ )の信号レベルが所定の期間にわたって実質的に(例えば、初期信号レベルの10%の最大の変化で)一定に留まることをもたらし得る。この期間は、スイッチ376(S2)が閉じることにより終了し、それにより、第2の電流源372によりキャパシタンスの放電動作が再開される。

30

## 【0051】

さらなるスイッチ376(S2)のこの閉じる時点は、検出回路369により決定され得、検出回路369は、半導体スイッチ304の制御入力電流または制御入力電圧におけるミラープラトーの終端を検出するように設計されている。図3に示す例において、ミラープラトーの終端は、オフ状態用の駆動装置の可変抵抗を有する要素364の制御入力における電圧358( $U_{G_OFF}$ )(例えば、可変抵抗を有する要素364のゲート電圧)に基づいて決定される。この電圧が所定の閾値 $U_{TH}$ 未満に立ち下がった場合、これがミラープラトートの終端を示し得る(この場合、ミラープラトートの終端とアンダーシュートされている閾値との一致は完全ではない可能性があるが、アンダーシュートされている閾値は、ミラープラトートの終端の時点に対する良好な推定を提供する)。

40

## 【0052】

図7に、閾値 $U_{TH}$ を生成する例示的な回路を示す。一例において、閾値 $U_{TH}$ は、可変抵抗を有する要素364の予定ゲート閾値電圧の50%から150%の範囲にある。他の例において、閾値 $U_{TH}$ は、0.3から2ボルトの範囲であり得る。図7に示す例において、閾値 $U_{TH}$ を生成する回路は、オフ状態用の駆動装置の可変抵抗を有する要素764と同じ技術に基づく、可変抵抗を有する第2の要素799(図7に示す例におけるN MOS半導体スイッチ)を含む。基準電流785( $I_{REF}$ )は、第2の要素799の制御入力(例えば、ゲート端子)と、第2の要素799の第1の端子(例えば、ドレイン端子)とに接続され得る。第2の要素799の面積またはゲート幅は、オフ状態用の駆動装置

50

の可変抵抗を有する要素 7 6 4 の面積またはゲート幅の K 倍であり得、基準電流 7 8 5 (  $I_{REF}$  ) は、ミラープラトーの終端に対して設計されている可変抵抗を有する要素 7 6 4 の出力電流の閾値の K 倍であるように選択される。一例において、基準電流 7 8 5 (  $I_{REF}$  ) は、100 マイクロアンペア未満であり、K は 1% 未満である。このような回路を備えることにより、閾値  $U_{TH}$  は、可変抵抗を有する第 2 の要素 7 9 9 の制御入力における電圧に対応し得る。

#### 【 0 0 5 3 】

図 3 に示す例において、オフ状態用の駆動装置 3 4 6 の可変抵抗を有する要素 3 6 4 の制御入力における電圧 ( NMOS 3 6 4 のゲート電圧 ) は、ミラープラトーの終端の時点を検出するのに使用され得る。しかし、この時点は、さらに、他の信号に基づいて決定され得る。他の例において、オフ状態用の駆動装置の可変抵抗を有する要素 3 6 4 の制御入力における電流がミラープラトーの終端を決定するため使用される。例えば、オフ状態用の駆動装置 3 4 6 の可変抵抗を有する要素 3 6 4 の制御入力における電流は、ミラープラトーの終端に達したとき、ゼロに向かう傾向があり得る。さらに別の例において、半導体スイッチ 3 0 4 の制御電圧または制御電流が使用され得る。さらなる例において、ミラープラトーの終端を検出するため、半導体スイッチのコレクタ・エミッタ電圧または半導体スイッチのスイッチ電流が検出され得る。

#### 【 0 0 5 4 】

スイッチ 3 7 6 ( S2 ) を閉じることにより、キャパシタンスは、ミラープラトーの終端から始まって、第 2 の速度で放電される。この放電動作は、キャパシタンスが完全に放電されるまで ( または、所定の最小値までキャパシタンスが放電されるまで ) 続き得る。従って、基準信号 3 7 0 (  $U_{REF}$  ) は、図 4 に示すような、信号レベルが立ち下がる 2 つの領域をもつ波形をとり得る。この場合、所望の値として第 1 速度と第 2 の速度とが設定され得る。例えば、第 2 の速度は、第 1 の速度の 2 倍の大きさであり得るか、または、第 1 の速度より大きいものであり得る。他の例において、第 1 の速度と第 2 の速度とは、同じである。

#### 【 0 0 5 5 】

図 3 に示す制御入力基準信号を生成する回路により生成された基準信号 3 7 0 (  $U_{REF}$  ) は、信号レベルが立ち下がる 2 つの領域を含み得、その領域の間に、実質的に一定の信号レベルである領域が組み込まれている。しかし、領域のこの順序は、重要ではない。例えば、第 1 の速度及び / または第 2 の速度は、経時的に異なり得る。他の例において、基準信号 3 7 0 (  $U_{REF}$  ) は、信号が異なる速度で低減する、信号レベルが立ち下がる 3 つ以上の領域を有し得る。実質的に一定の信号レベルをとるさらなる領域が、これらの領域の間に組み込まれ得る。

#### 【 0 0 5 6 】

ここまで段落で、基準信号 3 7 0 (  $U_{REF}$  ) の生成について説明してきたので、「ソフト遮断」を達成するこの基準信号 3 7 0 (  $U_{REF}$  ) の使用について以下で説明する。この点で、基準信号 3 7 0 (  $U_{REF}$  ) は、第 1 の比較回路 3 6 8 により、半導体スイッチの制御入力における電圧 3 3 0 (  $U_{GE}$  ) と比較され得る。この比較に応答して、オフ状態用の駆動装置 3 4 6 の可変抵抗を有する要素 3 6 4 に対する、変更された制御信号 3 5 6 (  $U_{OFF*}$  ) が生成され得る。図 3 に示す例において、オフ信号 3 5 2 (  $U_{OFF}$  ) は、この目的において、変更されたオフ信号 3 5 6 (  $U_{OFF*}$  ) に変換される。これは、減算回路 3 6 5 において行われ得る。

#### 【 0 0 5 7 】

このようにして、可変抵抗を有する要素 3 6 4 の可変抵抗は、基準信号 3 7 0 (  $U_{REF}$  ) の波形に対応した、半導体スイッチの制御入力における電圧 3 3 0 (  $U_{GE}$  ) の波形を達成するため、閉制御ループ内で調節され得る。このようにして、半導体スイッチは、「ソフト遮断」を受ける。

#### 【 0 0 5 8 】

他の例において、閉制御ループのフィードバック変数は、半導体スイッチの制御入力に

10

20

30

40

50

おける電圧  $U_{G_E}$  ) とは異なる信号であり得、これに基づいて、半導体スイッチのオフ切り替え動作が監視され得る ( 例えは、半導体スイッチの制御入力における電流または半導体スイッチのコレクタ・エミッタ電圧 ) 。これらの場合において、基準信号  $370$  ( $U_{REF}$  ) に、図 3 の例に示す波形とは異なる波形を与えることが必要であり得る。しかし、これらの例においても、閉制御ループの操作を受ける変数は、オフ状態用の駆動装置  $346$  の可変抵抗を有する要素  $364$  の抵抗 ( または、可変抵抗を有する要素  $364$  の抵抗を変化させる制御信号 ) であり得る。

#### 【 0059 】

図 4 は、本明細書で説明するオフ切り替え回路をもつ半導体スイッチの制御回路を含むシステムにおける例示的な信号波形を示す。図 4 における信号は、半導体スイッチの 2 つの例示的なスイッチングサイクルを示す。第 1 のスイッチングサイクル ( ページの左側の曲線 ) は、通常の波形であり、第 2 のスイッチングサイクル ( ページの右側の曲線 ) では短絡事象または過電流事象が発生する。第 1 の曲線は、例えは、図 2 におけるドライバインターフェース  $226$  から制御回路  $228$  に送信される制御信号  $450$  ( $U_{CMD}$  ) を示す。これらの制御信号  $450$  ( $U_{CMD}$  ) から、オン信号  $452$  ( $U_{ON}$  ) とオフ信号  $454$  ( $U_{OFF}$  ) とが生成され得る。第 5 の曲線は、半導体スイッチのコレクタ・エミッタ電圧  $422$  ( $V_{CE}$  ) の波形と、半導体スイッチのコレクタ・エミッタ電流  $423$  ( $I_{CE}$  ) の波形とを示す。これらの波形のいくつかの特性については、図 1B を参照して既に説明した。第 2 のオン期間の始めに、異常が発生する。コレクタ・エミッタ電圧  $422$  ( $V_{CE}$  ) は、通常時に想定される程には大幅に減少しない。加えて、コレクタ・エミッタ電流  $423$  ( $I_{CE}$  ) は、通常時より大きな値まで増加する ( 高い異常電流  $449$  ( $I_{FT}$  ) が流れている ) 。これは、短絡及び / または過電圧検出回路により検出され得、短絡及び / または過電圧検出回路は、その結果、図 4 において第 6 の曲線として示す異常信号  $448$  ( $U_{FLT}$  ) を出力する。その結果、「ソフト遮断」を確実なものとするため、オフ切り替え回路が有効化され得る。

#### 【 0060 】

この目的において、制御入力基準信号  $470$  ( $U_{REF}$  ) が生成され得る。図 4 における例示的な基準信号  $470$  ( $U_{REF}$  ) は、まず、所定のレベルから第 1 の速度で減少し、次に、ある期間にわたって実質的に一定に留まり、この期間は、半導体スイッチのミラープラターの終端により終わる。次に、基準信号  $470$  ( $U_{REF}$  ) の信号レベルは、第 2 の速度で減少する。図 4 に示すように、過電流及び / または短絡が検出されると、オフ切り替え回路は、半導体スイッチのゲート・エミッタ電圧  $430$  ( 下から 3 番目の曲線として示す  $U_{GE}$  ) を基準信号  $470$  ( $U_{REF}$  ) に調節する。これは、半導体スイッチのオフ切り替え動作が、通常動作中の「ハード遮断」と比べて延長されるという結果をもたらし得る。図 4 において、この延長は、第 1 のスイッチングサイクルにおけるゲート・エミッタ電圧  $430$  の立ち下がりエッジと、第 2 のスイッチングサイクルにおけるゲート・エミッタ電圧  $430$  の立ち下がりエッジとの比較により確認され得る。オフ切り替え動作の遅延は、この場合、半導体スイッチのミラープラターの終端の検出に結びついている。すなわち、半導体スイッチは、ミラープラターの終端に既に達している場合にのみ最終的にオフに切り替えられる。従って、負荷にかかる危険なほどに高い電圧が防止され得る。

#### 【 0061 】

図 4 における第 4 の曲線は、オフ切り替え回路 ( 例えは、図 3 に示すオフ切り替え回路 ) により変更された例示的なオフ信号  $456$  ( $U_{OFF*}$  ) を示す。この信号は、半導体スイッチのオフ切り替え動作を調節するため、半導体スイッチのオフ状態用の駆動装置の可変抵抗を有する要素の制御入力に供給され得る。図 4 に示す例において、変更されたオフ信号  $456$  ( $U_{OFF*}$  ) の立ち上がりエッジは、オフ信号  $454$  ( $U_{OFF}$  ) の立ち上がりエッジより長い。これは、「ソフト遮断」を可能にするため、オフ状態用の駆動装置における半導体スイッチ ( 例えは、図 3 における NMOS 364 ) のオン切り替え動作と、従って、半導体スイッチ ( 例えは、図 3 における IGBT 304 ) のオフ切り替え動作とが、時間的に伸長されることをもたらし得る。図 4 における一番下の曲線は、半導体

10

20

30

40

50

スイッチの制御入力電圧または対応する制御入力電流におけるミラープラトーの終端を検出するように設計された検出回路 369 に対する検出信号 458 ( $U_{G\_OFF}$ ) を示す。検出信号 458 ( $U_{G\_OFF}$ ) は、変更されたオフ信号 456 ( $U_{OFF\ast}$ ) に対応するか、または、変更されたオフ信号 456 ( $U_{OFF\ast}$ ) に基づいて生成され得る。

#### 【0062】

図 6 は、図 4 の信号に対応した、オフ切り替え回路に対するシミュレーションした信号の波形を示す。特に、スイッチングされる電力半導体スイッチ ( $U_{GE}$ ) のゲートにおける電圧の波形が、例示的なオフ切り替え回路により、どのようにしてゲート基準信号 ( $V_{Gref}$ ) に調節されるのかが、上から 4 番目の曲線に見られ得る。

#### 【0063】

図 5 は、アクティブクランプ回路と組み合わせた例示的なオフ切り替え回路 542 を示す。この場合における、オフ切り替え回路とオン状態用の駆動装置とオフ状態用の駆動装置との要素は、図 3 に示す各要素に対応する。オフ切り替え回路 542 は、比較器 568 の非反転入力に接続されているスイッチ S3 566 と制御入力基準信号 ( $U_{REF}$ ) を伴うキャパシタンス 570 とをさらに含む。異常が検出されない（異常信号  $U_{FLT}$  548 が論理ローであり、反転した異常信号が論理ハイである）場合、スイッチ S3 566 が閉じて、比較器 568 の非反転入力における電圧は、戻り 512 に実質的に等しい。従って、図 3 と同様に、変更されたオフ信号 556 ( $U_{OFF\ast}$ ) は、実質的にオフ信号 552 ( $U_{OFF}$ ) である。異常が検出された（異常信号  $U_{FLT}$  548 が論理ハイであり、スイッチ S4B 576 がオンである）場合、制御入力基準信号 570 ( $U_{REF}$ ) は、所定の信号レベルにおいて「開始」され、これは、所定の基準電位 560 ( $V_{DD}$ ) に対応する。スイッチ S4A がオンである場合（すなわち、 $U_{ON}$  554 が論理ハイである場合）、制御入力基準信号 570 ( $U_{REF}$ ) が所定の基準電位 560 ( $V_{DD}$ ) まで充電される。しかし、加えて、対応する信号 560 ( $U_{ACL}$ ) がこれを示す場合、図 5 におけるオフ切り替え回路が無効化され得る。これは、図 5 の例を使用して、オフ切り替え回路が有効になる必要がないように、アクティブクランプ回路が「ソフト遮断」を確実なものとすることを意味する。

#### 【0064】

図 5 に示す例において、約ゼロの信号 560 ( $U_{ACL}$ ) の信号レベルは、アクティブクランプ回路が無効であることを意味する。アクティブクランプ回路が有効な場合、信号 560 ( $U_{ACL}$ ) は、正のレベルまたは負のレベルをとる。この状態は、比較回路 578、579 により（例えば、信号 560 ( $U_{ACL}$ ) の信号レベルと、第 1 の（より小さい）閾値 ( $E1$ ) と第 2 の（より上方の）閾値 ( $E2$ ) との比較により）検出される。信号 560 ( $U_{ACL}$ ) の信号レベルが第 2 の閾値 ( $E2$ ) を上回っている状態と、第 1 の閾値 ( $E1$ ) を下回っている状態とのいずれでもないことが検出されるように、比較回路が NOR 回路 580 に接続されている。その結果、オフ切り替え回路に対する、対応する有効化信号 577 (SSD\_EN) が生成され得る。例えば、NOR 回路 580 の出力は、D フリップフロップ 581 のデータ入力に接続され得、その出力に応答して、有効化信号 566 (SSD\_EN) が生成される。この場合、異常信号 548 ( $U_{FLT}$ ) は、D フリップフロップ 581 のクロック入力に接続され得る。これは、オフ切り替え回路の第 1 の比較回路 568 の出力信号に接続されている。従って、有効化信号 566 (SSD\_EN) が高信号レベルをとる場合、上でさらに説明したように、オフ切り替え回路がオフ切り替え動作に従事する。その一方で、有効化信号 566 (SSD\_EN) が低信号レベル（アクティブクランプ回路の動作を示す）をとる場合、オフ切り替え回路の影響が抑制される。この場合、アクティブクランプ回路が、「ソフト遮断」を確実なものとする。アクティブクランプ回路の存在とは無関係に、オフ切り替え装置を有効化する装置が提供され得る。それに伴い、所定の制御回路において、アクティブクランプ回路が提供される場合、オフ切り替え装置を有効化する装置は、対応する回路を有し得る。

#### 【0065】

他の例において、オフ切り替え回路とアクティブクランプ回路との間で選択する選択回

10

20

30

40

50

路は、さらに別の要素を備え得る。例えば、各オフ切り替え動作の前に、電流が、信号 560 ( $U_{ACL}$ ) に対する入力に供給され得る。内部回路により提供され、同じネットワークに対する源となるさらなる電流（すなわち、図 5 における  $U_{ACL}$ ）は、このネットワークに提供される電流が、ネットワークにおける電圧をもたらすか試験するのに使用され得る。その場合、アクティブクランプ信号が効果的であり得る。加えて、フリップフロップ 581 の出力パルスの持続期間であって、この持続期間に応答して有効化信号 566 (SSD\_EN) が生成される持続時間が、所定の最小持続期間まで延長され得る。代替的に、比較回路 578、579 の出力パルスの持続時間が、所定の最小持続期間まで延長され得る。これらの方策により、選択回路の異常による影響の受けやすさが低減し得る。本発明に関する例に対する上記の説明は、網羅的であることも、その例に限定することも意図していない。本発明の特定の実施形態と例とは、本明細書において例示を目的として説明しており、本発明から逸脱することなく様々な変形が可能である。電圧、電流、周波数、電力、範囲の値、時間などの特定の例は、例示にすぎないため、本発明は、これらの変数に他の値を使用しても実装され得る。

### 【0066】

これらの変更は、上記の詳細な説明を踏まえて、本発明の例を使用して実現され得る。後述の請求項で使用する用語は、本発明を説明と請求項とに開示した特定の実施形態に限定するように解釈してはならない。本説明と図面とは、例示的とみなされ、限定的とはみなされない。

10

20

【図 1A】

FIG. 1A

【図 1B】

FIG. 1B

【 図 2 】

【図3】

【 図 4 】

FIG. 4

【 义 5 】

**FIG. 3**

【図6】

FIG. 6

【図7】

FIG. 7

---

フロントページの続き

審査官 麻生 哲朗

(56)参考文献 特開平06-291631(JP, A)

特開2011-200037(JP, A)

特開2012-016110(JP, A)

米国特許出願公開第2008/0266727(US, A1)

特開2009-225506(JP, A)

特開2001-197724(JP, A)

米国特許第06459324(US, B1)

(58)調査した分野(Int.Cl., DB名)

H02M 1/00 - 1/44

H03K 17/00 - 17/70