(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7403972号**

**(P7403972)**

(45)発行日 令和5年12月25日(2023.12.25)

(24)登録日 令和5年12月15日(2023.12.15)

(51)国際特許分類

F I

|         |                  |         |        |

|---------|------------------|---------|--------|

| H 0 4 N | 25/704 (2023.01) | H 0 4 N | 25/704 |

| H 0 4 N | 25/779 (2023.01) | H 0 4 N | 25/779 |

| H 0 4 N | 25/76 (2023.01)  | H 0 4 N | 25/76  |

| H 0 1 L | 27/146 (2006.01) | H 0 1 L | 27/146 |

A

請求項の数 17 (全27頁)

(21)出願番号 特願2019-90581(P2019-90581)

(22)出願日 令和1年5月13日(2019.5.13)

(65)公開番号 特開2020-17941(P2020-17941A)

(43)公開日 令和2年1月30日(2020.1.30)

審査請求日 令和4年5月11日(2022.5.11)

(31)優先権主張番号 10-2018-0085245

(32)優先日 平成30年7月23日(2018.7.23)

(33)優先権主張国・地域又は機関

韓国(KR)

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 12

9

129, Samsung-ro, Yeo

ngtong-gu, Suwon-si

, Gyeonggi-do, Repub

lic of Korea

110000051

弁理士法人共生国際特許事務所

李 景 鎬

大韓民国京畿道水原市靈通区靈通路 17

4番街 12, 203 棟 2101号

最終頁に続く

(54)【発明の名称】 イメージセンサ

**(57)【特許請求の範囲】****【請求項 1】**

第1方向及び第2方向に沿って配列された複数のピクセルを含み、前記複数のピクセルはそれぞれ、第1フォトダイオードグループと第2フォトダイオードグループとに区分され、1つのカラーフィルタを共有する複数のフォトダイオードを含み、第1フォトダイオードグループ及び第2フォトダイオードグループのうちの少なくとも1つが、前記第1方向及び前記第2方向のうちの少なくとも一方において互いに隣接して配置される2つ以上の前記フォトダイオードを有するピクセルアレイと、

前記複数のピクセルからピクセル信号を獲得してイメージデータを生成し、1つの前記ピクセルにおいて前記第1フォトダイオードグループと前記第2フォトダイオードグループのうちの少なくとも1つに含まれる前記複数のフォトダイオードのうちの2つ以上が生成した電荷に対応するピクセル電圧を一度に読み出すコントロールロジックと、を含み、

前記複数のピクセルはそれぞれ、前記複数のフォトダイオードの下部に配置された素子連結層と、前記素子連結層の下部に配置されたピクセル回路とを含み、

前記素子連結層は、前記複数のフォトダイオードのうちの少なくとも一部を互いに連結して前記第1フォトダイオードグループ及び前記第2フォトダイオードグループを提供し、

前記コントロールロジックは、前記複数のピクセルのそれぞれにおいて前記第1フォトダイオードグループに連結された第1転送トラジスタをターンオンさせて、前記第1フォトダイオードグループで生成された電荷に対応する第1ピクセル電圧を検出し、前記複数のピクセルのそれぞれにおいて前記第2フォトダイオードグループに連結された第2転送

トランジスタをターンオンさせて、前記第1フォトダイオードグループと前記第2フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、前記和のピクセル電圧と前記第1ピクセル電圧との差を計算して、前記第2フォトダイオードグループで生成された電荷に対応する第2ピクセル電圧を検出し、

前記コントロールロジックは、前記第1ピクセル電圧を検出した後、前記和のピクセル電圧を検出する前に前記第1転送トランジスタ及び前記第2転送トランジスタに連結され、電荷が蓄積されるフローティングディフュージョンをリセットしないことを特徴とするイメージセンサ。

#### 【請求項2】

前記ピクセル回路は、前記フローティングディフュージョンに蓄積された電荷に対応する電圧を生成する駆動トランジスタ、前記駆動トランジスタが生成した電圧を前記コントロールロジックに出力する選択トランジスタ、及び前記フローティングディフュージョンをリセットするリセットトランジスタを含むことを特徴とする請求項1に記載のイメージセンサ。

10

#### 【請求項3】

前記コントロールロジックは、前記第1ピクセル電圧及び前記第2ピクセル電圧を用いて自動焦点機能を提供することを特徴とする請求項1に記載のイメージセンサ。

#### 【請求項4】

前記コントロールロジックは、前記ピクセル電圧を用いてイメージデータを生成することを特徴とする請求項1に記載のイメージセンサ。

20

#### 【請求項5】

前記素子連結層は、N型不純物でドープされた領域であることを特徴とする請求項1に記載のイメージセンサ。

#### 【請求項6】

前記複数のピクセルのうちの互いに隣接する一部のピクセルに含まれる前記素子連結層は、互いに異なる面積または形状を有することを特徴とする請求項1に記載のイメージセンサ。

#### 【請求項7】

前記複数のピクセルのうちの少なくとも1つにおいて、前記第1フォトダイオードグループと前記第2フォトダイオードグループとは、互いに異なる大きさの受光面積を有することを特徴とする請求項1に記載のイメージセンサ。

30

#### 【請求項8】

前記複数のピクセルのうちの少なくとも1つにおいて、前記第1フォトダイオードグループと前記第2フォトダイオードグループとは、互いに同一の大きさの受光面積を有することを特徴とする請求項1に記載のイメージセンサ。

#### 【請求項9】

第1方向及び第2方向に沿って配列された複数のピクセルを含み、前記複数のピクセルはそれぞれ、第1フォトダイオードグループと第2フォトダイオードグループとに区分され、1つのカラーフィルタを共有する複数のフォトダイオードを含み、第1フォトダイオードグループ及び第2フォトダイオードグループのうちの少なくとも1つが、前記第1方向及び前記第2方向のうちの少なくとも一方向において互いに隣接して配置される2つ以上の前記フォトダイオードを有するピクセルアレイと、

40

前記複数のピクセルからピクセル信号を獲得してイメージデータを生成し、1つの前記ピクセルにおいて前記第1フォトダイオードグループと前記第2フォトダイオードグループのうちの少なくとも1つに含まれる前記複数のフォトダイオードのうちの2つ以上が生成した電荷に対応するピクセル電圧を一度に読み出すコントロールロジックと、を含み、前記コントロールロジックは、前記複数のピクセルのそれぞれにおいて前記第1フォトダイオードグループに連結された第1転送トランジスタをターンオンさせて、前記第1フォトダイオードグループで生成された電荷に対応する第1ピクセル電圧を検出し、前記複数のピクセルのそれぞれにおいて前記第2フォトダイオードグループに連結された第2転送

50

トランジスタをターンオンさせて、前記第1フォトダイオードグループと前記第2フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、前記和のピクセル電圧と前記第1ピクセル電圧との差を計算して、前記第2フォトダイオードグループで生成された電荷に対応する第2ピクセル電圧を検出し、

前記コントロールロジックは、前記第1ピクセル電圧を検出した後、前記和のピクセル電圧を検出する前に前記第1転送トランジスタ及び前記第2転送トランジスタに連結され、電荷が蓄積されるフローティングディフュージョンをリセットせず、

前記複数のピクセルはそれぞれ、前記複数のフォトダイオードにそれぞれ連結された複数の転送トランジスタ、及び前記複数の転送トランジスタのうちの少なくとも一部のゲート電極層を互いに連結して、前記複数のフォトダイオードを前記第1フォトダイオードグループと前記第2フォトダイオードグループとに分離する連結ラインを有することを特徴とするイメージセンサ。10

#### 【請求項 10】

前記複数のピクセルのうちの互いに隣接する一部のピクセルにおいて、前記第1フォトダイオードグループは、互いに異なる位置に設けられることを特徴とする請求項9に記載のイメージセンサ。

#### 【請求項 11】

前記連結ラインは、前記第1フォトダイオードグループを提供する第1連結ライン、及び前記第2フォトダイオードグループを提供する第2連結ラインを含むことを特徴とする請求項9に記載のイメージセンサ。20

#### 【請求項 12】

前記コントロールロジックは、

前記第1連結ラインに連結された転送トランジスタをターンオンさせて、前記第1フォトダイオードグループで生成された電荷に対応する第1ピクセル電圧を検出し、

前記第2連結ラインに連結された転送トランジスタをターンオンさせて、前記第1フォトダイオードグループ及び前記第2フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、

前記和のピクセル電圧と前記第1ピクセル電圧との差を計算して、前記第2フォトダイオードグループで生成された電荷に対応する第2ピクセル電圧を検出することを特徴とする請求項11に記載のイメージセンサ。30

#### 【請求項 13】

前記コントロールロジックは、前記ピクセル電圧を用いてイメージデータを生成し、前記第1ピクセル電圧及び前記第2ピクセル電圧を用いて自動焦点機能を提供することを特徴とする請求項12に記載のイメージセンサ。

#### 【請求項 14】

前記第1フォトダイオードグループと前記第2フォトダイオードグループとは、互いに同一の大きさの受光面積を有することを特徴とする請求項9に記載のイメージセンサ。

#### 【請求項 15】

前記コントロールロジックは、前記複数のピクセルのうちの少なくとも一部から互いに異なる方向への自動焦点機能を提供するための情報を獲得することを特徴とする請求項1に記載のイメージセンサ。40

#### 【請求項 16】

第1方向及び第2方向に沿って配列された複数のピクセルを含み、前記複数のピクセルはそれぞれ、第1フォトダイオードグループと第2フォトダイオードグループとに区分された複数のフォトダイオードを有するピクセルアレイと、

前記複数のピクセルからピクセル信号を獲得してイメージデータを生成し、前記複数のピクセルのうちの1つに含まれる前記複数のフォトダイオードのうちの2つ以上が生成した電荷に対応するピクセル電圧を一度に読み出すコントロールロジックと、を含み、

前記第1フォトダイオードグループ及び前記第2フォトダイオードグループのうちの少なくとも1つは、前記第1方向及び前記第2方向のうちの少なくとも一方向において互いに

10

20

30

40

50

に隣接する 2 つ以上のフォトダイオードを含み、

前記複数のピクセルはそれぞれ、前記複数のフォトダイオードの下部に配置され、前記複数のフォトダイオードのうちの少なくとも一部を互いに連結して前記複数のフォトダイオードを前記第 1 フォトダイオードグループと前記第 2 フォトダイオードグループとに区分する素子連結層、及び前記素子連結層の下に配置されるピクセル回路を含み、

前記ピクセル回路は、前記第 1 フォトダイオードグループに連結された第 1 転送トランジスタ、前記第 2 フォトダイオードグループに連結された第 2 転送トランジスタ、及び前記第 1 転送トランジスタと前記第 2 転送トランジスタとに連結されたフローティングディフュージョンを含み、

前記コントロールロジックは、前記第 1 転送トランジスタをターンオンさせて、前記第 1 フォトダイオードグループで生成された電荷に対応する第 1 ピクセル電圧を検出し、前記第 2 転送トランジスタをターンオンさせて、前記第 1 フォトダイオードグループ及び前記第 2 フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、前記和のピクセル電圧と前記第 1 ピクセル電圧との差を計算して、前記第 2 フォトダイオードグループで生成された電荷に対応する第 2 ピクセル電圧を検出することを特徴とするイメージセンサ。10

#### 【請求項 17】

第 1 方向及び第 2 方向に沿って配列された複数のピクセルを含み、前記複数のピクセルはそれぞれ、第 1 フォトダイオードグループと第 2 フォトダイオードグループとに区分された複数のフォトダイオードを有するピクセルアレイと、20

前記複数のピクセルからピクセル信号を獲得してイメージデータを生成し、前記複数のピクセルのうちの 1 つに含まれる前記複数のフォトダイオードのうちの 2 つ以上が生成した電荷に対応するピクセル電圧を一度に読み出すコントロールロジックと、を含み、

前記第 1 フォトダイオードグループ及び前記第 2 フォトダイオードグループのうちの少なくとも 1 つは、前記第 1 方向及び前記第 2 方向のうちの少なくとも一方向において互いに隣接する 2 つ以上のフォトダイオードを含み、

前記複数のピクセルはそれぞれ、前記複数のフォトダイオードにそれぞれ連結された複数の転送トランジスタ、及び前記複数の転送トランジスタのゲート電極層のうちの少なくとも一部を互いに連結して、前記複数のフォトダイオードを前記第 1 フォトダイオードグループと前記第 2 フォトダイオードグループとに区分する複数の連結ラインを含み、30

前記連結ラインは、前記第 1 フォトダイオードグループに含まれる前記フォトダイオードを互いに連結する第 1 連結ライン、及び前記第 2 フォトダイオードグループに含まれる前記フォトダイオードを互いに連結する第 2 連結ラインを含み、

前記コントロールロジックは、前記第 1 連結ラインに連結された転送トランジスタをターンオンさせて、前記第 1 フォトダイオードグループで生成された電荷に対応する第 1 ピクセル電圧を検出し、前記第 2 連結ラインに連結された転送トランジスタをターンオンさせて、前記第 1 フォトダイオードグループ及び前記第 2 フォトダイオードグループで生成された電荷の和に対応する和のピクセル電圧を検出し、前記和のピクセル電圧と前記第 1 ピクセル電圧との差を計算して、前記第 2 フォトダイオードグループで生成された電荷に対応する第 2 ピクセル電圧を検出することを特徴とするイメージセンサ。40

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、イメージセンサに関する。

##### 【背景技術】

##### 【0002】

イメージセンサは、光を受け入れて電気信号を生成する半導体基板に形成されたセンサであって、複数のピクセルを有するピクセルアレイと、ピクセルアレイを駆動してイメージを生成するためのロジック回路などを含む。複数のピクセルは、外部の光に反応して電荷を生成するフォトダイオード及びフォトダイオードが生成した電荷を電気信号に変換す50

るピクセル回路などを含む。イメージセンサは、写真や動画を撮影するためのカメラに加えて、スマートフォン、タブレットPC、ラップトップコンピュータ、テレビジョン、自動車などに幅広く適用される。最近では、イメージセンサで撮影するイメージの品質を改善するべく、イメージセンサの自動焦点(Auto Focus)機能を向上させるための様々な方法が提案されている。

【先行技術文献】

【特許文献】

【0003】

【文献】特開2013-196004号公報

10

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は、上記従来技術に鑑みてなされたものであって、本発明の目的は、優れた自動焦点機能を提供すると同時に、ピクセル電圧を読み出すリードアウト時間とリードアウト動作による消費電力及びノイズ特性とが改善されたイメージセンサを提供することにある。

【課題を解決するための手段】

【0005】

上記目的を達成するためになされた本発明の一態様によるイメージセンサは、第1方向及び第2方向に沿って配列される複数のピクセルを含み、前記複数のピクセルはそれぞれ、第1フォトダイオードグループと第2フォトダイオードグループとに区分された複数のフォトダイオードを含み、第1フォトダイオードグループ及び第2フォトダイオードグループのうちの少なくとも1つが、前記第1方向及び上記第2方向のうちの少なくとも一方において互いに隣接して配置される2つ以上の前記フォトダイオードを有するピクセルアレイと、前記複数のピクセルからピクセル信号を獲得してイメージデータを生成し、1つの前記ピクセルに含まれる前記複数のフォトダイオードのうちの2つ以上が生成した電荷に対応するピクセル電圧を一度に読み出すコントロールロジックと、を含むことを特徴とする。

20

【0006】

上記目的を達成するためになされた本発明の他の態様によるイメージセンサは、複数のピクセルを有するピクセルアレイと、前記複数のピクセルのそれぞれで生成された電荷を用いてイメージデータを生成するコントロールロジックと、を含み、前記複数のピクセルのそれぞれは、半導体基板内の互いに同一の深さに形成される複数のフォトダイオードと、前記複数のフォトダイオードの下部に配置されるピクセル回路と、前記複数のフォトダイオードと前記ピクセル回路との間に配置されて、前記複数のフォトダイオードのうちの少なくとも一部を互いに物理的に連結する素子連結層と、を含むことを特徴とする。

30

【0007】

上記目的を達成するためになされた本発明のさらに他の態様によるイメージセンサは、複数のピクセルを有するピクセルアレイと、前記複数のピクセルのそれぞれで生成された電荷を用いてイメージデータを生成するコントロールロジックと、を含み、前記複数のピクセルのそれぞれは、半導体基板内の互いに同一の深さに形成される複数のフォトダイオードと、前記複数のフォトダイオードにそれぞれ連結された複数の転送トランジスタと、前記複数の転送トランジスタのうちの少なくとも一部のゲート電極層を互いに連結する連結ラインと、を含むことを特徴とする。

40

【発明の効果】

【0008】

本発明によれば、イメージセンサの複数のピクセルのそれぞれに含まれる複数のフォトダイオードのうちの少なくとも一部で生成された電荷に対応するピクセル電圧を一度に読み出すことにより、リードアウト時間、及びリードアウト動作で消費される電力を低減することができる。また、複数のピクセルのそれぞれから読み出したピクセル電圧の差を計算して自動焦点機能を提供し、一度に読み出すフォトダイオードの組み合わせを様々な設

50

定することにより、自動焦点機能を向上させることができる。

**【図面の簡単な説明】**

**【0 0 0 9】**

【図1】本発明の一実施形態によるイメージセンサを含むイメージ処理装置を示す概略図である。

【図2】本発明の一実施形態によるイメージセンサを示す概略図である。

【図3】本発明の他の実施形態によるイメージセンサを示す概略図である。

【図4】本発明の一実施形態によるイメージセンサの動作を説明するブロック図である。

【図5】本発明の一実施形態によるイメージセンサのピクセルアレイを示す概略図である。

【図6】本発明の一実施形態によるイメージセンサのピクセル回路の一例を示す回路図である。

10

【図7】本発明の一実施形態によるイメージセンサのピクセル回路の他の例を示す回路図である。

【図8】本発明の一実施形態によるイメージセンサのピクセルアレイの一例を示す平面図である。

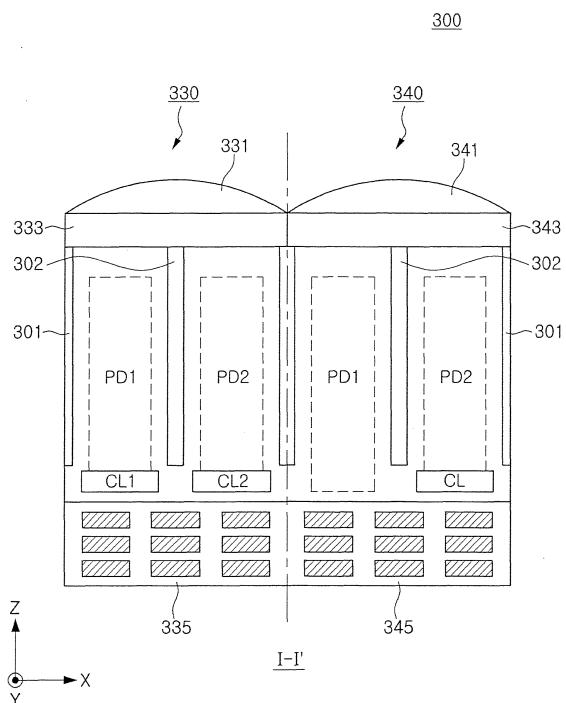

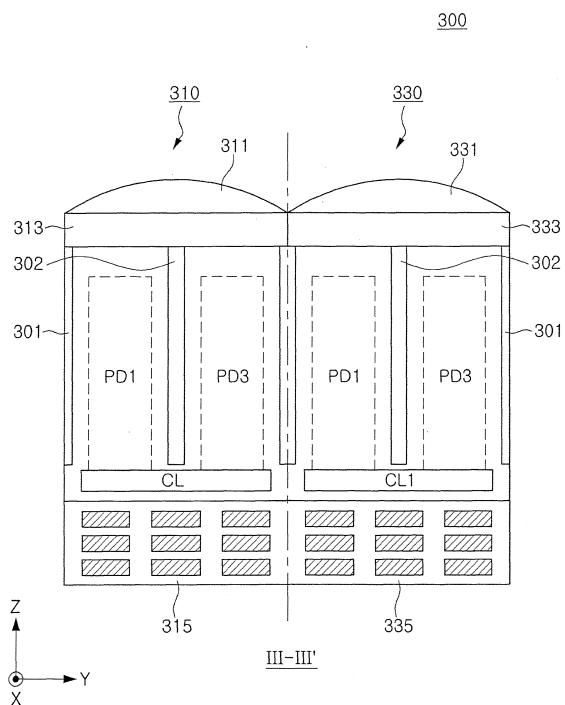

【図9】図8に示すピクセルアレイをI - I'方向から見た断面図である。

【図10】図8に示すピクセルアレイをII - II'方向から見た断面図である。

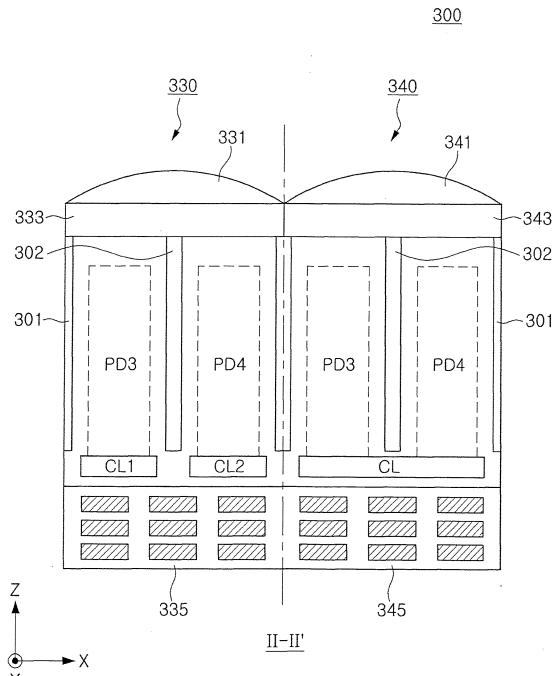

【図11】図8に示すピクセルアレイをIII - III'方向から見た断面図である。

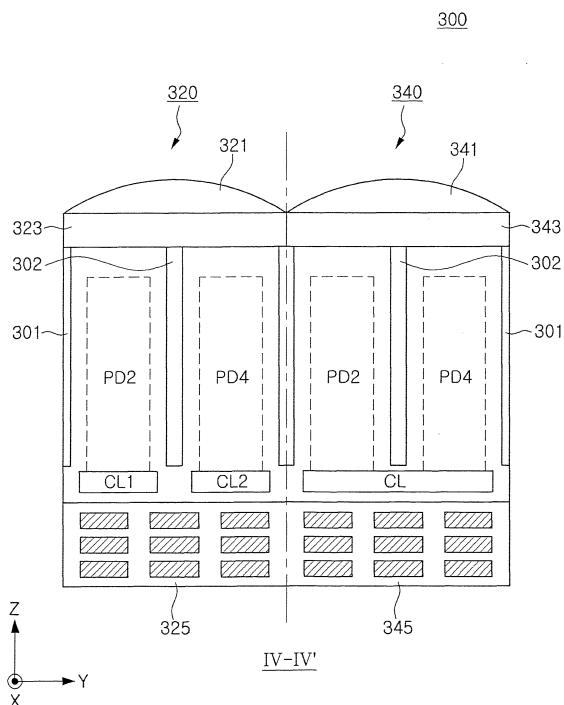

【図12】図8に示すピクセルアレイをIV - IV'方向から見た断面図である。

【図13】本発明の一実施形態によるイメージセンサのピクセルアレイの他の例の一部領域を示す平面図である。

20

【図14】図13に示すピクセルアレイをV - V'方向から見た断面図である。

【図15】本発明の一実施形態によるイメージセンサのピクセルアレイの一部領域を示す平面図である。

【図16】図15に示すピクセルアレイをVI - VI'方向から見た断面図である。

【図17】本発明のさらに他の実施形態によるイメージセンサのピクセルアレイの一部領域を示す平面図である。

【図18】本発明のさらに他の実施形態によるイメージセンサのピクセル回路を示す回路図である。

【図19】本発明のさらに他の実施形態によるイメージセンサの動作を説明するためのタイミング図である。

30

【図20】本発明の一実施形態によるイメージセンサを含む電子機器の概要を示すブロック図である。

**【発明を実施するための形態】**

**【0 0 1 0】**

以下、図面を参照しながら、本発明の好適な実施形態を詳細に説明する。

**【0 0 1 1】**

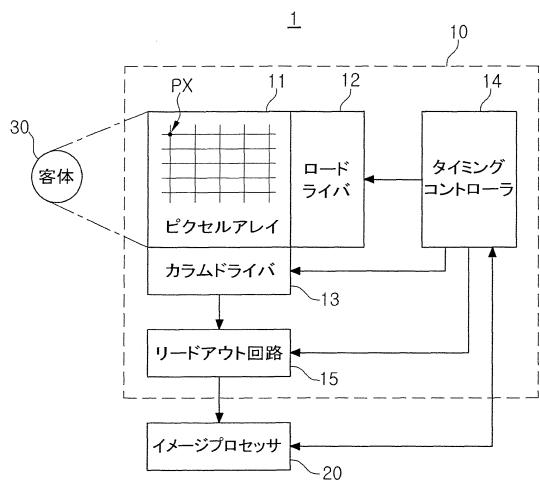

図1は、本発明の一実施形態によるイメージセンサを含むイメージ処理装置を示す概略図である。

**【0 0 1 2】**

図1を参照すると、本発明の一実施形態によるイメージ処理装置1は、イメージセンサ10、及びイメージプロセッサ20を備える。イメージセンサ10は、ピクセルアレイ11、ロードライバ12、カラムドライバ13、リードアウト回路15、及びタイミングコントローラ14を含む。ロードライバ12、カラムドライバ13、リードアウト回路15、及びタイミングコントローラ14は、ピクセルアレイ11を制御するための回路であつて、コントロールロジックに含まれる。

40

**【0 0 1 3】**

イメージセンサ10は、イメージプロセッサ20から受信した制御命令に従って動作し、客体(object)30から伝達される光を電気信号に変換してイメージプロセッサ20に出力する。イメージセンサ10に含まれるピクセルアレイ11は、複数のピクセル

50

P X を含み、複数のピクセル P X は、光を受け入れて電荷を生成する光電素子、例えば、フォトダイオード (Photo Diode、PD) を含む。一実施形態において、複数のピクセル P X のうちの少なくとも 1 つは、2 つ以上のフォトダイオードを含み、イメージセンサ 10 は、複数のピクセル P X のうちの少なくとも 1 つに含まれる 2 つ以上のフォトダイオードのそれぞれによって生成されるピクセル信号の位相差を用いて自動焦点 (Auto Focus) 機能を提供する。

#### 【0014】

一方、複数のピクセル P X はそれぞれ、フォトダイオードで生成される電荷からピクセル信号を生成するためのピクセル回路を含む。一実施形態において、ピクセル回路は、転送トランジスタ、駆動トランジスタ、選択トランジスタ、及びリセットトランジスタを含む。ピクセル回路は、複数のピクセル P X のそれからリセット電圧とピクセル電圧を検出し、その差を計算することにより、ピクセル信号を獲得する。ピクセル電圧は、複数のピクセル P X のそれぞれに含まれているフォトダイオードで生成された電荷が反映された電圧である。

10

#### 【0015】

複数のピクセル P X のそれぞれが 2 つ以上のフォトダイオードを有する場合、複数のピクセル P X はそれぞれ、2 つ以上のフォトダイオードのそれぞれで生成された電荷を処理するためのピクセル回路を含む。すなわち、本実施形態において、ピクセル回路は、転送トランジスタ、駆動トランジスタ、選択トランジスタ、及びリセットトランジスタの少なくとも 1 つのトランジスタを 2 つ以上含む。

20

#### 【0016】

ロードライバ 12 は、ピクセルアレイ 11 を行 (row) 単位で駆動する。例えば、ロードライバ 12 は、ピクセル回路の転送トランジスタを制御する転送制御信号、リセットトランジスタを制御するリセット制御信号、選択トランジスタを制御する選択制御信号を生成する。

#### 【0017】

カラムドライバ 13 は、相関二重サンプラー (Correlated Double Sampler、CDS)、及びアナログ - デジタルコンバータ (Analog-to-Digital Converter、ADC) を含む。相関二重サンプラーは、ロードライバ 12 が供給する行選択信号によって選択される行に含まれるピクセル P X にカラムラインを介して連結され、相関二重サンプリングを行ってリセット電圧及びピクセル電圧を検出する。アナログ - デジタルコンバータは、相関二重サンプラーが検出したリセット電圧及びピクセル電圧をデジタル信号に変換してリードアウト回路 15 に伝達する。

30

#### 【0018】

リードアウト回路 15 は、デジタル信号を一時記憶するラッチまたはバッファ回路及び増幅回路を含み、カラムドライバ 13 から受信したデジタル信号を一時記憶したり増幅することでイメージデータを生成する。ロードライバ 12、カラムドライバ 13、及びリードアウト回路 15 の動作タイミングは、タイミングコントローラ 14 によって決定され、タイミングコントローラ 14 は、イメージプロセッサ 20 が転送する制御命令によって動作する。イメージプロセッサ 20 は、リードアウト回路 15 が出力するイメージデータを信号処理して、ディスプレイ装置などに出力し、メモリなどの記憶装置に記憶する。また、イメージ処理装置 1 が自律走行車両に搭載される場合、イメージプロセッサ 20 は、イメージデータを信号処理して、自律走行車両を制御するメインコントローラなどに転送する。

40

#### 【0019】

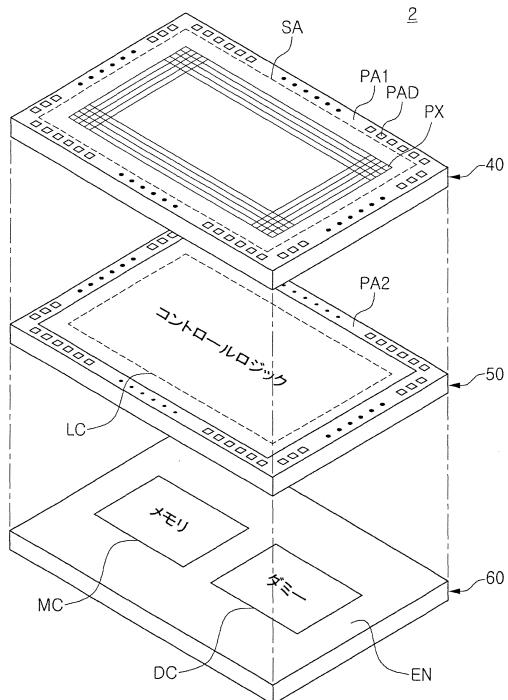

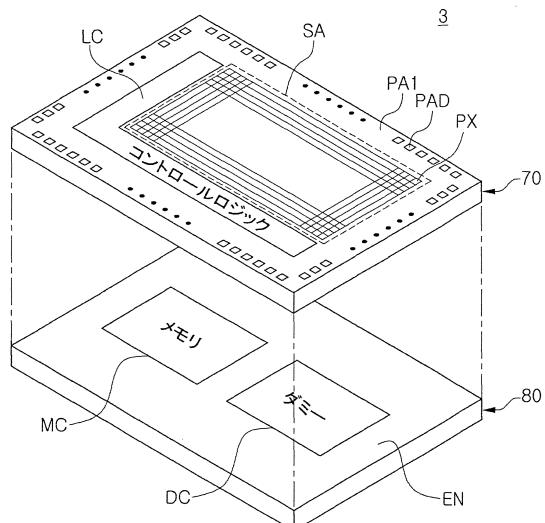

図 2 は、本発明の一実施形態によるイメージセンサを示す概略図であり、図 3 は、本発明の他の実施形態によるイメージセンサを示す概略図である。説明の便宜のために、図 2 及び図 3 において互いに重複する一部の構成要素の説明は省略する。

#### 【0020】

まず、図 2 を参照すると、本発明の一実施形態によるイメージセンサ 2 は、第 1 層 40

50

、第1層40の下部に設けられた第2層50、及び第2層50の下部に設けられた第3層60を含む。第1層40、第2層50、及び第3層60は、互いに垂直方向に積層される。一実施形態において、第1層40及び第2層50は、ウェハレベルで互いに積層され、第3層60は、チップレベルで第2層50の下部に付着される。第1層40～第3層60は、1つの半導体パッケージとして提供される。

#### 【0021】

第1層40は、複数のピクセルPXが設けられたセンシング領域SAと、センシング領域SAの周辺に設けられた第1パッド領域PA1と、を含む。第1パッド領域PA1には、複数の上部パッドPADが含まれ、複数の上部パッドPADは、ビア(VIA、図示せず)を介して、第2層50の第2パッド領域PA2に設けられたパッド及びコントロールロジックLCに連結される。

10

#### 【0022】

複数のピクセルPXはそれぞれ、光を受け入れて電荷を生成するフォトダイオードと、フォトダイオードで生成された電荷を処理するピクセル回路を含む。ピクセル回路は、フォトダイオードで生成された電荷に対応する電圧を出力するための複数のトランジスタを含む。

#### 【0023】

第2層50は、コントロールロジックLCを提供する複数の素子を含む。コントロールロジックLCに含まれる複数の素子は、第1層40に設けられたピクセル回路を駆動するための回路、例えば、ロードライバ、カラムドライバ、及びタイミングコントローラなどを提供する。コントロールロジックLCは、コントロールロジック回路と解釈され、コントロールロジックまたはコントロールロジック回路という用語は、互いに等価的な用語として用いられる。コントロールロジックLCに含まれる複数の素子は、第1パッド領域PA1及び第2パッド領域PA2を介してピクセル回路に連結される。コントロールロジックLCは、複数のピクセルPXからリセット電圧及びピクセル電圧を獲得して、ピクセル信号を生成する。

20

#### 【0024】

本発明の一実施形態において、複数のピクセルPXのうちの少なくとも1つは、同一のレベルに配置された複数のフォトダイオードを含む。複数のフォトダイオードのそれぞれの電荷から生成されたピクセル信号は、互いに位相差を有し、コントロールロジックLCは、1つのピクセルPXに含まれた複数のフォトダイオードで生成されたピクセル信号の位相差に基づいて自動焦点機能を提供する。

30

#### 【0025】

第2層50の下部に設けられた第3層60は、メモリチップMC、ダミーチップDC、及びメモリチップMCとダミーチップDCとを封止する保護層ENを含む。メモリチップMCは、ダイナミックランダムアクセスメモリ(DRAM)または静态ランダムアクセスメモリ(SRAM)であり、ダミーチップDCはデータを実際に記憶する機能は有しない。メモリチップMCは、バンプによって、第2層50のコントロールロジックLCに含まれた素子のうちの少なくとも一部に電気的に連結され、自動焦点機能を提供する上で必要な情報を記憶する。一実施形態において、バンプはマイクロバンプである。

40

#### 【0026】

次に、図3を参照すると、本発明の他の実施形態によるイメージセンサ3は、第1層70及び第2層80を含む。第1層70は、複数のピクセルPXが設けられたセンシング領域SA、複数のピクセルPXを駆動するための素子が設けられたコントロールロジック領域LC、並びにセンシング領域SA及びコントロールロジック領域LCの周辺に設けられた第1パッド領域PA1を含む。第1パッド領域PA1には、複数の上部パッドPADが含まれ、複数の上部パッドPADは、ビア(VIA、図示せず)を介して、第2層80に設けられたメモリチップMCに連結される。第2層80は、メモリチップMC、ダミーチップDC、及びメモリチップMCとダミーチップDCとを封止する保護層ENを含む。

#### 【0027】

50

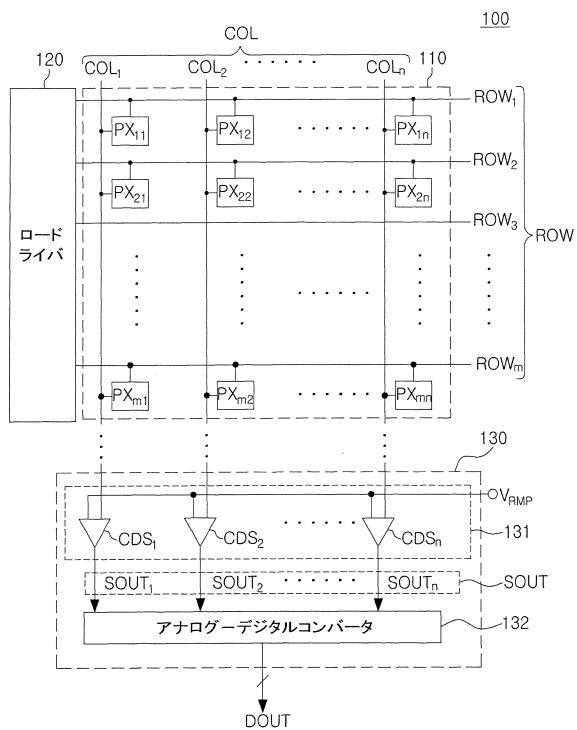

図4は、本発明の一実施形態によるイメージセンサの動作を説明するブロック図である。

#### 【0028】

図4を参照すると、本発明の一実施形態によるイメージセンサ100は、ピクセルアレイ110、ロードライバ120、及びリードアウト回路130を含む。ロードライバ120は、ローライン(ROW: ROW<sub>1</sub> ~ ROW<sub>m</sub>)を介して転送制御信号、リセット制御信号、及び選択制御信号を各ピクセル回路に入力する。リードアウト回路130は、ロードライバ120が選択したローラインROWに連結されたピクセルPXからピクセル電圧及びリセット電圧を検出する。リードアウト回路130は、複数の相関二重サンプラー(CDS<sub>1</sub> ~ CDS<sub>n</sub>)を含むサンプリング回路131と、サンプリング回路131の出力(SOUT: SOUT<sub>1</sub> ~ SOUT<sub>n</sub>)をデジタルデータDOUTに変換するアナログ-デジタルコンバータ132とを含む。一例として、図4に示す実施形態において、アナログ-デジタルコンバータ132は、デジタルデータDOUTを出力する。

#### 【0029】

ピクセルアレイ110は、一方向に沿って延長される複数のローラインROW及びローラインROWと交差するカラムライン(COL: COL<sub>1</sub> ~ COL<sub>n</sub>)を含む。ローラインROWとカラムラインCOLとは、ピクセル(PX<sub>11</sub> ~ PX<sub>mn</sub>)に連結され、ピクセル(PX<sub>11</sub> ~ PX<sub>mn</sub>)はそれぞれ、フォトダイオード及びピクセル回路を含む。一実施形態において、ピクセル(PX<sub>11</sub> ~ PX<sub>mn</sub>)はそれぞれ、自動焦点機能を提供するように、同一のレベルに配置される複数のフォトダイオードを含む。

#### 【0030】

自動焦点機能を提供するために、複数のピクセル(PX<sub>11</sub> ~ PX<sub>mn</sub>)がそれぞれ複数のフォトダイオードを含む場合、リードアウト回路130は、複数のフォトダイオードのそれぞれからピクセル電圧を検出する。したがって、ピクセル(PX<sub>11</sub> ~ PX<sub>mn</sub>)のそれぞれから、複数回にわたってピクセル電圧を検出しなければならないため、リードアウト動作に必要な時間及び消費電力が増加する。また、ピクセル(PX<sub>11</sub> ~ PX<sub>mn</sub>)のそれぞれに含まれるフォトダイオードからピクセル電圧を検出するため、リードアウト動作で現れるノイズ成分が増加し、イメージセンサ100の性能が低下する。

#### 【0031】

本発明の一実施形態では、上述の問題を解決するために、ピクセル(PX<sub>11</sub> ~ PX<sub>mn</sub>)のそれぞれに含まれる複数のフォトダイオードのうちの少なくとも一部で生成された電荷が反映されたピクセル電圧を一度に読み出す。したがって、リードアウト動作に必要な時間及び消費電力を減らすことができ、リードアウト動作の回数を減らしてノイズ成分を低減させ、イメージセンサ100の性能を改善される。

#### 【0032】

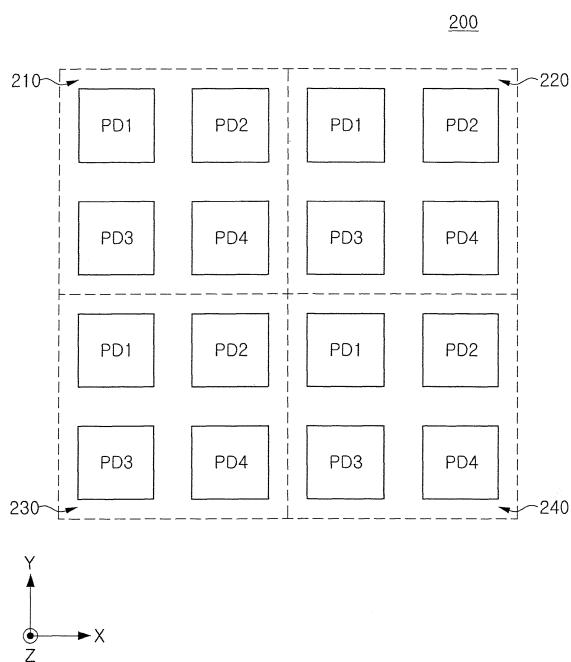

図5は、本発明の一実施形態によるイメージセンサのピクセルアレイを示す概略図である。

#### 【0033】

図5を参照すると、本発明の一実施形態によるイメージセンサのピクセルアレイ200は、複数のピクセル(210 ~ 240)を含む。複数のピクセル(210 ~ 240)は、第1方向(X軸方向)及び第2方向(Y軸方向)に沿って配列される。複数のピクセル(210 ~ 240)はそれぞれ、複数のフォトダイオード(PD1 ~ PD4)を含む。図5に示す実施形態では、複数のピクセル(210 ~ 240)が、それぞれ4つのフォトダイオード(PD1 ~ PD4)を含むと仮定したが、複数のピクセル(210 ~ 240)のそれぞれに含まれるフォトダイオード(PD1 ~ PD4)の個数は、様々に変更される。

#### 【0034】

通常の場合、イメージセンサのリードアウト回路は、複数のフォトダイオード(PD1 ~ PD4)からピクセル電圧をそれぞれ読み出してピクセル信号を獲得する。一例として、第1ピクセル210からピクセル信号を獲得する動作は、第1 ~ 第4フォトダイオード(PD1 ~ PD4)のそれぞれからピクセル電圧を読み出す動作を含む。したがって、第1ピクセル210からピクセル信号を獲得するために、ピクセル電圧を読み出すリードア

10

20

30

40

50

ウト動作は4回行われ、これは、リードアウト動作に必要な時間及び／または消費電力の増加につながる。また、リードアウト動作ごとにピクセル電圧にノイズ成分が含まれるため、イメージ品質が低下する。

#### 【0035】

本発明では、複数のピクセル（210～240）のそれぞれに含まれる複数のフォトダイオード（PD1～PD4）のうちの少なくとも一部で生成された電荷に対応するピクセル電圧を、リードアウト回路が一度に読み出す。リードアウト回路が少なくとも一部のフォトダイオード（PD1～PD4）で生成された電荷に対応するピクセル電圧を一度に読み出すことができるよう、複数のフォトダイオード（PD1～PD4）のうちの少なくとも一部が連結されるか、またはピクセル回路の構成などが変更される。

10

#### 【0036】

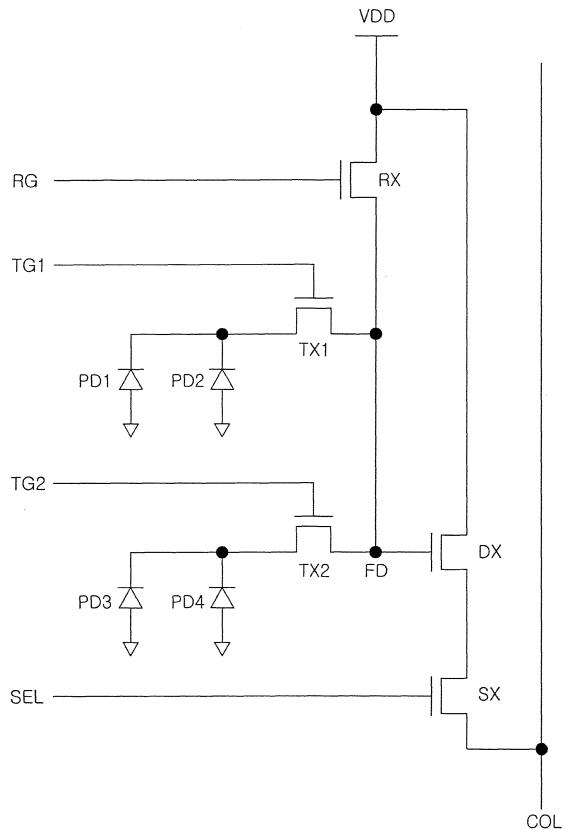

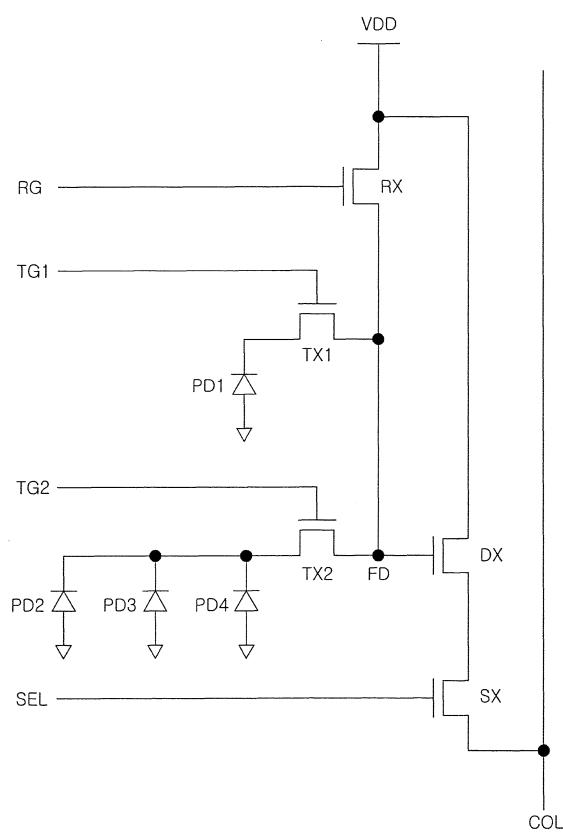

図6及び図7は、本発明の一実施形態によるイメージセンサのピクセル回路を示す回路図である。一例として、図6及び図7の実施形態によるピクセル回路は、図5に示すイメージセンサに適用されるピクセル回路である。

#### 【0037】

まず、図6を参照すると、本発明の一実施形態によるイメージセンサのピクセル回路の一例は、リセットトランジスタRX、駆動トランジスタDX、選択トランジスタSX、第1転送トランジスタTX1、及び第2転送トランジスタTX2を含む。第1転送トランジスタTX1は、第1フォトダイオードPD1及び第2フォトダイオードPD2に連結され、第2転送トランジスタTX2は、第3フォトダイオードPD3及び第4フォトダイオードPD4に連結される。

20

#### 【0038】

以下、図6に示すピクセル回路の動作を説明する。まず、リセットトランジスタRXがリセット制御信号RGによってターンオンされると、フローティングディフュージョンFDが電源電圧VDDによってリセットされる。その後に選択トランジスタSXが選択制御信号SELによってターンオンされると、イメージセンサのリードアウト回路は、カラムラインCOLを介してフローティングディフュージョンFDからリセット電圧を検出する。

#### 【0039】

リセット電圧を検出する動作が完了すると、第1転送トランジスタTX1がターンオンされる。このとき、第2転送トランジスタTX2はターンオフされる。第1転送トランジスタTX1が第1転送制御信号TG1によってターンオンされると、第1及び第2フォトダイオード（PD1、PD2）で生成された電荷がフローティングディフュージョンFDに蓄積される。その後に選択トランジスタSXがターンオンされると、リードアウト回路は、カラムラインCOLを介して、第1及び第2フォトダイオード（PD1、PD2）で生成された電荷の量に対応する第1ピクセル電圧を検出する。

30

#### 【0040】

第1ピクセル電圧を検出する動作が完了すると、第2転送トランジスタTX2がターンオンされる。第2転送トランジスタTX2がターンオンされると、第3及び第4フォトダイオード（PD3、PD4）で生成された電荷がフローティングディフュージョンFDに蓄積される。このとき、フローティングディフュージョンFDに蓄積された電荷は、第1～第4フォトダイオード（PD1～PD4）で生成された電荷である。リードアウト回路は、カラムラインCOLを介して、第1～第4フォトダイオード（PD1～PD4）で生成された電荷の総量に対応するピクセル電圧を検出する。

40

#### 【0041】

イメージセンサのコントロールロジックは、上述のピクセル電圧と第1ピクセル電圧との差を計算することにより、第3及び第4フォトダイオード（PD3、PD4）で生成された電荷の量に対応する第2ピクセル電圧を獲得する。コントロールロジックは、第1ピクセル電圧及び第2ピクセル電圧を用いて第1ピクセル信号及び第2ピクセル信号を獲得し、第1ピクセル信号と第2ピクセル信号との位相差を用いて自動焦点機能を提供する。一方、コントロールロジックは、第1～第4フォトダイオード（PD1～PD4）で生成

50

された電荷の和に対応するピクセル電圧から獲得したピクセル信号を用いて、イメージデータを生成する。

#### 【0042】

本実施形態では、リードアウト回路がピクセル回路を介して複数のフォトダイオード（P D 1 ~ P D 4）のそれぞれからピクセル電圧を獲得せず、フォトダイオード（P D 1 ~ P D 4）のうちの少なくとも一部からピクセル電圧を一度に読み出す。したがって、リードアウト動作の回数を減らしてリードアウト動作に必要な時間及び／または消費電力を低減させ、リードアウト動作回数の増加によるノイズ成分の増加及びそれによるイメージ品質の低下を最小限に抑えることができる。

#### 【0043】

次に、図7を参照すると、本発明の一実施形態によるイメージセンサのピクセル回路の他の例は、第1転送トランジスタT X 1が第1フォトダイオードP D 1に連結され、第2転送トランジスタT X 2が第2～第4フォトダイオード（P D 2～P D 4）に連結される。第1転送トランジスタT X 1がターンオンされて、第1フォトダイオードP D 1の電荷がフローティングディフュージョンF Dに蓄積されると、リードアウト回路は、第1フォトダイオードP D 1の電荷に対応する第1ピクセル電圧を検出する。次に、第2転送トランジスタT X 2がターンオンされて、第2～第4フォトダイオード（P D 2～P D 4）の電荷がフローティングディフュージョンF Dに移動すると、リードアウト回路は、第1～第4フォトダイオード（P D 1～P D 4）で生成された電荷の和に対応するピクセル電圧を検出する。

10

#### 【0044】

コントロールロジックは、ピクセル電圧と第1ピクセル電圧との差を計算することにより、第2～第4フォトダイオード（P D 2～P D 4）で生成された電荷の和に対応する第2ピクセル電圧を獲得する。コントロールロジックは、第1ピクセル電圧及び第2ピクセル電圧のそれぞれから生成される第1ピクセル信号と第2ピクセル信号との位相差を用いて自動焦点機能を提供する。また、ピクセル電圧から生成されるピクセル信号を用いてイメージデータを生成する。

20

#### 【0045】

図6及び図7に示す実施形態ではそれぞれ、互いに異なる方向への自動焦点機能を提供する。図6に示す実施形態では、第1及び第2フォトダイオード（P D 1、P D 2）の電荷からピクセル電圧が一度に検出され、第3及び第4フォトダイオード（P D 3、P D 4）の電荷からピクセル電圧が一度に検出される。したがって、図5に示す実施形態によるピクセルアレイ200を仮定すると、図6に示す実施形態によるピクセル回路は、第2方向（Y軸方向）に焦点を合わせるのに必要な情報を生成する。同様に、図7に示す実施形態によるピクセル回路は、第2方向（Y軸方向）を基準に反時計回りに45度回転移動した方向に焦点を合わせるのに必要な情報を提供する。

30

#### 【0046】

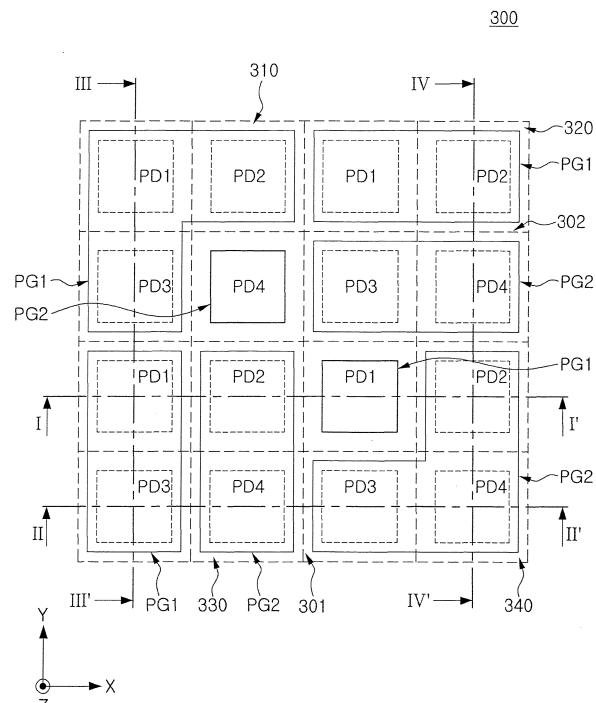

図8～図12は、本発明の一実施形態によるイメージセンサのピクセル構造の一例を説明するために提供される図である。

#### 【0047】

図8は、本発明の一実施形態によるイメージセンサのピクセルアレイの一例を示す平面図である。図8を参照すると、本実施形態によるイメージセンサのピクセルアレイ300は、複数のピクセル（310～340）を含む。図8に示す実施形態は、説明の便宜のために、ピクセルアレイ300の一部領域のみを示したものである。

40

#### 【0048】

複数のピクセル（310～340）はそれぞれ、第1～第4フォトダイオード（P D 1～P D 4）を含む。第1～第4フォトダイオード（P D 1～P D 4）は、第1方向（X軸方向）及び第2方向（Y軸方向）に沿って配列され、第3方向（Z軸方向）において実質的に同一のレベルに位置する。複数のピクセル（310～340）の間には、第1素子分離膜301が設けられ、複数のピクセル（310～340）のそれぞれには、第2素子分

50

離膜 302 が設けられる。第 2 素子分離膜 302 によって、複数のピクセル (310 ~ 340) のそれぞれにおいて、第 1 ~ 第 4 フォトダイオード (PD1 ~ PD4) が形成された複数の単位領域が定義される。

#### 【0049】

図 8 に示す実施形態では、複数のピクセル (310 ~ 340) のそれぞれにおいて、第 1 ~ 第 4 フォトダイオード (PD1 ~ PD4) のうちの少なくとも一部が互いに物理的に連結される。一例として、第 1 ピクセル 310 の場合、第 1 ~ 第 3 フォトダイオード (PD1 ~ PD3) が互いに物理的に連結されて第 1 フォトダイオードグループ PG1 を提供する。第 1 ピクセル 310 の第 4 フォトダイオード PD4 は、単独で第 2 フォトダイオードグループ PG2 を提供する。一方、第 2 ピクセル 320 では、第 1 及び第 2 フォトダイオード (PD1, PD2) が互いに物理的に連結されて第 1 フォトダイオードグループ PG1 を提供し、第 3 及び第 4 フォトダイオード (PD3, PD4) が互いに物理的に連結されて第 2 フォトダイオードグループ PG2 を提供する。

#### 【0050】

また、第 3 ピクセル 330 の第 1 フォトダイオードグループ PG1 は、互いに物理的に連結された第 1 及び第 3 フォトダイオード (PD1, PD3) を含み、第 2 フォトダイオードグループ PG2 は、互いに物理的に連結された第 2 及び第 4 フォトダイオード (PD2, PD4) を含む。第 4 ピクセル 340 の場合、第 1 フォトダイオード PD1 が単独で第 1 フォトダイオードグループ PG1 を提供し、互いに物理的に連結された第 2 ~ 第 4 フォトダイオード (PD2 ~ PD4) が第 2 フォトダイオードグループ PG2 を提供する。

#### 【0051】

上記の説明において、物理的に連結されるという表現は、第 1 ~ 第 4 フォトダイオード (PD1 ~ PD4) のうちの 2 つ以上のフォトダイオードが素子連結層を介して直接連結されるという意味に解釈される。すなわち、第 1 ピクセル 310 の場合、第 1 ~ 第 3 フォトダイオード (PD1 ~ PD3) が素子連結層で共通に連結されて第 1 フォトダイオードグループ PG1 を形成する。本発明の一実施形態において、第 1 フォトダイオードグループ PG1 または第 2 フォトダイオードグループ PG2 を提供するための素子連結層は、互いに隣接するピクセル (310 ~ 340) において互いに異なる形状または面積を有する。一例として、第 1 ピクセル 310 と第 2 ピクセル 320 のそれぞれにおける素子連結層の形状、面積、及び個数は、互いに異なる。

#### 【0052】

本発明の一実施形態において、素子連結層は、複数のフォトダイオード (PD1 ~ PD4) の下部に配置される。また、素子連結層は、複数のフォトダイオード (PD1 ~ PD4) のうちの少なくとも一部を互いに連結することにより、複数のフォトダイオード (PD1 ~ PD4) を第 1 フォトダイオードグループ PG1 と第 2 フォトダイオードグループ PG2 とに分離する。

#### 【0053】

第 1 ~ 第 4 フォトダイオード (PD1 ~ PD4) のうちの少なくとも一部が素子連結層を介して互いに連結されることにより、ピクセル回路は、素子連結層に連結された 2 つ以上のフォトダイオード (PD1 ~ PD4) からピクセル電圧を一度に読み出すことができる。したがって、複数のピクセル (310 ~ 340) のそれこれからピクセル電圧を読み出すリードアウト動作の回数を減らすことができ、それによりリードアウト動作の所要時間及び消費電力を減らす一方、リードアウト動作回数の増加によるノイズの増加を最小限に抑えることができる。また、第 1 フォトダイオードグループ PG1 と第 2 フォトダイオードグループ PG2 とのそれぞれに転送トランジスタが 1 つずつ連結される。すなわち、複数のピクセル (310 ~ 340) のそれこれらにおけるフォトダイオード (PD1 ~ PD4) の個数は、転送トランジスタの個数よりも多い。

#### 【0054】

図 9 及び図 10 は、図 8 に示すピクセルアレイをそれぞれ I-I' 方向と II-II' 方向とから見た断面図である。図 9 及び図 10 を参照すると、第 3 ピクセル 330 と第 4 ピ

10

20

30

40

50

クセル340とは、第1素子分離膜301によって互いに分離され、第3ピクセル330及び第4ピクセル340のそれぞれの内部には、第2素子分離膜302が形成される。第2素子分離膜302によって、第3ピクセル330及び第4ピクセル340のそれぞれが複数の単位領域を有し、複数の単位領域に複数のフォトダイオード(PD1～PD4)が形成される。

#### 【0055】

第3ピクセル330及び第4ピクセル340は、マイクロレンズ(331、341)、カラーフィルター(333、343)、及びピクセル回路(335、345)を含む。互いに隣接する第3ピクセル330及び第4ピクセル340のそれぞれにおいて、カラーフィルタ(333、343)は互いに異なる色の光を通過させる。一例として、第3ピクセル330のカラーフィルタ333は、緑色の光を通過させ、第4ピクセル340のカラーフィルタ343は、赤色の光を通過させる。ピクセル回路(335、345)は、上述の駆動トランジスタ、リセットトランジスタ、選択トランジスタ、及び転送トランジスタを含む。

10

#### 【0056】

第3ピクセル330では、第1及び第3フォトダイオード(PD1、PD3)が第1素子連結層CL1によって互いに連結されて第1フォトダイオードグループPG1を提供し、第2及び第4フォトダイオード(PD2、PD4)が第2素子連結層CL2によって互いに連結されて第2フォトダイオードグループPG2を提供する。一方、第4ピクセル340では、1つの素子連結層CLによって第2～第4フォトダイオード(PD2～PD4)が互いに連結されて第2フォトダイオードグループPG2を提供する。

20

#### 【0057】

図9及び図10に示すように、素子連結層(CL1、CL2、CL)は、フォトダイオード(PD1～PD4)とピクセル回路(335、345)との間に配置される。また、素子分離膜(301、302)は、カラーフィルタ(333、343)とピクセル回路(335、345)とにすべて連結されなくてもよい。素子連結層(CL1、CL2、CL)は、素子分離膜(301、302)が形成されない領域に形成される。一例として、フォトダイオード(PD1～PD4)のうちの一部を物理的に連結すると共に、ピクセル回路(335、345)のフローティングディフュージョンに電気的に連結されるように、素子連結層(CL1、CL2、CL)は不純物でドープされる。一実施形態において、素子連結層(CL1、CL2、CL)はN型不純物でドープされる。

30

#### 【0058】

図11は、図8に示すピクセルアレイをIII-I'I'方向から見た断面図である。図11を参照すると、第1ピクセル310及び第3ピクセル330は、第1素子分離膜301によって互いに分離され、第3ピクセル330及び第4ピクセル340のそれぞれの内部には、第2素子分離膜302が形成される。第3方向(Z軸方向)における第1素子分離膜301及び第2素子分離膜302の深さは、フォトダイオード(PD1～PD4)が形成される半導体基板の深さよりも小さい。

30

#### 【0059】

第1ピクセル310は、マイクロレンズ311、カラーフィルタ313を含む。第1ピクセル310では、素子連結層CLによって第1～第3フォトダイオード(PD1～PD3)が連結される。素子連結層CLによって連結される第1～第3フォトダイオード(PD1～PD3)は、第1フォトダイオードグループPG1を提供し、第4フォトダイオードPD4は、単独で第2フォトダイオードグループPG2を提供する。第1ピクセル310のピクセル回路315は、素子連結層CLを介して、第1～第3フォトダイオード(PD1～PD3)で生成された電荷の和に対応する第1ピクセル電圧を一度に獲得する。したがって、ピクセル電圧を獲得するリードアウト動作の回数を減らすことにより、イメージセンサの動作速度、消費電力、及びノイズ特性を改善することができる。

40

#### 【0060】

図12は、図8に示すピクセルアレイをIV-I'V'方向から見た断面図である。図12

50

を参照すると、第2ピクセル320及び第4ピクセル340は、第1素子分離膜301によって互いに分離され、第2ピクセル320及び第4ピクセル340のそれぞれの内部には、第2素子分離膜302が形成される。第2ピクセル320は、マイクロレンズ321、カラーフィルタ323、及びピクセル回路325を含む。素子連結層(CL1、CL2、CL)は、第3方向(Z軸方向)において素子分離膜(301、302)とピクセル回路(325、345)との間に配置される。

#### 【0061】

第2ピクセル320は、第1素子連結層CL1と第1及び第2フォトダイオード(PD1、PD2)とを有する第1フォトダイオードグループPG1、及び第2素子連結層CL2と第3及び第4フォトダイオード(PD3、PD4)とを有する第2フォトダイオードグループPG2を含む。一方、第4ピクセル340では、1つの素子連結層CLによって第2～第4フォトダイオード(PD2～PD4)が互いに物理的に連結されて第2フォトダイオードグループPG2を提供する。10

#### 【0062】

イメージセンサは、各ピクセル(310～340)のそれぞれのフォトダイオードグループ(PG1、PG2)から獲得したピクセル信号の位相差を用いて自動焦点機能を提供する。一方、図8～図12を参照して説明した実施形態では、互いに隣接するピクセル(310～340)のうちの少なくとも一部において、フォトダイオードグループ(PG1、PG2)が互いに異なる形状または面積を有する。したがって、互いに隣接するピクセル(310～340)のうちの少なくとも一部が互いに異なる方向に焦点を合わせるのに必要な情報を提供するため、様々な方向への自動焦点機能を提供してイメージセンサの性能を向上させる。また、各ピクセル(310～340)のそれに含まれるフォトダイオード(PD1～PD4)のうちの少なくとも一部をフォトダイオードグループ(PG1、PG2)にまとめることにより、リードアウト動作に必要な消費電力、時間、及びリードアウト動作で発生するノイズを低減することができる。20

#### 【0063】

図13及び図14は、本発明の一実施形態によるイメージセンサのピクセル構造の他の例を説明するために提供される図である。

#### 【0064】

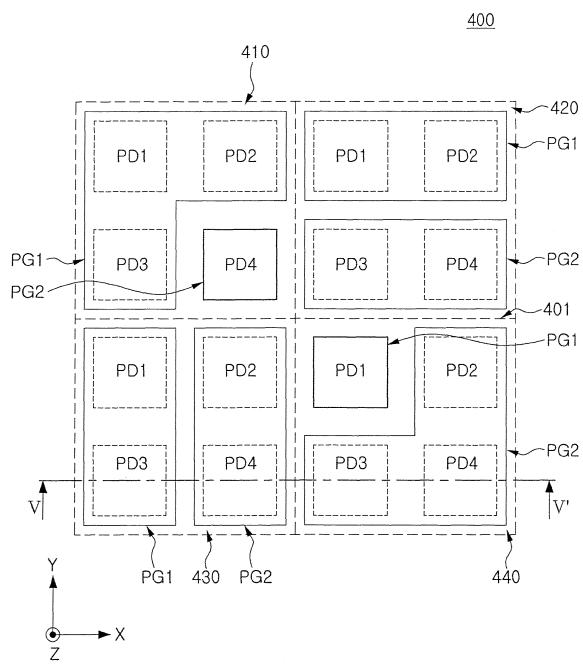

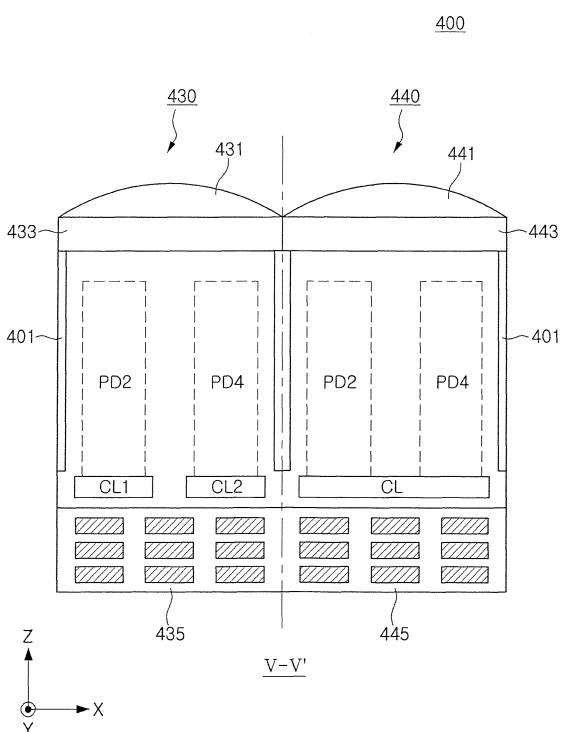

図13は、本発明の一実施形態によるイメージセンサのピクセルアレイの他の例の一部領域を示す平面図であり、図14は、図13に示すピクセルアレイをV-V'方向から見た断面図である。30

#### 【0065】

図13及び図14を参照すると、複数のピクセル(410～440)は、素子分離膜401によって互いに分離され、複数のピクセル(410～440)はそれぞれ、第1～第4フォトダイオード(PD1～PD4)を含む。複数のピクセル(410～440)のそれれにおいて、第1～第4フォトダイオード(PD1～PD4)のうちの少なくとも一部は互いに連結されて第1フォトダイオードグループPG1または第2フォトダイオードグループPG2を提供する。第1～第4フォトダイオード(PD1～PD4)のうちの少なくとも一部を互いに連結する素子連結層(CL1、CL2、CL)によって、フォトダイオードグループ(PG1、PG2)が定義される。第3ピクセル430は、マイクロレンズ431、カラーフィルタ433、及びピクセル回路435を含み、第4ピクセル440は、マイクロレンズ441、カラーフィルタ443、及びピクセル回路445を含む。40

#### 【0066】

図13及び図14に示す実施形態では、複数のピクセル(410～440)の間の境界のみに素子分離膜401が形成され、複数のピクセル(410～440)のそれぞれの内部には素子分離膜401が形成されない。また、図14を参照すると、素子連結層(CL1、CL2、CL)は、ピクセル回路(435、445)とカラーフィルター(433、443)との間に配置されて、第1～第4フォトダイオード(PD1～PD4)のうちの少なくとも一部を互いに物理的に連結する。50

**【 0 0 6 7 】**

素子連結層（CL1、CL2、CL）は、N型不純物でドープされ、互いに隣接する複数のピクセル（410～440）に含まれる素子連結層（CL1、CL2、CL）は、互いに異なる形状または面積を有する。一例として、第4ピクセル440に形成された素子連結層CLは、第3ピクセル430に形成された第1及び第2素子連結層（CL1、CL2）よりも大きい面積を有する。

**【 0 0 6 8 】**

複数のピクセル（410～440）に含まれるフォトダイオードグループ（PG1、PG2）の受光面積は、素子連結層（CL1、CL2、CL）によって決定される。一例として、第3ピクセル430のフォトダイオードグループ（PG1、PG2）は、第4ピクセル440のフォトダイオードグループ（PG1、PG2）とは互いに異なる受光面積を有する。一方、第3ピクセル430のフォトダイオードグループ（PG1、PG2）は、第2ピクセル420のフォトダイオードグループ（PG1、PG2）と実質的に互いに同一の受光面積を有する。10

**【 0 0 6 9 】**

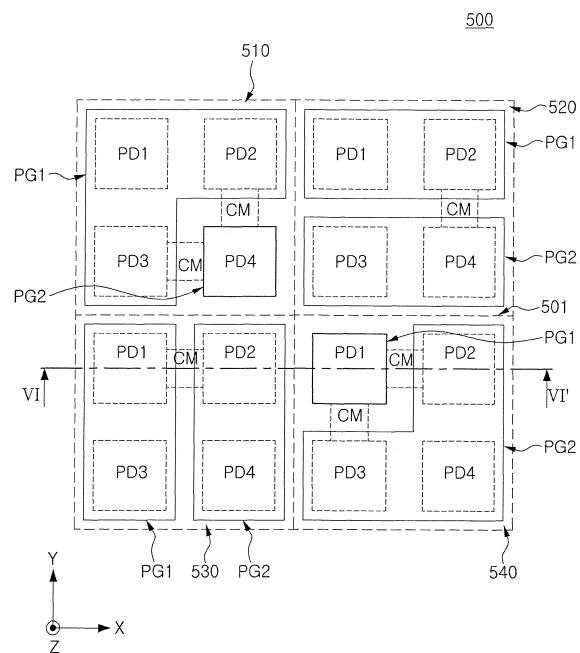

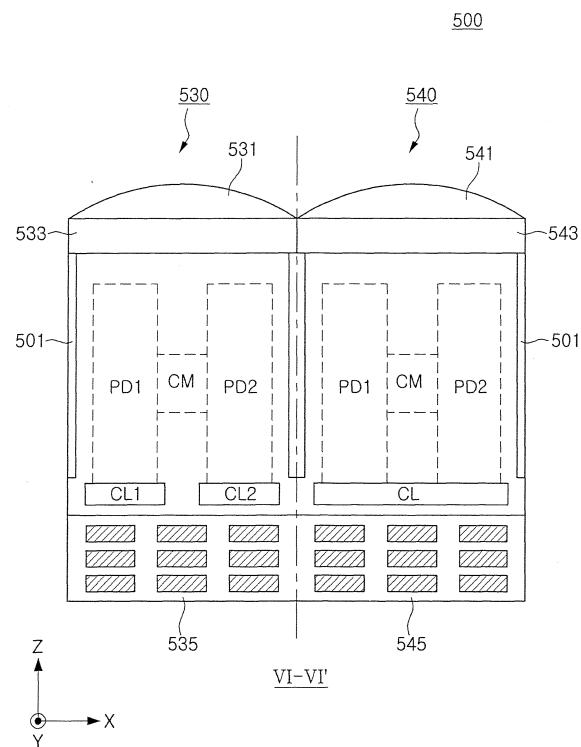

図15及び図16は、本発明の一実施形態によるイメージセンサのピクセル構造のさらに他の例を説明するために提供される図である。

**【 0 0 7 0 】**

図15は、本発明の一実施形態によるイメージセンサのピクセルアレイのさらに他の例の一部領域を示す平面図であり、図16は、図15に示すピクセルアレイをV1-V1'方向から見た断面図である。20

**【 0 0 7 1 】**

ピクセルアレイ500は、素子分離膜501によって分離された複数のピクセル（510～540）を含み、複数のピクセル（510～540）のそれぞれに複数のフォトダイオード（PD1～PD4）が第1方向（X軸方向）及び第2方向（Y軸方向）に沿って配置される。複数のピクセル（510～540）のそれぞれにおいて複数のフォトダイオード（PD1～PD4）のうちの少なくとも一部は、素子連結層（CL1、CL2、CL）によって互いに連結されてフォトダイオードグループ（PG1、PG2）を提供する。図16を参照すると、第3ピクセル530は、マイクロレンズ531、カラーフィルタ533、及びピクセル回路535を含み、第4ピクセル540は、マイクロレンズ541、カラーフィルター543、及びピクセル回路545を含む。素子連結層（CL1、CL2、CL）は、ピクセル回路（535、545）とカラーフィルター（533、543）との間に配置される。カラーフィルタ（533、543）の上部には、マイクロレンズ（531、541）が形成される。30

**【 0 0 7 2 】**

図15及び図16に示す実施形態では、フォトダイオード（PD1～PD4）を互いに連結する電荷移動層CMが形成される。一例として、第3ピクセル530において、第1フォトダイオードPD1に光が過剰に流入して飽和する場合、第1フォトダイオードPD1で生成された電荷の一部が電荷移動層CMを介して第2フォトダイオードPD2に移動する。したがって、電荷移動層CMによって、フォトダイオード（PD1～PD4）の飽和が防止される。電荷移動層CMは、互いに異なるフォトダイオードグループ（PG1、PG2）の間に連結されるか、または、実施形態によっては、同一のフォトダイオードグループ（PG1、PG2）に属するフォトダイオード（PD1～PD4）の間にも連結される。図16に示すように、電荷移動層は、第3方向（Z軸方向）において素子連結層（CL1、CL2、CL）とカラーフィルター（533、543）との間に位置する。40

**【 0 0 7 3 】**

図17は、本発明のさらに他の実施形態によるイメージセンサを示す図である。

**【 0 0 7 4 】**

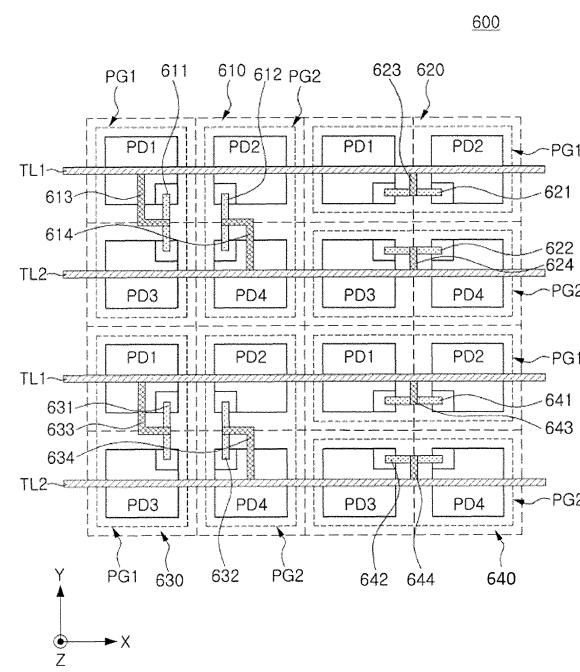

図17は、本発明のさらに他の実施形態によるイメージセンサのピクセルアレイの一部領域を示す平面図である。図17を参照すると、ピクセルアレイ600は、第1方向（X

軸方向)及び第2方向(Y軸方向)に沿って配列された複数のピクセル(610~640)を含み、複数のピクセル(610~640)はそれぞれ、複数のフォトダイオード(PD1~PD4)を含む。複数のピクセル(610~640)のそれぞれに含まれる複数のフォトダイオード(PD1~PD4)の個数は多様に変更される。

#### 【0075】

図17に示す実施形態において、複数のピクセル(610~640)はそれぞれ、複数のフォトダイオード(PD1~PD4)に連結された転送トランジスタを含む。複数のピクセル(610~640)のそれぞれにおいて、フォトダイオード(PD1~PD4)の個数及び転送トランジスタの個数は互いに同一である。また、複数のピクセル(610~640)のそれぞれにおいて、転送トランジスタの少なくとも一部のゲート電極層が、連結ライン(611、612、621、622、631、632、641、642)によって互いに連結される。10

#### 【0076】

一例として、第1ピクセル610を参照すると、第1フォトダイオードPD1及び第3フォトダイオードPD3に連結された転送トランジスタのゲート電極層は、第1連結ライン611によって互いに連結される。第1連結ライン611は、中間ライン613を介して第1転送制御ラインTL1に連結される。一方、第1ピクセル610において第2フォトダイオードPD2及び第4フォトダイオードPD4に連結された転送トランジスタのゲート電極層は、第2連結ライン612によって互いに連結される。第2連結ライン612は、中間ライン614を介して第2転送制御ラインTL2に連結される。20

#### 【0077】

したがって、第1転送制御ラインTL1を介して伝達される転送制御信号によって、第1フォトダイオードPD1及び第3フォトダイオードPD3で生成された電荷が共にフローティングディフュージョンに移動する。また、第2転送制御ラインTL2を介して伝達される転送制御信号によって、第2フォトダイオードPD2及び第4フォトダイオードPD4で生成された電荷が共にフローティングディフュージョンに移動する。すなわち、第1及び第3フォトダイオード(PD1、PD3)が第1フォトダイオードグループPG1として動作し、第2及び第4フォトダイオード(PD2、PD4)が第2フォトダイオードグループPG2として動作する。

#### 【0078】

次に、第2ピクセル620を参照すると、第1フォトダイオードPD1及び第2フォトダイオードPD2に連結された転送トランジスタのゲート電極層は、第1連結ライン621によって互いに連結される。第1連結ライン621は、中間ライン623を介して第1転送制御ラインTL1に連結される。第2ピクセル620において第3フォトダイオードPD3及び第4フォトダイオードPD4に連結された転送トランジスタのゲート電極層は、第2連結ライン622によって互いに連結される。第2連結ライン622は、中間ライン624を介して第2転送制御ラインTL2に連結される。30

#### 【0079】

本実施形態において、連結ライン(611、612、621、622、631、632、641、642)のうちの少なくとも一部は、複数の転送トランジスタのゲート電極層の少なくとも一部を互いに連結することにより、第1~第4フォトダイオード(PD1~PD4)を第1フォトダイオードグループPG1と第2フォトダイオードグループPG2とに分離する。40

#### 【0080】

第1転送制御ラインTL1を介して伝達される転送制御信号によって、第2ピクセル620の第1フォトダイオードPD1及び第2フォトダイオードPD2で生成された電荷が共にフローティングディフュージョンに移動する。また、第2転送制御ラインTL2を介して伝達される転送制御信号によって、第2ピクセル620の第3フォトダイオードPD3及び第4フォトダイオードPD4で生成された電荷が共にフローティングディフュージョンに移動する。すなわち、第1及び第2フォトダイオード(PD1、PD2)が第1フ50

オトダイオードグループ PG1 として動作し、第3及び第4フォトダイオード(PD3、PD4)が第2フォトダイオードグループ PG2 として動作する。

#### 【0081】

第3ピクセル630は、第1ピクセル610と類似の構造を有し、第4ピクセル640は、第2ピクセル620と類似の構造を有する。しかし、これとは異なって、第3ピクセル630が第2ピクセル620と類似の構造を有し、第4ピクセル640が第1ピクセル610と類似の構造を有してもよい。

#### 【0082】

第1ピクセル610及び第2ピクセル620を参照すると、第1転送制御ラインTL1は第1フォトダイオードグループPG1に連結され、第2転送制御ラインTL2は第2フォトダイオードグループPG2に連結される。したがって、第1転送制御ラインTL1を介して、第1ピクセル610及び第2ピクセル620の第1フォトダイオードグループPG1が同時に活性化され、第2転送制御ラインTL2を介して、第1ピクセル610及び第2ピクセル620の第2フォトダイオードグループPG2が同時に活性化される。

10

#### 【0083】

第3ピクセル630において、第1連結ライン631は、中間ライン633を介して第1転送制御ラインTL1に連結され、第2連結ライン632は、中間ライン634を介して第2転送制御ラインTL2に連結される。第4ピクセル640において、第1連結ライン641は、中間ライン643を介して第1転送制御ラインTL1に連結され、第2連結ライン642は、中間ライン644を介して第2転送制御ラインTL2に連結される。

20

#### 【0084】

以下、図18及び図19を参照して、本発明のさらに他の実施形態によるイメージセンサの動作を詳細に説明する。

#### 【0085】

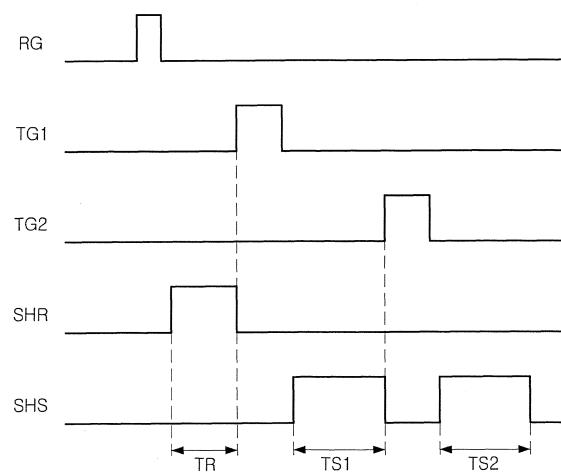

図18は、本発明のさらに他の実施形態によるイメージセンサのピクセル回路を示す回路図であり、図19は、本発明のさらに他の実施形態によるイメージセンサの動作を説明するためのタイミング図である。

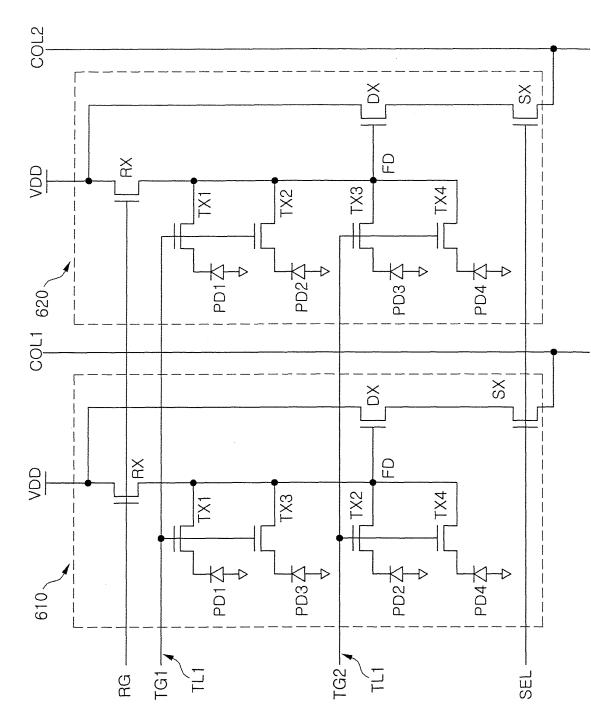

#### 【0086】

図18は、図17に示すピクセルアレイ600のうちの第1ピクセル610及び第2ピクセル620のピクセル回路を示す回路図である。図18を参照すると、第1ピクセル610及び第2ピクセル620はそれぞれ、第1～第4フォトダイオード(PD1～PD4)、第1～第4転送トランジスタ(TX1～TX4)、リセットトランジスタRX、駆動トランジスタDX、及び選択トランジスタSXを含む。第1ピクセル610の選択トランジスタSXは第1カラムラインCOL1に連結され、第2ピクセル620の選択トランジスタSXは第2カラムラインCOL2に連結される。

30

#### 【0087】

第1ピクセル610及び第2ピクセル620のリセットトランジスタRXは、リセット制御信号RGによって制御され、第1ピクセル610及び第2ピクセル620の選択トランジスタSXは、選択制御信号SELによって制御される。一方、第1ピクセル610の第1及び第3転送トランジスタ(TX1、TX3)と第2ピクセル620の第1及び第2転送トランジスタ(TX1、TX2)とは、第1転送制御ラインTL1を介して伝達される第1転送制御信号TG1によって制御される。また、第1ピクセル610の第2及び第4転送トランジスタ(TX2、TX4)と第2ピクセル620の第3及び第4転送トランジスタ(TX3、TX4)とは、第2転送制御ラインTL2を介して伝達される第2転送制御信号TG2によって制御される。

40

#### 【0088】

図19を参照すると、本発明のさらに他の実施形態によるイメージセンサの動作は、リセット制御信号RGによってリセットトランジスタRXがターンオンされることから始まる。リセットトランジスタRXがターンオンされることにより、第1ピクセル610及び第2ピクセル620のフローティングディフュージョンFDが電源電圧VDDによってリ

50

セットされる。図19を参照すると、リセットトランジスタR<sub>X</sub>がターンオフされた後、リセット電圧サンプリング信号S<sub>H</sub>Rがハイロジック値を有するリセットサンプリング時間T<sub>R</sub>の間に、リードアウト回路が第1ピクセル610及び第2ピクセル620のそれぞれのリセット電圧をサンプリングする。

#### 【0089】

リセットサンプリング時間T<sub>R</sub>が経過すると、第1転送制御信号T<sub>G</sub>1によって、第1ピクセル610の第1及び第3転送トランジスタ(T<sub>X</sub>1、T<sub>X</sub>3)と第2ピクセル620の第1及び第2転送トランジスタ(T<sub>X</sub>1、T<sub>X</sub>2)とがターンオンされる。したがって、第1ピクセル610の第1及び第3フォトダイオード(PD1、PD3)の電荷がフローティングディフュージョンFDに共に移動する。また、第2ピクセル620の第1及び第2フォトダイオード(PD1、PD2)の電荷がフローティングディフュージョンFDに共に移動する。

10

#### 【0090】

第1ピクセル610の第1及び第3転送トランジスタ(T<sub>X</sub>1、T<sub>X</sub>3)と第2ピクセル620の第1及び第2転送トランジスタ(T<sub>X</sub>1、T<sub>X</sub>2)とがターンオフされると、リードアウト回路は、ピクセル電圧サンプリング信号S<sub>H</sub>Sに応答して、第1ピクセル610及び第2ピクセル620のそれぞれから第1ピクセル電圧を獲得する。リードアウト回路が第1ピクセル610から獲得する第1ピクセル電圧は、第1ピクセル610の第1及び第3フォトダイオード(PD1、PD3)の電荷に対応する電圧である。また、リードアウト回路が第2ピクセル620から獲得する第1ピクセル電圧は、第2ピクセル620の第1及び第2フォトダイオード(PD1、PD2)の電荷に対応する電圧である。リードアウト回路が獲得した第1ピクセル電圧は、メモリに記憶される。一例として、上記メモリは、イメージセンサと同一の半導体パッケージ内に含まれるメモリである。

20

#### 【0091】

第1サンプリング時間T<sub>S</sub>1が経過すると、第2転送制御信号T<sub>G</sub>2によって、第1ピクセル610の第2及び第4転送トランジスタ(T<sub>X</sub>2、T<sub>X</sub>4)と第2ピクセル620の第3及び第4転送トランジスタ(T<sub>X</sub>3、T<sub>X</sub>4)とがターンオンされる。したがって、第1ピクセル610の第2及び第4フォトダイオード(PD2、PD4)の電荷がフローティングディフュージョンFDに共に移動する。また、第2ピクセル620の第3及び第4フォトダイオード(PD3、PD4)の電荷がフローティングディフュージョンFDに共に移動する。

30

#### 【0092】

第1転送制御信号T<sub>G</sub>1及び第2転送制御信号T<sub>G</sub>2のそれぞれがハイロジック値を有する区間の間に、リセット制御信号R<sub>G</sub>によってフローティングディフュージョンFDがリセットされる区間は存在しない。したがって、第2転送制御信号T<sub>G</sub>2がハイロジック値を有する間、第1ピクセル610及び第2ピクセル620のフローティングディフュージョンFDのそれぞれには、第1～第4フォトダイオード(PD1～PD4)から生成された電荷が蓄積される。

#### 【0093】

第2転送制御信号T<sub>G</sub>2によって、第1ピクセル610の第2及び第4転送トランジスタ(T<sub>X</sub>2、T<sub>X</sub>4)と第2ピクセル620の第3及び第4転送トランジスタ(T<sub>X</sub>3、T<sub>X</sub>4)とがターンオフされると、リードアウト回路は、第2サンプリング時間T<sub>S</sub>2の間にピクセル電圧を検出する。リードアウト回路が第1ピクセル610から検出するピクセル電圧は、第1ピクセル610における第1～第4フォトダイオード(PD1～PD4)の電荷の総和に対応する電圧である。同様に、リードアウト回路が第2ピクセル620から検出するピクセル電圧は、第2ピクセル620における第1～第4フォトダイオード(PD1～PD4)の電荷の総和に対応する電圧である。

40

#### 【0094】

リードアウト回路を含むコントロールロジックは、第1ピクセル610及び第2ピクセル620のそれぞれから検出したピクセル電圧を用いてイメージデータを生成する。また

50

、コントロールロジックは、第1ピクセル610及び第2ピクセル620のそれから検出したピクセル電圧と第1ピクセル電圧との差を計算し、第2ピクセル電圧を獲得する。第1ピクセル610の場合、第2ピクセル電圧は第2及び第4フォトダイオード(PD2、PD4)で生成された電荷に対応する電圧である。第2ピクセル620の場合、第2ピクセル電圧は第3及び第4フォトダイオード(PD3、PD4)で生成された電荷に対応する電圧である。

#### 【0095】

コントロールロジックは、上述の方法で獲得した第1ピクセル電圧及び第2ピクセル電圧を用いて、複数のピクセル(610～640)のそれぞれにおける第1ピクセル信号及び第2ピクセル信号を計算する。一例として、第1ピクセル信号は、複数のピクセル(610～640)のそれぞれの第1フォトダイオードグループPG1で生成された電荷に対応する信号であり、第2ピクセル信号は、第2フォトダイオードグループPG2で生成された電荷に対応する信号である。10

#### 【0096】

コントロールロジックは、第1ピクセル信号と第2ピクセル信号との位相差を計算し、イメージセンサの焦点調節に必要な情報を生成する。図17に示すように、ピクセル(610～640)のうちの少なくとも一部において、第1フォトダイオードグループPG1と第2フォトダイオードグループPG2とは、互いに異なる方式で定義されるため、コントロールロジックは、様々な方向に焦点を調節するために必要な情報を生成する。同時に、複数のピクセル(610～640)のそれぞれに含まれるフォトダイオード(PD1～PD4)の個数よりも少ない回数のリードアウト動作のみで、焦点調節に必要な情報、及びイメージデータを獲得する。したがって、リードアウト動作に必要な時間と消費電力を減らし、リードアウト動作で発生するノイズの影響を低減させて、イメージセンサの性能を改善することができる。20

#### 【0097】

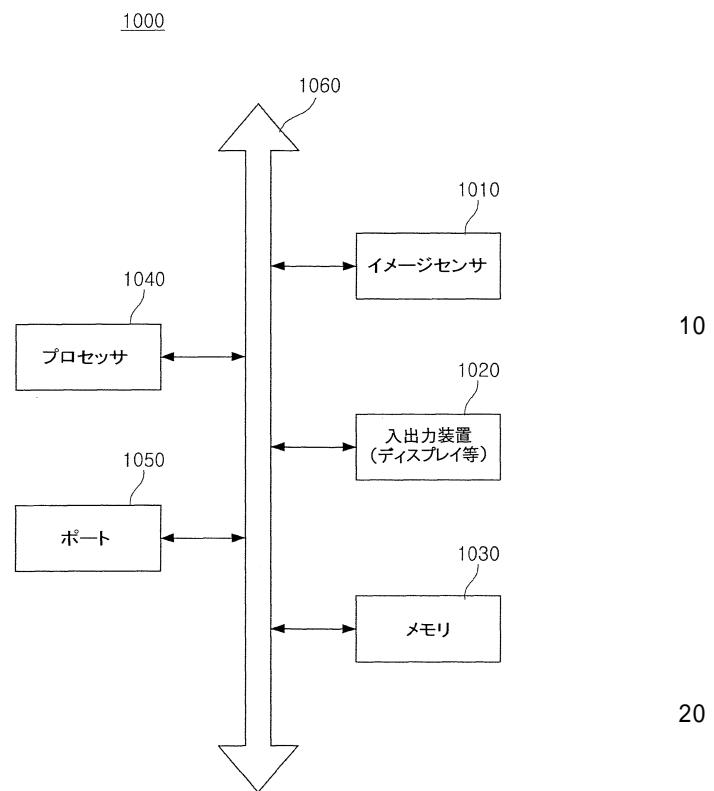

図20は、本発明の一実施形態によるイメージセンサを含む電子機器の概要を示すプロック図である。

#### 【0098】

図20に示す実施形態によるコンピュータ装置1000は、イメージセンサ1010、ディスプレイなどを含む入出力装置1020、メモリ1030、プロセッサ1040、及びポート1050を備える。その他にも、コンピュータ装置1000は、有線／無線通信装置、電源装置などをさらに含む。図20に示す構成要素のうちのポート1050は、コンピュータ装置1000がビデオカード、サウンドカード、メモリカード、USB装置などと通信するために提供される装置である。コンピュータ装置1000は、通常のデスクトップコンピュータやラップトップコンピュータの他に、スマートフォン、タブレットPC、スマートウェアラブル機器などをすべて包括する概念である。30

#### 【0099】

プロセッサ1040は、特定の演算や命令及びタスクなどを行う。プロセッサ1040は、中央処理装置(CPU)またはマイクロプロセッサユニット(MCU)、システム・オン・チップ(SoC)などであり、バス1060を介してイメージセンサ1010、入出力装置1020、メモリ1030はもちろん、ポート1050に連結された他の装置と通信する。40

#### 【0100】

メモリ1030は、コンピュータ装置1000の動作に必要なデータ、またはマルチメディアデータなどを記憶する記憶媒体である。メモリ1030は、ランダムアクセスメモリ(RAM)のような揮発性メモリ、またはフラッシュメモリなどのような不揮発性メモリを含む。また、メモリ1030は、記憶装置としてソリッドステートドライブ(SSD)、ハードディスクドライブ(HDD)、及び光学ドライブ(ODD)のうちの少なくとも1つを含む。入出力装置1020は、ユーザーに提供されるキーボード、マウス、タッチスクリーンなどの入力装置、及びディスプレイ、オーディオ出力部などのよう50

出力装置を含む。

【0101】

イメージセンサ1010は、パッケージ基板に実装され、バス1060または他の通信手段によってプロセッサ1040に連結される。イメージセンサ1010は、図1～図19を参照して説明した様々な実施形態による形態でコンピュータ装置1000に採用される。

【0102】

以上、本発明の実施形態について詳細に説明したが、本発明の技術範囲はこれに限定されず、本発明の技術的思想から逸脱しない範囲内で多様な修正及び変形が可能であることは、当技術分野の通常の知識を有する者には明らかである。

10

【符号の説明】

【0103】

- |                                 |                |    |

|---------------------------------|----------------|----|

| 1                               | イメージ処理装置       |    |

| 2、3、10、100、1010                 | イメージセンサ        |    |

| 11、110、200、300、400、500、600      | ピクセルアレイ        |    |

| 12、120                          | ロードライバ         |    |

| 13                              | カラムドライバ        |    |

| 14                              | タイミングコントローラ    |    |

| 15、130                          | リードアウト回路       |    |

| 20                              | イメージプロセッサ      | 20 |

| 30                              | 客体             |    |

| 40、70                           | 第1層            |    |

| 50、80                           | 第2層            |    |

| 60                              | 第3層            |    |

| 131                             | サンプリング回路       |    |

| 132                             | アナログ-デジタルコンバータ |    |

| 210、310、410、510、610             | 第1ピクセル         |    |

| 220、320、420、520、620             | 第2ピクセル         |    |

| 230、330、430、530、630             | 第3ピクセル         |    |

| 240、340、440、540、640             | 第4ピクセル         | 30 |

| 301                             | 第1素子分離膜        |    |

| 302                             | 第2素子分離膜        |    |

| 311、321、331、341、431、441、531、541 | マイクロレンズ        |    |

| 313、323、333、343、433、443、533、543 | カラーフィルター       |    |

| 315、325、335、345、435、445、535、545 | ピクセル回路         |    |

| 401、501                         | 素子分離膜          |    |

| 611、621、631、641                 | 第1連結ライン        |    |

| 612、622、632、642                 | 第2連結ライン        |    |

| 613、614、623、624、633、634、643、644 | 中間ライン          |    |

| 1000                            | コンピュータ装置       | 40 |

| 1020                            | 入出力装置          |    |

| 1030                            | メモリ            |    |

| 1040                            | プロセッサ          |    |

| 1050                            | ポート            |    |

| 1060                            | バス             |    |

| C L 1                           | 第1素子連結層        |    |

| C L 2                           | 第2素子連結層        |    |

| C L                             | 素子連結層          |    |

| C M                             | 電荷移動層          |    |

| P D 1                           | 第1フォトダイオード     | 50 |

- P D 2 第2フォトダイオード

P D 3 第3フォトダイオード

P D 4 第4フォトダイオード

P G 1 第1フォトダイオードグループ

P G 2 第2フォトダイオードグループ

【図面】

【図1】

【図2】

10

20

30

40

50

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【図8】

【 四 9 】

【図10】

【図 1 1】

【図 1 2】

10

20

【図 1 3】

【図 1 4】

30

40

50

【図 1 5】

【図 1 6】

10

20

【図 1 7】

【図 1 8】

30

40

50

【図 19】

【図 20】

---

フロントページの続き

審査官 鈴木 明

(56)参考文献 特開2017-184181 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 04 N 25/00 - 25/79

H 01 L 27/146