(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2008-541333

(P2008-541333A)

(43) 公表日 平成20年11月20日(2008.11.20)

| (51) Int.Cl. | F 1                                                                            | テーマコード (参考) |

|--------------|--------------------------------------------------------------------------------|-------------|

| G 11 C 11/41 | (2006.01) G 11 C 11/34 K 5 B 005                                               |             |

| G 11 C 15/04 | (2006.01) G 11 C 15/04 6 3 1 C 5 B 015                                         |             |

| G 06 F 12/08 | (2006.01) G 11 C 15/04 6 0 1 A<br>G 06 F 12/08 5 1 1 E<br>G 06 F 12/08 5 5 3 B |             |

審査請求 未請求 予備審査請求 未請求 (全 15 頁) 最終頁に続く

|               |                              |          |                                                                                                            |

|---------------|------------------------------|----------|------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2008-512275 (P2008-512275) | (71) 出願人 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 78735 テキサス州<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (86) (22) 出願日 | 平成18年3月29日 (2006.3.29)       | (74) 代理人 | 100116322<br>弁理士 桑垣 衡                                                                                      |

| (85) 翻訳文提出日   | 平成19年10月23日 (2007.10.23)     | (72) 発明者 | ラマラジュ、ラビンドララジ<br>アメリカ合衆国 78681 テキサス州<br>ラウンド ロック エバンス ドライブ<br>7014                                         |

| (86) 國際出願番号   | PCT/US2006/011560            |          |                                                                                                            |

| (87) 國際公開番号   | W02006/127117                |          |                                                                                                            |

| (87) 國際公開日    | 平成18年11月30日 (2006.11.30)     |          |                                                                                                            |

| (31) 優先権主張番号  | 11/132,457                   |          |                                                                                                            |

| (32) 優先日      | 平成17年5月19日 (2005.5.19)       |          |                                                                                                            |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                            |

最終頁に続く

(54) 【発明の名称】記憶回路及びその方法

## (57) 【要約】

記憶回路(180 - 183 及び 280 - 281)は、高速読出しアクセスを可能にしつつ、低電力動作に用い得る。例えば、回路100では、共用相補書き込みビット線(101、102)、個別読み出しビット線(103 - 106)、共用読み出しワード線(107)、及び個別書き込みワード線(108 - 111)が用いられる。回路200では、共用相補書き込みビット線(201、202)、共用読み出しビット線(203)、個別読み出しワード線(206 - 207)、及び個別書き込みワード線(208 - 209)が用いられる。記憶回路は、例えば、レジスタファイル(17)、分岐ユニット(15)、SRAM(19)、他のモジュール(20)、キャッシュ(18)、バッファ(21)、及び/又はメモリ(14)等の様々な文脈で用い得る。

**【特許請求の範囲】****【請求項 1】**

第1端子及び第2端子を有し第1データ値を記憶するための第1記憶セルと、

第1端子及び第2端子を有し第2データ値を記憶するための第2記憶セルと、

前記第1記憶セル及び前記第2記憶セルの各々に接続され、それぞれ前記第1データ値

及び前記第2データ値双方を前記第1記憶セル及び前記第2記憶セルに選択的に提供する

ための共用書き込みビット線と、

前記第1記憶セルに接続され、前記第1記憶セルだけを選択的に読み出すための第1読

出しふィット線と、

前記第2記憶セルに接続され、前記第2記憶セルだけを選択的に読み出すための第2読

出しふィット線と、

が含まれる記憶回路。

**【請求項 2】**

更に、共用読み出し信号に応じて、前記第1記憶セル及び第2記憶セルの各々の読み出しを

選択的に可能にするための共用読み出しワード線が含まれる請求項1に記載の記憶回路。

**【請求項 3】**

前記第1記憶セル及び前記第2記憶セルは、各々、静的ランダムアクセスメモリ(SRAM)

セル、レジスタ、キャッシュ・タグ・アレイ・メモリセル、バッファ、又は分岐ユニットメモリセルの内の1つからなる請求項1に記載の記憶回路。

**【請求項 4】**

更に、前記第1記憶セルの前記第1端子に接続された第1選択ゲートと、

前記第2記憶セルの前記第2端子に接続された第2選択ゲートと、

前記第1選択ゲートに接続された、同第1選択ゲートによる前記第1記憶セルへの書き

込みを可能にする第1書き込みワード線と、

前記第2選択ゲートに接続された、前記第2選択ゲートによる前記第2記憶セルへの書

き込みを可能にする前記第2書き込みワード線と、

が含まれる請求項1に記載の記憶回路。

**【請求項 5】**

更に、前記第1記憶セルの前記第2端子に接続された、前記第1書き込みワード線によ

って制御される第3選択ゲートと、

前記第2記憶セルの前記第1端子に接続された、前記第2書き込みワード線によって制

御される第4選択ゲートと、

が含まれる請求項4に記載の記憶回路。

**【請求項 6】**

前記第1記憶セルは、連想メモリの第1経路に割り当てられ、前記第2記憶セルは、前記

連想メモリの第2経路に割り当てられる請求項1に記載の記憶回路。

**【請求項 7】**

データ記憶回路においてデータを処理するための方法であって、

第1端子及び第2端子を有する第1記憶セルに第1データ値を記憶する段階と、

第1端子及び第2端子を有する第2記憶セルに第2データ値を記憶する段階と、

それぞれ前記第1データ値及び前記第2データ値双方を前記第1記憶セル及び前記第

2記憶セルに選択的に提供するための共用書き込みビット線を前記第1記憶セル及び前記第

2記憶セルの各々に接続する段階と、

前記第1記憶セルに接続された第1読み出しふィット線を介して前記第1記憶セルだけを選

択的に読み出す段階と、

前記第2記憶セルに接続された第2読み出しふィット線を介して前記第2記憶セルだけを選

択的に読み出す段階と、

が含まれる方法。

**【請求項 8】**

更に、共用読み出しワード線を介して、共通読み出し信号に応じて、前記第1記憶セル及び

10

20

30

40

50

前記第2記憶セルの各々の読み出しを選択的に可能にする段階が含まれる請求項7に記載の方法。

**【請求項9】**

更に、静的ランダムアクセスメモリ(SRAM)セル、レジスタ、キャッシュ・タグ・アレイ・メモリセル、バッファ、又は分岐ユニットメモリセルの内の1つとして前記第1記憶セル及び前記第2記憶セルを実装する段階が含まれる請求項7に記載の方法。

**【請求項10】**

更に、第1書き込みワード線を介して前記第1記憶セルの前記第1端子に接続された第1選択ゲートをイネーブル状態にする段階と、

前記第1記憶セルを書き込む段階と、

第2書き込みワード線を介して前記第2記憶セルの前記第2端子に接続された第2選択ゲートをイネーブル状態にする段階と、

前記第2記憶セルを書き込む段階と、

が含まれる請求項7に記載の方法。

**【請求項11】**

更に、前記第1記憶セルの前記第2端子に接続された第3選択ゲートを提供する段階であって、前記第3選択ゲートは、前記第1書き込みワード線によって制御される前記段階と、

前記第2記憶セルの前記第1端子に接続された第4選択ゲートを提供する段階であって、前記第4選択ゲートは、前記第2書き込みワード線によって制御される前記段階と、

が含まれる請求項10に記載の方法。

**【請求項12】**

更に、連想メモリの第1経路に前記第1記憶セルを割り当てる段階と、

前記連想メモリの第2経路に前記第2記憶セルを割り当てる段階と、

が含まれる請求項10に記載の方法。

**【請求項13】**

記憶回路であって、

第1端子及び第2端子を有し第1データ値を記憶するための第1記憶セルと、

第1端子及び第2端子を有し第2データ値を記憶するための第2記憶セルと、

前記第1記憶セルに接続され、前記第1記憶セルだけに選択的に書き込むための第1書き込みワード線と、

前記第2記憶セルに接続され、前記第2記憶セルだけに選択的に書き込むための第2書き込みワード線と、

前記第1記憶セルに接続された第1選択ゲート及び前記第2記憶セルに接続された第2選択ゲートと、

前記第1選択ゲート及び前記第2選択ゲートの各々に接続され、それぞれ前記第1データ値及び前記第2データ値双方を前記第1記憶セル及び前記第2記憶セルから提供する制御信号を選択的に提供するための共用読出しづード線と、

が含まれる記憶回路。

**【請求項14】**

更に、前記第1記憶セル及び前記第2記憶セルの各々に接続され、それぞれ前記第1データ値及び前記第2データ値双方を前記第1記憶セル及び前記第2記憶セルに選択的に提供するための共用書き込みビット線が含まれる請求項13に記載の記憶回路。

**【請求項15】**

記憶回路であって、

第1端子及び第2端子を有し第1データ値を記憶するための第1記憶セルと、

第1端子及び第2端子を有し第2データ値を記憶するための第2記憶セルと、

前記第1記憶セル及び前記第2記憶セルの各々に接続され、それぞれ前記第1データ値及び前記第2データ値双方を前記第1記憶セル及び前記第2記憶セルに選択的に提供するための共用書き込みビット線と、

10

20

30

40

50

前記第1記憶セルの読み出しを選択的に可能にするための第1読み出し選択ゲート及び前記第2記憶セルの読み出しを選択的に可能にするための第2読み出し選択ゲートと、

前記第1読み出し選択ゲート及び前記第2読み出し選択ゲートの各々に接続され、前記第1記憶セル及び前記第2記憶セルの各々を選択的に読み出すための共用読み出しひット線と、が含まれる記憶回路。

#### 【請求項16】

前記共用書き込みヒット線及び前記共用読み出しひット線の内の少なくとも1つには、更に、前記第1記憶セル及び前記第2記憶の前記第1端子又は前記第2端子の1つに選択的に影響を及ぼす又はそれによって影響が及ぼされる相補ヒット線が含まれる請求項15に記載の記憶回路。

10

#### 【請求項17】

更に、前記第1記憶セル及び前記第2記憶セルを選択的に別々に書き込むための前記第1記憶セルに接続された第1書き込みワード線及び前記第2記憶セルに接続された第2書き込みワード線と、

前記第1記憶セル及び前記第2記憶セルを選択的に別々に読み出すための前記第1記憶セルに接続された第1読み出しワード線及び前記第2記憶セルに接続された第2読み出しワード線と、

が含まれる請求項15に記載の記憶回路。

#### 【請求項18】

データ記憶回路においてデータを処理するための方法であって、

20

第1端子及び第2端子を有し第1データ値を記憶するための第1記憶セルを提供する段階と、

第1端子及び第2端子を有し第2データ値を記憶するための第2記憶セルを提供する段階と、

それぞれ前記第1データ値及び前記第2データ値双方を前記第1記憶セル及び前記第2記憶セルに選択的に提供するための共用書き込みヒット線を前記第1記憶セル及び前記第2記憶セル各々の前記第1端子に接続する段階と、

前記第1記憶セル及び前記第2記憶セル各々を選択的に読み出すための共用読み出しひット線を前記第1記憶セル及び前記第2記憶セル各々に接続する段階と、が含まれる方法。

#### 【請求項19】

更に、前記第1記憶セル及び前記第2記憶セルの動作を強化する、前記共用書き込みヒット線又は前記共用読み出しひット線の内の少なくとも1つの補完である相補ヒット線を提供する段階が含まれる請求項18に記載の方法。

30

#### 【請求項20】

更に、前記第1記憶セル及び前記第2記憶セルを選択的に別々に書き込むために、第1書き込みワード線を前記第1記憶セルに接続し、第2書き込みワード線を前記第2記憶セルに接続する段階と、

前記第1記憶セル及び前記第2記憶セルを選択的に別々に読み出すために、第1読み出しワード線を前記第1記憶セルに接続し、第2読み出しワード線を前記第2記憶セルに接続する段階と、が含まれる請求項18に記載の方法。

40

#### 【請求項21】

請求項18に記載の方法であって、更に、

データ処理システムにおいて、第1文脈又は第1スレッドに前記第1記憶セルを割り当てる段階と、

前記データ処理システムにおいて、第2文脈又は第2スレッドに前記第2記憶セルを割り当てる段階と、が含まれる方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、一般的に、集積回路に関し、特に、集積回路における記憶回路に関する。

50

**【背景技術】****【0002】**

低消費電力化は、例えば、携帯用途や手持ち式用途が普及したために、データ処理システムにおいて重要な要素になっている。今日、多くのデータ処理システムが、メモリ（メインメモリ又は他の内部又は外部メモリ等）へのアクセス数を低減するために、小型化され、高速化され、効率化されたメモリであって集積回路に配置されたキャッシュとも称されるメモリを用いている。キャッシュへのアクセスでは、一般的に、他の内部又は外部メモリへのアクセスと比較して、消費電力が少なく、待ち時間が低減される。従って、電力を低減し、性能を向上させるために、高速化され効率化されたキャッシュに後で再度必要な項目を記憶することは、望ましいことである。

10

**【発明の開示】****【発明が解決しようとする課題】****【0003】**

更に、消費電力を低減するために、また、できるだけ高速でキャッシュを動作させるために、キャッシュの文脈で用い得る改善された記憶回路に対するニーズや、他の選択肢として、記憶回路を利用する様々な他の用途に対する適用可能性を有し得る改善された記憶回路に対するニーズが存在する。消費電力が小さく読み出しアクセスが速い記憶回路に対する1つのそのような用途は、文脈又はスレッドスイッチングである。他の数多くの用途が、消費電力が小さく読み出しアクセスが速い記憶回路を利用し得る。

20

**【課題を解決するための手段】****【0004】**

本発明は、添付の図によって、例として示すものであって、これらによって限定されるものではない。図では、同様な参照符号は、同様な要素を示す。

当業者は、図の要素が、簡単明瞭に示されており、必ずしも縮尺通りに描かれていないことを認識されたい。例えば、図の要素には、本発明の実施形態の理解を改善する一助とするために、他の要素と比較して寸法を誇張したものがある。

**【0005】**

本明細書に用いる用語「バス」は、データ、アドレス、制御、又は状態等の、1つ又は複数の様々な種類の情報を伝達するのに用い得る複数の信号又は導体を意味するために用いられる。本明細書において述べる導体は、単一の導体、複数の導体、单方向の導体、又は双方向の導体であることに関連して例示又は記述し得る。しかしながら、異なる実施形態では、導体の実装も異なり得る。例えば、双方向の導体よりもむしろ別個の单方向導体を用いたり、その逆の場合もあったりする。また、複数の導体は、直列に又は時分割多重方式で多数の信号を伝達する単一の導体で置き換え得る。同様に、多数の信号を搬送する単一の導体は、これらの信号の一部を搬送する様々な異なる導体に分離し得る。従って、信号を伝達するための多くの選択肢が存在する。

30

**【発明を実施するための最良の形態】****【0006】**

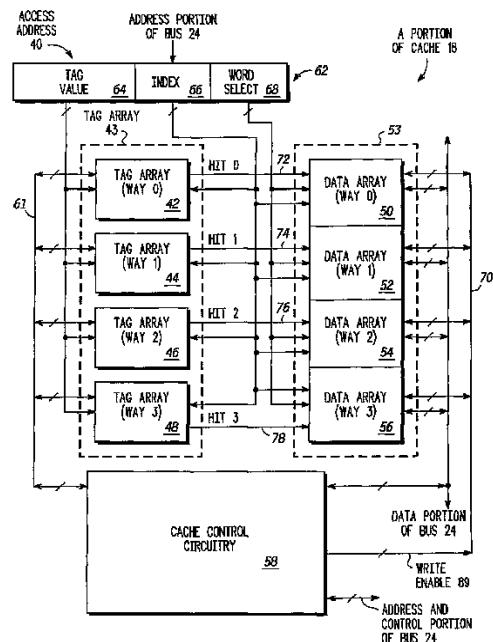

図1にデータ処理システム10の一実施形態を示す。データ処理システム10には、集積回路12及び外部メモリ14が含まれる。集積回路12には、プロセッサ16、キャッシュメモリ18、静的ランダムアクセスメモリ(SRAM)19、バスインターフェイス22、及び他のモジュール20が含まれる。集積回路12には、更に、バス24及びバス26が含まれる。バス24は、プロセッサ16、キャッシュ18、SRAM19、バスインターフェイス22、及び他のモジュール20を接続する。バス26は、外部メモリ14にバスインターフェイス22を接続する。データ処理システム10の具体的な代表的実施形態を開示したが、そのような処理システムの様々な構成及び他の選択肢としての実施形態が実現できると考えられる。

40

**【0007】**

例えば、キャッシュ18は、集積回路12の一部として示したが、キャッシュ18は、他の選択肢として、集積回路12の外に、例えば、外部メモリ14内に配置してよい。ま

50

た、集積回路 12 は、例えば、多重プロセッサデータ処理システムでのように、任意の数のプロセッサを含んでよく、また、他のモジュール 20 は、例えば、他のマスタ、スレーブ、又はメモリ等、いずれか他の周辺装置を含んでよいことに留意されたい。更に、データ処理システム 10 には、データ処理システム 10 の異なる部位を異なる半導体基板に配置し得るよう、任意の数の集積回路を含んだり又は他の選択肢として、データ処理システム 10 は、同じ基板上に組み立てたりしてよい。更に、外部メモリ 14 は、集積回路 12 と同じ半導体基板上に配置したり又は別の基板上に配置したりしてよい。

#### 【 0 0 0 8 】

一実施形態において、プロセッサ 16 は、レジスタファイル 17 及び分岐ユニット 15 を有する。他の実施形態は、データ処理システム 10 の任意の部位にレジスタファイル 17 を配置し得る。一実施形態において、分岐ユニット 15 を用いて、プロセッサ 16 用の枝路予測を実施し得る。枝路予測を実施するための様々な方法が、当分野では公知である。一実施形態において、バスインターフェイス 22 は、バッファ 21 を有する。他の実施形態は、データ処理システム 10 の任意の部位にバッファ 21 を配置し得る。データ処理システム 10 については、図 2 乃至 5 を参照して後述するように、本発明の実施形態を理解するために必要な範囲でのみ議論する。残りの機能は、当分野で公知の通りであり、従って、当分野で知られている様々な異なる方法で実現し得る。データ処理システム 10 の全ての又は任意の部位は、单一の集積回路上に共に実装し得ることに留意されたい。

#### 【 0 0 0 9 】

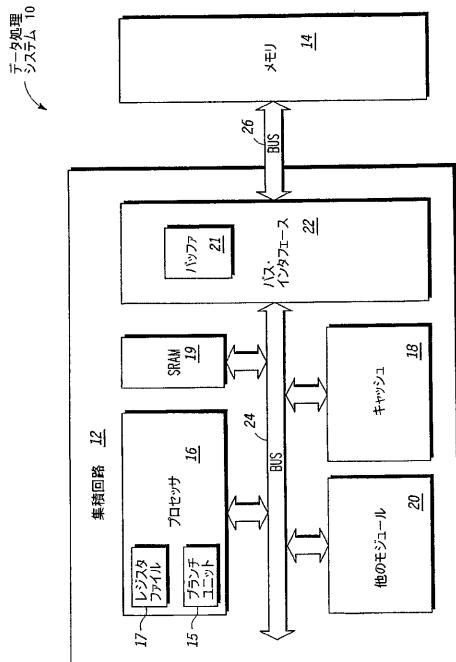

図 2 において、キャッシュ 18 の部位の特定の実施形態を開示する。このキャッシュ 18 の部位には、レジスタ 62、多数の経路 42 - 48 用のタグメモリアレイ、多数の経路 50 - 56 用のデータメモリアレイ、及びキャッシュ制御回路 58 が含まれる。アクセスアドレス 40 は、バス 24 のアドレス部から受け取られ、タグ値部 64、インデックス部 66、及びワード選択部 68 を有する。例えば、読み出しアクセスの場合、アクセスアドレス 40 は、要求された情報（例えば、データ又は命令）のアドレスに対応する。例示した実施形態において、受信されると、アクセスアドレス 40 は、レジスタ 62 内に記憶される。アクセスアドレス 40 のタグ部 64 は、多重経路タグアレイ 43 に提供されるタグ値データを含む。例示した実施形態において、タグアレイ 43 は、経路 0 用のタグアレイ 42、経路 1 用のタグアレイ 44、経路 2 用のタグアレイ 46、及び経路 3 用のタグアレイ 48 を有する。インデックス部 66 からのデータは、多重経路タグアレイ 43 及び多重経路データアレイ 53 双方に提供され、また、タグアレイ (42, 44, 46, 48) 及びデータアレイ (50, 52, 54, 56) にインデックスを提供するために用いられる。例えば、一実施形態において、インデックス部 66 には、各経路のタグ及びデータ部において所定数の組の 1 つを選択するための組標識が含まれる。ワード選択部 68 からのデータは、多重経路データアレイ 50 - 56 に提供され、データアレイ (経路 0) 50 等のデータアレイ内のデータは、インデックス部 66 及びワード選択部 68 双方によって示される。即ち、インデックス部 66 は、データアレイ (経路 0) 50 の 1 つの入力項目を識別し、そして、ワード選択 68 は、その入力項目の一部を識別する。多重経路データアレイは、バス 24 の双方向データ部にも接続され、バス 24 との間でデータを取りする。

#### 【 0 0 1 0 】

タグアレイ (経路 0) 42 等のタグアレイ 43 の各部は、タグ値 64 とインデックス値 66 に対して配置されたタグアレイ (経路 0) 42 内のデータとの間の比較に基づき、データアレイ (経路 0) 50 等の対応するデータアレイにヒット信号を提供する。例えば、動作中、タグ部 64 は、インデックス部 66 を介してタグアレイ (経路 0) 42 から検索された値と比較され、ヒット信号 72 を提供する。比較された値が一致した場合、ヒット信号 72 は、アサートされ、ヒットを示す。データアレイ (経路 0) 50 には、複数のデータブロックが含まれ、インデックス値 66 及びワード選択値 68 双方によってアドレス指定され、また、ヒットに応じて、アドレス指定されたデータ項目は、データアレイ (経路 0) 50 からデータ部バス 24 に出力される。しかしながら、比較された値が一致しな

10

20

30

40

50

い場合、ヒット信号 72 は、アサートされず、キャッシング 18 のその経路における失敗を示す。タグ値 64 とタグアレイ 42 - 48 のいずれかのタグとの間が一致しない場合、ヒット信号 72 - 78 は、いずれもアサートされず、アクセスアドレス 40 がキャッシング 18 において失敗したことを示す。

#### 【0011】

図 2 は、キャッシング 18 の一部の単なる一例を示すことに留意されたい。しかしながら、他の実施形態において、レジスタ 62、タグアレイ 42 - 48、及びデータアレイ 50 - 56 は、当分野で公知なように、様々な異なる方法で実装して、所望の機能を実現し得ることに留意されたい。キャッシング制御回路 58 は、キャッシング 18 を動作させるために用いられる制御信号を提供し得る。

10

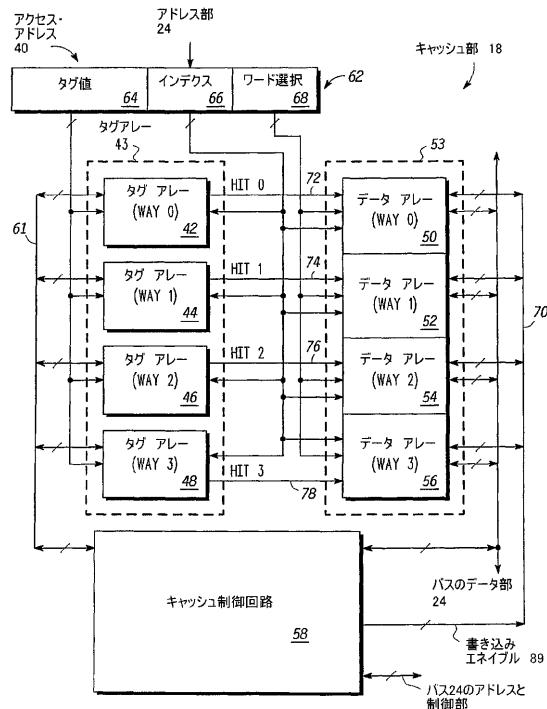

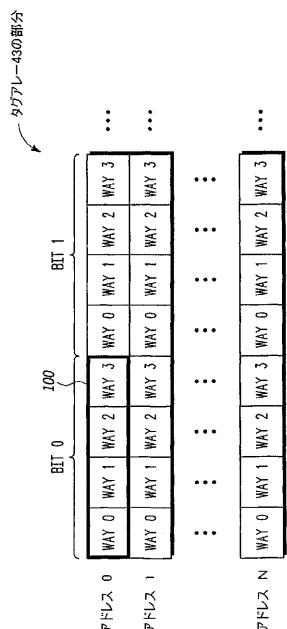

#### 【0012】

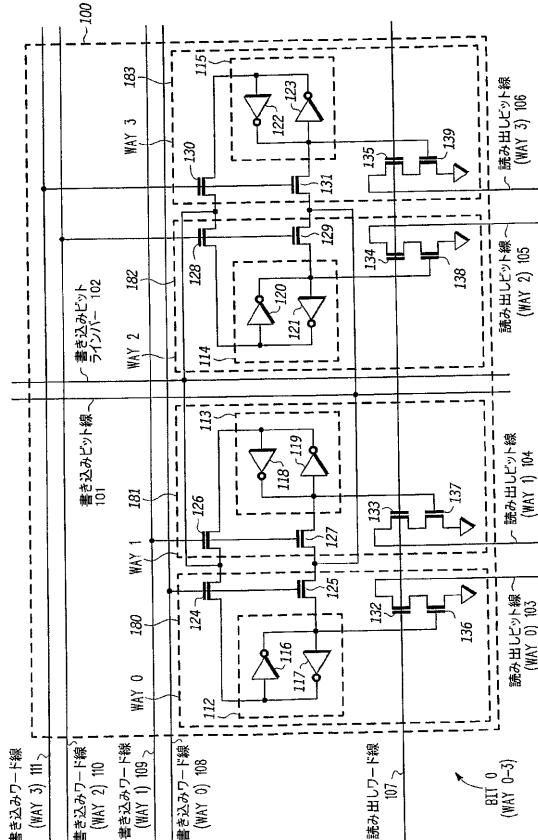

図 3 は、図 2 のタグアレイ 43 の一部の一実施形態を示す。例示した実施形態において、アドレス 0 用のビット 0 及びビット 1 を示す。他の実施形態は、各アドレスに対応する任意の所望数のビットを有し得る（例えば、アドレス 0 が、8 ビット、9 ビット、16 ビット、32 ビット、64 ビットに対応し得る等）。例示した実施形態の場合、所定のアドレス（例えば、アドレス 0）の各ビット（例えば、ビット 0）は、各経路（例えば、経路 0、経路 1、経路 2、経路 3）用の別個の部分を有することに留意されたい。また、タグアレイ 43 は、任意の所望数のアドレス（例えば、N を整数とすると、アドレス 0 乃至アドレス N）を有し得ることに留意されたい。例示した実施形態において、アドレス 0 用のビット 0 には、経路 0 用の回路、経路 1 用の回路、経路 2 用の回路、及び経路 3 用の回路を含む回路 100 が含まれる。

20

#### 【0013】

図 3 は、ビットセルを含むタグアレイ 43 の部分だけを示すことを当業者は認識されるであろう。各ビットセルには、記憶要素（1つ又は複数）と、記憶要素（1つ又は複数）の読み出し及び書き込みを行うためのトランジスタと、が含まれる（図 4 参照）。図 3 に示さないタグアレイ 43 の部分は、任意の適切な従来技術による方法を含む任意の所望の方法で実現し得る。例えば、幾つかの実施形態において、タグアレイ 43 には、アドレス、制御、及び書き込みデータ用の入力ラッチが含まれることがある。更に、アドレスデコーダ、ワード線ドライバ、及び列回路が存在することがある。列回路は、列多重化装置、センス增幅器又はデータインバータ、出力ドライバ、及び出力ラッチを包含し得るが、これらは、全て任意の適切な従来技術による方法を含む任意の所望の方法で実現し得る。本明細書に用いる用語「ビットセル」は、記憶回路の 1 つのタイプである。

30

#### 【0014】

更に、1 つのタグ経路だけが、所定の時間に書き込まれることがあることを当業者は認識されるであろう。更に一般的には、所定の入力項目用のビットセルの一部（ワード線）だけを書き込む必要があることは、極めて普通のことである。従って、ビットセルの残りは、それらの元の状態を保持すべきである。一般的に用いられる従来技術は、ワード線に関連する全てのビットセル用のプリチャージされた書き込みビット線対（ビット線及びビット線バー）を用いることによって、この機能を達成する。更新する必要がないビットセルは、第 2 電源電圧（例えば、電力又は VDD）に実質的に近い値でプリチャージされたままであるビット線及びビット線バーを有する。更新する必要があるビットセルは、ビット線及びビット線バー用の（VDD に近いものに対して接地に近いもの又はその逆の）相補値を有する。

40

#### 【0015】

上記パラグラフに述べた解決策は、当業者によって通常用いられる。しかしながら、それは、低消費電力及び低電圧動作を必要とする用途に対して固有の弱さを有する。特に、更新する必要がないビットセルは、依然としてそれらの選択トランジスタ（1つ又は複数）が導通状態にあることに留意すべきである。その結果、ビットセルの内部記憶ノードは、VDD 近くにプリチャージされたビット線及びビット線バー信号にさらされる。その結果、ビットセルの“論理 0”側に関連するビット線（又はビット線バー）から流れる電流

50

が存在する。これは、ビット線（又はビット線バー）を部分的に放電する“ダミー読出し”動作である。結局、部分的に放電されるビット線（又はビット線バー）は、プリチャージ動作中、再び補充する必要がある。従って、これは、無駄な電力である。

#### 【0016】

無駄な電力とは別に、この解決策固有の他の弱さがある。特に、“ダミー読出し”では、ビットセルの内部記憶ノードが、プリチャージされたビット線及びビット線バーにさらされる必要がある。すると、このことにより、ビットセルの状態が意図せずに変わる可能性がある。これを保護するために、ビットセルトランジスタは、ダミー読出し中、安定性が改善されるように大きさが決定されなければならない。このことの副作用は、これによって、ビットセルが低電圧で書き込むのが更に困難になることである。

10

#### 【0017】

図4に示す提案された解決策は、書き込まれる予定の各タグ経路に個別書き込みワード線を用いることによって、“ダミー読出し”を無くする。個別書き込みワード線によって、ビットセル面積が必ずしも増えるとは限らない。その理由は、これが、一般的に、メタルレイアウトルールに対して、トランジスタレイアウトルールによって支配されるためである。更に、図4の提案された解決策は、4つの経路用の全ての書き込み金属ビット線を1つの共用金属ビット線（及び／又はビット線バー）に統合する。この利点について、図4に関連する説明で議論する。

#### 【0018】

図4は、図3の回路100（経路0-3用のアドレス0のビット0）の一実施形態を示す。経路0用の記憶セル112には、交差接続インバータ116及び117が含まれる。記憶セル112は、トランジスタ124の第1電流電極に接続された第1端子及びトランジスタ125の第1電流電極に接続された第2端子を有する。トランジスタ124及び125の制御電極は、双方共、書き込みワード線（経路0）108に接続される。記憶セル112の第2端子は、トランジスタ136の制御電極に接続される。トランジスタ136の第1電流電極は、第1電源電圧に接続される。トランジスタ136の第2電流電極は、トランジスタ132の第1電流電極に接続される。読出しワード線107は、トランジスタ132の制御電極に接続される。トランジスタ132の第2電流電極は、読出しひット線（経路0）103に接続される。

20

#### 【0019】

経路1用の記憶セル113には、交差接続インバータ118及び119が含まれる。記憶セル113は、トランジスタ126の第1電流電極に接続された第1端子及びトランジスタ127の第1電流電極に接続された第2端子を有する。トランジスタ126及び127の制御電極は、双方共、書き込みワード線（経路1）109に接続される。トランジスタ126の第2電流電極は、トランジスタ124の第2電流電極及び書き込みビット線バー102に接続される。用語「バー」は、相補信号を示すために用いられる（例えば、書き込みビット線バー102は、書き込みビット線101に対して補完的である）ことに留意されたい。トランジスタ127の第2電流電極は、トランジスタ125の第2電流電極及び書き込みビット線101に接続される。記憶セル113の第2端子は、トランジスタ137の制御電極に接続される。トランジスタ137の第1電流電極は、第1電源電圧に接続される。トランジスタ137の第2電流電極は、トランジスタ133の第1電流電極に接続される。トランジスタ133の第2電流電極は、読出しひット線（経路1）104に接続される。回路180は、経路0に用いられ、回路181は、経路1に用いられる。

30

#### 【0020】

経路2用の記憶セル114には、交差接続インバータ120及び121が含まれる。記憶セル114は、トランジスタ128の第1電流電極に接続された第1端子及びトランジスタ129の第1電流電極に接続された第2端子を有する。トランジスタ128及び129の制御電極は、双方共、書き込みワード線（経路2）110に接続される。記憶セル114の第2端子は、トランジスタ138の制御電極に接続される。トランジスタ138の

40

50

第1電流電極は、第1電源電圧に接続される。トランジスタ138の第2電流電極は、トランジスタ134の第1電流電極に接続される。読み出しワード線107は、トランジスタ134の制御電極に接続される。トランジスタ134の第2電流電極は、読み出しひット線(経路2)105に接続される。

#### 【0021】

経路3用の記憶セル115には、交差接続インバータ122及び123が含まれる。記憶セル115は、トランジスタ130の第1電流電極に接続された第1端子及びトランジスタ131の第1電流電極に接続された第2端子を有する。トランジスタ130及び131の制御電極は、双方共、書き込みワード線(経路3)111に接続される。トランジスタ130の第2電流電極は、トランジスタ128の第2電流電極及び書き込みヒット線バ-102に接続される。トランジスタ131の第2電流電極は、トランジスタ129の第2電流電極及び書き込みヒット線101に接続される。記憶セル115の第2端子は、トランジスタ139の制御電極に接続される。トランジスタ139の第1電流電極は、第1電源電圧に接続される。トランジスタ139の第2電流電極は、トランジスタ135の第1電流電極に接続される。読み出しワード線107は、トランジスタ135の制御電極に接続される。トランジスタ135の第2電流電極は、読み出しひット線(経路3)106に接続される。回路182は、経路2に用いられ、回路183は、経路3に用いられる。図4に示すトランジスタは、全てnチャネル電界効果トランジスタである。他の実施形態は、代わりに、pチャネル電界効果トランジスタ、又は回路100内で適切に接続されたnチャネル及びpチャネルトランジスタの組合せを用い得る。

10

20

30

40

#### 【0022】

図4の回路100の幾つかの実施形態の場合、第1電源電圧は、ほぼ接地電圧であってよく、第2電源電圧は、第1電源電圧より高くてよく、また、プリチャージする(例えば、図4の読み出しひット線103-106をプリチャージする)目的に用いてよい。

#### 【0023】

図4の回路100は、アドレス(例えば、アドレス0)における追加の各ビットに対しても複製されることに留意されたい。更に、回路100は、アドレス0からアドレスNまでのアドレスにおける各ビット0に対しても複製される。例えば、アドレス1のビット0は、回路100の複製を利用する。

#### 【0024】

図4の回路100に示した特定の実施形態には、上述したもの以外の多くの恩恵がある。書き込みヒット線(101及び102)を共用することによって、また、各記憶回路(180-183)用にそれらを複製しないことによって、ルーティングが低減されることを当業者は認識されるであろう。これによって、読み出しひット線(103-106)の間隔が大きくなつて寄生容量が減少し、また、読み出しひット線(103-106)の幅が広くなつて導体配線の寄生抵抗が減少し得る。これら恩恵のいずれかによつて、回路100の読み出し動作を高速化し得る。更に、回路100に示した実施形態は、記憶要素を用いる他の用途より書き込みヒット線(101及び102)が少なく、従つて、書き込みヒット線(101及び102)を駆動するのに必要な回路が低減される。これは、用いる回路が小さくなり、また、寄生電力消費を受けるデバイスが少なくなり得ることを意味する。従つて、必要な半導体面積が小さくなり、漏れ電流が小さくなり得る。

#### 【0025】

次に、図4の回路100の読み出し動作の一実施形態について述べる。一実施形態において、アドレス0に対する読み出し動作中、読み出しワード線107がアサートされ、これにより、トランジスタ132、133、134、及び135が導通状態になる。トランジスタ136、137、138、及び139は、それぞれ記憶セル112、113、114、及び115に記憶された値に基づき、導通状態又は非導通状態のいずれかである。トランジスタ136が導通状態である場合、プリチャージされた読み出しひット線(経路0)103は、論理レベル“1”から論理レベル“0”に放電される。トランジスタ137が非導通状態である場合、プリチャージされた読み出しひット線(経路1)104は、論理レベル“

50

0"に放電されない。読み出しビット線(経路2)105及び読み出しビット線(経路3)106は、トランジスタ138及び139が導通状態又は非導通状態かどうかに依存して、放電されたり放電されなかつたりする。例示した実施形態では、全経路(経路0-3)が同時に読み出されることに留意されたい。

#### 【0026】

次に、図4の回路100の書き込み動作の一実施形態について述べる。一実施形態では、書き込み動作中、一度に1つの経路だけが書き込まれる。例えば、経路0のアドレス0への書き込みアクセスの場合、書き込みワード線(経路0)108が、アサートされ、他の全ての書き込みワード線109-111は、アサートされない。書き込まれるデータは、書き込みビット線101に印加又は供給され、補完データは、書き込みビット線バー102に印加又は供給される。書き込みワード線(経路0)108がアサートされると、トランジスタ124及び125は、導通状態になる。これによって、記憶セル112の2つの端子は、書き込みデータ値を記憶セル112に伝達するために、それぞれ書き込みビット線101及び書き込みビット線バー102に接続される。

10

#### 【0027】

例示した実施形態の場合、読み出しアクセス及び書き込みアクセスは、互いに独立することに留意されたい。従って、読み出し動作及び書き込み動作は、読み出しアクセスが、書き込みアクセスと異なるアドレスに対するものであれば、同時に起こり得る。従って、例示した実施形態の場合、異なるアドレスへの読み出しアクセス及び書き込みアクセスは、時間的に、同時に、部分的に重なり合って、又は重なり合わずに起こり得る。

20

#### 【0028】

本発明の他の実施形態は、わずかな回路を追加することによって、追加の読み出し及び/又は書き込みポートを追加し得ることに留意されたい。例えば、追加の読み出しポートは、各経路用にトランジスタ132及び136、133及び137、134及び138、並びに135及び139と並列に別のトランジスタを追加することによって、また、別の読み出しづる線及び別の読み出しつつ線を追加することによって、追加し得る。追加の書き込みポートは、各経路用にトランジスタ124及び125、126及び127、128及び129、並びに130及び131と並列に別のトランジスタを追加することによって、また、別の書き込みワード線及び別の書き込みビット線を追加することによって、追加し得る。

30

#### 【0029】

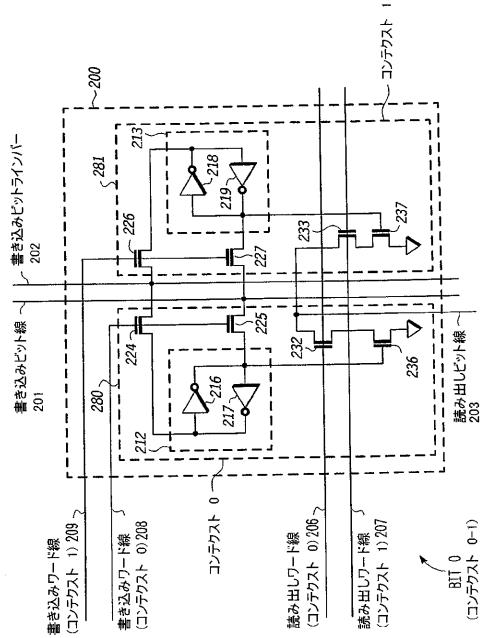

次に、図5において、図5の回路200は、キャッシュ18の文脈でも用い得るが、レジスタファイル(例えば、図1のレジスタファイル17)の文脈で述べる。従って、キャッシュに用いられる“経路”の概念の代わりに、“文脈”の概念を用いる。例えば、レジスタファイル17は、文脈スイッチングに、例えば、多数のタスク又はスレッドが用いられる場合に用い得る。本発明は、任意の所望の用途に用い得ること、及び本明細書において述べた用途(例えば、キャッシュ経路、文脈スイッチング)は、単に2つの可能な用途であることに留意されたい。更に、図4及び5で本明細書に述べた回路は、データ処理システム10の任意の部分に、例えば、レジスタファイル17、(例えば、潜在的な枝路アドレスを記憶するための)分岐ユニット15、SRAM19、他のモジュール20、キャッシュ18、バッファ21、及びメモリ14等に用い得る。他の実施形態は、任意の所望の方法で、また、任意の所望の用途に、図4-5に示す回路を用い得る。

40

#### 【0030】

図5は、図1のレジスタファイル17の一部の回路200の一実施形態(文脈0-1用のアドレス0のビット0)を示す。文脈0用の記憶セル212には、交差接続インバータ216及び217が含まれる。記憶セル212は、トランジスタ224の第1電流電極に接続された第1端子及びトランジスタ225の第1電流電極に接続された第2端子を有する。トランジスタ224及び225の制御電極は、双方共、書き込みワード線(文脈0)208に接続される。記憶セル212の第2端子は、トランジスタ236の制御電極に接続される。トランジスタ236の第1電流電極は、第1電源電圧に接続される。トランジ

50

スタ 2 3 6 の第 2 電流電極は、トランジスタ 2 3 2 の第 1 電流電極に接続される。読み出しワード線 2 0 6 は、トランジスタ 2 3 2 の制御電極に接続される。トランジスタ 2 3 2 の第 2 電流電極は、読み出しひット線 2 0 3 に接続される。

#### 【 0 0 3 1 】

文脈 1 用の記憶セル 2 1 3 には、交差接続インバータ 2 1 8 及び 2 1 9 が含まれる。記憶セル 2 1 3 は、トランジスタ 2 2 6 の第 1 電流電極に接続された第 1 端子及びトランジスタ 2 2 7 の第 1 電流電極に接続された第 2 端子を有する。トランジスタ 2 2 6 及び 2 2 7 の制御電極は、双方共、書き込みワード線（文脈 1）2 0 9 に接続される。トランジスタ 2 2 6 の第 2 電流電極は、トランジスタ 2 2 4 の第 2 電流電極及び書き込みヒット線バー 2 0 2 に接続される。トランジスタ 2 2 7 の第 2 電流電極は、トランジスタ 2 2 5 の第 2 電流電極及び書き込みヒット線 2 0 1 に接続される。記憶セル 2 1 3 の第 2 端子は、トランジスタ 2 3 7 の制御電極に接続される。トランジスタ 2 3 7 の第 1 電流電極は、第 1 電源電圧に接続される。トランジスタ 2 3 7 の第 2 電流電極は、トランジスタ 2 3 3 の第 1 電流電極に接続される。読み出しワード線 2 0 7 は、トランジスタ 2 3 3 の制御電極に接続される。トランジスタ 2 3 3 の第 2 電流電極は、読み出しひット線 2 0 3 に接続される。回路 2 8 0 は、文脈 0 に用いられ、回路 2 8 1 は、文脈 1 に用いられる。図 5 に示すトランジスタは、全て n チャネル電界効果トランジスタである。他の実施形態は、代わりに、p チャネル電界効果トランジスタ、又は回路 2 0 0 内で適切に接続された n チャネル及び p チャネルトランジスタの組合せを用い得る。

#### 【 0 0 3 2 】

図 5 の回路 2 0 0 の幾つかの実施形態の場合、第 1 電源電圧は、ほぼ接地電圧であってよく、第 2 電源電圧は、第 1 電源電圧より高くてよく、また、プリチャージする（例えば、図 5 の読み出しひット線 2 0 3 をプリチャージする）目的に用いてよい。

#### 【 0 0 3 3 】

図 5 の回路 2 0 0 は、アドレス（例えば、アドレス 0）における追加の各ビットに対して複製されることに留意されたい。更に、回路 2 0 0 は、アドレス 0 からアドレス Nまでのアドレスにおける各ビット 0 に対しても複製される。例えば、アドレス 1 のビット 0 は、回路 2 0 0 の複製を利用する。

#### 【 0 0 3 4 】

図 5 に示す回路は、単一の読み出しなート及び単一の書き込みポートによる 2 スレッドレジスタファイル（例えば、図 1 のレジスタファイル 1 7）での用途に適用可能である。各スレッド（即ち、“文脈”）は、別個の記憶要素 2 1 2、2 1 3 によって表される。所定の時間において、レジスタファイル 1 7 のアクセスが、2 つのスレッドの内の 1 つにおいて起こる。例えば、この特定のビットへの書き込み動作は、適切な書き込みワード線（2 0 8 又は 2 0 9）上において、論理レベル “1” を必然的に伴う。アクセスされないスレッドは、その書き込みワード線が、論理レベル “0” である。そして、書き込みヒット線 2 0 1 及び 2 0 2 上に存在するデータ値は、それぞれの選択トランジスタ（2 2 4 及び 2 2 5、2 2 6 及び 2 2 7）を通して、適切な記憶セル 2 1 2 及び 2 1 3 に接続される。

#### 【 0 0 3 5 】

次に、図 5 の回路 2 0 0 用の読み出し動作の一実施形態について述べる。例示した実施形態において、読み出しあクセスでは、適切な読み出しワード線（2 0 6 又は 2 0 7）が論理レベル “1” である必要がある。一実施形態において、文脈 0 に対する読み出し動作中、読み出しワード線 2 0 6 が、アサートされ（即ち、論理レベル “1”）、これによって、トランジスタ 2 3 2 が導通状態になり、トランジスタ 2 3 3 は、実質的に非導通状態になる。その結果、記憶セル 2 1 2 に記憶された値は、この時点で、読み出しひット線 2 0 3 の合成値を決定する。一実施形態において、読み出しひット線 2 0 3 は、初期的に論理レベル “1” にプリチャージした。読み出しひット線 2 0 3 は、論理レベル “0” に放電するか、又は、論理レベル “1” にプリチャージされたままである。一実施形態において、読み出しひット線 2 0 3 の値は、インバータ又はバッファ（図示せず）のいずれかを通して、レジスタファイル 1 7 データ出力バス（図示せず）に接続してよい。上記読み出し動作の場合、トラン

10

20

30

40

50

ジスタ 233 が実質的に非導通状態であるという事実により、記憶セル 213 に記憶された値は、読み出しひット線 203 に影響を及ぼさないことに留意されたい。

#### 【0036】

図 5 の上記説明は、具体的には、単一の読み出しポート及び単一の書き込みポートの場合に該当する。しかしながら、図 5 に示す回路は、簡単に多数の読み出しポート及び / 又は多数の書き込みポートの場合に拡張し得る。図 5 の例示した実施形態において、読み出しポートを追加すると、(積層 236、232 及び積層 233、237 と同様な) n チャネル直列積層に各々接続される読み出しワード線(206、207 等)の追加及び読み出しひット線(203 等)の追加が必然的に伴う。書き込みポートを追加すると、選択トランジスタ(224、225 及び 226、227 等)に各々接続される書き込みワード線(208、209 等)及び書き込みヒット線(201、202 等)の追加が必然的に伴う。

10

#### 【0037】

上記明細書において、具体的な実施形態を参照して、本発明について説明した。しかしながら、当業者が理解されるように、以下の請求項に記載した本発明の範囲から逸脱することなく、様々な修正及び変更を行い得る。例えば、読み出し及び / 又は書き込みヒット線は、単一端ヒット線であってよく又は他の選択肢としてヒット線対であってよい。ヒット線対の場合、多くの可能性がある。例えば、ヒット線対は、予めハイに充電したり、予めローに充電したり、接地と VDD との間の値にプリチャージしたり、小信号差動電圧を持持したり、あるいは、全レール相補電圧を持持し得る。したがって、明細書及び図は、限定的でなく例示的であると見なすものとし、また、そのような全ての修正は、本発明の範囲内に含まれるものとする。

20

#### 【0038】

恩恵、他の利点、及び問題の解決策について、具体的な実施形態を基にこれまで述べた。しかしながら、これらの恩恵、利点、問題の解決策、及び何らかの恩恵、利点、又は解決策を生じさせる又はより顕著にさせる如何なる要素(1つ又は複数)も、全ての請求項の重要な、必要な、若しくは不可欠な特徴又は要素として解釈してはならない。本明細書に用いた用語「“a”又は“an”(不定冠詞)」は、1つ又は1つ以上と定義する。本明細書に用いた用語「“including”(含む)」及び / 又は「“having”(有する)」は、「“comprising”(含む)」(即ち、オープンランゲージ)と定義する。本明細書に用いた用語「“comprises”(含む)」、「“comprising”(含む)」又はその派生語は、非排他的な包括を網羅するものであり、一連の要素を含むプロセス、方法、物、又は装置が、これらの要素だけでなく、明示的に列記されていない他の要素や、このようなプロセス、方法、物、又は装置に固有の他の要素も含み得る。

30

#### 【図面の簡単な説明】

#### 【0039】

- 【図 1】本発明の一実施形態に基づくデータ処理システムを示すブロック図。

- 【図 2】本発明の一実施形態に基づく図 1 のキャッシュの一部を示すブロック図。

- 【図 3】本発明の一実施形態に基づく図 2 のタグアレイの一部を示すブロック図。

- 【図 4】本発明の一実施形態に基づく図 3 のアドレス 0 のヒット 0 を示す概略図。

- 【図 5】本発明の一実施形態に基づく図 1 のレジスタファイル 17 の一部におけるアドレス 0 のヒット 0 を示す概略図。

40

〔 図 1 〕

【 図 2 】

【図3】

【 図 4 】

【図 5】

---

フロントページの続き

(51) Int.Cl.

F I

G 0 6 F 12/08 5 7 9

テーマコード(参考)

(81) 指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,LV,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LC,LK,L,R,LS,LT,LU,LY,MA,MD,MG,MK,MN,MW,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SM,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(72) 発明者 ケンケア、プラシャント ユー.

アメリカ合衆国 7 8 7 3 6 テキサス州 オースティン コニファー コーブ 6 5 0 1

(72) 発明者 パルマー、ジェレミア ティ.シー.

アメリカ合衆国 7 8 6 8 1 テキサス州 ラウンド ロック グレン キャニオン ドライブ

8 8 0 5

F ターム(参考) 5B005 JJ12 JJ22 MM01

5B015 HH01 HH03 JJ01 JJ21 KA09 NN01