# (19) 대한민국특허청(KR)

# (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

*G11C* 7/22 (2015.01) *G11C* 7/10 (2021.01) *H03L* 7/081 (2006.01) *H03L* 7/089 (2006.01)

(52) CPC특허분류 G11C 7/222 (2013.01) G11C 7/1045 (2013.01)

(21) 출원번호 10-2019-0081148

(22) 출원일자 **2019년07월05일**

심사청구일자 없음

(11) 공개번호 10-2021-0004551

(43) 공개일자 2021년01월13일

(71) 출원인

#### 삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

#### 김화평

경기도 화성시 삼성전자로 1 삼성전자(주)화성사 업장

#### 최훈대

경기도 화성시 삼성전자로 1 삼성전자(주)화성사 업장

(74) 대리인 **하영욱**

전체 청구항 수 : 총 10 항

## (54) 발명의 명칭 지연 동기 루프 회로 및 이를 구비하는 반도체 메모리 장치

#### (57) 요 약

본 발명은 지연 동기 루프 회로 및 이를 구비하는 반도체 메모리 장치를 개시한다. 지연 동기 루프 회로는 입력 클럭신호를 버퍼하여 기준 클럭신호를 발생하는 클럭신호 입력버퍼, 코스 지연 코드 또는 파인 지연 코드에 응답 하여 기준 클럭신호를 지연하여 내부 클럭신호를 발생하는 지연부, 내부 클럭신호를 클럭신호 입력버퍼의 지연 시간만큼 지연하여 피드백 클럭신호를 발생하는 클럭신호 지연 레플리카부, 기준 클럭신호와 피드백 클럭신호를 입력하여 기준 클럭신호의 천이 시점과 기준 클럭신호의 천이 시점 보다 앞서서 발생되는 피드백 클럭신호의 천이 시점 사이의 시간을 검출하여 코스 지연 코드를 발생하는 코스 지연 제어부, 및 기준 클럭신호의 위상과 피드백 클럭신호의 위상을 비교하여 파인 제어 코드를 발생하는 파인 지연 제어부를 포함할 수 있다.

## 대표도

# (52) CPC특허분류

HO3L 7/0814 (2013.01) HO3L 7/0818 (2013.01) HO3L 7/089 (2013.01)

## 명 세 서

#### 청구범위

### 청구항 1

외부로부터 인가되는 외부 클럭신호를 지연하여 내부 클럭신호를 발생하고, 상기 외부 클럭신호에 동기된 피드백 클럭신호를 발생하는 지연 동기 루프 회로;

로우 어드레스를 디코딩하여 복수개의 워드라인 선택신호들을 발생하는 로우 어드레스 디코더;

컬럼 어드레스를 디코딩하여 복수개의 컬럼 선택신호들을 발생하는 컬럼 어드레스 디코더;

복수개의 메모리 셀들을 포함하고, 상기 복수개의 워드라인 선택신호들과 상기 복수개의 컬럼 선택신호들에 의해서 상기 복수개의 메모리 셀들 중 선택된 메모리 셀들에 저장된 데이터를 출력하는 메모리 셀 어레이;

리드 명령에 응답하여 상기 메모리 셀 어레이로부터 출력되는 데이터를 입력하고 상기 내부 클럭신호에 응답하여 상기 데이터를 출력하는 데이터 리드 경로부; 및

상기 데이터를 버퍼하여 외부로 버퍼된 데이터를 출력하는 데이터 출력버퍼;

상기 내부 클럭신호를 버퍼하여 상기 외부 클럭신호에 동기된 데이터 스트로우브 신호를 출력하는 데이터 스트 로우브 신호 버퍼를 포함하고,

상기 지연 동기 루프 회로는

상기 외부 클럭신호를 버퍼하여 기준 클럭신호를 발생하는 클럭신호 입력버퍼;

코스 지연 코드 및 파인 지연 코드에 응답하여 상기 기준 클럭신호를 지연하여 내부 클럭신호를 발생하는 지연 부;

상기 내부 클럭신호를 상기 클럭신호 입력버퍼의 지연 시간에 상기 데이터 스트로우브 신호 출력버퍼의 지연 시간을 더한 지연 시간 만큼 지연하여 상기 피드백 클럭신호를 발생하는 클럭신호 지연 레플리카부;

상기 기준 클럭신호와 상기 피드백 클럭신호를 입력하여 상기 기준 클럭신호의 천이 시점과 상기 기준 클럭신호의 천이 시점 보다 앞서서 발생되는 상기 피드백 클럭신호의 천이 시점 사이의 시간을 검출하여 상기 코스 지연 코드를 발생하는 코스 지연 제어부; 및

상기 기준 클럭신호의 위상과 상기 피드백 클럭신호의 위상을 비교하여 상기 파인 제어 코드를 발생하는 파인 지연 제어부를 포함하는 반도체 메모리 장치.

#### 청구항 2

제1 항에 있어서, 상기 반도체 메모리 장치는

모드 설정 명령에 응답하여 외부로부터 인가되는 모드 설정 코드를 입력하여 리드 레이턴시 및 버스트 길이를 설정하는 모드 설정 레지스터; 및

상기 리드 명령에 응답하여 상기 내부 클럭신호, 상기 리드 레이턴시, 및 상기 버스트 길이를 이용하여 상기 데이터 출력버퍼를 통하여 데이터가 출력되는 기간 동안 활성화되는 레이턴시 신호를 발생하는 레이턴시 제어부를 추가적으로 포함하는 반도체 메모리 장치.

## 청구항 3

제1 항에 있어서, 상기 지연부는

상기 코스 지연 코드에 응답하여 상기 기준 클럭신호를 지연하는 코스 지연부; 및

상기 파인 지연 코드에 응답하여 상기 코스 지연부로부터 출력되는 클럭신호를 지연하여 상기 내부 클럭신호를 발생하는 파인 지연부를 포함하는 반도체 메모리 장치.

#### 청구항 4

제1 항에 있어서, 상기 코스 지연 제어부는

상기 기준 클럭신호의 천이 시점과 상기 기준 클럭신호의 천이 시점 보다 앞서서 발생되는 상기 피드백 클럭신호의 천이 시점을 검출하여 분주된 기준 클럭신호 및 분주된 피드백 클럭신호를 발생하는 피드백 클럭신호 우선 발생기; 및

상기 분주된 피드백 클럭신호의 천이 시점과 상기 분주된 기준 클럭신호의 천이 시점 사이의 시간을 검출하고 상기 시간에 대응하는 상기 코스 지연 코드를 발생하는 코스 지연 코드 발생기를 포함하는 반도체 메모리 장치.

#### 청구항 5

제4 항에 있어서, 상기 피드백 클럭신호 우선 발생기는

상기 피드백 클럭신호의 상승 천이에서 상기 기준 클럭신호의 레벨을 검출하여 위상 감시신호를 활성화하는 위상 감시기;

상기 피드백 클럭신호의 상승 천이 동안 상기 기준 클럭신호의 하강 천이를 검출하여 엣지 검출신호를 활성화하는 엣지 검출기;

상기 위상 감시신호 또는 상기 엣지 검출신호가 활성화되면, 상기 피드백 클럭신호의 상승 천이에 응답하여 제1 선택신호를 활성화하고, 상기 기준 클럭신호의 상승 천이에 응답하여 상기 제1 선택신호를 입력하여 제2 선택신 호를 활성화하고, 상기 위상 감시신호 또는 상기 엣지 검출신호가 모두 비활성화되면, 상기 피드백 클럭신호의 하강 천이에 응답하여 상기 제1 선택신호를 활성화하고, 상기 기준 클럭신호의 상승 천이에 응답하여 상기 제1 선택신호를 입력하여 상기 제2 선택신호를 활성화하는 분주 엣지 선택기;

상기 분주된 피드백 클럭신호의 레벨에 응답하여 상기 제1 선택신호를 입력하여 제1 인에이블 신호를 발생하고, 상기 위상 감시신호 또는 상기 엣지 검출신호가 활성화되는 경우에 상기 제2 선택신호를 입력하고 상기 위상 감 시신호 및 상기 엣지 검출신호가 모두 비활성화되면 상기 제1 선택신호를 입력하고 상기 분주된 기준 클럭신호 의 레벨에 응답하여 제2 인에이블 신호를 발생하는 분주 인에이블 신호 발생기;

상기 제1 인에이블 신호에 응답하여 인에이블되고 상기 피드백 클럭신호를 분주하여 상기 분주된 피드백 클럭신호를 발생하는 제1 분주기; 및

상기 제2 인에이블 신호에 응답하여 인에이블되고 상기 기준 클럭신호를 분주하여 상기 분주된 기준 클럭신호를 발생하는 제2 분주기를 포함하는 반도체 메모리 장치.

### 청구항 6

제5 항에 있어서, 상기 위상 감시기는

상기 피드백 클럭신호의 상승 천이에 응답하여 상기 기준 클럭신호를 입력하여 상기 위상 감시신호를 발생하는 제1 플립플롭을 포함하는 반도체 메모리 장치.

### 청구항 7

제5 항에 있어서, 상기 엣지 검출기는

상기 기준 클럭신호를 소정 시간 만큼 지연하여 지연된 기준 클럭신호를 발생하는 제1 지연기;

상기 피드백 클럭신호를 상기 소정 시간 만큼 지연하여 지연된 피드백 클럭신호를 발생하는 제2 지연기;

상기 피드백 클럭신호에 응답하여 상기 지연된 기준 클럭신호를 입력하여 제1 검출신호를 발생하는 제2 플립플롭;

상기 지연된 피드백 클럭신호에 응답하여 상기 기준 클럭신호를 입력하여 제2 검출신호를 발생하는 제3 플립플롭;

상기 제2 검출신호를 반전하여 반전된 제2 검출신호를 발생하는 제1 인버터;

상기 제1 검출신호 및 상기 반전된 제2 검출신호를 비논리곱하는 NAND게이트; 및

상기 NAND게이트의 출력신호를 반전하여 상기 엣지 검출신호를 발생하는 제2 인버터를 포함하는 반도체 메모리장치.

#### 청구항 8

제5 항에 있어서, 상기 분주 엣지 선택기는

상기 위상 감시신호와 상기 엣지 검출신호를 비논리합하는 NOR게이트;

상기 NOR게이트의 출력신호를 반전하여 제3 검출신호를 발생하는 인버터;

상기 제3 검출신호에 응답하여 상기 피드백 클럭신호의 위상과 동일한 위상을 가지거나, 반대 위상을 가지는 중 간 피드백 클럭신호를 발생하는 피드백 클럭신호 위상 결정기;

상기 중간 피드백 클럭신호에 응답하여 코스 동기 인에이블 신호를 래치하여 상기 제1 선택신호를 발생하는 제4 플립플롭; 및

상기 기준 클럭신호에 응답하여 상기 제1 선택신호를 래치하여 상기 제2 선택신호를 발생하는 제5 플립플롭을 포함하는 반도체 메모리 장치.

#### 청구항 9

제8 항에 있어서, 상기 분주 인에이블 신호 발생기는

상기 제1 선택신호를 입력하고 소정 시간 만큼 지연하여 상기 제1 인에이블 신호를 발생하는 지연기;

상기 제3 검출신호에 응답하여 상기 제1 선택신호 또는 상기 제2 선택신호를 선택하고 상기 소정 시간 만큼 지연하여 상기 제2 인에이블 신호를 발생하는 선택기를 포함하는 반도체 메모리 장치.

#### 청구항 10

제1 항에 있어서, 상기 파인 지연 제어부는

상기 코스 지연 제어부의 동작이 완료된 후, 상기 기준 클럭신호의 위상과 상기 피드백 클럭신호의 위상을 비교 하여 비교 결과에 따라 업 신호 또는 다운 신호를 발생하는 위상 비교기; 및

상기 업 신호 또는 상기 다운 신호에 응답하여 카운팅 동작을 수행하여 상기 파인 지연 코드를 발생하는 파인 지연 코드 발생기를 포함하는 반도체 메모리 장치.

#### 발명의 설명

## 기술분야

[0001] 본 개시에 따른 실시예들은 지연 동기 루프 회로 및 이를 구비하는 반도체 메모리 장치에 관한 것이다.

#### 배경기술

- [0002] 지연 동기 루프 회로는 입력 클럭신호의 위상에 동기된 출력 클럭신호를 발생하기 위하여 구성될 수 있다.

- [0003] 일반적으로, 지연 동기 루프 회로는 코드 값에 따라 입력 클럭신호를 버퍼하여 발생되는 기준 클럭신호를 가변 적으로 지연하는 지연 셀들을 포함하는 가변 지연부 및 기준 클럭신호와 출력 클럭신호를 복제하여 발생되는 피드백 클럭신호의 위상 차를 검출하여 코드를 발생하는 위상 차 검출기를 포함할 수 있다.

- [0004] 그런데, 지연 동기 루프 회로는 위상 차 검출기의 오동작(위상 차 검출의 불명확성(uncertainty))으로 인해서 기준 클럭신호와 피드백 클럭신호의 위상 차가 실제 위상 차 보다 크게 검출될 수 있다.

## 발명의 내용

#### 해결하려는 과제

[0005] 본 개시에 따른 실시예들의 과제는 기준 클럭신호와 피드백 클럭신호의 위상 차를 정확하게 검출할 수 있는 지

연 동기 루프 회로 및 이를 구비하는 반도체 메모리 장치를 제공하는데 있다.

[0006] 본 개시에 따른 실시예들의 과제는 이상에서 언급한 과제에 제한되지 않으며, 언급되지 않은 또 다른 과제들은 아래의 기재로부터 당업자에게 명확하게 이해될 수 있을 것이다.

### 과제의 해결 수단

- [0007] 본 개시에 따른 실시예들의 지연 동기 루프 회로는 입력 클럭신호를 버퍼하여 기준 클럭신호를 발생하는 클럭신호를 발생하는 클럭신호를 발생하는 크럭신호를 발생하는 지연부; 상기 내부 클럭신호를 상기 클럭신호 입력버퍼의 지연 시간만큼 지연하여 피드백 클럭신호를 발생하는 클럭신호 지연 레플리카부; 상기 기준 클럭신호와 상기 피드백 클럭신호를 입력하여 상기 기준 클럭신호의 천이 시점과 상기 기준 클럭신호의 천이 시점 보다 앞서서 발생되는 상기 피드백 클럭신호의 천이 시점 사이의 시간을 검출하여 상기 코스 지연 코드를 발생하는 코스 지연 제어부; 및 상기 기준 클럭신호의 위상과 상기 피드백 클럭신호의 위상을 비교하여 상기 파인 제어 코드를 발생하는 파인 지연 제어부를 포함할 수 있다.

- [0008] 본 개시에 따른 실시예들의 지연 동기 루프 회로는 입력 클럭신호를 버퍼하여 기준 클럭신호를 발생하는 클럭신호 입력버퍼; 코스 지연 코드에 응답하여 상기 기준 클럭신호를 지연하는 코스 지연부; 파인 지연 코드에 응답하여 상기 코스 지연부로부터 출력되는 클럭신호를 지연하여 상기 내부 클럭신호를 발생하는 파인 지연부; 상기 내부 클럭신호를 지연하여 출력 클럭신호를 발생하는 클럭신호 지연 경로부; 상기 내부 클럭신호를 상기 클럭신호 입력버퍼의 지연 시간에 상기 클럭신호 지연 경로부의 지연 시간을 더한 지연 시간 만큼 지연하여 피드백 클럭신호를 발생하는 클럭신호 지연 레플리카부; 상기 기준 클럭신호와 상기 피드백 클럭신호를 입력하여 상기 기준 클럭신호의 천이 시점 보다 앞서서 발생되는 상기 피드백 클럭신호의 천이 시점 사이의 시간을 검출하여 상기 코스 지연 코드를 발생하는 코스 지연 제어부; 및 상기 기준 클럭신호의 위상과 상기 피드백 클럭신호의 위상을 비교하여 상기 파인 제어 코드를 발생하는 파인 지연 제어부를 포함할수 있다.

- [0009] 본 개시에 따른 실시예들의 반도체 메모리 장치는 외부로부터 인가되는 외부 클럭신호를 지연하여 내부 클럭신 호를 발생하고, 상기 외부 클럭신호에 동기된 피드백 클럭신호를 발생하는 지연 동기 루프 회로; 로우 어드레스 를 디코딩하여 복수개의 워드라인 선택신호들을 발생하는 로우 어드레스 디코더; 컬럼 어드레스를 디코딩하여 복수개의 컬럼 선택신호들을 발생하는 컬럼 어드레스 디코더; 복수개의 메모리 셀들을 포함하고, 상기 복수개의 워드라인 선택신호들과 상기 복수개의 컬럼 선택신호들에 의해서 상기 복수개의 메모리 셀들 중 선택된 메모리 셀들에 저장된 데이터를 출력하는 메모리 셀 어레이; 리드 명령에 응답하여 상기 메모리 셀 어레이로부터 출력 되는 데이터를 입력하고 상기 내부 클럭신호에 응답하여 상기 데이터를 출력하는 데이터 리드 경로부; 상기 데 이터를 버퍼하여 외부로 버퍼된 데이터를 출력하는 데이터 출력버퍼; 및 상기 내부 클럭신호를 버퍼하여 상기 외부 클럭신호에 동기된 데이터 스트로우브 신호를 출력하는 데이터 스트로우브 신호 버퍼를 포함하고, 상기 지 연 동기 루프 회로는 상기 외부 클럭신호를 버퍼하여 기준 클럭신호를 발생하는 클럭신호 입력버퍼; 코스 지연 코드 또는 파인 지연 코드에 응답하여 상기 기준 클럭신호를 지연하여 내부 클럭신호를 발생하는 지연부; 상기 내부 클럭신호를 상기 클럭신호 입력버퍼의 지연 시간에 상기 데이터 스트로우브 신호 출력버퍼의 지연 시간을 더한 지연 시간 만큼 지연하여 상기 피드백 클럭신호를 발생하는 클럭신호 지연 레플리카부; 상기 기준 클럭신 호와 상기 피드백 클럭신호를 입력하여 상기 기준 클럭신호의 천이 시점과 상기 기준 클럭신호의 천이 시점 보 다 앞서서 발생되는 상기 피드백 클럭신호의 천이 시점 사이의 시간을 검출하여 상기 코스 지연 코드를 발생하 는 코스 지연 제어부; 및 상기 기준 클럭신호의 위상과 상기 피드백 클럭신호의 위상을 비교하여 상기 파인 제 어 코드를 발생하는 파인 지연 제어부를 포함할 수 있다.

## 발명의 효과

- [0010] 본 개시에 따른 실시예들의 지연 동기 루프 회로는 기준 클럭신호의 천이 시점과 기준 클럭신호의 천이 시점 보다 (1 클럭 사이클 이전 내에) 앞서서 발생되는 피드백 클럭신호의 천이 시점을 검출하여 코스 지연 코드를 발생함으로써 기준 클럭신호의 천이 시점과 피드백 클럭신호의 천이 시점 사이의 시간을 정확하게 검출할 수있다.

- [0011] 따라서, 본 개시에 따른 실시예들의 지연 동기 루프 회로 및 이를 구비하는 반도체 메모리 장치의 동작의 신뢰 성이 개선될 수 있다.

## 도면의 간단한 설명

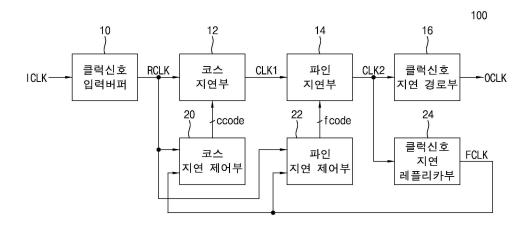

- [0012] 도 1은 본 개시에 따른 실시예의 지연 동기 루프 회로의 구성을 나타내는 블록도이다.

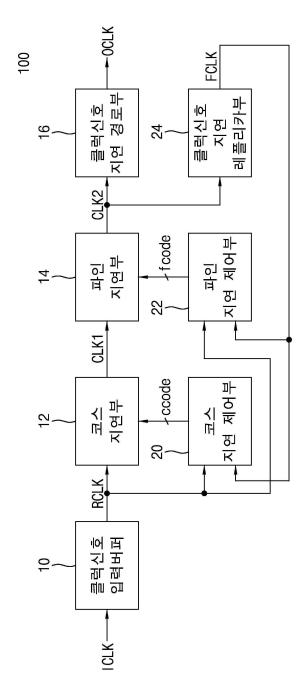

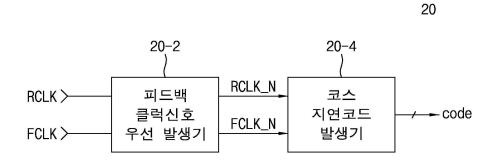

- 도 2는 본 개시에 따른 실시예의 코스 지연 제어부의 구성을 나타내는 블록도이다.

- 도 3은 본 개시에 따른 실시예의 피드백 클럭신호 우선 발생기의 구성을 나타내는 블록도이다.

- 도 4는 본 개시에 따른 실시예의 위상 감시기의 구성을 나타내는 것이다.

- 도 5는 본 개시에 따른 실시예의 엣지 검출기의 구성을 나타내는 것이다.

- 도 6은 본 개시에 따른 실시예의 분주 엣지 선택기의 구성을 나타내는 것이다.

- 도 7은 본 개시에 따른 실시예의 분주 인에이블 신호 발생기의 구성을 나타내는 것이다.

- 도 8은 본 개시에 따른 실시예의 제1 분주기 및 제2 분주기의 구성을 나타내는 것이다.

- 도 9 내지 도 11은 본 개시에 따른 실시예의 피드백 클럭신호 우선 발생기의 동작을 설명하기 위한 동작 타이밍 도들이다.

- 도 12는 본 개시에 따른 실시예의 코스 지연 코드 발생기의 구성을 나타내는 블록도이다.

- 도 13은 본 개시에 따른 실시예의 파인 지연 제어부의 구성을 나타내는 블록도이다.

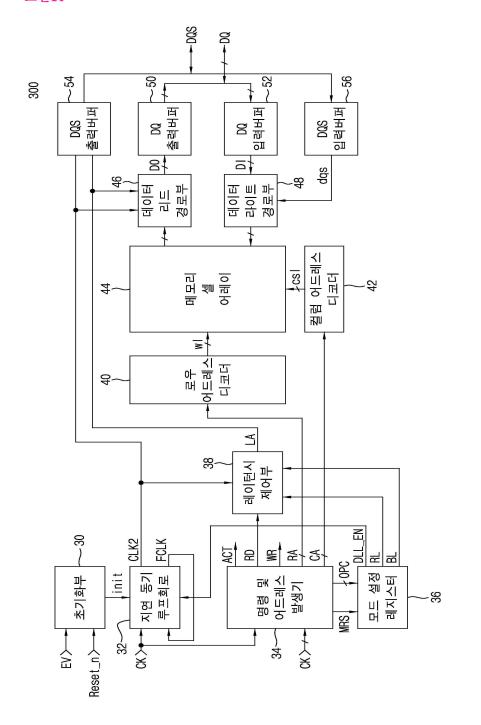

- 도 14는 본 개시에 따른 실시예의 반도체 메모리 장치를 나타내는 블록도이다.

## 발명을 실시하기 위한 구체적인 내용

- [0013] 이하, 첨부된 도면을 참고로 하여 본 개시에 따른 실시예들의 지연 동기 루프 회로 및 이를 구비하는 반도체 메모리 장치를 설명하면 다음과 같다.

- [0014] 도 1은 본 개시에 따른 실시예의 지연 동기 루프 회로의 구성을 나타내는 블록도로서, 클럭신호 입력버퍼(10), 코스(coarse) 지연부(12), 파인(fine) 지연부(14), 클럭신호 지연 경로부(16), 코스 지연 제어부(20), 위상 차 검출부(22), 및 클럭신호 지연 레플리카부(24)를 포함할 수 있다.

- [0015] 도 1에 나타낸 블록들 각각의 기능을 설명하면 다음과 같다.

- [0016] 클럭신호 입력버퍼(10)는 입력 클럭신호(ECLK)를 버퍼하여 기준 클럭신호(RCLK)를 발생할 수 있다.

- [0017] 코스 지연부(12)는 복수개의 직렬 연결된 제1 지연 셀들(미도시)을 포함하며, 코스 지연 코드(ccode)에 응답하여 코스 지연부(12)의 지연 시간이 가변될 수 있다. 코스 지연부(12)는 기준 클럭신호(RCLK)를 코스 지연부(12)의 지연 시간만큼 지연하여 제1 클럭신호(CLK1)를 발생할 수 있다.

- [0018] 파인 지연부(14)는 복수개의 직렬 연결된 제2 지연 셀들(미도시)을 포함하며, 파인 지연 코드(fcode)에 응답하여 파인 지연부(14)의 지연 시간이 가변될 수 있다. 파인 지연부(14)는 제1 클럭신호(CLK1)를 파인 지연부(14)의 지연 시간만큼 지연하여 제2 클럭신호(CLK2)를 발생할 수 있다.

- [0019] 클럭신호 지연 경로부(16)는 더미 지연부일 수 있다. 클럭신호 지연 경로부(16)는 제2 클럭신호(CLK2)를 클럭신호 지연 경로부(16)의 지연 시간만큼 지연하여 출력 클럭신호(OCLK)를 발생할 수 있다. 출력 클럭신호(OCLK)는 입력 클럭신호(ICLK)에 동기된 클럭신호일 수 있다.

- [0020] 코스 지연 제어부(20)는 기준 클럭신호(RCLK)와 피드백 클럭신호(FCLK)를 이용하여 코스 지연 코드(ccode)를 발생할 수 있다. 코스 지연 제어부(20)는 기준 클럭신호(RCLK)와 피드백 클럭신호(FCLK)를 입력하여 기준 클럭신호(RCLK)의 천이 시점(상승 천이 또는 하강 천이 시점)과 기준 클럭신호(RCLK)의 천이 시점(상승 천이 또는 하강 천이 시점) 보다 (1 클럭 사이클 이전 내에) 앞서서 발생되는 피드백 클럭신호(FCL)의 천이 시점(상승 천이 또는 하강 천이) 사이의 시간을 검출하여 코스 지연 코드(ccode)를 발생할 수 있다.

- [0021] 파인 지연 제어부(22)는 기준 클럭신호(RCLK)의 위상과 피드백 클럭신호(FCLK)의 위상을 비교하여 파인 지연 코드(fcode)를 발생할 수 있다. 파인 지연 제어부(22)는 코스 지연 제어부(20)에 의한 코스 동기 동작이 수행된 후 파인 동기 동작을 수행할 수 있다.

- [0022] 클럭신호 지연 레플리카부(24)는 제2 클럭신호(CLK2)를 지연 시간(예를 들면, 클럭신호 입력버퍼(10)의 지연 시간 + 클럭신호 지연 경로부(16)의 지연 시간)만큼 지연하여 피드백 클럭신호(FCLK)를 발생할 수 있다.

- [0023] 도 2는 본 개시에 따른 실시예의 코스 지연 제어부의 구성을 나타내는 블록도로서, 코스 지연 제어부(20)는 피

드백 클럭신호 우선 발생기(20-2), 및 코스 지연 코드 발생기(20-4)를 포함할 수 있다.

- [0024] 도 2에 도시된 블록들 각각의 기능을 설명하면 다음과 같다.

- [0025] 피드백 클럭신호 우선 발생기(20-2)는 기준 클럭신호(RCLK)의 천이(상승 천이 또는 하강 천이)와 기준 클럭신호 (RCLK)의 천이(상승 천이 또는 하강 천이) 보다 (1 클럭 사이클 이전 내에) 앞서서 발생되는 피드백 클럭신호 (FCL)의 천이(상승 천이 또는 하강 천이)를 검출하여 분주된 기준 클럭신호(RCLK\_N) 및 분주된 피드백 클럭신호 (FCLK\_N)를 발생할 수 있다.

- [0026] 코스 지연 코드 발생기(20-4)는 분주된 피드백 클럭신호(FCLK\_N)의 천이 시점(상승 천이 또는 하강 천이 시점) 과 분주된 기준 클럭신호(RCLK\_N)의 천이 시점(상승 천이 또는 하강 천이 시점) 사이의 시간을 검출하여 코스지연 코드(ccode)를 발생할 수 있다.

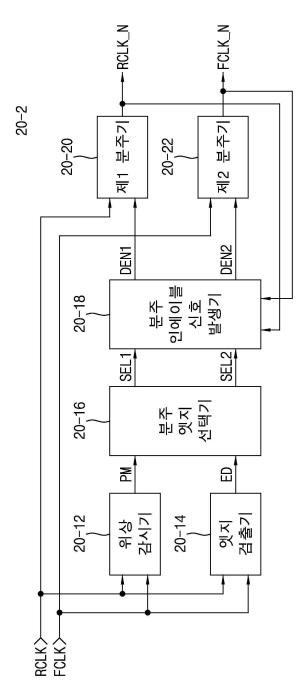

- [0027] 도 3은 본 개시에 따른 실시예의 피드백 클럭신호 우선 발생기의 구성을 나타내는 블록도로서, 피드백 클럭신호 우선 발생기(20-2)는 위상 감시기(20-12), 엣지 검출기(20-14), 분주 엣지 선택기(20-16), 분주 인에이블 신호 발생기(20-18), 제1 분주기(20-20), 및 제2 분주기(20-22)를 포함할 수 있다.

- [0028] 도 3에 도시된 블록들 각각의 기능을 설명하면 다음과 같다.

- [0029] 위상 감시기(20-12)는 기준 클럭신호(RCLK)와 피드백 클럭신호(FCLK)를 입력하여 위상 감시신호(PM)를 발생할 수 있다. 위상 감시기(20-12)는 피드백 클럭신호(FCLK)의 상승 천이에서 기준 클럭신호(RCLK)의 레벨(예를 들면, "하이" 레벨)을 검출하여 위상 감시신호(PM)를 활성화할 수 있다.

- [0030] 엣지 검출기(20-14)는 기준 클럭신호(RCLK)와 피드백 클럭신호(FCLK)를 입력하여 엣지 검출신호(ED)를 발생할수 있다. 엣지 검출기(20-14)는 피드백 클럭신호(FCLK)의 상승 천이 동안 기준 클럭신호(RCLK)의 하강 천이를 검출하여 엣지 검출신호(ED)를 활성화할 수 있다.

- [0031] 분주 엣지 선택기(20-16)는 위상 감시신호(PM) 또는 엣지 검출신호(ED)가 활성화되면, 피드백 클럭신호(FCLK)의 상승 천이에 응답하여 제1 선택신호(SEL1)를 활성화하고, 기준 클럭신호(RCLK)의 상승 천이에 응답하여 제1 선택신호(SEL1)를 입력하여 제2 선택신호(SEL2)를 활성화할 수 있다. 분주 엣지 선택기(20-16)는 위상 감시신호 (PM) 및 엣지 검출신호(ED)가 모두 비활성화되면, 피드백 클럭신호(FCLK)의 하강 천이에 응답하여 제1 선택신호(SEL1)를 활성화하고, 기준 클럭신호(RCLK)의 상승 천이에 응답하여 제1 선택신호(SEL1)를 입력하여 제2 선택신호(SEL2)를 활성화할 수 있다.

- [0032] 분주 인에이블 신호 발생기(20-18)는 분주된 피드백 클럭신호(FCLK\_N)에 응답하여 제1 선택신호(SEL1)를 입력하여 제1 인에이블 신호(DEN1)를 활성화하고, 위상 감시신호(PM) 또는 엣지 검출신호(ED)가 활성화되는 경우에 제2 선택신호(SEL2)를 입력하고, 위상 감시신호(PM) 및 엣지 검출신호(ED)가 모두 비활성화되면, 제1 선택신호 (SEL1)를 입력하여 분주된 기준 클럭신호(RCLK\_N)에 응답하여 제2 인에이블 신호(DEN2)를 활성화할 수 있다. 분주 인에이블 신호 발생기(20-18)는 제1 인에이블 신호(DEN1)를 제2 인에이블 신호(DEN2) 보다 먼저 활성화하거나 동일한 시점에 활성화할 수 있다.

- [0033] 제1 분주기(20-20)는 제1 인에이블 신호(DEN1)에 응답하여 인에이블되고 피드백 클럭신호(FCLK)를 분주하여 분주된 피드백 클럭신호(FCLK\_N)를 발생할 수 있다.

- [0034] 제2 분주기(20-22)는 제2 인에이블 신호(DEN2)에 응답하여 인에이블되고 기준 클럭신호(RCLK)를 분주하여 분주된 기준 클럭신호(RCLK\_N)를 발생할 수 있다.

- [0035] 즉, 피드백 클럭신호 우선 발생기(20-2)는 기준 클럭신호(RCLK)의 상승 천이와 기준 클럭신호(RCLK)의 상승 천이 보다 (1 클럭 사이클 이전 내에) 앞서서 발생되는 피드백 클럭신호(FCL)의 상승 천이를 검출하여 분주된 기준 클럭신호(RCLK\_N) 및 분주된 피드백 클럭신호(FCLK\_N)를 발생할 수 있다.

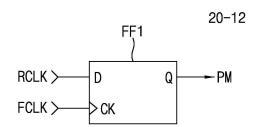

- [0036] 도 4는 본 개시에 따른 실시예의 위상 감시기의 구성을 나타내는 것으로, 위상 감시기(20-12)는 제1 플립플롭 (FF1)을 포함할 수 있다.

- [0037] 도 4를 참조하면, 제1 플립플롭(FF1)은 피드백 클럭신호(FCLK)의 상승 천이에 응답하여 기준 클럭신호(RCLK)를 래치하여 위상 감시신호(PM)를 발생할 수 있다. 제1 플립플롭(FF1)는 피드백 클럭신호(FCLK)의 상승 천이에 응답하여 기준 클럭신호(RCLK)가 "하이"레벨이면 "하이"레벨의 위상 감시신호(PM)를 발생하고, "로우"레벨이면, "로우"레벨의 위상 감시신호(PM)를 발생할 수 있다.

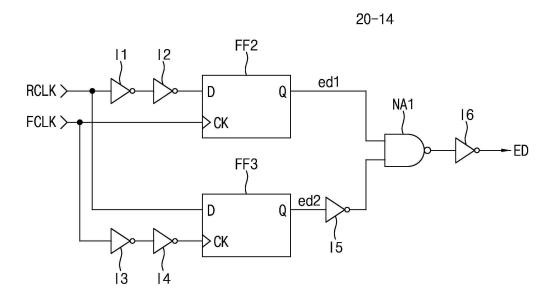

- [0038] 도 5는 본 개시에 따른 실시예의 엣지 검출기의 구성을 나타내는 것으로, 엣지 검출기(20-14)는 제2 및 제3 플립플롭들(FF2, FF3), 제1 내지 제6 인버터들(I1 ~ I6), 및 NAND 게이트(NA)를 포함할 수 있다.

- [0039] 도 5를 참조하면, 제1 및 제2 인버터들(I1, I2)은 기준 클럭신호(RCLK)를 제1 소정 시간 만큼 지연하여 지연된 기준 클럭신호를 발생할 수 있다. 제3 및 제4 인버터들(I3, I4)은 피드백 클럭신호(FCLK)를 제2 소정 시간 만큼 지연하여 지연된 피드백 클럭신호를 발생할 수 있다. 제1 소정 시간 및 제2 소정 시간은 서로 동일하거나 유사할 수 있다. 제2 플립플롭(FF2)은 피드백 클럭신호(FCLK)의 상승 천이에 응답하여 "하이"레벨의 지연된 기준 클럭신호를 래치하여 "하이"레벨의 제1 검출신호(ed1)를 발생할 수 있다. 제3 플립플롭(FF3)은 지연된 피드백 클럭신호의 상승 천이에 응답하여 "로우"레벨의 기준 클럭신호(RCLK)를 래치하여 "로우"레벨의 제2 검출신호(ed2)를 발생할 수 있다. 제5 인버터(I5)는 "로우"레벨의 제2 검출신호(ed2)를 반전하여 "하이"레벨의 비전된 제2 검출신호(ed2)를 발생할 수 있다. NAND 게이트(NA) 및 제6 인버터(I6)는 "하이"레벨의 제1 검출신호(ed1) 및 "하이"레벨의 반전된 제2 검출신호(ed2)를 논리곱하여 "하이"레벨의 엣지 검출신호(ED)를 발생할 수 있다.

- [0040] 즉, 엣지 검출기(20-14)는 기준 클럭신호(RCLK)가 하강 천이하는 동안 피드백 클럭신호(FCLK)가 상승 천이하는 것을 검출하여 "하이"레벨의 엣지 검출신호(ED)를 발생할 수 있다.

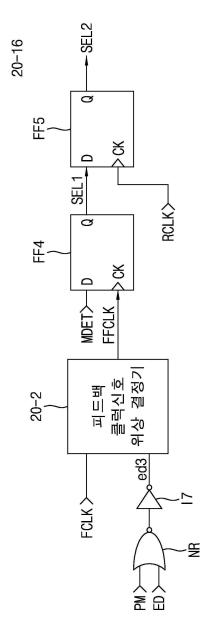

- [0041] 도 6은 본 개시에 따른 실시예의 분주 엣지 선택기의 구성을 나타내는 것으로, 분주 엣지 선택기(20-16)는 NOR 게이트(NR), 제7 인버터(I7), 피드백 클럭신호 위상 결정기(20-26), 및 제4 및 제5 플립플롭들(FF4, FF5)을 포함할 수 있다.

- [0042] 도 6을 참조하면, NOR 게이트(NR) 및 제7 인버터(I7)는 "하이"레벨의 위상 감시신호(PM) 또는 "하이"레벨의 엣지 검출신호(ED)가 입력되면 "하이"레벨의 제3 검출신호(ed3)를 발생하고, 모두 "로우"레벨인 위상 감시신호(PM) 및 엣지 검출신호(ED)가 입력되면 "로우"레벨의 제3 검출신호(ed3)를 발생한 수 있다. 피드백 클럭신호 위상 결정기(20-26)는 "하이"레벨의 제3 검출신호(ed3)에 응답하여 피드백 클럭신호(FCLK)의 위상과 동일한 위상을 가지는 중간 피드백 클럭신호(FFCLK)를 발생하고, "로우"레벨의 제3 검출신호(ed3)에 응답하여 피드백 클럭신호(FCLK)의 위상과 반대 위상을 가지는 중간 피드백 클럭신호(FFCLK)를 발생할 수 있다. 제4 플립플롭(FF4)은 중간 피드백 클럭신호(FFCLK)의 상승 천이에 응답하여 "하이"레벨의 코스 동기 인에이블 신호(MDED)를 래치하여 "하이"레벨의 제1 선택신호(SEL1)를 발생할 수 있다. 코스 동기 인에이블 신호(MDED)는 코스 동기 동작 동안 "하이"레벨의 제1 선택신호(SEL1)를 래치하여 "하이"레벨의 제2 선택신호(SEL2)를 발생할 수 있다.

- [0043] 즉, 분주 엣지 선택기(20-16)는 "하이"레벨의 위상 감시신호(PM) 또는 "하이"레벨의 엣지 검출신호(ED)가 발생되면, 피드백 클럭신호(FCLK)의 상승 천이에 응답하여 "하이"레벨의 제1 선택신호(SEL1)를 발생하고, 기준 클럭신호(RCLK)의 상승 천이에 응답하여 "하이"레벨의 제2 선택신호(SEL2)를 발생할 수 있다. 분주 엣지 선택기(20-16)는 "로우"레벨의 위상 감시신호(PM) 및 "로우"레벨의 엣지 검출신호(ED)가 발생되면, 피드백 클럭신호(FCLK)의 하강 천이에 응답하여 "하이"레벨의 제1 선택신호(SEL1)를 발생하고, 기준 클럭신호(RCLK)의 상승 천이에 응답하여 "하이"레벨의 제2 선택신호(SEL2)를 발생할 수 있다.

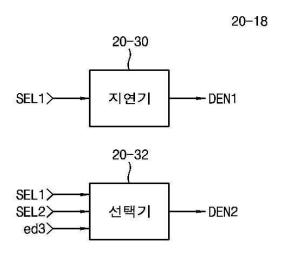

- [0044] 도 7은 본 개시에 따른 실시예의 분주 인에이블 신호 발생기의 구성을 나타내는 것으로, 분주 인에이블 신호 발생기(20-18)는 지연기(20-30) 및 선택기(20-32)를 포함할 수 있다.

- [0045] 도 7을 참조하면, 지연기(20-30)는 "하이" 레벨의 제1 선택신호(SEL1)를 소정 시간 만큼 지연하여 "하이" 레벨의 제1 인에이블 신호(DEN1)를 발생할 수 있다. 선택기(20-32)는 "하이" 레벨의 제3 검출 신호(ed3)가 발생되면, "하이" 레벨의 제2 선택신호(SEL2)를 선택하여 소정 시간 만큼 지연하고, "로우" 레벨의 제3 검출 신호(ed3)가 발생되면, "하이" 레벨의 제1 선택신호(SEL1)를 선택하여 소정 시간 만큼 지연하여 "하이" 레벨의 제2 인에이블 신호(DEN2)를 발생할 수 있다.

- [0046] 즉, 분주 인에이블 신호 발생기(20-18)는 "하이" 레벨의 위상 감시신호(PM) 또는 "로우" 레벨의 엣지 검출신호(ED)가 발생되면, "하이" 레벨의 제1 선택신호(SEL1)를 입력하여 "하이" 레벨의 제1 인에이블 신호(DEN1)를 발생하고, "하이" 레벨의 제2 선택신호(SEL2)를 입력하여 "하이" 레벨의 제2 인에이블 신호(DEN2)를 발생할수 있다. 또한, 분주 인에이블 신호 발생기(20-18)는 모두 "로우" 레벨인 위상 감시신호(PM) 및 엣지 검출신호(ED)가 발생되면, "하이" 레벨의 제1 선택신호(SEL1)를 입력하여 "하이" 레벨의 제1 인에이블 신호(DEN1) 및 "하이" 레벨의 제2 인에이블 신호(DEN2)를 발생할수 있다.

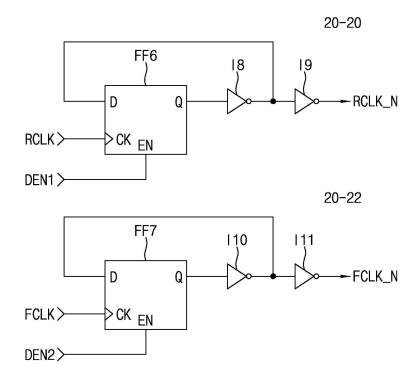

- [0047] 도 8은 본 개시에 따른 실시예의 제1 분주기 및 제2 분주기의 구성을 나타내는 것으로, 제1 분주기(20-20)는 제 6 플립플롭(FF6), 및 제8 및 제9 인버터들(I8, I9)을 포함하고, 제2 분주기(20-22)는 제7 플립플롭(FF7), 및 제10 및 제11 인버터들(I10, I11)을 포함할 수 있다.

- [0048] 도 8을 참조하면, 제6 플립플롭(FF6)은 "로우"레벨의 제1 인에이블 신호(DEN1)에 응답하여 리셋되고, "하이"레벨의 제1 인에이블 신호(DEN1)에 응답하여 인에이블될 수 있다. 마찬가지로, 제7 플립플롭(FF7)은 "로우"레벨의 제2 인에이블 신호(DEN2)에 응답하여 리셋되고, "하이"레벨의 제2 인에이블 신호(DEN2)에 응답하여 인에이블될 수 있다.

- [0049] 도 8을 참조하면, 제6 플립플롭(FF6), 및 제8 및 제9 인버터들(I8, I9)은 기준 클럭신호(RCLK)의 상승 천이에 응답하여 제8 인버터(I8)의 출력신호를 래치하여 분주된 기준 클럭신호(RCLK\_N)를 발생할 수 있다. 제7 플립플롭(FF7), 및 제10 및 제11 인버터들(I10, I11)은 피드백 클럭신호(FCLK\_N)의 상승 천이에 응답하여 제10 인버터 (I10)의 출력신호를 래치하여 분주된 피드백 클럭신호(FCLK\_N)를 발생할 수 있다.

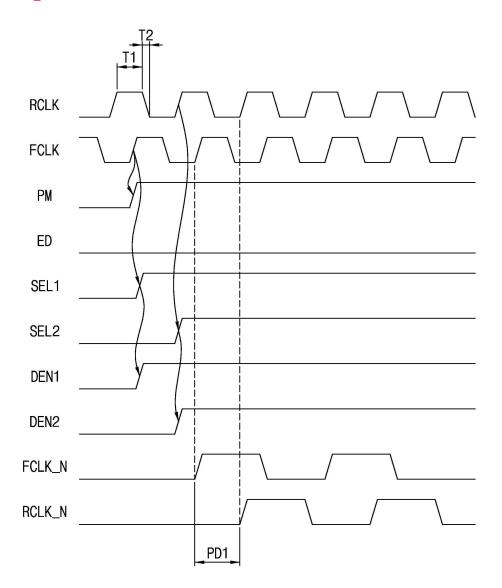

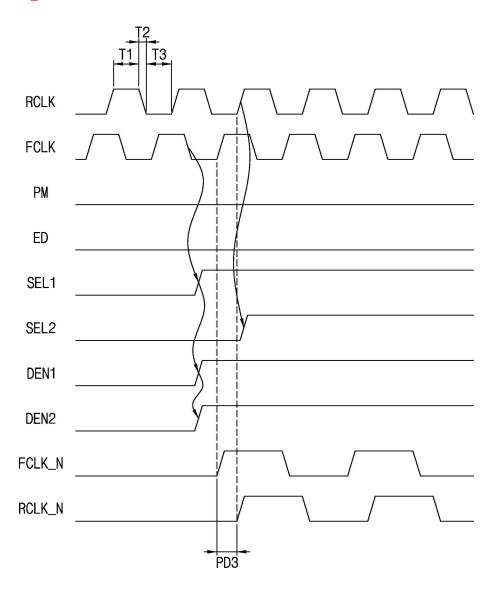

- [0050] 도 9는 본 개시에 따른 실시예의 피드백 클럭신호 우선 발생기의 동작을 설명하기 위한 동작 타이밍도로서, 기준 클럭신호(RCLK)의 "하이"레벨 기간(T1)에서 피드백 클럭신호(FCLK)가 상승 천이하는 경우의 피드백 클럭신호 우선 발생기(20-2)의 동작을 나타내는 동작 타이밍도이다.

- [0051] 도 1 내지 도 9를 참조하면, 위상 감시기(20-12)는 피드백 클럭신호(FCLK)의 상승 천이에 응답하여 기준 클럭신호(RCLK)의 "하이"레벨을 래치하여 "하이"레벨의 위상 감시신호(PM)를 발생할 수 있다. 위상 감시기(20-12)는 기준 클럭신호(RCLK)의 "하이"레벨 기간(T1) 내에서 피드백 클럭신호(FCLK)가 상승 천이하면 위상 감시신호(PM)를 활성화할 수 있다.

- [0052] 옛지 검출기(20-14)는 기준 클럭신호(RCLK)의 하강 천이 기간(T2) 내에서 피드백 클럭신호(FCLK)가 상승 천이하지 않으므로 "로우"레벨의 엣지 검출신호(ED)를 발생할 수 있다.

- [0053] 분주 엣지 선택기(20-16)는 "하이" 레벨의 위상 감시신호(PM)가 발생되면, 피드백 클럭신호(FCLK)의 상승 천이에 응답하여 "하이"레벨의 제1 선택신호(SEL1)를 발생하고, 기준 클럭신호(RCLK)의 상승 천이에 응답하여 "하이"레벨의 제1 선택신호(SEL1)를 입력하여 "하이"레벨의 제2 선택신호(SEL2)를 발생할 수 있다.

- [0054] 분주 인에이블 신호 발생기(20-18)는 분주된 피드백 클럭신호(FCLK\_N)의 "로우"레벨에 응답하여 "하이"레벨의 제1 선택신호(SEL1)를 입력하여 "하이"레벨의 제1 인에이블 신호(DEN1)를 발생하고, "하이"레벨의 위상 감시신호(PM) 또는 "하이"레벨의 엣지 검출신호(ED)에 응답하여(도시하지는 않았지만, "하이"레벨의 제3 검출신호(ed3)에 응답하여) "하이"레벨의 제2 선택신호(SEL2)를 입력하고 분주된 기준 클럭신호(RCLK\_N)의 "로우"레벨에 응답하여 "하이"레벨의 제2 인에이블 신호(DEN2)를 발생할 수 있다.

- [0055] 제1 분주기(20-20)는 "하이"레벨의 제1 인에이블 신호(DEN1)에 응답하여 인에이블되어 피드백 클럭신호(FCL K)를 분주하여 분주된 피드백 클럭신호(FCLK\_N)를 발생할 수 있다.

- [0056] 제2 분주기(20-22)는 "하이" 레벨의 제2 인에이블 신호(DEN2)에 응답하여 인에이블되어 기준 클럭신호(RCLK)를 분주하여 분주된 기준 클럭신호(RCLK\_N)를 발생할 수 있다.

- [0057] 도 1 내지 도 9를 참조하면, 코스 지연 코드 발생기(20-4)는 분주된 기준 클럭신호(RCLK\_N)의 상승 천이 시점과 분주된 피드백 클럭신호(FCLK\_N)의 상승 천이 시점 사이의 펄스폭(PD1)을 검출하여 코스 지연 코드(ccode)를 발생할 수 있다.

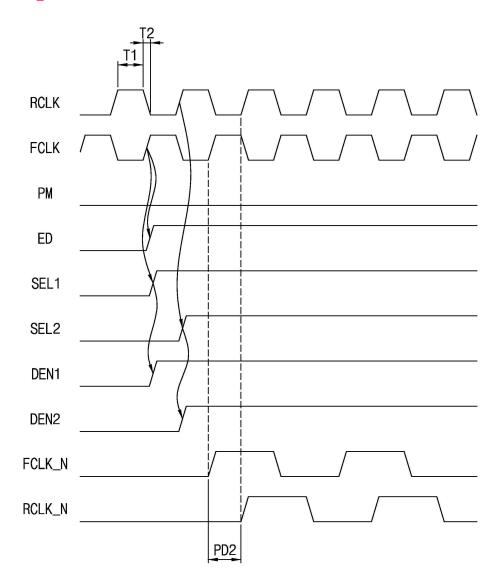

- [0058] 도 10은 본 개시에 따른 실시예의 피드백 클럭신호 우선 발생기의 동작을 설명하기 위한 동작 타이밍도로서, 기준 클럭신호(RCLK)가 하강 천이하는 기간(T2)에서 피드백 클럭신호(FCLK)가 상승 천이하는 경우의 피드백 클럭신호 우선 발생기(20-2)의 동작을 나타내는 동작 타이밍도이다.

- [0059] 도 1 내지 8, 및 도 10을 참조하면, 위상 감시기(20-12)는 피드백 클럭신호(FCLK)의 상승 천이에 응답하여 기준 클럭신호(RCLK)가 "로우" 레벨이므로 "로우" 레벨의 위상 감시신호(PM)를 발생할 수 있다.

- [0060] 엣지 검출기(20-14)는 기준 클럭신호(RCLK)의 하강 천이 기간(T2) 내에서 피드백 클럭신호(FCLK)가 상승 천이하는 것을 검출하여 "하이"레벨의 엣지 검출신호(ED)를 발생할 수 있다.

- [0061] 이 후, 분주 엣지 선택기(20-16), 분주 인에이블 신호 발생기(20-18), 제1 분주기(20-20), 및 제2 분주기(20-22)의 동작은 상술한 도 9의 동작과 동일할 수 있다.

- [0062] 도 1 내지 도 8, 및 도 10을 참조하면, 코스 지연 코드 발생기(20-4)는 분주된 피드백 클럭신호(FCLK\_N)의 상승 천이 시점과 분주된 기준 클럭신호(RCLK\_N)의 상승 천이 시점 사이의 펄스폭(PD2)을 검출하여 코스 지연 코드 (ccode)를 발생할 수 있다.

- [0063] 도 11은 본 개시에 따른 실시예의 피드백 클럭신호 우선 발생기의 동작을 설명하기 위한 동작 타이밍도로서, 기준 클럭신호(RCLK)의 "로우"레벨 기간(T3)에서 피드백 클럭신호(FCLK)가 상승 천이하는 경우의 피드백 클럭신호 우선 발생기(20-2)의 동작을 나타내는 동작 타이밍도이다.

- [0064] 도 1 내지 도 8, 및 도 11을 참조하면, 위상 감시기(20-12)는 피드백 클럭신호(FCLK)의 상승 천이에 응답하여 기준 클럭신호(RCLK)의 "로우"레벨을 래치하여 "로우"레벨의 위상 감시신호(PM)를 발생할 수 있다.

- [0065] 옛지 검출기(20-14)는 기준 클럭신호(RCLK)의 하강 천이 기간(T2) 내에서 피드백 클럭신호(FCLK)가 상승 천이하지 않으므로 "로우"레벨의 엣지 검출신호(ED)를 발생할 수 있다.

- [0066] 분주 엣지 선택기(20-16)는 "로우"레벨의 위상 감시신호(PM) 및 "로우"레벨의 엣지 검출신호(ED)가 발생되면, 피드백 클럭신호(FCLK)의 하강 천이에 응답하여 "하이"레벨의 제1 선택신호(SEL1)를 발생하고, 기준 클럭신호(RCLK)의 상승 천이에 응답하여 "하이"레벨의 제1 선택신호(SEL1)를 입력하여 "하이"레벨의 제2 선택신호(SEL2)를 활성화할 수 있다.

- [0067] 분주 인에이블 신호 발생기(20-18)는 분주된 피드백 클럭신호(FCLK\_N)의 "로우"레벨에 응답하여 "하이"레벨의 제1 선택신호(SEL1)를 입력하여 "하이"레벨의 제1 인에이블 신호(DEN1)를 발생하고, 모두 "로우"레벨인 위상 감시신호(PM) 및 엣지 검출신호(ED)에 응답하여(도시하지는 않았지만, "로우"레벨의 제3 검출신호(ed3)에 응답하여) "하이"레벨의 제1 선택신호(SEL1)를 입력하고 분주된 기준 클럭신호(RCLK\_N)의 "로우"레벨에 응답하여 제2 인에이블 신호(DEN2)를 발생할 수 있다.

- [0068] 제1 분주기(20-20) 및 제2 분주기(20-22)의 동작은 상술한 도 9의 동작과 동일할 수 있다.

- [0069] 도 2 및 도 11을 참조하면, 코스 지연 코드 발생기(20-4)는 분주된 피드백 클럭신호(FCLK\_N)의 상승 천이 시점 과 분주된 기준 클럭신호(RCLK\_N)의 상승 천이 시점 사이의 펄스폭(PD3)을 검출하여 코스 지연 코드(ccode)를 발생할 수 있다.

- [0070] 도 1 내지 도 8, 및 도 9 내지 도 11을 참조하면, 피드백 클럭신호 우선 발생기(20-2)는 기준 클럭신호(RCLK)의 상승 천이 시점과 기준 클럭신호(RCLK)의 상승 천이 시점 보다 (1 클럭 사이클 이전 내에) 앞서서 발생되는 피드백 클럭신호(FCLK)의 상승 천이 시점을 검출하여 분주된 기준 클럭신호(RCLK\_N) 및 분주된 피드백 클럭신호(RCLK\_N)를 발생할 수 있다. 이에 따라, 코스 지연 코드 발생기(20-4)는 기준 클럭신호(RCLK)의 상승 천이 시점과 피드백 클럭신호(FCLK)의 상승 천이 시점 사이의 시간을 정확하게 검출할 수 있다.

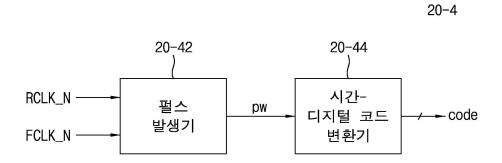

- [0071] 도 12는 본 개시에 따른 실시예의 코스 지연 코드 발생기의 구성을 나타내는 블록도로서, 코드 지연 코드 발생기(20-4)는 펄스 발생기(20-42) 및 시간 -디지털 코드 변환기(20-44)를 포함할 수 있다.

- [0072] 도 12를 참조하면, 펄스 발생기(20-42)는 분주된 기준 클럭신호(RCLK\_N)의 상승 천이 시점과 분주된 피드백 클럭신호(FCLK\_N)의 상승 천이 시점 사이의 시간을 검출하여 펄스 신호(PW)를 발생할 수 있다. 도 9 내지 도 11 및 도 12를 참조하면, 펄스 발생기(20-42)는 분주된 기준 클럭신호(RCLK\_N)의 상승 천이 시점과 분주된 피드백 클럭신호(FCLK\_N)의 상승 천이 시점 사이의 펄스폭(PD1, PD2, 또는 PD3)을 가진 펄스 신호(PW)를 발생할 수 있다.

- [0073] 도 12를 참조하면, 시간-디지털 코드 변환기(20-44)는 필스 신호(PW)의 필스폭에 해당하는 시간을 디지털 코드로 변환하여 코스 지연 코드(ccode)를 발생할 수 있다.

- [0074] 도 13은 본 개시에 따른 실시예의 파인 지연 제어부의 구성을 나타내는 블록도로서, 파인 지연 제어부(22)는 위상 비교기(22-2) 및 파인 지연 코드 발생기(22-4)를 포함할 수 있다.

- [0075] 도 13을 참조하면, 위상 비교기(22-2)는 코스 동기 동작이 수행된 후, 기준 클럭신호(RCLK)의 위상 피드백 클럭 신호(FCLK)의 위상을 비교하여 비교 결과에 따라 업 신호(UP) 또는 다운 신호(DN)를 발생할 수 있다. 파인 지연 코드 발생기(22-4)는 업 신호(UP) 또는 다운 신호(DN)에 기초하여 카운팅 동작을 수행하여 파인 지연 코드 (fcode)를 발생할 수 있다.

- [0076] 도 14는 본 개시에 따른 실시예의 반도체 메모리 장치를 나타내는 블록도로서, 반도체 메모리 장치(300)는 초기화부(30), 지연 동기 루프 회로(32), 명령 및 어드레스 발생기(34), 모드 설정 레지스터(36), 레이턴시 제어부

(38), 로우 어드레스 디코더(40), 컬럼 어드레스 디코더(42), 메모리 셀 어레이(44), 데이터 리드 경로부(46), 데이터 라이트 경로부(48), 데이터(DQ) 출력버퍼(50), DQ 입력버퍼(52), 데이터 스트로우브 신호(DQS) 출력버퍼(54), 및 DQS 입력버퍼(56)를 포함할 수 있다.

- [0077] 도 14에 도시된 블록들 각각의 기능을 설명하면 다음과 같다.

- [0078] 초기화부(30)는 외부로부터 공급되는 외부 전원전압(EV)이 목표 전압 레벨에 도달한 후 외부로부터 "하이"레벨로 천이하는 리셋 신호(Reset\_n)가 인가되면 초기화 신호(init)를 발생할 수 있다.

- [0079] 지연 동기 루프 회로(32)는 초기화 신호(init) 및 지연 동기 루프 인에이블 신호(DLL\_EN)에 응답하여 코스 동기 동작 및 파인 동기 동작을 수행하여 외부로부터 인가되는 외부 클럭신호(CK)에 동기된 피드백 클럭신호(FCLK)를 발생할 수 있다. 지연 동기 루프 회로(32)는 초기화 신호(init)와 무관하게 지연 동기 루프 인에이블 신호 (DLL\_EN)가 발생할 때마다 코스 동기 동작 및 파인 동기 동작을 수행할 수 있다. 지연 동기 루프 회로(32)는 도 1 내지 도 13을 참조하여 설명한 구성을 가지고 동작을 수행할 수 있다. 외부 클럭신호(CK)는 도 1의 입력 클럭신호(ICLK)이고, 데이터 스트로우브 신호(DQS)는 도 1의 출력 클럭신호(OCLK)일 수 있다. 도 1의 클럭신호 지연 레플리카부(24)는 도 1의 클럭신호 입력버퍼(10)의 지연 시간 + DQS 출력버퍼(54)의 지연 시간만큼 피드백 클럭신호(FCLK)를 지연할 수 있다.

- [0080] 명령 및 어드레스 발생기(34)는 클럭신호(CK)에 응답하여 명령 및 어드레스(CA)를 디코딩하여 모드 설정 명령 (MRS), 액티브 명령(ACT), 리드 명령(RD), 및 라이트 명령(WR)을 발생할 수 있다. 또한, 명령 및 어드레스 발생 기(34)는 모드 설정 명령(MRS)에 응답하여 명령 및 어드레스(CA)에 포함된 어드레스 신호를 모드 설정 코드 (OPC)를 발생하고, 액티브 명령(ACT)에 응답하여 명령 및 어드레스(CA)에 포함된 어드레스 신호를 로우 어드레스(RA)로 발생하고, 리드 명령(RD) 또는 라이트 명령(WR)에 응답하여 명령 및 어드레스(CA)에 포함된 어드레스 신호를 컬럼 어드레스(CA)로 발생할 수 있다.

- [0081] 모드 설정 레지스터(36)는 모드 설정 명령(MRS)에 응답하여 모드 설정 코드(OPC)를 저장하여 지연 동기 루프 인에이블 신호(DLL\_EN), 리드 레이턴시(RL), 및 버스트 길이(BL)를 설정할 수 있다. 모드 설정 레지스터(36)는 모드 설정 코드(OPC)를 입력하여 지연 동기 루프 인에이블 신호(DLL\_EN)를 활성화할 수 있다.

- [0082] 레이턴시 제어부(38)는 리드 명령(RD)이 인가되면 제2 클럭신호(CLK2)를 이용하여 리드 레이턴시(RL)의 값에 해당하는 클럭 사이클의 수 만큼 지연한 후에 활성화되고, 리드 레이턴시(RL)의 값에 해당하는 클럭 사이클의 수 + 버스트 길이(BL)의 값에 해당하는 클럭 사이클의 수 만큼 지연한 후에 비활성화되는 레이턴시 신호(LA)를 발생할 수 있다. 레이턴시 제어부(38)는 리드 명령(RD)에 응답하여 제2 클럭신호(CLK2), 리드 레이턴시(RL), 및 버스트 길이(BL)를 이용하여 DQ 출력버퍼(50)를 통하여 데이터(DQ)가 출력되는 동안 활성화되는 레이턴시 신호(LA)를 발생할 수 있다.

- [0083] 로우 어드레스 디코더(40)는 로우 어드레스(RA)를 디코딩하여 복수개의 워드 라인 선택신호들(wl)을 발생할 수 있다.

- [0084] 컬럼 어드레스 디코더(42)는 컬럼 어드레스(CA)를 디코딩하여 복수개의 컬럼 선택신호 라인들(csl)을 발생할 수 있다.

- [0085] 메모리 셀 어레이(44)는 복수개의 워드라인 선택신호들에 의해서 선택되는 복수개의 워드라인들과 복수개의 컬 럼 선택신호들에 의해서 선택되는 복수개의 비트라인들 사이에 연결된 복수개의 메모리 셀들(미도시)을 포함할수 있다. 메모리 셀 어레이(36)는 리드 명령(RD)에 응답하여 복수개의 워드라인 선택신호들(wl)과 복수개의 컬럼 선택신호들(csl)에 의해서 선택된 메모리 셀들로부터 데이터를 출력하고, 라이트 명령(WR)에 응답하여 복수개의 워드라인 선택신호들(wl)과 복수개의 컬럼 선택신호들(csl)에 의해서 선택된 메모리 셀들로 데이터를 입력할수 있다.

- [0086] 데이터 리드 경로부(46)는 메모리 셀 어레이(44)로부터 출력되는 데이터를 래치하고, 레이턴시 신호(LA)의 활성화 기간 동안 제2 클럭신호(CLK2)에 응답하여 데이터(D0)를 출력할 수 있다.

- [0087] 데이터 라이트 경로부(48)는 내부 데이터 스트로우브 신호(dqs)에 응답하여 데이터(D1)를 래치하고, 메모리 셀어레이(44)로 데이터를 출력할 수 있다.

- [0088] DQ 출력버퍼(50)는 데이터(D0)를 버퍼하여 데이터(DQ)를 발생할 수 있다.

- [0089] DQ 입력버퍼(52)는 외부로부터 수신되는 데이터(DQ)를 버퍼하여 데이터(DI)를 발생할 수 있다.

[0090] DQS 출력버퍼(54)는 레이턴시 신호(LA)의 활성화 기간 동안 제2 클럭신호(CLK2)를 버퍼하여 외부 클럭신호(CK)에 동기된 데이터 스트로우브 신호(DQS)를 발생할 수 있다.

[0091] DQS 입력버퍼(56)는 외부로부터 수신되는 데이터 스트로우브 신호(DQS)를 버퍼하여 내부 데이터 스트로우브 신호(das)를 발생할 수 있다.

[0092] 상술한 실시예들에서, 기준 클럭신호(RCLK)의 상승 천이 및 피드백 클럭신호(FCLK)의 상승 천이는 기준 클럭신호(RCLK)의 하강 천이 및 피드백 클럭신호(FCLK)의 하강 천이일 수 있고, 기준 클럭신호(RCLK)의 하강 천이 및 피드백 클럭신호(FCLK)의 하강 천이는 기준 클럭신호(RCLK)의 상승 천이 및 피드백 클럭신호(FCLK)의 상승 천이일 수 있다.

[0093] 이상, 첨부된 도면을 참조하여 본 발명의 기술적 사상에 따른 실시예들을 설명하였지만, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자는 본 발명이 그 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해하여야 한다.

### 부호의 설명

[0094] 100, 32: 지연 동기 루프 회로 10: 클럭신호 입력버퍼

12: 코스 지연부 14: 파인 지연부

16: 클럭신호 지연 경로부 20: 코스 지연 제어부

22: 파인 지연 제어부 24: 클럭신호 지연 레플리카부

20-2: 피드백 클럭신호 우선 발생기 20-4: 코스 지연 코드 발생기

20-12: 위상 감시기 20-14: 엣지 검출기

20-16: 분주 엣지 선택기 20-18: 분주 인에이블 신호 발생기

20-20: 제1 분주기 20-22: 제2 분주기

FF1 ~ FF7: 제1 내지 제7 플립플롭 20-26: 피드백 클럭신호 위상 결정기

20-30: 지연기 20-32: 선택기

20-42: 펄스 발생기 20-44: 시간-디지털 코드 변환기

22-2: 위상 비교기 22-4: 파인 지연 코드 발생기

300: 반도체 메모리 장치 30: 초기화부

34: 명령 및 어드레스 발생기 36: 모드 설정 레지스터

38: 레이턴시 제어부 40: 로우 어드레스 디코더

42: 메모리 셀 어레이 44: 컬럼 어드레스 디코더

46: 데이터 리드 경로부 48: 데이터 라이트 경로부

50: 데이터 출력버퍼 52: 데이터 입력버퍼

54: 데이터 스트로우브 신호 출력버퍼 56: 데이터 스트로우브 신호 입력버퍼

# 도면1

22

도면13