(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6022012号

(P6022012)

(45) 発行日 平成28年11月9日(2016.11.9)

(24) 登録日 平成28年10月14日(2016.10.14)

(51) Int.Cl.

F 1

H04N 5/3745 (2011.01)

H04N 5/335 745

H04N 5/378 (2011.01)

H04N 5/335 780

請求項の数 13 (全 12 頁)

(21) 出願番号 特願2015-198830 (P2015-198830)

(22) 出願日 平成27年10月6日 (2015.10.6)

(62) 分割の表示 特願2011-130266 (P2011-130266)

原出願日 平成23年6月10日 (2011.6.10)

(65) 公開番号 特開2016-29817 (P2016-29817A)

(43) 公開日 平成28年3月3日 (2016.3.3)

審査請求日 平成27年10月30日 (2015.10.30)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 小林 大祐

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 山崎 善一

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】撮像装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

複数行および複数列に画素が配された画素アレイと、前記画素アレイの前記複数列の各々に対応して各々が設けられた複数の信号処理部を、

各々が有する第1の信号処理部群および第2の信号処理部群と、駆動信号を生成する駆動信号生成部と、前記駆動信号を前記駆動信号生成部から伝送する複数のバッファ回路を有する駆動信号

伝送部とを有し、複数のバッファ回路は、各々の入力端子に入力された信号を反転せずに各々の出力端子

から出力する、複数の第1のバッファ回路および複数の第2のバッファ回路を有し、前記複数の第2のバッファ回路のうちの1つの第2のバッファ回路の出力端子が、前記

第1の信号処理部群の前記複数の信号処理部に並列に接続され、前記複数の第2のバッファ回路のうちの別の1つの第2のバッファ回路の出力端子が、

前記第2の信号処理部群の前記複数の信号処理部に並列に接続され、前記複数の第1のバッファ回路のうちの1つの第1のバッファ回路の出力端子が、前記

1つの第2のバッファ回路の入力端子と、前記複数の第1のバッファ回路のうちの別の1

つの第1のバッファ回路の入力端子とに接続され、前記別の1つの第1のバッファ回路の出力端子が、前記別の1つの第2のバッファ回路

の入力端子に接続され、前記駆動信号伝送部において、前記駆動信号生成部から前記第2の信号処理部群に前記

10

20

駆動信号を伝送する全てのバッファ回路の段数が、前記駆動信号伝送部において、前記駆動信号生成部から前記第1の信号処理部群に前記駆動信号を伝送する全てのバッファ回路の段数よりも多いことを特徴とする撮像装置。

【請求項2】

各々が複数の信号処理部を有するS個( $S > 2$ の自然数)の信号処理部群を有し、

前記S個の信号処理部群の各々が有する前記複数の信号処理部の個数の和をN、

前記第1のバッファ回路による信号の遅延時間をt1、

前記第2のバッファ回路による信号の遅延時間をt2、

前記駆動信号の周波数をFとして、

前記Sが $(N/S - 1) \times t_1 + t_2 < 1/F$ の関係を満たすこと

を特徴とする請求項1に記載の撮像装置。 10

【請求項3】

前記駆動信号伝送部は、第1の駆動信号伝送部と第2の駆動信号伝送部とを含み、

前記第1の駆動信号伝送部と前記第2の駆動信号伝送部とは、

同じ数の前記第2のバッファ回路を有することを特徴とする請求項1または2に記載の撮像装置。 20

【請求項4】

前記駆動信号伝送部は、第1の駆動信号伝送部と第2の駆動信号伝送部とを含み、

前記第2の駆動信号伝送部は前記第1の駆動信号伝送部よりも少ない数の前記第2のバッファ回路を有し、

前記第2の駆動信号伝送部は、前記第1の駆動信号伝送部よりも低い周波数の駆動信号を伝送すること

を特徴とする請求項1または2に記載の撮像装置。 20

【請求項5】

前記複数の信号処理回路に前記駆動信号を供給する第3の駆動信号伝送部をさらに備え、

前記第3の駆動信号伝送部は、前記第2の駆動信号伝送部よりも低い周波数の駆動信号を伝送すること

を特徴とする請求項4に記載の撮像装置。 30

【請求項6】

駆動信号伝送部は、第1の駆動信号伝送部と第2の駆動信号伝送部とを含み、

前記第1の駆動信号伝送部と前記第2の駆動信号伝送部とは、遅延時間が等しいことを特徴とする請求項1ないし5のいずれかに記載の撮像装置。 30

【請求項7】

前記第2のバッファ回路から供給された前記駆動信号の周波数を変換する周波数変換部をさらに有することを特徴とする請求項1ないし6のいずれかに記載の撮像装置。 30

【請求項8】

前記周波数変換部は分周回路またはPLL回路を含むことを特徴とする請求項7に記載の撮像装置。 40

【請求項9】

前記信号処理部は、前記画素から出力された信号に対してノイズ低減、增幅、およびA/D変換のうち、少なくとも1つの機能を有することを特徴とする、請求項1ないし8のいずれかに記載の撮像装置。 40

【請求項10】

前記撮像装置は

出力部と

前記信号処理部から出力された信号を前記出力部に転送する転送部をさらに有し、

前記転送部は、シフトレジスタまたはデコーダによって前記出力部に信号を転送する前記信号処理部を選択すること

を特徴とする請求項1ないし9のいずれかに記載の撮像装置。 50

**【請求項 1 1】**

前記駆動信号伝送部は、さらに前記駆動信号を前記転送部に供給することを特徴とする請求項1 0に記載の撮像装置。

**【請求項 1 2】**

半導体基板上に形成されたことを特徴とする請求項 1 ないし1 1のいずれかに記載の撮像装置。

**【請求項 1 3】**

請求項 1 ないし1 2のいずれかに記載の撮像装置と、

前記撮像装置から出力された信号を処理して画像データを生成する映像信号処理部と、

をさらに備えたこと

を特徴とする撮像システム。

10

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は撮像装置に関し、特に、画素アレイの列に対応して信号処理回路を備える撮像装置に関する。

**【背景技術】****【0 0 0 2】**

画素が行列状に配列された画素アレイの各列、あるいは複数列につき信号処理回路を設けて、並列に信号処理を行う撮像装置が一般に知られている。信号処理回路は、画素から出力された信号に対して相關二重サンプリング (Correlated Double Sampling ; CDS) やオフセット調整、増幅、アナログ / デジタル変換 (A / D 変換) といった処理を行う。

20

**【0 0 0 3】**

複数の信号処理回路を駆動する駆動信号を供給する手法の例として、特許文献 1 に記載された技術がある。特許文献 1 では、複数の信号処理回路を 1 つのグループとした各グループ内で、駆動信号を伝達するバッファ素子を直列に接続することにより、ピーク電流の低減およびバッファ素子の数の低減を図っている。

**【先行技術文献】****【特許文献】****【0 0 0 4】**

【特許文献 1】特開 2007 - 060036 号公報

**【発明の概要】****【発明が解決しようとする課題】****【0 0 0 5】**

しかしながら、特許文献 1 に記載された構成では、各信号処理回路に対してバッファ素子を設けているため、信号処理回路の数に比例してバッファ素子の数が増大する。さらに、半導体基板に形成するに際してチップ面積が増大する。

**【0 0 0 6】**

また、信号処理回路の各グループ内で駆動信号が遅延して供給されるので、動作タイミングのマージンを長く設定する必要が生じる。つまり、動作の高速化が図りにくい。

40

**【0 0 0 7】**

本発明はバッファ素子数の増大を抑制しつつ、動作の高速化を実現する撮像装置を提供することを目的とする。

**【課題を解決するための手段】****【0 0 0 8】**

上記課題を解決する本発明は、複数行および複数列に画素が配された画素アレイと、

前記画素アレイの前記複数列の各々に対応して各々が設けられた複数の信号処理部を、

各々が有する第 1 の信号処理部群および第 2 の信号処理部群と、駆動信号を生成する駆動

信号生成部と、前記駆動信号を前記駆動信号生成部から伝送する複数のバッファ回路を有

50

する駆動信号伝送部とを有し、複数のバッファ回路は、各々の入力端子に入力された信号を反転せずに各々の出力端子から出力する、複数の第1のバッファ回路および複数の第2のバッファ回路を有し、前記複数の第2のバッファ回路のうちの1つの第2のバッファ回路の出力端子が、前記第1の信号処理部群の前記複数の信号処理部に並列に接続され、前記複数の第2のバッファ回路のうちの別の1つの第2のバッファ回路の出力端子が、前記第2の信号処理部群の前記複数の信号処理部に並列に接続され、前記複数の第1のバッファ回路のうちの1つの第1のバッファ回路の出力端子が、前記1つの第2のバッファ回路の入力端子と、前記複数の第1のバッファ回路のうちの別の1つの第1のバッファ回路の入力端子とに接続され、前記別の1つの第1のバッファ回路の出力端子が、前記別の1つの第2のバッファ回路の入力端子に接続され、前記駆動信号伝送部において、前記駆動信号生成部から前記第2の信号処理部群に前記駆動信号を伝送する全てのバッファ回路の段数が、前記駆動信号伝送部において、前記駆動信号生成部から前記第1の信号処理部群に前記駆動信号を伝送する全てのバッファ回路の段数よりも多いことを特徴とする撮像装置である。

10

## 【発明の効果】

## 【0010】

本発明によれば、バッファ素子数の増大を抑制しつつ、動作の高速化が可能となる。

## 【図面の簡単な説明】

## 【0011】

【図1】第1の実施形態に係る撮像装置の構成例を示す図

20

【図2】第1の実施形態に係る信号処理部および駆動信号伝送部の構成例を示す図

【図3】第1の実施形態に係る信号の位相関係を示す図

【図4】画素の構成例を示す等価回路図

【図5】信号処理回路に含まれる増幅器と転送部の構成例を示す図

【図6】第2の実施形態に係る撮像装置の構成例を示す図

【図7】第2の実施形態に係る信号の位相関係を示す図

【図8】第2の実施形態に係る撮像装置の別の構成例を示す図

【図9】第3の実施形態に係る信号処理回路と駆動信号伝送部の構成例を示す図

【図10】第4の実施形態に係る撮像システムの構成例を示す図

## 【発明を実施するための形態】

30

## 【0012】

## (第1の実施形態)

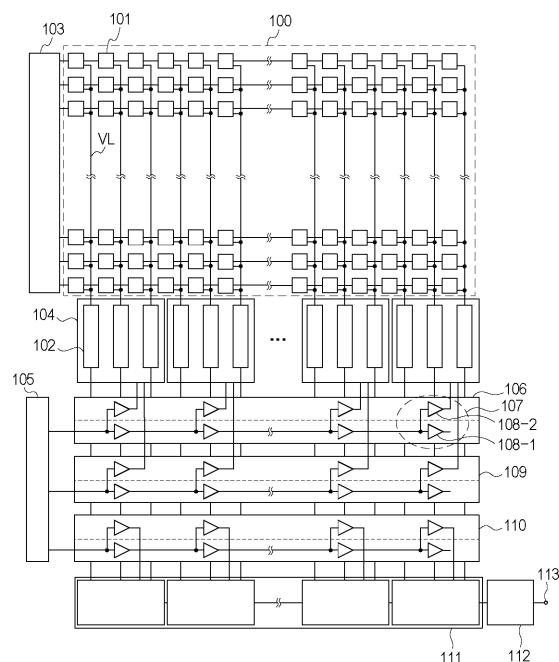

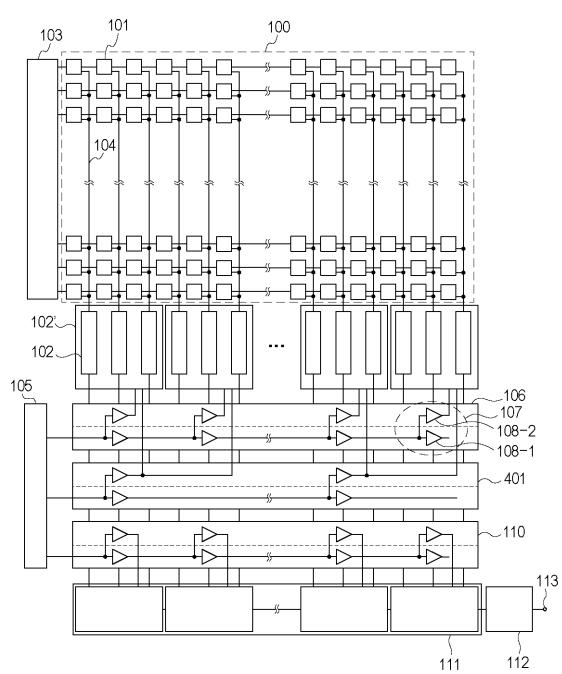

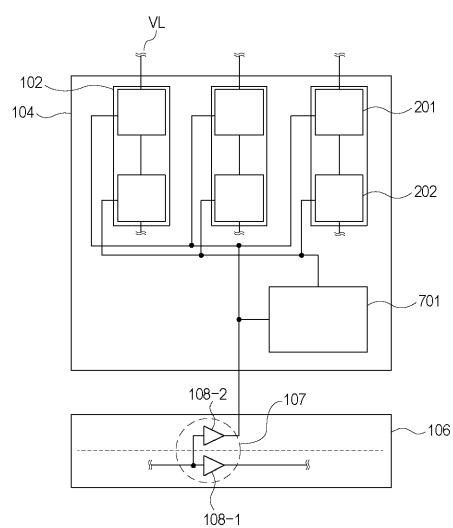

図1は、本発明の第1の実施形態に係る撮像装置の構成例を示す図である。ここではM行N列の画素101が配列された画素アレイ100と、画素アレイ100の各列に信号処理回路102を備える構成を例にとって説明する。

## 【0013】

画素101は光電変換部を含み、光電変換によって得られた電荷量に応じた信号を信号線VLに出力する。行選択回路103は画素101の動作を行単位で制御するもので、画素101のリセットや信号を読み出す動作を制御する。信号処理部群である信号処理回路群104の各々は複数の信号処理回路102を含み、信号線VLを介して伝達された信号を処理する回路である。信号処理回路102が備える機能の例としては、CDSによるノイズ低減、信号の増幅、A/D変換がある。A/D変換機能を有する構成では、A/D変換によって得られたデジタル信号を一時的に保持するためにSRAM(Static Random Access Memory)などのデジタルメモリを備えても良い。

40

## 【0014】

信号処理回路102は駆動信号の供給を受けて動作する。駆動信号生成部105で生成された駆動信号は、駆動信号伝送部106、109を介して各信号処理回路102に伝達される。ここでは、信号処理部である信号処理回路102がA/D変換器とデジタルメモリを含み、それぞれを異なる駆動信号で駆動する例を示している。図示の通り、同一の信号処理回路群104に含まれる複数の信号処理回路102は共通の駆動信号が与えられる

50

ように構成される。

**【0015】**

信号処理回路102から出力された信号は、転送部111を介して出力部112へと伝達され、出力端子113から後段の回路に伝達される。転送部111は、画素アレイ100の列に対応したシフトレジスタやデコーダを含み、出力部112へ信号を伝送する信号処理回路102を選択する機能を有する。転送部111は、駆動信号伝送部110を介して供給される、駆動信号生成部105で生成された駆動信号を受けて動作する。

**【0016】**

次に、駆動信号伝送部106、109、110について詳細な説明を行う。駆動信号伝送部106は、複数のバッファブロック107を有する。各バッファブロック106は、各信号処理回路群104に対して1個設けられている。各バッファブロック106は、第1のバッファ回路108-1と第2のバッファ回路108-2とを含んでなる。第1のバッファ回路の出力は他のバッファブロック107に含まれる第1及び第2のバッファ回路の入力に与えられるように接続される。また、第2バッファ回路108-2の出力は対応する信号処理回路群104の複数の信号処理回路に並列に与えられる。言い換えると、駆動信号伝送部106は、複数の第1のバッファ回路108-1が直列に接続され、第2のバッファ回路108-2は第1のバッファ回路108-1に対して並列に設けられた構成である。また、第1のバッファ回路108-1は別の第1のバッファ回路108-1及び第2のバッファ回路108-2に駆動信号を供給するとも表現できる。

**【0017】**

駆動信号伝送部109も駆動信号伝送部106と同様に、第1及び第2のバッファ回路が設けられており、各第2のバッファ回路は、複数の信号処理回路102に対して駆動信号を供給する。

**【0018】**

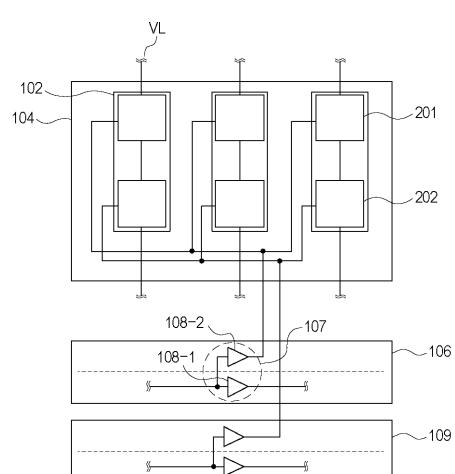

図2は、ある信号処理回路群104と、これに対応付けられた駆動信号伝送部106および109のバッファブロックの接続関係を示したブロック図である。ここでは、信号処理回路群104に3個の信号処理回路102が含まれる場合を例示した。各信号処理回路102はA/D変換器201とデジタルメモリ202とを含む。駆動信号伝送部109の第2のバッファ回路は、3個のデジタルメモリ202に駆動信号を供給し、駆動信号伝送部106の第2のバッファ回路は、3個のA/D変換器201に駆動信号を供給する。

**【0019】**

第3の駆動信号伝送部である駆動信号伝送部110は駆動信号伝送部106と同様に、第1及び第2のバッファ回路が設けられているが、第2のバッファ回路は転送ブロックに対して駆動信号を供給する。転送ブロックの各々は例えば複数段のシフトレジスタを含み、それらに共通の駆動信号を供給する。

**【0020】**

本実施例の構成によれば、第2のバッファ回路から複数の信号処理回路や転送ブロックに駆動信号を供給するので、動作タイミングのマージンを短縮できることとともに、バッファ回路の数が増大することを抑制できる。また、同一の第2のバッファ回路から駆動信号を供給される信号処理回路あるいは転送ブロックは同時に動作するが、異なる第2のバッファ回路から駆動信号を供給される信号処理回路間では動作するタイミングが異なるので、ピーク電流を抑制することができる。

**【0021】**

複数の信号処理回路102に対して共通の第2のバッファ回路から駆動信号を供給することは、信号処理回路102がA/D変換器とデジタルメモリとを含む場合に特に有用である。これは、A/D変換器は比較器とデジタルメモリとが同期して動作しなければならないため、駆動信号の位相関係を維持する必要があるからである。本実施例に示すように、駆動信号伝送部106および109のバッファブロックは、同じ信号処理回路群104に駆動信号を供給するので、信号処理回路群104の中では駆動信号の位相関係が保たれる。つまり、信号の位相管理が容易になるという利点がある。なお、本実施例では、第1

10

20

30

40

50

の駆動信号伝送部である駆動信号伝送部 106 と、第 2 の駆動信号伝送部である駆動信号伝送部 109 とは、同数の第 1 のバッファ回路を含んで構成される例を示しているので、両者で生じる遅延時間は等しくすることができる。ここで、遅延時間が等しいとは、伝送される駆動信号が  $F [ \text{Hz} ]$  である場合には、2 つの駆動信号伝送部が伝送する信号の間で、位相差が 1 周期以内であることを意味する。

#### 【0022】

次に、信号処理回路 102 が A / D 変換器を含む場合の信号処理回路群 104 の数  $S$  について説明する。A / D 変換器の構成として、変換対象となるアナログ信号と、時間に対してスロープ状に変化する参照信号とを比較器に入力し、参照信号が変化を開始してからアナログ信号と参照信号との大小関係が逆転するまでにカウンタに入力されるクロック数をカウントするものが知られている。このような構成の A / D 変換器が複数設けられているときに、各 A / D 変換器に与えられるクロック信号が 1 周期以上遅延すると、同じレベルのアナログ信号に対してことなるデジタル信号が生成されてしまう。撮像装置においては、行に沿った方向にシェーディングとして画像に現れる。

#### 【0023】

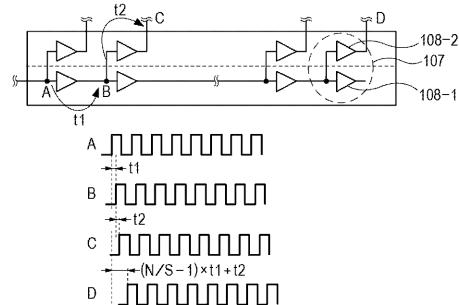

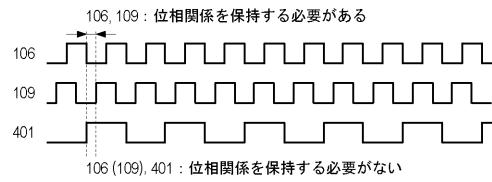

図 3 は、駆動信号伝送部と、A ~ D で示した各ノードにおける信号の波形を示した図である。例えば、駆動信号伝送部で伝送する信号が A / D 変換器におけるカウント動作を制御するためのクロック信号であるとする。クロック信号の周波数を  $F [ \text{Hz} ]$  として、全信号処理回路 102 の間で 1 周期、すなわち  $1 / F [ \text{sec} ]$  以上の位相差が生じると、A / D 変換結果が信号処理回路どうしで異なってしまう。このような制約の下、第 1 のバッファ回路で生じる遅延時間を  $t_1 [ \text{sec} ]$ 、第 2 のバッファ回路で生じる遅延時間を  $t_2 [ \text{sec} ]$  とし、信号処理回路 102 が  $N$  個存在する場合を考える。

#### 【0024】

ノード A が、駆動信号生成部 105 から出力された駆動信号が与えられるとする。第 1 のバッファ回路を 1 段経たノードを B、さらにノード B から第 2 のバッファ回路を経たノードを C とし、最終段の第 2 のバッファ回路を経たノードを D とすると、上述の制約から、ノード A とノード D との間で  $1 / F [ \text{sec} ]$  よりも少ない遅延時間でなければならない。これを数式で表現すると、式(1)のように表せる。

$$(N / S - 1) \times t_1 + t_2 < 1 / F \quad \dots (1)$$

#### 【0025】

したがって、信号処理回路群 104 の数  $S$  を、式(1)を満たすような自然数であるように設計することで、シェーディングが生じることを抑制することができる。なお、ここでは A / D 変換器を例に取っているためにクロック信号として示したが、A / D 変換器以外においても上記条件を満足することが好ましい。

#### 【0026】

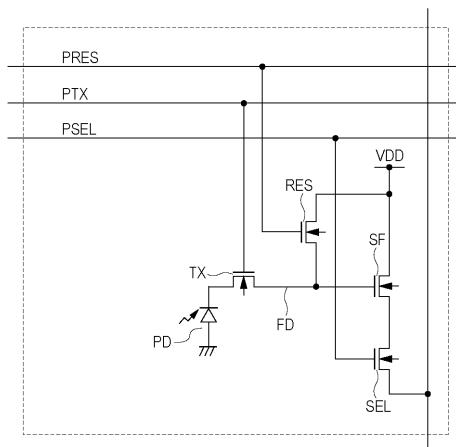

図 4 は、画素 101 の構成例を示す等価回路図である。画素 101 は光電変換部 P D、転送トランジスタ TX、リセットトランジスタ RES、増幅トランジスタ SF、選択トランジスタ SEL と、を有する。転送スイッチ TX は、転送パルス PTX によって駆動され、導通すると光電変換部 P D で生成された電荷が増幅トランジスタ SF の制御電極のノード FD に転送される。リセットスイッチ RES は、リセットパルス PRES によって駆動され、導通するとノード FD が電源電圧 V DD にリセットされる。行選択スイッチ SEL は、行選択パルス PSEL によって駆動され、導通すると増幅トランジスタ SF は不図示の定電流源とソースフォロワ回路を構成して、ノード FD の電位に応じた信号を信号線 VL に出力する。

#### 【0027】

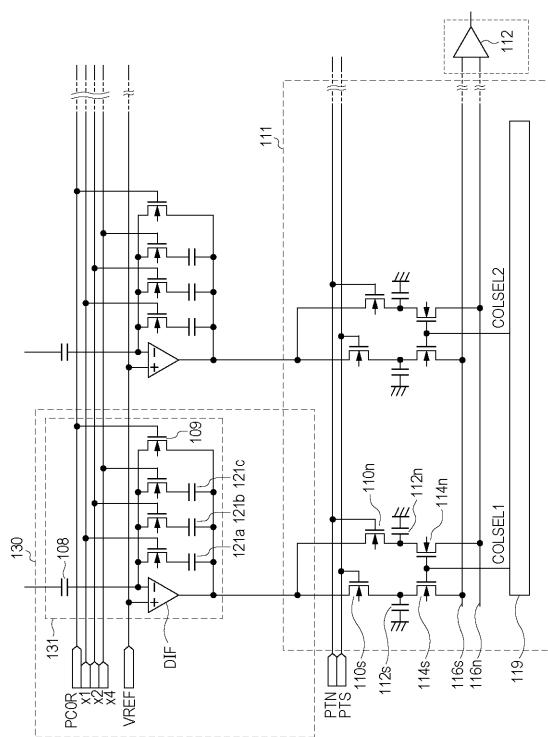

図 5 は、信号処理回路に含まれる増幅器と、転送部の構成例を示すである。増幅器 130 は、差動増幅器 DIF と入力容量 C0、帰還容量 121a ~ 121c、短絡スイッチ 109 を含む。差動増幅器 DIF の反転入力端子と出力端子とを接続する帰還容量は、信号  $\times 1$ 、 $\times 2$ 、 $\times 4$  によって選択することができるようになっており、入力容量 C0 の容量との容量値の比によって増幅器 130 のゲインが決められる。また、短絡スイッチ 109

10

20

30

40

50

が導通すると差動増幅器 D I F はボルテージフォロワとして動作し、このときに出力と入力容量とを使って、画素から出力される信号をクランプすることができる。これにより、画素で生じたノイズを低減することが可能となる。

#### 【0028】

転送部は、保持容量 112s および 112n と、を含む。このうち一方に増幅器 130 のオフセットを保持させ、他方には増幅器 130 で増幅された信号を保持させる。そして、例えば出力部が持つ差動増幅器で両者の差分をとることで、増幅器 130 のオフセットを低減することができる。また、信号処理回路が A/D 変換器を含む場合には、保持容量を廃して、デジタル信号として同様の処理を行っても良い。

#### 【0029】

以上で説明したとおり、本実施例によれば、バッファ素子の数が増大することを抑制しつつ、動作の高速化を図ることができる。

#### 【0030】

##### (第2の実施形態)

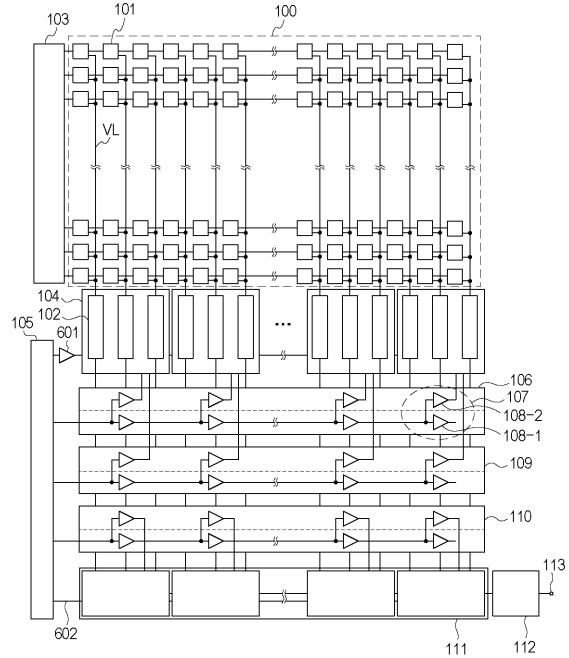

図 6 は、本発明の第 2 の実施形態に係る撮像装置の構成例を示す図である。図 1 に示した構成との違いは、駆動信号伝送部 109 に換えて駆動信号伝送部 401 が設けられた点である。ここでは、第 1 の実施形態との相違点を説明する。

#### 【0031】

第 1 の実施形態では、駆動信号伝送部 109 の 1 個のバッファブロックが 3 列の信号処理回路 102 に対して設けられていたのに対して、本実施形態では、駆動信号伝送部 401 の 1 個のバッファブロックが N/2 列の信号処理回路 102 に対して設けられる。第 1 の実施形態では、駆動信号伝送部 109 を通して伝送される駆動信号が、駆動信号伝送部 106 を通して伝送される高周波数の駆動信号との間で位相関係が保たれる必要があった。このため、駆動信号伝送部 109 は駆動信号伝送部 106 と同数の信号処理回路 102 に対して 1 個のバッファブロックを設けていた。

#### 【0032】

一方、駆動信号伝送部 401 を通して伝送される信号が低周波数であれば、高周波数の駆動信号を伝送する駆動信号伝送部 106 よりも少ない数のバッファブロックで駆動信号伝送部 401 を構成できる。また、異なる駆動信号伝送部で伝送される駆動信号どうしで位相を揃える必要がない場合も同様である。図 7 は、第 1 の実施形態と比較するために、駆動信号伝送部 106、109、および 401 を通して伝送される駆動信号の波形を示した図である。駆動信号伝送部 106 と 109 とで伝送される駆動信号との間では位相関係を保たれるのに対して、駆動信号伝送部 106 と 401 とで伝送される駆動信号の間では位相関係を保たないことを示している。駆動信号伝送部 401 を通して伝送する駆動信号の例としては、信号処理回路 102 が CDS 回路を含んでいる場合には CDS 回路の動作に必要な信号、ADC を含んでいる場合には比較器をリセットするための信号や、デジタルメモリをリセットしたりカウント値をラッチしたりするための信号が該当する。

#### 【0033】

さらに、信号処理回路 102 の構成によっては、図 8 に示すように、一個のバッファ回路 601 や 602 によって全列の信号処理回路 102 に信号を供給しても良い。このような信号は、信号処理回路 102 が備える増幅器のゲインを設定する信号や、動作モードを指定する信号、シフトレジスタのスタートパルスなどが例として挙げられる。

#### 【0034】

つまり、信号処理回路 102 に供給する全ての信号を同じ数のバッファブロックで伝送するのではなく、伝送する駆動信号の種類に応じて駆動信号伝送部が備えるバッファ回路の数を設定することで、バッファ回路が占める面積や消費電力を適正化できる。

#### 【0035】

##### (第3の実施形態)

図 9 を参照しながら、本発明の第 3 の実施形態について説明を行う。

#### 【0036】

10

20

30

40

50

図9は、信号処理回路群104の構成例を示す図である。駆動信号伝送部106から供給される駆動信号に対して遅延あるいは分周した信号との間での位相管理が必要となる場合がある。そこで、本実施形態においては周波数変換部701を設ける。

#### 【0037】

各駆動信号部が備えるバッファ回路間にはばらつきや寄生負荷の違いが存在するため、駆動信号が高周波数である場合には特に、駆動信号間で位相関係を保つことが困難になる。これに対して、本実施形態では周波数変換部701を用いることで、位相関係を保つことを容易にすることができます。周波数変換部には、例えばPLL回路や分周回路を用いることができる。

#### 【0038】

以上で説明した各実施形態に示した撮像装置は、例えば半導体基板上に形成することができる。全ての要素を同一の基板に設ける必要はなく、駆動信号生成部を、画素アレイや信号処理部、駆動信号伝送部とは別の半導体基板に設ける構成も考えられる。

#### 【0039】

##### (第4の実施形態)

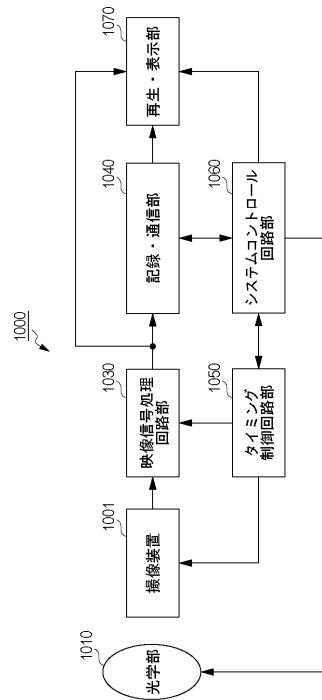

次に、本実施形態に係る撮像システムの概略を、図10を用いて説明する。

#### 【0040】

撮像システム1000は、例えば、光学部1010、撮像装置1001、映像信号処理回路部1030、記録・通信部1040、タイミング制御回路部1050、システムコントロール回路部1060、および再生・表示部1070を含む。撮像装置1001は、先述の各実施例で説明した撮像装置が用いられる。

#### 【0041】

レンズなどの光学系である光学部は1010、被写体からの光を撮像装置1001の、複数の画素が2次元状に配列された画素アレイに結像させ、被写体の像を形成する。撮像装置1001は、タイミング制御回路部1050からの信号に基づくタイミングで、画素部に結像された光に応じた信号を出力する。

#### 【0042】

撮像装置1001から出力された信号は、映像信号処理部である映像信号処理回路部1030に入力され、映像信号処理回路部1030が、プログラムなどによって定められた方法に従って、入力された電気信号に対してA/D変換などの処理を行う。映像信号処理回路部での処理によって得られた信号は画像データとして記録・通信部1040に送られる。記録・通信部1040は、画像を形成するための信号を再生・表示部1070に送り、再生・表示部1070に動画や静止画像が再生・表示させる。記録通信部は、また、映像信号処理回路部1030からの信号を受けて、システムコントロール回路部1060とも通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。

#### 【0043】

システムコントロール回路部1060は、撮像システムの動作を統括的に制御するものであり、光学部1010、タイミング制御回路部1050、記録・通信部1040、および再生・表示部1070の駆動を制御する。また、システムコントロール回路部1060は、例えば記録媒体である不図示の記憶装置を備え、ここに撮像システムの動作を制御するのに必要なプログラムなどが記録される。また、システムコントロール回路部1060は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内で供給する。具体的な例としては、読み出す行やリセットする行の変更、電子ズームに伴う画角の変更や、電子防振に伴う画角のずらしなどである。

#### 【0044】

タイミング制御回路部1050は、制御部であるシステムコントロール回路部1060による制御に基づいて撮像装置1001および映像信号処理回路部1030の駆動タイミングを制御する。

#### 【0045】

10

20

30

40

50

映像信号処理回路部 1030 は、先述の各実施例で説明した補正係数を保持し、撮像装置 1001 から出力された信号に対して補正処理を行う。

【符号の説明】

【0046】

|     |          |    |

|-----|----------|----|

| 100 | 画素アレイ    |    |

| 101 | 画素       |    |

| 102 | 信号処理回路   |    |

| 103 | 行選択回路    |    |

| 104 | 信号処理回路群  | 10 |

| 105 | 駆動信号生成部  |    |

| 106 | 駆動信号伝送部  |    |

| 107 | バッファブロック |    |

| 108 | 第2のバッファ段 |    |

| 109 | 駆動信号伝送部  |    |

| 110 | 駆動信号伝送部  |    |

| 401 | 駆動信号伝送部  |    |

| 601 | バッファ回路   |    |

| 602 | バッファ回路   |    |

| 701 | 周波数変換部   |    |

| VL  | 信号線      | 20 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(56)参考文献 特開2011-160318(JP,A)

特開2011-182095(JP,A)

特開2006-303752(JP,A)

特開2007-060036(JP,A)

特開2011-166197(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5 / 3745

H04N 5 / 378