(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7279552号**

**(P7279552)**

(45)発行日 令和5年5月23日(2023.5.23)

(24)登録日 令和5年5月15日(2023.5.15)

(51)国際特許分類

|         |                 |     |         |       |

|---------|-----------------|-----|---------|-------|

| C 3 0 B | 29/38 (2006.01) | F I | C 3 0 B | 29/38 |

| C 3 0 B | 25/02 (2006.01) |     | C 3 0 B | 25/02 |

請求項の数 6 (全10頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2019-129089(P2019-129089) |

| (22)出願日  | 令和1年7月11日(2019.7.11)        |

| (65)公開番号 | 特開2021-14376(P2021-14376A)  |

| (43)公開日  | 令和3年2月12日(2021.2.12)        |

| 審査請求日    | 令和3年6月16日(2021.6.16)        |

|          |                                                             |

|----------|-------------------------------------------------------------|

| (73)特許権者 | 000190149<br>信越半導体株式会社<br>東京都千代田区大手町二丁目2番1号                 |

| (74)代理人  | 100102532<br>弁理士 好宮 幹夫<br>100194881<br>弁理士 小林 俊弘            |

| (72)発明者  | 萩本 和徳<br>群馬県安中市磯部二丁目13番1号 信<br>越半導体株式会社 半導体磯部研究所内<br>後藤 正三郎 |

| (72)発明者  | 東京都千代田区大手町二丁目2番1号<br>信越半導体株式会社 本社内                          |

| 審査官      | 今井 淳一                                                       |

最終頁に続く

(54)【発明の名称】 電子デバイス用基板およびその製造方法

**(57)【特許請求の範囲】****【請求項1】**

シリコン単結晶の接合基板上に窒化物半導体膜が形成された電子デバイス用基板であつて、

前記接合基板は、複数のシリコン単結晶基板を接合した基板であつて、前記複数のシリコン単結晶基板を含んでおり、厚さが $2\,0\,0\,0\,\mu\text{m}$ より厚く、

前記複数のシリコン単結晶基板は、CZ法により製造された基板であつて、抵抗率が $0.1\,\text{cm}$ 以下のもので、かつ、各々、 $1\,0\,0\,0\,\mu\text{m}$ 以上の厚さを有するものであることを特徴とする電子デバイス用基板。

**【請求項2】**

前記複数のシリコン単結晶基板は、酸素濃度が $3.0 \times 10^{17} \sim 1 \times 10^{18}\,\text{atom s/cm}^3$ (ASTM'79)のものであることを特徴とする請求項1に記載の電子デバイス用基板。

**【請求項3】**

前記接合基板は、複数のCZシリコン単結晶基板が $\text{SiO}_2$ 膜を介して接合されたものであることを特徴とする請求項1又は請求項2に記載の電子デバイス用基板。

**【請求項4】**

シリコン単結晶の接合基板上に窒化物半導体膜を形成する電子デバイス用基板の製造方法であつて、

複数のシリコン単結晶基板を接合して、厚さが $2\,0\,0\,0\,\mu\text{m}$ より厚い接合基板とする工

程と、

前記複数のシリコン単結晶基板を含む前記接合基板上に窒化物半導体膜をエピタキシャル成長させる工程とを含み、

前記複数のシリコン単結晶基板として、CZ法により製造された、抵抗率が0.1 c m以下のもので、かつ、各々、 $1000 \mu\text{m}$ 以上の厚さを有するものを用いることを特徴とする電子デバイス用基板の製造方法。

**【請求項 5】**

前記複数のシリコン単結晶基板として、酸素濃度が $3.0 \times 10^{17} \sim 1 \times 10^{18}$  at o m s / c m<sup>3</sup> (ASTM'79) のものを用いることを特徴とする請求項4に記載の電子デバイス用基板の製造方法。 10

**【請求項 6】**

前記接合基板とする工程において、複数のCZシリコン単結晶基板をSiO<sub>2</sub>膜を介して接合することを特徴とする請求項4又は請求項5に記載の電子デバイス用基板の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、電子デバイス用基板およびその製造方法に関する。

**【背景技術】**

**【0002】**

GaNやAlNをはじめとする窒化物半導体は、2次元電子ガスを用いた高電子移動度トランジスタ(HEMT)や高耐圧電子デバイスの作製に用いることができる。 20

**【0003】**

これらの窒化物半導体を基板上に成長させた窒化物ウェーハを製作することは難しく、基板としては、サファイア基板やSiC基板が用いられている。しかし、大口径化や基板のコストを抑えるために、シリコン基板上への気相成長によるエピタキシャル成長が用いられている。シリコン基板上への気相成長によるエピタキシャル成長膜の作製は、サファイア基板やSiC基板に比べて大口径の基板が使用できるのでデバイスの生産性が高く、放熱性の点で有利である。ただし、格子定数差や熱膨張係数差による応力により、反りの増大や塑性変形が起こりやすく、成長条件や緩和層による応力低減が行われている。 30

**【0004】**

高耐圧電子デバイスでは、高耐圧特性を向上させるため、エピタキシャル層を厚く積む必要がある。その為、エピタキシャル層を厚く積むと、その基板であるシリコン基板がエピタキシャル層との熱膨張係数の違いにより、ウェーハに反りが発生する。

**【0005】**

特許文献1では、エピタキシャル層AlN/Si(1000 c m以上)/Si(10 c m以下)として、高抵抗基板を低抵抗基板と接合して反り形状を制御した電子デバイス用エピタキシャル基板が開示されている。また、特許文献2では、エピタキシャル層AlN/Si(CZ低抵抗)/Si(FZ高抵抗)として、低抵抗CZ基板を高抵抗FZ基板と接合して反りを抑制した電子デバイス用エピタキシャル基板が開示されている。 40

**【0006】**

しかしながら、高耐圧電子デバイスに用いる電子デバイス用基板において、エピタキシャル層を厚く積んだ際のウェーハの反りをさらに抑制することが望まれていた。

**【先行技術文献】**

**【特許文献】**

**【0007】**

**【文献】国際公開第2011/016219号**

特開2014-192226号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

10

20

30

40

50

**【 0 0 0 8 】**

本発明は上記課題を解決するためになされたもので、シリコン基板上に窒化物半導体膜が形成された電子デバイス用基板において、反りを抑制し、高耐圧品にも用いることが可能な電子デバイス用基板及びその製造方法を提供することを目的とする。

**【課題を解決するための手段】****【 0 0 0 9 】**

上記目的を解決するために、本発明は、シリコン単結晶の接合基板上に窒化物半導体膜が形成された電子デバイス用基板であって、

前記接合基板は、複数のシリコン単結晶基板を接合した基板であって、厚さが 2000  $\mu\text{m}$  より厚く、

前記複数のシリコン単結晶基板は、CZ 法により製造された基板であって、抵抗率が 0.1  $\Omega \cdot \text{cm}$  以下のものであることを特徴とする電子デバイス用基板を提供する。

**【 0 0 1 0 】**

本発明の電子デバイス用基板であれば、複数のシリコン単結晶基板を、抵抗率が 0.1  $\Omega \cdot \text{cm}$  以下の CZ 法により製造された基板とし、さらに接合基板の厚さを 2000  $\mu\text{m}$  よりも厚くすることで、接合基板の強度が大幅に増す為、形成された窒化物半導体膜による電子デバイス用基板の反りを抑制することができる。このため、特に、高耐圧品に用いる電子デバイス用基板として最適なものとなる。

**【 0 0 1 1 】**

このとき、前記複数のシリコン単結晶基板は、酸素濃度が  $3.0 \times 10^{17} \sim 1 \times 10^{18}$  atoms /  $\text{cm}^3$  (ASTM'79) のものであることが好ましい。

**【 0 0 1 2 】**

このようなものであれば、シリコン単結晶基板におけるスリップの発生を防止できる。

**【 0 0 1 3 】**

また、前記接合基板は、複数の CZ シリコン単結晶基板が  $\text{SiO}_2$  膜を介して接合されたものであることが好ましい。

**【 0 0 1 4 】**

このようなものであれば、窒化物半導体膜による応力を緩和することができ、より厚い窒化物半導体膜を形成することができる。

**【 0 0 1 5 】**

また本発明は、シリコン単結晶の接合基板上に窒化物半導体膜を形成する電子デバイス用基板の製造方法であって、

複数のシリコン単結晶基板を接合して、厚さが 2000  $\mu\text{m}$  より厚い接合基板とする工程と、

前記接合基板上に窒化物半導体膜をエピタキシャル成長させる工程とを含み、

前記複数のシリコン単結晶基板として、CZ 法により製造された、抵抗率が 0.1  $\Omega \cdot \text{cm}$  以下のものを用いることを特徴とする電子デバイス用基板の製造方法を提供する。

**【 0 0 1 6 】**

本発明の電子デバイス用基板の製造方法であれば、抵抗率が 0.1  $\Omega \cdot \text{cm}$  以下の複数の CZ シリコン単結晶基板を用い、さらに接合基板の厚さを 2000  $\mu\text{m}$  よりも厚くすることで、強度が高い接合基板を作製できる為、窒化物半導体膜を形成させた際の電子デバイス用基板の反りを抑制することができる。このため、特に、高耐圧品に用いる電子デバイス用基板の製造方法として最適なものとなる。

**【 0 0 1 7 】**

また、前記複数のシリコン単結晶基板として、酸素濃度が  $3.0 \times 10^{17} \sim 1 \times 10^{18}$  atoms /  $\text{cm}^3$  (ASTM'79) のものを用いることが好ましい。

**【 0 0 1 8 】**

このようなものであれば、シリコン単結晶基板におけるスリップの発生を防止できる。

**【 0 0 1 9 】**

また、前記接合基板とする工程において、複数の CZ シリコン単結晶基板を  $\text{SiO}_2$  膜

10

20

30

40

50

を介して接合することが好ましい。

**【 0 0 2 0 】**

このようなものであれば、窒化物成長時に加わる応力を緩和することができ、窒化物半導体膜をより厚く形成することができる。

**【発明の効果】**

**【 0 0 2 1 】**

本発明の電子デバイス用基板及びその製造方法であれば、複数のシリコン単結晶基板を、抵抗率が $0.1\text{ cm}$ 以下のCZ法により製造された基板とし、さらに接合基板の厚さを $2000\mu\text{m}$ よりも厚くすることで、接合基板の強度が大幅に増す為、形成された窒化物半導体膜による電子デバイス用基板の反りを抑制することができる。このため、特に、高耐圧品に用いる電子デバイス用基板に最適なものとなる。

10

**【図面の簡単な説明】**

**【 0 0 2 2 】**

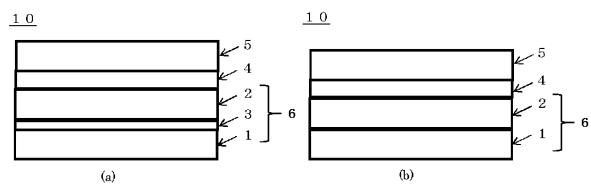

【図1】(a) 複数のシリコン単結晶基板間に接着層を有する場合、及び、(b) 接着層を有しない場合の、本発明の電子デバイス用基板を示す概念図である。

**【発明を実施するための形態】**

**【 0 0 2 3 】**

以下、本発明について詳細に説明するが、本発明はこれらに限定されるものではない。

**【 0 0 2 4 】**

本発明者らは、シリコン基板に窒化物半導体をエピタキシャル成長させて製造する電子デバイス用基板において、熱膨張係数の違いにより発生する反りが抑制された電子デバイス用基板及びその製造方法について鋭意検討を重ねたところ、低抵抗率の複数のCZシリコン単結晶基板を接合した基板であって厚さが $2000\mu\text{m}$ より厚い基板を用いることで、著しく反りが抑制されることがわかり、本発明を完成させた。

20

**【 0 0 2 5 】**

**[ 電子デバイス用基板 ]**

即ち、本発明は、シリコン単結晶の接合基板上に窒化物半導体膜が形成された電子デバイス用基板であって、

前記接合基板は、複数のシリコン単結晶基板を接合した基板であって、厚さが $2000\mu\text{m}$ より厚く、

30

前記複数のシリコン単結晶基板は、CZ法により製造された基板であって、抵抗率が $0.1\text{ cm}$ 以下のものであることを特徴とする電子デバイス用基板である。

**【 0 0 2 6 】**

本発明の電子デバイス用基板は、シリコン単結晶の接合基板上に窒化物半導体膜が形成されたものである。また、本発明において、接合基板は、CZ法により製造された複数のシリコン単結晶基板を接合した基板である。

**【 0 0 2 7 】**

図1に本発明の電子デバイス用基板の概念図を示す。

**【 0 0 2 8 】**

図1(a)、(b)に示すように、本発明の電子デバイス用基板10は、シリコン単結晶基板1とシリコン単結晶基板2(複数のシリコン単結晶基板)を接合した接合基板6と、窒化物からなる窒化物半導体膜(デバイス層)5とで構成される。複数のシリコン単結晶基板間の接合形態は特に限定されないが、接着層を設けることができる。図1(a)はシリコン単結晶基板1と、シリコン単結晶基板2の間に接着層3を有する構造を示す。接着層は特に限定されないが、例えば酸化膜( $\text{SiO}_2$ )とすることができます。また、図1(b)にはシリコン単結晶基板1と、シリコン単結晶基板2の間に接着層3の無い構造を示す。例えば接合前の酸化膜を薄膜化することで接合後の結合熱処理により、酸化膜の酸素のみが拡散し、接合界面部で酸化膜の無い構造とすることができます。このように、シリコン単結晶基板の接着が酸化膜により行われたものであれば、窒化物成長時に加わる応力を緩和することができる。なお、接合するシリコン単結晶基板の枚数は2枚に限らず3枚

40

50

以上としてもよい。以下では図1を参照して、接合基板が2枚のシリコン単結晶基板を接合した基板である場合を例に説明する。

#### 【0029】

本発明では、シリコン単結晶基板1及びシリコン単結晶基板2を、CZ法により製造したシリコン単結晶基板（以下、単にCZ単結晶基板と言う場合がある）で、抵抗率が0.1cm以下とし、接合後の接合基板の厚みを2000μmよりも厚くする。抵抗率が0.1cm以下のCZ単結晶基板とすることでシリコン単結晶基板の剛性が上がり、接合基板の強度が増す為、窒化物半導体膜を形成させた際の電子デバイス用基板の反りを抑制することができる。

#### 【0030】

また、本発明において、酸素濃度は $3.0 \times 10^{17} \sim 1 \times 10^{18}$ atoms/cm<sup>3</sup>（ASTM'79）とすることが好ましい。一般にCZ単結晶は、FZ単結晶と異なり、酸素を含有し、それによって基板の強度や硬度が向上する。一方、酸素濃度が $3.0 \times 10^{17} \sim 1 \times 10^{18}$ atoms/cm<sup>3</sup>（ASTM'79）のものとすることでCZ単結晶基板におけるスリップの発生を防止できる。

10

#### 【0031】

また、シリコン単結晶基板2とデバイス層5の間には中間層4が形成されていてもよい。中間層4は、デバイス層の結晶性改善や応力の制御のために挿入される緩衝層として働く。上記中間層4は、窒化物半導体膜と同一の設備で作製できるので、窒化物で作製されたものであることが望ましい。

20

#### 【0032】

シリコン単結晶基板2の上には、例えばGaN、AlN、InN、AlGaN、InGaN、AlInN等の窒化物の薄膜からなるデバイス層5が形成されている。ここで、中間層4が形成されている場合は、デバイス層5が中間層4の上に形成されたものとすることができます。デバイス層5はMOVPE法やスパッタリングなどの気相成長で成長させることができる。窒化物の薄膜は1~20μmとることができ、デバイスに合わせて設計することができる。

#### 【0033】

例えば窒化ガリウムは、Si(111)単結晶と格子定数差が17%、熱膨張係数差が116%あり、高温での成長中に薄膜や基板に応力がかかる。また、成長中1000以上に加熱されているため、ウェーハに応力がかかると脆性破壊せずに、延性を示すようになり、転位を発生させて塑性変形する。

30

#### 【0034】

本発明の電子デバイス用基板であれば、基板の厚さを十分厚くし、抵抗率が0.1cm以下のCZ単結晶基板とすることで、成長中の塑性変形を防止して、反りを小さくすることができる。また、接合基板の厚さを2000μmよりも厚くすることで、接合基板の強度が増す為、形成された窒化物半導体膜による電子デバイス用基板の反りをさらに抑制することができる。このため、特に、高耐圧品に用いる電子デバイス用基板として最適なものとなる。

#### 【0035】

40

#### [電子デバイス用基板の製造方法]

また、本発明は、シリコン単結晶の接合基板上に窒化物半導体膜を形成する電子デバイス用基板の製造方法であって、

複数のシリコン単結晶基板を接合して、厚さが2000μmより厚い接合基板とする工程と、

前記接合基板上に窒化物半導体膜をエピタキシャル成長させる工程とを含み、

前記複数のシリコン単結晶基板として、CZ法により製造された、抵抗率が0.1cm以下のものを用いることを特徴とする電子デバイス用基板の製造方法を提供する。

#### 【0036】

本発明の製造方法では、まず複数のシリコン単結晶基板を接合して、厚さが2000μ

50

mより厚い接合基板とする。ここで、本発明の製造方法では、複数のシリコン単結晶基板として、硬く強度に優れるCZ法により製造された、抵抗率が0.1 cm以下のものを用いる。

#### 【0037】

また、複数のシリコン単結晶基板として、酸素濃度が $3.0 \times 10^{17} \sim 1 \times 10^{18}$  atoms/cm<sup>3</sup> (ASTM'79) のものを用いることが好ましい。酸素濃度が $3.0 \times 10^{17} \sim 1 \times 10^{18}$  atoms/cm<sup>3</sup> (ASTM'79) のものを用いることでCZ単結晶基板におけるスリップの発生を防止できる。

#### 【0038】

複数のシリコン単結晶基板を接合する方法は特に限定されないが、酸化膜により貼り合わせることが好ましい。また、接合前の酸化膜を薄膜化することで接合後の結合熱処理により、酸化膜の酸素のみを拡散させ、接合界面部で酸化膜の無い構造とすることもできる。このように、シリコン単結晶基板の接着を酸化膜により行うことで、窒化物成長時に加わる応力を緩和することができる。

10

#### 【0039】

また、複数のシリコン単結晶基板のそれぞれの厚みを1000 μm以上とすることが好ましい。2000 μmを超える厚みの接合基板を製作するには、装置類の治具等を準備する必要があるが、1000 μm以上の厚みのシリコン単結晶基板2枚を貼り合わせることで、簡単に2000 μmを超える厚みの接合基板を製作することができる。

#### 【0040】

次に、上記のようにして製造した接合基板上に窒化物半導体膜をエピタキシャル成長させる。ここで、窒化物半導体膜の成長前に中間層を形成することができる。窒化物成長時に中間層を形成して適切な緩衝層を入れることで、冷却後には熱膨張係数差と格子定数差による薄膜からの応力を制御することができ、基板を厚くすることで、高温成長中の塑性変形を防ぎ、さらに反りの小さいウェーハを製造することができる。工程を簡単にするため、中間層を窒化物で作製することが望ましい。

20

#### 【0041】

このような製造方法であれば、抵抗率が0.1 cm以下の複数のCZシリコン単結晶基板を用い、さらに接合基板の厚さを2000 μmよりも厚くすることで、強度が高い接合基板を作製できる為、窒化物半導体膜を形成させた際の電子デバイス用基板の反りを抑制することができる。このため、特に、高耐圧品に用いる電子デバイス用基板の製造方法として最適なものとなる。

30

#### 【実施例】

#### 【0042】

以下、実施例及び比較例を示し、本発明をより具体的に説明するが、本発明は下記の実施例に制限されるものではない。

#### 【0043】

##### (実施例1)

抵抗率が0.007 cm、酸素濃度が $7 \times 10^{17}$  atoms/cm<sup>3</sup> (ASTM'79) のCZシリコン単結晶基板の厚みが1100 μmのウェーハ(直径150 mm、結晶方位(111))を2枚準備した。

40

次に以下のようにして、図1(a)に示すような電子デバイス用基板を作製した。CZシリコン単結晶基板(ベースウェーハ)1及び両面研磨したCZシリコン単結晶基板(ボンドウェーハ)2を熱酸化し、それぞれに厚さ100 nmのSiO<sub>2</sub>膜を形成した。そして、結合工程を経て、結合熱処理を1150℃で2時間行った。その後、酸化膜除去として、10%HFに浸漬し表面酸化膜を除去し、得られた厚さ2200 μm(1100 μm基板2枚+接合層200 nm)の接合基板を作製した。そして、作製した接合基板をMOVPE炉で8 μm厚のGaN(中間層:4 μm、デバイス層4 μm)をエピタキシャル成長した。エピタキシャル成長後のウェーハの反りは、10 μmであった。

#### 【0044】

50

## (比較例 1 )

比較例 1 では、CZシリコン単結晶基板の厚みを変更した以外は実施例 1 と同様にして基板を作製した。抵抗率が 0 . 0 0 7 cm、酸素濃度が  $7 \times 10^{17}$  atoms / cm<sup>3</sup> (ASTM'79) の CZシリコン単結晶基板の厚みが 500 μm、625 μm のウェーハ (直径 150 mm、結晶方位 (111)) をそれぞれ 2 枚準備した。

CZシリコン単結晶基板 (ベースウェーハ) を熱酸化 (厚さ 100 nm)、両面研磨した CZシリコン単結晶基板 (ボンドウェーハ) を熱酸化 (厚さ 100 nm) し、結合工程を経て、結合熱処理を 1150 で 2 時間行った。その後、酸化膜除去として、10% HF に浸漬し表面酸化膜を除去し、得られた厚さ 1000 μm (500 μm 基板 2 枚 + 接合層 200 nm)、1250 μm (625 μm 基板 2 枚 + 接合層 200 nm) の結合基板を作製した。そしてそれぞれの結合基板を同一の MOVPE 炉で 8 μm 厚の GaN (中間層 : 4 μm、デバイス層 4 μm) をエピタキシャル成長した。基板厚み 1250 μm のウェーハの反りは、20 μm であった。基板厚み 1000 μm のウェーハでは、50 μm であった。

## 【0045】

## (比較例 2 )

比較例 2 では、FZシリコン単結晶基板と CZシリコン単結晶基板とを貼り合わせた結合基板を作製し、作製した結合基板にエピタキシャル層を成長させた。抵抗率が 0 . 0 0 7 cm、酸素濃度が  $7 \times 10^{17}$  atoms / cm<sup>3</sup> (ASTM'79) の CZシリコン単結晶基板と、抵抗率が 5000 cm、窒素濃度が  $8 \times 10^{14}$  atoms / cm<sup>3</sup> の FZシリコン単結晶基板それぞれの基板の厚みが 625 μm、675 μm のウェーハ (直径 150 mm、結晶方位 (111)) を準備した。

CZシリコン単結晶基板 (ベースウェーハ) を熱酸化 (厚さ 100 nm)、両面研磨した FZシリコン単結晶基板 (ボンドウェーハ) を熱酸化 (厚さ 100 nm) し、結合工程を経て、結合熱処理を 1150 で 2 時間行った。その後、酸化膜除去として、10% HF に浸漬し表面酸化膜を除去し、得られた厚さ 1250 μm (625 μm 基板 2 枚 + 接合層 200 nm)、1350 μm (675 μm 基板 2 枚 + 接合層 200 nm) の結合基板を作製した。そしてそれぞれの結合基板を同一の MOVPE 炉で 8 μm 厚の GaN (中間層 : 4 μm、デバイス層 4 μm) をエピタキシャル成長した。基板厚み 1250 μm のウェーハの反りは、25 μm であった。基板厚み 1350 μm のウェーハでは、15 μm であった。

## 【0046】

## (比較例 3 )

比較例 3 では、FZシリコン単結晶基板同士を貼り合わせた結合基板を作製し、作製した結合基板にエピタキシャル層を成長させた。抵抗率が 5000 cm、窒素濃度が  $8 \times 10^{14}$  atoms / cm<sup>3</sup> の FZシリコン単結晶基板の厚みが 625 μm、675 μm のウェーハ (直径 150 mm、結晶方位 (111)) それぞれ 2 枚を準備した

FZシリコン単結晶基板 (ベースウェーハ) 1 を熱酸化 (厚さ 100 nm)、両面研磨した FZシリコン単結晶基板 (ボンドウェーハ) 2 を熱酸化 (厚さ 100 nm) し、結合工程を経て、結合熱処理を 1150 で 2 時間行った。その後、酸化膜除去として、10% HF に浸漬し表面酸化膜を除去し、得られた厚さ 1250 μm (625 μm 基板 2 枚 + 接合層 200 nm)、1350 μm (675 μm 基板 2 枚 + 接合層 200 nm) の結合基板を作製した。そしてそれぞれの結合基板を同一の MOVPE 炉で 8 μm 厚の GaN (中間層 : 4 μm、デバイス層 4 μm) をエピタキシャル成長した。基板厚み 1250 μm のウェーハの反りは、30 μm であった。基板厚み 1350 μm のウェーハでは、20 μm であった。

## 【0047】

## (比較例 4 )

比較例 4 では、CZシリコン単結晶基板の厚みを比較例 1 よりもさらに薄くして、比較例 1 と同様に基板を作製した。抵抗率が 0 . 0 0 7 cm 以下、酸素濃度が  $7 \times 10^{17}$

10

20

30

40

50

$\text{atoms/cm}^3$  (ASTM'79) のCZシリコン基板で、基板の厚みが $400\mu\text{m}$ と $400\mu\text{m}$ のウェーハ(直径 $150\text{mm}$ 、結晶方位 $(111)$ )を準備した。

CZシリコン単結晶基板(ベースウェーハ)1を熱酸化(厚さ $50\text{nm}$ )、両面研磨したCZシリコン単結晶基板(ボンドウェーハ)2を熱酸化(厚さ $50\text{nm}$ )し、結合工程を経て、結合熱処理を $1150^\circ\text{C}$ で2時間行った。その後、酸化膜除去として、 $10\%$ HFに浸漬し表面酸化膜を除去し、得られた厚さ $800\mu\text{m}$ ( $400\mu\text{m}$ 基板2枚+接合層 $100\text{nm}$ )の結合基板を作製した。そして基板をMOVPE炉で $8\mu\text{m}$ 厚のGaN(中間層: $4\mu\text{m}$ 、デバイス層 $4\mu\text{m}$ )をエピタキシャル成長した。ウェーハの反りは $200\mu\text{m}$ であった。

#### 【0048】

10

##### (比較例5)

比較例5では、CZシリコン単結晶基板の貼り合わせを行わずにエピタキシャル層を成長させた。抵抗率が $0.007\text{cm}$ 以下、酸素濃度が $7 \times 10^{17}\text{atoms/cm}^3$ (ASTM'79)のCZシリコン基板で、基板の厚みが $625\mu\text{m}$ のウェーハ(直径 $150\text{mm}$ 、結晶方位 $(111)$ )を準備した。

そして基板をMOVPE炉で $8\mu\text{m}$ 厚のGaN(中間層: $4\mu\text{m}$ 、デバイス層 $4\mu\text{m}$ )をエピタキシャル成長した。ウェーハの反りは $300\mu\text{m}$ であった。

#### 【0049】

上記の結果から、実施例1のように、抵抗率が $0.1\text{cm}$ 以下のCZシリコン単結晶基板を貼り合わせ、貼り合わせ後の接合基板の厚さを $2000\mu\text{m}$ より厚くした場合は、窒化物半導体膜を形成させた場合に、ウェーハの反りが最も小さいものとなった。一方で、同様の抵抗率を有するCZシリコン単結晶基板を用いても、比較例1、4、5のように、基板の厚さが $2000\mu\text{m}$ 以下の場合は、ウェーハの反りがより大きくなることがわかった。また、比較例1と比較例2、3との比較から、同様の基板の厚さであっても、CZシリコン単結晶基板と比較して軟らかいFZシリコン単結晶基板を用いると、ウェーハの反りがより大きくなることがわかった。

20

#### 【0050】

なお、本発明は、上記実施形態に限定されるものではない。上記実施形態は例示であり、本発明の特許請求の範囲に記載された技術的思想と実質的に同一な構成を有し、同様な作用効果を奏するものは、いかなるものであっても本発明の技術的範囲に包含される。

30

#### 【符号の説明】

#### 【0051】

- 1 0 ... 電子デバイス用基板、

- 1、2 ... (複数の)シリコン単結晶基板、 3 ... 接着層、 4 ... 中間層、

- 5 ... 窒化物半導体膜(デバイス層)、 6 ... 接合基板。

40

50

【図面】

【図 1】

10

20

30

40

50

---

フロントページの続き

(56)参考文献      特開2007-246289(JP,A)

特開2018-041851(JP,A)

特開2010-225947(JP,A)

特開2011-103380(JP,A)

(58)調査した分野 (Int.Cl., DB名)

C30B 29/38

C30B 25/02