(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4843927号

(P4843927)

(45) 発行日 平成23年12月21日(2011.12.21)

(24) 登録日 平成23年10月21日(2011.10.21)

(51) Int.Cl.

F 1

HO1L 27/04 (2006.01)

HO1L 21/822 (2006.01)

HO1L 21/338 (2006.01)

HO1L 29/812 (2006.01)

HO1L 21/8232 (2006.01)

HO1L 27/04

HO1L 29/80

HO1L 27/06

H

P

F

請求項の数 5 (全 12 頁) 最終頁に続く

(21) 出願番号

特願2004-298955 (P2004-298955)

(22) 出願日

平成16年10月13日 (2004.10.13)

(65) 公開番号

特開2006-114618 (P2006-114618A)

(43) 公開日

平成18年4月27日 (2006.4.27)

審査請求日

平成19年9月26日 (2007.9.26)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 小浜 一正

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

審査官 田代 吉成

最終頁に続く

(54) 【発明の名称】高周波集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

入出力端子を有する高周波回路と、

化合物半導体基板上に少なくとも一部が前記高周波回路と一体的に形成され、ソースとドレインの一方が前記高周波回路の入出力端子に接続され、ゲートが第1の抵抗を介してコントロール信号の入力端子に接続されたディプレッションタイプ電界効果トランジスタと、

前記化合物半導体基板上に形成され、前記高周波回路に設けられ、ソースとドレインの一方が前記ディプレッションタイプ電界効果トランジスタの前記ソースとドレインの他方に接続され、ソースとドレインの他方が基準電位に接続され、ゲートが第2の抵抗を介して前記基準電位に接続されたエンハンスマントタイプ電界効果トランジスタと、

前記エンハンスマントタイプ電界効果トランジスタの前記ソースとドレインの一方と前記基準電位間に接続された第1のキャパシタと

を有する高周波集積回路。

## 【請求項 2】

前記高周波集積回路は更に第2のキャパシタを有し、該第2のキャパシタは前記ディプレッションタイプ電界効果トランジスタまたは前記エンハンスマントタイプ電界効果トランジスタのソースとドレイン間に接続された

請求項1記載の高周波集積回路。

## 【請求項 3】

前記化合物半導体基板は G a A s を有する基板である

請求項 1 または 2 記載の高周波集積回路。

【請求項 4】

前記エンハンスマントタイプ電界効果トランジスタは H E M T とする

請求項 1 または 2 記載の高周波集積回路。

【請求項 5】

前記エンハンスマントタイプ電界効果トランジスタは複数のエンハンスマントタイプ電界効果トランジスタで接続された

請求項 1 記載の高周波集積回路。

【発明の詳細な説明】

10

【技術分野】

【0 0 0 1】

本発明は、 M M I C ( M o n o l i t h   M i c r o w a v e   I n t e g r a t e d   C i r c u i t ) の静電保護素子付き高周波集積回路に関し、さらに詳しくは、高周波 M M I C の入力または出力部に静電保護素子を設け、静電放電 ( E S D : E l e c t r i c   S t a t i c   D i s c h a r g e ) 保護に関する。

【背景技術】

【0 0 0 2】

セルラーなどでは、 8 0 0 M H z ~ 2 . 3 G H z の帯域の高周波信号を用いて通信を行っている。この周波数が比較的高いため、送信電力を増幅するパワーアンプ ( P A ) 、受信信号を増幅するローノイズアンプ ( L N A ) 、信号を切り替えるスイッチ ( S W ) などを用いたデバイスの選定において、高周波特性を重視して、通常使用される S i 半導体にかわり、 G a A s などの化合物半導体を用いる場合が多い。

20

G a A s など化合物半導体を用いた高周波集積回路は、一般に、優れた高周波特性を有するが、 E S D ( 静電放電 ) に対して非常に弱い場合が多い。これは、その中で用いられる各デバイス自身が、高周波特性の向上のため、 E S D などのノイズに対して脆弱であることも一つの原因である。また、保護素子を導入した場合、取り扱う周波数が高いため、寄生容量による悪影響が避けられず、十分な対策がとられない場合も多い。

【0 0 0 3】

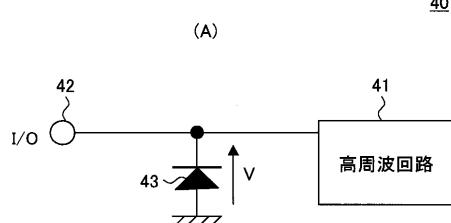

図 4 ( A ) に、従来の E S D 保護素子付の E S D 保護回路 4 0 の回路構成例を示す。 I / O ( 入出力 ) 端子 4 2 と G N G ( グランド ) の間に、 E S D 対策用の D i o d e 4 3 を接続してあり、正の D C ( 直流 ) バイアス、または、その D i o d e 4 3 の順方向閾値電圧 ( V f ) 以下の R F 振幅を持つ R F 信号であれば、この D i o d e 4 3 は、比較的、高インピーダンスに見え、回路特性に影響を与えない。一方、 E S D のような電圧振幅の大きいノイズが I / O ( 入出力 ) 端子 4 2 に印加されると、保護 D i o d e 4 3 の逆方向のブレークダウン電圧 ( V b ) を超え、ノイズは G N D へ引き込まれ、回路内部 ( 高周波回路 4 1 ) へのダメージを避けることができる。

30

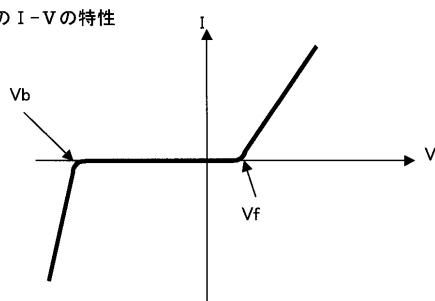

【0 0 0 4】

図 4 ( B ) にダイオードの電圧 - 電流特性を示す。横軸に D i o d e 4 3 に印加する電圧を示し、縦軸にこの D i o d e 4 3 に流れる電流の値を示す。このグラフから明らかのように、順方向に電圧を印加すると V f ( 順方向しきい値電圧 ) から電流が流れ、また逆方向に電圧を印加すると、 V b ( ブレークダウン電圧 ) まではほとんど電流は流れない。しかし、逆方向の印加電圧が V b を越えると、急激に電流が流れるようになる。その結果、 D i o d e 4 3 の抵抗 ( V / I ) は小さくなる。

40

S i 上で保護 D i o d e を作り込む場合、 D i o d e の正極、または、負極は、低抵抗である基板バルク側に取ることができる。一方、図 4 のような D i o d e 4 3 を G a A s 基板上に作り込む場合、 G a A s 基板自体が高抵抗であるため、 D i o d e の正極と負極の両方を基板表面に取り出す必要があり、構造が複雑になり、また、保護素子としての能力を引き出すのも難しい。さらに、 D i o d e を構成するため、 P N   J u n c t i o n ( 接合 ) 、 ショットキー J u n c t i o n などを用いるが、基本的に、この J u n c t

50

ionは、ESDなどに対して強くはなく、高性能なESD素子を得ることは困難である。

さらに、このJunction部分は、大きな寄生容量を持つため、高周波特性に悪影響を与えるやすい。

#### 【0005】

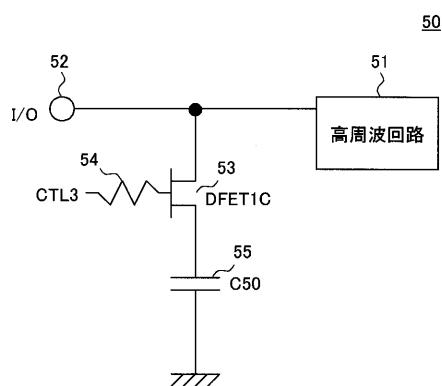

保護素子を有しない他の従来例の高周波集積回路50について図5に示す。図5において、高周波回路51の入力端子I/O52にDFET1C(Depletion型電界効果トランジスタ；ディプレッションタイプ電界効果トランジスタ)53のドレインが接続され、ソースはキャパシタC50(55)の一方の端子に接続され、キャパシタC50の他方の端子はGND(グランド)に接続されている。またゲートは抵抗54を介してコントロール端子(CTL3)に接続されている。10

ここでDFET1C(53)の直流バイアスを構成する抵抗は省略して、高周波(交流)信号に関する回路だけを図示する。

CTL3から基準電圧を抵抗54を介して、DFET1C(53)のゲートに電圧を印加し、ON/OFF動作させて、スイッチとして機能させている。

このCTL3端子に所定の電圧を印加して、DFET1C(53)をON状態とすると、I/O入力端子52から高周波信号が入力されても、DFET1Cのドレイン-ソースとキャパシタC50を介して流れ、高周波回路51には高周波信号は入力されない。

つぎに、DFET1CをOFF状態にして、入力信号を高周波回路51に供給する。この状態において、たとえばI/O入力端子52に高電圧ノイズまたは高電圧パルスが印加されたとすると、D電界効果トランジスタ(DFET1C)53は通常はOFF状態であるので、DEFT1Cの出力インピーダンスが高いので、キャパシタC50にパルス電流を急激に流すことはできず、高周波回路51の入力または出力に入力され、その結果高周波回路51の内部素子が破壊される。20

#### 【0006】

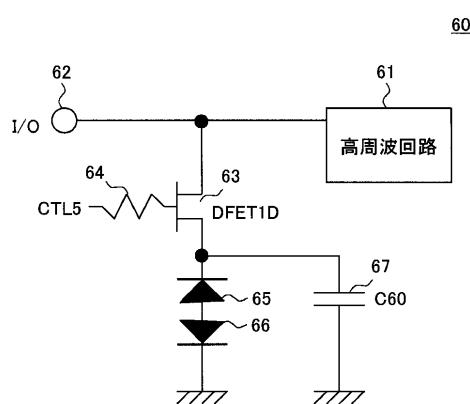

図5を改善するため保護素子を高周波回路61の入力端子または出力端子に設けた例を示す。図6は図5で示した高周波集積回路50に保護Diodeを追加した他の従来例を示す。図6において、高周波回路61の入力端子I/O62にD電界効果トランジスタ(DFET1D；ディプレッションタイプ電界効果トランジスタ)63のドレインが接続され、ソースはキャパシタC60(67)の一方の端子に接続され、キャパシタC60の他方の端子はGNDに接続されている。ソースはさらにDiode65のカソードに接続され、アノードはDiode66のアノードに接続されている。Diode66のカソードはGNDに接続されている。またD電界効果トランジスタ63のゲートは抵抗64を介してコントロール5(CTL5)に接続されている。30

CTL5から基準電圧を抵抗64を介して、D電界効果トランジスタ63のゲートに電圧を印加している。

#### 【0007】

D電界効果トランジスタ63のソースとGND間に2個のDiode65,66を用いて、アノードが共通接続され、両端にカソードを配置し、一方のカソードをD電界効果トランジスタ1D63のソースに他方のカソードをGNDに接続した保護素子が設けられている。この保護素子の電気的入出力特性は、入力電圧が順方向と逆方向ともVb+Vfの電圧の絶対値より小さいとき電流は流れず高抵抗となり、Vb+Vfの絶対値より大きいとき電流が急激に流れ、低抵抗になる。40

#### 【0008】

入出力端子I/O(62)からの高電圧ノイズまたは高電圧パルスが入力されると、D電界効果トランジスタ1D63がフローティング状態であるので、ドレイン-ソース間は導通状態となる。入力された電圧がDiode65,66の加算された耐圧以上になると、上述したようにDiode65,66がブレーキダウンを起こし、その合成抵抗値は高抵抗から低抵抗に変化する。その結果、低抵抗の電流通路を形成するDiode65,66を介してGNDに放電され、高周波回路61にノイズまたは高圧パルスは印加されなく50

なる。

#### 【0009】

しかしながら、この保護ダイオード付き高周波集積回路の例においても、図4と同様に、Diode 65, 66をGaN基板上に作り込む場合、GaN基板自体が高抵抗であるため、Diodeの正極と負極の両方を基板表面に取り出す必要があり、構造が複雑になり、また、保護素子としての能力を引き出すのも難しい。さらに、Diodeを構成するため、PN Junction、ショットキー Junctionなどを用いるが、基本的に、この Junctionは、ESDなどに対して強くはなく、高性能なESD素子を得ることは困難である。

さらに、この Junction部分は、大きな寄生容量を持つため、高周波特性に悪影響を与えるやすい。

#### 【0010】

【特許文献1】特開平6-13862号公報

【特許文献2】特表2000-510653号公報

【発明の開示】

【発明が解決しようとする課題】

#### 【0011】

前述のように、一般的に、GaN高周波集積回路は、ESD的に脆弱で、その対策も困難である。一方、携帯電話に代表されるコンシューマ用途にGaN高周波集積回路が使用されることも多くなり、優れた高周波性能はもちろん、ESD耐圧も大きいGaN高周波集積回路の実現が望まれている。

本発明は上記課題に鑑みてなされたものであり、ESD保護能力が高い素子を用いて優れた高周波特性と、高いESD耐圧の両立する保護回路付き高周波回路を提供することである。

【課題を解決するための手段】

#### 【0012】

本発明の高周波集積回路は、入出力端子を有する高周波回路と、化合物半導体基板上に少なくとも一部が前記高周波回路と一体的に形成され、ソースとドレインの一方が前記高周波回路の入出力端子に接続され、ゲートが第1の抵抗を介してコントロール信号の入力端子に接続されたディプレッショントランジスタと、前記化合物半導体基板上に形成され、前記高周波回路に設けられ、ソースとドレインの一方が前記ディプレッショントランジスタのソースとドレインの他方に接続され、ソースとドレインの他方が基準電位に接続され、ゲートが第2の抵抗を介して前記基準電位に接続されたエンハンスマントトランジスタと、前記エンハンスマントトランジスタの前記ソースとドレインの一方と前記基準電位間に接続された第1のキャパシタとを有する。

#### 【0015】

本発明は、高周波回路の入出力端子にエンハンスマントトランジスタ(電界効果トランジスタ)を備え、外部からノイズまたは高電圧パルスが入力されたとき、エンハンスマントトランジスタをブレークダウン動作させ、そのインピーダンスを低くすることにより、ノイズまたは高電圧パルスを放電させるようにした。

【発明の効果】

#### 【0016】

本発明の静電保護素子付き高周波集積回路は、E電界効果トランジスタ(エンハンスマントトランジスタ)を保護素子と使う場合、高周波回路で使用される、D電界効果トランジスタ(ディプレッショントランジスタ)、または、E電界効果トランジスタと、同じ、または、ほとんど同様な構造であるため、GaN上に作りこむプロセスにおいて、最小限の工程追加で、作製できる。また、Diode型保護素子のように、ESDなどノイズは、Junctionを通過しないため、保護素子自体の能力、耐圧も優れている。さらに、もともと、高周波回路内で用いられる電界効果トラン

10

20

30

40

50

ジスタと、同様な構造であるため、寄生容量も小さく、本来の回路に与える悪影響も小さい。

【発明を実施するための最良の形態】

【0017】

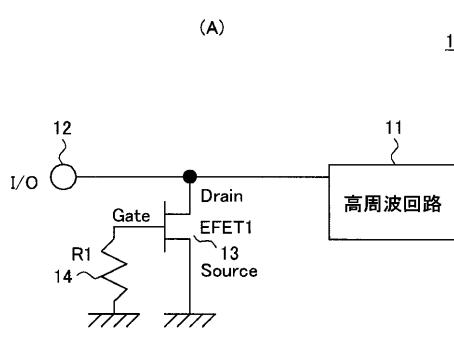

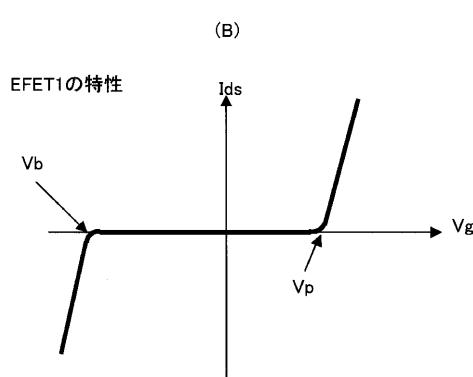

図1に静電保護素子付き高周波集積回路(回路)の実施形態例を示す。図1(A)において、入出力端子I/O12が高周波回路11に接続され、またE電界効果トランジスタ(エンハンスマント電界効果トランジスタ)1(13)のドレインに接続されている。ソースはGND(グランド)に接続され、またゲートは抵抗R1(14)を介してGNDに接続されている。

このE電界効果トランジスタ(EFET1)13は高周波回路11の素子、たとえば受信用RFアンプの電界効果トランジスタ、MIXなどや、送信用電界効果トランジスタなどと同一基板上に形成されている。

E電界効果トランジスタ13のゲートが0Vのとき、ソース接地E電界効果トランジスタの電気的特性を図1(B)に示す。横軸にVg(ゲート-ソース間電圧)、縦軸にドレイン電流Idsを示す。VgがVp(ピンチオフ電圧)以下のとき電流は流れずハイインピーダンスであり、Vp以上になるとドレイン電流Idsが流れ始めその結果低インピーダンスとなる。

一方Vdsに負の電圧が印加されブレークダウン電圧(Vb)より小さいとき、ドレイン電流は流れず、ハイインピーダンス状態である。しかし、Vbの絶対値より大きい負の電圧になると急激にドレイン電流Idsが流れはじめ低インピーダンスとなる。

【0018】

E電界効果トランジスタ13は、エンハンスマント(Enhancement)型であり、そのゲートは、抵抗R1(14)を介してGNDにバイアスされているため、OFF状態となっている。そのため、I/O端子12が正にバイアスされた場合や、小振幅のRF信号が入力された場合には、E電界効果トランジスタ1自体は高インピーダンスに見える。

一方、ESDのような電圧振幅の大きいノイズ信号などが入ると、E電界効果トランジスタ13の耐圧を超え、E電界効果トランジスタ13は低インピーダンス状態となりノイズはGNDに引き込まれ、高周波回路11内部にはダメージを与えない。E電界効果トランジスタを保護素子と使う場合、このE電界効果トランジスタ13は高周波回路11で使用される、D電界効果トランジスタ、または、E電界効果トランジスタと、同じ、または、ほとんど同様な構造であるため、GaN上に作りこむプロセスにおいて、最小限の工程追加で、作製できる。また、Diode型保護素子のように、ESDなどノイズは、junctionを通過しないため、保護素子自体の能力、耐圧も優れている。さらに、もともと、高周波回路内で用いられる電界効果トランジスタと、同様な構造であるため、寄生容量も小さく、本来の回路に与える悪影響も小さい。

今まで高周波回路11の入力端子側で説明したが、出力端子側でも同様に適用できる。さらに、エンハンスマントタイプ電界効果トランジスタやディプレッションタイプ電界効果トランジスタはMESFET、ゲート接合型FET, HEMTなどで構成することができる。

【0019】

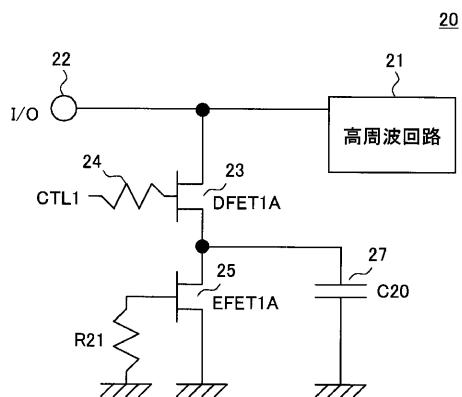

図2に、静電保護素子付き高周波集積回路20の別の実施形態例を示す。図2において、高周波回路21の入力端子I/O22にD電界効果トランジスタ(DFET1A;ディプレッションタイプ電界効果トランジスタ)23のドレインが接続され、ゲートは抵抗24の一方の端子に接続され、他方の端子は制御端子(CTL1)に接続されている。またソースはE電界効果トランジスタ(EFET1A;エンハンスマント電界効果トランジスタ)25のドレインに接続され、ソースはGNDにまたゲートも抵抗R1(26)を介してGNDにそれぞれ接続されている。E電界効果トランジスタ25のドレインはキャパシタC20の一方の端子に接続され、他方の端子GNDに接続されている。

このE電界効果トランジスタ25は高周波回路21の素子、たとえば受信用RFアンプ

10

20

30

40

50

の電界効果トランジスタ、MIXなどや、送信用電界効果トランジスタなどと同一基板上に形成されている。

### 【0020】

ここで、D電界効果トランジスタ23のDCバイアスについては省略し、高周波回路のみ図示してある。

D電界効果トランジスタ23は、コントロール信号をCTL1に印加することにより、ON/OFFさせる信号切り替え用スイッチトランジスタである。また、高周波バイパス用のC20(27)とE電界効果トランジスタ25により、D電界効果トランジスタ23は、DC的にGND電位から隔離させており、D電界効果トランジスタ23は適当なバイアスに設定されている。

抵抗R21を介してD電界効果トランジスタ25のゲートにCTL1の電圧を供給すると、D電界効果トランジスタ23はON動作状態となり、入力端子I/O22から入力された高周波信号は、D電界効果トランジスタ23のドレイン-ソースを通り、キャパシタC20(27)を介してグランドに流れる。その結果、入力高周波信号は高周波回路21には入力されない。すなわち、スイッチ用トランジスタとしてのD電界効果トランジスタ23がONのとき、この高周波集積回路20はOFFされた状態で、高周波回路21には信号が入力されない。

つぎに、スイッチ用トランジスタのD電界効果トランジスタ23がOFF状態で、高周波集積回路20がON状態の場合において、高周波回路21に信号が入力される時、入力端子I/O22から高電圧ノイズまたは高電圧パルスが入力されたときの動作について説明する。

すなわち、高周波回路21が動作状態のとき、外部から入力端子I/O22を介して高電圧ノイズまたは高電圧パルスなどが印加された場合、CTL1から制御電圧が印加されていない状態においてD電界効果トランジスタ23のゲートはフローティング状態となっているが、高電圧がドレインに印加された状態では導通するので、E電界効果トランジスタ25に高電圧が印加される。この印加電圧がE電界効果トランジスタ25の耐圧以上の場合、すなわちブレイクダウン電圧以上になるとドレイン-ソース間の抵抗は急激に小さくなり、入力端子I/O22から入力された高電圧ノイズまたは高電圧パルスにより発生する電荷(電流)は、このE電界効果トランジスタ25を介してGNDに引き込まれる。

この結果、高電圧ノイズや高電圧パルスは高周波回路21に流れないので、スイッチ用トランジスタのD電界効果トランジスタ23と静電保護用トランジスタのE電界効果トランジスタ25を介してGNDに流れる。したがって、高周波回路21内に設けられたトランジスタの能動素子やキャパシタなどの受動素子は破壊されない。

しかも、通常の入力信号が入力端子I/O22から入力されるときは、D電界効果トランジスタ23はOFF状態でありかつ保護素子のE電界効果トランジスタ25もOFF(ブレークダウンしていない)状態であるので、これらのインピーダンスは従来の保護Diodeと比較して高いので、高周波回路21の入力側で高周波特性を劣化させることなく、従来の保護素子としてDiodeを用いた高周波集積回路よりすぐれた周波数特性を維持することができる。

いままで高周波回路21の入力端子側で説明したが、出力端子側でも同様に適用できる。さらに、エンハンスマントタイプ電界効果トランジスタやディプレッションタイプ電界効果トランジスタはMESFET、ゲート接合型FET, HEMTなどで構成することができる。

### 【0021】

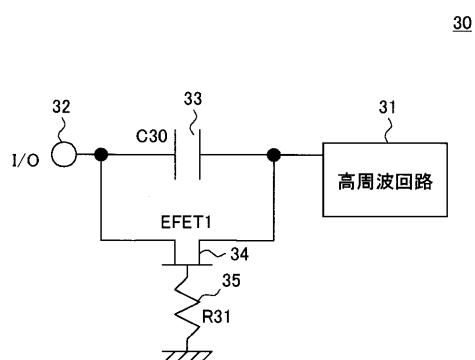

図3に保護素子としてEFET1B(34)を用いた高周波集積回路30の他の実施形態例を示す。図3において、入出力端子I/O32がキャパシタC30(33)の一方の端子に接続され、このキャパシタC30(33)の他方の端子が高周波回路31の入力または出力端子に接続されている。また、入出力端子I/O32(33)にE電界効果トランジスタ(EFET1B)34のソース(またはドレイン)が接続され、キャパシタC30(33)の他方の端子にドレイン(またはソース)が接続されている。さらのゲートは

抵抗 R 3 1 ( 3 5 ) を介して G N D に接続されている。

この E 電界効果トランジスタ 3 4 は高周波回路 3 1 の素子、たとえば受信用 R F アンプの電界効果トランジスタ、M I X などや、送信用電界効果トランジスタなどと同一基板上に形成されている。

#### 【 0 0 2 2 】

入出力端子 I / O 3 2 と高周波回路 3 1 の入出力間に接続されたキャパシタ C 3 0 ( 3 3 ) は、たとえば集積回路内部の高周波回路 3 1 と I / O 端子 ( 3 2 ) 外のバイアス ( 例えれば I / O ( 3 2 ) 外側は、G N D にバイアスされる。 ) を隔離する役目である。通常、G a A s 上に作られる容量は E S D に対して弱く、E S D 入力時には、内部が破壊される前に、このキャパシタ C 3 0 ( 3 3 ) が破壊されることも多い。一方、この例では、E 電界効果トランジスタ 3 4 を、キャパシタ C 3 0 とパラレルに接続しており、そのゲート端子を抵抗 R 3 1 ( 3 5 ) により G N D にバイアスされているため、E 電界効果トランジスタ 3 4 は O F F 状態を保たれ、高周波回路 ( 3 1 ) 側は、適当なバイアスを印加することが可能である。10

通常動作で、入力端子 I / O 3 2 から高周波信号が入力されるときは、キャパシタ C 3 0 ( 3 1 ) を介して、高周波回路 3 1 に入力される。この保護素子としての E 電界効果トランジスタ 3 4 の O F F 時の入出力インピーダンスは高く、また寄生容量も小さいので、キャパシタ C 3 0 ( 3 3 ) の容量値で高周波回路 3 1 の入力または出力の周波数特性は決まる。

つぎに、高電圧ノイズや高電圧パルスが I / O 端子 3 2 から入力され、E 電界効果トランジスタ 3 4 に印加される電圧がブレークダウン電圧以上になると、ソース - ドレイン間は低抵抗になるので、高電圧ノイズや高電圧パルスはキャパシタ C 3 0 ( 3 3 ) を通らないで、E 電界効果トランジスタ 3 4 を通過する。20

そのため、キャパシタ C 3 0 ( 3 3 ) の破壊を防ぐことができる。E S D は、このキャパシタ C 3 0 ( 3 3 ) と E 電界効果トランジスタ 3 4 の部分で一部反射され、さらに、高周波回路 ( 3 1 ) 内部で、対策をとるなどして、E S D 破壊を防ぐことができる。

いままで高周波回路 3 1 の入力端子側で説明したが、出力端子側でも同様に適用できる。さらに、エンハンスマントタイプ電界効果トランジスタやディプレッションタイプ電界効果トランジスタは M E S F E T 、ゲート接合型 F E T , H E M T などで構成することができる。30

#### 【 0 0 2 3 】

さらに、他の実施形態例として、図 3 において、キャパシタ C 3 0 ( 3 3 ) と高周波回路 3 1 の間にたとえば図 1 または図 2 に示した E S D 保護回路を設け、キャパシタ C 3 0 ( 3 3 ) だけでなく、上述の高周波回路 3 1 を更に保護することができる。

#### 【 0 0 2 4 】

このように、図 1 ~ 3 の実施形態例では、E S D に用いる保護素子をたとえば高周波回路集積回路の一部と同一の G a A s 基板上に形成することにより、G a A s 高周波集積回路の製造での追加工程が少なく、E S D 保護能力が高い、非常にシンプルな E 電界効果トランジスタ型保護素子により、従来、難しかった、優れた高周波特性と高い E S D 耐圧を両立できる。40

#### 【 0 0 2 5 】

表 1 に E S D の測定結果を示す。E S D 評価方法として、機械モデル ( M a c h i n e M o d e l ) と人体モデル ( H u m a n B o d y M o d e l ) などがある。機械モデルは、電子工業会規格 E I A / J E S D 2 2 - A 1 1 5 - A 等に規格化されていて、静電気を帯びている機械装置が素子のリード端子などに接触するときに発生する静電ストレスをモデル化したものである。

また、人体モデルは、たとえば電子工業会規格 E I A / J E S D 2 2 - A 1 1 4 に規格化されていて、静電気を帯びている人間が素子のリード端子などに接触するときに素子に発生する静電ストレスをモデル化したものである。

#### 【 0 0 2 6 】

10

20

30

40

50

ESD評価装置は可変電圧直流電源と充電用抵抗が直列接続された充電回路と、充電用キャパシタと、充電回路と放電回路間に設けられ、いずれか一方を選択する切り換えるスイッチと、充電用キャパシタに蓄積された電荷がスイッチを介して放電用抵抗と被測定素子(DUT)に印加される放電回路とから構成されている。

たとえば人体モデルの場合、ESD評価装置の充電用抵抗、放電用抵抗と充電用キャパシタの値は、それぞれ1MΩ、1.5kΩ、100pFと規定されている。

また一般に被測定素子は、着脱可能なようにソケットなどに装着された状態で測定される。

#### 【0027】

評価方法は、可変電圧直流電源を測定(充電)電圧に設定して、スイッチを切り換えて充電用抵抗側に接続し、充電用キャパシタに充電する。次に、スイッチを切り換えて放電用抵抗に接続し、充電用キャパシタに蓄積された電荷を放電用抵抗を介して被測定素子に印加する。それと同時に被測定素子の電気的特性の劣化を調べる。可変電圧直流電源の電圧をマイクロコンピュータなどを用いて自動的に充電電圧を任意に可変して同様な測定を行い、得られた結果をもとに演算処理して、印加電圧に伴う被測定素子の劣化状況を調べる。

#### 【0028】

以下、保護素子の有無に伴うESD強度を比較する。図5に示す従来例の保護素子の無い高周波集積回路は、本発明の図2の実施例の高周波集積回路に対応し、ESD保護用のE電界効果トランジスタ25がない構成となっている。図6は、Diode型保護素子を用いた例である。図2、5、6はいずれもGaN電界効果トランジスタを用いたスイッチMMIC(マイクロ波集積回路)で、それぞれのMMICを、マシンモデル(300pF, 0°の条件)と人体帶電モデル(100pF, 1500°の条件)で、ESD破壊強度試験を行った結果である。

表1には、回路構成が同じで保護Diode無しの図5、保護Diode付きの図6、そして電界効果トランジスタ保護素子付きの高周波集積回路の実施形態例の図2について、機械モデル(Machine Model)と人体モデル(Human Body Model)の測定結果を示す。

マシンモデルのとき、図5に示す保護素子無し高周波集積回路のESD強度は150V、図6に示すDiode保護素子付きの高周波集積回路のESD強度は200V、250Vであり、図3に示すE電界効果トランジスタ保護素子付きの高周波集積回路は300Vである。

すなわち、E電界効果トランジスタ保護素子付きの高周波集積回路は保護Diode無しと比較して約2倍のESD強度があり、またDiode保護付きと比較しても50~100V以上のESD強度が高い結果が得られた。

また、人体帶電モデルのとき、図5に示す保護素子無し高周波集積回路のESD強度は500Vと1000V、図6に示すDiode保護素子付きの高周波集積回路のESD強度は1000V、1500Vであり、図3に示すE電界効果トランジスタ保護素子付きの高周波集積回路は1500Vと2000Vである。その結果、E電界効果トランジスタ保護素子付きの高周波集積回路は保護Diode無しの高周波集積回路と比較して約2~3倍のESD強度があり、またDiode保護付き高周波集積回路と比較しても約1.5倍以上のESD強度が高い結果が得られた。

本発明の図2の回路は、明らかに、Diode保護素子タイプの図6の場合と保護素子が無い図5の場合に比べ、高いESD耐圧を有しており、その優位性が確認できた。

#### 【0029】

【表 1】

## E S D 強度試験結果

|                       | E 電界効果トランジスタ型保護素子<br>図 2 の例 | 保護素子なし<br>図 5 の例 | Diode 型保護素子<br>図 6 の例 |    |

|-----------------------|-----------------------------|------------------|-----------------------|----|

| マシンモデル<br>GND 基準 +印加  | 300V                        | 150V             | 200V                  | 10 |

| マシンモデル<br>GND 基準 +印加  | 300V                        | 150V             | 250V                  |    |

| 人体帶電モデル<br>GND 基準 +印加 | 1500V                       | 500V             | 1000V                 |    |

| 人体帶電モデル<br>GND 基準 -印加 | 2000V                       | 1000V            | 1500V                 | 20 |

## 【0030】

このように、本高周波集積回路は、高周波集積回路の入出力端子にエンハンスマントタイプ電界効果トランジスタを備え、外部からノイズまたは高電圧パルスが入力されたとき、エンハンスマントタイプ電界効果トランジスタをブレークダウン動作させ、そのインピーダンスを低くすることにより、ノイズまたは高電圧パルスを放電させるようにした。

エンハンスマントタイプだけでなく、ディプレッションタイプ電界効果トランジスタを用いても高周波回路のDCカップリングキャパシタを保護できる。さらにこれらを組み合わせることにより高周波回路の入力または出力のE S D強度を高めることができる。

また保護素子としてのエンハンスマントタイプ電界効果トランジスタを少なくとも高周波回路の一部と同一のG a A s基板に形成することにより、構造を単純化することができた。また、J u n c t i o n D i o d e保護素子と比較して寄生容量も小さくできるので、E S D耐圧を向上するとともに、優れた高周波特性も維持することもできる。

## 【図面の簡単な説明】

## 【0031】

【図1】本発明の静電保護素子付き高周波集積回路の全体回路構成を示す回路図である。

【図2】本発明の静電保護素子付き高周波集積回路の全体回路構成を示す回路図である。

【図3】本発明の静電保護素子付き高周波集積回路の全体回路構成を示す回路図である。

【図4】従来例の保護ダイオードを用いた静電保護素子付き高周波集積回路の全体回路構成を示す回路図である。

【図5】従来例の静電保護素子無しの高周波集積回路の全体回路構成を示す回路図である。

【図6】従来例の複数のダイオードを用いた静電保護素子付き高周波集積回路の全体回路構成を示す回路図である。

## 【符号の説明】

## 【0032】

1 0 , 2 0 , 3 0 , 4 0 , 6 0 ... 静電保護素子付き高周波集積回路、1 1 , 2 1 , 3 1 , 4 1 , 5 1 , 6 1 ... 高周波回路、1 2 , 2 2 , 4 2 , 5 2 , 6 2 ... 入出力端子(外部端子)

10

20

30

40

50

) 3 2 ... 外部端子、 1 3 , 2 5 , 2 4 ... E 電界効果トランジスタ (エンハンスマントタイプ電界効果トランジスタ)、 2 3 , 5 3 , 6 3 ... D 電界効果トランジスタ (ディプレッショントライプ電界効果トランジスタ)、 2 1 , 3 1 , 5 4 , 6 4 ... 抵抗、 2 7 , 3 3 , 5 5 , 6 7 ... キャパシタ、 4 3 , 6 5 , 6 6 ... D i o d e (ダイオード)。

【図 1】

【図 2】

【図 3】

【図4】

【図5】

ダイオードの I-V の特性

【図6】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/06 (2006.01)

(56)参考文献 特開平4-49652 (JP, A)

特開平11-154733 (JP, A)

特開平5-136360 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/822

H 01 L 21/338

H 01 L 21/8232

H 01 L 27/04

H 01 L 27/06

H 01 L 29/812