(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6139482号

(P6139482)

(45) 発行日 平成29年5月31日(2017.5.31)

(24) 登録日 平成29年5月12日(2017.5.12)

|                         |                                    |

|-------------------------|------------------------------------|

| (51) Int.Cl.            | F 1                                |

| G 0 9 F 9/30 (2006.01)  | G 0 9 F 9/30 3 3 8                 |

| H 0 1 L 51/50 (2006.01) | G 0 9 F 9/30 3 6 5                 |

| H 0 5 B 33/26 (2006.01) | H 0 5 B 33/14 A<br>H 0 5 B 33/26 Z |

請求項の数 2 (全 45 頁)

|              |                                     |           |                                                |

|--------------|-------------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2014-168083 (P2014-168083)        | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成26年8月21日 (2014.8.21)              | (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (62) 分割の表示   | 特願2013-164974 (P2013-164974)<br>の分割 | (72) 発明者  | 小山 潤<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| 原出願日         | 平成20年12月18日 (2008.12.18)            | (72) 発明者  | 棚田 好文<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号    | 特開2014-222368 (P2014-222368A)       | (72) 発明者  | 三宅 博之<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日     | 平成26年11月27日 (2014.11.27)            |           |                                                |

| 審査請求日        | 平成26年9月1日 (2014.9.1)                |           |                                                |

| 審判番号         | 不服2016-4387 (P2016-4387/J1)         |           |                                                |

| 審判請求日        | 平成28年3月24日 (2016.3.24)              |           |                                                |

| (31) 優先権主張番号 | 特願2007-329579 (P2007-329579)        |           |                                                |

| (32) 優先日     | 平成19年12月21日 (2007.12.21)            |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                            |           |                                                |

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の配線と、

前記第1の配線上方の第1の絶縁膜と、

前記第1の絶縁膜上方の発光素子と、

を有し、

前記発光素子は、第1の電極を有し、

前記第1の配線は、第1の部分と、前記第1の部分より厚さが小さい第2の部分と、を有し、

前記第1の部分の下面是、平坦であり、

前記第1の部分は、0.8 μm以上1.5 μm以下の膜厚を有し、

前記第1の電極は、前記第1の絶縁膜に設けられたコンタクトホールを介して、前記第1の配線の前記第2の部分に電気的に接続されていることを特徴とする表示装置。

## 【請求項 2】

トランジスタと、

前記トランジスタが有する半導体に電気的に接続された第1の配線と、

前記第1の配線上方の第1の絶縁膜と、

前記第1の絶縁膜上方の発光素子と、

を有し、

前記発光素子は、第1の電極を有し、

10

20

前記第1の配線は、第1の部分と、前記第1の部分より厚さが小さい第2の部分と、を有し、

前記第1の部分の下面は、平坦であり、

前記第1の部分は、 $0.8 \mu\text{m}$ 以上 $1.5 \mu\text{m}$ 以下の膜厚を有し、

前記第1の電極は、前記第1の絶縁膜に設けられたコンタクトホールを介して、前記第1の配線の前記第2の部分に電気的に接続されていることを特徴とする表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光素子が各画素に設けられた半導体表示装置に関する。

10

【背景技術】

【0002】

アクティブマトリクス型の半導体表示装置は、マトリクス状に配列された数十～数百万個の各画素に、スイッチング素子と表示素子とが設けられている。該スイッチング素子により、ビデオ信号を画素へ入力した後も表示素子への電圧の印加または電流の供給がある程度維持されるので、アクティブマトリクス型は半導体表示装置の大型化、高精細化に柔軟に対応することができ、今後の半導体表示装置の主流となりつつある。

【0003】

半導体表示装置の大型化に伴って浮上する問題の一つに、抵抗値の増大に起因する、配線の電位の降下が挙げられる。例えば、スイッチング素子として機能するトランジスタのゲート電極に接続された配線（走査線）の電位が降下してしまうと、走査線に入力された信号の波形に乱れが生じ、該トランジスタのスイッチングを的確なタイミングで制御できなくなってしまう。特に、走査線には、水平方向の全ての画素が有するトランジスタのゲート電極が接続されている。半導体表示装置が高精細化されることで画素数が増えると、一つの走査線に接続されるトランジスタの数も増大する。そのため、走査線の電位の降下がより著しくなってしまい、トランジスタのスイッチングを的確に制御することがより困難になる。

20

【0004】

走査線をより抵抗率の低い材料で形成することができれば、電位の降下を抑えることができる。しかし、画素が有するトランジスタのゲート電極と走査線とは、通常、一つの層上に形成された導電膜を、エッチング等により所望の形状に加工（パターニング）することで形成されている。ゲート電極には、トランジスタの作製工程において施される加熱処理に耐えうる程度の耐熱性が要求されるため、ゲート電極及び走査線に用いることができる材料の種類には、制限があった。

30

【0005】

下記の特許文献1には、走査線とは異なる層上において形成された補助配線と、走査線とを接続することで、走査線の電位の降下を抑える液晶表示装置について記載されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平10-198292号公報

40

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、発光素子を表示素子として用いた半導体表示装置は視認性が高く、薄型化に最適であると共に、視野角にも制限が無いため、CRT (cathode ray tube) や液晶表示装置に替わる半導体表示装置として注目されている。発光素子を用いたアクティブマトリクス型の半導体表示装置は、具体的に提案されている構成がメーカーによって異なるが、通常、少なくとも発光素子と、画素へのビデオ信号の入力を制御するトランジスタ（スイッチング用トランジスタ）と、該発光素子に供給する電流値を制御するト

50

ランジスタ（駆動用トランジスタ）とが、各画素に設けられている。

【0008】

液晶素子は一対の電極間に印加される電圧の大きさに従って階調を表示する表示素子であるのに対し、発光素子は一対の電極間に流れる電流の大きさに従って階調を表示する表示素子である。そのため、発光素子を用いた半導体表示装置は、液晶表示装置に比べて画素に供給する電流が大きい。よって、半導体表示装置が大型化されることで、電流を供給するべき表示素子の総面積が増大すると、表示する階調によっては画素に供給する電流値が著しく大きくなる。そのため、画素に電流を供給するための配線（電源線）の電位が大幅に降下してしまい、表示領域内の画素間において輝度の高さにむらが生じてしまう。

【0009】

上述した問題に鑑み、配線の電位の降下に起因する画素間の輝度むらを抑えることを目的とする。

【課題を解決するための手段】

【0010】

上記問題を解決するために、電源電位が与えられる電源線どうしを、画素が複数配列されている表示領域内において、電気的に接続する。さらに、電源線どうしを表示領域内において電気的に接続するための配線（補助電源線）と、画素が有するトランジスタのゲート電極との上には層間絶縁膜が形成されており、電源線は、補助電源線及びゲート電極よりも更に上層に位置する、上記層間絶縁膜上に形成されている。そして、補助電源線には、層間絶縁膜上に形成された配線（補助配線）が電気的に、或いは直接、接続されている。なお、本明細書において、電気的に接続という場合には、特別に断りがない限り、直接接続される状態も含むものとする。

【0011】

なお、電源線どうしの電気的な接続は、隣り合う全ての電源線どうしで行っても良いし、全ての電源線を幾つかのグループに分けて、各グループに属する電源線どうしで行っても良い。特に、各画素から得られる光の色ごとに、電源線に与えられる電源電位の高さが異なっている場合、共通の電源電位が与えられる電源線どうしを、補助電源線を介して電気的に接続する。なお、画素から得られる光の色は、発光素子に用いられる電界発光層の種類を変えることで、異ならせることができるし、或いは、発光素子から発せられる光のうち、特定の波長の光のみを透過することができるカラーフィルターを用いることで、異なることができる。

【0012】

また、スイッチング素子として機能するトランジスタのゲート電極に接続された走査線上に層間絶縁膜を形成し、上記層間絶縁膜上に形成された配線（走査線用補助配線）を、該走査線と、電気的に、或いは直接接続するようにしても良い。

【0013】

また、層間絶縁膜上に形成される電源線、補助配線、または走査線用補助配線は、その厚さが $0.8 \mu m$ 以上 $1.5 \mu m$ 以下であることが望ましい。

【0014】

また、層間絶縁膜上に形成される電源線、補助配線、または走査線用補助配線は、層間絶縁膜上に形成された単数の導電膜または積層された複数の導電膜を所望の形状に加工（パターニング）することで、形成される。層間絶縁膜の下に形成されるゲート電極、補助電源線、または走査線は、層間絶縁膜の前に形成された単数の導電膜または積層された複数の導電膜を、所望の形状に加工（パターニング）することで、形成される。なお、電源線、補助配線、または走査線用補助配線に用いられる少なくとも1つの導電膜の電気伝導率は、ゲート電極、補助電源線、または走査線に用いられる少なくとも1つの導電膜の電気伝導率よりも、高いことが望ましい。

【発明の効果】

【0015】

開示する発明において、電源線どうしを、より下層に形成された補助電源線を用いて電気

10

20

30

40

50

的に接続することで、電源線の電位の降下に起因する表示領域内の輝度むらを防ぐことができる。また、補助電源線を、電源線が形成されている層と同じ層上の補助配線と直接、或いは電気的に接続することで、補助電源線の電位の降下、延いては電源線の電位の降下を、より効果的に防ぐことができる。よって、配線の電位の降下に起因する画素間の輝度むらを抑えることができるので、大型の表示領域を有する高画質な半導体表示装置を提供することができる。

#### 【0016】

また、走査線より上層に形成された走査線用補助配線と、走査線とを電気的に、或いは直接接続することで、走査線の電位の降下により、スイッチング用トランジスタのスイッチングを、的確なタイミングで制御できなくなってしまうことを、防ぐことができる。

10

#### 【図面の簡単な説明】

#### 【0017】

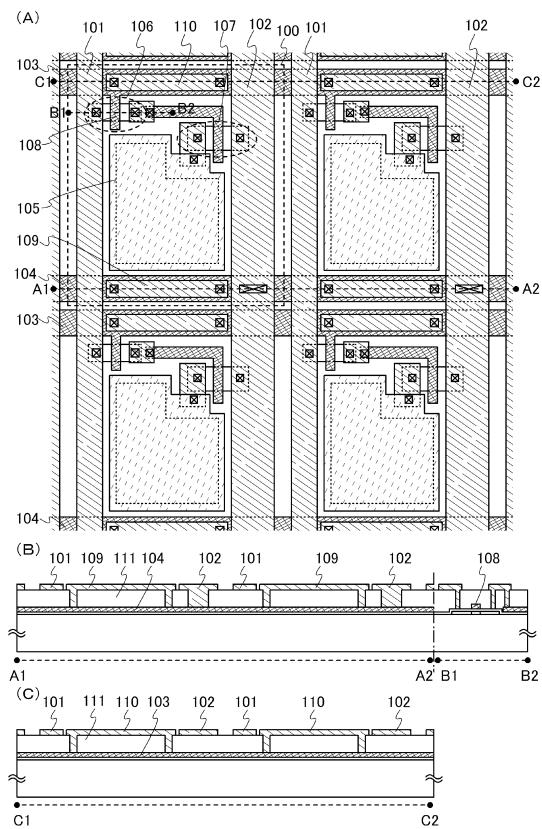

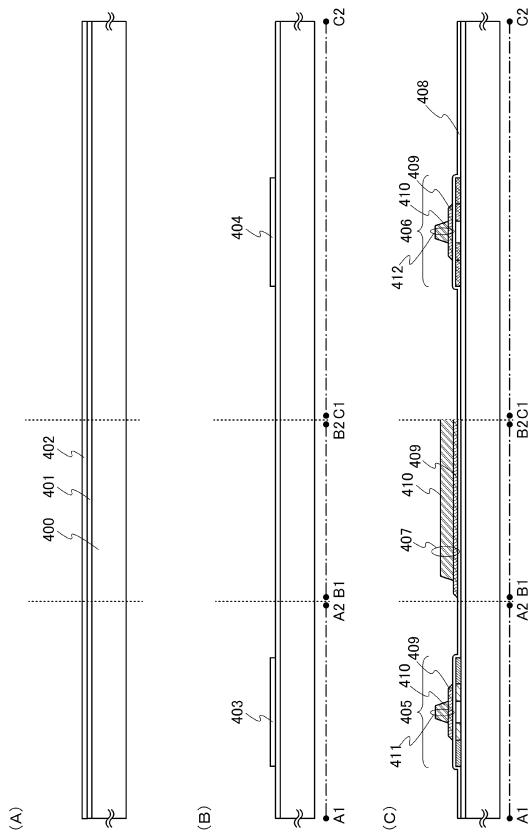

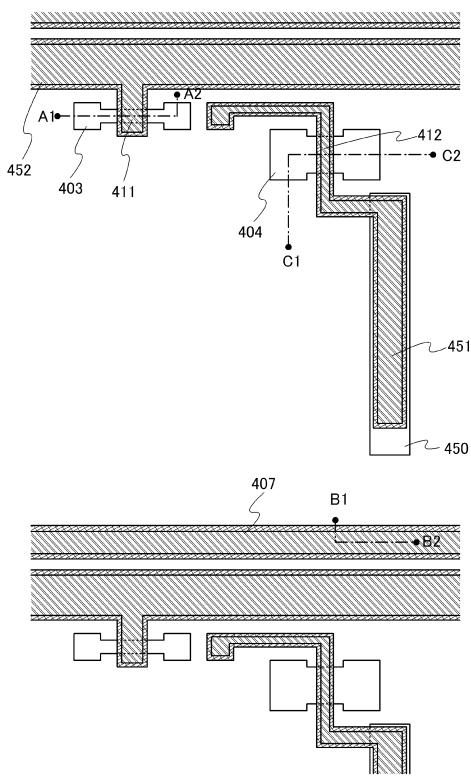

【図1】実施の形態1に係る半導体表示装置が有する表示領域の拡大図と、その断面図。

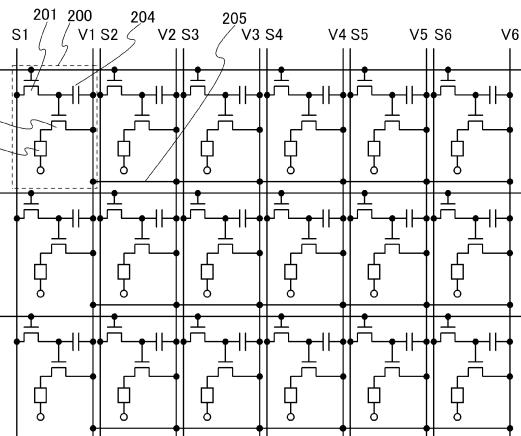

【図2】実施の形態1に係る半導体表示装置が有する表示領域の回路図。

【図3】実施の形態1に係る半導体表示装置が有する表示領域の回路図。

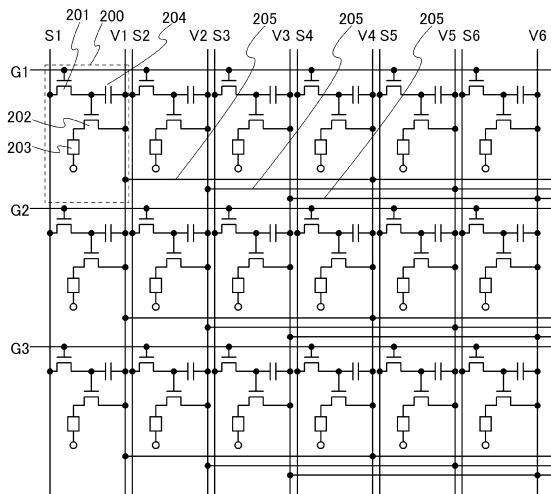

【図4】実施の形態1に係る半導体表示装置が有する表示領域の拡大図。

【図5】実施の形態2に係る半導体表示装置の作製方法を示す図。

【図6】実施の形態2に係る半導体表示装置の作製方法を示す図。

【図7】実施の形態2に係る半導体表示装置の作製方法を示す図。

【図8】実施の形態2に係る半導体表示装置の作製方法を示す図。

20

【図9】実施の形態2に係る半導体表示装置の作製方法を示す図。

【図10】実施の形態2に係る半導体表示装置の作製方法を示す図。

【図11】実施の形態2に係る半導体表示装置の作製方法を示す図。

【図12】実施の形態3に係る半導体表示装置が有する画素の回路図。

【図13】実施の形態3に係る半導体表示装置が有する画素の上面図。

【図14】実施の形態3に係る半導体表示装置が有する画素の断面図。

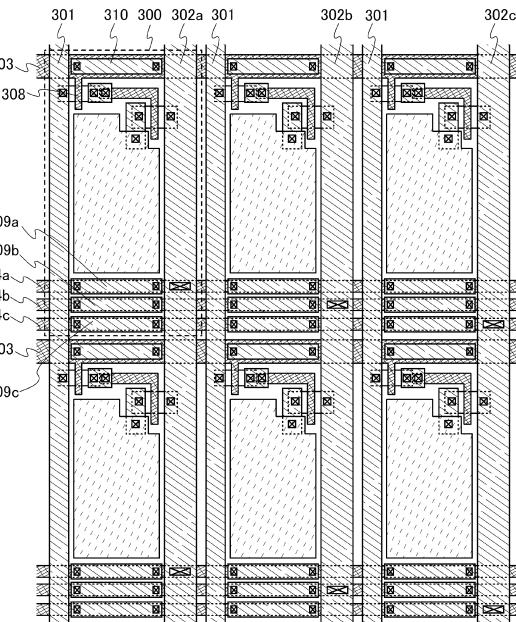

【図15】実施の形態3に係る半導体表示装置が有する表示領域の拡大図。

【図16】実施の形態4に係る半導体表示装置の作製方法を示す図。

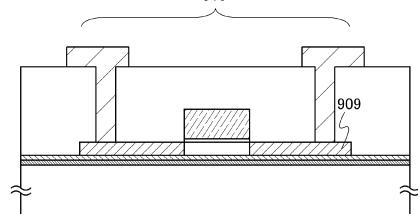

【図17】実施の形態5に係る半導体表示装置の発光素子及び配線の断面図。

30

【図18】実施例1に係る半導体表示装置の作製方法を示す図。

【図19】実施例1に係る半導体表示装置の作製方法を示す図。

【図20】実施例2に係る半導体表示装置のブロック図。

【図21】実施例3に係る半導体表示装置の上面図及び断面図。

【図22】実施例4に係る半導体表示装置を用いた電子機器の図。

#### 【発明を実施するための形態】

#### 【0018】

以下、実施の形態及び実施例について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて、本実施の形態及び実施例の記載内容に限定して解釈されるものではない。

40

#### 【0019】

なお、半導体表示装置は、発光素子が形成されたパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに本実施の形態で示す半導体表示装置は、該半導体表示装置を作製する過程における、発光素子が完成する前の一形態に相当する素子基板をも、その範疇に含む。具体的に素子基板は、発光素子が有する一対の電極のうち、一方の電極のみが形成された状態であっても良いし、該一方の電極となる導電膜を成膜した後であって、パターニングして前記一方の電極を形成する前の状態であっても良い。

#### 【0020】

(実施の形態1)

50

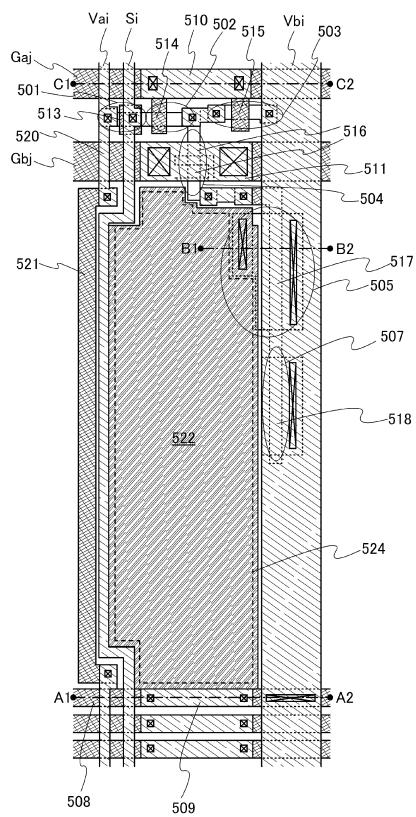

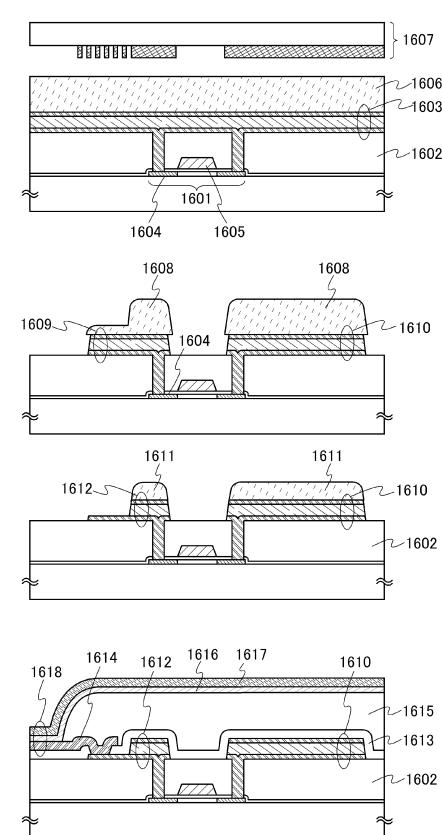

図1を用いて、半導体表示装置が有する画素の構成について説明する。図1(A)は、本発明の半導体表示装置が有する、表示領域の一部を拡大した上面図の一例である。また、図1(A)の破線A1-A2における断面図、及び破線B1-B2における断面図を図1(B)に示す。また、図1(A)の破線C1-C2における断面図を図1(C)に示す。

【0021】

図1に示す半導体表示装置は、表示領域内に複数の信号線101、複数の電源線102、複数の走査線103、複数の補助電源線104を有している。表示領域内に設けられた複数の各画素100は、信号線101の一つと、電源線102の一つと、走査線103の一つとを、少なくとも有している。

【0022】

そして、任意の画素100が有する電源線102は、補助電源線104を介して、上記電源線102とは別の電源線102と、電気的に接続されている。図1では、2つの電源線102と補助電源線104とが直接接続されることで、電源線102どうしを電気的に接続している例を示しているが、電源線102の一つと補助電源線104とが、別の配線を介して電気的に接続されていても良い。また、図1では、隣り合う電源線102どうしを電気的に接続しているが、表示領域内の電源線102が全て電気的に接続されている必要はない。

10

【0023】

開示する発明においては、少なくとも2つの電源線102を、補助電源線104を介して電気的に接続することで、画素に供給するべき電流の大きさが電源線102ごとに大幅に異なる場合でも、電位が低下することによって電源線102内に生じる電位差が、電源線102どうしで異なるのを防ぐことができる。よって、電位の低下に起因する表示領域内の輝度むらを防ぐことができる。

20

【0024】

また、各画素100は、発光素子105と、画素100へのビデオ信号の入力を制御するスイッチング用トランジスタ106と、発光素子105に供給する電流値を制御する駆動用トランジスタ107とを、少なくとも有する。なお図1(A)では、発光素子105となる領域を破線で示している。なお、図1では、各画素にトランジスタが2つ設けられた画素100を例に挙げて説明するが、本発明はこの構成に限定されない。本発明の半導体表示装置は、各画素100に少なくとも、画素100へのビデオ信号の入力を制御するトランジスタと、発光素子に供給する電流値を制御するトランジスタとを有していればよい。

30

【0025】

スイッチング用トランジスタ106が有するゲート電極108は、走査線103と、直接、或いは電気的に接続されている。なお、本明細書においてゲート電極とは、ゲート絶縁膜に接している単数の導電膜または複数の積層された導電膜のうち、ゲート絶縁膜を間に挟んで活性層である半導体膜と重なっている部分を意味する。図1(A)では、一続きの導電膜が走査線103及びゲート電極108として機能しており、走査線103とゲート電極108とが直接接続されている状態である。しかし、走査線103とゲート電極108とが、互いに分離した導電膜で形成されており、走査線103とゲート電極108とが別の配線を介して電気的に接続されていても良い。または、走査線103とゲート電極108とが、互いに異なる導電膜で形成されており、走査線103とゲート電極108とが直接、或いは別の配線を介して電気的に接続されていても良い。

40

【0026】

さらに、各画素100は、補助電源線104に直接接続された補助配線109と、走査線103に直接接続された走査線用補助配線110とを有する。なお、図1では、補助電源線104が直接補助配線109に接続されているが、補助電源線104が別の異なる配線を介して、補助配線109と電気的に接続されていても良い。また図1では、走査線103が直接走査線用補助配線110に接続されているが、走査線103が別の異なる配線を介して、走査線用補助配線110と電気的に接続されていても良い。

50

**【0027】**

本実施の形態で示す半導体表示装置では、補助電源線104に直接、或いは電気的に接続された補助配線109を設けることで、補助電源線104と、補助配線109との合成抵抗を下げることができる。よって、補助電源線104の電位の降下を防ぎ、延いては電源線102の電位の降下を防ぐことができる。

**【0028】**

また、図1に示す半導体表示装置では、走査線用補助配線110を有する構成を示しているが、本実施の形態で示す半導体表示装置では少なくとも補助配線109を有していれば良く、必ずしも走査線用補助配線110を有していないとも良い。ただし、走査線用補助配線110を設けることで、走査線103と、走査線用補助配線110との合成抵抗を下げることができる。よって、走査線103の電位の降下により、スイッチング用トランジスタ106のスイッチングを、的確なタイミングで制御できなくなってしまうことを、防ぐことができる。

10

**【0029】**

また本実施の形態では、少なくとも電源線102、補助配線109、走査線用補助配線110を、層間絶縁膜111の上に形成する。図1では、電源線102、補助配線109、走査線用補助配線110に加えて、信号線101も層間絶縁膜111の上に形成している例を示している。よって本実施の形態では、電源線102、補助配線109、走査線用補助配線110、信号線101を、層間絶縁膜の上に形成された単数の導電膜または積層された複数の導電膜を所望の形状に加工(パターニング)することで形成できる。従って、電源線102、補助配線109、走査線用補助配線110及び信号線101は、1つのマスクで形成することができる。また本実施の形態では、少なくともゲート電極108、補助電源線104、走査線103を、層間絶縁膜111の下に形成する。よって本実施の形態では、ゲート電極108、補助電源線104、走査線103を、層間絶縁膜を形成する前に、単数の導電膜または積層された複数の導電膜を所望の形状に加工することで形成できる。従って、ゲート電極108、補助電源線104、走査線103は、1つのマスクで形成することができる。このため、本実施の形態の半導体表示装置は、マスク数を従来よりも増やすことなく作製することができる。

20

**【0030】**

なお、ゲート電極108には、スイッチング用トランジスタ106の作製工程において施される加熱処理に耐えうる程度の耐熱性が要求される。よって、単数の導電膜または積層された複数の導電膜を所望の形状に加工(パターニング)することでゲート電極108と共に走査線103及び補助電源線104を形成する場合、ゲート電極108、走査線103及び補助電源線104に用いることができる材料の種類には、制限が生じる。そのため、ゲート電極108、走査線103及び補助電源線104をより抵抗率の低い材料で形成することが難しい。しかし本実施の形態では、スイッチング用トランジスタ106及び駆動用トランジスタ107上に形成された層間絶縁膜111の、更に上において電源線102、補助配線109、走査線用補助配線110を形成する。よって、電源線102、補助配線109、走査線用補助配線110は、スイッチング用トランジスタ106を作製した後に形成されるので、ゲート電極108、走査線103及び補助電源線104ほど高い耐熱性は要求されない。そのため、電源線102、補助配線109、走査線用補助配線110に用いることができる材料は比較的自由度が高く、ゲート電極108、走査線103及び補助電源線104より抵抗率の低い材料を選択することが可能である。抵抗率の低い材料で補助配線109、走査線用補助配線110を作製することで、補助電源線104と補助配線109の合成抵抗、走査線103と走査線用補助配線110の合成抵抗をより下げることができる。従って、電源線102の電位の降下、走査線103の電位の降下を防ぐことができる。

30

**【0031】**

なお、図1に示した半導体表示装置では、層間絶縁膜111の下に形成された補助電源線104、走査線103などの配線に、層間絶縁膜111の上に形成された補助配線109

40

50

、走査線用補助配線 110 などの合成抵抗を下げるための配線を接続している。しかし、本実施の形態では、層間絶縁膜 111 の上に形成された信号線 101 などの配線に、層間絶縁膜 111 の下で形成された合成抵抗を下げるための配線を接続するようにしても良い。

【0032】

次に、各画素から得られる光の色ごとに、電源線に与えられる電源電位の高さが異なっている場合において、共通の電源電位が与えられる電源線どうしを、補助電源線を介して電気的に接続する場合について説明する。

【0033】

まず、図 2 に、隣り合う電源線どうしを全て電気的に接続した場合の、表示領域の回路図を示す。図 2 に示す表示領域では、信号線 S1 ~ 信号線 S6 と、電源線 V1 ~ 電源線 V6 と、走査線 G1 ~ 走査線 G3 が設けられている。なお、表示領域に設けられる信号線、電源線、走査線の数は、図 2 に示した構成に限定されない。表示領域に設けられた各画素 200 は、信号線 S1 ~ 信号線 S6 の 1 つと、電源線 V1 ~ 電源線 V6 の 1 つと、走査線 G1 ~ 走査線 G3 の 1 つとを少なくとも有する。

10

【0034】

また各画素 200 は、少なくとも 1 つのスイッチング用トランジスタ 201 と、少なくとも 1 つの駆動用トランジスタ 202 と、発光素子 203 を有している。スイッチング用トランジスタ 201 のゲート電極は、走査線 G1 ~ 走査線 G3 の 1 つと接続されており、スイッチング用トランジスタ 201 のソース領域とドレイン領域は、一方が信号線 S1 ~ 信号線 S6 の 1 つに接続され、他方が駆動用トランジスタ 202 のゲート電極に接続されている。駆動用トランジスタ 202 のソース領域とドレイン領域は、一方が電源線 V1 ~ 電源線 V6 の 1 つに接続され、他方が発光素子 203 の画素電極に接続されている。また、画素 200 は保持容量 204 を有しており、該保持容量 204 は、一方の電極が電源線 V1 ~ 電源線 V6 の 1 つに接続され、他方の電極が駆動用トランジスタ 202 のゲート電極に接続されている。なお、図 2 に示す画素 200 の構成は、本発明の半導体表示装置が有する画素のほんの一例であり、本発明は図 2 に示す画素の構成に限定されない。

20

【0035】

図 2 に示す表示領域では、全ての電源線 V1 ~ 電源線 V6 が、補助電源線 205 を介して電気的に接続されている。さらに図 2 に示す表示領域では、補助電源線 205 が、隣り合う電源線どうしを複数箇所において電気的に接続している例を示している。隣り合う電源線どうしを 1 箇所においてのみ電気的に接続するよりも、図 2 に示すように、複数箇所において電気的に接続する方が、画素 200 に供給するべき電流の大きさが電源線ごとに大幅に異なる場合でも、電位が降下することによって電源線内に生じる電位差が、電源線どうしで異なるのをより防ぐことができる。よって、電位の降下に起因する表示領域内の輝度むらを防ぐことができる。

30

【0036】

次に、図 3 に、R(赤)、G(緑)、B(青)の各色に対応する電源線どうしを電気的に接続した場合の、表示領域の回路図を示す。図 3 に示す表示領域の構成は、補助電源線 205 以外、全て図 2 に示す構成と同じであるものとする。図 3 に示す表示領域では、電源線 V1 と電源線 V4 が、R(赤)に対応する画素 200 に電流を供給している。また、電源線 V2 と電源線 V5 が、G(緑)に対応する画素 200 に電流を供給している。また、電源線 V3 と電源線 V6 が、B(青)に対応する画素 200 に電流を供給している。

40

【0037】

そして、R(赤)に対応する電源線 V1 と電源線 V4 とが、補助電源線 205 によって電気的に接続されている。また、G(緑)に対応する電源線 V2 と電源線 V5 とが、補助電源線 205 によって電気的に接続されている。また、B(青)に対応する電源線 V3 と電源線 V6 とが、補助電源線 205 によって電気的に接続されている。

【0038】

図 3 に示す表示領域を有する半導体表示装置では、各色に対応する電源線ごとに与えられ

50

る電源電位が異なっている場合でも、電位が降下することによって電源線内に生じる電位差が、各色に対応する電源線どうしで異なるのをより防ぐことができる。よって、電位の降下に起因する表示領域内の輝度むらを色ごとに防ぐことができる。

〔 0 0 3 9 〕

なお、画素から得られる光の色は、発光素子 203 に用いられる電界発光層の種類を変えることで、異ならせることができる。この場合、発光素子 203 から発せられる光の波長の範囲自体が、各色に対応する画素 200 ごとに異なる。或いは、発光素子 203 から発せられる光のうち、特定の範囲内の波長の光を優先的に透過させることができるカラーフィルターを用いることで、画素 200 から得られる光の色を異ならせることもできる。この場合、発光素子 203 から発せられる光の波長の範囲は、全ての画素 200 において同じであるか、複数の色に対応する画素 200 において同じであっても良い。或いは、発光素子 203 から発せられる光の波長の範囲が、各色に対応する画素 200 ごとに異なっていても、カラーフィルターを用いていても良い。発光素子 203 から発せられる光の波長の範囲が、各色に対応する画素 200 ごとに異なっていても、カラーフィルターを併用することで、画素 200 から得られる光の色純度を高めることができる。

10

[ 0 0 4 0 ]

また、図3では、R(赤)、G(緑)、B(青)の光が得られる画素200を有する半導体表示装置を例に挙げて説明したが、本発明はこの構成に限定されない。シアン(青緑)、マゼンタ(赤紫)、イエロー(黄)の光が得られる画素200を有する半導体表示装置であっても良い。或いは、R(赤)、G(緑)、B(青)に加えてW(白)の光が得られる画素200を有する半導体表示装置であっても良い。

20

( 0 0 4 1 )

また、図3に示す表示領域では、補助電源線205が、各色に対応する電源線どうしを複数箇所において電気的に接続している例を示している。隣り合う電源線どうしを1箇所においてのみ電気的に接続するよりも、図3に示すように、複数箇所において電気的に接続する方が、画素200に供給するべき電流の大きさが電源線ごとに大幅に異なる場合でも、電位が降下することによって電源線内に生じる電位差が、各色に対応する電源線どうしで異なるのをより防ぐことができる。よって、電位の降下に起因する表示領域内の輝度むらを色ごとに防ぐことができる。

30

4 1- 3

【0043】

図 4 に示す本

図4に示す本実施の形態の半導体表示装置は、表示領域内に複数の信号線301、電源線302a、電源線302b、電源線302c、複数の走査線303、補助電源線304a、補助電源線304b、補助電源線304cを有している。表示領域内に設けられた複数の各画素300は、信号線301の一つと、電源線302a、電源線302b、電源線302cのいずれか一つと、走査線303の一つとを、少なくとも有している。

【 0 0 4 4 】

そして、図4では、電源線302a、電源線302b、電源線302cに与えられる電源電位が、互いに異なっている。さらに、電源線302aは、補助電源線304aを介して、隣接する他の電源線302aに電気的に接続される。また、電源線302bは、補助電源線304bを介して、隣接する他の電源線302bに電気的に接続される。また、電源線302cは、補助電源線304cを介して、隣接する他の電源線302cに電気的に接続される。

40

[ 0 0 4 5 ]

なお図4では、電源線302aと補助電源線304a、電源線302bと補助電源線304b、電源線302cと補助電源線304cとが、それぞれ直接接続されることで、隣接する電源線302aどうし、または隣接する電源線302bどうし、または隣接する電源線302cどうしを電気的に接続している例を示している。しかし、電源線302a、電源線302b、電源線302cと、補助電源線304a、補助電源線304b、補助電源

50

線 3 0 4 c とが、それぞれ別の配線を介して電気的に接続されていても良い。

【 0 0 4 6 】

さらに、各画素 3 0 0 は、補助電源線 3 0 4 a、補助電源線 3 0 4 b、補助電源線 3 0 4 c にそれぞれ直接接続された補助配線 3 0 9 a、補助配線 3 0 9 b、補助配線 3 0 9 c と、走査線 3 0 3 に直接接続された走査線用補助配線 3 1 0 とを有する。なお、図 4 では、補助電源線 3 0 4 a、補助電源線 3 0 4 b、補助電源線 3 0 4 c が直接補助配線 3 0 9 a、補助配線 3 0 9 b、補助配線 3 0 9 c にそれぞれ接続されているが、補助電源線 3 0 4 a、補助電源線 3 0 4 b、補助電源線 3 0 4 c が別の異なる配線を介して、補助配線 3 0 9 a、補助配線 3 0 9 b、補助配線 3 0 9 c とそれぞれ電気的に接続されていても良い。また図 4 では、走査線 3 0 3 が直接走査線用補助配線 3 1 0 に接続されているが、走査線 3 0 3 が別の異なる配線を介して、走査線用補助配線 3 1 0 と電気的に接続されていても良い。

【 0 0 4 7 】

本実施の形態の半導体表示装置では、補助電源線 3 0 4 a、補助電源線 3 0 4 b、補助電源線 3 0 4 c に直接、或いは電気的にそれぞれ接続された補助配線 3 0 9 a、補助配線 3 0 9 b、補助配線 3 0 9 c を設けることで、補助電源線 3 0 4 a と補助配線 3 0 9 a の合成抵抗、補助電源線 3 0 4 b と補助配線 3 0 9 b の合成抵抗、補助電源線 3 0 4 c と補助配線 3 0 9 c の合成抵抗を、それぞれ下げることができる。よって、補助電源線 3 0 4 a、補助電源線 3 0 4 b、補助電源線 3 0 4 c の電位の降下を防ぎ、延いては電源線 3 0 2 a、電源線 3 0 2 b、電源線 3 0 2 c の電位の降下を防ぐことができる。

【 0 0 4 8 】

また、図 4 に示す半導体表示装置では、走査線用補助配線 3 1 0 を有する構成を示しているが、本実施の形態の半導体表示装置では少なくとも補助配線 3 0 9 a、補助配線 3 0 9 b、補助配線 3 0 9 c を有していれば良く、必ずしも走査線用補助配線 3 1 0 を有していないとも良い。ただし、走査線用補助配線 3 1 0 を設けることで、走査線 3 0 3 と、走査線用補助配線 3 1 0 との合成抵抗を下げることができる。よって、走査線 3 0 3 の電位の降下により、トランジスタのスイッチングを、的確なタイミングで制御できなくなってしまうことを、防ぐことができる。

【 0 0 4 9 】

また本実施の形態では、少なくとも電源線 3 0 2 a、電源線 3 0 2 b、電源線 3 0 2 c、補助配線 3 0 9 a、補助配線 3 0 9 b、補助配線 3 0 9 c、走査線用補助配線 3 1 0 を、層間絶縁膜の上に形成する。図 4 では、電源線 3 0 2 a、電源線 3 0 2 b、電源線 3 0 2 c、補助配線 3 0 9 a、補助配線 3 0 9 b、補助配線 3 0 9 c、走査線用補助配線 3 1 0 に加えて、信号線 3 0 1 も層間絶縁膜の上に形成している例を示している。よって本実施の形態では、電源線 3 0 2 a、電源線 3 0 2 b、電源線 3 0 2 c、補助配線 3 0 9 a、補助配線 3 0 9 b、補助配線 3 0 9 c、走査線用補助配線 3 1 0、信号線 3 0 1 を、層間絶縁膜の上に形成された単数の導電膜または積層された複数の導電膜を所望の形状に加工(パターニング)することで形成できる。従って、電源線 3 0 2 a、電源線 3 0 2 b、電源線 3 0 2 c、補助配線 3 0 9 a、補助配線 3 0 9 b、補助配線 3 0 9 c、走査線用補助配線 3 1 0 及び信号線 3 0 1 は、1 つのマスクで形成することができる。

【 0 0 5 0 】

また本実施の形態では、少なくともゲート電極 3 0 8、補助電源線 3 0 4 a、補助電源線 3 0 4 b、補助電源線 3 0 4 c、走査線 3 0 3 を、層間絶縁膜の下に形成する。よって本実施の形態では、ゲート電極 3 0 8、補助電源線 3 0 4 a、補助電源線 3 0 4 b、補助電源線 3 0 4 c、走査線 3 0 3 を、層間絶縁膜を形成する前に、単数の導電膜または積層された複数の導電膜を所望の形状に加工することで形成できる。従って、ゲート電極 3 0 8、補助電源線 3 0 4 a、補助電源線 3 0 4 b、補助電源線 3 0 4 c、走査線 3 0 3 は、1 つのマスクで形成することができる。このため、本実施の形態の半導体表示装置は、マスク数を従来よりも増やすことなく作製することができる。

【 0 0 5 1 】

10

20

30

40

50

なお、ゲート電極 308 には、トランジスタの作製行程において施される加熱処理に耐えうる程度の耐熱性が要求される。よって、単数の導電膜または積層された複数の導電膜を所望の形状に加工（パターニング）することでゲート電極 308 と共に走査線 303 及び補助電源線 304a、補助電源線 304b、補助電源線 304c を形成する場合、ゲート電極 308、走査線 303、補助電源線 304a、補助電源線 304b、補助電源線 304c に用いることができる材料の種類には、制限が生じる。そのため、ゲート電極 308、走査線 303、補助電源線 304a、補助電源線 304b、補助電源線 304c をより抵抗率の低い材料で形成することが難しい。しかし本実施の形態では、トランジスタ上に形成された層間絶縁膜の、更に上において電源線 302a、電源線 302b、電源線 302c、補助配線 309a、補助配線 309b、補助配線 309c、走査線用補助配線 310 を形成する。よって、電源線 302a、電源線 302b、電源線 302c、補助配線 309a、補助配線 309b、補助配線 309c、走査線用補助配線 310 は、トランジスタを作製した後に形成されるので、ゲート電極 308、走査線 303、補助電源線 304a、補助電源線 304b、補助電源線 304c ほど高い耐熱性は要求されない。そのため、電源線 302a、電源線 302b、電源線 302c、補助配線 309a、補助配線 309b、補助配線 309c、走査線用補助配線 310 に用いることができる材料は比較的自由度が高く、ゲート電極 308、走査線 303、補助電源線 304a、補助電源線 304b、補助電源線 304c より抵抗率の低い材料を選択することが可能である。抵抗率の低い材料で補助配線 309a、補助配線 309b、補助配線 309c、走査線用補助配線 310 を作製することで、補助電源線 304a と補助配線 309a の合成抵抗、補助電源線 304b と補助配線 309b の合成抵抗、補助電源線 304c と補助配線 309c の合成抵抗、走査線 303 と走査線用補助配線 310 の合成抵抗をより下げることができる。従って、電源線 302a、電源線 302b、電源線 302c の電位の降下、走査線 303 の電位の降下を防ぐことができる。

10

20

#### 【0052】

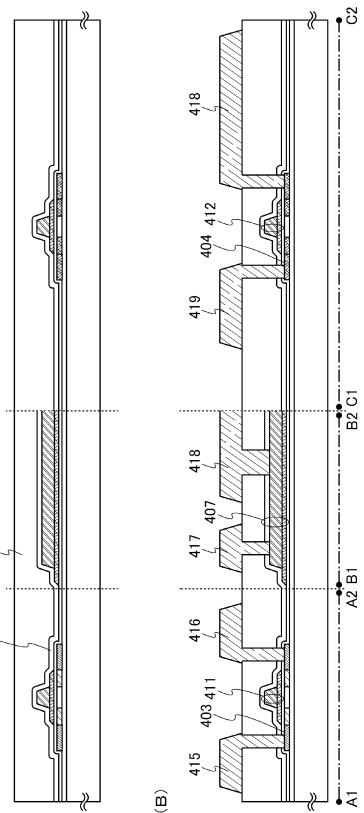

##### （実施の形態 2）

次に、半導体表示装置の作製方法について詳しく述べる。なお、本実施の形態では、薄膜トランジスタ（TFT）を半導体素子の一例として示すが、本発明の半導体表示装置に用いられる半導体素子はこれに限定されない。例えば TFT の他に、記憶素子、ダイオード、抵抗、容量、インダクタなどを用いることができる。

30

#### 【0053】

まず図 5（A）に示すように、耐熱性を有する基板 400 上に、絶縁膜 401、半導体膜 402 を順に形成する。絶縁膜 401 及び半導体膜 402 は連続して形成することができる。

#### 【0054】

基板 400 として、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、ステンレス基板を含む金属基板の表面に絶縁膜を形成したものまたはシリコン基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の合成樹脂を含む、可撓性を有する基板は、一般的に上記基板と比較して耐熱温度が低い傾向にあるが、作製工程における処理温度に耐え得るのであれば用いることが可能である。

40

#### 【0055】

プラスチック基板として、ポリエチレンテレフタラート（PET）に代表されるポリエステル、ポリエーテルスルホン（PES）、ポリエチレンナフタレート（PEN）、ポリカーボネート（PC）、ナイロン、ポリエーテルエーテルケトン（PEEK）、ポリスルホン（PSF）、ポリエーテルイミド（PEI）、ポリアリレート（PAR）、ポリブチレンテレフタレート（PBT）、ポリイミド、アクリロニトリルブタジエンスチレン樹脂、ポリ塩化ビニル、ポリプロピレン、ポリ酢酸ビニル、アクリル樹脂などが挙げられる。

#### 【0056】

絶縁膜 401 は基板 400 中に含まれるNaなどのアルカリ金属やアルカリ土類金属が、

50

半導体膜402中に拡散し、トランジスタなどの半導体素子の特性に悪影響を及ぼすのを防ぐために設ける。よってアルカリ金属やアルカリ土類金属の半導体膜402への拡散を抑えることができる窒化珪素や窒化酸化珪素などを用いて絶縁膜401を形成する。なお、ガラス基板、ステンレス基板またはプラスチック基板のように、アルカリ金属やアルカリ土類金属が多少なりとも含まれている基板を用いる場合、不純物の拡散を防ぐという観点から基板400と半導体膜402との間に絶縁膜401を設けることは有効である。しかし、石英基板など不純物の拡散がさして問題とならない基板400を用いる場合は、必ずしも設ける必要はない。

#### 【0057】

絶縁膜401は、単数の絶縁膜を用いたものであっても、複数の絶縁膜を積層して用いたものであっても良い。絶縁膜401は、CVD法やスパッタリング法等を用いて、酸化珪素、窒化珪素( $\text{SiN}_x$ 、 $\text{Si}_3\text{N}_4$ 等)、酸化窒化珪素( $\text{SiO}_x\text{N}_y$ )( $x > y > 0$ )、窒化酸化珪素( $\text{SiN}_x\text{O}_y$ )( $x > y > 0$ )等の絶縁性を有する材料を用いて形成する。

#### 【0058】

本実施の形態では、膜厚100nmの酸化窒化珪素膜、膜厚50nmの窒化酸化珪素膜、膜厚100nmの酸化窒化珪素膜を順に積層して絶縁膜401を形成するが、各膜の材質、膜厚、積層数は、これに限定されるものではない。例えば、下層の酸化窒化珪素膜に代えて、膜厚0.5~3μmのシロキサン系樹脂をスピンドルコート法、スリットコーティング法、液滴吐出法、印刷法などによって形成しても良い。また、中層の窒化酸化珪素膜に代えて、窒化珪素膜( $\text{SiN}_x$ 、 $\text{Si}_3\text{N}_4$ 等)を用いてもよい。また、上層の酸化窒化珪素膜に代えて、酸化珪素膜を用いていても良い。また、それぞれの膜厚は、0.05~3μmとするのが望ましく、その範囲から自由に選択することができる。

#### 【0059】

酸化珪素膜は、シランと酸素、TEOS(テトラエトキシシラン)と酸素等の組み合わせの混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR-CVD等の方法によって形成することができる。また、窒化珪素膜は、代表的には、シランとアンモニアの混合ガスを用い、プラズマCVDによって形成することができる。また、酸化窒化珪素膜、窒化酸化珪素膜は、代表的には、シランと一酸化ニ窒素の混合ガスを用い、プラズマCVDによって形成することができる。

#### 【0060】

半導体膜402は、絶縁膜401を形成した後、大気に曝さずに形成することが望ましい。半導体膜402の膜厚は20~200nm(望ましくは40~170nm、好ましくは50~150nm)とする。なお半導体膜402は、非晶質半導体であっても良いし、多結晶半導体であっても良い。また半導体は珪素だけではなくシリコンゲルマニウムも用いることができる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は0.01~4.5atomic%程度であることが好ましい。

#### 【0061】

なお半導体膜402は、公知の技術により結晶化しても良い。公知の結晶化方法としては、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。或いは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、基板400として石英のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化法、赤外光を用いたランプアニール結晶化法、触媒元素を用いる結晶化法、950程度の高温アニールを組み合わせた結晶法を用いても良い。

#### 【0062】

例えばレーザ結晶化を用いる場合、レーザ結晶化の前に、レーザに対する半導体膜402の耐性を高めるために、550~4時間の加熱処理を該半導体膜402に対して行なう。そして連続発振が可能な固体レーザを用い、基本波の第2高調波~第4高調波のレーザ光を照射することで、大粒径の結晶を得ることができる。例えば、代表的には、Nd:YVO<sub>4</sub>レーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355

10

20

30

40

50

$\text{nm}$ )を用いるのが望ましい。具体的には、連続発振の $\text{YVO}_4$ レーザから射出されたレーザ光を非線形光学素子により高調波に変換し、出力 $10\text{W}$ のレーザ光を得る。そして、好ましくは光学系により照射面にて矩形状または橍円形状のレーザ光に成形して、半導体膜 $402$ に照射する。このときのエネルギー密度は $0.01 \sim 100\text{MW/cm}^2$ 程度(好ましくは $0.1 \sim 10\text{MW/cm}^2$ )が必要である。そして、走査速度を $10 \sim 200\text{cm/sec}$ 程度とし、照射する。

#### 【0063】

連続発振の気体レーザとして、 $\text{Ar}$ レーザ、 $\text{Kr}$ レーザなどを用いることが出来る。また連続発振の固体レーザとして、 $\text{YAG}$ レーザ、 $\text{YVO}_4$ レーザ、 $\text{YLF}$ レーザ、 $\text{YAlO}_3$ レーザ、フォルステライト( $\text{Mg}_2\text{SiO}_4$ )レーザ、 $\text{GdVO}_4$ レーザ、 $\text{Y}_2\text{O}_3$ レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、 $\text{Ti}:\text{サファイア}$ レーザなどを用いることが出来る。

10

#### 【0064】

またパルス発振のレーザとして、例えば $\text{Ar}$ レーザ、 $\text{Kr}$ レーザ、エキシマレーザ、 $\text{CO}_2$ レーザ、 $\text{YAG}$ レーザ、 $\text{Y}_2\text{O}_3$ レーザ、 $\text{YVO}_4$ レーザ、 $\text{YLF}$ レーザ、 $\text{YAlO}_3$ レーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、 $\text{Ti}:\text{サファイア}$ レーザ、銅蒸気レーザまたは金蒸気レーザを用いることができる。

#### 【0065】

また、パルス発振のレーザ光の発振周波数を $10\text{MHz}$ 以上とし、通常用いられている数十 $\text{Hz} \sim$ 数百 $\text{Hz}$ の周波数帯よりも著しく高い周波数帯を用いてレーザ結晶化を行なっても良い。パルス発振でレーザ光を半導体膜 $402$ に照射してから半導体膜 $402$ が完全に固化するまでの時間は数十 $\text{nsec} \sim$ 数百 $\text{nsec}$ と言われている。よって上記周波数帯を用いることで、半導体膜 $402$ がレーザ光によって溶融してから固化するまでに、次のパルスのレーザ光を照射できる。したがって、半導体膜 $402$ 中において固液界面を連続的に移動させることができるので、走査方向に向かって連続的に成長した結晶粒を有する半導体膜 $402$ が形成される。具体的には、含まれる結晶粒の走査方向における幅が $10 \sim 30\text{μm}$ 、走査方向に対して垂直な方向における幅が $1 \sim 5\text{μm}$ 程度の結晶粒の集合を形成することができる。該走査方向に沿って連続的に成長した単結晶の結晶粒を形成することで、少なくとも $\text{ TFT}$ のチャネル方向には結晶粒界のほとんど存在しない半導体膜 $402$ の形成が可能となる。

20

#### 【0066】

なおレーザ結晶化は、連続発振の基本波のレーザ光と連続発振の高調波のレーザ光とを並行して照射するようにしても良いし、連続発振の基本波のレーザ光とパルス発振の高調波のレーザ光とを並行して照射するようにしても良い。

#### 【0067】

なお、希ガスや窒素などの不活性ガス雰囲気中でレーザ光を照射するようにしても良い。これにより、レーザ光照射による半導体表面の荒れを抑えることができ、界面準位密度のばらつきによって生じる閾値のばらつきを抑えることができる。

#### 【0068】

上述したレーザ光の照射により、結晶性がより高められた半導体膜 $402$ が形成される。なお、予め半導体膜 $402$ に、スパッタ法、プラズマCVD法、熱CVD法などで形成した多結晶半導体を用いるようにしても良い。

40

#### 【0069】

また本実施の形態では半導体膜 $402$ を結晶化しているが、結晶化せずに非晶質珪素膜または微結晶半導体膜のまま、後述のプロセスに進んでも良い。非晶質半導体、微結晶半導体を用いた $\text{TFT}$ は、多結晶半導体を用いた $\text{TFT}$ よりも作製工程が少ない分、コストを抑え、歩留まりを高くすることができるというメリットを有している。

#### 【0070】

非晶質半導体は、珪素を含む気体をグロー放電分解することにより得ることができる。珪素を含む気体としては、 $\text{SiH}_4$ 、 $\text{Si}_2\text{H}_6$ が挙げられる。この珪素を含む気体を、水

50

素、水素及びヘリウムで希釈して用いても良い。

【0071】

次に半導体膜402に対して、p型を付与する不純物元素又はn型を付与する不純物元素を低濃度に添加するチャネルドープを行う。チャネルドープは半導体膜402全体に対して行っても良いし、半導体膜402の一部に対して選択的に行っても良い。p型を付与する不純物元素としては、ボロン(B)やアルミニウム(A1)やガリウム(Ga)等を用いることができる。n型を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。ここでは、不純物元素として、ボロン(B)を用い、当該ボロンが $1 \times 10^{16} \sim 5 \times 10^{17} / \text{cm}^3$ の濃度で含まれるよう添加する。

【0072】

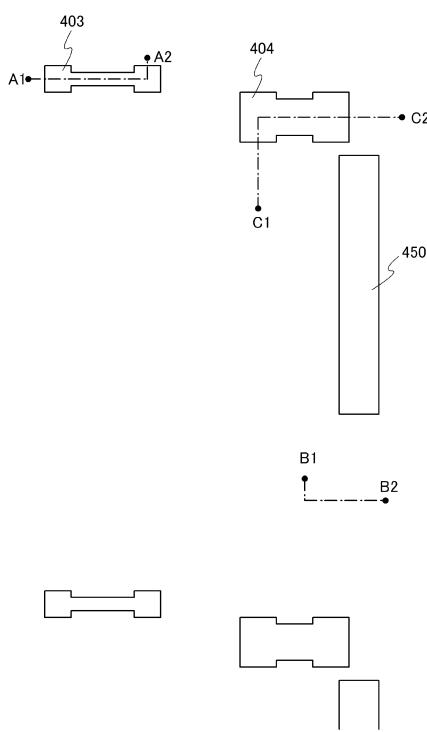

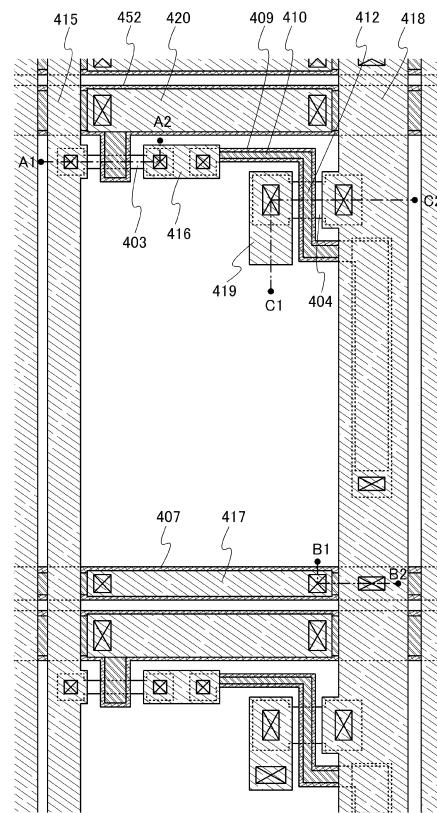

次に図5(B)に示すように、半導体膜402を所定の形状に加工(パターニング)し、島状の半導体膜403、半導体膜404を形成する。図8は、半導体膜403、半導体膜404が形成された画素の上面図に相当し、図8の破線A1-A2における断面図、破線B1-B2における断面図、破線C1-C2における断面図が、図5(B)に図示されている。図8において半導体膜450は、保持容量の一方の電極として機能する。

【0073】

そして、図5(C)に示すように、半導体膜403、半導体膜404を用いて、トランジスタ405、トランジスタ406を形成する。そしてトランジスタ405、トランジスタ406と共に、補助電源線407も形成する。

【0074】

具体的には、半導体膜403、半導体膜404を覆うようにゲート絶縁膜408を形成する。そして、ゲート絶縁膜408上に、所望の形状に加工(パターニング)された複数の導電膜409及び導電膜410を形成する。半導体膜403と重なる導電膜409及び導電膜410が、トランジスタ405のゲート電極411として機能する。半導体膜404と重なる導電膜409及び導電膜410が、トランジスタ406のゲート電極412として機能する。また、半導体膜403、半導体膜404とは異なる領域に形成された導電膜409及び導電膜410が、補助電源線407として機能する。

【0075】

そして、導電膜409、導電膜410、あるいはレジストを成膜しパターニングしたものをマスクとして用い、半導体膜403、半導体膜404にn型またはp型を付与する不純物を添加し、ソース領域、ドレイン領域、さらにはLDD領域として機能する不純物領域等を形成する。なおここでは、トランジスタ405をn型、トランジスタ406をp型とする。

【0076】

図9は、トランジスタ405、トランジスタ406、補助電源線407が形成された画素の上面図に相当し、図9の破線A1-A2における断面図、破線B1-B2における断面図、破線C1-C2における断面図が、図5(C)に図示されている。図9において、導電膜409及び導電膜410のうち、半導体膜450と重なっている部分が、保持容量の他方の電極451に相当する。そして、図9において電極451とトランジスタ406のゲート電極412とは、一続きの導電膜409及び導電膜410で形成されている。半導体膜450と電極451との間にゲート絶縁膜408が挟まれている領域が、保持容量として機能する。また、図9に示す走査線452は、補助電源線407と同様に、導電膜409及び導電膜410で形成されている。そして、図9において走査線452とトランジスタ405のゲート電極411とは、一続きの導電膜409及び導電膜410で形成されている。

【0077】

なおゲート絶縁膜408には、例えば酸化珪素、窒化珪素、窒化酸化珪素または酸化窒化珪素等を単層で、または積層させて用いる。積層する場合には、例えば、基板400側から酸化珪素膜、窒化珪素膜、酸化珪素膜の3層構造とするのが好ましい。また形成方法は、プラズマCVD法、スパッタ法などを用いることができる。例えば、酸化珪素を用いた

10

20

30

40

50

ゲート絶縁膜をプラズマCVD法で形成する場合、TEOS (Tetraethyl orthosilicate) とO<sub>2</sub>を混合したガスを用い、反応圧力40Pa、基板温度300～400、高周波(13.56MHz)及び電力密度0.5～0.8W/cm<sup>2</sup>とし、形成する。

【0078】

ゲート絶縁膜408は、高密度プラズマ処理を行うことにより半導体膜403、半導体膜404の表面を酸化または窒化することで形成しても良い。高密度プラズマ処理は、例えばHe、Ar、Kr、Xeなどの希ガスと酸素、酸化窒素、アンモニア、窒素、水素などの混合ガスとを用いて行う。この場合、プラズマの励起をマイクロ波の導入により行うことで、低電子温度で高密度のプラズマを生成することができる。このような高密度のプラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)や窒素ラジカル(NHラジカルを含む場合もある)によって、半導体膜403、半導体膜404の表面を酸化または窒化することにより、1～20nm、代表的には5～10nmの絶縁膜が半導体膜403、半導体膜404に接するように形成される。この5～10nmの絶縁膜をゲート絶縁膜408として用いる。

【0079】

上述した高密度プラズマ処理による半導体膜の酸化または窒化は固相反応で進むため、ゲート絶縁膜と半導体膜の界面準位密度をきわめて低くすることができる。また高密度プラズマ処理により半導体膜を直接酸化または窒化することで、形成される絶縁膜の厚さのばらつきを抑えることができる。また半導体膜が結晶性を有する場合、高密度プラズマ処理を用いて半導体膜の表面を固相反応で酸化させることにより、結晶粒界においてのみ酸化が速く進んでしまうのを抑え、均一性が良く、界面準位密度の低いゲート絶縁膜を形成することができる。高密度プラズマ処理により形成された絶縁膜を、ゲート絶縁膜の一部または全部に含んで形成されるトランジスタは、特性のばらつきを抑えることができる。

【0080】

また窒化アルミニウムをゲート絶縁膜408として用いることができる。窒化アルミニウムは熱伝導率が比較的高く、トランジスタで発生した熱を効率的に発散させることができる。またアルミニウムの含まれない酸化珪素や酸化窒化珪素等を形成した後、窒化アルミニウムを積層したものをゲート絶縁膜として用いても良い。

【0081】

また、本実施の形態では積層された2つの導電膜409、導電膜410を用いて、ゲート電極411、ゲート電極412、補助電源線407、電極451、走査線452を形成しているが、本発明はこの構成に限定されない。導電膜409、導電膜410の代わりに、単層の導電膜を用いていても良いし、3つ以上の導電膜を積層して用いていても良い。3つ以上の導電膜を積層する3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

【0082】

ゲート電極411、ゲート電極412、補助電源線407、電極451、走査線452を形成するための導電膜は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等を用いることができる。また上記金属を主成分とする合金を用いても良いし、上記金属を含む化合物を用いても良い。または、半導体膜に導電性を付与するリン等の不純物元素をドーピングした、多結晶珪素などの半導体を用いて形成しても良い。

【0083】

本実施の形態では、1層目の導電膜409として窒化タンタルまたはタンタル(Ta)を、2層目の導電膜410としてタングステン(W)を用いる。2つの導電膜の組み合わせとして、本実施の形態で示した例の他に、窒化タングステンとタングステン、窒化モリブデンとモリブデン、アルミニウムとタンタル、アルミニウムとチタン等が挙げられる。タングステンや窒化タンタルは、耐熱性が高いため、2層の導電膜を形成した後の工程において、熱活性化を目的とした加熱処理を行うことができる。また、2層の導電膜の組み合

10

20

30

40

50

わせとして、例えば、n型を付与する不純物がドーピングされた珪素とニッケルシリサイド、n型を付与する不純物がドーピングされた珪素とタンゲステンシリサイド等も用いることが出来る。

【0084】

導電膜409、導電膜410の形成にはCVD法、スパッタリング法等を用いることが出来る。本実施の形態では1層目の導電膜409を20~100nmの厚さで形成し、2層目の導電膜410を100~400nmの厚さで形成する。

【0085】

なお、ゲート電極411、ゲート電極412、補助電源線407、電極451、走査線452を形成する際に用いるマスクとして、レジストの代わりに酸化珪素、酸化窒化珪素等をマスクとして用いてもよい。この場合、パターニングして酸化珪素、酸化窒化珪素等のマスクを形成する工程が加わるが、エッチング時におけるマスクの膜減りがレジストよりも少ないため、所望の形状を有するゲート電極411、ゲート電極412、補助電源線407、電極451、走査線452を形成することができる。またマスクを用いずに、液滴吐出法を用いて選択的にゲート電極411、ゲート電極412、補助電源線407、電極451、走査線452を形成しても良い。なお液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出または噴出することで所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。

【0086】

なお、ゲート電極411、ゲート電極412、補助電源線407、電極451、走査線452を形成する際に、用いる導電膜の材料によって、最適なエッチングの方法、エッチャントの種類を適宜選択すれば良い。以下、1層目の導電膜409として窒化タンタルを、2層目の導電膜410としてタンゲステンを用いる場合のエッチングの方法の一例について、具体的に説明する。

【0087】

まず、窒化タンタル膜を形成した後、窒化タンタル膜上にタンゲステン膜を形成する。そして、タンゲステン膜上にマスクを形成し、第1のエッチングを行う。第1のエッチングでは、まず第1のエッチング条件を用いた後に、第2のエッチング条件を用いる。第1のエッチング条件では、ICP (Inductively Coupled Plasma : 誘導結合型プラズマ) エッチング法を用い、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25:25:10 (sccm) とし、1Paの圧力でコイル型の電極に500WのRF (13.56MHz) 電力を投入してプラズマを生成してエッチングを行う。そして、基板側(試料ステージ)にも150WのRF (13.56MHz) 電力を投入し、実質的に負の自己バイアス電圧を印加する。この第1のエッチング条件を用いることにより、タンゲステン膜を、その端部がテーパー形状になるようにエッチングすることができる。

【0088】

次に、第2のエッチング条件を用いてエッチングを行う。第2のエッチング条件は、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とを用い、それぞれのガス流量比を30:30 (sccm) とし、1Paの圧力でコイル型の電極に500WのRF (13.56MHz) 電力を投入してプラズマを生成して約30秒程度のエッチングを行う。基板側(試料ステージ)にも20WのRF (13.56MHz) 電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した第2のエッチング条件ではタンゲステン膜及び窒化タンタル膜とも同程度にエッチングされる。

【0089】

上記第1のエッチングでは、マスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により窒化タンタル膜及びタンゲステン膜の端部が、角度15~45°程度のテーパー形状となる。なお、ゲート絶縁膜408のうち、第1のエッチングにより露出した部分は、その他の窒化タンタル膜及びタンゲステン膜で覆われている部分よりも、20~50nm程度エッチングされ薄くなる。

10

20

30

40

50

## 【0090】

次いで、マスクを除去せずに第2のエッチングを行う。第2のエッチングでは、エッチングガスに  $\text{C F}_4$  と  $\text{C l}_2$  と  $\text{O}_2$  を用い、タンゲステン膜を選択的にエッチングする。この時、第2のエッチングにより、タンゲステン膜が優先的にエッチングされるが、窒化タンタル膜はほとんどエッチングされない。

## 【0091】

上述した第1のエッチング及び第2のエッチングにより、窒化タンタルを用いた導電膜409と、導電膜409よりも幅の狭い、タンゲステンを用いた導電膜410とを、形成することができる。

## 【0092】

そして、上述した第1のエッチング及び第2のエッチングにより形成される導電膜409及び導電膜410をマスクとして用いることで、マスクを新たに形成せずとも、ソース領域、ドレイン領域、LDD領域として機能する不純物領域を半導体膜403、半導体膜404内に作り分けることができる。

## 【0093】

不純物領域を形成した後、不純物領域の加熱処理による活性化を行っても良い。例えば、50nmの酸化窒化珪素膜を形成した後、550、4時間、窒素雰囲気中において、加熱処理を行えばよい。

## 【0094】

また、水素を含む窒化珪素膜を、100nmの膜厚に形成した後、410、1時間、窒素雰囲気中において加熱処理を行ない、半導体膜403、半導体膜404を水素化しても良い。或いは、酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で、400~700（好ましくは500~600）で加熱処理を行ない、さらに、3~100%の水素を含む雰囲気中で、300~450で1~12時間の加熱処理を行うことで、半導体膜403、半導体膜404を水素化するようにしても良い。この工程により、熱的に励起された水素によりダングリングボンドを終端することができる。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。また活性化処理は、後の絶縁膜413が形成された後に行っても良い。

## 【0095】

加熱処理には、ファーネスアニール炉を用いる熱アニール法、レーザーアニール法またはラピッドサーマルアニール法（RTA法）などを用いることが出来る。加熱処理により、水素化のみならず、半導体膜403、半導体膜404に添加された不純物元素の活性化も行なうことが出来る。

## 【0096】

上記一連の工程によって、nチャネル型トランジスタ405と、発光素子に供給する電流を制御するpチャネル型トランジスタ406とを形成することができる。なお、トランジスタの作製方法は、上述した工程に限定されない。

## 【0097】

次に図6（A）に示すように、トランジスタ405、トランジスタ406、補助電源線407を覆うように、また図6（A）には図示されていないが、さらに電極451、走査線452を覆うように、絶縁膜413を形成する。絶縁膜413は必ずしも設ける必要はないが、絶縁膜413を形成することで、アルカリ金属やアルカリ土類金属などの不純物が、トランジスタ405、トランジスタ406へ侵入するのを防ぐことが出来る。具体的に絶縁膜413として、窒化珪素、窒化酸化珪素、窒化アルミニウム、酸化アルミニウム、酸化珪素、酸化窒化珪素などを用いるのが望ましい。本実施の形態では、膜厚600nm程度の酸化窒化珪素膜を、絶縁膜413として用いる。この場合、上記水素化の工程は、該酸化窒化珪素膜形成後に行っても良い。

## 【0098】

次に、トランジスタ405、トランジスタ406、補助電源線407を覆うように、また図6（A）には図示されていないが、さらに電極451、走査線452を覆うように、絶

10

20

30

40

50

縁膜413上に絶縁膜414を形成する。絶縁膜414は、アクリル、ポリイミド、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）、シロキサン系樹脂、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、PSG（リンガラス）、BPSG（リンボロンガラス）、アルミナ等を用いることができる。シロキサン系樹脂は、シリコン（Si）と酸素（O）との結合で骨格構造が構成される材料である。置換基として、水素の他、フッ素、フルオロ基、有機基（例えばアルキル基、芳香族炭化水素基）のうち、少なくとも1種を有していても良い。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁膜414を形成しても良い。

## 【0099】

10

絶縁膜414の形成には、その材料に応じて、CVD法、スパッタ法、SOG法、スピニコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。

## 【0100】

本実施の形態では、絶縁膜413及び絶縁膜414が層間絶縁膜として機能しているが、単層の絶縁膜を層間絶縁膜として用いても良いし、積層させた三層以上の絶縁膜を層間絶縁膜として用いても良い。

## 【0101】

20

次に、半導体膜403、半導体膜404がそれぞれ一部露出するように絶縁膜413及び絶縁膜414にコンタクトホールを形成する。コンタクトホール開口時のエッチングに用いられるガスは、CHF<sub>3</sub>とHeの混合ガスを用いるのが好ましいが、これに限定されるものではない。そして、図6（B）に示されるように、該コンタクトホールを介して半導体膜403に接する導電膜415及び導電膜416と、該コンタクトホールを介して補助電源線407に接する導電膜417及び導電膜418と、該コンタクトホールを介して半導体膜404に接する導電膜419及び導電膜418とを形成する。

## 【0102】

図10は、導電膜415～導電膜419が形成された画素の上面図に相当し、図10の破線A1-A2における断面図、破線B1-B2における断面図、破線C1-C2における断面図が、図6（B）に図示されている。図10に示すように、導電膜416は、その一部がゲート電極412として機能する導電膜409及び導電膜410に、接続されている。導電膜415は信号線として機能する。また、導電膜417は、補助配線として機能する。また、導電膜418は電源線として機能し、他の電源線として機能する導電膜418に、補助電源線407を介して電気的に接続されている。そして図10に示すように、導電膜415～導電膜419と共に、導電膜420が、コンタクトホールを介して走査線452に接続するように、形成されている。導電膜420は、走査線用補助配線として機能する。

30

## 【0103】

導電膜415～導電膜420は、CVD法やスパッタリング法等により形成することができる。具体的に導電膜415～導電膜420として、アルミニウム（Al）、タンゲステン（W）、チタン（Ti）、タンタル（Ta）、モリブデン（Mo）、ニッケル（Ni）、白金（Pt）、銅（Cu）、金（Au）、銀（Ag）、マンガン（Mn）、ネオジム（Nd）、炭素（C）、珪素（Si）等を用いることが出来る。また上記元素を主成分とする合金を用いても良いし、上記元素を含む化合物を用いても良い。導電膜415～導電膜420は、上記元素を有する単数の膜を、または上記元素を有する積層された複数の膜を、用いることが出来る。

40

## 【0104】

アルミニウムを主成分とする合金の例として、アルミニウムを主成分としニッケルを含むものが挙げられる。また、アルミニウムを主成分とし、ニッケルと、炭素または珪素の一方または両方とを含むものも例として挙げることが出来る。アルミニウムやアルミニウム

50

シリコンは抵抗値が低く、安価であるため、導電膜415～導電膜420を形成する材料として最適である。特にアルミニウムシリコンは、導電膜415～導電膜420をパターニングするとき、レジストベークにおけるヒロックの発生をアルミニウム膜に比べて防止することができる。また、珪素(Si)の代わりに、アルミニウム膜に0.5%程度のCuを混入させても良い。

【0105】

導電膜415～導電膜420は、例えば、バリア膜とアルミニウムシリコン膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデンまたはモリブデンの窒化物を用いて形成された膜である。アルミニウムシリコン膜を間に挟むようにバリア膜を形成すると、アルミニウムやアルミニウムシリコンのヒロックの発生をより防止することができる。また、還元性の高い元素であるチタンを用いてバリア膜を形成すると、半導体膜403、半導体膜404上に薄い酸化膜ができていたとしても、バリア膜に含まれるチタンがこの酸化膜を還元し、導電膜415、導電膜416、導電膜418、導電膜419と、半導体膜403、半導体膜404とが良好なコンタクトをとることが出来る。またバリア膜を複数積層するようにして用いても良い。その場合、例えば、導電膜415～導電膜420を下層からチタン、窒化チタン、アルミニウムシリコン、チタン、窒化チタンの5層構造とすることが出来る。

【0106】

導電膜415～導電膜420に用いられる少なくとも1つの導電膜の電気伝導率は、絶縁膜413及び絶縁膜414の下層に形成されている、ゲート電極411、ゲート電極412、補助電源線407、電極451及び走査線452に用いられる少なくとも1つの導電膜の電気伝導率よりも高いことが望ましい。或いは、導電膜415～導電膜420のいずれかの部分の膜厚は、その厚さがゲート電極411、ゲート電極412、補助電源線407、電極451及び走査線452のいずれかの部分の膜厚よりも厚いことが望ましい。具体的に導電膜415～導電膜420のいずれかの部分の膜厚は、0.8μm以上1.5μm以下であることが望ましい。このように導電膜415～導電膜420の膜厚をとることによって、電気伝導率を高め、補助電源線と補助配線の合成抵抗及び走査線と走査線用補助配線の合成抵抗を低下させることができる。

【0107】

本実施の形態では、絶縁膜414に近い側から、膜厚100nm程度のチタン膜、膜厚700nm～1000nm程度のアルミニウム膜、膜厚100nm程度のチタン膜を積層し、これらの積層された膜をパターニングすることで、導電膜415～導電膜420を形成する。

【0108】

次に図7(A)に示すように、導電膜415～導電膜419を覆うように、また図示しないが導電膜420を覆うように、絶縁膜421を形成し、その後、導電膜419の一部が露出するように、該絶縁膜421にコンタクトホールを形成する。そして該コンタクトホールにおいて導電膜419と接するように、画素電極422を形成する。

【0109】

絶縁膜421は、有機樹脂膜、無機絶縁膜またはシロキサン系絶縁膜を用いて形成することができる。有機樹脂膜ならば、例えばアクリル、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテンなどを用いることができる。無機絶縁膜ならば酸化珪素、酸化窒化珪素、窒化酸化珪素、DLC(ダイヤモンドライカーボン)に代表される炭素を含む膜などを用いることができる。また絶縁膜421はその材料に応じて、CVD法、スパッタ法、液滴吐出法または印刷法などで形成することができる。なお、絶縁膜421は、水分や酸素などの発光素子の劣化を促進させる原因となる物質を、他の絶縁膜と比較して透過させにくい膜を用いることがより望ましい。この場合、RFスパッタ法で形成された窒化珪素、ダイヤモンドライカーボン(DLC)、窒化アルミニウムなどを絶縁膜421として用いることが望ましい。

10

20

30

40

50

## 【0110】

また、本実施の形態では、スパッタ法で、酸化珪素を含むインジウム錫酸化物 (ITO) を用いて透光性を有する導電膜を形成した後、該導電膜をパターニングすることで画素電極422を形成する。なおITOの他、インジウム錫酸化物 (ITO) 、酸化亜鉛 (ZnO) 、酸化インジウム亜鉛 (IZO) 、ガリウムを添加した酸化亜鉛 (GZO) など、ITO以外の透光性酸化物導電材料を、画素電極422に用いても良い。また画素電極422として、透光性酸化物導電材料の他に、例えば窒化チタン、窒化ジルコニウム、Ti、W、Ni、Pt、Cr、Ag、Al等の1つまたは複数からなる単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との三層構造等を用いることができる。ただし透光性酸化物導電材料以外の材料で画素電極422側から光を取り出す場合、光が透過する程度の膜厚 (好ましくは、5nm～30nm程度) で形成する。

10

## 【0111】

ITOを画素電極422に用いる場合、ターゲットとしてITOに酸化珪素が2～10重量%含まれたものを用いることができる。本実施の形態では、In<sub>2</sub>O<sub>3</sub>と、SnO<sub>2</sub>と、SiO<sub>2</sub>とを85:10:5の重量%の割合で含むターゲットを用い、Arの流量を50sccm、O<sub>2</sub>の流量を3sccm、スパッタ圧力を0.4Pa、スパッタ電力を1kW、成膜速度30nm/minとし、105nmの膜厚で、画素電極422となる導電膜を形成することができる。

20

## 【0112】

なお、導電膜419のうち画素電極422に接する部分に、アルミニウムなどのイオン化傾向が比較的大きい金属を用いる場合、透光性酸化物導電材料を画素電極422に用いると、導電膜419が電蝕を起こしやすい。しかし、本実施の形態では、絶縁膜414に近い側からチタン膜、アルミニウム膜、チタン膜を順に積層した導電膜で導電膜419を形成し、なおかつ導電膜419を絶縁膜421で覆っており、導電膜419のうち最上部のチタン膜と画素電極422とが、絶縁膜421に形成されたコンタクトホールを介して接している。よって、イオン化傾向が比較的小さい金属であるチタン膜などの金属膜で、イオン化傾向が比較的大きい金属であるアルミニウム膜などの金属膜を挟み込み、さらに絶縁膜421で導電膜419を覆うことで、導電膜419が画素電極422やその他の導電体と接触することにより電蝕を起こすのを防ぐことができる。なおかつ、導電率の比較的高いアルミニウム膜などの金属膜を導電膜419に用いることで、導電膜419の抵抗値を下げることができる。

30

## 【0113】

なお、画素電極422となる導電膜に、導電性高分子 (導電性ポリマーともいう) を含む導電性組成物を用いることもできる。導電性組成物は、画素電極422となる導電膜のシート抵抗が10000 / 以下、波長550nmにおける透光率が70%以上であることが好ましい。シート抵抗は、より低いことが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

## 【0114】

導電性高分子としては、いわゆる電子共役系導電性高分子を用いることができる。例えば電子共役系導電性高分子として、ポリアニリン及びまたはその誘導体、ポリピロール及びまたはその誘導体、ポリチオフェン及びまたはその誘導体、これらの2種以上の共重合体などがあげられる。

40

## 【0115】

共役系導電性高分子の具体例としては、ポリピロ-ル、ポリ(3-メチルピロ-ル)、ポリ(3-ブチルピロ-ル)、ポリ(3-オクチルピロ-ル)、ポリ(3-デシルピロ-ル)、ポリ(3,4-ジメチルピロ-ル)、ポリ(3,4-ジブチルピロ-ル)、ポリ(3-ヒドロキシピロ-ル)、ポリ(3-メチル-4-ヒドロキシピロ-ル)、ポリ(3-メトキシピロ-ル)、ポリ(3-エトキシピロ-ル)、ポリ(3-オクトキシピロ-ル)、ポリ(3-カルボキシルピロ-ル)、ポリ(3-メチル-4-カルボキシルピロ-ル)

50

、ポリ( N - メチルピロール)、ポリチオフェン、ポリ( 3 - メチルチオフェン)、ポリ( 3 - プチルチオフェン)、ポリ( 3 - オクチルチオフェン)、ポリ( 3 - デシルチオフェン)、ポリ( 3 - ドデシルチオフェン)、ポリ( 3 - メトキシチオフェン)、ポリ( 3 - エトキシチオフェン)、ポリ( 3 - オクトキシチオフェン)、ポリ( 3 - カルボキシリチオフェン)、ポリ( 3 - メチル - 4 - カルボキシリチオフェン)、ポリ( 3 , 4 - エチレンジオキシチオフェン)、ポリアニリン、ポリ( 2 - メチルアニリン)、ポリ( 2 - オクチルアニリン)、ポリ( 2 - イソブチルアニリン)、ポリ( 3 - イソブチルアニリン)、ポリ( 2 - アニリンスルホン酸)、ポリ( 3 - アニリンスルホン酸)等が挙げられる。

## 【 0116 】

上記 共役系導電性高分子を、単独で導電性組成物として画素電極 422 に使用してもよいし、導電性組成物の膜の厚さの均一性、膜強度等の膜特性を調整するために有機樹脂を添加して使用することができる。

10

## 【 0117 】

有機樹脂としては、導電性高分子と相溶または混合分散が可能であれば熱硬化性樹脂であつてもよく、熱可塑性樹脂であつてもよく、光硬化性樹脂であつてもよい。例えば、ポリエチレンテレフタレ - ト、ポリブチレンテレフタラ - ト、ポリエチレンナフタレ - ト等のポリエステル系樹脂、ポリイミド、ポリアミドイミド等のポリイミド系樹脂、ポリアミド 6 、ポリアミド 6 , 6 、ポリアミド 12 、ポリアミド 11 等のポリアミド樹脂、ポリフッ化ビニリデン、ポリフッ化ビニル、ポリテトラフルオロエチレン、エチレンテトラフルオロエチレンコポリマ - 、ポリクロロトリフルオロエチレン等のフッ素樹脂、ポリビニルアルコ - ル、ポリビニルエ - テル、ポリビニルブチラ - ル、ポリ酢酸ビニル、ポリ塩化ビニル等のビニル樹脂、エポキシ樹脂、キシレン樹脂、アラミド樹脂、ポリウレタン系樹脂、ポリウレア系樹脂、メラミン樹脂、フェノ - ル系樹脂、ポリエ - テル、アクリル系樹脂及びこれらの共重合体等が挙げられる。

20

## 【 0118 】

さらに、導電性組成物の電気伝導度を調整するために、導電性組成物にアクセプタ性またはドナー性ド - パントをド - ピングすることにより、共役系導電性高分子の共役電子の酸化還元電位を変化させてもよい。

## 【 0119 】

アクセプタ性ド - パントとしては、ハロゲン化合物、ルイス酸、プロトン酸、有機シアノ化合物、有機金属化合物等を使用することができる。ハロゲン化合物としては、塩素、臭素、ヨウ素、塩化ヨウ素、臭化ヨウ素、フッ化ヨウ素等が挙げられる。ルイス酸としては五フッ化燐、五フッ化ヒ素、五フッ化アンチモン、三フッ化硼素、三塩化硼素、三臭化硼素等が挙げられる。プロトン酸としては、塩酸、硫酸、硝酸、リン酸、ホウフッ化水素酸、フッ化水素酸、過塩素酸等の無機酸と、有機カルボン酸、有機スルホン酸等の有機酸を挙げることができる。有機カルボン酸及び有機スルホン酸としては、前記カルボン酸化合物及びスルホン酸化合物を使用することができる。有機シアノ化合物としては、共役結合に二つ以上のシアノ基を含む化合物が使用できる。例えば、テトラシアノエチレン、テトラシアノエチレンオキサイド、テトラシアノベンゼン、テトラシアノキノジメタン、テトラシアノアザナフタレン等を挙げられる。

30

## 【 0120 】

ドナー性ドーパントとしては、アルカリ金属、アルカリ土類金属、4級アミン化合物等を挙げることができる。

40

## 【 0121 】

導電性組成物を、水または有機溶剤(アルコール系溶剤、ケトン系溶剤、エステル系溶剤、炭化水素系溶剤、芳香族系溶剤など)に溶解させて、湿式法により画素電極 422 となる導電膜を形成することができる。

## 【 0122 】

導電性組成物を溶解する溶媒としては、特に限定することではなく、上記した導電性高分子及び有機樹脂などの高分子樹脂化合物を溶解するものを用いればよい。例えば、水、メタ

50

ノール、エタノール、プロピレンカーボネート、N-メチルピロリドン、ジメチルホルムアミド、ジメチルアセトアミド、シクロヘキサン、アセトン、メチルエチルケトン、メチルイソブチルケトン、トルエンなどの単独もしくは混合溶剤に導電性組成物を溶解すればよい。

【0123】

導電性組成物の成膜は上述のように溶媒に溶解した後、塗布法、コーティング法、液滴吐出法（インクジェット法ともいう）、印刷法等の湿式法を用いて成膜することができる。溶媒の乾燥は、熱処理を行ってもよいし、減圧下で行ってもよい。また、有機樹脂が熱硬化性の場合は、さらに加熱処理を行い、光硬化性の場合は、光照射処理を行えばよい。

【0124】

画素電極422となる導電膜を形成した後、その表面が平坦化されるように、CMP法、ポリビニルアルコール系の多孔質体による拭净などで研磨しておいても良い。

【0125】

次に、図7(A)に示すように、画素電極422の一部を覆うように、絶縁膜421上に、開口部を有する隔壁423を形成する。隔壁423の開口部において画素電極422はその一部が露出している。隔壁423は、有機樹脂膜、無機絶縁膜またはシロキサン系絶縁膜を用いて形成することができる。有機樹脂膜ならば、例えばアクリル、ポリイミド、ポリアミドなど、無機絶縁膜ならば酸化珪素、窒化酸化珪素などを用いることができる。特に感光性の有機樹脂膜を隔壁423に用い、画素電極422上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することで、画素電極422と後に形成される共通電極425とが接続してしまうのを防ぐことができる。このとき、マスクを液滴吐出法または印刷法で形成することができる。また隔壁423自体を、液滴吐出法または印刷法で形成することもできる。

【0126】

図11は、画素電極422及び隔壁423が形成された画素の上面図に相当し、図11の破線A1-A2における断面図、破線B1-B2における断面図、破線C1-C2における断面図が、図7(A)に図示されている。なお図11では、隔壁423が有する開口部の位置を、破線で示している。図11に示すように、隔壁423は、絶縁膜414上に形成された導電膜415～導電膜420を全て覆うように形成されている。上記構成により、抵抗値を下げるために導電膜415～導電膜420の膜厚を0.8μm以上1.5μm以下程度に大きくした場合においても、後に形成される電界発光層424が、導電膜415～導電膜420と絶縁膜414との間に形成される段差により、膜厚が極端に薄くなる、或いは段切れを起こすのを防ぐことができる。

【0127】

次に、電界発光層424を形成する前に、隔壁423及び画素電極422に吸着した水分や酸素等を除去するために、大気雰囲気下で加熱処理または真空雰囲気下で加熱処理（真空ベーク）を行なっても良い。具体的には、基板の温度を200～450、好ましくは250～300で、0.5～20時間程度、真空雰囲気下で加熱処理を行なう。望ましくは $3 \times 10^{-7}$  Torr以下とし、可能であるならば $3 \times 10^{-8}$  Torr以下とするのが最も望ましい。そして、真空雰囲気下で加熱処理を行なった後に電界発光層424を成膜する場合、電界発光層424を成膜する直前まで当該基板を真空雰囲気下に置いておくことで、信頼性をより高めることができる。また真空ベークの前または後に、画素電極422に紫外線を照射してもよい。

【0128】

そして、図7(B)に示すように、隔壁423の開口部において画素電極422と接するように、電界発光層424を形成する。電界発光層424は、単数の層で構成されていても、複数の層が積層されるように構成されていても良く、各層には有機材料のみならず無機材料が含まれていても良い。電界発光層424におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光（蛍光）と三重項励起状態から基底状態に戻る際の発光（リン光）とが含まれる。複数の層で構成されている場合、陰極に相当する画素電極4

10

20

30

40

50

22上に、電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層する。なお画素電極422が陽極に相当する場合は、電界発光層424を、ホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層の順に積層して形成する。

【0129】

また電界発光層424は、高分子系有機化合物、中分子系有機化合物（昇華性を有さず、連鎖する分子の長さが10μm以下の有機化合物）、低分子系有機化合物、無機化合物のいずれを用いていても、液滴吐出法で形成することが可能である。また中分子系有機化合物、低分子系有機化合物、無機化合物は蒸着法で形成しても良い。

【0130】

そして、図7(B)に示すように、電界発光層424を覆うように共通電極425を形成する。共通電極425は、一般的に仕事関数の小さい金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることができる。具体的には、LiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、およびこれらを含む合金(Mg:Ag、Al:Liなど)の他、YbやEr等の希土類金属を用いて形成することもできる。また、電子注入性の高い材料を含む層を共通電極425に接するように形成することで、アルミニウムや、透光性酸化物導電材料等を用いた、通常の導電膜も用いることができる。

10

【0131】

隔壁423の開口部において、画素電極422と電界発光層424と共に共通電極425が重なり合うことで、発光素子426が形成される。

20

【0132】

なお、発光素子426からの光の取り出しが、画素電極422側からであっても良いし、共通電極425側からであっても良いし、その両方からであっても良い。上記3つの構成にうち、目的とする構成に合わせて、画素電極422、共通電極425それぞれの材料及び膜厚を選択するようにする。

【0133】

なお発光素子426を形成したら、共通電極425上に、絶縁膜を形成しても良い。該絶縁膜は、水分や酸素などの発光素子の劣化を促進させる原因となる物質を、他の絶縁膜と比較して透過させにくい膜を用いる。代表的には、例えばDLC膜、窒化炭素膜、RFスパッタ法で形成された窒化珪素膜等を用いるのが望ましい。また上述した水分や酸素などの物質を透過させにくい膜と、該膜に比べて水分や酸素などの物質を透過させやすい膜とを積層させて、上記絶縁膜として用いることも可能である。

30

【0134】

なお実際には、図7(B)に示す状態まで完成したら、さらに外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

【0135】

上記プロセスを経て、半導体表示装置が作製できる。

【0136】

なお、本実施の形態では、表示領域内のトランジスタ405、トランジスタ406の作製方法について述べたが、上記表示領域内のトランジスタに加え、駆動回路やその他の集積回路に用いられるトランジスタも、共に形成することが可能である。この場合、表示領域内のトランジスタと、駆動回路やその他の集積回路に用いられるトランジスタとにおいて、ゲート絶縁膜408の膜厚を全て同じにする必要はない。例えば、高速動作が要求される駆動回路やその他の集積回路に用いられるトランジスタにおいて、表示領域内のトランジスタよりも、ゲート絶縁膜408の膜厚が小さくなるようにしても良い。

40

【0137】

また、SOI(Silicon on Insulator)基板を利用することで、単結晶半導体を半導体膜402、半導体膜403として用いることも出来る。SOI基板は、例えば、スマートカットに代表されるUNIBOND、ELTRAN(Epitaxi

50

al Layer Transfer)、誘電体分離法、PACE(Plasma Assisted Chemical Etching)法などの貼り合わせ方法や、SIMOX(Separation by Implanted Oxygen)法などを用いて作製することができる。

【0138】

また、上記方法を用いて作製される半導体素子を、プラスチックなどの可撓性を有する基板上に転写することで、半導体表示装置を形成しても良い。転写方法としては、次のようなものがある。基板と半導体素子の間に金属酸化膜を設け、該金属酸化膜を結晶化により脆弱化して半導体素子を剥離し、転写する方法。基板と半導体素子の間に水素を含む非晶質珪素膜を設け、レーザ光の照射またはエッティングにより該非晶質珪素膜を除去することで基板と半導体素子とを剥離し、転写する方法。半導体素子が形成された基板を機械的に削除または溶液やガスによるエッティングで除去することで半導体素子を基板から切り離し、転写する方法等、様々な方法を用いることができる。なお転写は、発光素子を作製する前に行なうことが望ましい。

10

【0139】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

【0140】

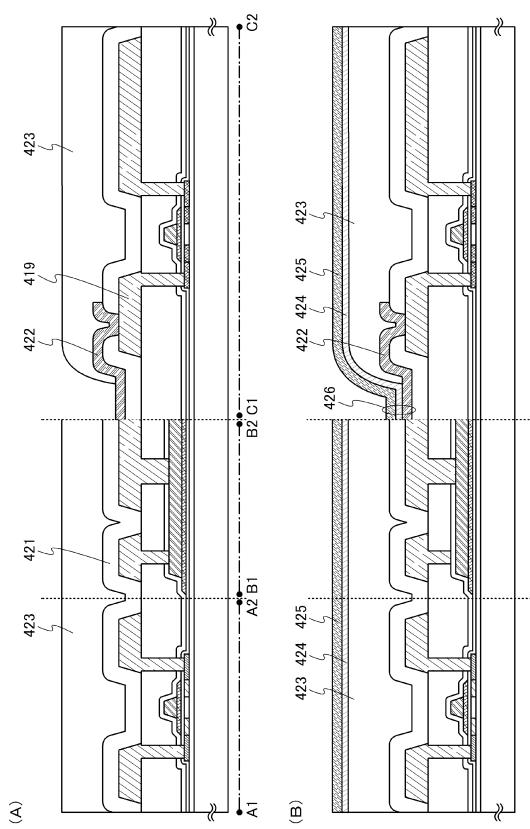

(実施の形態3)

本実施の形態では、画素の有するトランジスタの数及びその接続関係が実施の形態1とは異なる場合の、半導体表示装置の構成について説明する。

20

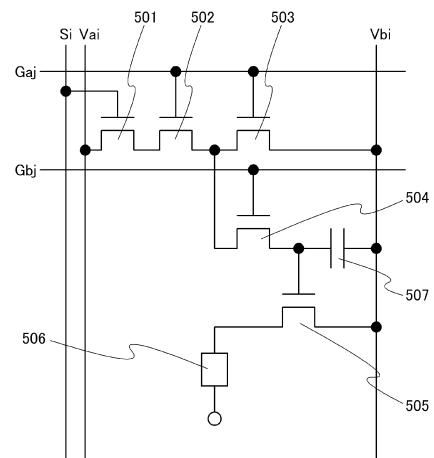

【0141】

図12に、本実施の形態の半導体表示装置が有する、画素の回路図を示す。図12に示す画素は、信号線 $S_i$ ( $i = 1 \sim x$ )と、第1の電源線 $V_{ai}$ ( $i = 1 \sim x$ )と、第2の電源線 $V_{bi}$ ( $i = 1 \sim x$ )と、第1の走査線 $G_{aj}$ ( $j = 1 \sim y$ )と、第2の走査線 $G_{bj}$ ( $j = 1 \sim y$ )とを少なくとも有している。さらに、図12に示す画素は、トランジスタ501～トランジスタ505と、発光素子506とを、少なくとも有している。また、図12に示す画素は、トランジスタ505のゲート電極と第2の電源線 $V_{bi}$ との間に保持容量507を有しているが、保持容量507は必ずしも設ける必要はない。

【0142】

トランジスタ501のゲート電極は、信号線 $S_i$ に接続されている。また、トランジスタ501のソース領域とドレイン領域は、一方が第1の電源線 $V_{ai}$ に接続されており、他方がトランジスタ502のソース領域とドレイン領域の一方に接続されている。トランジスタ502のゲート電極は、第1の走査線 $G_{aj}$ に接続されている。また、トランジスタ502のソース領域とドレイン領域の他方は、トランジスタ503のソース領域とドレイン領域の一方及びトランジスタ504のソース領域とドレイン領域の一方に、接続されている。トランジスタ503のゲート電極は、第1の走査線 $G_{aj}$ に接続されている。また、トランジスタ503のソース領域とドレイン領域の他方は、第2の電源線 $V_{bi}$ に接続されている。トランジスタ504のゲート電極は、第2の走査線 $G_{bj}$ に接続されている。また、トランジスタ504のソース領域とドレイン領域の他方は、トランジスタ505のゲート電極に接続されている。トランジスタ505のソース領域とドレイン領域は、一方が第2の電源線 $V_{bi}$ に接続されており、他方が発光素子506の画素電極に接続されている。

30

【0143】

また、トランジスタ502とトランジスタ503は、互いに逆の極性を有しており、一方がオンの時に他方はオフとなる。

【0144】

次に、図12に回路図で示した表示領域の上面図を、図13に一例として示す。また、図13の破線A1-A2における断面図を図14(A)に、破線B1-B2における断面図を図14(B)に、破線C1-C2における断面図を図14(C)に示す。なお、発光素子506は、画素電極と、共通電極と、画素電極及び共通電極によって電流が供給される

40

50

電界発光層とを有している。ただし、図13と図14では、各種配線やトランジスタの配置を明確にするために、発光素子506のうち、画素電極522のレイアウトのみを示している。

【0145】

図13及び図14に示す本実施の形態の半導体表示装置では、発光素子506に電流を供給するための第2の電源線Vbiが、補助電源線508に直接接続されている。そして、図13及び図14では図示していないが、上記補助電源線508は、図13及び図14に図示されている第2の電源線Vbiとは別の第2の電源線Vbiに接続されており、これらの2つの第2の電源線Vbiどうしは、補助電源線508を介して電気的に接続されている。なお、図13及び図14では、第2の電源線Vbiと補助電源線508とが直接接続されることで、第2の電源線Vbiどうしを電気的に接続している例を示しているが、第2の電源線Vbiの一つと補助電源線508とが、別の配線を介して電気的に接続されても良い。

10

【0146】

本実施の形態では、少なくとも2つの第2の電源線Vbiを、補助電源線508を介して電気的に接続することで、画素に供給するべき電流の大きさが第2の電源線Vbiごとに大幅に異なる場合でも、電位が降下することによって第2の電源線Vbi内に生じる電位差が、第2の電源線Vbiどうしで異なるのを防ぐことができる。よって、電位の降下に起因する表示領域内の輝度むらを防ぐことができる。

20

【0147】

さらに、図13及び図14に示す本実施の形態の半導体表示装置では、補助電源線508に直接接続された補助配線509と、第1の走査線Gajに直接接続された走査線用補助配線510と、第2の走査線Gbjに直接接続された走査線用補助配線511とを有する。なお、図13及び図14では、補助電源線508が直接補助配線509に接続されているが、補助電源線508が別の異なる配線を介して、補助配線509と電気的に接続されても良い。また図13及び図14では、第1の走査線Gajが直接走査線用補助配線510に接続されているが、第1の走査線Gajが別の異なる配線を介して、走査線用補助配線510と電気的に接続されても良い。また図13及び図14では、第2の走査線Gbjが直接走査線用補助配線511に接続されているが、第2の走査線Gbjが別の異なる配線を介して、走査線用補助配線511と電気的に接続されても良い。

30

【0148】

本実施の形態の半導体表示装置では、補助電源線508に直接、或いは電気的に接続された補助配線509を設けることで、補助電源線508と、補助配線509との合成抵抗を下げることができる。よって、補助電源線508の電位の降下を防ぎ、延いては第2の電源線Vbiの電位の降下を防ぐことができる。

【0149】

また、図13及び図14に示す半導体表示装置では、走査線用補助配線510及び走査線用補助配線511を有する構成を示しているが、本実施の形態の半導体表示装置では少なくとも補助配線509を有していれば良く、必ずしも走査線用補助配線510及び走査線用補助配線511を有していないとも良い。ただし、走査線用補助配線510または走査線用補助配線511を設けることで、第1の走査線Gajと、走査線用補助配線510との合成抵抗を下げる、或いは第2の走査線Gbjと、走査線用補助配線511との合成抵抗を下げることができる。よって、第1の走査線Gajの電位の降下により、トランジスタ502のスイッチングまたはトランジスタ503のスイッチングを、的確なタイミングで制御できなくなってしまうことを、防ぐことができる。また、第2の走査線Gbjの電位の降下により、トランジスタ504のスイッチングを、的確なタイミングで制御できなくなってしまうことを、防ぐことができる。

40

【0150】

また本実施の形態では、少なくとも第2の電源線Vbi、補助配線509、走査線用補助配線510、走査線用補助配線511を、層間絶縁膜512の上に形成する。図13及び

50

図14では、第2の電源線Vb<sub>i</sub>、補助配線509、走査線用補助配線510、走査線用補助配線511に加えて、第1の電源線Va<sub>i</sub>の一部520と、信号線Siも、層間絶縁膜512の上に形成している例を示している。よって本実施の形態では、第2の電源線Vb<sub>i</sub>、補助配線509、走査線用補助配線510、走査線用補助配線511、信号線Si、第1の電源線Va<sub>i</sub>の一部520を、層間絶縁膜512の上に形成された単数の導電膜または積層された複数の導電膜を所望の形状に加工(パターニング)することで形成できる。従って、第2の電源線Vb<sub>i</sub>、補助配線509、走査線用補助配線510、走査線用補助配線511、信号線Si及び第1の電源線Va<sub>i</sub>の一部520は、1つのマスクで形成することができる。

## 【0151】

10

また本実施の形態では、トランジスタ501が有するゲート電極513、トランジスタ502が有するゲート電極514、トランジスタ503が有するゲート電極515、トランジスタ504が有する2つのゲート電極516、トランジスタ505が有するゲート電極517、保持容量507が有する一方の電極518、補助電源線508、第1の走査線Ga<sub>j</sub>、第2の走査線Gb<sub>j</sub>、第1の電源線Va<sub>i</sub>の一部521を、層間絶縁膜512の下に形成する。よって本実施の形態では、ゲート電極513～ゲート電極517、電極518、補助電源線508、第1の走査線Ga<sub>j</sub>、第2の走査線Gb<sub>j</sub>、第1の電源線Va<sub>i</sub>の一部521を、層間絶縁膜512を形成する前に、単数の導電膜または積層された複数の導電膜を所望の形状に加工することで形成できる。従って、ゲート電極513～ゲート電極517、電極518、補助電源線508、第1の走査線Ga<sub>j</sub>、第2の走査線Gb<sub>j</sub>、第1の電源線Va<sub>i</sub>の一部521は、1つのマスクで形成することができる。このため、本実施の形態の半導体表示装置は、マスク数を従来よりも増やすことなく作製することができる。

20

## 【0152】

なお、第2の電源線Vb<sub>i</sub>の一部は保持容量507が有する他方の電極として機能し、第2の電源線Vb<sub>i</sub>と、ゲート絶縁膜519と、電極518とが重なっている領域が、保持容量507として機能する。電極518と、トランジスタ505のゲート電極517とは、一続きの導電膜で形成されている。

## 【0153】

30

なお、ゲート電極513～ゲート電極517には、トランジスタ501～トランジスタ505の作製行程において施される加熱処理に耐えうる程度の耐熱性が要求される。よって、単数の導電膜または積層された複数の導電膜を所望の形状に加工(パターニング)することでゲート電極513～ゲート電極517と共に補助電源線508、第1の走査線Ga<sub>j</sub>、第2の走査線Gb<sub>j</sub>を形成する場合、ゲート電極513～ゲート電極517、補助電源線508、第1の走査線Ga<sub>j</sub>、第2の走査線Gb<sub>j</sub>に用いることができる材料の種類には、制限が生じる。そのため、ゲート電極513～ゲート電極517、補助電源線508、第1の走査線Ga<sub>j</sub>、第2の走査線Gb<sub>j</sub>をより抵抗率の低い材料で形成することが難しい。しかし本実施の形態では、トランジスタ501～トランジスタ505上に形成された層間絶縁膜512の、更に上において第2の電源線Vb<sub>i</sub>、補助配線509、走査線用補助配線510、走査線用補助配線511を形成する。よって、第2の電源線Vb<sub>i</sub>、補助配線509、走査線用補助配線510、走査線用補助配線511は、トランジスタ501～トランジスタ505を作製した後に形成されるので、ゲート電極513～ゲート電極517、補助電源線508、第1の走査線Ga<sub>j</sub>、第2の走査線Gb<sub>j</sub>ほど高い耐熱性は要求されない。そのため、第2の電源線Vb<sub>i</sub>、補助配線509、走査線用補助配線510、走査線用補助配線511に用いることができる材料は比較的自由度が高く、ゲート電極513～ゲート電極517、補助電源線508、第1の走査線Ga<sub>j</sub>、第2の走査線Gb<sub>j</sub>より抵抗率の低い材料を選択することが可能である。抵抗率の低い材料で補助配線509、走査線用補助配線510、走査線用補助配線511を作製することで、補助電源線508と補助配線509の合成抵抗、第1の走査線Ga<sub>j</sub>と走査線用補助配線510の合成抵抗、第2の走査線Gb<sub>j</sub>と走査線用補助配線511の合成抵抗を、より下げるこ

40

50

ができる。従って、第2の電源線V<sub>b</sub>iの電位の降下、第1の走査線G<sub>a</sub>jの電位の降下、第2の走査線G<sub>b</sub>jの電位の降下を防ぐことができる。

【0154】

なお、図13及び図14では、画素電極522の一部、第2の電源線V<sub>b</sub>i、補助配線509、走査線用補助配線510、走査線用補助配線511、第1の電源線V<sub>a</sub>iの一部520、信号線S<sub>i</sub>が、隔壁523によって覆われている。そして、画素電極522が形成されている領域のうち、画素電極522が隔壁523によって覆われていない一部露出している領域524において、隔壁523の後に形成される電界発光層及び共通電極が、画素電極522上に直接積層される。よって、画素電極522と、電界発光層及び共通電極とが直接重なる領域524において、発光素子506が形成される。

10

【0155】

図13及び図14に示すように、隔壁523は、層間絶縁膜512上に形成された第2の電源線V<sub>b</sub>i、補助配線509、走査線用補助配線510、走査線用補助配線511、第1の電源線V<sub>a</sub>iの一部520、信号線S<sub>i</sub>を全て覆うように形成されている。上記構成により、抵抗値を下げるために第2の電源線V<sub>b</sub>i、補助配線509、走査線用補助配線510、走査線用補助配線511、第1の電源線V<sub>a</sub>iの一部520、信号線S<sub>i</sub>の膜厚を0.8μm以上1.5μm以下程度に大きくした場合においても、後に形成される電界発光層が、第2の電源線V<sub>b</sub>i、補助配線509、走査線用補助配線510、走査線用補助配線511、第1の電源線V<sub>a</sub>iの一部520、信号線S<sub>i</sub>と層間絶縁膜512との間に形成される段差により、膜厚が極端に薄くなる、或いは段切れを起こすのを防ぐことができる。

20

【0156】

また、図13では、補助電源線508が複数並んで配置されている例を示している。第2の電源線V<sub>b</sub>iに与えられる電源電位の高さが、他の第2の電源線V<sub>b</sub>iに与えられる電源電位と異なっている場合において、共通の電源電位が与えられる第2の電源線V<sub>b</sub>iどうしを、補助電源線を介して電気的に接続する。図13に示す第2の電源線V<sub>b</sub>iと接続されている補助電源線508以外の他の補助電源線508は、他の共通の電源電位が与えられる第2の電源線V<sub>b</sub>iどうしを電気的に接続するのに用いることができる。

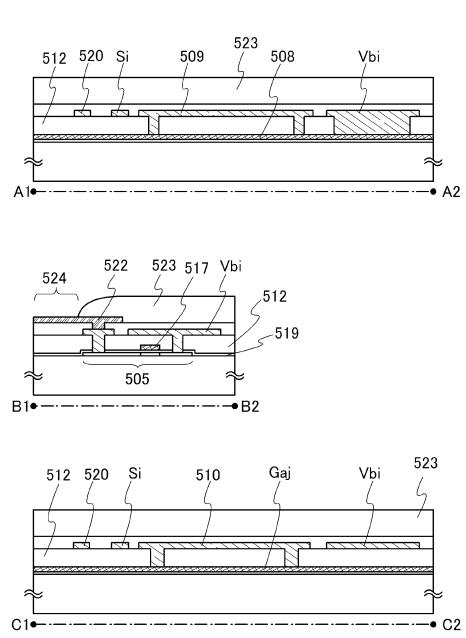

【0157】

図15に、R(赤)、G(緑)、B(青)の各色に対応する第2の電源線V<sub>b</sub>iどうしを電気的に接続した場合の、表示領域の上面図を一例として示す。図15では、R(赤)に対応する第2の電源線V<sub>b</sub>(R)、G(緑)に対応する第2の電源線V<sub>b</sub>(G)、B(青)に対応する第2の電源線V<sub>b</sub>(B)に、それぞれ与えられる電源電位が、互いに異なっている。さらに、第2の電源線V<sub>b</sub>(R)は、補助電源線508rを介して、隣接する他のR(赤)に対応する第2の電源線V<sub>b</sub>(R)に電気的に接続される。また、第2の電源線V<sub>b</sub>(G)は、補助電源線508gを介して、隣接する他のG(緑)に対応する第2の電源線V<sub>b</sub>(G)に電気的に接続される。また、第2の電源線V<sub>b</sub>(B)は、補助電源線508bを介して、隣接する他のB(青)に対応する第2の電源線V<sub>b</sub>(B)に電気的に接続される。

30

【0158】

なお図15では、第2の電源線V<sub>b</sub>(R)、第2の電源線V<sub>b</sub>(G)、第2の電源線V<sub>b</sub>(B)と、補助電源線508r、補助電源線508g、補助電源線508bとが、それぞれ直接接続されることで、隣接する第2の電源線V<sub>b</sub>(R)どうし、または隣接する第2の電源線V<sub>b</sub>(G)どうし、または隣接する第2の電源線V<sub>b</sub>(B)どうしを電気的に接続している例を示している。しかし、第2の電源線V<sub>b</sub>(R)、第2の電源線V<sub>b</sub>(G)、第2の電源線V<sub>b</sub>(B)と、補助電源線508r、補助電源線508g、補助電源線508bとが、それぞれ別の配線を介して電気的に接続されても良い。

40

【0159】

さらに図15では、補助電源線508r、補助電源線508g、補助電源線508bにそれぞれ直接接続された補助配線509r、補助配線509g、補助配線509bを示して

50

いる。なお、図15では、補助電源線508r、補助電源線508g、補助電源線508bが直接補助配線509r、補助配線509g、補助配線509bにそれぞれ接続されているが、補助電源線508r、補助電源線508g、補助電源線508bが別の異なる配線を介して、補助配線509r、補助配線509g、補助配線509bとそれぞれ電気的に接続されていても良い。

#### 【0160】

本実施の形態の半導体表示装置では、補助電源線508r、補助電源線508g、補助電源線508bに直接、或いは電気的にそれぞれ接続された補助配線509r、補助配線509g、補助配線509bを設けることで、補助電源線508rと補助配線509rの合成抵抗、補助電源線508gと補助配線509gの合成抵抗、補助電源線508bと補助配線509bの合成抵抗を、それぞれ下げることができる。よって、補助電源線508r、補助電源線508g、補助電源線508bの電位の降下を防ぎ、延いては第2の電源線Vb(R)、第2の電源線Vb(G)、第2の電源線Vb(B)の電位の降下を防ぐことができる。

10

#### 【0161】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【0162】

##### (実施の形態4)

本実施の形態では、層間絶縁膜上に形成される各種配線の膜厚を、部分的に異ならせることができる、半導体表示装置の作製方法について説明する。

20

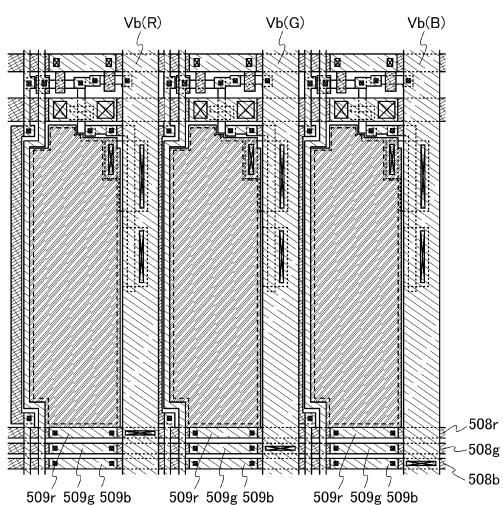

#### 【0163】

まず図16(A)に示すように、トランジスタ1601と、トランジスタ1601を覆っている層間絶縁膜1602と、層間絶縁膜1602を覆っている導電膜1603とを形成する。導電膜1603は、層間絶縁膜1602に形成されたコンタクトホールを介して、トランジスタ1601が有する半導体膜1604に接続されている。トランジスタ1601、層間絶縁膜1602、導電膜1603は、例えば、実施の形態2に示した作製方法を用いて形成することができる。

#### 【0164】

なお、図16では、導電膜1603は、3つの積層された導電膜で形成されている例を示している。ただし本実施の形態では、導電膜1603が1つの導電膜で形成されていても良いし、2つの積層された導電膜または4つ以上の積層された導電膜を用いて形成されていても良い。導電膜1603に用いられる少なくとも1つの導電膜の電気伝導率は、層間絶縁膜1602の下層に形成されている、トランジスタ1601のゲート電極1605に用いられる少なくとも1つの導電膜の電気伝導率よりも高いことが望ましい。或いは、導電膜1603のいずれかの部分の膜厚は、その厚さがゲート電極1605のいずれかの部分の膜厚よりも厚いことが望ましい。具体的に導電膜1603のいずれかの部分の膜厚は、0.8μm以上1.5μm以下であることが望ましい。このように導電膜1603の膜厚をとることによって、電気伝導率を高めることができる。

30

#### 【0165】

本実施の形態では、層間絶縁膜1602に近い側から、膜厚100nm程度のチタン膜、膜厚700nm~1000nm程度のアルミニウム膜、膜厚100nm程度のチタン膜を積層したものを、導電膜1603として用いる。

40

#### 【0166】

次に、図16(A)に示すように、導電膜1603上にレジスト1606を塗布する。レジスト1606は、ポジ型レジストまたはネガ型レジストを用いることができる。本実施の形態では、ポジ型レジストを用いて示す。そして、多階調マスク1607を用いてレジスト1606を部分的に露光する。

#### 【0167】

多階調マスクとは、露光部分、中間露光部分、及び未露光部分に3つの露光レベルを行うことが可能なマスクであり、一度の露光及び現像工程により、複数(代表的には二種類)

50

の厚さの領域を有するレジストマスクを形成することが可能である。このため、多階調マスクを用いることで、フォトマスクの枚数を削減することが可能である。

【0168】

多階調マスクの代表例としては、グレートーンマスク、ハーフトーンマスクがある。グレートーンマスクは、透光性を有する基板及びその上に形成される遮光部並びに回折格子で構成される。遮光部においては、光の透過率が0%である。一方、回折格子はスリット、ドット、メッシュ等の光透過部の間隔を、露光に用いる光の解像度限界以下の間隔とすることにより、光の透過率を制御することができる。なお、回折格子は、周期的なスリット、ドット、メッシュ、または非周期的なスリット、ドット、メッシュどちらも用いることができる。透光性を有する基板は、石英等の透光性を有する基板を用いることができる。遮光部及び回折格子は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成することができる。グレートーンマスクに露光光を照射した場合、遮光部においては、光の透過率は0%であり、遮光部及び回折格子が設けられていない領域では光の透過率は100%である。また、回折格子においては、10~70%の範囲で光の透過率を調整することができる。回折格子における光の透過率の調整は、回折格子のスリット、ドット、またはメッシュの間隔及びピッチの調整により可能である。

10

【0169】

一方、ハーフトーンマスクは、透光性を有する基板及びその上に形成される半透過部並びに遮光部で構成される。半透過部は、MoSiN、MoSi、MoSiO、MoSiON、CrSiなどを用いることができる。遮光部は、クロムや酸化クロム等の光を吸収する遮光材料を用いて形成することができる。ハーフトーンマスクに露光光を照射した場合、遮光部においては、光の透過率は0%であり、遮光部及び半透過部が設けられていない領域では光の透過率は100%である。また、半透過部においては、10~70%の範囲で光の透過率を調整することができる。半透過部に於ける光の透過率の調整は、半透過部の材料により調整により可能である。

20

【0170】

多階調マスクを用いて露光した後、現像することで、図16(B)に示すように、膜厚の異なる領域を有するレジストマスク1608を形成することができる。そして、レジストマスク1608を用いて導電膜1603をエッティングすることで、図16(B)に示すように、導電膜1609と導電膜1610とを形成する。導電膜1609と導電膜1610とは、それぞれコンタクトホールを介して半導体膜1604に接続されている。

30

【0171】

次に、レジストマスク1608をアッシングする。この結果、レジストの面積が縮小し、厚さが薄くなる。そして、レジストマスク1608のうち、導電膜1609上の膜厚の薄い領域のレジストが部分的に除去されることで、図16(C)に示すようにレジストマスク1611が形成される。

【0172】

次に、レジストマスク1611を用いて、導電膜1609をさらにエッティングする。この結果、図16(C)に示すように、膜厚が部分的に薄い導電膜1612を導電膜1609から形成することができる。なお、レジストマスク1608のアッシングの量が多いと、導電膜1610上のレジストマスク1611の面積が導電膜1610の面積よりも小さくなるため、レジストマスク1611を用いた上記エッティングにおいて、導電膜1610の端部もエッティングされることがある。

40

【0173】

また、図16(C)では、導電膜1609をエッティングする際、最も層間絶縁膜1602に近い導電膜のみが部分的に残存する例を示しているが、本発明はこの構成に限定されない。上層の2つの導電膜も、部分的に残存していても良い。

【0174】

そして図16(D)に示すように、レジストマスク1611を除去した後、導電膜1612及び導電膜1610を覆うように、層間絶縁膜1602上に絶縁膜1613を形成する

50

。そして絶縁膜1613にコンタクトホールを形成し、該コンタクトホールにおいて導電膜1612の膜厚の薄い部分と接続する画素電極1614を、絶縁膜1613上に形成する。

【0175】

そして、画素電極1614の一部を覆うように、絶縁膜1613上に隔壁1615を形成する。隔壁1615は開口部を有しており、該開口部において画素電極1614が一部露出している。また、隔壁1615は、少なくとも導電膜1612の膜厚の厚い部分と、導電膜1610と、重なるように形成する。上記構成により、抵抗値を下げるために、導電膜1612の膜厚の厚い部分及び導電膜1610の膜厚を、0.8μm以上1.5μm以下程度に大きくした場合においても、後に形成される電界発光層1616が、導電膜1612の膜厚の厚い部分及び導電膜1610と層間絶縁膜1602との間に形成される段差により、膜厚が極端に薄くなる、或いは段切れを起こすのを防ぐことができる。10

【0176】

さらに、画素電極1614が、導電膜1612の膜厚の薄い部分と接続されているので、画素電極1614が、導電膜1612の膜厚の薄い部分と層間絶縁膜1602との間に形成される段差により、膜厚が極端に薄くなる、或いは段切れを起こすのを防ぐことができる。

【0177】

次に、画素電極1614及び隔壁1615上に、電界発光層1616と、共通電極1617とを、順に積層するように形成する。画素電極1614と、電界発光層1616と、共通電極1617とが直接重なっている部分が、発光素子1618として機能する。20

【0178】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

【0179】

(実施の形態5)

本実施の形態では、層間絶縁膜上に形成された各種配線を用いて、発光素子から発せられる光を効率的に半導体表示装置の外部に取り出すことができる構成について、説明する。

【0180】

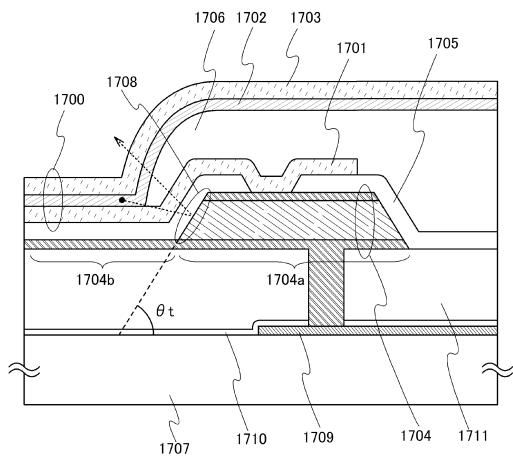

図17に、本実施の形態の半導体表示装置が有する発光素子と、該発光素子の近傍に設けられた配線との断面図を、一例として示す。発光素子1700は、画素電極1701と、電界発光層1702と、共通電極1703とを有している。また、配線1704は、その膜厚が異なる複数の領域で構成されている。具体的に、図17では、配線1704が、膜厚の大きい領域1704aと、膜厚の小さい領域1704bとを有している。30

【0181】

配線1704は絶縁膜1705で覆われており、絶縁膜1705に形成されたコンタクトホールを介して、配線1704と、絶縁膜1705上に形成された画素電極1701とが接続されている。なお図17では、配線1704のうち、膜厚の大きい領域1704aとコンタクトホールとが重なっている場合を例示しているが、本発明はこの構成に限定されない。配線1704のうち、膜厚の小さい領域1704bとコンタクトホールとが重なっていても良い。40

【0182】

また、画素電極1701の一部と、配線1704のうち膜厚の大きい領域1704aとは、隔壁1706によって覆われている。そして、画素電極1701のうち隔壁1706によって覆われずに露出している部分と、電界発光層1702と、共通電極1703とが重なり合っている部分が、発光素子1700として機能している。そして、該発光素子1700として機能している部分は、配線1704のうち、膜厚の小さい領域1704bと重なっている。

【0183】

配線1704のうち膜厚の大きい領域1704aが、隔壁1706によって覆われていることで、抵抗値を下げるために配線1704のうち領域1704aにおける膜厚を0.850

$\mu\text{m}$ 以上1.5  $\mu\text{m}$ 以下程度に大きくした場合においても、後に形成される電界発光層1702が、領域1704aと領域1704bとの間に形成される段差により、膜厚が極端に薄くなる、或いは段切れを起こすのを防ぐことができる。

【0184】

なお、膜厚の大きい領域1704aと膜厚の小さい領域1704bとを有する配線1704は、グレートーンマスク、ハーフトーンマスクなどの多階調マスクを用いることで、マスク数を増やすことに形成することができる。

【0185】

また、基板1707上には半導体膜1709が形成されており、半導体膜1709はゲート絶縁膜1710及び層間絶縁膜1711で覆われている。配線1704は層間絶縁膜1711上に形成されており、ゲート絶縁膜1710及び層間絶縁膜1711に形成されたコンタクトホールを介して配線1704と半導体膜1709が接続されている。なお、配線1704の種類によっては、ゲート電極と共にゲート絶縁膜1710上に形成された配線と、配線1704とが、層間絶縁膜1711に形成されたコンタクトホールを介して接続されていても良い。

10

【0186】

また、図17では、画素電極1701及び共通電極1703が透光性を有しており、配線1704が光を反射する材料を用いて形成されている。そして、配線1704のうち、膜厚の小さい領域1704bと、膜厚の大きい領域1704aの領域1704bに隣接している端部1708において、電界発光層1702から発せられる光を、基板1707とは反対の方向に向けて反射させることができる。よって、本実施の形態で示す半導体表示装置では、半導体表示装置から取り出される光は、電界発光層1702から直接基板1707とは反対の方向に発せられる光と、電界発光層1702から発せられた後、配線1704による反射を経て基板1707とは反対の方向に発せられる光とを含んでいる。

20

【0187】

さらに本実施の形態では、配線1704のうち、膜厚の大きい領域1704aの端部1708における勾配角度、すなわち端部1708で形成される面と、基板1707との間の角度tを、 $0^\circ < t < 90^\circ$ 、より好ましくは $50^\circ < t < 60^\circ$ とする。上記構成により、電界発光層1702から発せられる光のうち、横方向(基板1707の最大面積となる面と平行な方向)に向かっている光を、配線1704の端部1708において反射させ、基板1707と反対の方向に放出させることができる。

30

【0188】

なお、領域1704aの端部1708及び領域1704bにおいて、電界発光層1702から発せられる光が反射するように、配線1704に用いる材料を適宜選択する。例えば配線1704として、アルミニウム(A1)、タンクスチタン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pl)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、珪素(Si)等を用いることが出来る。また上記元素を主成分とする合金を用いても良いし、上記元素を含む化合物を用いても良い。配線1704は、上記元素を有する単数の膜を、または上記元素を有する積層された複数の膜を、用いることが出来る。

40

【0189】

なお、絶縁膜1705に酸化珪素を用いる場合、配線1704に用いる材料によっては、配線1704の表面が酸化してしまい、光が配線1704の表面において反射しにくくなることがある。絶縁膜1705として窒化珪素を用いるようにすることで、配線1704の表面における酸化を防ぎ、光を配線1704の表面において反射しやすくすることができる。或いは、配線1704に白金(Pl)、金(Au)、銀(Ag)などの酸化されにくい材料を用いることで、配線1704の表面における酸化を防ぐことができる。酸化されにくい材料を配線1704に用いる場合、窒化珪素よりも透光性の高い酸化珪素を絶縁膜1705に用いることができる。

【0190】

50

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

【実施例 1】

【0191】

本実施例では、半導体基板（ボンド基板）から支持基板（ベース基板）に転置した半導体膜を用いて半導体素子を形成する、半導体表示装置の作製方法について説明する。

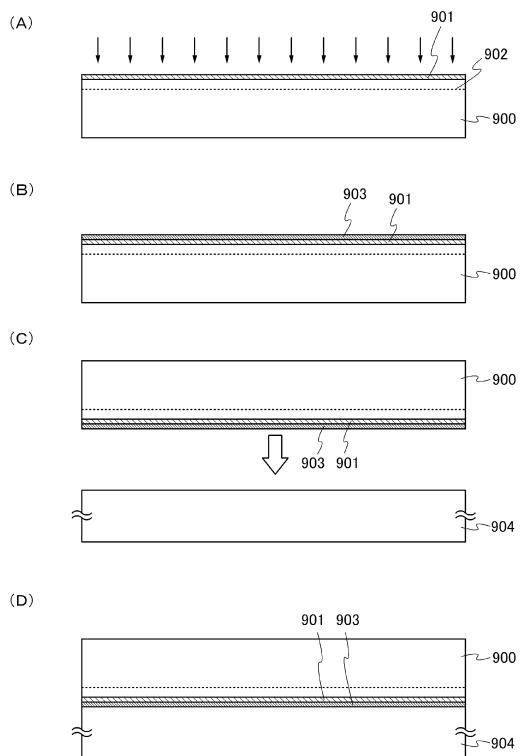

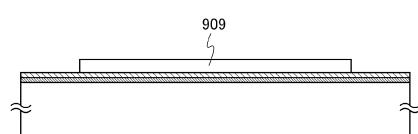

【0192】

まず図18（A）に示すように、ボンド基板900上に絶縁膜901を形成する。絶縁膜901は、酸化珪素、酸化窒化珪素、窒化酸化珪素、窒化珪素等の絶縁性を有する材料を用いて形成する。絶縁膜901は、単数の絶縁膜を用いたものであっても、複数の絶縁膜を積層して用いたものであっても良い。例えば本実施例では、ボンド基板900に近い側から、窒素よりも酸素の含有量が高い酸化窒化珪素、酸素よりも窒素の含有量が高い窒化酸化珪素の順に積層された絶縁膜901を用いる。

10

【0193】

例えば酸化珪素を絶縁膜901として用いる場合、絶縁膜901はシランと酸素、TEOS（テトラエトキシシラン）と酸素等の混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD等の気相成長法によって形成することができる。この場合、絶縁膜901の表面を酸素プラズマ処理で緻密化しても良い。また、窒化珪素を絶縁膜901として用いる場合、シランとアンモニアの混合ガスを用い、プラズマCVD等の気相成長法によって形成することができる。また、窒化酸化珪素を絶縁膜901として用いる場合、シランとアンモニアの混合ガス、またはシランと酸化窒素の混合ガスを用い、プラズマCVD等の気相成長法によって形成することができる。

20

【0194】

また絶縁膜901として、有機シランガスを用いて化学気相成長法により作製される酸化珪素を用いていても良い。有機シランガスとしては、テトラエトキシシラン（TEOS：化学式Si(OCH<sub>3</sub>)<sub>4</sub>）、テトラメチルシラン（TMS：化学式Si(CH<sub>3</sub>)<sub>4</sub>）、テトラメチルシクロテトラシロキサン（TMC TS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（SiH(OCH<sub>3</sub>)<sub>3</sub>）、トリスジメチルアミノシラン（SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>）等のシリコン含有化合物を用いることができる。

30

【0195】

次に図18（A）に示すように、ボンド基板900に、矢印で示すように水素又は希ガス、或いは水素イオン又は希ガスイオンを照射し、ボンド基板900の表面から一定の深さの領域に、微小ボイドを有する脆化層902を形成する。脆化層902が形成される位置は、上記照射の加速電圧によって決まる。そして脆化層902の位置により、ボンド基板900からベース基板904に転置する半導体膜908の厚さが決まるので、照射の加速電圧は半導体膜908の厚さを考慮して設定する。当該半導体膜908の厚さは10nm乃至200nm、好ましくは10nm乃至50nmの厚さとする。例えば水素をボンド基板900に照射する場合、ドーズ量は $3 \times 10^{16}$ 乃至 $1 \times 10^{17} / \text{cm}^2$ とするのが望ましい。

40

【0196】

なお、脆化層902を形成する上記工程において、ボンド基板900に高い濃度の水素又は希ガス、或いは水素イオン又は希ガスイオンを照射するので、ボンド基板900の表面が粗くなってしまい、ベース基板904との間ににおける接合で十分な強度が得られない場合がある。絶縁膜901を設けることで、水素又は希ガス、或いは水素と希ガスのイオンを照射する際にボンド基板900の表面が保護され、ベース基板904とボンド基板900の間ににおける接合を良好に行うことが出来る。

【0197】

次に図18（B）に示すように、絶縁膜901上に絶縁膜903を形成する。絶縁膜903は、絶縁膜901と同様に、酸化珪素、酸化窒化珪素、窒化酸化珪素、窒化珪素等の絶縁性を有する材料を用いて形成する。絶縁膜903は、単数の絶縁膜を用いたものであつ

50

ても、複数の絶縁膜を積層して用いたものであっても良い。また絶縁膜 903 として、有機シランガスを用いて化学気相成長法により作製される酸化珪素を用いていても良い。本実施例では、絶縁膜 903 として、有機シランガスを用いて化学気相成長法により作製される酸化珪素を用いる。

【0198】

なお絶縁膜 901 または絶縁膜 903 に窒化珪素、窒化酸化珪素などのバリア性の高い絶縁膜を用いることで、後に形成される半導体膜 909 にアルカリ金属やアルカリ土類金属などの不純物がベース基板 904 から入るのを防ぐことができる。

【0199】

なお本実施例では、脆化層 902 を形成した後に絶縁膜 903 を形成しているが、絶縁膜 903 は必ずしも設ける必要はない。ただし絶縁膜 903 は脆化層 902 を形成した後に形成されるので、脆化層 902 を形成する前に形成される絶縁膜 901 よりも、その表面の平坦性は高い。よって、絶縁膜 903 を形成することで、後に行われる接合の強度をより高めることができる。

【0200】

次に、ボンド基板 900 とベース基板 904 とを接合により貼り合わせる前に、ボンド基板 900 に水素化処理を行うようにしても良い。水素化処理は、例えば、水素雰囲気中にいて 350 、2 時間程度行う。

【0201】

そして図 18 (C) に示すように、ボンド基板 900 と、ベース基板 904 とを、絶縁膜 903 を間に挟むように重ねて、図 18 (D) に示すように貼り合わせる。絶縁膜 903 とベース基板 904 とが接合することで、ボンド基板 900 とベース基板 904 とを貼り合わせることができる。

【0202】

接合の形成はファン・デル・ワールス力を用いて行われているため、室温でも強固な接合が形成される。なお、上記接合は低温で行うことが可能であるため、ベース基板 904 は様々なものを用いることが可能である。例えばベース基板 904 としては、アルミニシリケートガラス、バリウムホウケイ酸ガラス、アルミニホウケイ酸ガラスなどのガラス基板の他、石英基板、サファイア基板などの基板を用いることが出来る。さらにベース基板 904 として、シリコン、ガリウムヒ素、インジウムリンなどの半導体基板などを用いることができる。

【0203】

なお、ベース基板 904 の表面にも絶縁膜を形成しておき、該絶縁膜と絶縁膜 903 との間で接合を行うようにしても良い。この場合、ベース基板 904 として上述したもののに、ステンレス基板を含む金属基板を用いても良い。また、プラスチック等の可撓性を有する合成樹脂からなる基板は、上記基板と比較して耐熱温度が一般的に低い傾向にあるが、作製工程における処理温度に耐え得るのであればベース基板 904 として用いることが可能である。プラスチック基板として、ポリエチレンテレフタラート (PET) に代表されるポリエステル、ポリエーテルスルホン (PES) 、ポリエチレンナフタレート (PEN) 、ポリカーボネート (PC) 、ポリエーテルエーテルケトン (PEEK) 、ポリスルホン (PSF) 、ポリエーテルイミド (PEI) 、ポリアリレート (PAR) 、ポリブチレンテレフタレート (PBT) 、ポリイミド、アクリロニトリルブタジエンスチレン樹脂、ポリ塩化ビニル、ポリプロピレン、ポリ酢酸ビニル、アクリル樹脂などが挙げられる。

【0204】

ボンド基板 900 として、シリコン、ゲルマニウムなどの単結晶半導体基板または多結晶半導体基板を用いることができる。その他に、ガリウムヒ素、インジウムリンなどの化合物半導体で形成された単結晶半導体基板または多結晶半導体基板を、ボンド基板 900 として用いることができる。またボンド基板 900 として、結晶格子に歪みを有するシリコン、シリコンに対しゲルマニウムが添加されたシリコンゲルマニウムなどの半導体基板を用いていても良い。歪みを有するシリコンは、シリコンよりも格子定数の大きいシリコン

10

20

30

40

50

ゲルマニウムまたは窒化珪素膜上における成膜により、形成することができる。

【0205】

なおベース基板904とボンド基板900とを貼り合わせた後に、加熱処理又は加圧処理を行っても良い。加熱処理又は加圧処理を行うことで接合の強度を向上させることができる。

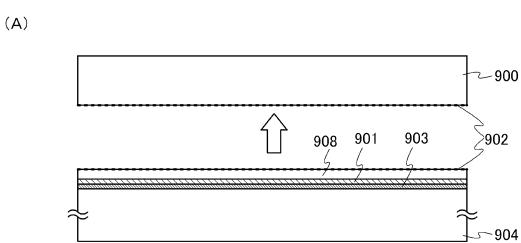

【0206】

上記接合を行った後、熱処理を行うことにより、脆化層902において隣接する微小ボイドどうしが結合して、微小ボイドの体積が増大する。その結果、図19(A)に示すように、脆化層902においてボンド基板900が劈開し、ボンド基板900の一部であった半導体膜908が乖離する。熱処理の温度はベース基板904の耐熱温度以下で行うことが好ましく、例えば400乃至600の範囲内で熱処理を行えば良い。この剥離により、半導体膜908が、絶縁膜901及び絶縁膜903と共にベース基板904に転置される。その後、絶縁膜903とベース基板904の接合をさらに強固にするため、400乃至600の熱処理を行うのが好ましい。

10

【0207】

半導体膜908の結晶面方位はボンド基板900の面方位によって制御することができる。形成する半導体素子に適した結晶面方位を有するボンド基板900を、適宜選択して用いればよい。またトランジスタの移動度は半導体膜908の結晶面方位によって異なる。より移動度の高いトランジスタを得たい場合、チャネルの向きと結晶面方位とを考慮し、ボンド基板900の貼り合わせの方向を定めるようにする。

20

【0208】

次に、転置された半導体膜908の表面を平坦化する。平坦化は必ずしも必須ではないが、平坦化を行うことで、後に形成されるトランジスタにおいて半導体膜908とゲート絶縁膜の界面の特性を向上させることが出来る。具体的に平坦化は、化学的機械的研磨(CMP: Chemical Mechanical Polishing)により、行うことができる。半導体膜908の厚さは、上記平坦化により薄膜化される。

【0209】

なお本実施例では、脆化層902の形成により半導体膜908をボンド基板900から剥離するスマートカット法を用いる場合について示すが、ELTRAN(Epitaxial Layer Transfer)、誘電体分離法、PACE(Plasma Assisted Chemical Etching)法などの、他の貼り合わせ法を用いて半導体膜908をベース基板904に貼り合わせるようにも良い。

30

【0210】

次に、図19(B)に示すように、半導体膜908を所望の形状に加工(パターニング)することで、島状の半導体膜909を形成する。

【0211】

上記工程を経て形成された半導体膜909を用い、トランジスタ等の各種半導体素子を形成することができる。図19(C)には、半導体膜909を用いて形成されたトランジスタ910を例示している。

40

【0212】

上述した作製方法を用いることで、上記実施の形態の半導体表示装置が有する半導体素子を作製することができる。

【0213】

本実施例は、上記実施の形態と適宜組み合わせて実施することができる。

【実施例2】

【0214】

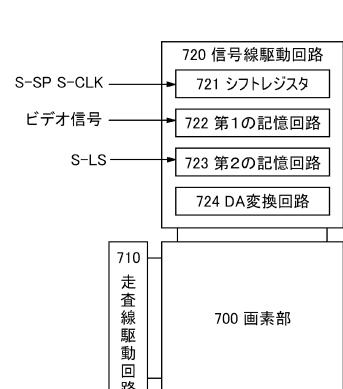

本実施例では、半導体表示装置の全体的な構成について説明する。図20(A)に、本実施例の半導体表示装置のブロック図を、一例として示す。

【0215】

図20(A)に示す半導体表示装置は、発光素子を備えた画素部(表示

50

領域 ) 700 と、各画素をラインごとに選択する走査線駆動回路 710 と、選択されたラインの画素へのビデオ信号の入力を制御する信号線駆動回路 720 とを有する。

【 0216 】

図 20 ( A )において信号線駆動回路 720 は、シフトレジスタ 721、第 1 の記憶回路 722、第 2 の記憶回路 723、D / A ( D i g i t a l to A n a l o g ) 変換回路 724 を有している。シフトレジスタ 721 には、クロック信号 S - C L K、スタートパルス信号 S - S P が入力される。シフトレジスタ 721 は、これらクロック信号 S - C L K 及びスタートパルス信号 S - S P に従って、パルスが順次シフトするタイミング信号を生成し、第 1 の記憶回路 722 に出力する。タイミング信号のパルスの出現する順序は、走査方向切り替え信号に従って切り替えるようにしても良い。

10

【 0217 】

第 1 の記憶回路 722 にタイミング信号が入力されると、該タイミング信号のパルスに従って、ビデオ信号が順に第 1 の記憶回路 722 に書き込まれ、保持される。なお、第 1 の記憶回路 722 が有する複数の記憶素子に順にビデオ信号を書き込んでも良いが、第 1 の記憶回路 722 が有する複数の記憶素子をいくつかのグループに分け、該グループごとに並行してビデオ信号を入力する、いわゆる分割駆動を行っても良い。なおこのときのグループ数を分割数と呼ぶ。例えば 4 つずつ記憶素子をグループに分けた場合、4 分割で分割駆動することになる。

【 0218 】

第 1 の記憶回路 722 の全ての記憶素子への、ビデオ信号の書き込みが一通り終了するまでの時間を、ライン期間と呼ぶ。実際には、上記ライン期間に水平帰線期間が加えられた期間をライン期間に含むことがある。

20

【 0219 】

1 ライン期間が終了すると、第 2 の記憶回路 723 に入力される信号 S - L S のパルスに従って、第 1 の記憶回路 722 に保持されているビデオ信号が、第 2 の記憶回路 723 に一斉に書き込まれ、保持される。ビデオ信号を第 2 の記憶回路 723 に送出し終えた第 1 の記憶回路 722 には、再びシフトレジスタ 721 からのタイミング信号に従って、次のビデオ信号の書き込みが順次行われる。この 2 順目の 1 ライン期間中には、第 2 の記憶回路 723 に書き込まれ、保持されているビデオ信号が、D / A 変換回路 724 に入力される。

30

【 0220 】

そして D / A 変換回路 724 は、入力されたデジタルのビデオ信号をアナログのビデオ信号に変換し、信号線を介して画素部 700 内の各画素に入力する。

【 0221 】

なお、D / A 変換回路 724 を設けずに、ビデオ信号をデジタルのまま画素部 700 に入力しても良い。

【 0222 】

また、信号線駆動回路 720 は、シフトレジスタ 721 の代わりに、パルスが順次シフトする信号を出力することができる別の回路を用いても良い。

【 0223 】

また図 20 ( A )では、D / A 変換回路 724 の後段に画素部 700 が直接接続されているが、本発明はこの構成に限定されない。画素部 700 の前段に、D / A 変換回路 724 から出力されたビデオ信号に信号処理を施す回路を設けることができる。信号処理を施す回路の一例として、例えば波形を整形することができるバッファなどが挙げられる。

40

【 0224 】

次に、走査線駆動回路 710 の動作について説明する。走査線駆動回路 710 は選択信号を生成し、該選択信号を複数の各走査線に入力することで、画素をラインごとに選択する。選択信号により画素が選択されると、走査線の一つにゲートが接続されたトランジスタがオンになり、画素へのビデオ信号の入力が行われる。

【 0225 】

50

なお、本実施例では複数の走査線に入力される選択信号を、全て一の走査線駆動回路 710 で生成している例について述べたが、本発明はこの構成に限定されない。複数の走査線駆動回路 710 で複数の走査線に入力される選択信号の生成を行うようにしても良い。

【0226】

また、各画素に走査線が複数設けられている場合、各走査線に対応する走査線駆動回路を複数設けるようにしても良い。

【0227】

なお、画素部 700、走査線駆動回路 710、信号線駆動回路 720 は、同じ基板に形成することができるが、いずれかを異なる基板で形成することもできる。

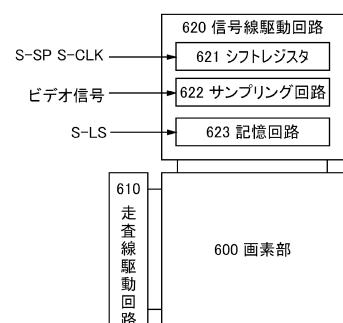

【0228】

次に、図 20 (A) とは異なる半導体表示装置のブロック図を、図 20 (B) に一例として示す。図 20 (B) に示す半導体表示装置は、複数の画素を有する画素部 (表示領域) 600 と、複数の画素をラインごとに選択することができる走査線駆動回路 610 と、選択されたライン内の画素へのビデオ信号の入力を制御する信号線駆動回路 620 とを有する。

【0229】

信号線駆動回路 620 は、シフトレジスタ 621 と、サンプリング回路 622 と、アナログ信号を記憶することができる記憶回路 623 とを少なくとも有する。シフトレジスタ 621 にクロック信号 S-CLK と、スタートパルス信号 S-SP が入力される。シフトレジスタ 621 はこれらクロック信号 S-CLK 及びスタートパルス信号 S-SP に従って、パルスが順次シフトするタイミング信号を生成し、サンプリング回路 622 に入力する。サンプリング回路 622 では、入力されたタイミング信号に従って、信号線駆動回路 620 に入力された 1 ライン期間分のアナログのビデオ信号をサンプリングする。そして 1 ライン期間分のビデオ信号が全てサンプリングされると、サンプリングされたビデオ信号は信号 S-LS に従って一斉に記憶回路 623 に出力され、保持される。記憶回路 623 に保持されるビデオ信号は、信号線を介して画素部 600 に入力される。

【0230】

なお本実施例では、サンプリング回路 622 において 1 ライン期間分のビデオ信号を全てサンプリングした後に、一斉に下段の記憶回路 623 にサンプリングされたビデオ信号を入力する場合を例に挙げて説明するが、本発明はこの構成に限定されない。サンプリング回路 622 において各画素に対応するビデオ信号をサンプリングしたら、1 ライン期間を待たずに、その都度下段の記憶回路 623 にサンプリングされたビデオ信号を入力しても良い。

【0231】

またビデオ信号のサンプリングは対応する画素毎に順に行っても良いし、1 ライン内の画素をいくつかのグループに分け、各グループに対応する画素ごとに並行して行っても良い。

【0232】

なお図 20 (B) では記憶回路 623 の後段に直接画素部 600 が接続されているが、本発明はこの構成に限定されない。画素部 600 の前段に、記憶回路 623 から出力されたアナログのビデオ信号に信号処理を施す回路を設けることができる。信号処理を施す回路の一例として、例えば波形を整形することができるバッファなどが挙げられる。

【0233】

そして、記憶回路 623 から画素部 600 にビデオ信号が入力されるのと並行して、サンプリング回路 622 は次のライン期間に対応するビデオ信号を再びサンプリングすることができる。

【0234】

次に、走査線駆動回路 610 の動作について説明する。走査線駆動回路 610 は選択信号を生成し、該選択信号を複数の各走査線に入力することで、画素をラインごとに選択する。選択信号により画素が選択されると、走査線の一つにゲートが接続されたトランジスタ

10

20

30

40

50

がオンになり、画素へのビデオ信号の入力が行われる。

【0235】

なお、本実施例では複数の走査線に入力される選択信号を、全て一の走査線駆動回路610で生成している例について述べたが、本発明はこの構成に限定されない。複数の走査線駆動回路610で複数の走査線に入力される選択信号の生成を行うようにしても良い。

【0236】

また、各画素に走査線が複数設けられている場合、各走査線に対応する走査線駆動回路を複数設けるようにしても良い。

【0237】

なお、画素部600、走査線駆動回路610、信号線駆動回路620は、同じ基板に形成することができるが、いずれかを異なる基板で形成することもできる。 10

【0238】

本実施例は、上記実施の形態または実施例と適宜組み合わせて実施することが可能である。

【実施例3】

【0239】

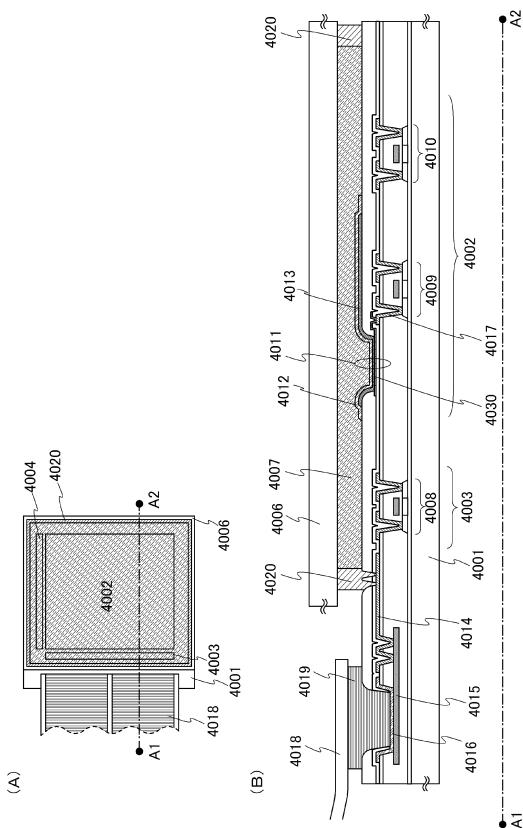

本実施例では、半導体表示装置の外観について、図21を用いて説明する。図21(A)は、第1の基板上に形成されたトランジスタ及び発光素子を、第1の基板と第2の基板の間にシール材で封止したパネルの上面図であり、図21(B)は、図21(A)のA1-A2における断面図に相当する。 20

【0240】

第1の基板4001上に設けられた画素部(表示領域)4002と、信号線駆動回路4003と、走査線駆動回路4004とを囲むように、シール材4020が設けられている。また画素部4002、信号線駆動回路4003及び走査線駆動回路4004の上に、第2の基板4006が設けられている。よって画素部4002、信号線駆動回路4003、走査線駆動回路4004は、第1の基板4001と第2の基板4006の間において、シール材4020により、充填材4007と共に密封されている。

【0241】

また第1の基板4001上に設けられた画素部4002、信号線駆動回路4003、走査線駆動回路4004は、それぞれトランジスタを複数有している。図21(B)では、信号線駆動回路4003に含まれるトランジスタ4008と、画素部4002に含まれるトランジスタ4009、トランジスタ4010とを例示している。 30

【0242】

また発光素子4011は、配線4017を介してトランジスタ4009のソース領域またはドレイン領域に電気的に接続されている画素電極4030と、電界発光層4013と、共通電極4012とを有している。なお発光素子4011の構成は、本実施例に示した構成に限定されない。発光素子4011から取り出す光の方向や、トランジスタ4009の極性などに合わせて、発光素子4011の構成は適宜変えることができる。

【0243】

また信号線駆動回路4003、走査線駆動回路4004または画素部4002に与えられる各種信号及び電圧は、図21(B)に示す断面図では図示されていないが、引き出し配線4014及び4015を介して、接続端子4016から供給されている。 40

【0244】

本実施例では、接続端子4016が、発光素子4011が有する共通電極4012と同じ導電膜から形成されている。また、引き出し配線4014は、配線4017と同じ導電膜から形成されている。また引き出し配線4015は、トランジスタ4009、トランジスタ4010、トランジスタ4008がそれぞれ有するゲート電極と、同じ導電膜から形成されている。

【0245】

接続端子4016は、FPC4018が有する端子と、異方性導電膜4019を介して電 50

気的に接続されている。

【0246】

なお、第1の基板4001、第2の基板4006として、ガラス、金属（代表的にはステンレス）、セラミックス、プラスチックを用いることができる。但し、発光素子4011からの光の取り出し方向に位置する第2の基板4006は、透光性を有していなければならない。よって第2の基板4006は、ガラス板、プラスチック板、ポリエステルフィルムまたはアクリルフィルムのような透光性を有する材料を用いることが望ましい。

【0247】

また、充填材4007としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂または熱硬化樹脂を用いることができる。本実施例では充填材4007として窒素を用いる例を示している。

10

【0248】

本実施例は、上記実施の形態または実施例と適宜組み合わせて実施することが可能である。

【実施例4】

【0249】

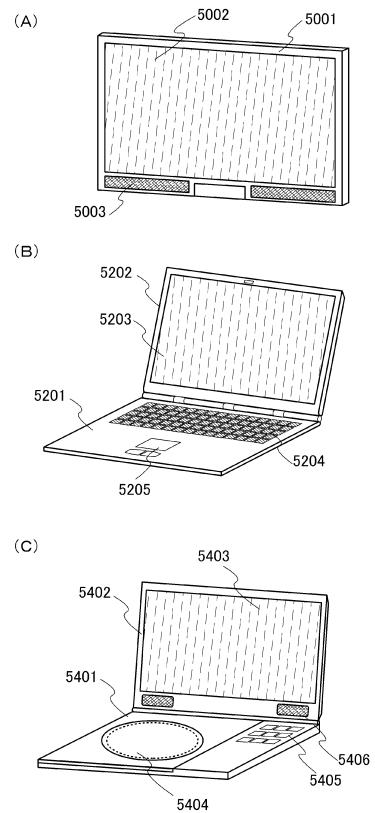

上記実施の形態及び実施例で示した半導体表示装置を用いることで、大型の表示領域を有する高画質な表示装置を提供することができる。よって、上記実施の形態及び実施例で示した半導体表示装置は、表示装置、ノート型パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、上記実施の形態及び実施例で示した半導体表示装置を用いることができる電子機器として、携帯電話、携帯型ゲーム機または電子書籍、ビデオカメラ、デジタルスチルカメラなどのカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、などが挙げられる。これら電子機器の具体例を図22に示す。

20

【0250】

図22（A）は表示装置であり、筐体5001、表示部5002、スピーカー部5003等を含む。上記実施の形態及び実施例で示した半導体表示装置は、表示部5002に用いることができる。なお、表示装置には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

30

【0251】

図22（B）はノート型パーソナルコンピュータであり、本体5201、筐体5202、表示部5203、キーボード5204、マウス5205等を含む。上記実施の形態及び実施例で示した半導体表示装置は、表示部5203に用いることができる。

【0252】

図22（C）は記録媒体を備えた携帯型の画像再生装置（具体的にはDVD再生装置）であり、本体5401、筐体5402、表示部5403、記録媒体（DVD等）読み込み部5404、操作キー5405、スピーカー部5406等を含む。記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。上記実施の形態及び実施例で示した半導体表示装置は、表示部5403に用いることができる。

40

【0253】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。

【0254】

本実施例は、上記実施の形態または上記実施例と適宜組み合わせて実施することができる。

【符号の説明】

【0255】

|         |               |    |

|---------|---------------|----|

| 1 0 1   | 信号線           |    |

| 1 0 2   | 電源線           |    |

| 1 0 3   | 走査線           |    |

| 1 0 4   | 補助電源線         |    |

| 1 0 5   | 発光素子          |    |

| 1 0 6   | スイッチング用トランジスタ |    |

| 1 0 7   | 駆動用トランジスタ     |    |

| 1 0 8   | ゲート電極         |    |

| 1 0 9   | 補助配線          |    |

| 1 1 0   | 走査線用補助配線      | 10 |

| 1 1 1   | 層間絶縁膜         |    |

| 2 0 0   | 画素            |    |

| 2 0 1   | スイッチング用トランジスタ |    |

| 2 0 2   | 駆動用トランジスタ     |    |

| 2 0 3   | 発光素子          |    |

| 2 0 4   | 保持容量          |    |

| 2 0 5   | 補助電源線         |    |

| 3 0 0   | 画素            |    |

| 3 0 1   | 信号線           |    |

| 3 0 2 a | 電源線           | 20 |

| 3 0 2 b | 電源線           |    |

| 3 0 2 c | 電源線           |    |

| 3 0 3   | 走査線           |    |

| 3 0 4   | 補助電源線         |    |

| 3 0 4 a | 補助電源線         |    |

| 3 0 4 b | 補助電源線         |    |

| 3 0 4 c | 補助電源線         |    |

| 3 0 8   | ゲート電極         |    |

| 3 0 9 a | 補助配線          |    |

| 3 0 9 b | 補助配線          | 30 |

| 3 0 9 c | 補助配線          |    |

| 3 1 0   | 走査線用補助配線      |    |

【図1】

【図2】

【図3】

【図4】

【 义 5 】

【 図 6 】

【 四 7 】

【 四 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

(B)

(C)

【図20】

(B)

## 【図21】

## 【図22】

---

フロントページの続き

(72)発明者 高橋 圭

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

合議体

審判長 森 竜介

審判官 伊藤 昌哉

審判官 松川 直樹

(56)参考文献 特開2006-18085 (JP, A)

特開2006-261109 (JP, A)

特開2006-310799 (JP, A)

特開2006-113571 (JP, A)

特開2004-6332 (JP, A)

特開2007-43114 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F1/1343-1/1345, 1/135-1/1368

G09F9/00-9/46

G09G3/00-3/08, 3/12-3/16, 3/19-3/26, 3/30-3/34, 3/38

H01L21/33, 27/32, 29/786, 51/50

H05B33/00-33/28