(19)日本国特許庁(JP)

**(12)特許公報(B2)**(11)特許番号

特許第7062430号

(P7062430)

(45)発行日 令和4年5月6日(2022.5.6)

(24)登録日 令和4年4月22日(2022.4.22)

(51)国際特許分類

H 0 4 N 5/3745(2011.01)

F I

H 0 4 N

5/3745 5 0 0

請求項の数 27 (全27頁)

(21)出願番号 特願2017-241119(P2017-241119)

(22)出願日 平成29年12月15日(2017.12.15)

(65)公開番号 特開2019-110406(P2019-110406)

A)

(43)公開日 令和1年7月4日(2019.7.4)

審査請求日 令和2年12月1日(2020.12.1)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281

特許業務法人大塚国際特許事務所

池戸 秀樹

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 審査官

大室 秀明

最終頁に続く

(54)【発明の名称】 撮像素子、撮像装置および画像処理方法

**(57)【特許請求の範囲】****【請求項1】**

予め決められた露光期間に入射したフォトンを検出して数を計数し、第1の計数値を出力する複数の画素と、

前記露光期間と前記第1の計数値とに基づいて、単位時間あたりの第2の計数値を求める算出手段と、

前記第2の計数値に基づいて補正係数を取得し、前記第1の計数値に対して、前記検出の誤差を、前記補正係数により補正するとともに、暗電流成分を補正する補正手段と、を有し、

前記補正手段は、前記第2の計数値が第1の値である場合に、該第1の値より小さい第2の値である場合よりも、大きい補正係数を取得することを特徴とする撮像素子。

**【請求項2】**

予め決められた露光期間に入射したフォトンを検出して数を計数し、第1の計数値を出力する複数の画素と、

測光手段から得られた測光結果と前記第1の計数値とに基づいて補正係数を取得し、前記第1の計数値に対して、前記検出の誤差を、前記補正係数により補正する補正手段と、を有し、

前記測光結果による輝度値が第1の輝度値である場合に、該第1の輝度値よりも小さい第2の輝度値である場合よりも、大きい補正係数を取得することを特徴とする撮像素子。

**【請求項3】**

前記複数の画素は、それぞれ、フォトンを検出する検出手段と、該検出したフォトンの数を計数して計数値を出力する計数手段と、前記計数値を保持する記憶手段とを有し、前記記憶手段に保持した計数値を前記第1の計数値として出力することを特徴とする請求項1または2に記載の撮像素子。

【請求項4】

予め決められた数の連続する前記露光期間について、前記露光期間ごとに出力され、前記補正手段により補正された前記第1の計数値を、前記複数の画素それぞれについて加算する加算手段を更に有し、

前記計数手段は、前記記憶手段に前記計数値が保持される度に、前記計数値を0にリセットすることを特徴とする請求項3に記載の撮像素子。

10

【請求項5】

各画素が、フォトンを検出する検出手段と、該検出したフォトンの数を計数して計数値を出力する計数手段と、前記計数値を保持する記憶手段とを有し、予め決められた露光期間ごとに、前記記憶手段に保持した計数値を第1の計数値として出力する複数の画素と、前記露光期間と、連続して出力された前記第1の計数値の差分値とに基づいて、単位時間あたりの第2の計数値を求める算出手段と、

前記第2の計数値に基づいて補正係数を取得し、前記差分値に対して、前記検出の誤差を、前記補正係数により補正する補正手段と、を有し、

前記補正手段は、前記第2の計数値が第1の値である場合に、該第1の値より小さい第2の値である場合よりも、大きい補正係数を取得することを特徴とする撮像素子。

20

【請求項6】

予め決められた数の連続する前記露光期間について、前記補正手段により補正された前記差分値を、前記複数の画素それぞれについて加算する加算手段を更に有し、

前記計数手段は、前記予め決められた数の連続する露光期間が経過する度に、前記計数値を0にリセットすることを特徴とする請求項5に記載の撮像素子。

【請求項7】

前記検出手段は、アバランシェフォトダイオードと、該アバランシェフォトダイオードに逆バイアス電圧をかけるためのクエンチ抵抗とを含むことを特徴とする請求項3乃至6のいずれか1項に記載の撮像素子。

30

【請求項8】

前記検出手段は、アバランシェフォトダイオードと、該アバランシェフォトダイオードに逆バイアス電圧をかけるためのMOSトランジスタとを含むことを特徴とする請求項3乃至6のいずれか1項に記載の撮像素子。

【請求項9】

前記撮像素子は積層構造を有し、前記検出手段と前記計数手段を異なる層に構成したことを特徴とする請求項3乃至8のいずれか1項に記載の撮像素子。

【請求項10】

前記補正係数は、前記検出の誤差が無い場合の理想値の前記単位時間あたりの値と、前記第2の計数値との誤差に基づいた値であることを特徴とする請求項1または5に記載の撮像素子。

40

【請求項11】

前記単位時間あたりの計数値に対応した補正係数を記憶した記憶手段を更に有し、前記補正手段は、前記記憶手段から、前記第2の計数値に対応した補正係数を選択することを特徴とする請求項1または5に記載の撮像素子。

【請求項12】

前記補正手段は、前記単位時間あたりの計数値に対応した補正係数を求めるための近似関数を用いて、前記第2の計数値に対応した補正係数を取得することを特徴とする請求項1または5に記載の撮像素子。

【請求項13】

前記複数の画素の一部は、遮光されたOB画素であって、

50

前記補正手段は、前記遮光されていない画素から出力され、前記検出の誤差を補正された前記第1の計数値の暗電流成分を前記OB画素の出力を用いて補正することを特徴とする請求項1または5に記載の撮像素子。

【請求項14】

前記補正手段は、補正する画素とその周囲の画素の前記第2の計数値の平均に基づいて、第2の補正係数を求め、前記OB画素から出力され、前記補正手段により前記検出の誤差を補正された前記第1の計数値の平均値を前記第2の補正係数により補正した値により、前記検出の誤差を補正された前記第1の計数値の暗電流成分を補正することを特徴とする請求項13に記載の撮像素子。

【請求項15】

前記補正手段は、予め決められた数の連続する前記露光期間に対して得られた、補正する画素の複数の前記第2の計数値の平均に基づいて、第2の補正係数を求め、前記OB画素から出力され、前記補正手段により前記検出の誤差を補正された前記第1の計数値の平均値を前記第2の補正係数により補正した値により、前記検出の誤差を補正された前記第1の計数値の暗電流成分を補正することを特徴とする請求項13に記載の撮像素子。

10

【請求項16】

予め決められた露光期間に入射したフォトンを検出して数を計数し、第1の計数値を出力する複数の画素を有する撮像素子と、

前記露光期間と前記第1の計数値とに基づいて、単位時間あたりの第2の計数値を求める算出手段と、

20

前記第2の計数値に基づいて補正係数を取得し、前記第1の計数値に対して、前記検出の誤差を、前記補正係数により補正するとともに、暗電流成分を補正する補正手段と、を有し、

前記補正手段は、前記第2の計数値が第1の値である場合に、該第1の値より小さい第2の値である場合よりも、大きい補正係数を取得することを特徴とする撮像装置。

【請求項17】

予め決められた露光期間に入射したフォトンを検出して数を計数し、第1の計数値を出力する複数の画素を有する撮像素子と、

測光手段と、

前記測光手段から得られた測光結果と前記第1の計数値とに基づいて補正係数を取得し、前記第1の計数値に対して、前記検出の誤差を、前記補正係数により補正する補正手段と、を有し、

30

前記補正手段は、前記測光結果による輝度値が第1の輝度値である場合に、該第1の輝度値よりも小さい第2の輝度値である場合よりも、大きい補正係数を取得することを特徴とする撮像装置。

【請求項18】

前記複数の画素は、それぞれ、フォトンを検出する検出手段と、該検出したフォトンの数を計数して計数値を出力する計数手段と、前記計数値を保持する記憶手段とを有し、前記記憶手段に保持した計数値を前記第1の計数値として出力し、

予め決められた数の連続する前記露光期間について、前記露光期間ごとに出力され、前記補正手段により補正された前記第1の計数値を、前記複数の画素それぞれについて加算する加算手段を更に有し、

40

前記計数手段は、前記記憶手段に前記計数値が保持される度に、前記計数値を0にリセットすることを特徴とする請求項16または17に記載の撮像装置。

【請求項19】

各画素が、フォトンを検出する検出手段と、該検出したフォトンの数を計数して計数値を出力する計数手段と、前記計数値を保持する記憶手段とを有し、予め決められた露光期間ごとに、前記記憶手段に保持した計数値を第1の計数値として出力する複数の画素を有する撮像素子と、

前記露光期間と、連続して出力された前記第1の計数値の差分値とに基づいて、単位時間

50

あたりの第2の計数値を求める算出手段と、

前記第2の計数値に基づいて補正係数を取得し、前記差分値に対して、前記検出の誤差を、前記補正係数により補正する補正手段と、を有し、

前記補正手段は、前記第2の計数値が第1の値である場合に、該第1の値より小さい第2の値である場合よりも、大きい補正係数を取得することを特徴とする撮像装置。

【請求項20】

前記複数の画素の一部は、遮光されたOB画素であって、

前記補正手段は、前記遮光されていない画素から出力され、前記検出の誤差を補正された前記第1の計数値の暗電流成分を前記OB画素の出力を用いて補正する黒レベル補正手段を更に有することを特徴とする請求項1\_6に記載の撮像装置。

10

【請求項21】

算出手段が、予め決められた露光期間に入射したフォトンを検出して数を計数した計数値を出力する複数の画素を有する像素子から得られた第1の計数値と前記露光期間とに基づいて、単位時間あたりの第2の計数値を求める算出工程と、

補正手段が、前記第2の計数値に基づいて補正係数を取得し、前記第1の計数値に対して、前記検出の誤差を、前記補正係数により補正するとともに、暗電流成分を補正する補正工程と、を有し、

前記補正工程では、前記第2の計数値が第1の値である場合に、該第1の値より小さい第2の値である場合よりも、大きい補正係数を取得することを特徴とする画像処理方法。

【請求項22】

補正手段が、予め決められた露光期間に入射したフォトンを検出して数を計数した計数値を出力する複数の画素を有する像素子から得られた第1の計数値と、測光手段から得られた測光結果とに基づいて補正係数を取得し、前記第1の計数値に対して、前記検出の誤差を、前記補正係数により補正する補正工程を有し、

前記補正工程では、前記測光結果による輝度値が第1の輝度値である場合に、該第1の輝度値よりも小さい第2の輝度値である場合よりも、大きい補正係数を取得することを特徴とする画像処理方法。

20

【請求項23】

前記複数の画素は、それぞれ、フォトンを検出する検出手段と、該検出したフォトンの数を計数して計数値を出力する計数手段と、前記計数値を保持する記憶手段とを有し、前記記憶手段に保持した計数値を前記第1の計数値として出力し、

加算手段が、予め決められた数の連続する前記露光期間について、前記露光期間ごとに出力され、前記補正工程で補正された前記第1の計数値を、前記複数の画素それぞれについて加算する加算工程を更に有し、

前記計数手段は、前記記憶手段に前記計数値が保持される度に、前記計数値を0にリセットすることを特徴とする請求項2\_1または2\_2に記載の画像処理方法。

30

【請求項24】

算出手段が、各画素が、フォトンを検出する検出手段と、該検出したフォトンの数を計数して計数値を出力する計数手段と、前記計数値を保持する記憶手段とを有し、予め決められた露光期間ごとに、前記記憶手段に保持した計数値を出力する複数の画素を有する像素子から連続して得られた、第1の計数値の差分値と、前記露光期間とに基づいて、単位時間あたりの第2の計数値を求める算出工程と、

補正手段が、前記第2の計数値に基づいて補正係数を取得し、前記差分値に対して、前記検出の誤差を、前記補正係数により補正する補正工程と、を有し、

前記補正工程では、前記第2の計数値が第1の値である場合に、該第1の値より小さい第2の値である場合よりも、大きい補正係数を取得することを特徴とする画像処理方法。

40

【請求項25】

前記複数の画素の一部は、遮光されたOB画素であって、

前記補正工程では、遮光されていない画素から出力され、前記検出の誤差を補正された前記第1の計数値の暗電流成分を前記OB画素の出力を用いて補正することを特徴とする請

50

求項 2\_1 に記載の画像処理方法。

【請求項 2\_6】

コンピュータに、請求項 2\_1 乃至 2\_5 のいずれか 1 項に記載の画像処理方法の各工程を実行させるためのプログラム。

【請求項 2\_7】

請求項 2\_6 に記載のプログラムを記憶したコンピュータが読み取り可能な記憶媒体。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像素子、撮像装置および画像処理方法に関し、特に、入射したフォトンの数を計数して計数値を出力する撮像素子、撮像装置および画像処理方法に関するものである。 10

【背景技術】

【0002】

従来から撮像装置には、CCD や CMOS イメージセンサが広く用いられていた。これらのイメージセンサでは、露光期間中に入射した光をフォトダイオードにおいて電荷に変換して蓄積し、その電荷を電流あるいは電圧のアナログ信号として取り出し、デジタル信号に変換する方法が一般的であった。

【0003】

ところで、近年、露光期間中にフォトダイオードに入射したフォトンの数を計数し、その計数値を信号値として出力するフォトンカウンティング方式のイメージセンサが提案されている。フォトンカウンティング方式を実現する手段として、例えば、アバランシェフォトダイオードと、カウンター回路を用いる方法がある。アバランシェフォトダイオードに、降伏電圧より大きな逆バイアス電圧を印加すると、フォトンの入射による生成キャリアがアバランシェ増倍を起こし、大電流が発生する。この電流をもとに生成したパルス信号をカウンター回路で計数することで、アバランシェフォトダイオードに入射したフォトンの数に応じた信号値を得ることができる。 20

【0004】

フォトンカウンティング方式のイメージセンサは、フォトダイオードに入射したフォトンの数をそのまま信号値として扱う。このことから、CCD や CMOS イメージセンサと比較して、回路ノイズによる信号への影響が少なく、微弱な光環境においても画像を鮮明にとらえることが可能である。 30

【0005】

しかしながら、フォトンカウンティング方式のイメージセンサでは、単位時間あたりの受光量が増加すると、パルス信号のパルス幅よりも短い周期でフォトンが入射するようになり、複数のパルス信号が結合してしまうことがある。そのため、カウンター回路で計数した計数値が本来のフォトンの数よりも低下してしまい、受光量に対して線形な信号値が得られなくなってしまう。すなわち、リニアリティ特性が悪化してしまう。その結果、撮影画像の画質が劣化してしまう。

【0006】

そこで、特許文献 1 には、フォトンカウンティング方式の光検出器において、計数値の低下を抑えるために、パルス信号のパルス幅を累積加算した出力値を求める累積手段を備えた構成が開示されている。この構成によれば、受光量に対して単調に増加する信号を得ることができる。 40

【0007】

また、特許文献 2 には、CMOS イメージセンサにおいて、電荷の不完全転送によって生じるリニアリティ特性の悪化を、露光量（すなわち、露光期間中に受光した光量）に応じたゲイン補正値およびオフセット補正値を用いて補正する方法が開示されている。

【先行技術文献】

【特許文献】

【0008】

50

20

30

40

50

【文献】特開2014-81253号公報

特許第5917160号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、特許文献1に記載の構成では、例えば、1つのアバランシェフォトダイオードに複数のフォトンが同時に入射した場合には正しい信号値を得ることができなかった。そのため、受光量に対する線形性は不十分である。

【0010】

また、特許文献2に記載の補正方法では、露光量に応じてゲイン補正值およびオフセット補正值を変更している。しかしながら、フォトンカウンティング方式のイメージセンサにおいては、露光量が同じであっても、高照度（単位時間あたりの受光量が多い）環境下で短秒撮影した場合と低照度（単位時間あたりの受光量が少ない）環境化で長秒撮影した場合とでは、前者の方が計数値の低下が大きくなる。したがって、露光量に応じて補正值を変更するだけでは不十分であり、低照度環境化では、過補正になり、かえって画質を劣化させてしまう場合もある。

10

【0011】

本発明は上記問題点を鑑みてなされたものであり、入射したフォトンの数を計数して信号値として出力する撮像装置において、単位時間あたりの受光量の違いによって生じる画質劣化を抑制することを目的とする。

20

【課題を解決するための手段】

【0012】

上記目的を達成するために本発明の撮像素子は、予め決められた露光期間に入射したフォトンを検出して数を計数し、第1の計数値を出力する複数の画素と、前記露光期間と前記第1の計数値とに基づいて、単位時間あたりの第2の計数値を求める算出手段と、前記第2の計数値に基づいて補正係数を取得し、前記第1の計数値に対して、前記検出の誤差を、前記補正係数により補正するとともに、暗電流成分を補正する補正手段と、を有し、前記補正手段は、前記第2の計数値が第1の値である場合に、該第1の値より小さい第2の値である場合よりも、大きい補正係数を取得する。

【発明の効果】

30

【0013】

本発明によれば、入射したフォトンの数を計数して信号値として出力する撮像装置において、単位時間あたりの受光量の違いによって生じる画質劣化を抑制することができる。

【図面の簡単な説明】

【0014】

【図1】本発明の第1の実施形態における撮像装置の全体構成を示すブロック図。

【図2】第1の実施形態における撮像素子の構成を示す図。

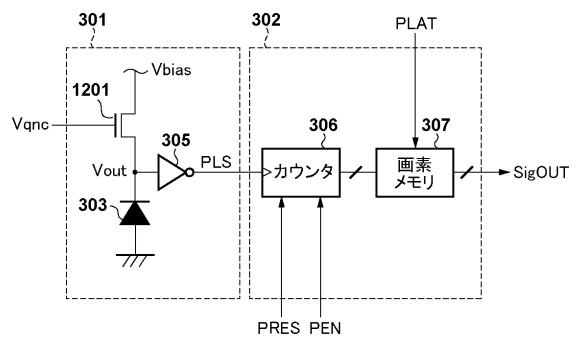

【図3】第1の実施形態における単位画素の構成の一例を示す回路図。

【図4】第1の実施形態における受光部の動作を説明する図。

【図5】第1の実施形態における画素領域の構成を示す概略図。

40

【図6】第1の実施形態における撮像素子のチップレイアウトの一例を示す概略図。

【図7】第1の実施形態における1フレームの画像を取得する際の撮像装置の駆動タイミングチャート。

【図8】第1の実施形態における補正部の構成を示すブロック図。

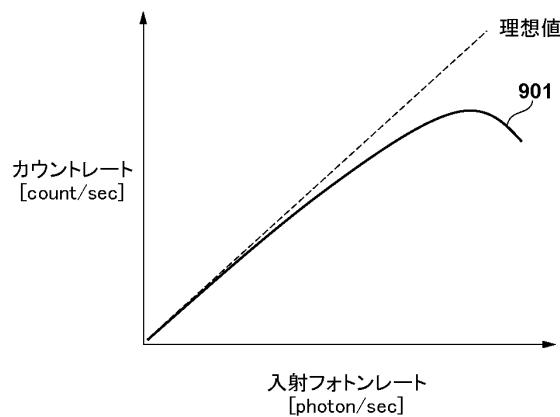

【図9】入射フォトンレートに対するカウントレートの関係を示す図。

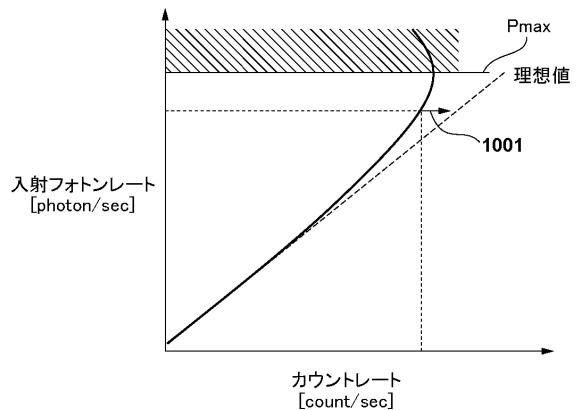

【図10】カウントレートに対する入射フォトンレートの関係を示す図。

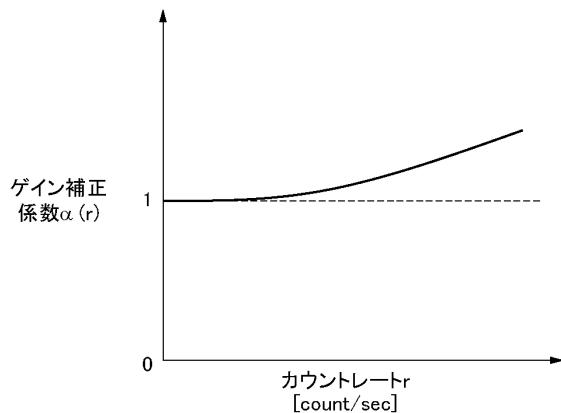

【図11】第1の実施形態におけるゲイン補正係数の一例を示す図。

【図12】第1の実施形態の変形例における単位画素の構成の一例を示す回路図。

【図13】第2の実施形態における補正部の構成を示すブロック図。

【図14】第2の実施形態におけるゲイン補正係数の一例を示す図。

50

【図15】第2の実施形態における撮影処理のフローチャート。

【図16】第3の実施形態における補正部の構成を示すブロック図。

【図17】第3の実施形態におけるオフセット補正方法を説明する図。

【図18】第4の実施形態における補正部の構成を示すブロック図。

【図19】第4の実施形態におけるオフセット補正方法を説明する図。

【図20】第5の実施形態における撮像素子の構成を示す図。

【図21】第5の実施形態における撮像素子のチップレイアウトの一例を示す概略図。

【図22】第5の実施形態における1フレームの画像を取得する際の撮像装置の駆動タイミングチャート。

【図23】第6の実施形態における信号処理ブロックの構成を示すブロック図。

10

【図24】第6の実施形態における1フレームの画像を取得する際の撮像装置の駆動タイミングチャート。

【発明を実施するための形態】

【0015】

以下、添付図面を参照して本発明を実施するための形態を詳細に説明する。

【0016】

<第1の実施形態>

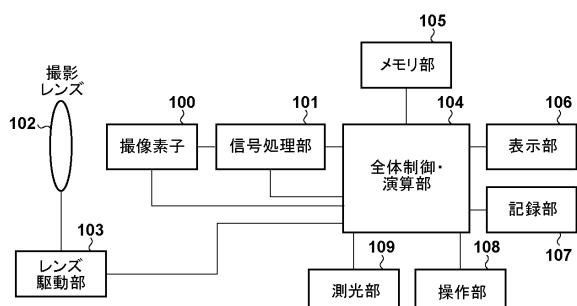

本発明における第1の実施形態について説明する。図1は、第1の実施形態における撮像装置の全体構成を示すブロック図である。図1において、撮影レンズ102は、レンズ駆動部103によって駆動され、ズーム制御、フォーカス制御、絞り制御などが行われて、被写体の光学像を撮像素子100に結像させる。

20

【0017】

撮像素子100は、入射したフォトンの数を計数して信号値として出力可能な構成を有し、撮影レンズ102により結像された被写体の光学像を入射光として取り込んで、画像信号を出力する。なお、撮像素子100の構成については、詳細に後述する。信号処理部101は、撮像素子100より出力される画像信号に対して、並べ替えを含む各種の信号処理を行う。全体制御・演算部104は、各種演算処理と撮像装置全体の制御を行う。

【0018】

メモリ部105は、画像データを一時的に記憶するために用いられ、表示部106は、各種情報や撮影画像を表示する。記録部107は、半導体メモリ等を着脱可能な構成を有し、画像データの記録または読み出しを行う。操作部108は、ボタン、ダイヤルなどで構成され、ユーザーからの操作入力を受け付ける。なお、表示部106がタッチパネルである場合には、当該タッチパネルも操作部108に含まれる。測光部109は、不図示のCCDやCMOSなどの測光用の撮像素子を備え、撮影レンズ102を通して入射した光を不図示の可動式ミラー等を介して受光し、複数の測光エリア毎に被写体輝度を測定する。

30

【0019】

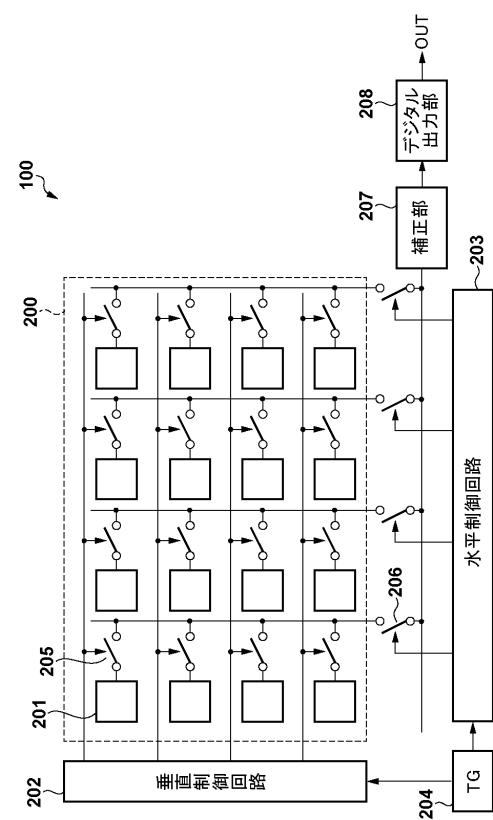

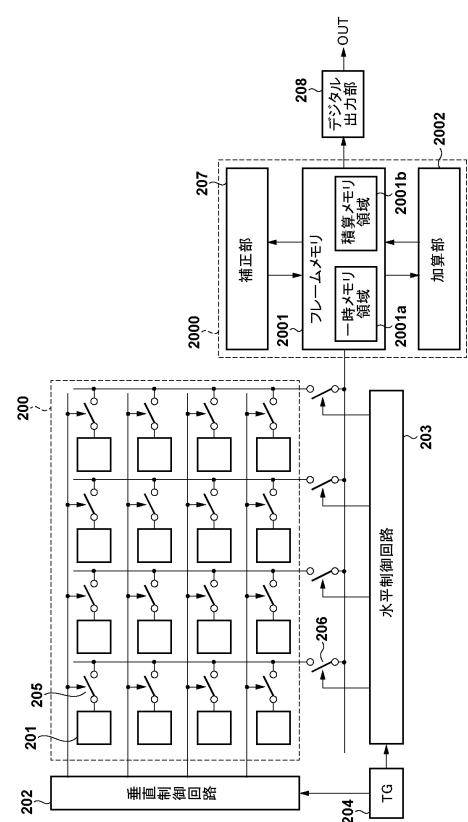

図2は、撮像素子100の全体構成を示す図である。撮像素子100は、画素領域200、垂直制御回路202、水平制御回路203、タイミングジェネレータ(TG)204、補正部207、デジタル出力部208を含んで構成される。

【0020】

画素領域200には、後述するように、アバランシェフォトダイオードとカウンター回路とを有する単位画素201が行列状に配置されている。ここでは、説明を簡単にするために $4 \times 4$ 画素の配列を示してあるが、実用上はさらに多数の画素が配置される。単位画素201は、入射したフォトンの数を計数してデジタルの信号値として出力することが可能である。なお、単位画素201の詳細は、図3を参照して説明する。

40

【0021】

垂直制御回路202は、画素領域200の画素をスイッチ205により1行単位で選択する。また、垂直制御回路202は、不図示の配線を介して画素領域の画素に行単位で制御信号を送出する。この制御信号の詳細についても、図3を参照して後述する。

【0022】

50

水平制御回路 203 は、画素領域 200 の画素をスイッチ 206 により 1 列単位で選択する。垂直制御回路 202 と水平制御回路 203 の組み合わせにより選択された画素の画素信号は、補正部 207 に出力される。

#### 【0023】

補正部 207 は、各画素から出力された画素信号に対して単位時間当たりの受光量の違いによって生じる画質劣化を抑制するための補正処理（画像処理）を行う。また、補正部 207 では、画素信号の黒レベルを基準値に合わせる補正処理も行う。これらの補正処理の詳細は、図 8 を参照して後述する。

#### 【0024】

デジタル出力部 208 は、補正部 207 で補正処理（画像処理）された画素信号を、撮像素子 100 の外部に出力する。TG 204 は、各画素の画素信号を出力するための制御信号を、垂直制御回路 202 および水平制御回路 203 に送出する。なお、TG 204 は、不図示の配線を介して補正部 207、デジタル出力部 208 にも制御信号を送出する。

10

#### 【0025】

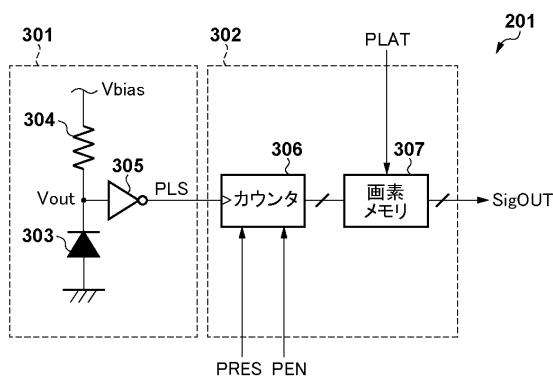

図 3 は、単位画素 201 の構成を示す図である。単位画素 201 は、大きく分けて、受光部 301 と計数部 302 を備える。

#### 【0026】

受光部 301 は、フォトダイオード（PD）303、クエンチ抵抗 304、反転バッファ 305 を含んで構成される。PD 303 は、アバランシェフォトダイオードであり、クエンチ抵抗 304 を介して降伏電圧より大きな逆バイアス電圧  $V_{bias}$  が印加され、ガイガーモードで動作する。したがって、PD 303 にフォトンが入射するとアバランシェ増倍現象を引き起こし、アバランシェ電流が発生する。クエンチ抵抗 304 は、PD 303 のアバランシェ増倍現象を停止されるための抵抗素子である。反転バッファ 305 は、アバランシェ増倍現象によって生じた電圧変化をパルス信号（以下、「PLS 信号」と記す。）として取り出すために設けられる。

20

#### 【0027】

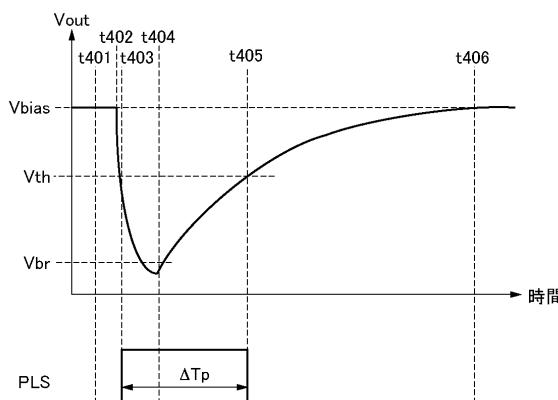

ここで、図 4 を参照して、受光部 301 の動作について説明する。図 4 は、PD 303 にフォトンが入射した際のカソード端子電圧  $V_{out}$  と、反転バッファ 305 から出力される PLS 信号の時間変化を表す図である。ここで、カソード端子電圧  $V_{out}$  は、PD 303 に印加される逆バイアス電圧の大きさでもある。

30

#### 【0028】

時刻  $t_{401}$  では、PD 303 には、降伏電圧  $V_{br}$  より大きな逆バイアス電圧  $V_{bias}$  が印加されており、ガイガーモードで動作している。この状態で時刻  $t_{402}$  において、PD 303 にフォトンが入射すると、PD 303 で生成されたキャリアがアバランシェ増倍現象を引き起こし、アバランシェ電流が発生する。このアバランシェ電流により、クエンチ抵抗 304 に接続された PD 303 のカソード端子電圧  $V_{out}$  が低下し始める。時刻  $t_{404}$  で  $V_{out}$  が降伏電圧  $V_{br}$  を下回るとアバランシェ増倍現象が停止する。そして、 $V_{bias}$  を印加している電源からクエンチ抵抗 304 を介して再充電が行われるため、カソード端子電圧  $V_{out}$  は上昇し始める。時刻  $t_{406}$  で再充電が完了すると、 $V_{out}$  は、再び逆バイアス電圧  $V_{bias}$  に戻る。ここで、再充電に掛かる時間はクエンチ抵抗 304 の抵抗値と寄生容量に依存する。

40

#### 【0029】

反転バッファから出力される PLS 信号が L および H に切り替わる閾値を  $V_{th}$  とすると、図 4 に示すように、時刻  $t_{403} \sim t_{405}$  の間で PLS 信号は H となる。したがって、1 回のフォトン入射によって、1 つの PLS 信号が受光部 301 から出力される。ここで、時刻  $t_{403} \sim t_{405}$  で発生する PLS 信号のパルス幅を  $T_p$  と記す。

#### 【0030】

図 3 の説明に戻り、計数部 302 は、カウンタ回路 306、画素メモリ 307 を含んで構成される。カウンタ回路 306 には、受光部 301 でフォトンの入射により発生した PLS 信号が入力され、PLS 信号が L から H に変化した回数をパルス数として計数する

50

。また、カウンター回路 306 には、垂直制御回路 202 からイネーブル信号（以下、「PEN 信号」と記す。）およびリセット信号（以下、「PRES 信号」と記す。）が供給される。カウンター回路 306 に供給される PEN 信号が H レベルの状態で、PLS 信号が L から H に変化すると、計数値が 1 つ増加する。PEN 信号が L レベルの状態では、PLS 信号が L から H に変化しても、計数値は増加せず、現在の計数値が保持される。また、カウンター回路 306 に供給される PRES 信号が H レベルになると、カウンター回路 306 の計数値は 0 にリセットされる。

#### 【0031】

画素メモリ 307 は、カウンター回路 306 で計数した計数値をデジタルの画素信号として取り込み、その画素信号を補正部 207 に読み出している間、一時的に保持するためのメモリである。画素メモリ 307 には垂直制御回路 202 からラッチ信号（以下、「PLAT 信号」と記す。）が供給される。PLAT 信号が L から H に変化すると、画素メモリ 307 は、その時点でのカウンター回路 306 の計数値をデジタルの画素信号として取り込んで保持する。これ以降、カウンター回路 306 が計数している値を計数値、画素メモリ 307 が保持した値を画素信号と表記して区別する。

10

#### 【0032】

垂直制御回路 202 と水平制御回路 203 の組み合わせによって選択された画素の画素メモリ 307 に保持された画素信号は、補正部 207 に出力される。

#### 【0033】

なお、第 1 の実施形態においては、垂直制御回路 202 から供給される PEN 信号、PRES 信号および PLAT 信号は、画素領域 200 内のすべての画素で同時に制御されるものとして説明するが、行単位で制御するタイミングを切り替えてよい。

20

#### 【0034】

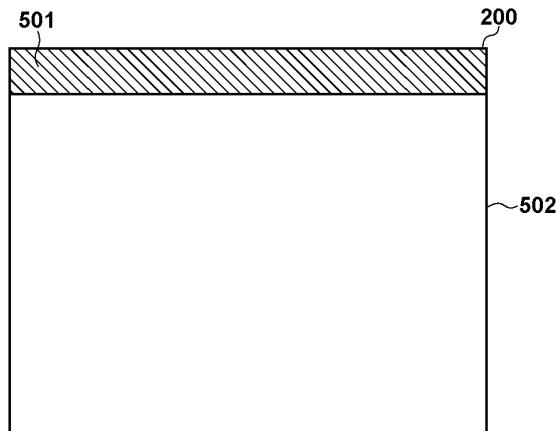

また、画素領域 200 の一部領域は、図 5 に示すようにオプティカルブラック画素領域（以下、「OB 領域」と記す。）501 と開口画素領域 502 で構成される。OB 領域 501 に配置される画素（OB 画素）の受光部 301 は不図示の金属遮光層等で遮光され、PD 303 に光が入射しない構成になっている。OB 領域の各画素から出力された画素信号は、補正部 207 で画素信号の黒レベルを基準値に合わせる補正に用いられる。一方、開口画素領域 502 に配置される画素の受光部 301 は、PD 303 に光が入射するようにな図示の開口を備える。開口画素領域の各画素からは、受光量に応じた画素信号が出力される。

30

#### 【0035】

なお、図 5 では、OB 領域 501 を画素領域の上側一帯に配置してあるが、例えば、画素領域 200 の左側や右側等、配置箇所は適宜選択することができる。

#### 【0036】

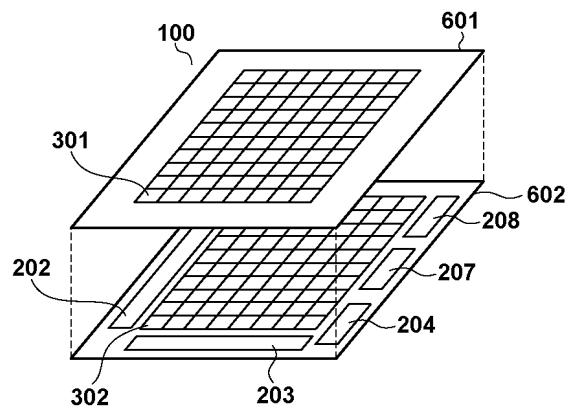

図 6 に、撮像素子 100 のチップレイアウトの一例を示す。撮像素子 100 は、受光部基板 601、計数部基板 602 を積層させた構成を有する。各基板間の配線は、シリコン貫通電極等を用いて電気的に接続される。受光部基板 601 には、各画素の受光部 301 が行列状に配置される。計数部基板 602 には、各画素の計数部 302 が行列状に配置される。また、計数部基板 602 には、垂直制御回路 202 および水平制御回路 203、TG 204、補正部 207、デジタル出力部 208 も配置される。図 5 に示すように、受光部 301 と計数部 302 を別々の基板に形成することで、受光部 301 の面積を確保することができ、これにより、受光部の開口率の低下を防止することができる。なお、撮像素子 100 を積層構造にせず、同一の基板上に形成してもよい。

40

#### 【0037】

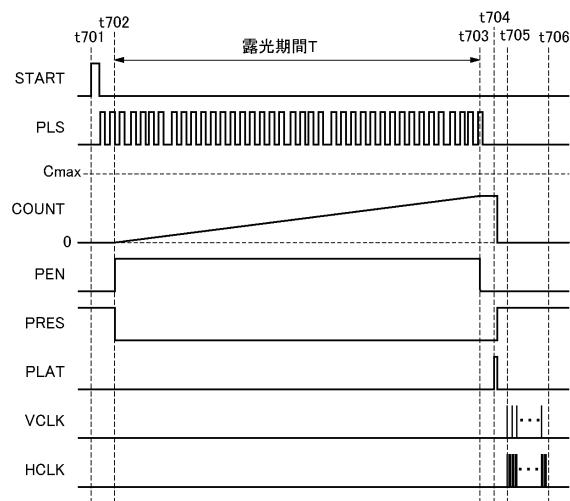

図 7 は、第 1 の実施形態において、1 フレームの画像を取得する際の撮像装置の駆動タイミングチャートを示す。時刻 t701 で撮影開始信号 START が L → H → L になると、各画素の受光部 301 にバイアス電圧 Vbias が供給される。そして、PD 303 には、降伏電圧より大きな逆バイアス電圧が印加され、ガイガーモードで動作を開始する。これにより、受光部 301 からは、入射したフォトンの数に応じて PLS 信号が出力される

50

。 C O U N T は任意の画素のカウンター回路 3 0 6 が計数した計数値の一例を示す。 C m a x は、カウンター回路 3 0 6 で計数できる最大値である。

【 0 0 3 8 】

時刻 t 7 0 1 の時点では、 P R E S 信号は H になっており、各画素のカウンター回路 3 0 6 の計数値は 0 にリセットされている。

【 0 0 3 9 】

時刻 t 7 0 2 で、 P R E S 信号が L となり、各画素のカウンター回路 3 0 6 のリセットが解除される。同時に P E N 信号が H となり、各画素のカウンター回路 3 0 6 はイネーブル状態となる。したがって、各画素のカウンター回路 3 0 6 では、入力された P L S 信号に応じて計数値が増加する。これにより撮像装置の露光期間が開始する。この露光期間は時刻 t 7 0 3 で P E N 信号が L になるまで続く。この時刻 t 7 0 2 から t 7 0 3 までの露光期間の長さを T とする。

10

【 0 0 4 0 】

時刻 t 7 0 3 で露光期間 T が終了すると、 P E N 信号が L になる。これにより、各画素のカウンター回路 3 0 6 がディセーブル状態になり、カウンター回路 3 0 6 に P L S 信号が入力されても計数値が増加しなくなる。また、受光部 3 0 1 へのバイアス電圧 V b i a s の供給が停止し、受光部 3 0 1 は P L S 信号を出力しなくなる。そして時刻 t 7 0 4 で垂直制御回路 2 0 2 から各画素に対して供給している P L A T 信号が一斉に L → H に変化する。これにより各画素のカウンター回路 3 0 6 の計数値が画素信号として画素メモリ 3 0 7 に保持される。その後、 P L A T 信号は L に戻る。また、画素メモリ 3 0 7 に画素信号が保持されると、すぐに P R E S 信号が H になり、各画素のカウンター回路 3 0 6 の計数値が 0 にリセットされる。

20

【 0 0 4 1 】

時刻 t 7 0 5 ~ t 7 0 6 では、垂直制御回路 2 0 2 に T G 2 0 4 から V C L K 信号が供給される。 V C L K 信号が H になる毎に、各行のスイッチ 2 0 5 が順番にオンし、垂直制御回路 2 0 2 が画素領域 2 0 0 の画素を 1 行ずつ選択していく。そして、任意の 1 行が選択されると、水平制御回路 2 0 3 に T G 2 0 4 から H C L K 信号が供給され、各列のスイッチ 2 0 6 が順番にオンする。これにより、選択行の画素の画素メモリ 3 0 7 に保持されていた画素信号が補正部 2 0 7 に順次出力される。

30

【 0 0 4 2 】

その後、補正部 2 0 7 で補正処理された画素信号は、デジタル出力部 2 0 8 を介して撮像素子 1 0 0 の外部に順次出力される。

【 0 0 4 3 】

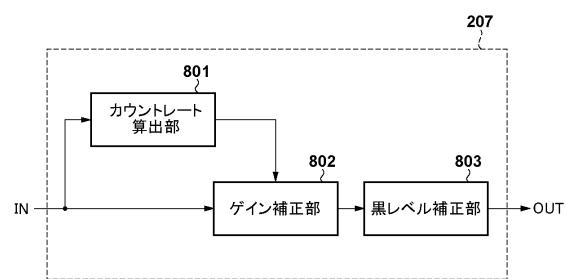

図 8 に、補正部 2 0 7 の構成を示す。補正部 2 0 7 は、カウントレート算出部 8 0 1 、ゲイン補正部 8 0 2 、黒レベル補正部 8 0 3 を含んで構成される。カウントレート算出部 8 0 1 およびゲイン補正部 8 0 2 は、単位時間あたりの受光量の違いによって生じる画質劣化を補正する。黒レベル補正部 8 0 3 は、各画素の P D 3 0 3 で発生した暗電流に起因して受光部 3 0 1 から出力される P L S 信号をカウンター回路 3 0 6 で計数して増加してしまった画素信号成分（暗電流成分）を、オフセット補正により除去する。

40

【 0 0 4 4 】

ここで、図 9 および図 1 0 を用いて、単位時間あたりの受光量の違いによって生じる画質劣化（誤差）の補正方法について説明する。

【 0 0 4 5 】

図 9 に、任意の画素の入射フォトンレートと、カウンター回路 3 0 6 のカウントレートとの関係を示す。ここで、入射フォトンレートは受光部 3 0 1 に単位時間あたりに入射するフォトンの数であり、単位時間あたりの受光量に比例した値となる。カウントレートはカウンター回路 3 0 6 の計数値の単位時間あたりの増加量である。本来であれば、理想値で示すようにカウントレートと入射フォトンレートは比例する。しかし、入射フォトンレートが高い状態、つまり単位時間あたりの受光量が多い状態では、1 つのフォトンが入射して発生した P L S 信号が H → L に戻る前に新たなフォトンが入射してしまう。その結果、

50

複数のPLS信号が重なってしまうため、カウンター回路306で計数する計数値が、本来のフォトンの数よりも低下してしまう。したがって、図9の901に示すように、入射フォトンレートが高くなるほど、カウントレートが本来の値よりも低下してしまう。

#### 【0046】

図10に、カウントレートに対する入射フォトンレートの関係を示す。この図10は、図9のグラフの縦軸と横軸を入れ替えたものである。図10に示すように、各画素のカウントレートに応じて、矢印1001のように理想値となるように画素信号にゲイン補正をすることで、受光量に対して線形な画素信号を得ることができる。ここで、入射フォトンレートがPmax以上となる斜線で示す領域では、入射フォトンレートが増えるにつれてカウントレートが減少し始める。したがって、入射フォトンレートがPmax以上となる場合は、カウントレートから本来の入射フォトンレートを算出することができない。そのため、撮影前に測光部109で測光処理を行い、その測光結果から、入射フォトンレートがPmax以上となるような高輝度被写体を含むと全体制御・演算部が判定した場合は、入射フォトンレートがPmax未満になるように撮影レンズの絞り制御を行ってから撮影すればよい。または、特許文献1に記載のように、各画素に受光部から出力されたPLS信号のパルス幅を累積加算する累積手段を設け、受光量に対して単調増加する信号が各画素から出力されるようにしてもよい。

#### 【0047】

次に、図8の各ブロックの具体的な処理について説明する。カウントレート算出部801には、各画素から出力された画素信号が順次入力される。そして、画素信号を露光期間Tで除算することで、単位時間あたりのカウント値の増加量であるカウントレートを算出する。

#### 【0048】

ゲイン補正部802は、カウントレート算出部801で算出したカウントレートをもとに、対応する画素の画素信号にゲイン補正を行う。各画素から出力され補正部207に入力される画素信号をx、ゲイン補正後の画素信号をyとすると、ゲイン補正後の画素信号yは、式(1)により表すことができる。

$$y = (r) \times x \quad \dots (1)$$

#### 【0049】

ここで、(r)はゲイン補正係数、rはカウントレート算出部801で算出したカウントレートである。

図11にゲイン補正係数(r)の例を示す。同図に示すように、ゲイン補正係数(r)は、カウントレート算出部801で算出したカウントレートrによって異なる値をとる。このゲイン補正係数(r)は図10のカウントレートが理想値になるために必要なゲイン補正量である。

#### 【0050】

ゲイン補正係数(r)は、ゲイン補正部802においてカウントレートrに応じた補正テーブルとして記憶しておけばよい。または、カウントレートrの近似関数として記憶しておき、各画素のカウントレートに応じてゲイン補正係数(r)を算出してもよい。

#### 【0051】

黒レベル補正部803は、ゲイン補正部802でゲイン補正された画素信号が入力され、オフセット補正により画素信号から暗電流成分を除去する。具体的には、OB領域501の画素信号を積算し、その平均値を算出することで、暗電流成分を算出する。そして、その平均値を開口画素領域502の各画素の画素信号から減算することで、暗電流成分を除去する。

#### 【0052】

黒レベル補正部803で補正された画素信号は、順次デジタル出力部208に送出され、撮像素子100の外部に出力される。

#### 【0053】

なお、ゲイン補正部802によるゲイン補正は、黒レベル補正部803によるオフセット

10

20

30

40

50

補正よりも前で行っている。これは、受光部 301において暗電流によって発生したパルス信号とフォトンの入射によって発生したパルス信号が重なることで、カウンター回路 306 で計数したフォトンによる画素信号成分と暗電流成分の双方が本来の値よりも低下するためである。したがって、ゲイン補正部 802において、本来のフォトンによる画素信号成分および暗電流成分になるようにゲイン補正を行った後、黒レベル補正部 803 で画素信号から OB 領域の平均画素信号を減算することで、暗電流成分を好適に除去することができる。

#### 【0054】

なお、フォトンによる画素信号成分に比べて暗電流成分が十分小さい場合には、黒レベル補正部 803 でオフセット補正を行った後、ゲイン補正部 802 でゲイン補正を行う構成 10 にしてよい。

#### 【0055】

以上で述べた補正部 207 の補正処理により単位時間あたりの受光量の違いによって生じる画質劣化を抑制することができる。なお、補正部 207 で行う補正処理は、信号処理部 101 や全体制御・演算部 104 で行う構成にしてもよい。

#### 【0056】

##### <変形例>

図 3 に示した単位画素 201 では、クエンチ抵抗 304 を用いてアバランシェ増倍を停止させていたが、クエンチ抵抗として、MOS トランジスタの抵抗成分を利用してもよい。図 12 に、第 1 の実施形態の変形例による単位画素 201 の構成を示す。図 12 は、図 3 20 に示す単位画素の構成に対応し、図 3 と同一の箇所については同一の番号を付与し、その説明は省略する。

#### 【0057】

図 12 は、MOS トランジスタ 1201 のドレイン - ソース間の抵抗成分をクエンチ抵抗として利用した場合の構成を示している。本構成では、MOS トランジスタ 1201 のゲート電圧  $V_{qnc}$  を変えることで、ドレイン - ソース間の抵抗値を変化させ、図 4 の時刻  $t_{404} \sim 406$  で示す再充電にかかる時間を変化させることができる。例えば、ゲート電圧  $V_{qnc}$  をゲート閾値電圧以上にすることで MOS トランジスタ 1201 をオンさせると、ドレイン - ソース間の抵抗値が減少する。これにより再充電にかかる時間が短縮し、PLS 信号のパルス幅  $T_p$  が短縮される。したがって、複数のフォトンが連続して受光部に入射した際に、それぞれのフォトンにより発生したパルスが重なってしまう確立を減少させることができる。

#### 【0058】

その結果、図 9 で示した入射フォトンレートが高い場合の出力カウントレートの低下を減少させることができる。この場合、ゲイン補正部 802 で画素信号に乗算するゲイン補正係数 ( $r$ ) をパルス幅  $T_p$  に応じて変えることで過補正になることを抑えることができる。したがって、単位時間あたりの受光量の違いによって生じる画質劣化を好適に抑制することが可能となる。

#### 【0059】

##### <第 2 の実施形態>

次に、本発明の第 2 の実施形態について説明する。上述した第 1 の実施形態では、画素毎にカウントレートを算出して、カウントレートに応じたゲイン補正係数を用いて補正を行っていた。これに対し、第 2 の実施形態では、測光部 109 の測光結果に基づいて画素信号に応じたゲイン補正係数を選択する。

#### 【0060】

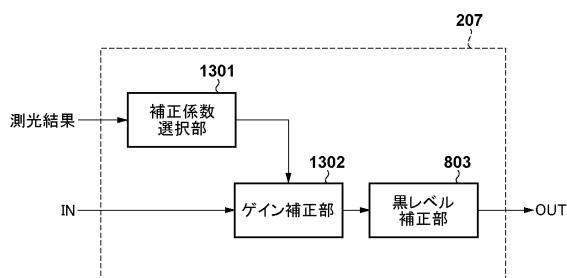

図 13 は、第 2 の実施形態における補正部 207 の構成を示すブロック図であり、第 1 の実施形態で説明した図 8 に示す補正部 207 に代えて用いられる。なお、図 8 と同様の構成については同じ参照番号を付し、説明を省略する。また、補正部 207 以外の構成は上述した第 1 の実施形態と同様であるため、説明を省略する。

#### 【0061】

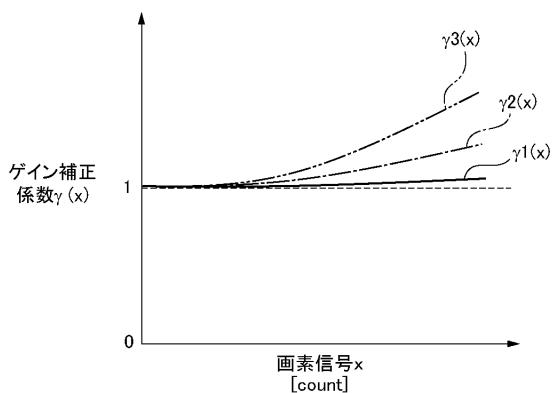

補正係数選択部 1301 は、測光部 109 で行った測光の測光結果を取得し、その結果に応じて、画素信号に応じたゲイン補正係数を選択する。具体的には、測光部 109 の測光エリア毎に測定した被写体輝度のうち、最大の輝度値に応じて図 14 の 1 ( x ) ~ 3 ( x ) で示すゲイン補正係数のいずれかを選択する。ここで、x はゲイン補正部 1302 に入力される画素信号であり、1 ( x ) ~ 3 ( x ) は画素信号に応じたゲイン補正係数である。

#### 【 0062 】

測光部 109 で測定した最大輝度値が予め決められた第 1 の閾値よりも低い場合はゲイン補正係数 1 ( x ) が選択され、最大輝度値が予め決められた第 2 の閾値以上の場合には、ゲイン補正係数 3 ( x ) が選択される。なお、第 1 の閾値 < 第 2 の閾値である。また、両者の中間の場合は、ゲイン補正係数 2 ( x ) が選択される。すなわち、同じ画素信号であっても、測光部 109 で測定した最大輝度値が高いほど、ゲイン補正量が大きくなるようなゲイン補正係数が選択される。これは、最大輝度値が高いほど、撮影時の単位時間あたりの受光量が増え、受光部からのパルス信号が重なることで発生する画素信号の低下の影響が大きくなるためである。

10

#### 【 0063 】

ゲイン補正部 1302 では、補正係数選択部 1301 で選択した補正係数を以下の式 ( 2 ) のように画素信号 x に乗算する。

$$y = ( x ) \times x \quad \dots ( 2 )$$

20

#### 【 0064 】

ここで、y はゲイン補正後の画素信号、( x ) は、補正係数選択部 1301 により、測光結果及び画素信号に基づいて選択されたゲイン補正係数である。

ゲイン補正部 1302 でゲイン補正された画素信号は、第 1 の実施形態と同様に、黒レベル補正部 803 でオフセット補正が行われ、補正後の画素信号がデジタル出力部に出力される。

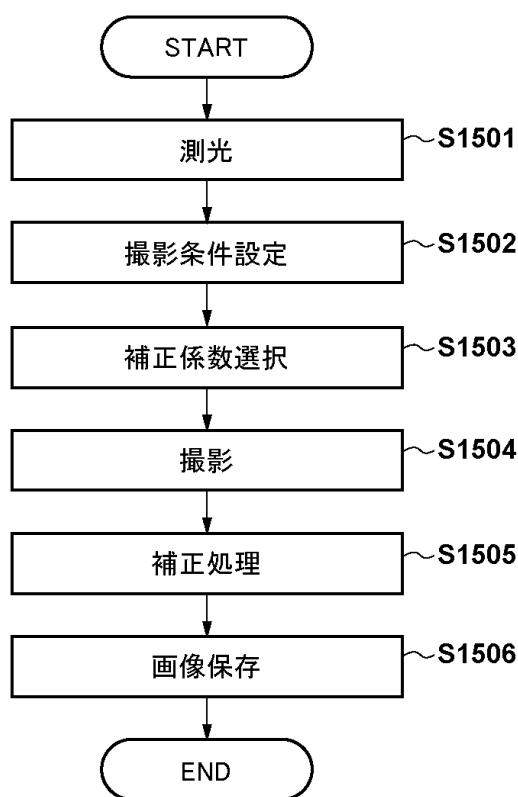

#### 【 0065 】

図 15 に、第 2 の実施形態における自動露出撮影処理のフローチャートを示す。撮影が開始されると、まず S1501 において、測光部 109 において測光処理を行う。具体的には、測光部 109 の測光エリア毎に被写体輝度を測定する。

30

#### 【 0066 】

次に S1502 において、測光部 109 の測光結果に応じて全体制御・演算部 104 が、絞り、露光期間等の撮影条件を設定する。S1503 では、補正係数選択部 1301 で、ゲイン補正係数の選択が行われる。ここでは、図 14 を参照して上述したように、測光部 109 で測定した最大輝度値が高いほど、ゲイン補正量が大きくなるようなゲイン補正係数が選択される。

#### 【 0067 】

S1504 では、S1502 で設定した撮影条件で撮像素子 100 により撮影を行う。具体的には、図 7 に示す駆動を行い、画素領域 200 から画素信号が補正部 207 に順次出力される。

40

#### 【 0068 】

S1505 では、画素領域 200 から順次出力される画素信号に対して補正部 207 にて補正処理を行う。ゲイン補正部 1302 では、補正係数選択部 1301 で選択されたゲイン補正係数のうち、画素信号に応じて選択されたゲイン補正係数を画素信号に乗算する。これにより、受光部からのパルス信号が重なることで発生する画素信号の低下を補うことができる。その後、黒レベル補正部 803 でオフセット補正された画素信号が撮像素子 100 から出力され、そして、S1506 で、記録部 107 にて画像データとして保存される。

#### 【 0069 】

以上で述べた補正部 207 の補正処理により単位時間あたりの受光量の違いによって生じる画質劣化を抑制することができる。

50

## 【0070】

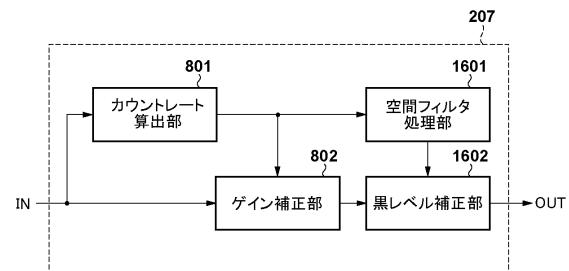

## &lt;第3の実施形態&gt;

次に、本発明の第3の実施形態について説明する。第3の実施形態では、単位時間あたりの受光量に応じて、黒レベル補正部の補正量を変える構成について説明する。

## 【0071】

単位時間あたりの受光量が大きい画素では、頻繁にアバランシェ増倍現象が発生し、大電流がクエンチ抵抗304を流れるため、クエンチ抵抗304での発熱量が大きくなる。そのため、クエンチ抵抗304の付近にあるPD303の温度が上昇し、暗電流量が増加する。その結果、光が入射しないOB領域の画素(OB画素)と、単位時間あたりの受光量の多い画素とで暗電流量に差が生じてしまう。そこで、第3の実施形態では、単位時間あたりの受光量に応じて黒レベル補正部の補正量を変更する。

10

## 【0072】

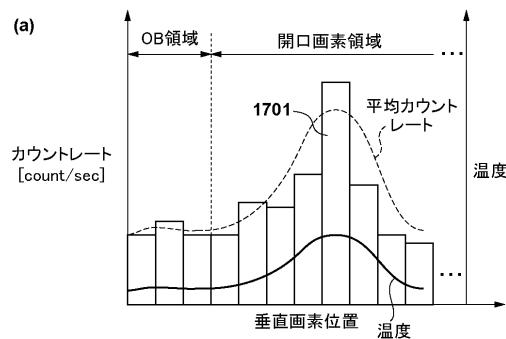

図16に、第3の実施形態における補正部207の構成を示すブロック図であり、第1の実施形態で説明した図8に示す補正部207に代えて用いられる。なお、図8と同様の構成については同じ参照番号を付し、説明を省略する。また、補正部207以外の構成は上述した第1の実施形態と同様であるため、説明を省略する。

## 【0073】

空間フィルタ処理部1601は、カウントレート算出部801で算出した画素毎のカウントレートに対してフィルタ処理を行う。例えば、対象画素とその周囲8画素のカウントレートの平均値である平均カウントレートを計算する。なお、フィルタ処理として、重み付け平均処理を行ってもよい。

20

## 【0074】

なお、対象画素よりも後に読み出す画素のカウントレートを平均化の対象とする場合は、補正部207の前に不図示の保持メモリを設けて、画素信号を一時的に保持してから空間フィルタ処理部1601でフィルタ処理を行うようにすればよい。黒レベル補正部1602には、ゲイン補正部802から出力された画素信号が入力され、以下の式(3)のようにオフセット補正を行う。

$$z = y - (r_{ave}) \times drk \quad \dots (3)$$

## 【0075】

ここで、zはオフセット補正後の画素信号、yは黒レベル補正部1602に入力される画素信号、drkはOB領域の平均画素信号、r<sub>ave</sub>は空間フィルタ処理部1601で算出した平均カウントレートである。(r<sub>ave</sub>)はオフセット補正係数であり、平均カウントレートr<sub>ave</sub>に応じた値となる。

30

ここで、オフセット補正係数(r<sub>ave</sub>)の詳細について、図17を参照して説明する。図17(a)は、画素領域の任意の一列の画素のカウントレートを算出した例を示す。1701に示すように単位時間あたりの受光量が多い画素では、カウントレートが高くなる。また、実線で示す温度のようにカウントレートの高い画素付近では、アバランシェ電流による発熱によって温度が高くなる。破線で示す平均カウントレートは空間フィルタ処理部1601で各画素のカウントレートを平均化処理した値である。

40

## 【0076】

図17(b)は、図17(a)に対応する画素の暗電流量の例である。1702に示す位置の付近の画素では、温度が高いため、OB領域に比べて暗電流量が多くなる。実線で示す(r<sub>ave</sub>)はOB領域の平均画素信号に乗算するオフセット補正係数である。オフセット補正係数(r<sub>ave</sub>)は、図17(b)に示すように、図17(a)の平均カウントレートが高い画素ほど大きな値となる。これにより、OB領域と、単位時間あたりの受光量が多い画素とで暗電流量が異なっていても、画素信号から暗電流成分を好適に除去することができる。

## 【0077】

なお、空間フィルタ処理部1601のフィルタ処理は、画素領域200がベイラー配列のカラーフィルターを備えている場合は、同一色の画素のみで平均化処理を行う構成にして

50

もよい。また、空間フィルタ処理部 1601 を設けず、カウントレート算出部 801 で算出したカウントレートに応じたオフセット補正係数を用いてもよい。

【0078】

上記の通り第3の実施形態によれば、単位時間あたりの受光量が多い画素の画素信号から暗電流成分を好適に除去することができ、単位時間あたりの受光量の違いによって生じる画質劣化を抑制することができる。

【0079】

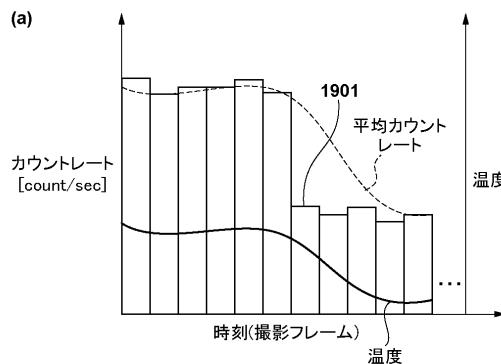

<第4の実施形態>

次に、本発明の第4の実施形態について説明する。動画等で連続して撮影を行う場合、高輝度の被写体が移動すると、被写体のあった位置の画素のカウントレートは低下するが、温度はそれよりもゆるやかに変化する。そして、各画素の暗電流量も温度変化に従ってゆるやかに変化する。このような場合でも暗電流成分を好適に補正することができる構成について説明する。

10

【0080】

図18は、第4の実施形態における補正部207の構成を示すブロック図であり、第1の実施形態で説明した図8に示す補正部207に代えて用いられる。なお、図8と同様の構成については同じ参照番号を付し、説明を省略する。また、補正部207以外の構成は上述した第1の実施形態と同様であるため、説明を省略する。

【0081】

時間フィルタ処理部1801はカウントレート算出部801で算出したカウントレートを複数フレームにわたってフィルタ処理をする。例えば、現在のフレームとそれより前の4フレーム分の画素毎の平均カウントレートを算出する。また、時間フィルタ処理部1801は、各画素の平均カウントレートを保持するための不図示の保持メモリを備える。

20

【0082】

黒レベル補正部1802にはゲイン補正部802から出力された画素信号が入力され、時間フィルタ処理部1801で算出した平均カウントレートに応じてオフセット補正係数を用いて黒レベルの補正を行う。この補正方法は第3の実施形態において説明した式(3)と同様であるため、説明を省略する。

【0083】

図19(a)に画素領域の任意の一つの画素のカウントレートを撮影フレーム毎に算出した例を示す。1901のフレームに示すように高輝度被写体の移動等により対象画素のカウントレートが低下した場合でも、同図に実線で示す対象画素の温度はすぐには低下せず、ゆるやかに追従する。そのため、図19(b)に示すように、各撮影フレームの暗電流は温度に従ってゆるやかに変化する。また、破線で示す平均カウントレートは時間フィルタ処理部1801で対象画素のカウントレートを複数フレームにわたって平均化処理した値である。

30

【0084】

図19(b)は、図19(a)に対応するフレームの暗電流量の例である。1902に示すフレームでは、カウントレートは低下しているが、画素の温度がまだ高いため、カウントレートと比べて暗電流量は多いままである。実線で示す(rave)は式(3)でOB領域の平均画素信号に乗算するオフセット補正係数である。オフセット補正係数(rave)は、図17(a)の平均カウントレートが高い画素ほど大きな値となる。このオフセット補正係数をOB領域の平均画素信号に乗算した値を用いてオフセット補正することで、画素信号から暗電流成分を除去することができる。

40

【0085】

上記の通り第4の実施形態によれば、動画撮影等の最中に単位時間あたりの受光量が大きく変化した場合でも、画素信号から暗電流成分を好適に除去することができる。

【0086】

<第5の実施形態>

次に、本発明の第5の実施形態について説明する。上述した第1の実施形態では、露光期

50

間終了後に出力した画素信号をもとにカウントレートを算出し、補正を行っていたため、露光期間中に被写体輝度が変化した場合に正確なカウントレートを求めることができなかった。これに対し、第5の実施形態では、露光期間中に被写体輝度が変化した場合でも対応可能な構成について説明する。

#### 【0087】

図20に、第5の実施形態における撮像素子100'の全体構成を示す図であり、第1の実施形態で説明した図2に示す撮像素子100に代えて用いられる。なお、図2と同様の構成については同じ参照番号を付し、説明を省略する。また、撮像素子100'以外の構成は上述した第1の実施形態と同様であるため、説明を省略する。

#### 【0088】

信号処理ブロック2000は、補正部207と、フレームメモリ2001と、加算部2002とを備える。フレームメモリ2001は、一時メモリ領域2001aと積算メモリ領域2001bとを備え、露光期間中に各画素からデジタルの画素信号を取得して、保持する記憶回路である。一時メモリ領域2001aは、各画素からデジタルの画素信号を取得し、一時的に保持する。一時メモリ領域2001aに保持された画素信号は補正部207に入力され、第1の実施形態と同様の補正処理が行われる。

#### 【0089】

加算部2002は、積算メモリ領域2001bに保持されていた画像信号に、各画素から新たに読み出して補正処理された画像信号を同一アドレス毎に加算する。加算された画像信号は積算メモリ領域2001bに再び保持される。これにより、積算メモリ領域2001bは、露光期間中に補正部207で補正処理された画素信号を同一アドレス毎に積算された画素信号を保持する。ここで、一時メモリ領域2001aは、1画素あたり単位画素201から出力されるデジタルの画素信号と同一のビット幅を備える。一方、積算メモリ領域2001bは、単位画素201から出力されるデジタルの画素信号に比べて、十分大きなビット幅を備える。

#### 【0090】

積算メモリ領域2001bに保持された画素信号は、露光期間終了後にデジタル出力部208を介して撮像素子100の外部に出力される。なお、フレームメモリ2001および加算部2002、補正部207は、撮像素子100'の外部に設ける構成でもよい。

#### 【0091】

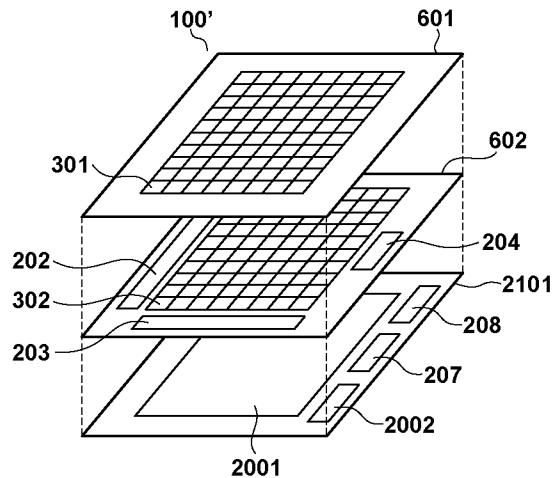

図21に、第5の実施形態における撮像素子100'のチップレイアウトの一例を示す。図21は、第1の実施形態の図6に対応し、図6と同一の構成については同一の番号を付与し、その説明は省略する。

#### 【0092】

撮像素子100'は、受光部基板601、計数部基板602およびフレームメモリ基板2101を積層させた構成を有する。各基板間の配線は、シリコン貫通電極等を用いて電気的に接続される。フレームメモリ基板2101には、フレームメモリ2001および加算部2002、補正部207、デジタル出力部208が配置される。フレームメモリ基板2101を、受光部基板601および計数部基板602よりも微細なプロセスで製造すれば、フレームメモリ2001は、大きなビット数を確保できる。なお、撮像素子100'を積層構造にせず、同一の基板上に形成してもよい。

#### 【0093】

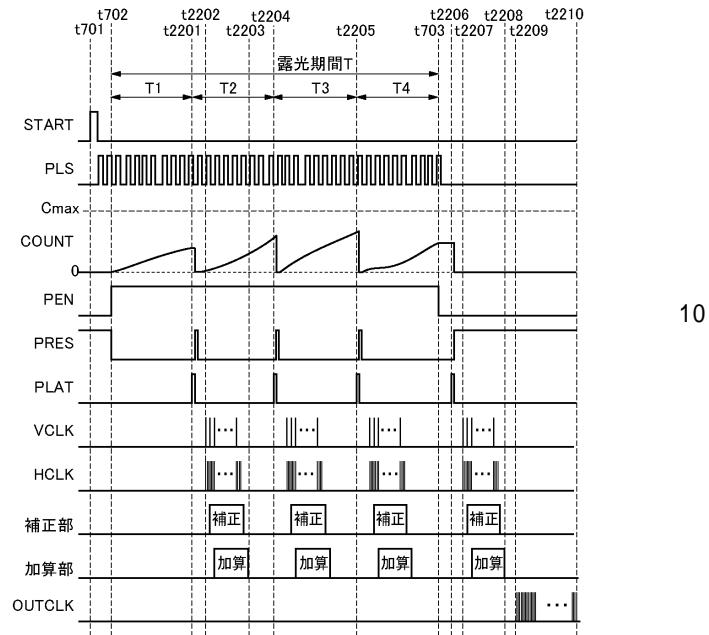

図22は、第5の実施形態において、1フレームの画像を取得する際の撮像装置の駆動タイミングチャートを示す。図22は、第1の実施形態の図7に示すタイミングチャートに対応し、図7と同一の動作をする処理については同一の番号を付与し、その説明は適宜省略する。

#### 【0094】

図22では、t702からt703の露光期間Tを4つの露光期間（以下、「分割露光期間」と呼ぶ。）T1～T4に分割し、分割露光期間毎に各画素から画素信号をフレームメモリ2001へ読み出す。

10

20

30

40

50

## 【0095】

時刻  $t_{2201}$  で分割露光期間  $T_1$  が経過すると、垂直制御回路 202 からすべての画素に対して供給している P L A T 信号が一斉に L H L と変化する。これにより、分割露光期間  $T_1$  の間に各画素のカウンター回路 306 で計数していた計数値が、画素信号として、各画素の画素メモリ 307 に保持される。画素信号が画素メモリ 307 に保持されると、すぐに P R E S が H になり、各画素のカウンター回路 306 の計数値が 0 にリセットされる。そして、P R E S が L に戻ると、リセットが解除され、各画素のカウンター回路 306 は、再び入射したフォトンに応じて計数を開始する。

## 【0096】

時刻  $t_{2202} \sim t_{2203}$  では、T G 204 から垂直制御回路 202 および水平制御回路 203 にそれぞれ V C L K 信号および H C L K 信号が供給される。そして、垂直制御回路 202 および水平制御回路 203 によって選択された画素の画素メモリ 307 に保持されていた画素信号が順次フレームメモリ 2001 内の一時メモリ領域 2001a に保持される。一時メモリ領域 2001a に保持された画素信号は、補正部 207 においてゲイン補正およびオフセット補正が行われ、補正後の画素信号は再び一時メモリ領域 2001a に保持される。なお、ここで補正部 207 により行われる補正処理は、第 1 ~ 第 4 の実施形態と同様のため、説明を省略する。

10

## 【0097】

そして、加算部 2002 において、一時メモリ領域 2001a に保持された補正後の画素信号と、積算メモリ領域 2001b に保持されていた同一アドレスの画素信号とを加算処理し、加算された画素信号を積算メモリ領域 2001b に再び格納する。なお、上記補正処理および加算処理は、各画素の画素メモリ 307 内の画素信号をフレームメモリ 2001 に保持する動作と並行して行われる。

20

## 【0098】

時刻  $t_{2202} \sim t_{2204}$  で行う最初の加算処理では、フレームメモリ 2001 内の積算メモリ領域 2001b には、画素信号が保持されていないため、補正部 207 で補正処理された画素信号が、そのまま積算メモリ領域 2001b に保持される。

## 【0099】

時刻  $t_{2204}$  で分割露光期間  $T_2$  が経過すると、再び P L A T 信号が L H L となり、時刻  $t_{2201} \sim t_{2203}$  の時と同様に、各画素の画素信号がフレームメモリ 2001 の一時メモリ領域 2001a に保持され、補正処理および加算処理が行われる。そして、加算処理が終わった画素信号は積算メモリ領域 2001b に再び保持される。以降、分割露光期間毎に同様の処理が繰り返される。

30

## 【0100】

ここで、時刻  $t_{2201} \sim t_{2203}$  で行われる、各画素の画素メモリ 307 に保持された画素信号に対する、一時メモリ領域 2001a への保持および補正部 207 の補正処理、加算部 2002 の加算処理は、時刻  $t_{2204}$  までに完了している必要がある。すなわち、次の分割露光期間が経過する前に完了している必要がある。したがって、この時間内に処理が完了するような動作周波数を設定する。または、次の分割露光期間が経過する前に処理が完了するように、分割露光期間の長さや分割数を調節する。

40

## 【0101】

時刻  $t_{2203}$  で、1 フレーム分の露光期間  $T$  が終了すると、P E N 信号が L となる。これにより、各画素のカウンター回路 306 がディセーブル状態になり、カウンター回路 306 の計数値が増加しなくなる。また、受光部 301 へのバイアス電圧 V b i a s の供給が停止し、受光部 301 は P L S 信号を出力しなくなる。そして、時刻  $t_{2206}$  で、P L A T 信号が L H L と切り替わり、露光終了時にカウンター回路 306 で計数していた計数値が画素メモリ 307 に保持される。そして、P R E S 信号が H になり、カウンター回路 306 の計数値が 0 にリセットされる。

## 【0102】

その後、時刻  $t_{2207} \sim t_{2208}$  では、 $t_{2202} \sim t_{2203}$  の時と同様に、各画

50

素の画素信号が一時メモリ領域 2001a に保持される。そして、補正処理および加算処理された画素信号が、積算メモリ領域 2001b に保持される。このとき、積算メモリ領域 2001b に保持された画素信号は、時刻  $t_{702} \sim t_{703}$  の露光期間中に画素メモリ 307 から取得した画素信号を積算した信号となる。この画素信号は、露光期間中に入射したフォトンの数に応じた信号となる。

【0103】

上記の通り本第 5 の実施形態によれば、分割した露光期間毎にカウントレートを算出して補正する。これにより、第 1 の実施形態と比べて、露光期間中に被写体輝度が変化した場合でも単位時間あたりの受光量の違いによって生じる画質劣化を好適に抑制することが可能となる。なお、上述した第 5 の実施形態における露光期間を分割する数や分割露光期間の長さは一例であり、本発明はこれに限られるものではない。

10

【0104】

<第 6 の実施形態>

次に、本発明の第 6 の実施形態について説明する。上述した第 5 の実施形態では、露光期間中に画素信号をフレームメモリ 2001 に読み出す度にカウンタ回路の計数値をリセットしたが、本第 6 の実施形態では、露光期間中にカウンタ回路の計数値をリセットしない構成について説明する。なお、第 6 の実施形態では、第 5 の実施形態と同様に、露光期間中に被写体輝度が変化した場合でも対応可能な構成である。

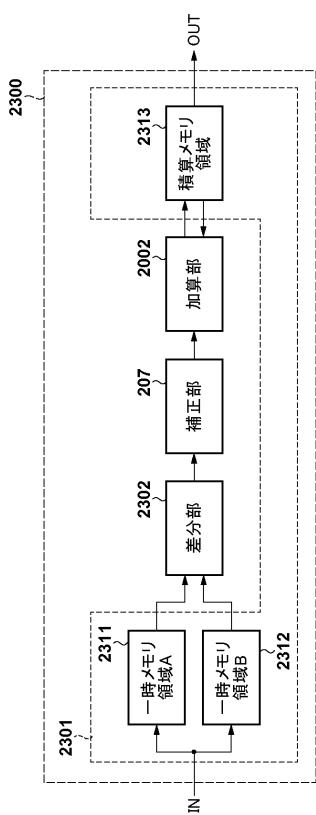

【0105】

図 23 は、画素領域 200 から出力された画素信号に信号処理をする信号処理ブロック 2300 の構成を示す。信号処理ブロック 2300 は、第 5 の実施形態において図 20 に示した信号処理ブロック 2000 の代わりに用いられる。なお、これ以外の箇所については、第 5 の実施形態と同様であるため、説明を省略する。

20

【0106】

フレームメモリ 2301 は、露光期間中に各画素からデジタルの画素信号を取得して、保持する記憶回路であり、一時メモリ領域 A2311、一時メモリ領域 B2312、積算メモリ領域 2313 で構成される。一時メモリ領域 A2311 および一時メモリ領域 B2312 は、各画素からデジタルの画素信号を取得し、一時的に保持するための一時メモリである。露光期間中に各画素から読み出し動作を行う毎に、読み出された画素信号は一時メモリ領域 A2311 と一時メモリ領域 B2312 に交互に保持される。積算メモリ領域 2313 は、露光期間中に補正部 207 で補正処理された画素信号を積算した値を保持する。

30

【0107】

差分部 2302 は、一時メモリ領域 A2311、一時メモリ領域 B2312 に保持された画素信号を同一アドレス毎に差分を計算して、その差分信号（差分値）を補正部 207 に出力する。なお、補正部 207 の補正処理は、第 1 ~ 第 4 の実施形態で述べた処理と同様であるため、ここでは説明を省略する。加算部 2002 は、フレームメモリ 2301 の積算メモリ領域 2313 に保持されていた画像信号に、補正部 207 で補正処理された画像信号を同一アドレス毎に加算する。加算された画像信号は積算メモリ領域 2313 に再び格納される。積算メモリ領域 2313 に保持された画素信号は、露光期間終了後にデジタル出力部 208 を介して撮像素子 100' の外部に出力される。なお、信号処理ブロック 2300 を撮像素子 100' の外部に設ける構成でもよい。

40

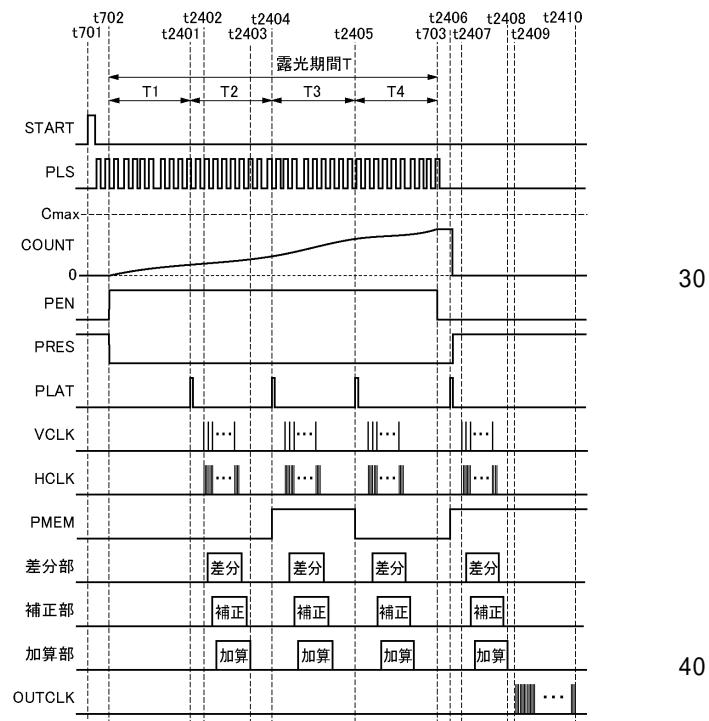

【0108】

図 24 に、第 6 の実施形態において、1 フレームの画像を取得する際の撮像装置の駆動タイミングチャートを示す。図 24 は、第 5 の実施形態の図 22 に示すタイミングチャートに対応し、図 22 と同一の動作をする処理については同一の番号を付与し、その説明は適宜省略する。

【0109】

図 24 では、第 5 の実施形態と同様に  $t_{702}$  から  $t_{703}$  の露光期間 T を 4 つの分割露光期間  $T_1 \sim T_4$  に分割し、分割露光期間毎に各画素から画素信号をフレームメモリ 2301 へ読み出す。ただし、第 5 の実施形態とは異なり、フレームメモリ 2301 に信号を

50

読み出した後にカウンター回路 306 の計数値はリセットしない。

【0110】

時刻  $t_{2401}$  で分割露光期間  $T_1$  が経過すると、垂直制御回路 202 からすべての画素に対して供給している P L A T 信号が一斉に L H L と変化する。これにより、分割露光期間  $T_1$  の間に各画素のカウンター回路 306 で計数していた計数値が、画素信号として、各画素の画素メモリ 307 に保持される。時刻  $t_{2402} \sim t_{2403}$  では、T G 204 から垂直制御回路 202 および水平制御回路 203 にそれぞれ V C L K 信号および H C L K 信号が供給される。そして、垂直制御回路 202 および水平制御回路 203 によって選択された画素の画素メモリ 307 に保持されていた画素信号が順次フレームメモリ 2001 内の一時メモリ領域に保持される。

10

【0111】

ここで、P M E M 信号は、画素信号を一時メモリ領域 A 2311 と一時メモリ領域 B 2312 のどちらに保持するかを選択するための制御信号であり、T G 204 からフレームメモリ 2301 に送出される。P M E M 信号が L レベルのとき、画素領域 200 から出力された画素信号は、一時メモリ領域 A 2311 に保持され、P M E M 信号が H レベルのときは、一時メモリ領域 B 2312 に保持される。 $t_{2402} \sim t_{2403}$  では、P M E M 信号が L レベルのため、画素領域 200 から出力された画素信号は、一時メモリ領域 A 2311 に保持される。

【0112】

一時メモリ領域 A 2311 に画素信号が保持されると、差分部 2302 では、一時メモリ領域 A 2311 に保持された画素信号から一時メモリ領域 B 2312 に保持された画素信号を、同一アドレス毎に減算して差分信号を生成する。そして、その差分信号を補正部 207 に出力する。このとき、一時メモリ領域 B 2312 には画素信号が保持されていないため、一時メモリ領域 A 2311 に保持された画素信号がそのまま補正部 207 に出力される。ここで、補正部 207 に出力される差分信号は、分割露光期間  $T_1$  の間にカウンター回路 306 で計数した信号である。補正部 207 に入力された画素信号は、ゲイン補正およびオフセット補正が行われた後、加算部 2002 によって補正処理後の画素信号と、積算メモリ領域 2313 に保持されていた同一アドレスの画素信号とを加算処理する。そして、加算された画素信号が積算メモリ領域 2313 に再び保持される。なお、上記差分処理、補正処理および加算処理は、各画素の画素信号をフレームメモリ 2301 の一時メモリ領域 A 2311 に保持する動作と並行して行われる。また、時刻  $t_{2402} \sim t_{2404}$  で行う最初の加算処理では、積算メモリ領域 2313 には、画素信号が保持されていないため、補正部 207 で補正処理された画素信号が、そのまま積算メモリ領域 2313 に格納される。

20

【0113】

時刻  $t_{2401}$  で、カウンター回路 306 の計数値を画素メモリ 307 に保持した後、カウンター回路 306 はリセットしていないため、入射したフォトンの数に応じて計数値は増加し続ける。

【0114】

時刻  $t_{2404}$  で分割露光期間  $T_2$  が経過すると、再び P L A T 信号が L H L となり、時刻  $t_{2401} \sim t_{2403}$  の時と同様に、各画素の画素信号がフレームメモリ 2301 に出力され保持される。このとき、P M E M 信号が H となるため、各画素の画素信号は、一時メモリ領域 B 2312 に保持される。そして、差分部 2302 は、一時メモリ領域 B 2312 に保持した画素信号から、時刻  $t_{2402} \sim t_{2403}$  で一時メモリ領域 A 2311 に保持した画素信号を同一アドレス毎に減算し、その差分信号を補正部 207 に出力する。ここで、差分部 2302 で行う差分処理は、一時メモリ領域 A 2311 と一時メモリ領域 B 2312 のうち、後から保持した信号から、先に保持した信号を減算することで行われる。したがって、この差分処理により生成される差分信号は、分割露光期間  $T_2$  の間に入射したフォトンの数に応じた信号となる。差分部 2302 で差分処理された差分信号は、補正部 207 および加算部 2002 で、補正処理および加算処理が行われる。そ

30

40

50

して、加算処理が終わった画素信号は積算メモリ領域 2313 に再び格納される。以降、分割露光期間毎に同様の処理が繰り返される。

【0115】

時刻 t703 で、1 フレーム分の露光期間 T が終了すると、PEN 信号が L となる。これにより、各画素のカウンター回路 306 がディセーブル状態になり、カウンター回路 306 の計数値が増加しなくなる。また、受光部 301 へのバイアス電圧 Vbias の供給が停止し、受光部 301 は PLS 信号を出力しなくなる。

【0116】

そして、時刻 t2406 で、PLAT 信号が L H L と切り替わり、露光終了時にカウンター回路 306 で計数していた計数値が画素メモリ 307 に保持される。そして、PRES 信号が H になり、カウンター回路 306 の計数値が 0 にリセットされる

10

【0117】

その後、時刻 t2407 ~ t2408 では、t2402 ~ t2403 の時と同様に、各画素の画素信号が一時メモリ領域 A2311 と一時メモリ領域 B2312 のいずれかに保持される。そして、差分処理および補正処理、加算処理された画素信号が積算メモリ領域 2313 に保持される。このとき、積算メモリ領域 2313 に保持された画素信号は、時刻 t702 ~ t703 の露光期間中に画素メモリ 307 から取得した画素信号を積算した信号となる。この画素信号は、露光期間中に入射したフォトンの数に応じた信号となる。

【0118】

上記の通り本第 6 の実施形態によれば、分割した露光期間毎にカウントレートを算出して補正する。これにより、第 1 の実施形態と比べて、露光期間中に被写体輝度が変化した場合でも単位時間あたりの受光量の違いによって生じる画質劣化を好適に抑制することが可能となる。なお、露光期間を分割する数や分割露光期間の長さは、一例であり、本発明はこれに限られるものではない。

20

【0119】

以上、本発明の実施形態について説明したが、本発明はこれらの実施形態に限定されるものではない。また、上述した実施形態を適宜組み合わせてもよい。

【0120】

<他の実施形態>

また、本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

30

【符号の説明】

【0121】

100：撮像素子、101：信号処理部、104：全体制御・演算部、105：メモリ部、107：記録部、108：操作部、109：測光部、200：画素領域、201：単位画素、202：垂直制御回路、203：水平制御回路、204：タイミングジェネレータ（T G）、207：補正部、208：デジタル出力部、301：受光部、302：計数部、303：フォトダイオード（PD）、304：クエンチ抵抗、305：反転バッファ、306：カウンター回路、307：画素メモリ、801：カウントレート算出部、802：ゲイン補正部、803, 1302, 1602, 1802：黒レベル補正部、1201：MOSトランジスタ、1301：補正係数選択部、1601：空間フィルタ処理部、1801：時間フィルタ処理部、2000：信号処理ブロック、2001, 2301：フレームメモリ、2001a：一時メモリ領域、2001b, 2313：積算メモリ領域、2002：加算部、2311：一時メモリ領域 A、2312：一時メモリ領域 B

40

【四面】

【 四 1 】

【 図 2 】

【 义 3 】

【 4 】

【図 5】

【図 6】

10

【図 7】

【図 8】

20

30

40

50

【図 9】

【図 10】

【図 11】

【図 12】

10

20

30

40

50

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

10

20

30

40

50

【図17】

【図18】

【図19】

【図20】

【図 2 1】

【図 2 2】

10

20

【図 2 3】

【図 2 4】

30

40

50

## フロントページの続き

(56)参考文献 特開2017-108457 (JP, A)

特開2014-081253 (JP, A)

特表2008-538606 (JP, A)

特開2017-125692 (JP, A)

特開2011-179863 (JP, A)

特開2013-108950 (JP, A)

米国特許出願公開第2006/0124832 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

G01T 1/00 - 1/16

G01T 1/167 - 7/12

H01L 21/339

H01L 27/14 - 27/148

H01L 27/30

H01L 29/762

H01L 31/00 - 31/02

H01L 31/0232

H01L 31/0248

H01L 31/0264

H01L 31/08

H01L 31/10

H01L 31/107 - 31/108

H01L 31/111

H01L 31/18

H01L 51/42

H04N 5/222 - 5/257

H04N 5/30 - 5/378