## (12)发明专利

(10)授权公告号 CN 107135357 B

(45)授权公告日 2019.05.31

(21)申请号 201710127423.3

(74)专利代理机构 北京市柳沈律师事务所

(22)申请日 2012.09.20

11105

(65)同一申请的已公布的文献号

代理人 安之斐

申请公布号 CN 107135357 A

(51)Int.Cl.

(43)申请公布日 2017.09.05

H04N 5/347(2011.01)

(30)优先权数据

H04N 5/374(2011.01)

JP2011-207368 2011.09.22 JP

H04N 5/3745(2011.01)

(62)分案原申请数据

H04N 5/378(2011.01)

201210352684.2 2012.09.20

H04N 9/04(2006.01)

(73)专利权人 索尼公司

(56)对比文件

地址 日本东京都

JP 2009044680 A, 2009.02.26,

(72)发明人 川口隆

CN 101990070 A, 2011.03.23,

CN 102098458 A, 2011.06.15,

审查员 魏玮

权利要求书2页 说明书22页 附图20页

## (54)发明名称

固态成像设备,控制固态成像设备的方法

## (57)摘要

固态成像设备包括：像素阵列单元，其具有以矩阵形式二维布置的多个像素和沿列方向布置的多个信号线；对应于各自的信号线提供的且将通过信号线从像素输出的模拟信号转换为数字信号A/D转换单元；以及切换单元，对下述通过每个信号线输出的模拟信号到数字信号的转换进行切换，该通过每个信号线输出的模拟信号到数字信号的转换使用对应于传送模拟信号的信号线提供的A/D转换单元和对应于不是传送模拟信号的信号线的信号线而提供的A/D转换单元的任一个。

1.一种成像设备,包括:

像素阵列,包括以矩阵图案布置的多个像素单元,其中所述多个像素单元包含被配置为生成第一模拟信号的第一像素单元,以及被配置为生成第二模拟信号的第二像素单元;

参考信号发生器,配置为生成参考信号;

第一比较器,耦接至所述第一像素单元,并配置为将所述参考信号与所述第一模拟信号进行比较;

第二比较器,耦接至所述第二像素单元,并配置为将所述参考信号与所述第二模拟信号进行比较;

第一切换电路,耦接至所述第一比较器的输出端子和第一计数器的输入端子;

第二切换电路,耦接至所述第二比较器的输出端子和第二计数器的输入端子;

第三切换电路,耦接至所述第一比较器的输出端子和第二计数器的输入端子;以及

第四切换电路,耦接至所述第二比较器的输出端子和第一计数器的输入端子;

切换电路控制器,配置为以第一切换状态或第二切换状态控制所述第一、第二、第三以及第四切换电路;

其中在所述第一切换状态中,所述第一切换电路和所述第二切换电路被激活;以及

其中在所述第二切换状态中,所述第三切换电路和所述第四切换电路被激活。

2.根据权利要求1所述的成像设备,其中所述第一像素单元包含多个光电二极管,其中所述多个光电二极管中的至少一个被配置为通过滤色器接收光,所述滤色器被配置为透射红光、蓝光、绿光。

3.根据权利要求1所述的成像设备,其中所述第一切换电路的第一端子耦接至所述第一比较器的所述输出端子;

其中所述第一切换电路的第二端子耦接至所述第一计数器的所述输入端子;

其中所述第二切换电路的第一端子耦接至所述第二比较器的所述输出端子;

其中所述第二切换电路的第二端子耦接至所述第二计数器的所述输入端子;

其中所述第三切换电路的第一端子耦接至所述第一比较器的所述输出端子;

其中所述第三切换电路的第二端子耦接至所述第二计数器的所述输入端子;

其中所述第四切换电路的第一端子耦接至所述第二比较器的所述输出端子;以及

其中所述第四切换电路的第二端子耦接至所述第一计数器的所述输入端子。

4.根据权利要求1所述的成像设备,其中所述第一比较器经由在第一方向上延伸的第一信号线耦接至所述第一像素单元;以及

其中所述第一比较器在垂直于所述第一方向的第二方向上与所述第二比较器相邻分布。

5.根据权利要求1所述的成像设备,其中所述第一像素单元包含多个光电二极管;以及其中所述多个光电二极管共享浮动扩散、放大晶体管以及选择晶体管中的至少一个。

6.根据权利要求1所述的成像设备,其中所述矩阵图案为Bayer图案。

7.一种成像设备,包括:

像素阵列,具有被配置为生成第一模拟信号的第一像素单元以及被配置为生成第二模拟信号的第二像素单元;

其中所述第一像素单元和所述第二像素单元中的每一个包含多个光电二极管,所述光

电二极管被配置为通过(i)被配置为透射红光的第一颜色滤色器、(ii)被配置为透射蓝光的第二颜色滤色器、(iii)被配置为透射绿光的第三颜色滤色器，或者(iv)被配置为透射红光、蓝光和绿光的第四颜色滤色器来接收光；

其中在所述第一像素单元中的所述多个光电二极管中的至少一个被配置为通过第四颜色滤色器接收光；

其中在所述第一像素单元中的所述多个光电二极管被配置为共享浮动扩散、放大晶体管以及选择晶体管中的至少一个；

参考信号发生器，配置为生成参考信号；

第一比较器，耦接至所述第一像素单元，并配置为将所述参考信号与所述第一模拟信号进行比较；

第二比较器，耦接至所述第二像素单元，并配置为将所述参考信号与所述第二模拟信号进行比较；

第一切换电路，耦接至所述第一比较器的输出端子和第一计数器的输入端子；

第二切换电路，耦接至所述第二比较器的输出端子和第二计数器的输入端子；

第三切换电路，耦接至所述第一比较器的输出端子和第二计数器的输入端子；以及

第四切换电路，耦接至所述第二比较器的输出端子和第一计数器的输入端子；

切换电路控制器，配置为以第一切换状态或第二切换状态控制所述第一、第二、第三以及第四切换电路；

其中在所述第一切换状态中，所述第一切换电路和所述第二切换电路被激活；以及

其中在所述第二切换状态中，所述第三切换电路和所述第四切换电路被激活。

8. 根据权利要求7所述的成像设备，其中所述第一切换电路的第一端子耦接至所述第一比较器的所述输出端子；

其中所述第一切换电路的第二端子耦接至所述第一计数器的所述输入端子；

其中所述第二切换电路的第一端子耦接至所述第二比较器的所述输出端子；

其中所述第二切换电路的第二端子耦接至所述第二计数器的所述输入端子；

其中所述第三切换电路的第一端子耦接至所述第一比较器的所述输出端子；

其中所述第三切换电路的第二端子耦接至所述第二计数器的所述输入端子；

其中所述第四切换电路的第一端子耦接至所述第二比较器的所述输出端子；以及

其中所述第四切换电路的第二端子耦接至所述第一计数器的所述输入端子。

9. 根据权利要求7所述的成像设备，其中所述第一比较器经由在第一方向上延伸的第一信号线耦接至所述第一像素单元；以及

其中所述第一比较器在垂直于所述第一方向的第二方向上与所述第二比较器相邻分布。

## 固态成像设备,控制固态成像设备的方法

[0001] 本申请是申请日为2012年9月20日、申请号为201210352684.2、发明名称“固态成像设备,控制固态成像设备的方法以及程序”的发明专利申请的分案申请。

### 技术领域

[0002] 本公开涉及包括像素阵列单元的固态成像设备、控制固态成像设备的方法,以及用于控制固态成像设备的程序,像素阵列单元具有以矩阵形式二维布置的多个像素和沿列方向布置的多个信号线,以及对应于每个信号线提供A/D(模拟/数字)转换单元,且该转换单元将通过信号线从像素输出的模拟信号转换为数字信号。

[0003] 固态成像设备中的像素相加(adding)方法被认为是在像素的浮动扩散部分(以下称为FD)上的累加和输出像素的电荷的FD相加方法、通过读出线同时地读取多个像素信号并且使用连接到读出信号线的负载MOS电路相加该像素信号的源跟随器(source follower)相加方法、使用列ADC电路中的计数器电路进行数字的相加(addition)的计数器相加方法,以及将多个电容器并联连接到列ADC电路中比较器的输入端以及相加多个垂直信号线的信号的容量相加方法。

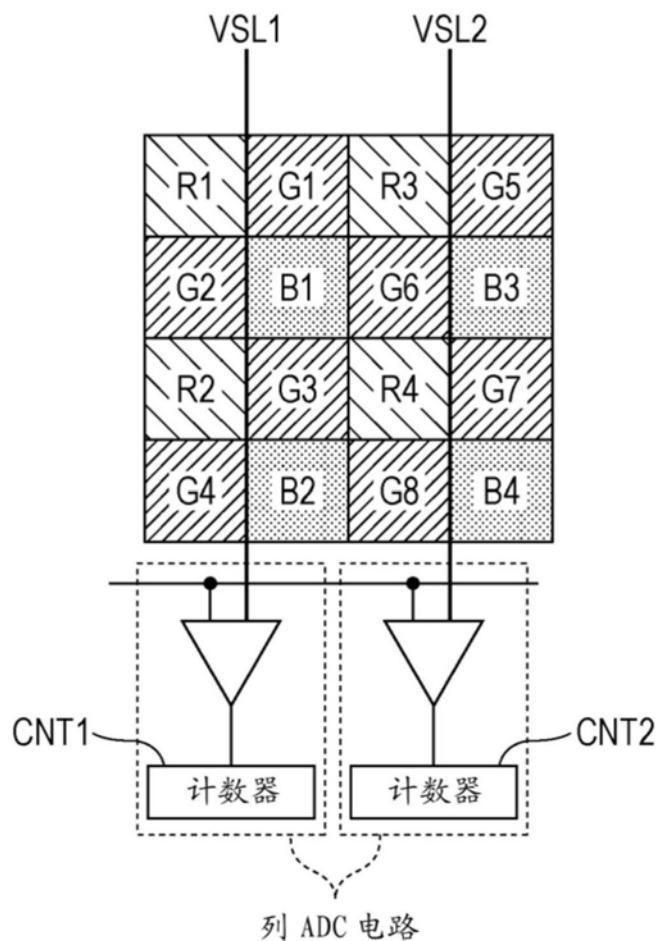

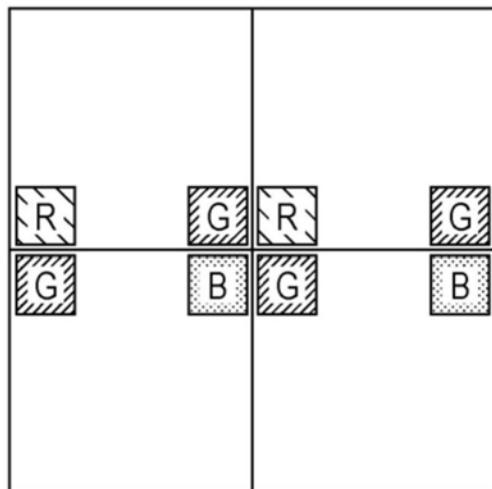

[0004] 将参照图29到图31B描述Bayer布置(Bayer arrangement)的抽取(decimation)读取中的像素相加。图29是说明当Bayer布置用作颜色滤色器阵列(color filter array)时使用列ADC电路进行的像素相加的例子的图。图30是图29中所示的列ADC电路中的像素相加时的时序图,并且图31A和图31B是当使用图29中所示的列ADC电路时的读出图像(reading image)。

[0005] 在图29中所示的Bayer布置中,用作亮度信号的主要分量的G滤色器(filter)在棋盘(checkerboard)形中以一个像素的间隔排布,R和B滤色器在棋盘形中以纵向和横向的一个像素的间距(pitch)排布在剩余的像素处,并且R和B滤色器排布为倾斜地偏离一个像素。图29所示的像素阵列由藉由通过浮动扩散部分(以下称为FD)连接垂直和水平2x2的四个像素而共享该FD的像素单元(以下称为FD共享像素单元)配置。

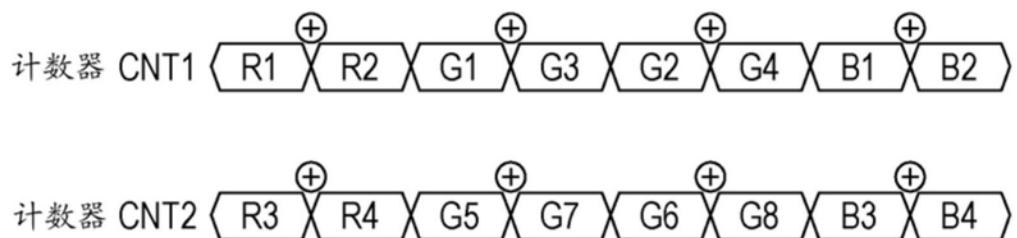

[0006] 在图29中所示的配置中,进行了相加和相加求平均,例如,作为R1和R2,G1和G3,G2和G4,B1和B2,R3和R4,G5和G7,G6和G8,以及B3和B4,共享相同的垂直信号线,相同颜色的像素顺序地输入到垂直方向的列ADC电路,使用每列的列ADC电路进行A/D转换,并且然后由计数器进行相加和相加求平均(例如,参见日本未经审查的专利申请公开No.2006-033454)。

[0007] 例如,如图30所示,首先,选择像素R1和像素R3,像素R1的像素信号输出到垂直信号线VSL1,且像素R3的像素信号输出到垂直信号线VSL2。然后选择像素R2和像素R4,像素R2的像素信号输出到垂直信号线VSL1,且像素R4的像素信号输出到垂直信号线VSL2。

[0008] 即,像素R1和R2的像素信号顺序地输出到垂直信号线VSL1,且像素R3和R4的像素信号顺序地输出到垂直信号线VSL2。因此,像素R1和R2的像素信号都由计数器CNT1计数,且像素R3和R4的像素信号都由计数器CNT2计数。

[0009] 类似地,剩余的像素被顺序地选择且输出到垂直信号线,且输出经受了计数器的计数相加的数字数据。

[0010] 图31A是在列ADC电路中相加的状态下的读出图像，并且从列ADC电路输出的图像对应于其中抽取一半垂直方向上的像素的数目下的状态。

[0011] 之后，从列ADC电路输出的像素的A/D转换值传送到后阶的逻辑信号处理电路，且在其中在水平的方向上进行相加和相加求平均。图31B是在逻辑信号处理电路中相加的状态下的读取图像，并且从逻辑信号处理电路输出的图像对应于其中在垂直和水平两者方向上的像素的数目被抽取一半的情况下下的状态。

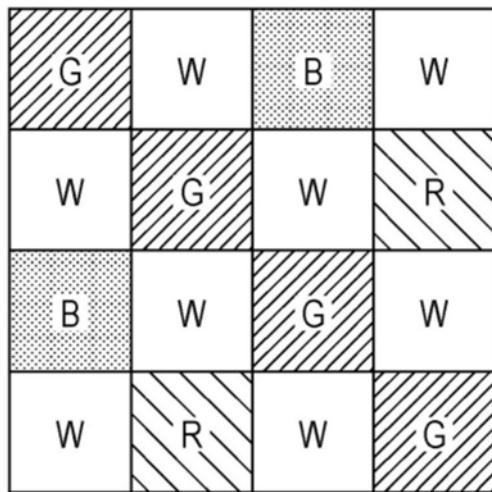

[0012] 近来，在固态成像设备中，作为亮度信号的主要分量的白色可以用在颜色滤色器阵列的颜色布置中（例如，参见日本未经检索的专利申请公开No. 2010-136226）。

[0013] 图32是包括白色的颜色滤色器阵列的颜色布置的例子。在图32所示的颜色布置中，白色的滤色器在棋盘形中以一个像素的间距排布，且RGB色滤色器均一地排布在剩余的像素处。更具体地，R和B滤色器以横向和纵向的两像素的间距布置在棋盘形中，R和B滤色器排布为倾斜地偏离一个像素，且剩余的像素为G滤色器。在这种情况下，G滤色器布置在斜带形中。

[0014] 在这样的颜色布置中，难以使用列ADC电路进行相加和相加求平均。因此，从列ADC电路输出的像素的A/D转换值传送到后阶的逻辑信号处理电路，在其中由计算处理进行垂直方向相加和相加求平均以及水平方向相加和相加求平均。

[0015] 在使用图29所示的颜色布置的同时当进行逻辑信号处理电路中的相加和相加求平均的抽取的处理时，4x4像素布置中的所有16个像素被选择，且使用对应于每个垂直信号线提供的列ADC电路进行AD转换从而进行相加和相加求平均。即，同样在抽取输出时，需要操作所有的ADC电路，且列ADC电路中的耗电量没有减少。

[0016] 需要将由AD转换获得的相加和相加求平均值传送到后阶的逻辑信号处理单元，并且需要在水平的方向上进行相加和相加求平均。因此后阶的逻辑信号处理单元必须配备用于处理接收的值的电路或线路存储器，而这引起电路规模、操作速度和耗电量中的任一项的增加。当然，逻辑信号处理单元中的这些缺点即使在上述图32中所示的包括白色滤色器阵列的颜色布置的情况下也是同样的。

[0017] 在上述相关的技术中在FD相加方法、源跟随器相加方法、计数器相加方法和容量相加方法中，当使用了图32中所示的颜色布置时，物理上难以使用连接到其它垂直信号线的像素中的相加和相加求平均进行抽取输出。在容量相加方法的情况下，有可能使用连接到相邻的垂直信号线的像素中的相加和相加求平均进行抽取输出，但不能进行替代其中没有进行抽取的输出方法。

## 发明内容

[0018] 期望提供一种固态成像设备，控制该固态成像设备的方法，以及用于控制该固态成像设备的程序，可以基于连接到其它的垂直信号线的像素中的相加和相加求平均进行抽取输出，而不增加电路规模、操作速度和耗电量。

[0019] 根据本公开的一个实施例，提供了一种固态成像设备，包括：像素阵列单元，其具有以矩阵形式二维布置的多个像素和沿列方向布置的多个信号线；A/D转换单元，对应于各自的信号线提供的且将通过信号线从像素输出的模拟信号转换为数字信号；以及切换单元，对下述通过每个信号线输出的模拟信号到数字信号的转换进行切换，该通过每个信号

线输出的模拟信号到数字信号的转换使用对应于传送模拟信号的信号线提供的A/D转换单元和对应于不是传送模拟信号的信号线的信号线而提供的A/D转换单元的任一个。

[0020] 如上所述的固态成像设备包括各种实施方式,例如,该固态成像设备实施为另一个装置中提供的固态成像设备,或由另一种方法而实施。本技术可以实现为配备有该固态成像设备的成像系统,具有对应于上述设备的配置的处理的方法,用于使得计算机执行对应于上述设备配置的功能的程序,在其中记录了该程序的计算机可读记录介质,以及制造该固态成像设备的方法。

[0021] 如上所述,根据本技术,有可能提供一种能够基于连接到其它的垂直信号线的像素中的相加和相加求平均进行抽取输出而不增加电路规模、操作速度和耗电量的固态成像设备。

## 附图说明

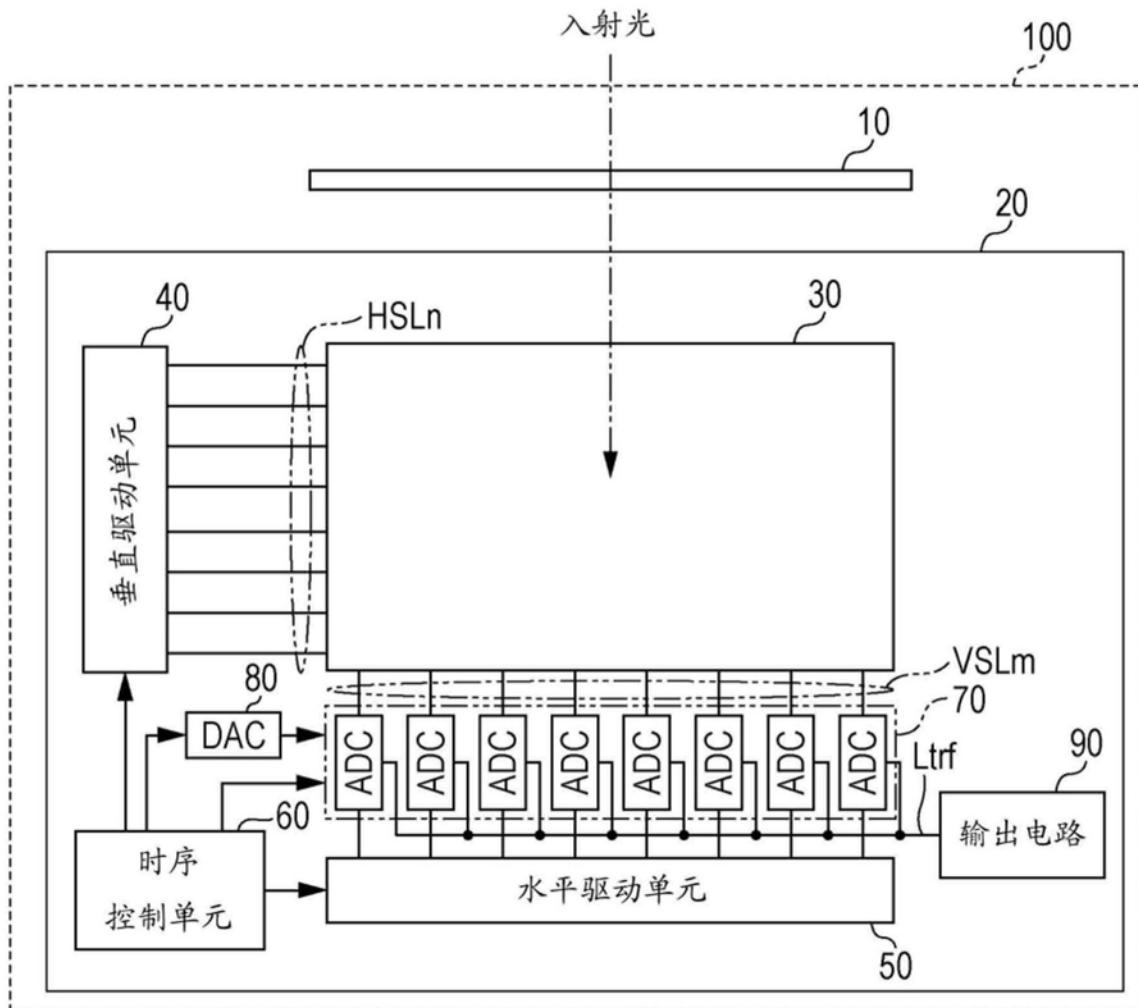

- [0022] 图1是说明固态成像设备的配置的框图。

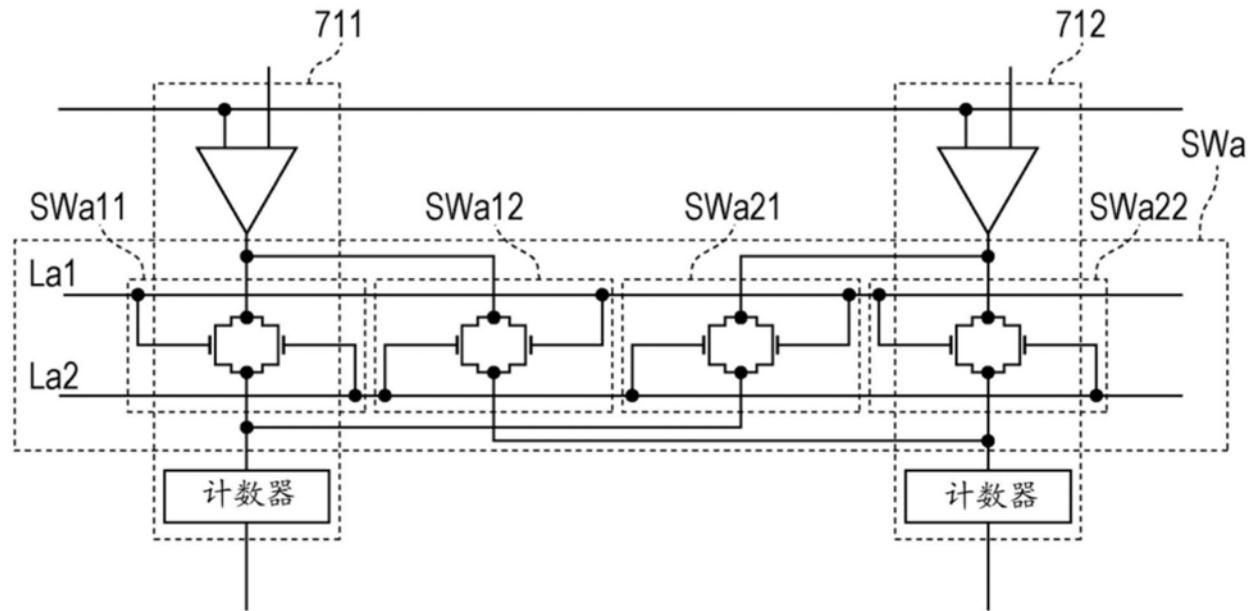

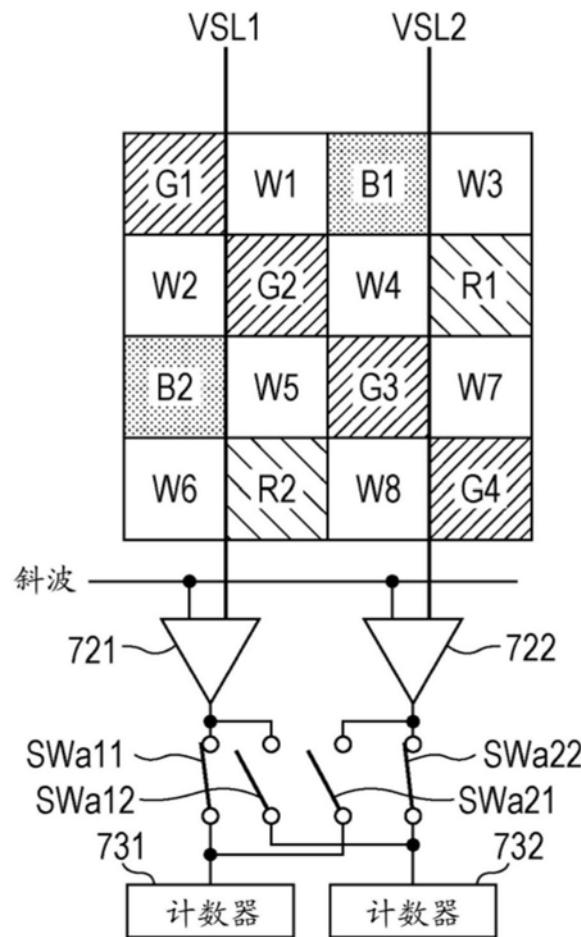

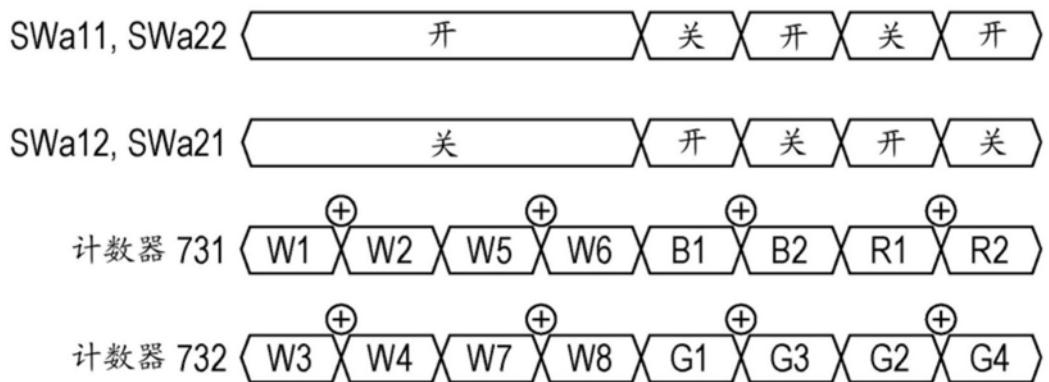

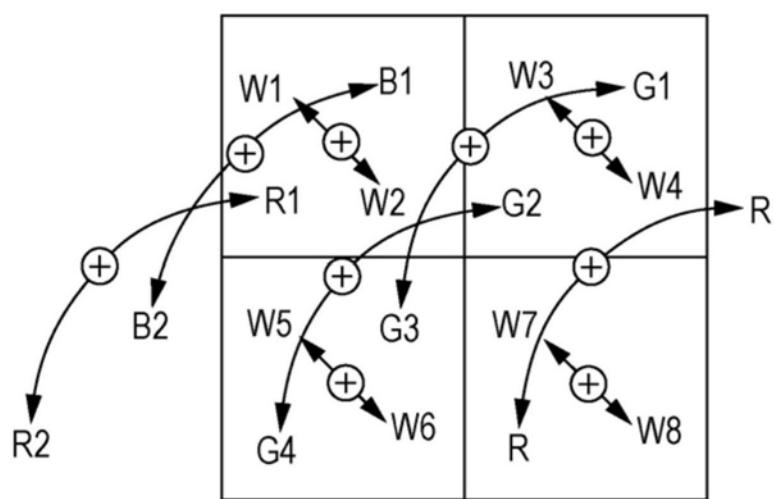

- [0023] 图2是说明根据第一实施例的列处理单元的图。

- [0024] 图3是说明根据第一实施例的开关(switch)的开/关的对应关系的表。

- [0025] 图4是说明在其中具体实现了根据第一实施例的开关的电路的例子的图。

- [0026] 图5是根据第一实施例的控制信号的真值表。

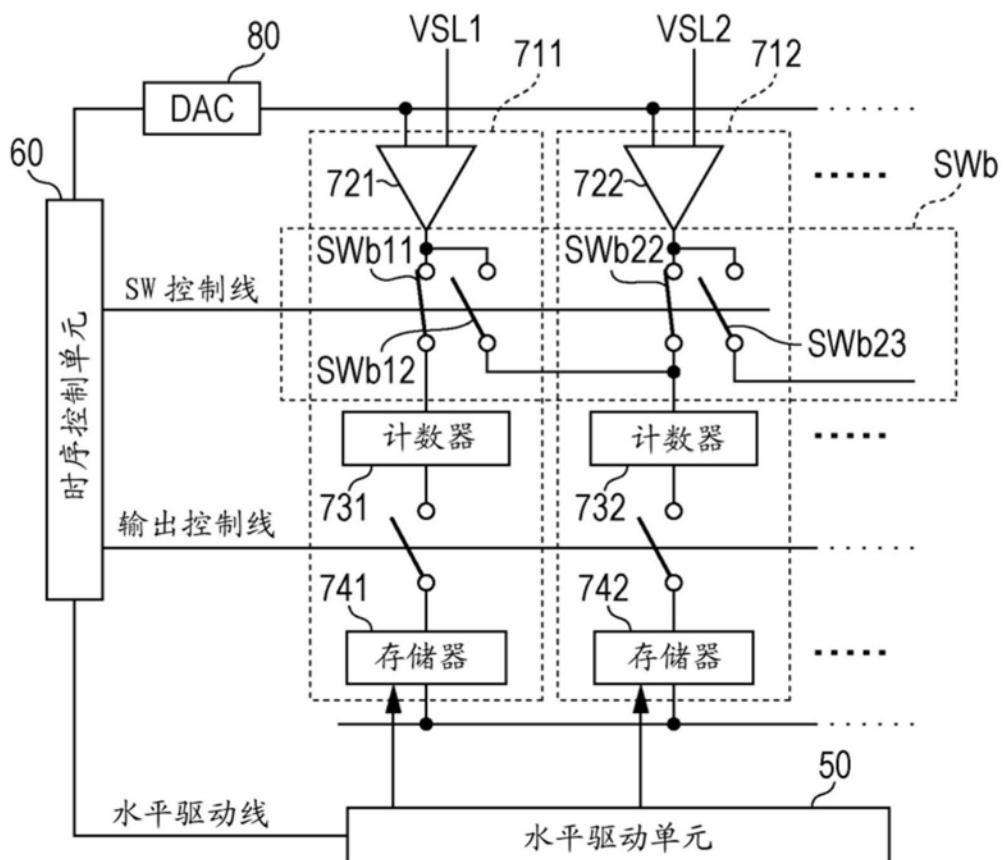

- [0027] 图6是说明根据第二实施例的列处理单元的图。

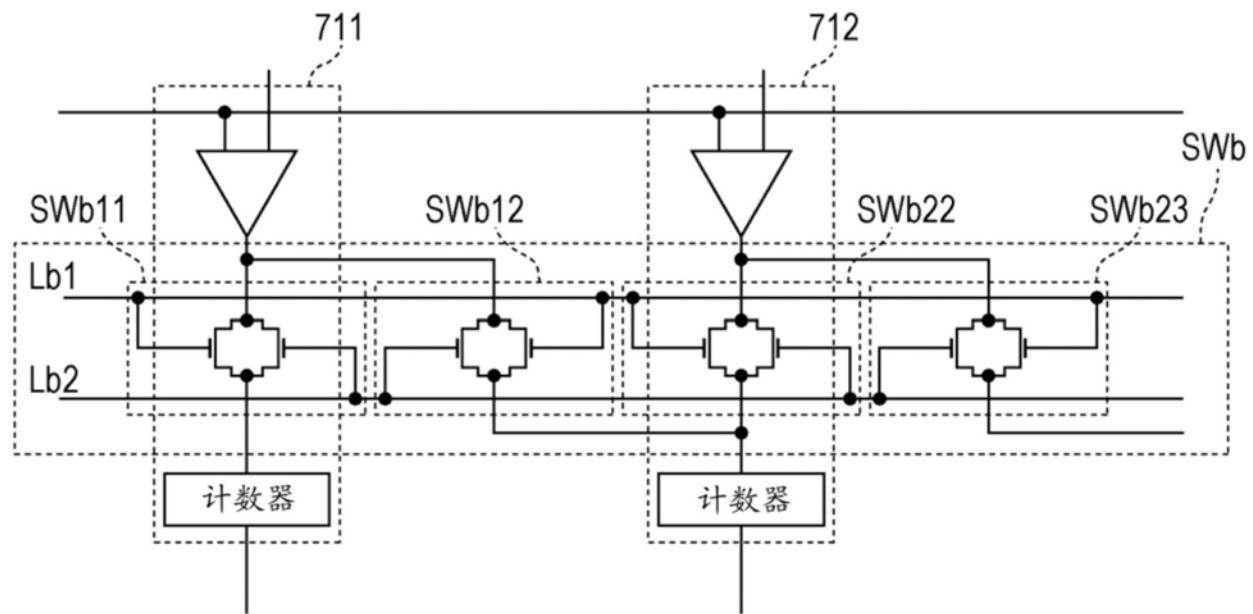

- [0028] 图7是说明根据第二实施例的开关的开/关的对应关系的表。

- [0029] 图8是说明在其中具体实现了根据第二实施例的开关的电路的例子的图。

- [0030] 图9是根据第二实施例的控制信号的真值表。

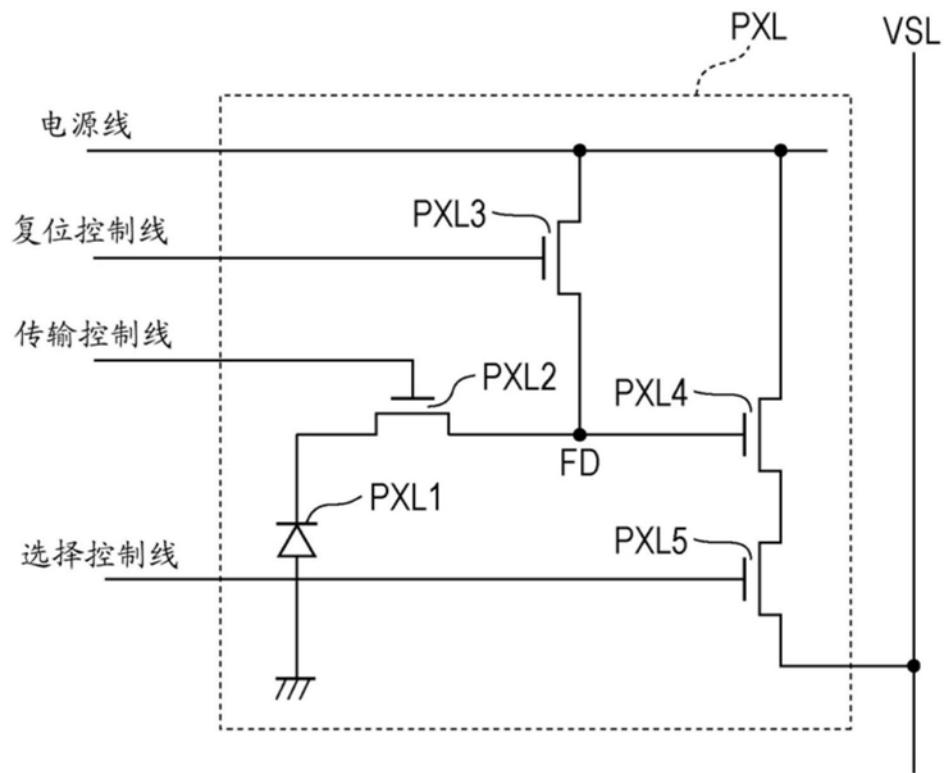

- [0031] 图10是说明COMS图像传感器的基本像素电路的例子的电路图。

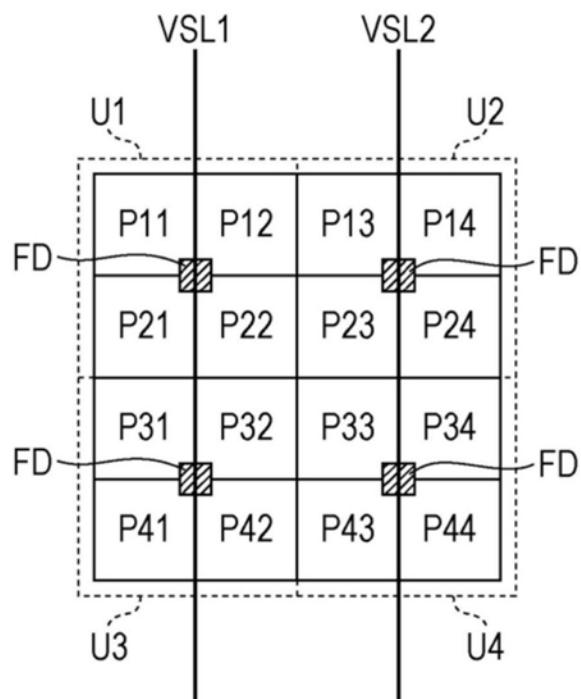

- [0032] 图11是说明FD共享像素单元的图。

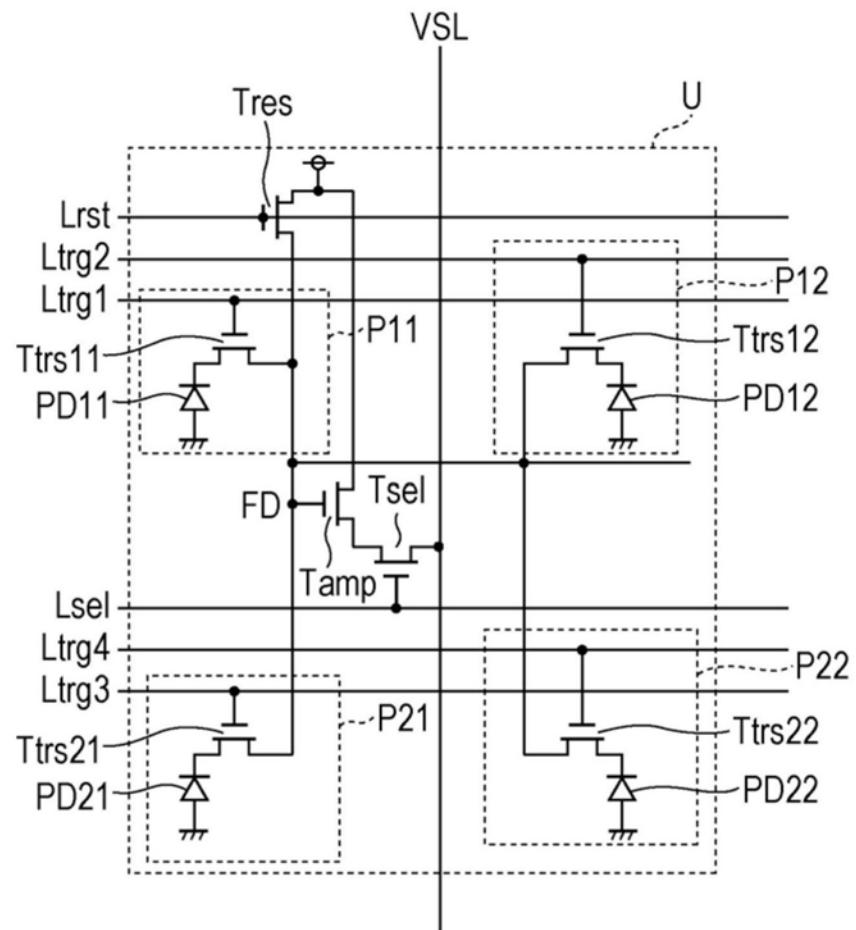

- [0033] 图12是说明FD共享像素单元的电路配置的例子的电路图。

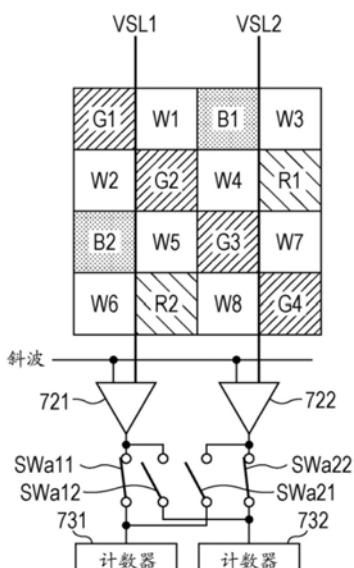

- [0034] 图13是说明根据第一实施例的颜色滤色器阵列和列处理单元的配置的图。

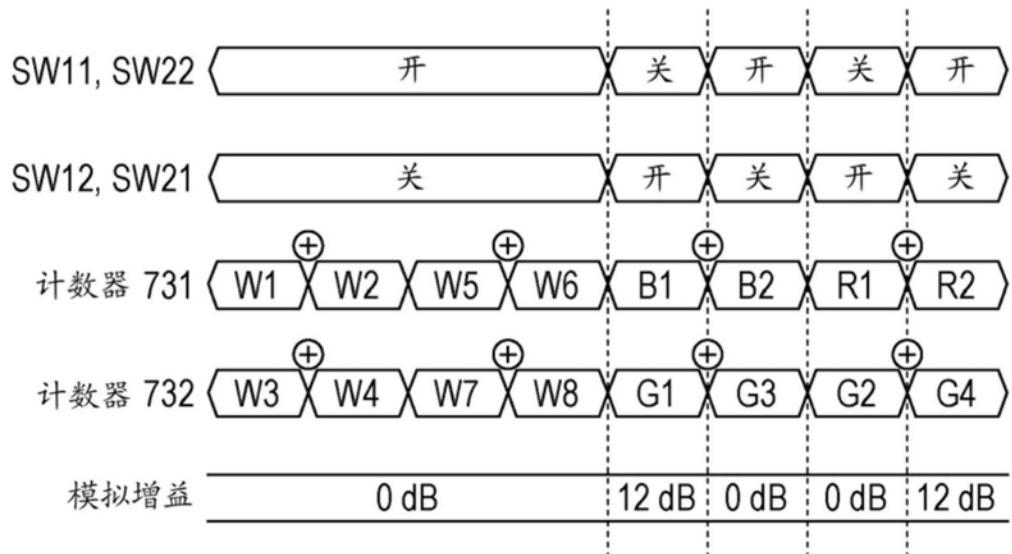

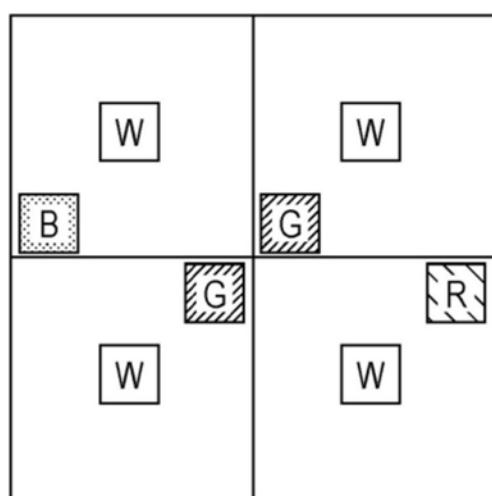

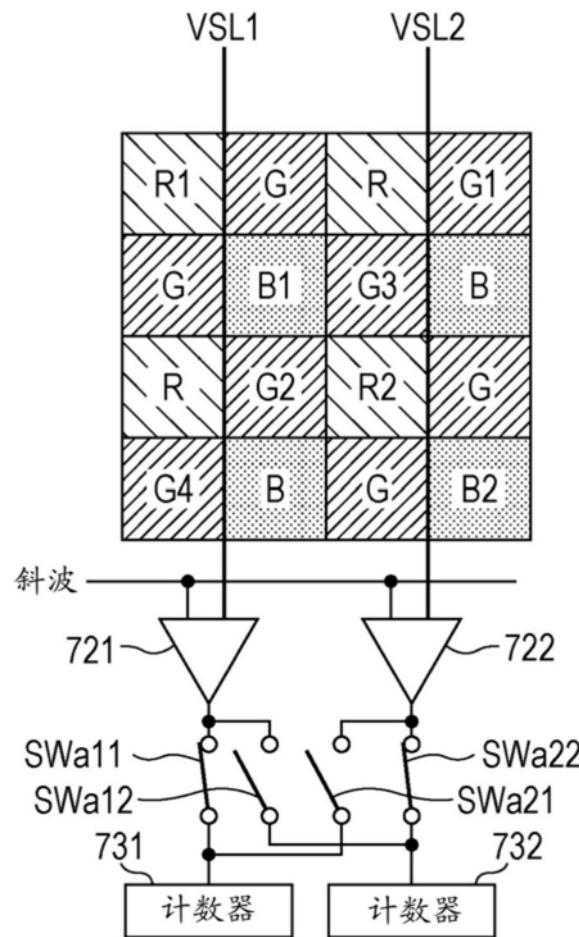

- [0035] 图14是根据第一实施例的相加操作的时序图。

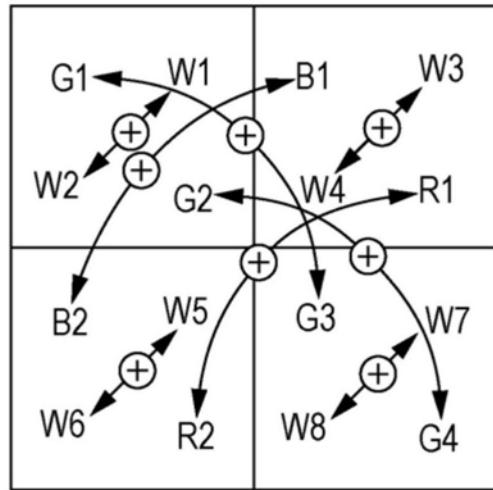

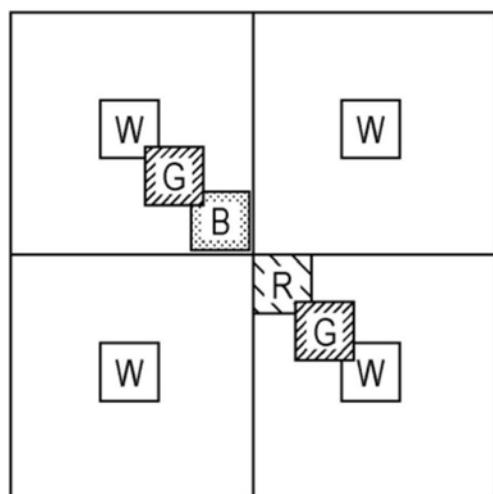

- [0036] 图15A和图15B是说明参照图13和图14描述的相加操作中的读出图像的图。

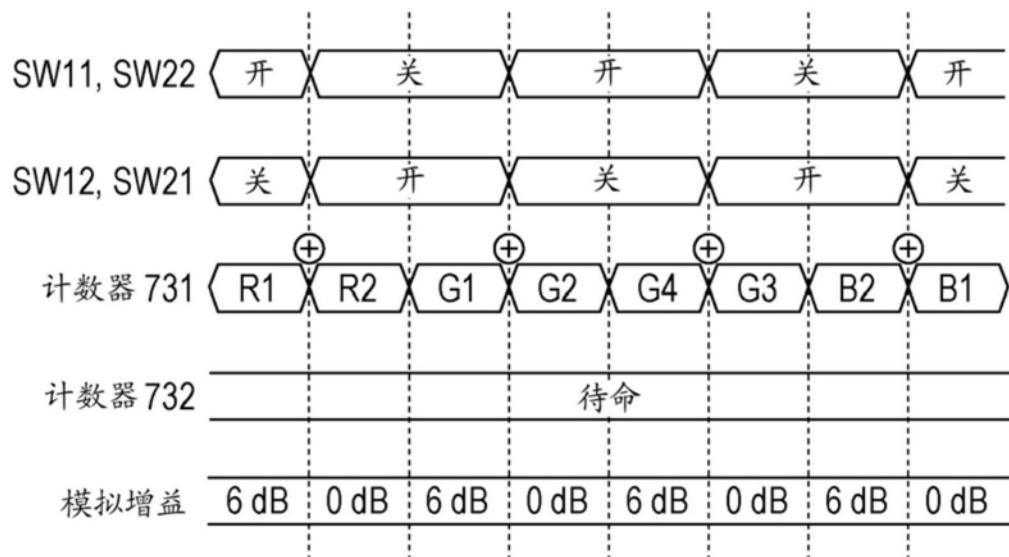

- [0037] 图16是说明在调整增益的同时进行的第一实施例的相加操作的时序图。

- [0038] 图17是说明作为图16所示的增益调整的结果而获得的读出图像的图。

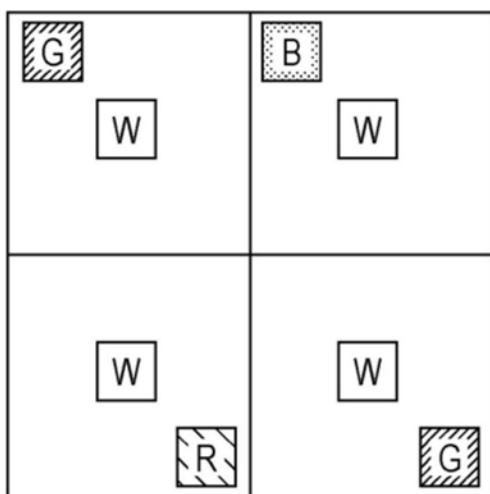

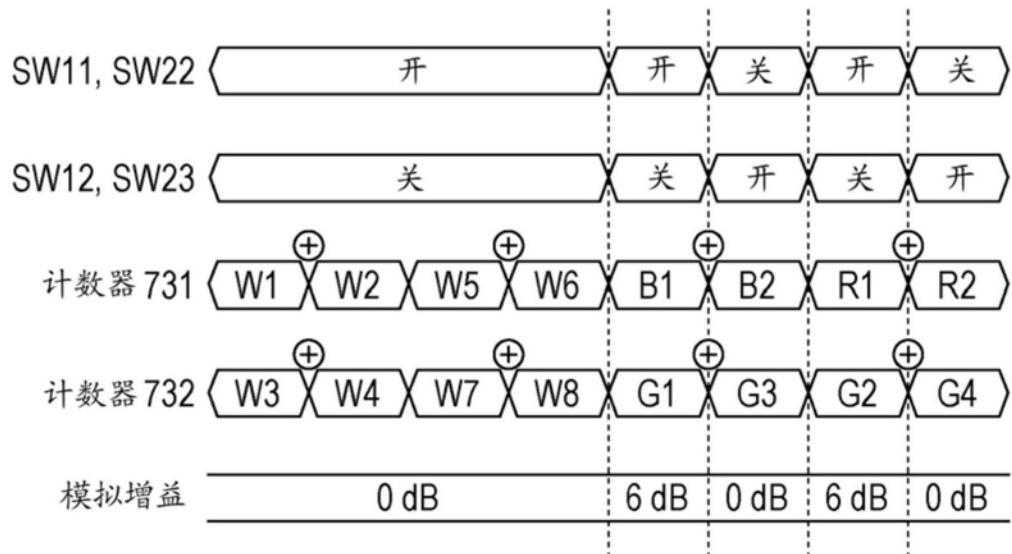

- [0039] 图18是说明根据第二实施例的颜色滤色器阵列和列处理单元的配置的图。

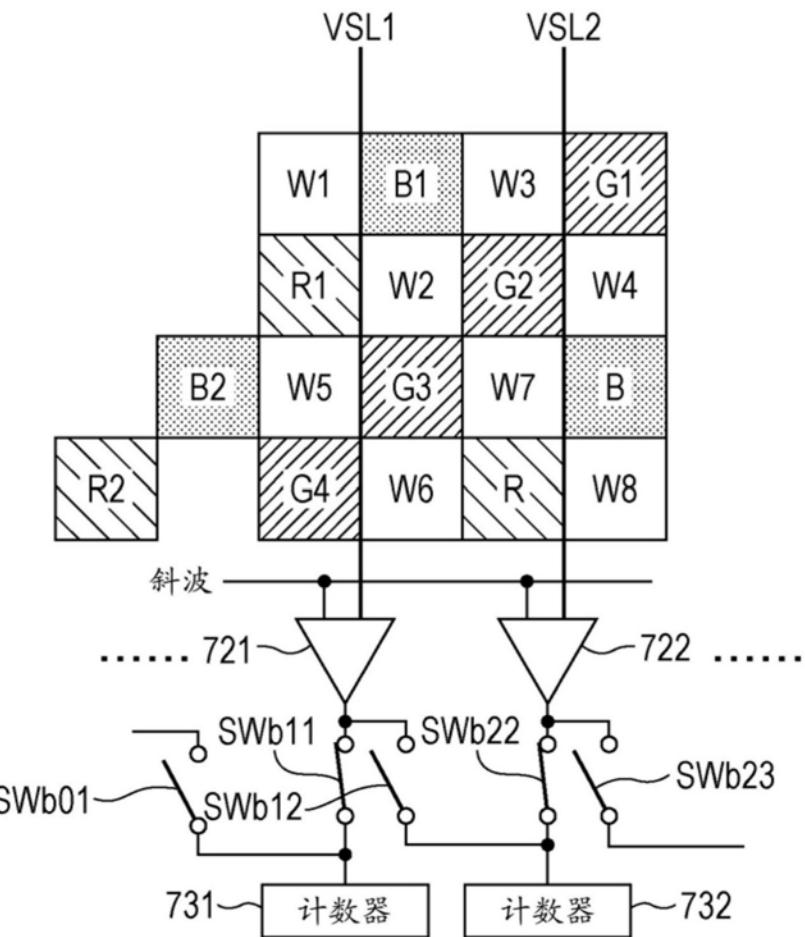

- [0040] 图19是根据第二实施例的相加操作的时序图。

- [0041] 图20A和图20B是说明参照图18和图19描述的相加操作中的读出图像图。

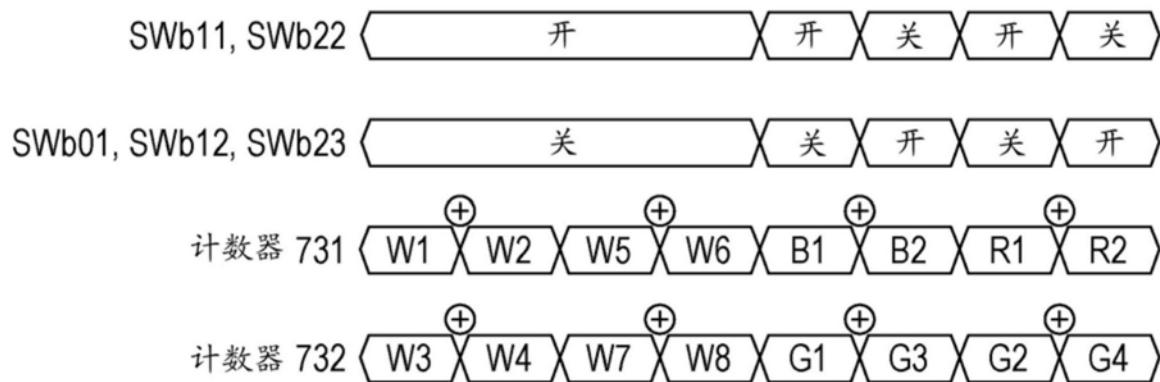

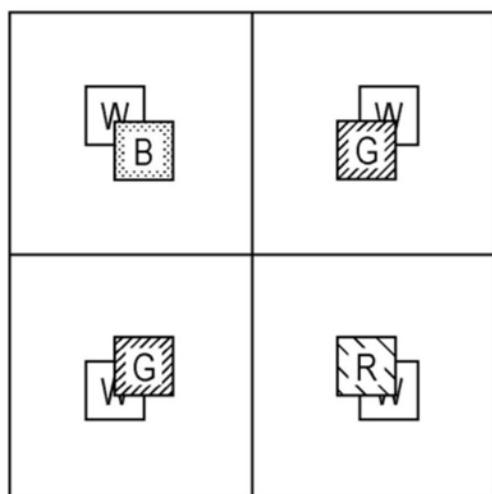

- [0042] 图21是说明当调整增益时进行的第二实施例的相加操作的时序图。

- [0043] 图22是说明作为图21所示的增益调整的结果而获得的读出图像的图。

- [0044] 图23是说明根据第三实施例的颜色滤色器阵列和列处理单元的配置的图。

- [0045] 图24是根据第三实施例的相加操作的时序图。

- [0046] 图25A和25B是说明参照图23和图24描述的相加操作中的读出图像的图。

- [0047] 图26是说明当调整增益时进行的第三实施例的相加操作的时序图。

- [0048] 图27是说明作为图26所示的增益调整的结果而获得的读出图像的图。

- [0049] 图28是说明根据第三修改示例的连接关系的图。

- [0050] 图29是说明当用Bayer布置作为颜色滤色器阵列时,使用列ADC电路进行的像素相加的例子的图。

- [0051] 图30是图29中所示的列ADC电路中的电路相加时的时序图。

- [0052] 图31A和图31B是当使用图29中所示的列ADC电路时的读出图像。

- [0053] 图32是包括白色的颜色滤色器的颜色布置的例子。

## 具体实施方式

- [0054] 以下,将以如下的顺序描述本技术的实施例

- [0055] (1) 固态成像设备的配置

- [0056] (2) 像素相加的第一实施例

- [0057] (3) 像素相加的第二实施例

- [0058] (4) 像素相加的第三实施例

- [0059] (5) 各种修改示例

- [0060] (1) 固态成像设备的配置

- [0061] 图1是说明固态成像设备的配置的框图。在实施例中,将描述作为成像设备的例子的、是一种X-Y地址型固态成像设备的CMOS图像传感器。

- [0062] 以下,将描述NMOS被用于CMOS图像传感器的所有像素中,但是这是一个例子,作为本技术的对象的设备不限于MOS型固态成像设备。例如,相对于从外部输入的电磁波(诸如光和辐射)具有感受性(sensitivity)的多个单元组成元件以线状或矩阵形式布置,并且所有的实施例类似地适用于用于检测物理分布从而由地址控制读取信号的所有半导体设备。

- [0063] 固态成像设备100具有像素单元,其中包括输出与入射光量对应的信号的光接收元件的多个像素被二维地排布在矩阵中,从每个像素输出的信号是电压信号,以及固态成像设备100具有以线平行提供的AD转换单元(ADC:模拟数字转换器)。

- [0064] 于此,线平行意味着与组成图像传感器的像素的垂直列平行分布的、数目与垂直信号线(列信号线的例子)的数目相同的AD转换单元排布为一一对应于垂直信号线,并且一个AD转换单元对应于一个线(一个垂直信号线)。

- [0065] 作为在其中以线平行提供ADC电路的例子,有列类型,其中在成像单元的输出侧上配备的称为列区域的部分为每个垂直信号线提供模拟信号处理单元或ADC电路,并且在输出侧顺序地读取信号。

- [0066] 本公开不限于列类型(线平行类型),并且可以使用分配一个ADC电路给多个(例如两个)相邻的垂直信号线的类型,或者分配一个ADC电路给N个间隔的N个(N是整数:之间排布有N-1个垂直信号线)垂直信号线的类型。

- [0067] 即使在除了列类型的其它类型中,多个垂直信号线共享一个ADC电路,并且因此提供切换电路(switch circuit),其向一个ADC电路提供与从像素阵列单元30提供的多个列对应的多个像素信号。根据后阶的处理,单独的对策是有必要的,例如,提供了用于存储输出信号的存储器。

- [0068] 从电路规模、处理速度(高速)以及分辨率的观点来看各种AD转换方法是有可以想到的,例如,有斜积分(slope integration)类型或斜波信号(rampsignal)比较类型(以下,

在说明书中,称为参考信号比较类型)。

[0069] 在参考信号比较类型中,作为AD转换的对象的模拟信号与斜波形(ramp-shaped)的参考信号(斜波)进行比较,斜波形的参考信号的值逐渐改变,且基于通过对比较处理的持续时间计数获得的计数值而获取作为AD转换的对象的模拟信号的数字值。在本实施例中,有斜波信号比较类型AD转换方法。

[0070] 当使用参考信号比较类型AD转换方法,可以想到提供多个参考信号产生单元。例如,可以提供向垂直信号线中的奇数编号的列提供参考信号的参考信号产生单元,以及向偶数编号的列提供参考信号的参考信号产生单元,或可以以线平行方式(对于每个信号线)提供参考信号产生单元。

[0071] 然而,当提供多个参考信号产生单元时,电路规模或耗电量增加。在本实施例中,关于所有的列共同配备参考信号产生单元,且对应于每个垂直信号线提供的列类型ADC电路共同使用从参考信号产生单元产生的参考信号。

[0072] 以下,将参照图1描述固态成像设备的一个特定的例子。如图1所示,固态成像设备100包括颜色滤色器阵列10和半导体衬底20。

[0073] 半导体衬底20配备有像素阵列单元30、垂直驱动单元40、水平驱动单元50、时序控制单元60、列处理单元70、参考信号产生单元80以及输出电路90。如果必要,可以在输出电路90的前端提供数字操作单元。例如,当通过相加和相加求平均进行水平方向或垂直方向上的抽取像素信号的处理时,提供数字操作单元。

[0074] 像素阵列单元30配备有颜色滤色器阵列10,其中对应于光接收面侧的像素将滤色器的颜色分类,并且包括作为光电转换元件的光电二极管的像素PXL布置在矩阵中。稍后将详细描述颜色滤色器阵列10的像素PXL和颜色布置的具体的电路配置。

[0075] 像素阵列单元30配备有n个像素驱动线HSLn(n是等于或大于2的整数)以及m个垂直信号线VSLm(m是等于或大于2的整数)。像素驱动线HSLn沿图的左和右的方向(像素行的像素布置方向,和水平方向)以相同距离排布,垂直信号线VSLm沿图的上和下的方向(像素列的像素布置方向,和垂直方向)以相同距离排布。

[0076] 像素驱动线HSLn的一端连接到与垂直驱动单元40的每行对应的输出端子。垂直信号线VSLm的一端连接到列处理单元70中的与每个垂直信号线VSLm对应的ADC电路。此外,将用稍后要描述的单元像素的描述来描述像素驱动线HSLn和垂直信号线VSLm的具体排布。

[0077] 在像素阵列单元30的外部提供包括垂直驱动单元40、水平驱动单元50、时序控制单元60等的驱动控制单元,且驱动控制单元进行从组成像素阵列单元30的像素顺序地读出信号的控制。

[0078] 时序控制单元60包括时序产生器和通信接口。时序产生器基于从外部输入的时钟(主时钟)产生各种时钟信号。通信接口接收从半导体衬底20的外部给出的指示操作模式的数据,并且输出包括固态成像设备100的内部信息的数据。

[0079] 时序控制单元60产生与主时钟的频率相同频率的时钟,由将其二分频而形成的时钟,以及通过进一步分频而形成的低速时钟,并将所述时钟提供给例如垂直驱动单元40、水平驱动单元50和列处理单元70。

[0080] 垂直驱动单元40由移位寄存器或地址解码器形成,并且配备有用于控制行地址的垂直地址设置单元或用于控制行扫描的行扫描控制单元。垂直驱动单元40可以进行读出扫

描或冲洗扫描 (flushing scanning)。

[0081] 读出扫描是顺序地选择单元像素读出信号的扫描。这个扫描基本上以行为单位顺序地进行的。然而,当处于预定位置关系中的多个像素的输出经受相加或相加求平均从而进行像素的抽取时,该扫描以稍后要描述的预定顺序进行。

[0082] 冲洗扫描对于其中在读出扫描中进行读取的行或像素组合在读出扫描之前快门速度的时间进行,并且是为了复位 (reset) 属于该进行读出的行或像素组合的单元像素。

[0083] 水平驱动单元50通过与来自时序控制单元60的时钟输出同步而顺序选择列处理单元70的ADC电路,并且将信号引导到水平信号线(水平输出线)Ltrf。

[0084] 水平驱动单元50配备有:水平地址设置单元,其规定 (regulate) (选择列处理单元70中的个体ADC电路) 水平方向上的读出列;以及水平扫描单元,其根据在水平地址设置单元中规定的读出地址将列处理单元70的信号引导到水平信号线Ltrf。

[0085] 由水平扫描单元的选择性扫描、使用组成列处理单元70的ADC电路信号-处理的像素通过水平信号线Ltrf顺序地输出到输出电路90。

[0086] 参考信号产生单元80配备有DAC(数模转换器),从时序控制单元60提供的初始值起与从时序控制单元60提供的计数时钟同步,产生随时间变化的阶梯的锯齿形波(斜波波形),并且将该信号作为参考信号提供给列处理单元的个体ADC电路。以下,参考信号产生单元80可以被称为DAC80。

[0087] 参考信号产生单元80调整计数时钟的周期。因此,当使用在其中可以调整参考信号的斜率的时钟,例如,相对于参考时钟被 $1/m$ 分频的时钟时,可能使斜率为 $1/m$ 。在这种情况下,当提供给包括在ADC电路中稍后描述的计数器的计数时钟是作为参考时,则计数值是 $m$ 倍。即,通过调整计数时钟的周期,有可能调整稍后描述的计数器中的计数值。

[0088] 例如,当如稍后将要描述ADC电路中顺序地计数两个像素的模拟值时,可以通过加倍AD转换的范围从而进行产生的计数值上两个像素的相加求平均而可以实现。当使用了参考信号产生单元80的参考信号时,例如,可能通过使参考信号的斜率为普通时钟的两倍而加倍AD转换的范围。

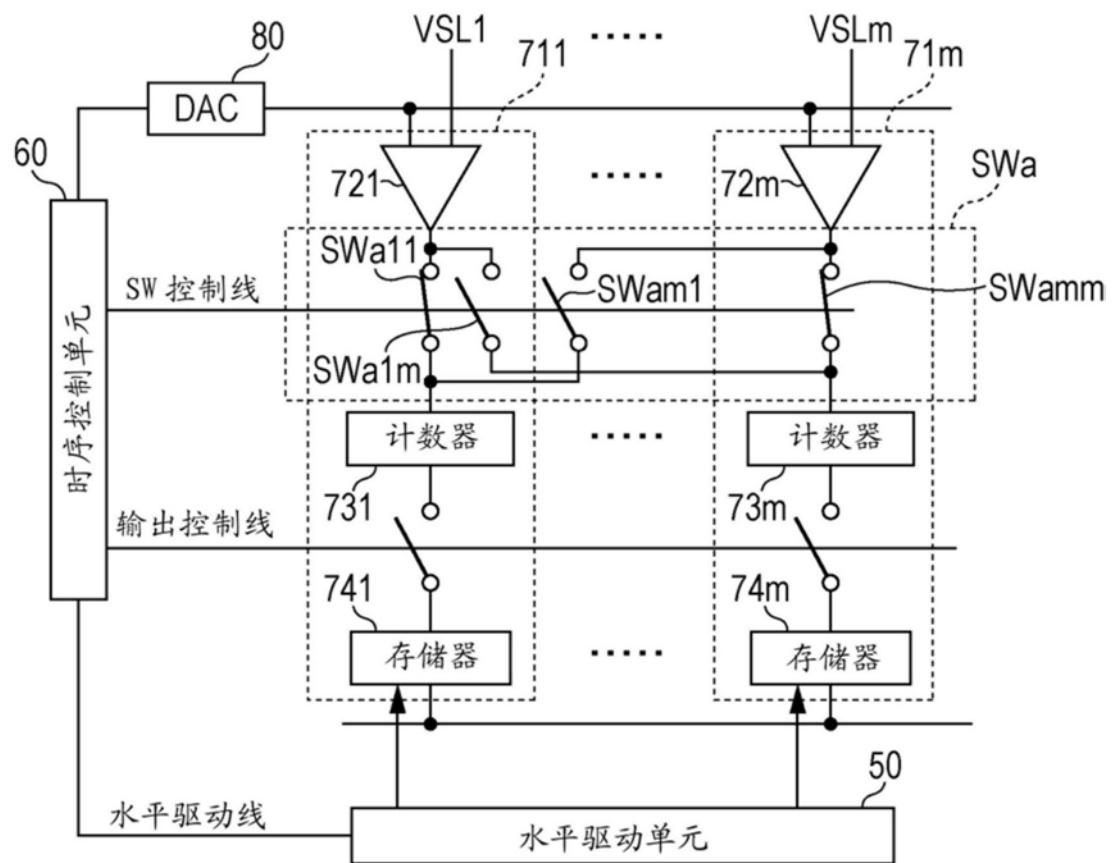

[0089] 列处理单元70配备有提供给每个垂直信号线VSLm的ADC电路71m( $m$ 是等于或大于2的整数),将从垂直信号线VSLm输出的模拟信号转换为数字信号,并且根据水平驱动单元50的控制将该数字信号输出到水平信号线Ltrf。以下,当没有将对应于 $m$ 的参考标记附加到ADC电路71m或内部配置(比较器72m、计数器73m和存储器74m)而进行描述时,该描述在ADC电路中是通用的。

[0090] 在实施例中,如图2和图6所示,ADC电路71包括比较器72、计数器73和存储器74。ADC电路71是A/D转换单元的一个例子。

[0091] 比较器72接收由参考信号产生单元80产生的参考信号和通过垂直信号线从像素输出的模拟像素信号,并且比较参考信号和像素信号。比较器72根据参考信号和像素信号之间的大小关系输出高电平信号或低电平信号。当参考信号和像素信号之间的大小关系改变时,输出在高电平和低电平之间反转。

[0092] 从时序控制单元60向计数器73提供时钟,并且计数器对从AD转换开始到结束的时间(计数操作有效时段)计数。可以基于参考信号改变的开始定时或比较器72的反转输出,指定AD转换的开始和结束的时机。其理由是因为比较器72的输出反转对应于参考信号和像

素信号的比较开始或比较结束。

[0093] 由计数器73产生的计数值是数字值,并且是与通过垂直信号线VSLm从像素输入到列处理单元70的模拟像素信号对应的数字数据。计数器73产生的数据存储(锁存)在存储器74中。

[0094] 当使用复位分量产生计数值时,例如计数器73根据时序控制单元60的控制在对应于复位分量的模拟信号从垂直信号线VSLm输出的同时进行下计数操作,以及在对应于信号分量的模拟信号从垂直信号线输出的同时进行与复位分量的情况相反的上计数操作。如上述而产生的计数值是与信号分量和复位分量之间的差对应的数字值,并且是由复位分量校正的信号分量。

[0095] 输出电路90通过计算处理进行将从像素阵列单元30输出到列处理单元70且对应于颜色滤色器阵列10的颜色布置的信号转换为颜色布置的处理。

[0096] 图2是说明根据第一实施例的列处理单元70的图。在图2中,为了描述的简化,示出两个垂直信号线,并且还示出包括在列处理单元70中的两个ADC电路。

[0097] 在图2中,列处理单元70包括ADC电路711和712,以及切换电路Swa。ADC电路71配备有计较器72、计数器73以及存储器74。ADC电路71中配备的计较器72和计数器73通过切换电路Swa连接。计较器、计数器和存储器的功能如上所述。

[0098] 切换电路Swa配备有开关Swa11、Swa12、Swa21和Swa22。计较器721和计数器731通过开关Swa11连接,且计较器722和计数器732通过开关Swa22连接。计较器721和计数器732通过开关Swa12连接,且计较器722和计数器731通过开关Swa21连接。

[0099] 即,切换电路Swa包括连接对应于相同的垂直信号线提供的计较器和计数器的开关,以及连接对应于一组两个相邻的垂直信号线中一个提供的计较器和对应于该组中另一个垂直信号线提供的计数器的开关。

[0100] 由通过两种类型的开关的连接,有可能使用相邻的垂直信号线的组中对应于一个垂直信号线提供的计数器和对应于另一个垂直信号线提供的计数器中的任一个进行选择性的计数。

[0101] 具体地,当开关Swa11接通时,有可能通过计数器731数字-转换并存储连接到垂直信号线VSL1的像素的模拟信号,并且当开关Swa12接通时,有可能由计数器732数字-转换并存储连接到垂直线VSL1的像素的模拟信号。

[0102] 当开关Swa22接通时,有可能通过计数器732数字-转换并存储连接到垂直信号线VSL2的像素的模拟信号,并且当开关Swa21接通时,有可能由计数器731数字-转换并存储连接到垂直线VSL2的像素的模拟信号。

[0103] 通过由相加累加当开关Swa11接通时的计数和当开关Swa21接通时的计数,有可能使计数器731产生通过累加连接到垂直信号线VSL1的像素的像素值和连接到垂直信号线VSL2的像素的像素值形成的数字数据。

[0104] 类似地,通过由相加累加当开关Swa22接通时的计数和当开关Swa12接通时的计数,有可能使计数器732产生通过累加连接到垂直信号线VSL1的像素的像素值和连接到垂直接口线VSL2的像素的像素值形成的数字数据。

[0105] 可以在对一个像素信号的计数完成后,通过使用根据该一个像素信号的计数值作为另一个像素信号的计数的初始值继续计数而实现计数器相加。

[0106] 根据由时序控制单元60(切换控制单元)通过SW控制线进行的控制进行开关Swa11、Swa12、Swa21和Swa22的开/关控制。图3是说明开关Swa11、Swa12、Swa21和Swa22的开/关对应关系的表。

[0107] 如图3所示,开关Swa11和开关Swa12选择性地接通,且开关Swa22和开关Swa21选择性地接通。同时,开关Swa11的开/关和开关Swa22的开/关互相联系,并且开关Swa12的开/关和开关Swa21的开/关也互相联系。

[0108] 以下,如上所述如此连接使得输出在对应于一组相邻垂直信号线的ADC电路之间可切换的列处理单元70可以被称为“交叉连接型列处理单元”。

[0109] 如上所述,通过由开关合适地选择负责AD转换的计数器,有可能由一个计数器产生通过累加连接到相邻垂直信号线的组的像素的像素值形成的数字数据。

[0110] 切换电路Swa作为列处理单元70的部分形成,并且排布在列部分(像素阵列的外部)。即,切换电路Swa的排布并没有被特别地限制,并且有根据像素布置对应于各种组合的优点。作为只可以取高和低中的一个的比较器输出的数字值的输入目的地被切换,且因此容易治理(case)在切换时的噪音。

[0111] 图4是说明其中具体实现了开关Swa11、Swa12、Swa21和Swa22的例子的图。图4所示的开关具有其中组合了NMOS晶体管和PMOS晶体管的互补开关的配置。

[0112] 由通过两个控制线La1和La2传送的控制信号控制互补开关。以下,通过控制线La1传送的控制信号被称为CROSS,且通过控制线La2传送的控制信号被称为XCROSS。

[0113] 互补开关是包括两个互补型MOS场效应晶体管的模拟开关,且是这样的模拟开关:其中源-漏电路并联排布在开关的输入端子和输出端子之间,用于控制开关的控制信号可以直接施加到一个沟道MOS场效应晶体管的栅极,并且可以通过反相器施加到另一个沟道MOS场效应晶体管的栅极。

[0114] 控制信号CROSS和XCROSS是在其中正性和负性彼此逻辑反相的信号,并且根据信号的状态,对应于一个垂直信号提供的比较器的输出可以输入到对应于同一个垂直信号线提供的计数器,或可以输入到对应于另一个垂直信号线提供的计数器。

[0115] 图5是控制信号XCROSS和CROSS的真值表。

[0116] 如图5所示,当通过控制线La1传送的控制信号XCROSS是正逻辑(高)且通过控制线La2传送的控制信号CROSS是负逻辑(低)时,开关Swa11和Swa22接通,且开关Swa12和开关Swa21断开。

[0117] 在这种情况下,对应于一个垂直信号线提供的比较器的输出输入到对应于同一个垂直信号线提供的计数器。即,从一个垂直信号线输出的模拟像素信号转换为作为对应于同一个垂直信号线提供的计数器中的计数值的数字数据。

[0118] 同时,当通过控制线La1传送的控制信号XCROSS是负逻辑且通过控制线La2传送的控制信号CROSS是正逻辑时,开关Swa11和Swa22断开,且开关Swa12和Swa21接通。

[0119] 在这种情况下,对应于一个垂直信号线提供的比较器的输出输入到对应于另一个垂直信号线提供的计数器。即,从一个垂直信号线输出的模拟像素信号转换为作为对应于另一个垂直信号线提供的计数器中的计数值的数字数据。

[0120] 根据上述互补开关,有可能通过PMOS场效应晶体管和NMOS场效应晶体管的组合以简单的配置实现切换电路。在制造CMOSLSI的过程中,有可能安装(mount)切换电路。

[0121] 图6是说明根据第二实施例的列处理单元70的图。在图6中,为了描述的简化,示出两个垂直信号线,并且还示出包括在列处理单元70中的两个ADC电路。

[0122] 在图6中,列处理单元70包括ADC电路711和712,以及切换电路Swb。ADC电路71配备有比较器72、计数器73以及存储器74。ADC电路71中配备的比较器72和计数器73通过切换电路Swb连接。比较器、计数器和存储器的功能如上所述。

[0123] 切换电路Swa配备有开关Swb11、Swb12、Swb22和Swb23。比较器721和计数器731通过开关Swb11连接,且比较器722和计数器732通过开关Swb22连接。比较器721和计数器732通过开关Swb12连接,且比较器722和ADC电路713(未示出)中的计数器733通过开关Swb23连接。

[0124] 即,切换电路Swb包括连接对应于一个垂直信号线提供的比较器和对应于邻近一个垂直信号线一侧的垂直信号线提供的计数器。这里所述的一侧是例如,图6中的右侧,并且是在一个固态成像设备中提供的所有垂直信号线的同侧。

[0125] 由此,有可能选择对应于垂直信号线提供的计数器和对应于提供为邻近该垂直信号线一侧提供的计数器中的任一个,并且进行计数。

[0126] 这里,当开关Swb11接通时,有可能由计数器731数字-转换并存储连接到垂直信号线VSL1的像素的模拟信号,并且当开关Swb12接通时,有可能由计数器732数字-转换并存储连接到垂直线VSL1的像素的模拟信号。

[0127] 当开关Swb22接通时,有可能由计数器732数字-转换并存储连接到垂直信号线VSL2的像素的模拟信号,并且当开关Swb23接通时,有可能由计数器733(未示出)数字-转换并存储连接到垂直线VSL3(未示出)的像素的模拟信号。

[0128] 通过由相加累加当开关Swb12接通时的计数和当开关Swb22接通时的计数,有可能使计数器732产生通过累加连接到垂直信号线VSL1的像素的像素值和连接到提供为邻近垂直信号线VSL1的右侧的垂直信号线VSL2的像素的像素值形成的数字数据。

[0129] 类似地,通过由相加累加当开关Swb23接通时的计数和当开关Swb33接通时的计数,有可能使计数器733产生通过累加连接到垂直信号线VSL2的像素的像素值和连接到垂直信号线VSL3(未示出)的像素的像素值形成的数字数据。垂直信号线VSL3(未示出)是提供为相邻垂直信号线VSL2的右侧的垂直信号线,且计数器733(未示出)是对应于垂直信号线VSL3提供的计数器。

[0130] 根据由时序控制单元60(切换控制单元)通过SW控制线进行的控制而控制开关的开/关。

[0131] 图7是说明开关Swb11、Swb12、Swb22和Swb23的开/关对应关系的表。开关Swb11、Swb12、Swb22和Swb23的开/关对应关系周期性地应用到提供在比开关Swb11、Swb12、Swb22和Swb23更靠右侧的开关。例如,上述的开关Swb33(未示出)具有与开关Swb11同样的开/关对应关系。

[0132] 如图7所示,开关Swb11和开关Swb12选择性地接通,且开关Swb22和开关Swb23选择性地接通。同时,开关Swb11的开/关和开关Swb22的开/关互相联系,并且开关Swb12的开/关和开关Swb23的开/关也互相联系。

[0133] 以下,如此连接使得每个垂直信号线的输出可以移位且输出到相邻其一侧的垂直信号线的列处理单元可以被称为“移位连接型列处理单元”。

[0134] 如上所述,由对应于垂直信号线提供的计数器,和对应于通过从该垂直信号线移到一侧提供的垂直信号线提供的计数器之间的一个计数器选择性地进行连接到每个垂直信号线的像素的像素信号的AD转换,并且因此可能产生通过累加连接到两个相邻的垂直信号线的像素的像素值形成的数字数据。

[0135] 切换电路Swb类似于上述交叉连接型列处理单元的情况形成为列处理单元70的一部分,并且排布在列部分(像素阵列的外部)。即,切换电路Swb的排布并没有被特别地限制,并且有根据像素布置对应于各种组合的优点。作为只可以取高和低中的一个的比较器输出的数字值的输入目的地被切换,且因此容易治理在切换时的噪音。

[0136] 图8是说明其中具体地实现了开关Swb11、Swb12、Swb22和Swa23的例子的图。与上述图4的情况类似地,图8所示的开关具有互补的开关的配置,其中组合了NMOS晶体管和PMOS晶体管。

[0137] 图9是控制信号XCROSS和CROSS的真值表。

[0138] 如图9所示,当通过控制线La1传送的控制信号XCROSS是正逻辑(高)且通过控制线La2传送的控制信号CROSS是负逻辑(低)时,开关Swb11和Swb22接通,且开关Swb12和开关Swa23断开。因此,对应于每个垂直信号线提供的比较器的输出输入到对应于同一个垂直信号线提供的计数器。即,从每个垂直信号线输出的模拟像素信号转换为作为对应于同一个垂直信号线提供的计数器中的计数值的数字数据。

[0139] 同时,当通过控制线Lb1传送的控制信号XCROSS是负逻辑(低)且通过控制线Lb2传送的控制信号CROSS是正逻辑(高)时,开关Swb11和Swb22断开,且开关Swb12和Swb23接通。因此,对应于每个垂直信号线提供的比较器的输出输入到对应于提供为邻近右侧的垂直信号线提供的计数器。即,从每个垂直信号线输出的模拟像素信号转换为作为对应于提供为邻近右侧的垂直信号线提供的计数器中的计数值的数字数据。

[0140] 根据上述互补开关,类似于在交叉连接侧上的列处理单元的情况,有可能通过PMOS场效应晶体管和NMOS场效应晶体管的组合以简单的配置实现切换电路。在制造CMOSLSI的过程中,有可能安装切换电路。

[0141] 下面,将描述单元像素的具体电路配置。该实施例的像素PXL具有在其中多个像素(例如,四个像素)共享浮动扩散部分FD的配置。然而,以下首先描述基本像素配置,然后描述在其中四个像素共享浮动扩散部分FD的配置。

[0142] 图10是说明由四个晶体管形成的CMOS图像传感器的基本像素电路的例子的电路图。图10所示的像素电路包括作为光接收元件的光电二极管PXL1、作为传输元件的传输晶体管PXL2、作为复位元件的复位晶体管PXL3、放大晶体管PXL4以及选择晶体管PXL5。

[0143] 光电二极管PXL1将入射光光电地转换为对应于其光量的电荷(这里,电子)的量。

[0144] 传输晶体管PXL2连接在光电二极管PXL1的阴极和作为输出节点的浮动扩散部分FD之间。当传输信号通过传输控制线Ltrg输入到PXL2的栅极(传输栅极)时传输晶体管PXL2导通。当传输晶体管PXL2导通时,由光电二极管PXL1的光电转换累积的信号电荷(这里,光子)传送到浮动扩散部分FD。

[0145] 复位晶体管PXL3的漏极连接到电源线LVDD,并且PXL3的源极连接到浮动扩散部分FD。在复位晶体管PXL3中,复位信号从垂直驱动单元40通过复位控制线Lrst输入到PXL3的栅极。当在来自光电二极管的电荷传送之前给复位晶体管PXL3一个复位脉冲时,复位晶体

管PXL3导通，并且通过将浮动扩散部分FD的电荷丢弃(abondon)给电源线LVDD而将浮动扩散部分FD的电势复位为电源线LVDD的电势。

[0146] 放大晶体管PXL4的栅极连接到浮动扩散部分FD。放大晶体管PXL4通过选择晶体管PXL5连接到垂直信号线VSL。

[0147] 当控制信号(地址信号或选择信号)通过选择控制线Lsel输入到PXL5的栅极时，该选择晶体管PXL5导通。

[0148] 当选择晶体管PXL5导通时，放大晶体管PXL4放大浮动扩散部分FD的电势，并向垂直信号线VSL输出与该电势对应的电压。通过垂直信号线VSL从每个像素输出的电压输出到列处理单元70。

[0149] 下面，将要描述在其中多个像素共享浮动扩散部分FD的像素电路。以下，共享浮动扩散部分FD的多个像素被称为“FD共享像素单元”。

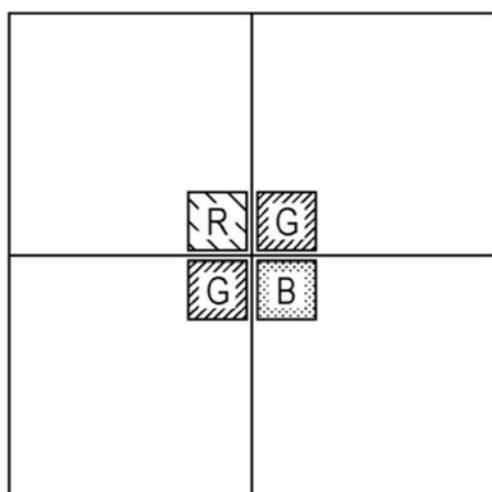

[0150] 图11是说明FD共享像素单元的图。在图11中，像素阵列由4x4的16个像素配置，且由2x2的四个像素配置的FD共享像素单元U1到U4的组合配置而成。每个FD共享像素单元共享在其中心处的FD，垂直信号线VSL1连接到FD共享像素单元U1和U3的FD，并且垂直信号线VSL2连接到FD共享像素单元U2和U4的FD。

[0151] 在FD共享像素单元中，在属于相同线的多个像素中具有基于用于FD共享像素单元的FD的共同(common)位置关系的像素由相同的像素驱动线驱动，且不具有基于用于FD共享像素单元的FD的共同位置关系的像素由其它像素驱动线驱动。

[0152] 具体地，在图11中，像素P11到P14、像素P21到P24、像素P31到P34以及像素P41到P44的每个属于相同的线。例如，像素P11到P14的线中，像素P11和像素P13由相同的像素驱动线驱动，并且像素P12和像素P14由相同的像素驱动线驱动。

[0153] 当然，上述像素和像素驱动线的组合是例子，并且可以被以各种方式修改。例如，通过同时驱动两个或更多个共享FD的像素，在FD中产生通过相加两个像素的模拟值而形成的值，并且该FD-相加的模拟值可以输出到垂直信号线。

[0154] 下面，将要描述FD共享像素单元的具体电路配置。

[0155] 图12是说明FD共享像素单元的电路配置的例子的电路图。

[0156] 在图12中，FD共享像素单元U由像素P11、P12、P21和P22配置。

[0157] FD共享像素单元U的每个单元像素包括光电二极管PD11、PD12、PD21和PD22中的一一个，以及传输晶体管Ttrs11、Ttrs12、Ttrs21和Ttrs22中的一个。

[0158] 在排布有像素P11和P12的线中，排布有传输控制线Ltrg1和Ltrg2，并且在排布有像素P21和P22的线中，排布有传输控制线Ltrg3和Ltrg4。

[0159] 传输控制线Ltrg1连接到第一像素P11的传输晶体管Ttrs11的栅极，以及传输控制线Ltrg2连接到第一像素P12的传输晶体管Ttrs12的栅极。传输控制线Ltrg3连接到第二像素P21的传输晶体管Ttrs21的栅极，以及传输控制线Ltrg4连接到第二像素P22的传输晶体管Ttrs22的栅极。

[0160] 有可能由垂直驱动单元40单个地驱动传输控制线Ltrg1、Ltrg2、Ltrg3和Ltrg4，并且有可能单个地控制通过浮动扩散部分FD每个单元像素从光电二极管的电荷输出。

[0161] 同时，FD共享像素单元U在四个像素P11、P12、P21和P22中配备有一个浮动扩散部分FD、一个复位晶体管Tres、一个放大晶体管Tamp和一个选择晶体管Tsel。

[0162] 复位控制线Lrst连接到复位晶体管Tres的栅极,且选择控制线Lsel连接到选择晶体管Tsel的栅极。

[0163] 即,浮动扩散部分FD的复位、浮动扩散部分中累积的电压的放大以及对于垂直信号线VSL的信号的输出对于FD共享像素单元U共同地进行。

[0164] 上述的FD共享像素电路是一个例子且单元像素的数目和单元像素的线可以适当地改变。例如,共享FD的单元像素的数目可以是3x3的9个像素,或者是8x8的64个像素。共享FD的单元像素可以具有相对于1x4的4个像素共享FD的配置,即4个像素纵向布置在一条线上,并且可以具有相对于4x1的4个像素共享FD的配置,即4个像素横向布置在一条线上。

[0165] (2) 像素相加的第一实施例

[0166] 下面,将描述像素相加的第一实施例。在第一实施例中,使用包括白色的颜色滤色器阵列,且在列处理单元中使用交叉-校正型。

[0167] 图13是说明根据第一实施例的颜色滤色器阵列和列处理单元的配置的图。图13中所示的颜色滤色器阵列示出4x4的16个像素用于简要描述。

[0168] 在图13中所示的颜色滤色器阵列中,具有最高输出级(level1)的W(白色)滤色器排布在棋盘形中,R(红色)和B(蓝色)滤色器在棋盘形中以纵向和横向的两个像素的间距布置,R和B滤色器布置为以一个像素的间距倾斜地偏离,且剩余的像素是G(绿色)滤色器。在这种情况下,G滤色器布置在斜带形中。

[0169] 具体地,W滤色器以棋盘形排布,R滤色器排布在第2行第4个以及第4行第2个,且B滤色器排布在第1行第3个以及第3行第1个。R滤色器和B滤色器的布置是两个像素的间距的棋盘布置。

[0170] G滤色器排布在其它的像素位置。当然,包括白色的颜色滤色器阵列的颜色布置不限于此,并且可以使用各种种类的颜色布置。

[0171] 在像素阵列中,垂直和水平的2x2的4个像素组成FD共享像素单元。

[0172] 具体地,左上的4个像素(G1、G2、W1和W2)组成一个FD共享像素单元,且左下的4个像素(B2、R2、W5和W6)组成一个FD共享像素单元。该FD共享像素单元通过每个共享FD连接到垂直信号线VSL1。

[0173] 右上的4个像素(B1、R1、W3和W4)组成一个FD共享像素单元,且右下的4个像素(G3、G4、W7和W8)组成一个FD共享像素单元。该FD共享像素单元通过每个共享FD连接到垂直信号线VSL2。

[0174] 通过垂直信号线VSL1输出的像素信号输入到比较器721。比较器721确定从DAC 80输入的参考信号和像素信号之间的大小。例如,当逐渐增加的斜波被用作参考信号时,当该参考信号低于像素信号时比较器721输出低,并且当该参考信号等于或高于像素信号时输出高。

[0175] 同时,通过垂直信号线VSL2输出的像素信号输入到比较器722。比较器722确定从DAC 80输入的参考信号和像素信号之间的大小。例如,当逐渐增加的斜波被用作参考信号时,当该参考信号低于像素信号时比较器722输出低,并且当该参考信号等于或高于像素信号时输出高。

[0176] 比较器721的输出端子通过开关Swa11连接到对应于垂直线VSL1提供的计数器731,并且通过开关Swa12连接到对应于垂直线VSL2提供的计数器732。垂直信号线VSL2是邻

近垂直接信号线VSL1排布的垂直接信号线。

[0177] 比较器722的输出端子通过开关Swa22连接到对应于垂直接线VSL2提供的计数器732，并且通过开关Swa21连接到对应于垂直接线VSL1提供的计数器731。垂直接信号线VSL1是邻近垂直接信号线VSL2排布的垂直接信号线。

[0178] 时序控制单元60藉由通过SW控制线输出的SW控制信号控制开关Swa11、Swa12、Swa22和Swa21的开/关。开关接通或断开以满足上述图3中所示的关系。

[0179] 图14是根据第一实施例的相加操作的时序图。

[0180] 首先，将描述作为亮度的主要分量的白色像素的相加操作。为了进行白色像素的相加，开关Swa11和Swa22接通，开关Swa12和Swa21断开。

[0181] 选择像素W1和像素W3，像素W1的像素信号输出到垂直接信号线VSL1，且像素W3的像素信号输出到垂直接信号线VSL2。然后，选择像素W2和像素W4，像素W2的像素信号输出到垂直接信号线VSL1，且像素W4的像素信号输出到垂直接信号线VSL2。

[0182] 即，像素W1和W2的像素信号顺序地输出到垂直接信号线VSL1，且像素W3和W4的像素信号顺序地输出到垂直接信号线VSL2。

[0183] 由于开关Swa11和Swa22接通且开关Swa12和Swa21断开，像素W1和W2的两个像素信号都由计数器731计数，且像素W3和W4的两个像素信号都由计数器732计数。

[0184] 计数器731，通过时序控制单元60的控制，在像素W1和W2的两个像素信号的计数完成之前不初始化计数地继续计数。因此，计数器731的计数值是对应于像素W1和W2的像素信号的累加的数字数据。

[0185] 类似地，计数器732，通过时序控制单元60的控制，在像素W3和W4的两个像素信号的计数完成之前不初始化计数地继续计数。因此，计数器732的计数值是对应于像素W3和W4的像素信号的累加的数字数据。

[0186] 换言之，时序控制单元60在作为相加对象的两个像素的计数之前不初始化计数器731和732的计数值，并且在作为相加对象的两个像素的计数完成并将计数值输出到存储器741和742（参见图2）时初始化计数器731和732的计数值。

[0187] 当完成两个像素的像素信号的计数时，计数器731和732通过时序控制单元60的控制向存储器741和742输出计数值。

[0188] 作为结果，通过累加像素W1和W2而形成的数字数据和通过累加像素W3和W4而形成的数字数据分别存储在存储器741和742中。通过时序控制单元60的控制，在其后进行的相加处理期间，存储器741和742中存储的数字数据通过水平信号线输出到输出电路90。

[0189] 通过对作为其它白色像素的像素W5、W6、W7和W8进行相同的相加处理，通过累加像素W5和W6而形成的数字数据和通过累加像素W7和W8而形成的数字数据存储在存储器741和742中，且通过时序控制单元60的控制，在其后进行的相加处理期间，该数字数据通过水平信号线输出到输出电路90。

[0190] 下面，将描述R、G和B像素的相加操作。在该实施例中，首先进行白色像素的相加操作，随后进行RGB像素的相加操作。然而当然，该顺序可以是反过来的或交替的（alternate），且可以适当地改变顺序。

[0191] 为了相加R、G和B像素，首先，开关Swa11和Swa22断开，且开关Swa12和开关Swa21接通。选择像素G1和像素B1，像素G1的像素信号输出到垂直接信号线VSL1，且像素B1的像素信号

输出到垂直信号线VSL2。

[0192] 由于开关Swa11和Swa22断开且开关Swa12和Swa21接通,因此通过垂直信号线VSL1输出的像素G1的像素信号由对应于相邻的垂直信号线VSL2提供的计数器732计数,且通过垂直信号线VSL2输出的像素B1的像素信号由对应于相邻的垂直信号线VSL1提供的计数器731计数。

[0193] 然后,开关Swa11和Swa22接通,且开关Swa12和Swa21断开。选择像素B2和像素G3,像素B2的像素信号输出到垂直信号线VSL1,且像素G3的像素信号输出到垂直信号线VSL2。

[0194] 由于开关Swa11和Swa22接通且开关Swa12和Swa21断开,因此通过垂直信号线VSL1输出的像素B2的像素信号由计数器732计数,且通过垂直信号线VSL2输出的像素G3的像素信号由计数器732计数。

[0195] 类似于白色的计数,由于计数器731继续通过控制单元60的控制计数直到像素B1和B2的两个像素的计数,计数器731的计数值是对应于像素B1和B2的像素信号的累加的数字数据。

[0196] 类似地,由于计数器732也继续通过控制单元60的控制计数直到像素G1和G3的两个像素的计数,计数器732的计数值是对应于像素G1和G3的像素信号的累加的数字数据。

[0197] 当两个像素的像素信号的计数完成时,计数器731和732通过时序控制单元60的控制分别输出计数值到存储器741和742。

[0198] 即,时序控制单元60在两个像素的计数完成前不初始化计数器731和732中的计数值,且当计数两个像素时初始化计数器731和732的计数值。

[0199] 作为结果,通过累加像素B1和B2而形成的数字数据和通过累加像素G1和G3而形成的数字数据分别存储在存储器741和742中。通过时序控制单元60的控制,在其后进行的相加处理期间,存储器741和742中存储的数字数据通过水平信号线输出到输出电路90。

[0200] 通过对像素R1、R2、G2和G4进行相同的相加处理,通过累加像素R1和R2而形成的数字数据和通过累加像素G2和G4而形成的数字数据存储在存储器741和742中,且通过时序控制单元60的控制,在其后进行的相加处理期间通过水平信号线输出到输出电路90。

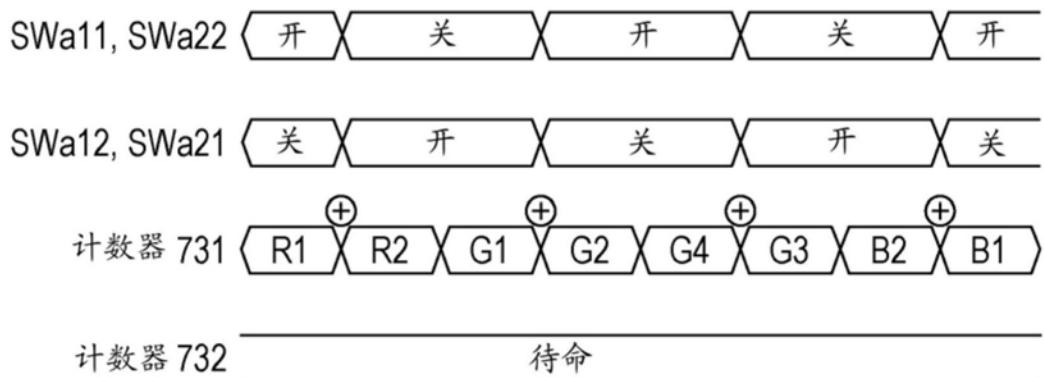

[0201] 图15A和图15B是说明参照图13和图14描述的相加操作中的读出图像的图。如图15A所示,通过进行上述的相加操作,对于白色像素,获取了通过相加倾斜的方向上相邻的白色像素而形成的数字数据,且对于RGB像素,获取了通过相加倾斜的方向上偏离两个像素的相同颜色的像素而形成的数字数据。

[0202] 然而,如图15B中所示,由图14中所示的时序图的相加操作获得的白色像素的相加值对应于FD共享像素单元的中心处的像素值,但是RGB像素的相加值对应于偏离FD共享像素单元的中心的位置处的计数值。

[0203] 当进行了相加操作,有可能通过调整A/D转换中的增益而调整最终获得的像素的相加值使其接近FD共享像素单元的中心处的像素值。

[0204] 图16是说明在调整增益的同时进行的第一实施例的相加操作的时序图。可以通过例如如上所述调整参考信号产生单元80产生的参考信号的斜率而实现增益调整。即,为了增加增益,最好减少参考信号的斜率,并且为了降低增益,最好增加参考信号的斜率。

[0205] 如图16所示,在读出像素B1、G1、R2和G4时的增益是12dB,在读出像素W1到W8和像素B2、G3、R1和G2时增益是0dB。即,通过增加图15中相加的两个像素中的一个增益比另一个

增益更多,对于该相加值的位置调整到接近于更高增益侧的像素位置。这里描述的增益值是例子,并且明显地可以任意地调整。

[0206] 图17是说明作为图16所示的增益调整的结果而获得的读出图像的图。

[0207] 如图17中所示,通过增加像素B1的增益比像素B2的增益更高,对于像素B1和像素B2的相加值的位置接近于像素B1的像素位置,通过增加像素G1的增益比像素G3的增益更高,对于像素G1和像素G3的相加值的位置接近于像素G1的像素位置,通过增加像素R2的增益比像素R1的增益更高,对于像素R1和像素R2的相加值的位置接近于像素R2的像素位置,通过增加像素G4的增益比像素G2的增益更高,对于像素G2和像素G4的相加值的位置接近于像素G4的像素位置。

[0208] 由于对应于相加值的白色像素W1到W8的位置原本对应于每个像素单元的中心,因此第一实施例中不需要调整增益,且白色像素W1到W8对应于图15B中所示的相同的位置。

[0209] (3) 像素相加的第二实施例

[0210] 下面,将描述像素相加的第二实施例。在第二实施例中,使用包括白色颜色滤色器阵列,且在列处理单元中使用移位-校正型。

[0211] 图18是说明根据第二实施例的颜色滤色器阵列和列处理单元的配置的图。类似于第一实施例,在图18中所示的颜色滤色器阵列中,示出4x4的16个像素,具有最高输出级的W滤色器排布在棋盘形中,R和B滤色器在棋盘形中以纵向和横向的两个像素的间距布置,R和B滤色器布置为倾斜地偏离一个像素的间距,且剩余的像素是G滤色器。

[0212] 在像素阵列中,垂直和水平的2x2的4个像素组成FD共享像素单元。

[0213] 具体地,左上的4个像素(B1、R1、W1和W2)组成一个FD共享像素单元,且左下的4个像素(G3、G4、W5和W6)组成一个FD共享像素单元。FD共享像素单元通过每个共享FD连接到垂直信号线VSL1。

[0214] 右上的4个像素(G1、G2、W3和W4)组成一个FD共享像素单元,且右下的4个像素(B、R、W7和W8)组成一个FD共享像素单元。FD共享像素单元通过每个共享FD连接到垂直信号线VSL2。

[0215] 左下部分处所示的两个像素(B2和R2)是连接到邻近垂直信号线VSL1的左侧的垂直信号线VSL0(未示出)的像素,且当开关Swb01接通时由计数器731计数。

[0216] 通过垂直信号线VSL0(未示出)输出的像素信号输入到对应于垂直信号线VSL0提供的比较器720(未示出)。比较器720确定从DAC 80输入的参考信号和像素信号之间的大小。例如,当逐渐增加的斜波被用作参考信号时,当该参考信号低于像素信号时比较器720输出低,并且当该参考信号等于或高于像素信号时输出高。

[0217] 通过垂直信号线VSL1输出的像素信号输入到比较器721。比较器721确定从DAC 80输入的参考信号和像素信号之间的大小。例如,当逐渐增加的斜波被用作参考信号时,当该参考信号低于像素信号时比较器721输出低,并且当该参考信号等于或高于像素信号时输出高。

[0218] 通过垂直信号线VSL2输出的像素信号输入到比较器722。比较器722确定从DAC 80输入的参考信号和像素信号之间的大小。例如,当逐渐增加的斜波被用作参考信号时,当该参考信号低于像素信号时比较器722输出低,并且当该参考信号等于或高于像素信号时输出高。

[0219] 比较器720(未示出)的输出端子通过Swb01连接到对应于垂直线VSL1提供的计数器731。

[0220] 比较器721的输出端子通过开关Swb11连接到对应于垂直线VSL1提供的计数器731,并且通过开关Swb12连接到对应于垂直线VSL2(未示出)提供的计数器732。垂直信号线VSL2是邻近垂直信号线VSL1的右侧排布的垂直信号线。

[0221] 比较器722的输出端子通过开关Swb22连接到对应于垂直线VSL2提供的计数器732,并且通过开关Swb23连接到对应于垂直线VSL3(未示出)提供的计数器733。垂直信号线VSL3是邻近垂直信号线VSL2的右侧排布的垂直信号线。

[0222] 时序控制单元60藉由通过SW控制线输出的SW控制信号控制开关Swb01、Swa11、Swb12、Swb22和Swb23的开/关。开关接通或断开以满足上述图7中所示的关系。

[0223] 图19是根据第二实施例的相加操作的时序图。

[0224] 首先,将描述作为亮度的主要分量的白色像素的相加操作。为了进行白色像素的相加,开关Swb11和Swb22接通,开关Swb12和Swa23断开。

[0225] 选择像素W1和像素W3,像素W1的像素信号输出到垂直信号线VSL1,且像素W3的像素信号输出到垂直信号线VSL2。然后,选择像素W2和像素W4,像素W2的像素信号输出到垂直信号线VSL1,且像素W4的像素信号输出到垂直信号线VSL2。

[0226] 即,像素W1和W2的像素信号顺序地输出到垂直信号线VSL1,且像素W3和W4的像素信号顺序地输出到垂直信号线VSL2。

[0227] 由于开关Swb11和Swb22接通且开关Swb12和Swb23断开,像素W1和W2的两个像素信号都由计数器731计数,且像素W3和W4的两个像素信号都由计数器732计数。

[0228] 计数器731,通过时序控制单元60的控制,在像素W1和W2的两个像素信号的计数完成之前不初始化计数地继续计数。因此,计数器731的计数值是对应于像素W1和W2的像素信号的累加的数字数据。

[0229] 类似地,计数器732,通过时序控制单元60的控制,在像素W3和W4的两个像素信号的计数完成之前不初始化计数地继续计数。因此,计数器732的计数值是对应于像素W3和W4的像素信号的累加的数字数据。

[0230] 换言之,时序控制单元60在作为相加对象的两个像素的计数之前不初始化计数器731和732的计数值,并且在作为相加对象的两个像素的计数完成并将计数值输出到存储器741和742(参见图2)时初始化计数器731和732的计数值。

[0231] 当完成两个像素的像素信号的计数时,计数器731和732通过时序控制单元60的控制向存储器741和742输出计数值。

[0232] 作为结果,通过累加像素W1和W2而形成的数字数据和通过累加像素W3和W4而形成的数字数据分别存储在存储器741和742中。通过时序控制单元60的控制,在其后进行的相加处理期间,存储器741和742中存储的数字数据通过水平信号线输出到输出电路90。

[0233] 通过对作为其它白色像素的像素W5、W6、W7和W8进行相同的相加操作,通过累加像素W5和W6而形成的数字数据和通过累加像素W7和W8而形成的数字数据存储在存储器741和742中,且通过时序控制单元60的控制,在其后进行的相加处理期间,该数字数据通过水平信号线输出到输出电路90。

[0234] 下面,将描述R、G和B像素的相加操作。在第二实施例中,首先进行白色像素的相加

操作,随后进行RGB像素的相加操作。然而当然,该顺序可以是反过来的或交替的(alternate),且可以适当地改变顺序。

[0235] 为了相加R、G和B像素,首先,开关Swb11和Swb22接通,且开关Swb12和开关Swb23(和开关Swb01)断开。选择像素B1和像素G1,像素B1的像素信号输出到垂直信号线VSL1,且像素G1的像素信号输出到垂直信号线VSL2。

[0236] 由于开关Swb11和Swb22接通且开关Swa12和Swa23断开,因此通过垂直信号线VSL1输出的像素B1的像素信号由对应于垂直信号线VSL1提供的计数器731计数,且通过垂直信号线VSL2输出的像素G1的像素信号由对应于垂直信号线VSL2提供的计数器732计数。

[0237] 然后,开关Swb11和Swb22断开,且开关Swb12和Swa23(和开关Swb01)接通。选择像素B2和像素G3,像素B2的像素信号输出到垂直信号线VSL0(未示出),且像素G3的像素信号输出到垂直信号线VSL1。

[0238] 由于开关Swb11和Swb22断开且开关Swa12和Swa23(和开关Swb01)接通,因此通过垂直信号线VSL0(未示出)输出的像素B2的像素信号由计数器731计数,且通过垂直信号线VSL1输出的像素G3的像素信号由计数器732计数。

[0239] 类似于白色的计数,由于计数器731通过控制单元60的控制继续计数直到像素B1和B2的两个像素的计数,计数器731的计数值是对应于像素B1和B2的像素信号的累加的数字数据。

[0240] 类似地,由于计数器732也继续通过控制单元60的控制计数直到像素G1和G3的两个像素的计数,计数器732的计数值是对应于像素G1和G3的像素信号的累加的数字数据。

[0241] 当两个像素的像素信号的计数完成时,计数器731和732通过时序控制单元60的控制分别输出计数值到存储器741和742。

[0242] 即,时序控制单元60在两个像素的计数完成前不初始化计数器731和732中的计数值,且当计数两个像素时初始化计数器731和732的计数值。

[0243] 作为结果,通过累加像素B1和B2而形成的数字数据和通过累加像素G1和G3而形成的数字数据分别存储在存储器741和742中。通过时序控制单元60的控制在其后进行的相加处理期间,存储器741和742中存储的数字数据通过水平信号线输出到输出电路90。

[0244] 通过对像素R1、R2、G2和G4进行相同的相加处理,通过累加像素R1和R2而形成的数字数据和通过累加像素G2和G4而形成的数字数据存储在存储器741和742中,且通过时序控制单元60的控制,在其后进行的相加处理期间通过水平信号线输出到输出电路90。

[0245] 图20A和图20B是说明参照图18和图19描述的相加操作中的读出图像的图。如图20A所示,通过进行上述的相加操作,对于白色像素,获得通过相加倾斜的方向上相邻的白色像素而形成的数字数据,且对于RGB像素,获得通过相加倾斜的方向上偏离两个像素的相同颜色的像素而形成的数字数据。

[0246] 然而,如图20B中所示,由图19中所示的时序图的相加操作获得的白色像素的相加值对应于FD共享像素单元的中心处的像素值,但是RGB像素的相加值对应于偏离FD共享像素单元的中心的位置处的像素值。

[0247] 当进行相加操作时,有可能通过调整A/D转换中的增益而调整最终获得的像素的相加值使其接近FD共享像素单元的中心处的像素值。

[0248] 图21是说明在调整增益的同时进行的第二实施例的相加操作的时序图。

[0249] 如图21所示,在读出像素B1、G1、R1和G2时增益是6dB,在读出像素W1到W8和像素B2、G3、R2和G4时增益是0dB。即,通过增加图20中相加的两个像素中的一个增益比另一个增益更多,对应于该相加值的位置调整到接近于更高增益侧的像素位置。

[0250] 更具体地,为了调整像素的相加值以对应于FD共享像素单元的中心,当像素B2、G3、R2和G4的增益是0dB时,像素B1、G1、R1和G2的增益是6.64dB,从而使得像素B1、G1、R1和G2的增益和像素B2、G3、R2和G4的增益的比率是3:1。

[0251] 图22是说明作为图21所示的增益调整的结果而获得的读出图像的图。

[0252] 如图22中所示,通过增加像素B1的增益比像素B2的增益更高,对应于像素B1和像素B2的相加值的位置接近于像素B1的像素位置,通过增加像素G1的增益比像素G3的增益更高,对应于像素G1和像素G3的相加值的位置接近于像素G1的像素位置,通过增加像素R2的增益比像素R1的增益更高,对应于像素R1和像素R2的相加值的位置接近于像素R2的像素位置,通过增加像素G4的增益比像素G2的增益更高,对应于像素G2和像素G4的相加值的位置接近于像素G4的像素位置。

[0253] 由于对应于相加值的白色像素W1到W8的位置原本对应于每个像素单元的中心,因此第二实施例中不调整该增益,且白色像素W1到W8对应于图20B中所示的相同的位置。

[0254] (4) 像素相加的第三实施例:

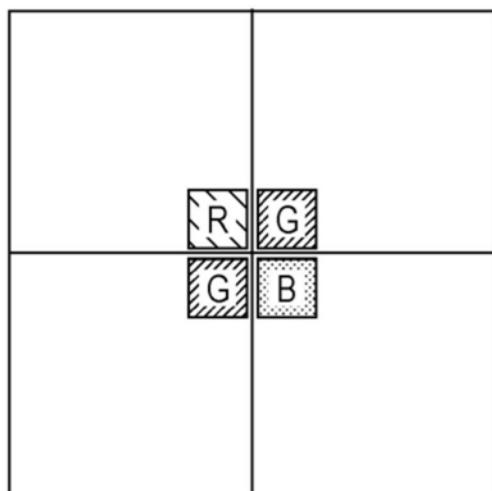

[0255] 下面,将描述像素相加的第三实施例。在第三实施例中,在列处理单元中使用现有技术中的Bayer布置的颜色滤色器阵列以及所述的交叉-校正型。

[0256] 图23是说明根据第三实施例的颜色滤色器阵列和列处理单元的配置的图。图23中所示的颜色滤色器阵列示出类似于第一实施例的4x4的16个像素。在像素阵列中,垂直和水平的2x2的4个像素组成FD共享像素单元。

[0257] 具体地,左上的4个像素(R1、B1、G和G)组成一个FD共享像素单元,且左下的4个像素(G2、G4、R和B)组成一个FD共享像素单元。该FD共享像素单元通过每个共享FD连接到垂直信号线VSL1。

[0258] 右上的4个像素(R、B、G1和G3)组成一个FD共享像素单元,且右下的4个像素(R2、B2、G和G)组成一个FD共享像素单元。该FD共享像素单元通过每个共享FD连接到垂直信号线VSL2。

[0259] 通过垂直信号线VSL1输出的像素信号输入到比较器721。比较器721确定从DAC 80输入的参考信号和像素信号之间的大小。例如,当逐渐增加的斜波被用作参考信号时,当该参考信号低于像素信号时比较器721输出低,并且当该参考信号等于或高于像素信号时输出高。

[0260] 同时,通过垂直信号线VSL2输出的像素信号输入到比较器722。比较器722确定从DAC 80输入的参考信号和像素信号之间的大小。例如,当逐渐增加的斜波被用作参考信号时,当该参考信号低于像素信号时比较器722输出低,并且当该参考信号等于或高于像素信号时输出高。

[0261] 比较器721的输出端子通过开关Swa11连接到对应于垂直线VSL1提供的计数器731,并且通过开关Swa12连接到对应于垂直线VSL2提供的计数器732。垂直信号线VSL2是邻近垂直信号线VSL1排布的垂直信号线。

[0262] 比较器722的输出端子通过开关Swa22连接到对应于垂直线VSL2提供的计数器

732，并且通过开关Swa21连接到对应于垂直线VSL1提供的计数器731。垂直信号线VSL1是邻近垂直信号线VSL2排布的垂直信号线。

[0263] 时序控制单元60藉由通过SW控制线输出的SW控制信号控制开关Swa11、Swa12、Swa22和Swa21的开/关。开关接通或断开以满足上述图3中所示的关系。

[0264] 图24是根据第三实施例的相加操作的时序图。

[0265] 首先，开关Swa11和Swa22接通，且开关Swa12和开关Swa21断开。选择像素R1，且像素R1的像素信号输出到垂直信号线VSL1。这里，由于开关Swa11和Swa22接通且开关Swa12和Swa21断开，因此由计数器731计数像素R1的像素信号。

[0266] 然后，开关Swa11和Swa22断开，且开关Swa12和Swa21接通。选择像素R2，且像素R2的像素信号输出到垂直信号线VSL2。这里，由于开关Swa11和Swa22断开且开关Swa12和Swa21接通，因此由计数器731计数像素R2的像素信号。

[0267] 计数器731，通过时序控制单元60的控制，在像素R1和R2的两个像素信号的计数完成之前不初始化计数地继续计数。因此，计数器731的计数值是对应于像素R1和R2的像素信号的累加的数字数据。

[0268] 然后，开关保持原样，选择像素G1，且像素G1的像素信号输出到垂直信号线VSL2。然后，由计数器731计数像素G1的像素信号。

[0269] 然后，开关Swa11和Swa22接通，且开关Swa12和Swa21断开。选择像素G2，且像素G2的像素信号输出到垂直信号线VSL1。然后，由计数器731计数像素G2的像素信号。

[0270] 如上所述，交替地重复开关的开/关和计数值的输出，且因此可能对于剩余的像素G4、G3、B2和B1将像素的相加值顺序地输出到输出电路90。

[0271] 在第三实施例中，没有使用对应于信号线VSL2提供的比较器722、计数器732和存储器742，因此有可能以作为待命状态(standby state)的这样的配置降低耗电量。

[0272] 图25A和图25B是说明参照图23和图24描述的相加操作中的读出图像的图。如图25A所示，通过进行上述的相加操作，相对于RGB像素，获得通过相加倾斜的方向上偏离两个像素的相同颜色的像素而形成的数字数据。

[0273] 然而，如图25B中所示，由图24中所示的时序图的相加操作获得的RGB像素的相加值对应于偏离FD共享像素单元的中心的位置处的像素值。

[0274] 当进行相加操作时，有可能通过调整A/D转换中的增益而调整最终获得的像素的相加值使其接近FD共享像素单元的中心处的像素值。

[0275] 图26是说明在调整增益的同时进行的第三实施例的相加操作的时序图。

[0276] 如图26中所示，在读出像素R1、G1、G4和B2时的增益是6dB，且在读出像素R2、G2、G3和B1时的增益是0dB。即，通过增加图25中相加的两个像素的一个增益比另一个增益更多，对应于该相加值的位置调整到接近于更高增益侧的像素位置。

[0277] 图27是说明作为图26所示的增益调整的结果而获得的读出图像的图。

[0278] 如图27中所示，通过增加像素R1的增益比像素R2的增益更高，对应于像素R1和像素R2的相加值的位置接近于像素R1的像素位置，通过增加像素G1的增益比像素G2的增益更高，对应于像素G1和像素G2的相加值的位置接近于像素G1的像素位置，通过增加像素G4的增益比像素G3的增益更高，对应于像素G4和像素G3的相加值的位置接近于像素G4的像素位置，通过增加像素B2的增益比像素B1的增益更高，对应于像素B2和像素B1的相加值的位置

接近于像素B2的像素位置。

[0279] (5) 各种修改示例：

[0280] (5-1) 第一修改示例

[0281] 在该实施例中,可以一起使用FD相加方法。

[0282] 即,从FD共享像素单元选择多个像素,从多个像素的光电二极管输出电荷到浮动扩散部分,并且事先将像素值模拟-相加到浮动扩散部分FD且输出到垂直信号线。

[0283] 例如,在第一实施例和第二实施例中,当属于一个FD共享像素单元的两个白色像素经受FD相加且输出时,有可能将输出白色像素中所用的处理时间减半。

[0284] (5-2) 第二修改示例：

[0285] 在上述的实施例和修改示例中,已经描述了垂直和水平的4x4的16个像素的抽取输出为垂直和水平的2x2的4个像素的情况,但是显然本公开可以对应于各种抽取程度,例如垂直和水平的8x8的64个像素的抽取输出为垂直和水平的2x2的4个像素。

[0286] (5-3) 第三修改示例：

[0287] 在如上的实施例和修改示例中,对应于每个垂直信号线的比较器和计数器连接到第一开关,且对应于每个垂直信号线的比较器和对应于相邻的垂直信号线的计数器连接到第二开关。然而,本公开不限于作为第二开关的连接目的地的计数器不一定对应于垂直信号线的情况。

[0288] 图28是说明根据第三修改示例的连接关系的图。图28的基本配置与图2的基本配置相同且改变并示出切换电路Swa的连接关系。

[0289] 切换电路Swa包括开关Swa11、Swa1m、Swam1和Swamm。比较器721和计数器731通过开关Swa11连接,且比较器72m和计数器73m通过开关Swamm连接。比较器721和计数器73m通过开关Swa1m连接,且比较器72m和计数器731通过开关Swam1连接。

[0290] 即,切换电路Swa包括连接对应于一个垂直信号线提供的比较器和计数器的开关,以及连接对应于一个垂直信号线提供的比较器和对应于与该一个垂直信号线不同的另一个垂直信号线提供的计数器的开关。

[0291] 由此,在一组垂直信号线VSL1和VSLm中,选出对应于一个垂直信号线提供的计数器和对应于另一个垂直信号线提供的计数器的任一个进行计数。该组垂直信号线VSL1和VSLm可以相邻或可以不相邻。

[0292] 因此,可以由计数器731和计数器73m相加并输出连接到垂直信号线VSL1的像素和连接到垂直信号线VSLm的像素的像素值。

[0293] 这里,已经作为例子描述了交叉-连接型列处理单元70,但是显然第三修改示例可以应用到移位-连接型列处理单元70。

[0294] (5-4) 第四修改示例：

[0295] 在以上描述的实施例和修改示例中,一个垂直信号线提供在两个像素列中,但是当然,一个垂直信号线可以提供在一个像素列中,且一个垂直信号线可以提供在三个或更多个像素列中。

[0296] 本技术不限于上述的实施例和修改示例,且包括如下配置,其中上述的实施例和修改示例中公开的配置被取代或其组合被修改,以及其中上述现有技术和实施例以及修改示例中公开的配置被取代或其组合被修改。本技术的技术范围不限于上述的实施例,且包

括在权利要求书及其等同物中描述的内容。

[0297] 本技术可以具有如下的配置。

[0298] (1)一种固态成像设备,包括:像素阵列单元和A/D转换单元,所述像素阵列单元具有以矩阵形式二维布置的多个像素和沿列方向布置的多个信号线;对应于各自的信号线提供且将通过信号线从像素输出的模拟信号转换为数字信号的A/D转换单元;以及切换单元(switching unit),对下述通过每个信号线输出的模拟信号到数字信号的转换进行切换,该通过每个信号线输出的模拟信号到数字信号的转换使用对应于传送模拟信号的信号线提供的

[0299] A/D转换单元和对应于不是传送模拟信号的信号线的信号线而提供的A/D转换单元的任一个。

[0300] (2)根据(1)所述的固态成像设备,其中A/D转换单元具有:将随时间变化的参考信号与从像素获得的模拟信号进行比较的比较器,以及对直到在该比较器中的比较完成的时间进行计数的计数器,并且其中所述切换单元包括将对应于每个信号线提供的A/D转换单元中的比较器的输出端子连接到计数器的输入端子的第一开关,和将对应于每个信号线提供的A/D转换单元中的比较器的输出端子连接到对应于另一个信号线提供的A/D转换单元的计数器的输入端子的第二开关,以及控制第一开关和第二开关的切换的切换控制单元。

[0301] (3)根据(1)或(2)所述的固态成像设备,其中切换单元对从两个信号线中的一个信号线输出的模拟信号到数字信号的转换进行切换,该从两个信号线中的一个信号线输出的模拟信号到数字信号的转换使用对应于一个信号线提供的A/D转换单元和对应于另一个信号线提供的A/D转换单元的任一个。

[0302] (4)根据(1)到(3)的任一个所述的固态成像设备,其中所述切换单元对通过多个信号线的每个信号线输出的模拟信号到数字信号的转换进行切换,该通过多个信号线的每个信号线输出的模拟信号到数字信号的转换使用对应于传送模拟信号的信号线提供的A/D转换单元和对应于与传送模拟信号的信号线一侧邻接地提供的信号线提供的A/D转换单元的任一个。

[0303] (5)根据(1)到(4)的任一个所述的固态成像设备,其中该多个像素中的预定数目的像素共享浮动扩散部分,且其中所述切换单元通过浮动扩散部分对共享相同的浮动扩散部分的两个或更多个像素的模拟信号进行模拟相加,且输出模拟-相加的信号到信号线。

[0304] (6)根据(1)到(5)的任一个所述的固态成像设备,其中所述多个像素在光接收面侧配备有颜色滤色器阵列,其中滤色器(filter)的颜色对应于各自的像素而分类,并且其中颜色滤色器阵列中的白色滤色器按棋盘形排布,红色和蓝色滤色器按纵向和横向两像素间距的棋盘形布置,所述红色和蓝色滤色器被布置为倾斜地偏离一个像素,且剩余的像素为绿色滤色器。

[0305] (7)根据(1)到(6)的任一个所述的固态成像设备,其中所述多个像素在光接收面侧配备有颜色滤色器阵列,其中滤色器的颜色对应于各自的像素而分类,并且其中在所述颜色滤色器阵列中,颜色滤色器按Bayer布置形式。

[0306] (8)一种用于控制固态成像设备的方法,该固态成像设备包括:具有以矩阵形式二维布置的多个像素和沿列方向布置的多个信号线的像素阵列单元,以及对应于信号线提供且将通过信号线从像素输出的模拟信号转换为数字信号的A/D转换单元,所述方法包括:对

下述通过每个信号线输出的模拟信号到数字信号的转换进行切换,该通过每个信号线输出的模拟信号到数字信号的转换使用对应于传送模拟信号的信号线提供的A/D转换单元和对应于不是传送模拟信号的信号线的信号线而提供的A/D转换单元的任一个。

[0307] (9)一种用于控制固态成像设备的程序,该固态成像设备包括:具有以矩阵形式二维布置的多个像素和沿列方向布置的多个信号线的像素阵列单元,以及对应于信号线提供且将通过信号线从像素输出的模拟信号转换为数字信号的A/D转换单元,所述程序包括:对下述通过每个信号线输出的模拟信号到数字信号的转换进行切换,该通过每个信号线输出的模拟信号到数字信号的转换使用对应于传送模拟信号的信号线提供的A/D转换单元和对应于不是传送模拟信号的信号线的信号线而提供的A/D转换单元的任一个。

[0308] 本申请包含与于2011年9月22日向日本专利局提交的日本优先权专利申请JP 2011-207368中公开的内容有关的主题,其全部内容通过引用被并入于此。

[0309] 本领域的技术人员应该理解在不偏离所附权利要求及其等同物的范围内,取决于设计要求和此范围内的其它因素,可以作各种修改、组合、子组合和改变。

图1

图2

| SWa11 | SWa12 | SWa21 | SWa22 |

|-------|-------|-------|-------|

| 开     | 关     | 关     | 开     |

| 关     | 开     | 开     | 关     |

图3

图4

| La1 (XCROSS) | La2 (CROSS) | SWa11 | SWa12 | SWa21 | SWa22 |

|--------------|-------------|-------|-------|-------|-------|

| 高            | 低           | 开     | 关     | 关     | 开     |

| 低            | 高           | 关     | 开     | 开     | 关     |

图5

图6

| SWb11 | SWb12 | SWb22 | SWb23 |

|-------|-------|-------|-------|

| 开     | 关     | 开     | 关     |

| 关     | 开     | 关     | 开     |

图7

图8

| Lb1 (XCROSS) | Lb2 (CROSS) | SWb11 | SWb12 | SWb22 | SWb23 |

|--------------|-------------|-------|-------|-------|-------|

| 高            | 低           | 开     | 关     | 开     | 关     |

| 低            | 高           | 关     | 开     | 关     | 开     |

图9

图10

图11

图12

图13

图14

图15A

图15B

图16

图17

图18

图19

图20A

图20B

图21

图22

图23

图24

图25A

图25B

图26

图27

图28

图29

图30

图31A

图31B

图32