(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4918047号

(P4918047)

(45) 発行日 平成24年4月18日(2012.4.18)

(24) 登録日 平成24年2月3日(2012.2.3)

(51) Int.Cl.

F 1

H03L 7/081 (2006.01)

H03L 7/095 (2006.01)H03L 7/08

H03L 7/08J

B

請求項の数 25 (全 27 頁)

(21) 出願番号 特願2007-553423 (P2007-553423)

(86) (22) 出願日 平成18年2月3日 (2006.2.3)

(65) 公表番号 特表2008-529426 (P2008-529426A)

(43) 公表日 平成20年7月31日 (2008.7.31)

(86) 國際出願番号 PCT/CA2006/000143

(87) 國際公開番号 WO2006/081668

(87) 國際公開日 平成18年8月10日 (2006.8.10)

審査請求日 平成20年9月11日 (2008.9.11)

(31) 優先権主張番号 11/050,644

(32) 優先日 平成17年2月3日 (2005.2.3)

(33) 優先権主張国 米国(US)

(73) 特許権者 593138296

モーセッド・テクノロジーズ・インコーポ

レイテッド

M o s a i d T e c h n o l o g i e s

I n c o r p o r a t e d

カナダ国 ケイ2ケイ2エックス1 オ

ンタリオ、オタワ、ハインズ・ロード 1

1, スイート 203

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

最終頁に続く

(54) 【発明の名称】遅延ロックループを初期化する方法および装置

## (57) 【特許請求の範囲】

## 【請求項1】

クロック信号についての遅延を与える遅延ロックループであって、複数の遅延のところに複数の潜在的なロック点をもち：

前記複数の潜在的なロック点のうち第一の潜在的なロック点への近接を検出するロック検出器と；

前記ロック検出器の出力に結合された初期化コントロールとを有しており、前記初期化コントロールは、クロック信号の遅延をある初期遅延から一方向に変化させ、前記第一の潜在的なロック点をスキップし、前記複数の潜在的なロック点のうちから選択される動作点を探索するために前記と同じ一方向に遅延を変化させ続ける、遅延ロックループ。

10

## 【請求項2】

前記初期化コントロールが、動作点への近接を検出すると、遅延の増加および減少の両方を可能にする、請求項1記載の遅延ロックループ。

## 【請求項3】

前記ロック検出器が：

複数の段を有し、各段が異なる精度でロック点近接を示す、請求項1または2記載の遅延ロックループ。

## 【請求項4】

前記初期化コントロールが電源投入後に従事する、請求項1ないし3のうちいずれか一

20

項記載の遅延ロックループ。

**【請求項 5】**

前記初期化コントロールがリセット後に従事する、請求項 1ないし 3のうちいずれか一項記載の遅延ロックループ。

**【請求項 6】**

クロック信号の位相をシフトさせることによって前記第一の潜在的なロック点がスキップされる、請求項 1ないし 5のうちいずれか一項記載の遅延ロックループ。

**【請求項 7】**

前記クロック信号と遅延されたフィードバック・クロックのエッジが互いにどのくらい近いかに基づいて前記第一の潜在的なロック点への近接が検出される、請求項 1ないし 6のうちいずれか一項記載の遅延ロックループ。 10

**【請求項 8】**

複数の所定の時間期間を使い、前記クロック信号および遅延されたフィードバック・クロックのエッジが前記複数の所定の時間期間それぞれの範囲内にあるかどうかを判定することによって前記第一の潜在的なロック点への近接が解析される、請求項 7記載の遅延ロックループ。

**【請求項 9】**

前記所定の時間期間の値が、二つの隣り合う電圧制御遅延線の取り出される出力の間の遅延時間のある割合である、請求項 8記載の遅延ロックループ。

**【請求項 10】**

クロック信号についての遅延を与える遅延ロックループであって、複数の遅延のところに複数の潜在的なロック点をもち：

前記複数の潜在的なロック点のうち第一の潜在的なロック点への近接を検出するロック検出器と；

前記ロック検出器の出力に結合された初期化コントローラを有しており、前記初期化コントローラが：

ある初期遅延から一方向にクロック信号の遅延を変化させ；

第一の潜在的なロック点をスキップし、前記複数の潜在的なロック点のうちから選択される動作点を探索するために前記と同じ一方向に遅延を変化させ続け； 20

動作点への所望の度合いの近接が検出されると、当該遅延ロックループの通常動作を許容する、 30

論理を含んでいる、

遅延ロックループ。

**【請求項 11】**

遅延ロックループ(DLL)を初期化する方法であって、前記DLLは位相検出器および前記位相検出器に結合された制御電圧発生器を含み、前記位相検出器は前記制御電圧発生器によって積分されてDLL制御電圧を与えるよう適応された信号を出力し、当該方法は：

初期制御電圧を設定するために前記制御電圧発生器に第一の信号(RST)を提供する段階と；

アサートされているときにDLL内で初期化プロセスが行われているという指標を与える、前記第一の信号と異なる第二の信号を前記位相検出器において受信する段階と； 40

前記第二の信号がアサートされている場合、前記DLL制御電圧を安定性が増したDLL動作領域に位置される目標電圧レベルに近づけるような仕方で前記DLL制御電圧の調整を引き起こすよう前記出力される信号を制御する段階とを有する、方法。

**【請求項 12】**

前記制御する段階が、前記出力される信号のうちの選択された一つの生成を妨げることを含む、請求項 11記載の方法。

**【請求項 13】**

前記制御する段階のあとに、前記初期化プロセスが完了されたとの指標を受信する段階 50

をさらに有する、請求項1\_1または1\_2記載の方法。

【請求項 1 4】

前記指標が、前記第二の信号がデアサー<sup>ト</sup>されることである、請求項1\_3記載の方法。

【請求項 1 5】

遅延ロックループ (DLL) であつて：

電圧制御遅延線と；

初期制御電圧を設定するための第一の信号を受信するよう適応され、前記電圧制御遅延線にDLL制御電圧を与える制御電圧発生器と；

位相検出器とを有しており、該位相検出器は

i ) 通常動作のもとで、前記制御電圧発生器による積分のために少なくとも二つの信号を出力し；

i i ) アサー<sup>ト</sup>されているときにDLL内で初期化プロセスが行われているという指標を与える、前記第一の信号とは異なる第二の信号を受信し；

i i i ) 前記第二の信号がアサー<sup>ト</sup>されている場合、前記出力される信号を制御して、前記DLL制御電圧を安定性が増したDLL動作領域に位置される目標電圧レベルに近づけるような仕方で前記DLL制御電圧の調整を引き起こすようにする、

遅延ロックループ。

【請求項 1 6】

前記初期化プロセスの完了時に、前記位相検出器が完了の指標を受信する、請求項1\_5記載の位相ロックループ。

20

【請求項 1 7】

前記指標が、前記第二の信号がデアサー<sup>ト</sup>されることである、請求項1\_6記載の位相ロックループ。

【請求項 1 8】

参照クロックと遅延されたフィードバック・クロックのエッジが第一の所定の時間期間以内にあるかどうかを判定するよう前記初期化プロセスの間使うための粗い整列判定要素をさらに有する、請求項1\_5ないし1\_7のうちいずれか一項記載の遅延ロックループ。

【請求項 1 9】

前記粗い整列判定要素がロック検出器であり、前記位相検出器が、参照クロックと遅延されたフィードバック・クロックのエッジが前記第一の所定の時間期間より短い第二の所定の時間期間以内にあるかどうかを判定するよう適応されている、請求項1\_8記載の遅延ロックループ。

30

【請求項 2 0】

参照クロック信号についての遅延を与える遅延ロックループであつて、当該遅延ロックループは少なくとも一つの潜在的なロック点をもち：

前記少なくとも一つの潜在的なロック点への近接を検出するロック点近接検出器と；

前記ロック点近接検出器の出力に結合された初期化コントロール回路と；

マルチプレクサおよび前記マルチプレクサの入力に結合された出力をもつ少なくとも一つの反転器を有する反転回路であつて、前記参照クロック信号の遅延を変えるために前記初期化コントロール回路の出力に基づいて異なる遅延をもつ二つのバージョンのクロック信号のうちの単一の信号の選択を可能にする反転回路と；

40

前記反転回路に結合された出力を有する可変遅延線とを有する、

遅延ロックループ。

【請求項 2 1】

前記少なくとも一つの潜在的なロック点が、複数の遅延のところにある複数の潜在的なロック点である、請求項2\_0記載の遅延ロックループ。

【請求項 2 2】

前記複数の潜在的なロック点が三つ以上である、または前記複数の潜在的なロック点の数が約3ないし5の範囲にある、請求項2\_1記載の遅延ロックループ。

【請求項 2 3】

50

前記可変遅延線が電圧制御遅延線である、請求項2\_0記載の遅延ロックループ。

**【請求項 2\_4】**

前記電圧制御遅延線が直列に接続された複数のシングル・エンドのバッファを有する、請求項2\_3記載の遅延ロックループ。

**【請求項 2\_5】**

前記電圧制御遅延線が直列に接続された複数の差動バッファを有する、請求項2\_3記載の遅延ロックループ。

**【発明の詳細な説明】**

**【背景技術】**

**【0\_0\_0\_1】**

10

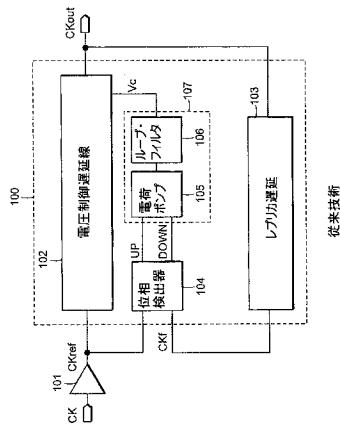

図1は、従来技術で通常の遅延ロックループ(DLL: delay locked loop)100のプロック図である。DLLの主な機能は、立ち上がりエッジを揃えることにより二つのクロック信号を同期させることである。外部から供給されるクロック信号CKはクロック・バッファ101によってバッファリングされて参照クロック信号CKrefを与え、その参照クロック信号が電圧制御遅延線(VCDL: voltage controlled delay line)102および位相検出器(PD: phase detector)104に結合される。電圧制御遅延線102はDLL出力クロック信号CKoutを生成する。これはCKrefの遅延バージョンであり、クロックツリーと称されるバッファリング構造を通じて、装置内のさまざまな回路に向けて経路制御される。

**【0\_0\_0\_2】**

20

クロックツリーのある分枝の端末ノードでフィードバック・クロック信号CKfが引き出されるか、あるいはクロックツリー分枝のレプリカ、すなわちレプリカ遅延回路103に出力クロック信号CKoutを加えることによってフィードバック・クロック信号CKfが得られ、これがPD104にフィードバックされる。遅延モデルまたはクロックツリー分枝レプリカとしても知られるレプリカ遅延回路103は、クロックツリーの多段のバッファリング構造によって出力クロック信号CKoutに加えられるあらゆる遅延を再現する。遅延は、論理ゲートおよびバッファを通じたあらゆる伝搬遅延および長い線の寄生インピーダンスによって引き起こされる遅延を含む。フィードバック・クロック信号CKfの最終的な同期されたバージョンがクロックツリーの全分枝の末端で出力される。VCDL102によって生成される遅延は可変であり、VCDL102に加えられる可変制御電圧Vcを通じて制御可能である。生成される遅延をVCDL102によって変えられることを利用して、DLL100は参照クロック信号CKrefとフィードバック・クロック信号CKfをクロック信号(CKref、CKf)の立ち上がりエッジを揃えることにより同期させる。

**【0\_0\_0\_3】**

30

位相検出器104は典型的には、参照クロック信号CKrefとフィードバック・クロック信号CKfとの間の位相差に依存してUPおよびDOWN出力信号上に可変幅のパルスを生成する。UPおよびDOWN出力信号上の可変幅のパルスは、電荷ポンプ(charge pump)105および該電荷ポンプ105の出力に結合されたループ・フィルタ106によって積分され、それによりVCDL102のための可変制御電圧Vcが与えられる。制御電圧Vcは、フィードバック・クロック信号CKfと参照クロック信号CKrefの立ち上がりエッジを揃えるためにVCDL102によって参照クロック信号CKrefに加えられるべき遅延を決定する。電荷ポンプ105とループ・フィルタ106は一緒になって制御電圧発生器107を構成する。

40

**【0\_0\_0\_4】**

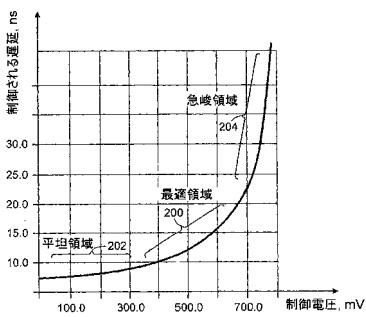

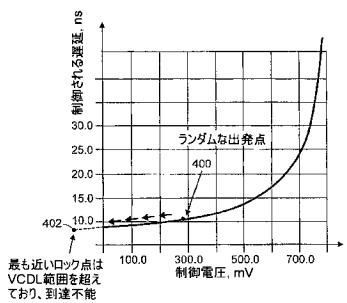

図2は、典型的な制御電圧Vcに対する制御された遅延特性を示すグラフである。特性は非線形であり、平坦領域202、最適領域200および急峻領域204を含む。平坦領域202では、比較的小さな遅延範囲のためにも制御電圧Vcの広い変動が必要とされる。

**【0\_0\_0\_5】**

急峻領域204では、制御電圧Vcの小さな変動が大きな遅延範囲を与える。よって、急峻領域204では、制御電圧Vcの小さなノイズ擾乱が遅延の大きな変動に、ひいてはクロック・ジッタの増大につながるので、VCDLは非常に高感度である。そのような高感度では

50

、安定した発振のないループ動作を提供することがより困難にもなる。

#### 【0006】

「最適領域」200では、制御電圧の変化に対する遅延の変化はほどほどである。よって、DLL100は、発振やドリフトや蓄積するノイズなしに「最適領域」で動作する。

#### 【0007】

ロック点とは、特性中で、DLLがロックできる任意の点である。特性上には複数のロック点があつてもよい。動作点とは、通常の動作の間にDLLがロックされるロック点である。DLLを設計する際の一つの重要な側面は、特性中で正しい動作点を選び、電源投入またはリセット後、その動作点にすばやく到達し、ロックするようDLLを操ることである。このプロセスは典型的にはDLL初期化と称される。DLLの適正な初期化により、良好なDLLパフォーマンスおよび確固としたロックが保証される。10

#### 【0008】

正しい動作点を選択すると、制御電圧Vcは安定動作領域に関係した目標電圧レベルに設定される。安定したDLL動作を保証するため、DLLは、VCDL遅延対制御電圧の特性の「最適領域」200内の動作点に初期化されるべきである。

#### 【0009】

DLLが動作点に達したのち、温度および電力供給といった動作条件の変化のため、動作点が動くことがありうる。よって、DLL設計のもう一つの重要な側面は、動作条件が変化する間、動作点を遅延対電圧特性上のロック点から所定の限界内に保つことである。制御電圧Vcの変動は高々電源電圧の変動に制限され、しばしば制御電圧Vcの変動は電源電圧の変動よりも小さい。したがって、図2に示される遅延対制御電圧特性は両端で無限にはなっておらず、動作条件が変わると、動作点が特性の左極限または右極限のどちらかにドリフトし、DLLが最終的にロックを失うことがありうる。これは、DLLが特性の二つの端いはずれかに近すぎる動作点に初期化される場合に起こる確率がとりわけ高い。20

#### 【0010】

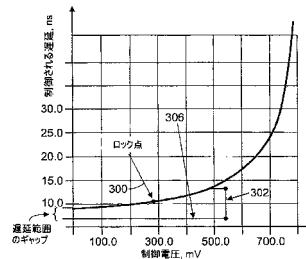

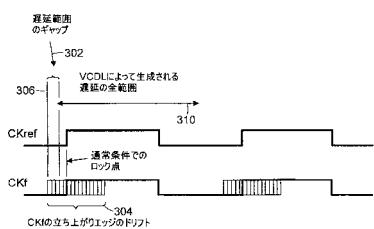

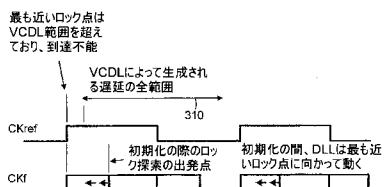

動作点を特性の左側のロック点にロックさせることができないという意味でよりよい領域だからである。しかしながら、動作点が特性の左端に近すぎると、動作条件の変化のためにDLLが特性の左極限に達することができない。この状況は図3Aおよび3Bに示されている。

#### 【0011】

図3Aのグラフは、制御電圧に対する遅延の特性の左端に近いロック点300を示している。図3Bは、図3Aの制御電圧に対する遅延の特性に対応するクロック信号タイミング図である。動作点は、通常の条件では、ロック点300にある。動作条件の変動を補償するためにVCDLにおける遅延の範囲302が必要とされる。クロック信号タイミング図を参照すると、フィードバック・クロック信号CKfの立ち上がりエッジのドリフト304が図3Aのグラフに示された遅延の範囲302に対応している。遅延範囲302の最小の遅延306は、遅延範囲のギャップ308によって示されるように、VCDL310によって生成される遅延の全範囲を超えている。よって、動作点はVCDL範囲の端まで動くことができ、DLLにロックを失わせる。30

#### 【0012】

もう一つの潜在的なリスクは、起動の際に、DLLが、特性上のランダムな点から、探索方向について何の制約もなしにロック点の探索を開始するということである。外部供給されるクロック信号CKは自走(free running)なので、リセットまたは電源投入後のフィードバック・クロック信号CKfと参照クロック信号CKrefとの間の初期位相関係は知られていない。また、電源投入またはリセット後、初期のDLLのロックされていない動作点の位置は未知であり、特性上の任意のところでありうる。よって、VCDL遅延は、フィードバック・クロック信号CKfの立ち上がりエッジと参照クロック信号CKrefの立ち上がりエッジのどちらがPD104(図1)によって先に検出されるかに依存して初期に増加させられることもあれば、減少させされることもある。したがって、VCDL遅延が初期に調整される方向は予測不可能である。4050

## 【0013】

図4Aのグラフは、ある探索方向へのロック点の初期探索で、ロックに到達できる前にVCDL102(図1)の遅延限界に突き当たる結果となる場合を示している。図4Bは、図4Aに示された探索に対応するクロック信号タイミング図である。ロック点の探索はランダムな探索点400で始まる。DLLが特性の端に近い点から出発してその端に向かって進む場合、ロックに到達できる前にVCDLの遅延限界に突き当たることがありうる。図4A、4Bに示した例では、初期化の間、DLLはVCDL範囲を超えていて到達できない最近接ロック点402に向かって予測不可能に動く。たとえば、位相検出器104(図1)が初期に、VCDL範囲310を超えた最近接ロック点402の方向にDLL100を操るUP/DOWNパルスを生成する場合にこの状況が起こり得る。

10

## 【0014】

DLLにおける可変VCDL遅延の範囲も重要である。通常、可変VCDL遅延の範囲は、最小の遅延がDLL仕様が要求するよりやや高いクロック周波数に対応し、最大遅延がやや低いクロック周波数に対応するように計算される。可変VCDL遅延はマージンを保証するために計算される。広いクロック周波数範囲にわたって動作するよう設計されるDLLのためには、すなわち、クロック周期が定数値でなく、可能なすべての値が同じVCDLによって受け容れられる場合、VCDLは一層広い範囲の遅延を生成する必要がある。結果として、典型的には、特定の周波数をもつクロック信号のためのVCDL特性上にいくつかの可能なロック点がある。より高いクロック周波数については、VCDLはクロック周波数の倍数よりも長い遅延を生成できる。目標は、安定したロック条件および低い出力クロック・ジッタを保証できる点にロックすることである。たいていの場合、VCDLについての遅延範囲は、DLL特性上の可能なロック点の数が2より多いが約3ないし5は超えないように選ばれる。ロック点が多いすぎると、それらのロック点は特性上で互いに密接して共存することになり、ノイズによって擾乱されればDLLはあるロック点から別のロック点にジャンプし始め、それにより一時的にロックを失うことがありうるのである。

20

【特許文献1】米国特許第4,338,569号明細書

【特許文献2】米国特許第4,590,602号明細書

【特許文献3】米国特許第4,604,582号明細書

【特許文献4】米国特許第4,623,805号明細書

【特許文献5】米国特許第4,754,164号明細書

30

【特許文献6】米国特許第4,755,704号明細書

【特許文献7】米国特許第5,109,394号明細書

【特許文献8】米国特許第5,223,755号明細書

【特許文献9】米国特許第5,272,729号明細書

【特許文献10】米国特許第5,317,202号明細書

【特許文献11】米国特許第5,440,514号明細書

【特許文献12】米国特許第5,440,515号明細書

【特許文献13】米国特許第5,544,203号明細書

【特許文献14】米国特許第5,604,775号明細書

【特許文献15】米国特許第5,614,855号明細書

40

【特許文献16】米国特許第5,796,673号明細書

【特許文献17】米国特許第6,067,272号明細書

【特許文献18】米国特許第6,205,083号明細書

【特許文献19】米国特許第6,337,590号B1明細書

【特許文献20】米国特許第6,504,408号B1明細書

【特許文献21】米国特許第6,518,807号明細書

【特許文献22】米国特許第6,542,040号明細書

【特許文献23】米国特許第6,633,201号明細書

【特許文献24】米国特許第6,670,834号明細書

【特許文献25】米国特許第6,828,835号明細書

50

|                                            |    |

|--------------------------------------------|----|

| 【特許文献 26】米国特許第 6 , 867 , 627 号 B1 明細書      |    |

| 【特許文献 27】米国特許第 6 , 989 , 700 号明細書          |    |

| 【特許文献 28】米国特許出願公開第 2002 / 0089361 号 A1 明細書 |    |

| 【特許文献 29】米国特許出願公開第 2004 / 0264621 号明細書     |    |

| 【特許文献 30】米国特許出願公開第 2005 / 0035798 号 A1 明細書 |    |

| 【特許文献 31】米国特許出願公開第 2005 / 0093579 号明細書     |    |

| 【特許文献 32】米国特許第 5 , 233 , 314 号明細書          |    |

| 【特許文献 33】米国特許第 5 , 362 , 990 号明細書          |    |

| 【特許文献 34】米国特許第 5 , 473 , 283 号明細書          |    |

| 【特許文献 35】米国特許第 5 , 933 , 037 号明細書          | 10 |

| 【特許文献 36】米国特許第 6 , 124 , 755 号明細書          |    |

| 【特許文献 37】米国特許第 6 , 160 , 432 号明細書          |    |

| 【特許文献 38】米国特許第 6 , 229 , 362 号 B1 明細書      |    |

| 【特許文献 39】米国特許第 6 , 278 , 332 号 B1 明細書      |    |

| 【特許文献 40】米国特許第 6 , 316 , 987 号 B1 明細書      |    |

| 【特許文献 41】米国特許第 6 , 512 , 404 号 B2 明細書      |    |

| 【特許文献 42】米国特許第 6 , 535 , 051 号 B2 明細書      |    |

| 【特許文献 43】米国特許第 6 , 603 , 340 号 B2 明細書      |    |

| 【特許文献 44】米国特許第 6 , 617 , 936 号 B2 明細書      |    |

| 【特許文献 45】米国特許第 6 , 636 , 098 号 B1 明細書      | 20 |

| 【特許文献 46】米国特許第 6 , 642 , 753 号 B2 明細書      |    |

| 【特許文献 47】米国特許第 6 , 664 , 829 号 B1 明細書      |    |

| 【特許文献 48】米国特許第 6 , 667 , 641 号 B1 明細書      |    |

| 【特許文献 49】米国特許第 6 , 710 , 665 号 B2 明細書      |    |

| 【特許文献 50】米国特許第 6 , 741 , 110 号 B2 明細書      |    |

| 【特許文献 51】米国特許第 6 , 744 , 292 号 B2 明細書      |    |

| 【特許文献 52】米国特許第 6 , 771 , 114 号 B2 明細書      |    |

| 【特許文献 53】米国特許第 6 , 861 , 916 号 B2 明細書      |    |

| 【特許文献 54】米国特許第 6 , 924 , 992 号 B2 明細書      |    |

| 【特許文献 55】米国特許第 6 , 954 , 511 号 B2 明細書      | 30 |

| 【特許文献 56】米国特許第 7 , 092 , 689 号 B1 明細書      |    |

| 【特許文献 57】米国特許出願公開第 2002 / 0041196 号 A1 明細書 |    |

| 【特許文献 58】米国特許出願公開第 2003 / 0076142 号 A1 明細書 |    |

| 【特許文献 59】米国特許出願公開第 2004 / 0057546 号 A1 明細書 |    |

| 【特許文献 60】欧州特許第 0484059 号 A2 明細書            |    |

| 【特許文献 61】欧州特許第 0755120 号 A1 明細書            |    |

| 【特許文献 62】欧州特許第 1292033 号 A1 明細書            |    |

| 【特許文献 63】米国特許第 6 , 314 , 052 号 B2 明細書      |    |

| 【特許文献 64】米国特許第 6 , 314 , 150 号 B1 明細書      |    |

| 【特許文献 65】米国特許第 6 , 330 , 296 号 B1 明細書      | 40 |

| 【特許文献 66】米国特許第 6 , 448 , 820 号 B1 明細書      |    |

| 【特許文献 67】米国特許第 6 , 549 , 041 号 B2 明細書      |    |

| 【特許文献 68】米国特許第 6 , 239 , 634 号 B1 明細書      |    |

| 【特許文献 69】米国特許第 6 , 088 , 255 号明細書          |    |

| 【特許文献 70】米国特許第 6 , 166 , 990 号明細書          |    |

| 【特許文献 71】米国特許第 6 , 100 , 736 号明細書          |    |

| 【特許文献 72】米国特許第 6 , 556 , 643 号明細書          |    |

| 【特許文献 73】米国特許第 6 , 346 , 839 号明細書          |    |

| 【特許文献 74】米国特許第 6 , 642 , 762 号明細書          |    |

| 【特許文献 75】米国特許第 6 , 437 , 618 号明細書          | 50 |

【特許文献 7 6】米国特許第 5 , 9 9 4 , 9 3 4 号明細書

【特許文献 7 7】米国特許第 6 , 7 3 1 , 6 6 7 号明細書

【特許文献 7 8】米国特許第 6 , 4 0 7 , 5 9 7 号明細書

【特許文献 7 9】米国特許出願公開第 2 0 0 2 / 0 0 0 5 7 6 3 号明細書

【特許文献 8 0】米国特許出願公開第 2 0 0 3 / 0 0 9 0 2 9 6 号 A 1 明細書

【特許文献 8 1】米国特許出願公開第 2 0 0 7 / 0 0 0 7 9 4 1 号明細書

【特許文献 8 2】米国特許出願公開第 2 0 0 4 / 0 0 5 9 8 4 6 号明細書

【特許文献 8 3】米国特許第 7 , 2 1 5 , 5 9 6 号明細書

【特許文献 8 4】米国特許第 7 , 0 9 8 , 7 1 4 号明細書

【特許文献 8 5】米国特許出願公開第 2 0 0 5 / 0 1 6 2 2 0 0 号明細書 10

### 【発明の開示】

#### 【発明が解決しようとする課題】

##### 【0 0 1 5】

既知の技術においては、DLLの確固としたロックおよび良好なパフォーマンスを保証するための解決策は、二重ループ (dual-loop) 構造のような込み入った構造を含む。クロック信号の多重位相 (multiphase) バージョンまたは最も単純な場合ではクロック反転も使用される。しかしながら、それらはVCDLにおける位相引き出し口 (phase tap) の数を最小化するため、および / またはより段数の少ない遅延線を提供するために使用される。位相引き出し口は今度は、パイプライン段の同期における柔軟性を増加させるのに使われるが、DLLそのものの確固としたロックおよび安定したパフォーマンスを達成する目的のためではない。 20

##### 【0 0 1 6】

典型的には、DLLの設計者は、初期化のような「副次的」問題を扱うのに多くの時間を費やすのに消極的で、伝統的な「実証済みの」手法に頼る。したがって、従来の手法の問題を緩和するDLL初期化方法を提供することが望ましい。

#### 【課題を解決するための手段】

##### 【0 0 1 7】

我々は、遅延対制御電圧特性のどちらの端にも近すぎない正しい動作点にDLLが初期化されることを保証するための方法および装置を提示する。初期化回路は、DLLがロック点を探索する際に、常に遅延対電圧特性の一端に対応する初期遅延から出発し、それにより最終的なロックに達するまで、制御される遅延を変動させるのが一方向にのみ許容されるよう、DLLを強制する。最終的なロックに達したあとは、ロック点を動的に維持するためには、DLLは必要に応じて制御される遅延を増加または減少させることができる。本発明によって提供される方法によれば、DLLは最初のロック点をスキップすることも強制される。スキップするプロセスは、DLL内部クロック信号の位相をシフトさせることによってより簡単かつより高速にされる。 30

##### 【0 0 1 8】

本発明のある種の諸実施形態では、DLLは、遅延対制御電圧特性の最小遅延に対応する端点から出発することによってロック点を探索する。初期化の間のロック点探索の方向は、遅延を増加させることのみに制約される。すなわち、位相検出器は、該位相検出器の内部構造に依存して、遅延増に対応するUPおよびDOWN信号の組合せのみを生成するよう強制される。DLLは最初のロック点に達するまで遅延を増加させる。次いで、遅延されたクロック信号の位相がシフトさせられる。ある実施形態では、クロック信号が反転される。これは、最初のロック点をスキップして次のロック点に進むことをDLLに強制する。この位相シフトの結果として、位相検出器はその二つの入力クロック信号の間の新しい位相差を検知し、特性上の動作点に達するまでUPおよびDOWN信号を生成することを開始する。これはまるまる 1 クロック周期の継続時間にほぼ等しい、VCDL遅延時間の総増加につながる。動作点に達したあとは、遅延変動は増加または減少のどちらもされることができる。DLLが初期化されたあとでは、DLLは入力クロック信号位相ドリフトおよび動作条件変動を補償し、よって安定なロックを動的に維持する。 40 50

**【0019】**

他の諸実施形態では、DLLは、遅延対制御電圧特性の最大遅延に近い点から出発することによってロック点を探索する。初期化の間のロック点探索の方向は、遅延を減少させることのみに制約される。すなわち、位相検出器は、該位相検出器の内部構造に依存して、遅延減に対応するUPおよびDOWN信号の組合せのみを生成するよう強制される。この実施形態は、遅延対制御電圧特性が図2の例よりも非線形性がおそらくやや弱く、境界制御電圧値に対応する有限の最大遅延を有する場合に適用される。換言すれば、VCDLが最小遅延および最大遅延の両方で、つまり制御電圧境界値の両方においてうまく動作できる場合である。この場合にもVCDL出力クロック反転および位相シフトが適用できる。

**【0020】**

遅延ロックループは、ロック検出器と、該ロック検出器の出力に結合された初期化コントロールとを含む。ロック検出器はロック点への近接を検出する。初期化コントロールは、初期遅延から一方向に遅延を変化させる。初期化コントロールは第一のロック点をスキップし、第一のロック点への近接の検出に際しては、動作点を探索するために遅延を前記一方向に変化させ続ける。動作点への近接を検出すると、初期化コントロールは遅延の増加および減少の両方を可能にする。動作点は第二のロック点でもよい。

**【0021】**

ロック検出器は異なる所定の時間期間をもつ複数の段を含みうる。各段は、異なる精度でロック点への近接を示す。初期化状態は電源投入またはリセットでありうる。第一のロック点は、クロック信号の位相をシフトさせる（単純な場合ではクロック信号を反転させる）ことによってスキップされる。クロック信号の位相は、クロック信号の周期のある割合だけシフトされる。電圧制御遅延線の途中で引き出された出力が、クロック信号の位相をシフトさせるために使われる。クロック信号の位相は、当該遅延ロックループ内の内部クロック信号に対して位相シフトを実行することによってシフトされうる。内部クロック信号は、電圧制御遅延線の入力クロック信号または電圧制御遅延線の出力クロック信号でありうる。

**【0022】**

ロック点の近接は、参照クロックと遅延されたフィードバック・クロックのエッジの整列に基づいて検出される。近接は、複数の所定の時間期間の少なくとも一つを適用することによって解析される。所定の時間期間の値は、電圧制御遅延線内の諸段のレプリカに基づくことができ、クロック周期の4分の1より短い、あるいは二つの隣接する電圧制御遅延線の引き出された出力の間の遅延時間のある割合でもよい。

**【0023】**

本発明の以上のこととを含むさまざまな目的、特徴および利点は、本発明の好ましい諸実施形態の以下の、付属の図面において例示される、より具体的な記載から明らかとなろう。図面においては、同様の参照符号は異なる図を通じて同じ部分を指す。図面は必ずしも縮尺通りではなく、本発明の原理を解説することに重点が置かれている。

**【発明を実施するための最良の形態】****【0024】**

本発明の好ましい諸実施形態について以下に述べる。

**【0025】**

以下の記述においては本発明の十分な理解を与えるために数多くの個別的詳細が述べられる。しかしながら、本発明がこうした個別的詳細なしでも実施しうることは理解される。他方では、本発明を埋没させないよう、よく知られた構造および/またはプロセスは詳細に記述したり図示したりしていない。記述および図面において、同様の符号は同様の構造またはプロセスを指す。一般に、遅延ロックループ(DLL)の動作は当技術分野においてよく知られており、本発明の諸側面を明確にするために必要な場合を除き、さらに説明することはしない。

**【0026】**

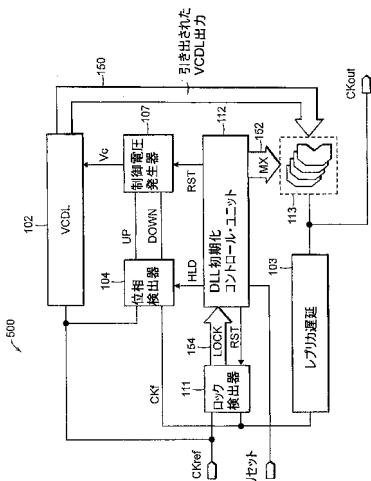

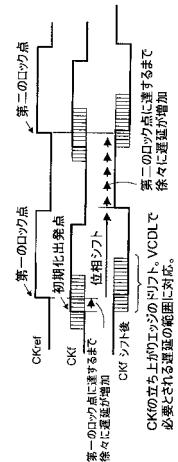

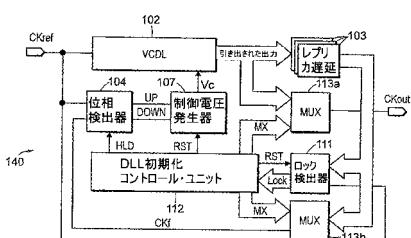

図5は、本発明の原理に基づく、電源投入またはリセット後にDLL500を初期化する

10

20

30

40

50

ためのDLL初期化コントロール112を含む遅延ロックループ(DLL)500のある実施形態のブロック図である。DLL500は、図1に示した従来技術のDLLとの関連で述べたような、電圧制御遅延線(VCDL)102、位相検出器(PD)104、制御電圧発生器107およびレプリカ遅延103を含む。本DLLはまた、電源投入またはリセット後にDLL500を初期化するために使われる、マルチプレクサ113、ロック検出器111およびDLL初期化コントロール112をも含む。

#### 【0027】

参照クロック信号CKrefが、電圧制御遅延線(VCDL)102の入力、位相検出器(PD)104およびロック検出器111の二つの入力の一方に結合されている。VCDL102は、引き出された位相シフトされた出力クロック信号116を生成する。該信号116のそれぞれは、参照クロック信号CKrefの遅延バージョンである。DLL出力クロック信号CKoutは、DLL初期化コントロール112から出力されるMXコード152に依存して、引き出されたVCDL出力116からマルチプレクサ113を通じて選択される。出力クロック信号CKoutはたとえば、クロックツリーと称されるバッファリング構造を通じて半導体チップ上のさまざまな回路に向けて経路制御される。

#### 【0028】

フィードバック・クロック信号CKfは、参照クロック信号CKrefがVCDL102およびレプリカ遅延回路103によって遅延されたバージョンである。フィードバック・クロック信号CKfは、クロックツリーのある分枝のある端末ノードで引き出される。あるいはまた、ここではレプリカ遅延回路103と称されるクロックツリー分枝のレプリカに出力クロック信号CKoutを加えることによって得ることもできる。フィードバック・クロック信号CKfはPD104およびロック検出器111にフィードバックされる。遅延モデルまたはクロックツリー分枝レプリカとしても知られるレプリカ遅延回路103は、クロックツリーの多段のバッファリング構造によってCKout信号に加えられるあらゆる遅延を再現する。遅延は、論理ゲートおよびバッファを通じたあらゆる伝搬遅延および長い線の寄生インピーダンスによって引き起こされる遅延を含む。フィードバック・クロック信号CKfは、クロックツリー分枝の端末ノードにおけるクロック信号を複製する。たとえば、半導体チップにおいて、諸端末ノードにおけるクロック信号が諸同期プロックのクロック入力に加えられ、それらは通常、参照クロック信号CKrefと同期されている。

#### 【0029】

DLL入力または参照クロック信号CKrefはVCDL102に結合される。VCDL102は可変遅延をもつ同様のバッファからなるチェーンを含む。チェーンは数十または数百のバッファさえ含むことができる。VCDL102によって生成される遅延は可変であり、制御電圧発生器107を通じてVCDL102中の各バッファに加えられる可変制御電圧Vcを通じて制御可能である。

#### 【0030】

初期化プロセスの最初に、制御電圧Vcは境界電圧レベル(端点)に、すなわちVCDL102の遅延が最小遅延に設定される電圧レベルに設定される。該境界電圧レベルはたとえば、電源電圧または接地であることができる。DLL初期化コントロール112によって生成されるRST信号が制御電圧発生器107に結合されて、初期制御電圧Vcが設定される。初期制御電圧Vcの設定は、たとえば、Vcノードを電源ノード(レール[rail])または接地のどちらかと単一トランジスタ・スイッチを通じて短絡させることによって実行できる。

#### 【0031】

位相検出器104は、参照クロック信号CKrefとフィードバック・クロック信号CKfとの間の位相差に依存してUPおよびDOWN出力信号上に可変幅のパルスを生成する。両クロック信号は位相検出器104の入力に結合される。UPおよびDOWN出力信号上の可変幅のパルスは、制御電圧発生器107によって積分され、それにより直流(DC)モードの制御電圧Vcが与えられる。ある実施形態では、制御電圧発生器107は、図1のDLL100との関連で述べたように電荷ポンプ105およびループ・フィルタ106を含みうる。制御電圧発生器107は、当業者によく知られているように、フィルタ動作および電圧レベル・シフ

10

20

30

40

50

ト動作を適用することによってPDの出力信号(UP、DOWN)を積分する。VCDLの実施形態は、図7および図8との関連でのちに述べる。

#### 【0032】

Dieter Haerleによる「High Output Impedance Charge Pump for PLL/DLL」との名称の同時係属中の米国特許出願(米国特許出願第60/528,958号)は、制御電圧発生器の中の電荷ポンプのある実施形態を記載しており、その内容はここに参照によってその全体において組み込まれる。電荷ポンプのもう一つの例は、Patrik Larsson, 「A 2-1600 MHz 1.2-2.5 V CMOS Clock Recovery PLL with Feedback Phase-Selection and Averaging Phase-Interpolation for Jitter Reduction」1999 IEEE ISSCC, WA 20.6, 0-7803-5129-0/99, 図20.6.3に見出すことができ、その内容はここに参照によってその全体において組み込まれる。10

#### 【0033】

位相検出器104は、入力に加えられたクロック信号(CKref、CKf)の間の位相差に比例する、ある電気的な特性(たとえば電圧レベルまたはパルス幅)の出力信号(UP、DOWN)を生成する任意の位相検出器であることができる。位相検出器は当業者にはよく知られたものであり、本発明の範囲を超える。位相検出器の例は、Yongsam Moon et al, "An All-Analog Multiphase Delay-Locked Loop Using a Replica Delay Line for Wide Range Operation and Low-Jitter Performance", JSSC Vol. 35, No. 3, March 2000, pp. 377-384に記載されており、その内容はここで参照によってその全体において組み込まれる。20

#### 【0034】

生成される遅延をVCDL102によって変えられることを利用して、DLL100は参照クロック信号CKrefとフィードバック・クロック信号CKfをそれぞれの立ち上がりエッジを揃えることにより同期させる。制御電圧Vcは、フィードバック・クロック信号CKfと参照クロック信号CKrefの立ち上がりエッジを揃えるためにVCDL102が参照クロック信号CKrefに加えるべき遅延を決定する。

#### 【0035】

参照クロック信号CKrefおよびフィードバック・クロック信号CKfはロック検出器111の入力にも結合される。ロック検出器111は入力クロック信号(CKref、CKf)の立ち上がりエッジの相互の位置付けを評価し、両クロック信号の立ち上がりエッジの間のタイミング差を示すLOCK指示信号154を発生させる。LOCK指示信号154は単一ビット信号でも、多ビット・コードであってもよい。ロック検出器111のある実施形態の内部構造および動作はのちに図9との関連で論じる。30

#### 【0036】

マルチプレクサ113は、多ビット・コード(MX152)の値に従って、いくつかの入力信号(本記載では引き出されたVCDL出力116)のうちから、その単一の出力(本記載ではCKout)に伝送されるべき一つを選択する、当技術分野で既知の任意の好適な型のマルチプレクサである。引き出されたVCDL出力については、のちに図7および図8との関連で述べる。

#### 【0037】

DLL初期化コントロール112は初期化プロセスを管理し、初期化プロセスの適正なシーケンスを維持することを担う。DLL初期化コントロール112は、ロック検出器111から受信したLOCK指示信号154に基づいてコード(MX152)および信号(HLD、RST)についての適切な値も選択する。40

#### 【0038】

電源投入またはリセット後、DLL初期化コントロール112は、ロック検出器111および制御電圧発生器107をリセットするためにRST信号をアサートする。制御電圧発生器107から出力される制御電圧Vcは、最小のVCDL遅延を与える電圧レベルに設定される。DLL初期化コントロール112は、位相検出器104に結合されるHLD信号をもアサートする。HLD信号がアサートされている間は、位相検出器104は、適切なUP/DOWN信号を50

発生させることによってVCDL 102の遅延を増加させることができるのみである。ロック指示信号154の状態から、動作点が第一のロック点に近いことを検出すると、DLL初期化コントロール・ユニット112は、出力クロック信号CKoutの位相を切り換えるために適切なMXコード152を出力する。位相が切り換えられたのち、位相検出器104は、次のロック点に達するまで、ロック指示信号154によって指示される適切なUP/DOWN信号を発生させることを通じて制御電圧Vcを修正することによってVCDL遅延を増加させ続ける。

#### 【0039】

マルチプレクサ113は複数の入力および単一の出力をもつ。MXコード152は、引き出された(tapped)VCDL出力信号のうちから、その単一の出力に伝えられる一つを選択する。マルチプレクサ出力には、一時には一つの引き出されたVCDL出力信号しか伝えられない。MXコードの現在の値に対応する一つである。隣接する引き出されたVCDL出力の間には限られた数の遅延段しかないで、多重の引き出されたVCDL出力は、二つの隣り合う引き出された信号間の位相差が比較的小さく、クロック信号周期よりも短い、「位相グリッド」を生成する。隣接する引き出し口の間の位相差が小さいので、大きめの位相シフトを発生させるためには比較的多数の引き出し口をスキップしなければならない。よって、マルチプレクサの出力において要求される位相シフトが180°(大きな跳躍)に近い場合には、引き出されたVCDL信号の補角信号(complements)が使われ、必要であれば、その後、引き出し口間の小さな位相差(小さめの跳躍)を使ってより精密な調整が実行されうる。

#### 【0040】

次のロック点に達したのち、初期化プロセスは完了する。DLL初期化ユニット112はHLD信号をデアサーントし、位相検出器104は、本DLLの通常動作の間、VCDL102の遅延を増加させることも減少させることもできるようになる。

#### 【0041】

こうして、DLL初期化コントロール・ユニット112が初期化プロセスを制御する仕方は、VCDL遅延が最小遅延から出発し、遅延が第一のロック点に向かって増加し、第一のロック点がスキップされ、DLL500が第二のロック点でロックされるまで遅延がさらに増加させられるようなものである。DLL初期化コントロール・ユニット112の動作のさらなる詳細は、のちに図11との関連で論じる。

#### 【0042】

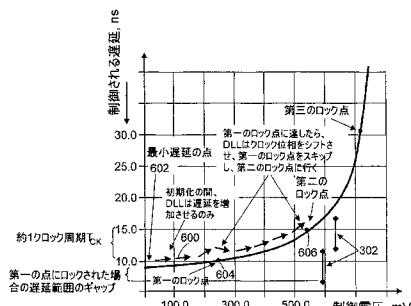

図6Aは、図5に示されたDLL500を使っての制御電圧に対する遅延の特性上での初期化プロセスを示すグラフである。図6Bは、図6Aに示された初期化プロセスに対応するクロック信号図である。図6Aおよび図6Bについて、図5との関連で述べる。

#### 【0043】

制御電圧Vcは最初に、境界電圧レベルに、すなわちVCDL102によって生成される最小遅延に対応する電圧にリセットされる。該境界電圧レベルはたとえば、電源電圧または接地であることができる。

#### 【0044】

リセットまたは電源投入後、PD104から出力されるUP/DOWN信号に基づいて制御電圧Vcが増加させられるにつれ、電圧制御遅延線(VCDL)102は、図6Aに示される最小遅延点602(遅延対制御電圧特性の再左端の点)から方向600に遅延を増加させ始める。

#### 【0045】

初期化プロセスの最初に、ロック検出器111は二つの入力クロック信号(CKref、CKf)の立ち上がりエッジの相対位置を評価する。その評価に基づいて、ロック検出器111は、両クロックの立ち上がりエッジの近接性の指標となるLOCK信号154を発生させる。ある実施形態では、LOCK信号154は多ビット・コードである。LOCK信号はDLL初期化コントロール・ユニット112によって受信される。DLL初期化コントロール・ユニット112は、LOCK信号154の値に基づいて多ビットの出力選択コードMX152を発生させる。出力選択コードMX152は、VCDL102から受信された引き出された位相シフトされた

10

20

30

40

50

出力信号 116 のうちから一つを選択するために使用される。

#### 【0046】

VCDL102を通じた遅延は、最小遅延点 602 から一方向に徐々に増加させられる。初期化の間、DLL初期化コントロール・ユニット112 から出力され、PD104 に結合されるHLD信号がアサートされ、PD104 が初期化状態に保持される。初期化状態にある間は、PDは、制御電圧Vcの適切な修正によってVCDL遅延が増加させられるのみのUPまたはDOWN信号のみを生成する。初期化プロセスは、参照クロック信号CKrefとフィードバック・クロック信号CKfの立ち上がりエッジが所定の近接度で揃うまで続く。該近接度は、参照クロック信号CKrefの周期の半分よりも実質的に小さいよう設定される。

#### 【0047】

10

参照クロック信号CKrefおよびフィードバック・クロック信号CKfの立ち上がりエッジが選択された近接度まで揃っていることを検出したのち、DLL初期化コントロール・ユニット112 による出力選択コードMX152 の適切な選択を通じて、出力クロック信号CKout が反転される（すなわち、デューティー・サイクル50%のクロック信号については180°シフトされる）。こうして、第一のロック点 604 がスキップされる。DLL初期化コントロール・ユニット112 によって制御されるHLD信号は、PD104 を初期化状態に保持し続け、その結果、VCDL遅延は引き続き増加する。

#### 【0048】

第一のロック点 604 がスキップされたのち、DLL500 は、徐々に制御電圧Vcを増加させることによって遅延を増加させ続け、参照クロック信号CKrefとフィードバック・クロック信号CKfの立ち上がりエッジの精密な整列に達するまで続ける。精密な整列は、LOCK信号154 によって、あるいはPD104 のUPおよびDOWN出力信号の状態によって指示される。前の文で述べたように初期化プロセスにおける微細整列指示デバイスとしてPD104 が使われる場合、PD104 は、初期化専用であって、制御電圧発生器107 の入力に結合されていない別個のUP出力およびDOWN出力の対を持ちうる。PD104 の方式に依存して、これが必要であることもある。というのも、制御電圧発生器107 の入力に接続されたUPおよびDOWN入力は、初期化の間、無効にされることがあるからである。

20

#### 【0049】

第二のロック点 606 に達したのち、HLD信号の状態がデアサートに切り換えられ、PD104 の通常動作が許容されるようになる。これでDLL500 は、必要に応じてVCDL遅延を増加または減少させることが許容される。PD104 を解放することにより、初期化プロセスは終了され、DLLの通常動作が可能にされる。

30

#### 【0050】

ある実施形態では、ロック指示信号154 は多ビットのロック・コードである。多ビットLOCKコード154 は、DLL500 に、所望のロック点 606 に対応する引き出されたVCDL出力116 を選択することによって所望のロック点に向かってすばやく移動することを許容する。これにより、制御電圧Vcが徐々に変化させられるのを待つ必要なく、第二の（所望される）ロック点 606 にすばやく到達されることが許容される。代替的な実施形態では、LOCK信号154 は単一ビットである。

#### 【0051】

40

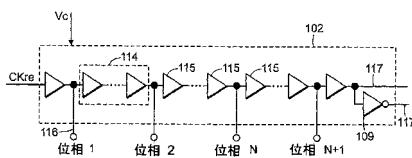

図7は、図5に示されたVCDL102 のシングルエンドの実施形態のブロック図である。VCDL102 は、直列に接続されて遅延線を与える、複数のシングルエンド・バッファ115 を含む。各バッファ115 は一つのシングルエンド入力および一つのシングルエンド出力を有している。一つのバッファ115 のシングルエンド出力は、VCDL102 における後続バッファのシングルエンド入力に結合されている。制御電圧Vcは、各バッファ115 に直接供給され、各バッファによって生成される遅延時間を決定する。制御電圧Vcの各バッファ115 への接続は、簡単のため、図7には示していない。この実施形態では、VCDL出力信号117 もシングルエンドである。VCDL出力信号の反転バージョン（デューティー・サイクル50%のクロックについては180°シフトされている）117 が反転器109 の出力を通じて与えられる。反転器109 の入力はVCDL出力信号117 に結合されている。

50

## 【0052】

参照クロック信号CKrefの中間遅延バージョンが、一群のバッファ114の出力を引き出すことによって得られる。複数の引き出し口116は、図5に示された引き出されたVCDL出力116をなす。各引き出し口116は、参照クロック信号CKrefの遅延された、あるいは位相シフトされたバージョンである。本発明の異なる諸実施形態では、VCDL102は複数の引き出された出力116または単一の出力信号117を、それぞれの補角信号117とともに、あるいは補角信号117なしで、出力できる。

## 【0053】

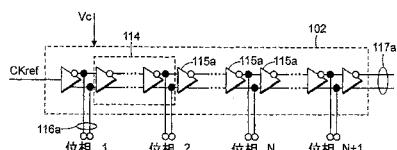

図8は、VCDL102のディファレンシャルエンドの実施形態のブロック図である。この実施形態では、VCDL102は、制御電圧Vcによって制御される複数の差動バッファ115aを含む。制御電圧Vcは各差動バッファ115a（簡単のため図示せず）に結合されている。前記複数の差動バッファ115aは直列に接続されている。この実施形態では、差動バッファ115aは差動入力および差動出力を有する。第一のバッファ115bは、シングルエンドの参照クロック信号CKrefを受け取るためのシングルエンド入力および差動出力を有する。VCDL102のディファレンシャルエンドの実施形態は、VCDLのシングルエンドの実施形態よりもノイズの影響の受けにくさの点でよりよい傾向がある。また、VCDL出力117aおよびすべての引き出された出力116aはいずれも信号およびその補角信号をもつ。各引き出された出力信号の補角信号が与えられることで、図7のシングルエンドの実施形態に示されていた反転器109の必要はない。VCDL102は複数の引き出された差動出力116aをもつこともできれば、単一の差動出力117aをもつこともできる。

## 【0054】

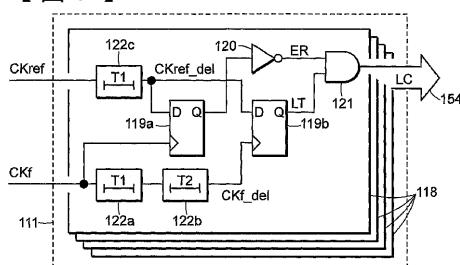

図9は、ロック検出器111のある実施形態の概略図である。ロック検出器111は、参照クロック信号CKrefとフィードバック・クロック信号CKfとの間の位相差に基づいて、当該DLLがどのくらいロック点に近いかを示すロック指示信号（LC）154を提供する。ロック検出器111中の各段118は、入力において二つのクロック信号（CKref、CKf）を受け取り、その入力クロック信号の一方の立ち上がりエッジと他方の入力クロック信号の立ち上がりエッジとの間の時間差を示す単ビットのLOCK信号（LC）を出力する。

## 【0055】

各段118は、二つのフリップフロップ119a、119bおよび三つの遅延線122a、122b、122cを含む自己完結ユニットである。遅延線122a、122b、122cのそれぞれは、該遅延線に埋め込まれているそれぞれの遅延時間期間（T1, T2）を有する。最も単純な実装では、ロック検出器111は、単ビットのロック指示信号を出力する単一の段118を有する。

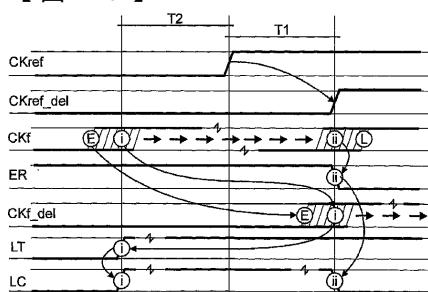

## 【0056】

図10は、図9に示されたロック検出器111の段の一つにおける信号を示すタイミング図である。図10は、ロック検出器111の動作を説明するために図9との関連で使用される。参照クロック信号CKrefの立ち上がりエッジの位置と遅延された参照クロック信号CKref\_de1の立ち上がりエッジの位置は安定していると想定される。タイミング図は、フィードバック・クロック信号CKfの立ち上がりエッジの左から右への、「早期」（E: early）位置から「後期」（L: late）位置への移動を示している。位置Eは参照クロック信号CKrefの立ち上がりエッジより前であり、位置Lは遅延された参照クロック信号CKref\_de1の立ち上がりエッジより後である。

## 【0057】

図9を参照すると、各段118において、段118の入力クロック信号CKrefは遅延時間T1をもつ遅延線122cによって遅延させられる。遅延された入力クロック信号CKref\_de1はフリップフロップ119a、119bの「D」入力に結合される。フリップフロップ119aのクロック入力は、フィードバック・クロック信号CKfに結合される。フリップフロップ119bのクロック入力は、遅延時間期間T1をもつ遅延線122aおよび遅延時間期間T2をもつ遅延線122bを通じて遅らされた、遅延されたフィードバック・クロックCKf\_de1に結合される。遅延線122a、122bは直列に接続される。

10

20

30

40

50

## 【0058】

遅延時間期間T1およびT2は、遅延線122a～cに埋め込まれており、同じ値であってもいいし、異なっていてもよい。遅延時間期間は、アプリケーションに依存して修正されることもできる。一般に、ロック検出器111は図9との関連で述べた同様の構造の複数の段118を含む。しかしながら、異なる諸実装については、諸段118は、遅延線112a～cに埋め込まれたT1およびT2の遅延値において異なることができる。T1およびT2の両方についての好ましい値は、参照クロック信号およびフィードバック・クロック信号(CKref, CKf)の周期のある割合である。ここで、前記割合は最高クロック信号周波数におけるクロック周期の1/4よりも小さい。いくつかの実施形態では、遅延時間期間は、二つの隣り合うVCDL引き出し口116、116aの間の遅延時間の半分よりも短い。その他の実施形態については、遅延時間期間は二つの隣り合うVCDL引き出し口116、116aの間の遅延時間の半分よりもやや長い。

## 【0059】

示されている実施例では、遅延時間期間T1およびT2は異なっている。フィードバック・クロック信号CKfの立ち上がりエッジが、初期化の間に参照クロックCKrefの立ち上がりエッジに一方の側(たとえば図6のタイミング図の左)から「接近」することが期待されるならば、遅延時間期間T2は「ロック窓を開き」、遅延時間期間T1は当該ロック検出器のためのマージンをなす。一般に、T1およびT2は異なる値である。この例では、典型的に、遅延時間期間T1は遅延時間期間T2よりも小さくなるよう選ばれ、それにより、ロック点が近づいているという「早期警報」と、ロック点の反対側に対するより厳しい制御とが保証される。

## 【0060】

典型的には、遅延時間期間(T1、T2)は短い。というのも、より長い遅延を得るために、著しいシリコン面積のオーバーヘッドがかかるからである。しかしながら、遅延時間期間は短すぎるわけにはいかない。というのも、VCDL遅延がDLL500によって調整される間、数クロック・サイクルにわたってLC信号154が安定のままである必要があるからである。

## 【0061】

図9の概略図を参照すると、フィードバック・クロック信号CKfの立ち上がりエッジが「E」位置にあるとき、フィードバック・クロック信号CKfの立ち上がりエッジは参照クロック信号CKrefに対して早い。反転器120の出力におけるER信号は「1」で、フリップフロップ119bのQ出力におけるLT信号は「0」なので、LC信号154は「0」である。

## 【0062】

ER信号およびLT信号はAND論理ゲート121によって組み合わされ、出力にLC信号を与える。LT信号の「0」とER信号の「1」の組合せは、AND論理ゲート121の出力におけるLC信号上の「0」を生じる。

## 【0063】

VCDL遅延が増加させられるにつれて、フィードバック・クロック信号CKfの立ち上がりエッジは右に向かって動き、「i」位置に達する。「ER」信号と「LT」信号がいずれも「1」なので、LC信号は「1」に切り替わる。

## 【0064】

概略図を参照すると、遅延されたフィードバック・クロック信号CKf\_de1もそれぞれの「i」位置に達する。遅延されたフィードバック・クロック信号CKf\_de1の立ち上がりエッジにおいて、遅延された参照クロック信号CKref\_de1は「1」であり、フリップフロップのD入力上の「1」はフリップフロップ119bのQ出力にラッチされる。LT信号上の「1」とER信号上の「1」との組み合わせは、AND論理ゲート121の出力におけるLC信号上の「1」を生じる。

## 【0065】

図10の例においてフィードバック・クロック信号CKfの立ち上がりエッジの位置が「ii」位置に達するまで右に動き続ける間、LC信号は「1」に留まる。「ii」位置では、遅延

10

20

30

40

50

された参照クロック信号CKref\_deIは「1」である。フリップフロップ119aのD入力は「1」なのである。フィードバック・クロックCKfの次の立ち上がりエッジはフリップフロップ119aのQ出力に「1」をクロックし、反転器120の出力におけるER信号は「0」に切り替わる。LT信号上の「1」とER信号上の「01」との組合せは、AND論理ゲート121の出力におけるLC信号上の「1」を生じる。

#### 【0066】

LC信号の状態は、フィードバック・クロックCKfの立ち上がりエッジと参照クロックCKrefの立ち上がりエッジとの間の時間の指標を与える。LC信号は、フィードバック・クロック信号CKfの立ち上がりエッジがCKrefクロック信号の立ち上がりエッジから時間T2およびT1以内にある、すなわち位置(i)と(ii)の間にあるうちは、「1」のままである。

10

#### 【0067】

ロック検出器111に複数の段118が含まれ、各段がVCDL102から、同じフィードバック・クロック信号CKfと参照クロック信号CKrefの異なる引き出し116とを受け取るならば、フィードバック・クロック信号CKfの立ち上がりエッジに最も近い立ち上がりエッジをもつ参照クロックCKrefの引き出し口を簡単に同定できる。一つの方法は、DLLがフィードバック・クロックCKfの立ち上がりエッジを進める、すなわち制御電圧Vcの値を徐々に変化させることによってVCDL遅延を増加させることを繰り返す、複数のLC信号のどれが「1」に切り替わるかを監視することである。

#### 【0068】

もう一つの方法は、LC信号の代わりに、ER信号とLT信号を直接監視することである。ER信号とLT信号の組合せは、4つの可能な状態(00、01、10および11)を与える。フィードバック・クロック信号CKfの立ち上がりエッジが参照クロック信号CKrefの立ち上がりエッジよりもT2より長い期間、早ければ、状態は「10」(ER信号が「1」、LT信号が「0」)である。フィードバック・クロック信号CKfの立ち上がりエッジが参照クロック信号CKrefの立ち上がりエッジよりもT1より長い期間、遅ければ、状態は「01」(ER信号が「0」、LT信号が「1」)である。よって、順序番号「N」のVCDL引き出し口116、116aではフィードバック・クロックCKfの立ち上がりエッジが参照クロックCKrefの立ち上がりエッジより遅いが、順序番号「N+1」の次の引き出し口116、116aではフィードバック・クロックCKfの立ち上がりエッジが参照クロックCKrefの立ち上がりエッジより早いならば、引き出し口「N」での状態(ER信号とLT信号の組み合わせ)は「11」または「01」であり、引き出し口「N+1」での状態(ER信号とLT信号の組み合わせ)は「10」または「11」である。値T1およびT2が両方とも隣り合う引き出し口の間の時間遅延のある小さな割合、たとえば二つの隣り合う引き出し口N、N+1の間の時間遅延の1/10として選ばれるならば、「11」の組合せは二つの隣り合う引き出し口において同時に存在することは決してなく、ロック点(状態「11」)が二つの引き出し口の間であることを見るのは容易である。

20

#### 【0069】

各段118からの単独のLC信号出力のみを使う方法は、ER信号およびLT信号を使う方法より実装が簡単である。しかしながら、ER信号およびLT信号の組合せを使う方法は、DLLをロック点に持ち込むのにより高速な方法である。当業者は、代替的な実施形態では、DLL動作点を初期化するために三つの信号LC、LT、ERのすべてを使うこともできることを理解するであろう。

30

#### 【0070】

図5に戻ると、DLL初期化コントロール112は初期化プロセスを制御する。初期化コントロール112は状態機械である。プロセスは、DLL初期化プロセスの間の加えられる信号(RST、HLD、MX)についての正しい値を選ぶことを含む。当業者は、状態機械を実装または合成するためには多くの方法があることを理解する。したがって、DLL初期化コントロールそのものの内部構造の概略図または要素ではなく、DLL初期化コントロール112の所望の機能をもつ状態機械を合成するために使われるアルゴリズムについて述べる。ここで論じられ、図11に表現されるアルゴリズムが、初期化プロセスを実装するために使うことのできる唯一の論理方式ではないことも注意しておく。ステップの序列は変更す

40

50

ることもでき、ステップを追加、除去または修正することもできる。

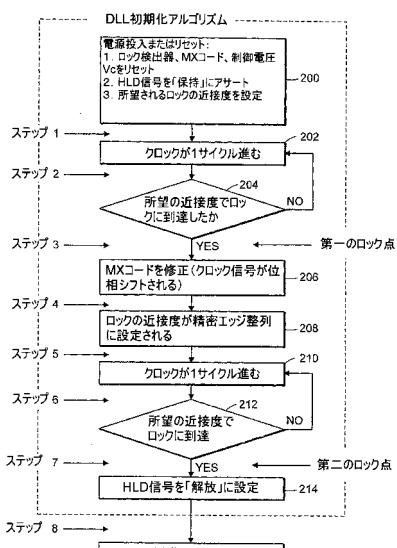

#### 【0071】

図11は、DLL初期化コントロール112内で実装されるDLL初期化プロセスを示すフローチャートである。DLL初期化プロセスは、電源投入またはシステム・リセットが発生するたびに開始される。図11は、図9および図5との関連で述べる。

#### 【0072】

ステップ200において、図5を参照するに、システム・リセット信号（簡単のため図示せず）がDLL500に、およびDLL500内のさまざまなモジュールに結合される。RST信号がロック検出器111および制御電圧発生器107に入力される。RST信号はロック検出器111を必要ならリセットする。たとえば、リセット信号は、フリップフロップ119a、119bのクリアなインプットに結合されたとき、図9に示された両フリップフロップ119a、119bをクリアして各フリップフロップのそれぞれのQ出力が「0」に設定されるようにすることによって、ロック検出器111をリセットできる。リセット信号はまた、制御電圧ノードVcを境界値、すなわち最小遅延を生成する値に放電する。リセット信号はまた、HLD信号を「保持（hold）」モードにアサートし、MX制御コード152についての初期値と探索されるロック点についての所望される近接度を設定する。

10

#### 【0073】

電源投入において、MXコード値152は初期値に設定され、それによりVCDLの引き出された出力116または116aは最小の位相シフトをもつもの（図7および図8に示されている最左端の引き出された出力（位相1））が選択される。所望されるロック近接度は、クロック信号（CKref、CKf）の立ち上がりエッジの近接度を評価するためのデバイスとして、PD104ではなくロック検出器111を選択することによって設定される。

20

#### 【0074】

電源投入におけるDLL初期化コントロール112からのMX出力152の値は、実装に依存して異なりうる。MX出力152は単一ビットまたは多ビットのどちらでもありうる。図5に示された実施形態では、MXは多ビット・コードである。単一ビットおよび多ビットの実装については、のちに論じる。HLD信号が「保持」に設定されている間は、PD104は「保持モード」にあり、PD104は、VCDL102遅延が増加のみされるようUPおよびDOWN出力信号を制御する。PD104が「保持モード」にある間も、その別個の専用の出力信号は相変わらず、入力クロック信号（CKref、CKf）の立ち上がりエッジの近接度をより高い精度で測定するために使われることができる。

30

#### 【0075】

最も高精度の位相検出器でさえ、ある有限の精度でエッジ整列を記録する。他の要因の中でも、この精度が、DLLクロック整列の精度を決定する。たとえば、PD誤差が20psで、DLLが確固としたロックにあるとすると、他の要因を除外すれば、クロック・エッジは互いから20ps以内にある。したがって、PD出力信号は、クロック・エッジ間の時間差が20ps以下であるときに、クロック・エッジの整列を指示する。

#### 【0076】

DLLの初期化は最小のVCDL102遅延をもって始まり、遅延は増加のみさせられる。図11に戻ると、ステップ202において、クロック（CKref、CKf）は1サイクル（すなわち1クロック周期）進み、当該クロック・サイクルにおけるクロック（CKref、CKf）の立ち上がりエッジの整列は、先に論じたようにロック検出器111および／またはPD104によって測定される。

40

#### 【0077】

ステップ204では、DLL初期化コントロール112が、ロック検出器111（図5）から転送されたLOCKコード154（図5）に基づいて、所望の近接度でロックが見出されたかどうかを判定する。ロックの近接度は、ロック点が見出される精度である。ロックの近接度は、DLL初期化コントロール112内で、レジスタ内の読み込み可能なコードまたはヒューズ・プログラムされた（fuse programmed）コードとして、記憶されている。ロックの近接度は、ロック検出器111内のT1およびT2の時間期間についての値を設定する

50

ために使われる。

**【 0 0 7 8 】**

ロックの検出器 111 は、先に論じたように、粗い整列または精密な整列のいずれを判定することもできる。それが立ち上がりエッジの近接の度合い（粗いか精密か）であり、これは T1 および T2 の時間期間の値の設定および ER、LT、LC 信号またはそれらの組合せのうちどれがロック点を選択するために使われるかによって決定される。

**【 0 0 7 9 】**

DLL 初期化プロセスの間に整列の精度は変わってもよい。初期化プロセスの最初は、整列を粗く検出するので十分である。粗い整列は典型的には、図 9 および図 10 との関連で記載されたロック検出器 111 によって実行される。近似的なエッジ整列で十分な DLL 初期化プロセスの始めには、長い T1 および T2 時間期間およびシンプルな LOCK コードをもつロック検出器の段 118 が使われる。より精密な整列が必要になると、より短い T1 および T2 時間期間ならびに LOCK コードにおける ER、ET および LC 信号のより複雑な組合せが使用される。あるいはまた、PD104 がこの段階でエッジ整列検出器として従事することもできる。

**【 0 0 8 0 】**

初期化プロセスを続ける：各立ち上がりクロック・エッジにおいて、DLL はクロック信号の立ち上がりエッジ間の近接（整列）の度合いを評価し、補正信号を生成する。制御電圧 Vc は常時、位相検出器 104 からの UP、DOWN 信号の値に基づいて修正される。

**【 0 0 8 1 】**

最初の数クロック・サイクル後、LOCK コードは、DLL が第一のロック点に接近していることを示す状態に落ち着く。所望の近接度で第一のロック点に到達したのち、プロセスはステップ 206 に進む。

**【 0 0 8 2 】**

ステップ 206 では、MX コードを修正して、マルチプレクサ 113 を通じてフィードバック・クロック信号 CKf の位相がシフトされることによって、第一のロック点がスキップされる。VCDL 遅延は、電源投入またはリセットのすぐあとのごくわずかの数クロック・サイクル経過後、位相シフトを実行することによって迅速に増加させることもできる。この場合、高い粒度の VCDL 引き出しをもつ精密なロック検出器が使われる。これは、第一および第二のロック点 604、606 の高速かつ精密な位置特定を許容し、それは今度は第二のロック点に対応する MX コードの値が迅速に生成されることを許容する。

**【 0 0 8 3 】**

図 6B のタイミング図および図 6A のグラフを参照すると、第一のロック点 604 に到達してスキップしたのち、遅延は、制御電圧 Vc の値を修正することにより増加され続け、そのため DLL は次の第二のロック点 606 へと移動する。遅延は最初は位相をシフトさせることによって迅速に増加させられる。次いで、遅延は、制御電圧 Vc を徐々に修正する

各クロック・サイクルでの比較的小さな変化 ことによって徐々に増加させられる。タイミング図は、VCDL 遅延を徐々に大きくすることによって第二のロック点 604 に達することを示している。制御電圧 Vc の値を徐々に変化させることは、位相シフトよりも遅いが、それでも VCDL 遅延を大きくし、DLL が第二のロック点に対応する制御電圧 Vc 値に達することを許容する。

**【 0 0 8 4 】**

VCDL の最小の遅延に対応する値に設定された制御電圧 Vc をもって、DLL は最終ロック点（たとえば第二のロック点 606）に单一の位相シフトで持ち込まれうる。この動作を実行するため、引き出し口 116、116a の選択は、DLL が第一のロック点をスキップして、最小遅延を生じるよう保持されている Vc をもつ第二のロック点の非常に近くに着地するようになる。しかしながら、動作条件が変化する際 Vc が解放されたのち、DLL は遅延を減らすための余り多くの余地をもたないことになる。というのも、制御電圧 Vc が最小遅延を生じる値からあまり遠くないからである。よって、クロック信号エッジのドリフトおよび動作条件の変化を補償するために著しい遅延減少が必要とされるような場合には、DL

10

20

30

40

50

Lは容易にロックを失うことになる。

#### 【0085】

Vc電圧レベル修正に起因して最終的なロック前に達成されるVCDL遅延増の部分は、DLL通常動作の間に必要とされる最大のVCDL遅延減（図3Bの範囲304）に何らかの安全マージンを加えたものより大きいか、あるいは少なくとも等しい必要があるだけである。明らかに、より長いタイミング期間を選ぶことは、最終的なロックの探索も長くする。しかしながら、すでに論じたように、タイミング期間は、クロック信号エッジのドリフトおよび動作条件の変化の影響のもとで、通常のDLL動作の間の何らかの時点において必要とされるかもしれない最大のVCDL遅延修正（減少）によって決定される。

#### 【0086】

ある実施形態では、ロック検出器111は、ロック検出器111出力LOCKコードにおいて各個別段118のLC出力のみが使われる複数の段118を含む。この実施形態では、段118は、それぞれの遅延線122a～cに埋め込まれたT1およびT2の遅延時間の異なる値を有する。この場合の遅延線122a～cは、VCDL102バッファ・チェーン114の諸部分のレプリカである。第一段118aは遅延線122a～c内に比較的少ないバッファを有し、参照クロック信号CKrefおよびフィードバック・クロック信号CKfの立ち上がりエッジが互いに比較的近いときに次の段のLC信号がアサートされる（論理的な「1」に設定される）。

#### 【0087】

それぞれの次の段118bは、前段に比べてより多くのバッファをもつ。よって、それぞれの次の段118bにおける近接度の精度は下がり（より粗くなる）、クロック信号（CKref、CKf）の立ち上がりエッジが互いからより隔たっているときにアサートされる。組み合わされたLCはすべての段から出力される。それがこの実施形態におけるロック検出器111のLOCK出力コードである。LOCKコードは、クロック信号CKrefおよびCKfの立ち上がりエッジを互いに近づけるために、VCDLにおいて、参照クロック信号CKref経路に单一VCDLバッファをいくつ追加する必要があるかを示す。換言すれば、LOCK出力コード154は、第一のロック点604をスキップしてDLL動作点を第二のロック点606に近づけるために、引き出されたVCDL出力のうちからMXコード152によって選択されるべき引き出し口を同定する。

#### 【0088】

こうして、ステップ208において、DLL初期化コントロール112は、第二のロック点に対応するMXコード値をアサートし、PD104制御に切り換えることによって、所望される近接度を精密に変化させる。初期化プロセスのこの段階で、専用のUP信号およびDOWN信号が高精度でクロック立ち上がりエッジの位置付けを評価するために使われる。その一方、UP出力およびDOWN出力はいまだHLD信号によって、VCDL102遅延をいまだ増加のみさせるよう保持されている。あるいはまた、ロック検出器111が制御する立場に留まり、その一方でPD104はVCDL102遅延時間を増加させるためのUPおよびDOWN出力信号を生成するよう保持されるのでもよい。

#### 【0089】

ステップ210では、クロック（CKref、CKf）は1サイクル進む。参照クロック信号CKrefおよびフィードバック・クロック信号CKfの次の立ち上がりエッジが検出され、近接度が測定される。

#### 【0090】

ステップ212では、第二のロック点に所望の近接度で到達していれば、プロセスはステップ214に進む。そうでなければ、プロセスはステップ210に進んで、参照クロック信号CKrefとフィードバック・クロック信号CKfとの間の整列の度合いの監視を続ける。

#### 【0091】

ステップ214では、精密な最終ロックに到達しており、HLD信号を「解放」状態に切り換えることによってPD104が解放される。

#### 【0092】

10

20

30

40

50

ステップ216では、PD104が制御電圧Vcを制御し、通常のDLL動作が始まる。

**【実施例1】**

**【0093】**

DLLの他の諸実施形態が図12～図15に示されている。

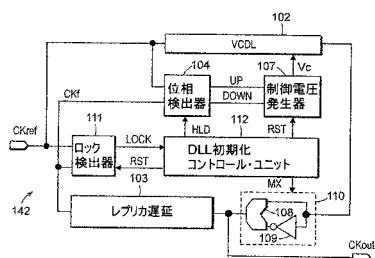

**【0094】**

図12は、本発明の原理に基づくDLL初期化を含む、ある代替的な実施形態のDLL140のブロック図である。この実施形態は、より高速なDLL初期化が要求される場合、すなわち、最終的なDLLロック点に到達し、通常のDLL動作に切り換えるために必要とされる時間が重要であるときにより好適である。

**【0095】**

DLL140は、図5との関連で記載されたDLL500の実施形態と多くの共通の要素を有する。本DLLは、図5に示された実施形態において論じたように、複数の引き出された出力116または116aをもつVCDL102、PD104、制御電圧発生器107、マルチプレクサ113およびDLL初期化コントロール112を含む。図5に示したDLL500における単一のレプリカ遅延103と対照的に、DLL140は複数のレプリカ遅延ブロック103を含んでいる。VCDL102の引き出された出力116または116aのそれについて、一つのレプリカ遅延ブロック103である。

**【0096】**

ロック検出器111は図9で示したような内部構造を有し、VCDLの引き出された出力116または116aの数と同数の複数の段118をもつ。タイミング期間T1およびT2の値は二つの隣接するVCDL引き出し口116または116aの間の遅延時間よりずっと短い。ロック検出器111によるLOCKコード出力は、全段118のLC、LTおよびER出力を含む。これは、クロック信号の立ち上がりエッジの相互の位置付けを判定する際のより高い精度を許容する。二つのマルチプレクサ113a～bが使われる：いくつかのVCDL102の引き出された出力からDLL出力のクロック信号を選択するためのマルチプレクサ113aと、フィードバック・クロック信号CKfを選択するためのマルチプレクサ113bである。両方のマルチプレクサ113a～bは、同じMX多ビット・コードによって制御される。図5に関連して述べた実施形態に比べ、ロックするためのより高い精度およびより高速な時間を提供するために、マルチプレクサ113a～bを二つ、レプリカ遅延103を複数およびロック検出器111内のクロック検出器段118を収容するために、追加的なシリコン面積のオーバーヘッドが必要とされる。

**【0097】**

引き出されたVCDL出力116または116aからのクロック信号は、レプリカ遅延103および第一のマルチプレクサ113aに転送される。レプリカ遅延103を通過後、クロック信号はロック検出器111および第二のマルチプレクサ113bに転送される。DLL初期化コントロール112は、図11との関連で述べた初期化プロセスを制御する。電源投入またはシステム・リセットに際して、制御電圧発生器107は、VCDL102が最小の遅延を生成するよう、制御電圧Vcを境界値にリセットする。図5の実施形態で示したりセット信号は簡単のため除いてある。HLD信号の状態は、PD104を遅延増加モードに保持するため「保持」に設定される。ロック検出器111はリセットされ、MX多ビット・コードはデフォルト値に設定されるか、あるいはこのときは初期のランダムな値のままにされる。

**【0098】**

所望の近接度の設定が、ロック検出器111が制御電圧Vcを制御するのを許容し、PD104を「保持」モードに保持することによって行われる。数クロック・サイクル後、LOCKコードの値は安定化し、参照クロック信号CKrefの立ち上がりエッジと比べてのレプリカ遅延103の諸出力における複数のクロック信号の立ち上がりエッジの位置に基づいて、クロック信号CKref、CKfの間の位相差を高精度で指示する。ロック検出器111から受け取られたLOCKコード値を使って、DLL初期化コントロール112は、マルチプレクサ113aを通じては、出力クロック信号CKoutのためにVCDL102から出力されたクロックの

10

20

30

40

50

最も近いバージョンを選択し、マルチブレクサ113bを通じては、PD104にフィードバックするために、レプリカ遅延ユニット103から出力されたクロック信号CKfのそれぞれのバージョンを選択する。

#### 【0099】

MXコードについての値を決定するため、マルチブレクサ113a、113bの両方によって選択されたクロック信号のバージョンが、VCDL102からの同じ引き出された出力に関係していることに注意しておくことが重要である。よって、クロック信号の諸バージョンは該MXコードによって選択され、位相シフトはリセットまたは電源投入後ほとんどただちに実行される。位相シフト後、DLLの動作点は第二のロック点606(図6A)に近く、DLL初期化コントロール112はPD104を通じて制御電圧Vcを徐々に増加させる。その一方、HLD信号は、PD104がVCDL遅延を大きくするだけとなるよう、PD104の出力を保持する。制御電圧Vcの増加は、第二のロック点606(図6A)に達するまで続く。第二のロック点606(図6A)に達したのち、DLL初期化コントロール112はHLD信号の状態を「解放」に変更し、所望されるロックの近接度は、制御電圧Vcの制御をPD104に移すことによって、「精密」に切り換えられる。DLLの通常動作が始まる。この「ロック加速された」実施形態でさえ、Vcが最小遅延に対応する値に留まったまま位相シフトだけによってDLLを厳密に第二のロック点に持ってくることはできない。上で論じたように、クロック・エッジのドリフトおよび動作条件変化を補償するためにVCDL遅延の変動に対するマージンが必要とされる。したがって、位相シフトはDLLを第二ロック点にマージンの近さまで持ってき、残りの行程(マージン)は徐々にVcを修正することによってカバーされる。1020

#### 【実施例2】

#### 【0100】

図13～図15に示されるDLLの諸実施形態は、図5との関連で前に記載されたDLLの実施形態や図1との関連で記載された従来技術のDLLでは使われていない反転ユニット110を含む。

#### 【0101】

図13を参照すると、最も単純な場合において、反転ユニット110は反転器109およびマルチブレクサ108を含む。反転ユニット110の機能は、入力信号を反転バージョンと非反転バージョンに分割し、單一ビットのMX信号の論理値に従って該バージョンの一方を出力に供給されるべく選択することである。たとえば、MX信号が「0」のときは非反転バージョンの信号が出力され、MX信号が「1」のときは反転バージョンの信号が出力される、あるいはその逆とするなどである。したがって、反転ユニット110は、図12に示した実施形態との関連で先に記載したマルチブレクサ113と同様である。30

#### 【0102】

当業者にはよく知られているように、反転ユニット110の機能を実装するには多くの可能な方法がある。反転ユニットは本発明の主題ではないので、ここでは議論しない。ユニット機能が提供される限り、いかなる変形を選んでもよい。当業者は、反転ユニット110の内部構造が図13に示されたものとは異なりうることを理解するであろう。たとえば、反転ユニット110は、シングルエンド入力またはディファレンシャル入力とディファレンシャル出力とをもつことができ、出力はMX信号によって選択される順相または逆相であることができる。反転ユニット110はまた、該ユニット内の二つの経路　反転および非反転　の追加的なチェーン平衡化(balancing)遅延をも含むことができる。また、VCDL102出力が信号と補角信号の対117a(図8)または信号と補角信号11740

(図7)を提供する場合には、反転器109は反転ユニット110内に必要ないことがありうることも理解される。この場合、反転ユニット110は、マルチブレクサ113の2入力1出力バージョンを含む。

#### 【0103】

図13に示されたDLLの実施形態は、図12との関連で記載した実施形態ほど迅速にロック点を見出さない。しかしながら、図13の実施形態は実装がより簡単で、必要とされ50

るシリコン面積オーバーヘッドもより少ない。

#### 【0104】

DLL142は、ただ一つのVCDL出力と、一つの反転ユニット110と、ただ一つの段118をもつロック検出器110を含んでいる。あるいはまた、VCDL102が図8に示すように出力信号とその補角信号を与える場合、反転ユニット110は2入力単一出力のマルチプレクサ113によって置き換えられる。ロック検出器111内のタイミング期間T1およびT2はクロック周期のある小さな割合に設定されている。ロック検出器111は、参照クロック信号CKrefとフィードバック・クロック信号CKfの立ち上がりエッジが互いに近いときにのみ、ロック点を検出する。

#### 【0105】

DLL初期化コントロール112は、リセットまたは電源投入後、初期遅延から遅延を徐々に増加させる。ロック信号の状態に基づいて第一のロック点604(図6A)が検出されたのち、反転ユニット110はDLL初期化コントロール112によって出力されるMX信号に基づいて反転されたクロックに切り替え、こうして第一のロック点を飛び越す。反転ユニット110の切り替え後、PD104は相変わらず、制御電圧Vcを上げることによって遅延を増加のみさせるようHLD信号によって保持されている。DLL142は、参照クロック信号CKrefとフィードバック・クロック信号CKfの立ち上がりエッジの間の時間遅延に基づいて、制御電圧Vcを上げることによって遅延を徐々に増加させ続ける。第二のロック点606(図6A)が検出されたのち、PD104は、HLD信号の状態を変えることによって解放され、通常動作が始まる。

10

#### 【0106】

図14および図15に示すDLLの実施形態では、反転ユニット110は、前に論じられた諸実施形態とは異なる位置に接続されている。

#### 【0107】

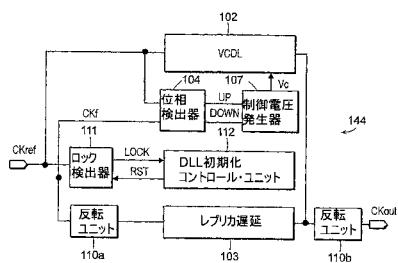

図14を参照すると、DLL144は二つの反転ユニット110a、110bを含む。反転ユニット110aの入力はレプリカ遅延103の出力に接続されている。反転ユニット110bの入力はVCDL102の出力に接続されている。反転ユニット110aの出力はDLL出力クロック信号CKoutである。反転ユニット110bの出力は、DLL内部のフィードバック・クロック信号CKfであり、PD104の入力およびロック検出器111の入力に結合される。

30

#### 【0108】

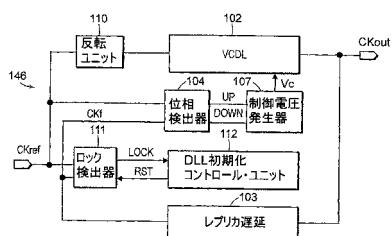

図15を参照すると、DLL146は、参照クロック信号CKrefとVCDL102の入力との間に、すなわち参照クロック信号CKrefの経路中に結合される反転ユニット110を含む。

#### 【0109】

DLL144(図14)もDLL146(図15)もリセット信号やMX、RST、HLDといった内部DLL信号は示していない。これらの信号は簡単のため図からは除いた。当業者は、こうした信号がみなシステムに存在しており、これまでに論じられたすべての実施形態において適用されているのと同じ仕方で適用されることを理解するであろう。

#### 【0110】

当業者は、DLL初期化プロセスを使ったDLL構造は記載されているものに限定されないことを認識するであろう。経験のある設計者は、DLL初期化プロセスに関してここに記載された着想から裨益する他のDLL構造を設計できる。

40

#### 【0111】

他の実施形態では、DLLは、遅延対制御電圧特性の最大遅延に近い点から出発することによってロック点を探索する。初期化の間のロック点探索の方向は、遅延減少のみに制約される。すなわち、位相検出器は、該位相検出器の内部構造に依存して遅延減少に対応するUP信号およびDOWN信号の組合せのみを生成するよう強制される。ある実施形態では、出発点は、急峻領域を避けるため、急峻領域の下で最大遅延に対応するところである。動作点は初期遅延より下になるので、DLL内の段の一部しか使用されず、他は初期化の間無効にされていることもありうる。

50

**【0112】**

本発明についてその好ましい実施形態を参考しつつ具体的に示し、説明してきたが、当業者は、付属の請求項によって包含される本発明の範囲から外れることなくそれに形式および詳細においてさまざまな変更をなしうることを理解するであろう。

**【図面の簡単な説明】****【0113】**

【図1】従来技術の通常の遅延ロックループ(DLL)のブロック図である。

【図2】典型的な、制御電圧 $V_c$ に対するVCDL遅延の特性を示すグラフである。

【図3A】制御電圧に対する遅延の特性の左端に近いロック点を示すグラフである。 10

【図3B】図3Aの制御電圧に対する遅延の特性に対応するクロック信号図である。

【図4A】ある探索方向へのロック点の探索で、ロックに到達する前にVCDLの遅延限界に突き当たる結果となる場合を示すグラフである。

【図4B】図4Aに示されたロック点の探索に対応するクロック信号図である。

【図5】本発明の原理に基づく、DLLを初期化するためのDLL初期化コントロールを含む遅延ロックループ(DLL)のある実施形態のブロック図である。

【図6A】図5に示されたDLLのDLL初期化コントロールを使っての、制御電圧に対する遅延の特性上での初期化プロセスを示すグラフである。

【図6B】図6Aに示された初期化プロセスに対応するクロック信号図である。

【図7】図5に示されたVCDLのシングルエンドの実施例のブロック図である。 20

【図8】ディファレンシャルエンドをもつVCDLのブロック図である。

【図9】ロック検出器のある実施形態の概略図である。

【図10】図9に示されたロック検出器の段の一つにおける信号を示すタイミング図である。

【図11】DLLを初期化するためのアルゴリズムを示すフローチャートである。

【図12】本発明の原理に基づくDLL初期化を含む、DLLの代替的な実施形態のブロック図である。

【図13】本発明の原理に基づくDLL初期化を含む、DLLの代替的な実施形態のブロック図である。

【図14】本発明の原理に基づくDLL初期化を含む、DLLの代替的な実施形態のブロック図 30である。

【図15】本発明の原理に基づくDLL初期化を含む、DLLの代替的な実施形態のブロック図である。

【図1】

【図2】

【図3 A】

【図3 B】

【図4 A】

【図4 B】

【図5】

【図 6 A】

【図 6 B】

【図 7】

【図 8】

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

【図 12】

【図13】

【図14】

【図15】

---

フロントページの続き

(72)発明者 ヘールレ, ディーター

オーストリア共和国 9500 ヴィラハ, ゲルベルガッセ 40, トップ 11

(72)発明者 マイ, トニー

カナダ国 ケイ2ケイ 3エ-6 オンタリオ州 カナタ, ウィゾーン・アヴェニュー 9

(72)発明者 ヴラセンコ, ピーター

カナダ国 ケイ2エル 3イ-1 オンタリオ州 カナタ, クラークソン・クレセント 145

審査官 上田 智志

(56)参考文献 特開平11-205102(JP, A)

国際公開第2004/114524(WO, A1)

特開2000-082954(JP, A)

特開2003-110423(JP, A)

特開平08-316827(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03L 7/00-7/23