(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7590656号

(P7590656)

(45)発行日 令和6年11月27日(2024.11.27)

(24)登録日 令和6年11月19日(2024.11.19)

(51)国際特許分類

|         |                  |         |        |       |

|---------|------------------|---------|--------|-------|

| H 1 0 B | 10/00 (2023.01)  | H 1 0 B | 10/00  |       |

| G 1 1 C | 11/412 (2006.01) | G 1 1 C | 11/412 | 1 2 0 |

| H 0 1 L | 21/8238(2006.01) | H 0 1 L | 27/092 | A     |

| H 0 1 L | 27/092 (2006.01) | H 0 1 L | 27/092 | C     |

|         |                  | H 0 1 L | 27/092 | G     |

請求項の数 7 (全27頁)

(21)出願番号 特願2021-527512(P2021-527512)

(86)(22)出願日 令和2年5月27日(2020.5.27)

(86)国際出願番号 PCT/JP2020/020978

(87)国際公開番号 WO2020/255656

(87)国際公開日 令和2年12月24日(2020.12.24)

審査請求日 令和5年4月14日(2023.4.14)

(31)優先権主張番号 特願2019-115211(P2019-115211)

(32)優先日 令和1年6月21日(2019.6.21)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 514315159

株式会社ソシオネクスト

神奈川県横浜市港北区新横浜2丁目10

番23

(74)代理人 110001427

弁理士法人前田特許事務所

(72)発明者 廣瀬 雅庸

神奈川県横浜市港北区新横浜2丁目10

番23 株式会社ソシオネクスト内

審査官 加藤 俊哉

最終頁に続く

(54)【発明の名称】 半導体記憶装置

## (57)【特許請求の範囲】

## 【請求項1】

1 ポートS R A Mセルを含む半導体記憶装置であって、

前記1ポートS R A Mセルは、

一方のノードが第1電圧を供給する第1電源に、他方のノードが第1ノードに、ゲート

が第2ノードにそれぞれ接続された第1トランジスタと、

一方のノードが前記第1電源に、他方のノードが前記第2ノードに、ゲートが前記第1

ノードにそれぞれ接続された第2トランジスタと、

一方のノードが前記第1ノードに、他方のノードが前記第1電圧と異なる第2電圧を供

給する第2電源に、ゲートが前記第2ノードにそれぞれ接続された第3トランジスタと、

一方のノードが前記第2ノードに、他方のノードが前記第2電源に、ゲートが前記第1

ノードにそれぞれ接続された第4トランジスタと、

一方のノードが第1ビット線に、他方のノードが前記第1ノードに、ゲートがワード線

にそれぞれ接続された第5トランジスタと、

一方のノードが前記第1ビット線と相補ビット線対を構成する第2ビット線に、他方の

ノードが前記第2ノードに、ゲートが前記ワード線にそれぞれ接続された第6トランジス

タと

を備え、

前記第3および第4トランジスタは、それぞれ、

第1層に形成された第1導電型の立体構造トランジスタである、第1立体構造トラン

ジスタと、

少なくとも一部が、前記第1立体構造トランジスタと平面視で重なるように、前記第1層より上層の第2層に形成された前記第1導電型の立体構造トランジスタである、第2立体構造トランジスタとを含み、

前記第5および第6トランジスタは、それぞれ、前記第1および第2層の少なくともいずれか一方に形成された前記第1導電型の立体構造トランジスタを含み、

前記第1および第2トランジスタは、それぞれ、前記第2層に形成された前記第1導電型と異なる第2導電型の立体構造トランジスタを含み、

前記第1トランジスタを構成する立体構造トランジスタの数は、前記第3トランジスタを構成する立体構造トランジスタの数よりも少なく、

前記第2トランジスタを構成する立体構造トランジスタの数は、前記第4トランジスタを構成する立体構造トランジスタの数よりも少なく、

前記第5および第6トランジスタは、それぞれ、

前記第1層に形成された第3立体構造トランジスタと、

少なくとも一部が、前記第3立体構造トランジスタと平面視で重なるように、前記第2層に形成された第4立体構造トランジスタとを含み、

前記第3トランジスタにおける前記第1および第2立体構造トランジスタは、前記第5トランジスタにおける前記第3および第4立体構造トランジスタと、前記第1～第6トランジスタのチャネル部が延びる方向である第1方向に、それぞれ並んで形成されており、

前記第4トランジスタにおける前記第1および第2立体構造トランジスタは、前記第6トランジスタにおける前記第3および第4立体構造トランジスタと、前記第1方向にそれぞれ並んで形成されている

ことを特徴とする半導体記憶装置。

## 【請求項2】

1ポートSRAMセルを含む半導体記憶装置であって、

前記1ポートSRAMセルは、

一方のノードが第1電圧を供給する第1電源に、他方のノードが第1ノードに、ゲートが第2ノードにそれぞれ接続された第1トランジスタと、

一方のノードが前記第1電源に、他方のノードが前記第2ノードに、ゲートが前記第1ノードにそれぞれ接続された第2トランジスタと、

一方のノードが前記第1ノードに、他方のノードが前記第1電圧と異なる第2電圧を供給する第2電源に、ゲートが前記第2ノードにそれぞれ接続された第3トランジスタと、

一方のノードが前記第2ノードに、他方のノードが前記第2電源に、ゲートが前記第1ノードにそれぞれ接続された第4トランジスタと、

一方のノードが第1ビット線に、他方のノードが前記第1ノードに、ゲートがワード線にそれぞれ接続された第5トランジスタと、

一方のノードが前記第1ビット線と相補ビット線対を構成する第2ビット線に、他方のノードが前記第2ノードに、ゲートが前記ワード線にそれぞれ接続された第6トランジスタとを備え、

前記第3および第4トランジスタは、それぞれ、

第1層に形成された第1導電型の立体構造トランジスタである、第1立体構造トランジスタと、

少なくとも一部が、前記第1立体構造トランジスタと平面視で重なるように、前記第1層より上層の第2層に形成された前記第1導電型の立体構造トランジスタである、第2立体構造トランジスタとを含み、

前記第5および第6トランジスタは、それぞれ、前記第1および第2層の少なくともいずれか一方に形成された前記第1導電型の立体構造トランジスタを含み、

前記第1および第2トランジスタは、それぞれ、前記第2層に形成された前記第1導電型と異なる第2導電型の立体構造トランジスタを含み、

前記第1トランジスタを構成する立体構造トランジスタの数は、前記第3トランジスタを

10

20

30

40

50

構成する立体構造トランジスタの数よりも少なく、

前記第2トランジスタを構成する立体構造トランジスタの数は、前記第4トランジスタを構成する立体構造トランジスタの数よりも少なく、

前記第5および第6トランジスタは、それぞれ、

前記第1層に形成された第3立体構造トランジスタと、

少なくとも一部が、前記第3立体構造トランジスタと平面視で重なるように、前記第2層に形成された第4立体構造トランジスタとを含み、

前記第3トランジスタにおける前記第1および第2立体構造トランジスタは、前記第5トランジスタにおける前記第3および第4立体構造トランジスタと、前記第1～第6トランジスタのチャネル部が延びる方向である第1方向に、それぞれ並んで形成されており、

前記第4トランジスタにおける前記第1および第2立体構造トランジスタは、前記第6トランジスタにおける前記第3および第4立体構造トランジスタと、前記第1方向にそれぞれ並んで形成されており、

前記第3および第4トランジスタのそれぞれにおいて、

前記第1立体構造トランジスタは、前記第1～第6トランジスタのチャネル部が延びる方向である第1方向と垂直をなす第2方向に並んで形成された複数の第1立体構造トランジスタを含み、

前記第1トランジスタは、少なくとも一部が、前記第3トランジスタにおける前記複数の第1立体構造トランジスタのいずれかと平面視で重なっており、

前記第2トランジスタは、少なくとも一部が、前記第4トランジスタにおける前記複数の第1立体構造トランジスタのいずれかと平面視で重なっている

ことを特徴とする半導体記憶装置。

### 【請求項3】

1ポートSRAMセルを含む半導体記憶装置であって、

前記1ポートSRAMセルは、

一方のノードが第1電圧を供給する第1電源に、他方のノードが第1ノードに、ゲートが第2ノードにそれぞれ接続された第1トランジスタと、

一方のノードが前記第1電源に、他方のノードが前記第2ノードに、ゲートが前記第1ノードにそれぞれ接続された第2トランジスタと、

一方のノードが前記第1ノードに、他方のノードが前記第2電圧と異なる第2電圧を供給する第2電源に、ゲートが前記第2ノードにそれぞれ接続された第3トランジスタと、

一方のノードが前記第2ノードに、他方のノードが前記第2電源に、ゲートが前記第1ノードにそれぞれ接続された第4トランジスタと、

一方のノードが第1ビット線に、他方のノードが前記第1ノードに、ゲートがワード線にそれぞれ接続された第5トランジスタと、

一方のノードが前記第1ビット線と相補ビット線対を構成する第2ビット線に、他方のノードが前記第2ノードに、ゲートが前記ワード線にそれぞれ接続された第6トランジスタとを備え、

前記第3および第4トランジスタは、それぞれ、

第1層に形成された第1導電型の立体構造トランジスタである、第1立体構造トランジスタと、

少なくとも一部が、前記第1立体構造トランジスタと平面視で重なるように、前記第1層より上層の第2層に形成された前記第1導電型の立体構造トランジスタである、第2立体構造トランジスタとを含み、

前記第5および第6トランジスタは、それぞれ、前記第1および第2層の少なくともいずれか一方に形成された前記第1導電型の立体構造トランジスタを含み、

前記第1および第2トランジスタは、それぞれ、前記第2層に形成された前記第1導電型と異なる第2導電型の立体構造トランジスタを含み、

前記第1トランジスタを構成する立体構造トランジスタの数は、前記第3トランジスタを構成する立体構造トランジスタの数よりも少なく、

10

20

30

40

50

前記第2トランジスタを構成する立体構造トランジスタの数は、前記第4トランジスタを構成する立体構造トランジスタの数よりも少なく、

前記1ポートS R A Mセルは、

前記第1層に形成された前記第1導電型の立体構造トランジスタである、第1ダミートランジスタと、

前記第1層に形成された前記第1導電型の立体構造トランジスタである、第2ダミートランジスタと

をさらに備え、

前記第5および第6トランジスタは、それぞれ、前記第2層に形成された立体構造トランジスタを含み、かつ、少なくとも一部が、前記第1および第2ダミートランジスタとそれぞれ平面視で重なっている

ことを特徴とする半導体記憶装置。

**【請求項4】**

請求項3記載の半導体記憶装置において、

前記第5および第6トランジスタは、前記第3および第4トランジスタにおける前記第2立体構造トランジスタと、前記第1～第6トランジスタのチャネル部が延びる方向である第1方向に、それぞれ並んで形成されており、

前記第1および第2ダミートランジスタは、前記第3および第4トランジスタにおける前記第1立体構造トランジスタと前記第1方向にそれぞれ並んで形成されている

ことを特徴とする半導体記憶装置。

**【請求項5】**

請求項1～3のいずれか1項記載の半導体記憶装置において、

前記第5トランジスタは、前記第3トランジスタにおける前記第1および第2立体構造トランジスタの少なくとも一方と、前記第1～第6トランジスタのチャネル部が延びる方向である第1方向に並んで形成されており、

前記第6トランジスタは、前記第4トランジスタにおける前記第1および第2立体構造トランジスタの少なくとも一方と前記第1方向に並んで形成されている

ことを特徴とする半導体記憶装置。

**【請求項6】**

請求項1～3のいずれか1項記載の半導体記憶装置において、

前記第5および第6トランジスタは、それぞれ、前記第1層に形成された立体構造トランジスタを含み、

前記第5トランジスタは、前記第3トランジスタにおける前記第1立体構造トランジスタと、前記第1～第6トランジスタのチャネル部が延びる方向である第1方向に並んで形成されており、

前記第6トランジスタは、前記第4トランジスタにおける前記第1立体構造トランジスタと前記第1方向に並んで形成されている

ことを特徴とする半導体記憶装置。

**【請求項7】**

請求項1～3のいずれか1項記載の半導体記憶装置において、

前記第3トランジスタにおける前記第1および第2立体構造トランジスタは、ゲートに同一のゲート配線である、第1ゲート配線が直接接続されており、

前記第4トランジスタにおける前記第1および第2立体構造トランジスタは、ゲートに同一のゲート配線である、第2ゲート配線が直接接続されていることを特徴とする半導体記憶装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本開示は、立体構造トランジスタを備えた半導体記憶装置に関し、特に立体構造トランジスタを用いた1ポートS R A M (Static Random Access Memory) セルのレイアウト

10

20

30

40

50

ト構造に関する。

【背景技術】

【0002】

S R A M は半導体集積回路において広く用いられている。

【0003】

また、L S I の基本構成要素であるトランジスタは、ゲート長の縮小（スケーリング）により、集積度の向上、動作電圧の低減、および動作速度の向上を実現してきた。しかし近年、過度なスケーリングによるオフ電流と、それによる消費電力の著しい増大が問題となっている。この問題を解決するため、トランジスタ構造を従来の平面型から立体型に変更した立体構造トランジスタが盛んに研究されている。

10

【0004】

非特許文献1, 2では、新規デバイスとして、立体構造のP型F E TとN型F E Tを基板に対して垂直方向に積層した立体構造デバイスと、これを用いたS R A Mセル（以下、単に、セルともいう）が開示されている。

【先行技術文献】

【非特許文献】

【0005】

【文献】Ryckaert J. et al., "The Complementary FET (CFET) for CMOS scaling beyond N3", 2018 Symposium on VLSI Technology Digest of Technical Papers

【文献】A. Mocuta et al., "Enabling CMOS Scaling Towards 3nm and Beyond", 2018 Symposium on VLSI Technology Digest of Technical Papers

20

【発明の概要】

【発明が解決しようとする課題】

【0006】

本明細書では、立体構造のP型F E TとN型F E Tを基板に対して垂直方向に積層した立体構造デバイスのことを、非特許文献1の記載にない、C F E T（Complementary FET）と呼ぶこととする。また、基板に対して垂直をなす方向のことを、深さ方向と呼ぶ。

【0007】

ところで、非特許文献1の図4には、C F E Tを用いた1ポートS R A Mセルのレイアウト構造が開示されている。非特許文献1の図4では、1ポートS R A Mセル内の1ポートS R A M回路を構成する6つのトランジスタが、それぞれ、1つのナノワイヤトランジスタからなる。

30

【0008】

しかし、1ポートS R A Mセルでは、回路の動作速度、動作安定性等を考慮して、1ポートS R A M回路を構成する6つのトランジスタの能力比が決定される。これまでに、6つのトランジスタが異なる数のナノワイヤトランジスタで構成されている1ポートS R A Mセルのレイアウトに関して、具体的な検討はまだされていない。

【0009】

本開示は、C F E Tを用いた1ポートS R A Mセルのレイアウト構造において、1ポートS R A M回路を構成する6つのトランジスタが異なる数のナノワイヤトランジスタで構成される1ポートS R A Mセルのレイアウト構造を提供することを目的とする。

40

【課題を解決するための手段】

【0010】

本開示の第1態様では、1ポートS R A Mセルを含む半導体記憶装置であって、前記1ポートS R A Mセルは、一方のノードが第1電圧を供給する第1電源に、他方のノードが第1ノードに、ゲートが第2ノードにそれぞれ接続された第1トランジスタと、一方のノードが前記第1電源に、他方のノードが前記第2ノードに、ゲートが前記第1ノードにそれぞれ接続された第2トランジスタと、一方のノードが前記第1ノードに、他方のノードが前記第2電圧と異なる第3電圧を供給する第3電源に、ゲートが前記第2ノードにそれぞれ接続された第3トランジスタと、一方のノードが前記第2ノードに、他方のノードが

50

前記第2電源に、ゲートが前記第1ノードにそれぞれ接続された第4トランジスタと、一方のノードが第1ビット線に、他方のノードが前記第1ノードに、ゲートがワード線にそれぞれ接続された第5トランジスタと、一方のノードが前記第1ビット線と相補ビット線対を構成する第2ビット線に、他方のノードが前記第2ノードに、ゲートが前記ワード線にそれぞれ接続された第6トランジスタとを備える。前記第3～第6トランジスタは、それぞれ、第1層に形成された、第1導電型の立体構造トランジスタからなる。前記第1および第2トランジスタは、それぞれ、前記第1層と異なる第2層に形成された前記第1導電型と異なる第2導電型の立体構造トランジスタからなる。前記第1および第2トランジスタを構成する立体構造トランジスタの数は、それぞれ、前記第3トランジスタを構成する立体構造トランジスタの数よりも少なく、かつ、前記第4トランジスタを構成する立体構造トランジスタの数よりも少ない。前記第1および第2トランジスタは、少なくとも一部が、前記第3および第4トランジスタとそれぞれ平面視において重なっている。

#### 【0011】

本開示によると、第1～第6トランジスタにより1ポートSRAM回路が構成されており、第1～第6トランジスタは、それぞれ、立体構造トランジスタにより構成されている。また、第1および第2トランジスタを構成する立体構造トランジスタの数は、それぞれ、第3トランジスタを構成する立体構造トランジスタの数よりも少なく、かつ、第4トランジスタを構成する立体構造トランジスタの数よりも少ない。これにより、CFETを用いた、1ポートSRAMセルのレイアウト構造において、1ポートSRAM回路を構成する6つのトランジスタが、異なる数のナノワイヤトランジスタで構成された1ポートSRAMセルのレイアウト構造を実現することができる。

#### 【0012】

また、第1および第2トランジスタは、少なくとも一部が、第3および第4トランジスタとそれぞれ平面視において重なっている。すなわち、第1および第2トランジスタは、第3および第4トランジスタとそれぞれ積層されている。これにより、1ポートSRAMセルの小面積化を図ることができる。

#### 【0013】

本開示の第2態様では、1ポートSRAMセルを含む半導体記憶装置であって、前記1ポートSRAMセルは、一方のノードが第1電圧を供給する第1電源に、他方のノードが第1ノードに、ゲートが第2ノードにそれぞれ接続された第1トランジスタと、一方のノードが前記第1電源に、他方のノードが前記第2ノードに、ゲートが前記第1ノードに、他方のノードが前記第1電圧と異なる第2電圧を供給する第2電源に、ゲートが前記第2ノードにそれぞれ接続された第3トランジスタと、一方のノードが前記第2ノードに、他方のノードが前記第2電源に、ゲートが前記第1ノードにそれぞれ接続された第4トランジスタと、一方のノードが第1ビット線に、他方のノードが前記第1ノードに、ゲートがワード線にそれぞれ接続された第5トランジスタと、一方のノードが前記第1ビット線と相補ビット線対を構成する第2ビット線に、他方のノードが前記第2ノードに、ゲートが前記ワード線にそれぞれ接続された第6トランジスタとを備える。前記第3および第4トランジスタは、それぞれ、第1層に形成された第1導電型の立体構造トランジスタである、第1立体構造トランジスタと、少なくとも一部が、前記第1立体構造トランジスタと平面視で重なるように、前記第1層より上層の第2層に形成された前記第1導電型の立体構造トランジスタである、第2立体構造トランジスタとを含む。前記第5および第6トランジスタは、それぞれ、前記第1および第2層の少なくともいずれか一方に形成された前記第1導電型の立体構造トランジスタを含む。前記第1および第2トランジスタは、それぞれ、前記第2層に形成された前記第1導電型と異なる第2導電型の立体構造トランジスタを含む。前記第1および第2トランジスタを構成する立体構造トランジスタの数は、それぞれ、前記第3トランジスタを構成する立体構造トランジスタの数よりも少なく、かつ、前記第4トランジスタを構成する立体構造トランジスタの数よりも少ない。

#### 【0014】

10

20

30

40

50

本開示によると、第1～第6トランジスタにより1ポートSRAM回路が構成されており、第1～第6トランジスタは、それぞれ、立体構造トランジスタにより構成されている。また、第1および第2トランジスタを構成する立体構造トランジスタの数は、それぞれ、第3トランジスタを構成する立体構造トランジスタの数よりも少なく、かつ、第4トランジスタを構成する立体構造トランジスタの数よりも少ない。これにより、CFETを用いた、1ポートSRAMセルのレイアウト構造において、1ポートSRAM回路を構成する6つのトランジスタが、異なる数のナノワイヤトランジスタで構成された1ポートSRAMセルのレイアウト構造を実現することができる。

#### 【0015】

また、第3および第4トランジスタにおいて、第1立体構造トランジスタは、少なくとも一部が、第2立体構造トランジスタと平面視において重なっている。すなわち、第3および第4トランジスタのそれぞれにおいて、第1立体構造トランジスタは、第2立体構造トランジスタと積層されている。これにより、1ポートSRAMセルの小面積化を図ることができる。

10

#### 【発明の効果】

#### 【0016】

本開示によると、CFETを用いた、1ポートSRAMセルのレイアウト構造において、1ポートSRAM回路を構成する6つのトランジスタが、異なる数のナノワイヤトランジスタで構成された1ポートSRAMセルのレイアウト構造を実現することができる。

#### 【図面の簡単な説明】

20

#### 【0017】

【図1】第1実施形態に係る1ポートSRAMセルのレイアウト構造の例を示す平面図。

【図2】第1実施形態に係る1ポートSRAMセルのレイアウト構造の例を示す断面図。

【図3】第1実施形態に係る1ポートSRAMセルの構成を示す回路図。

【図4】第1実施形態に係る1ポートSRAMセルのレイアウト構造の他の例を示す平面図。

【図5】第1実施形態に係る1ポートSRAMセルのレイアウト構造の他の例を示す平面図。

【図6】第2実施形態に係る1ポートSRAMセルのレイアウト構造の例を示す平面図。

【図7】第2実施形態に係る1ポートSRAMセルのレイアウト構造の他の例を示す平面図。

30

【図8】第2実施形態に係る1ポートSRAMセルのレイアウト構造の他の例を示す平面図。

【図9】第2実施形態に係る1ポートSRAMセルのレイアウト構造の他の例を示す平面図。

【図10】CFETを備えた半導体装置の構造を示す断面図。

【図11】CFETを備えた半導体装置の構造を示す断面図。

【図12】CFETを備えた半導体装置の構造を示す断面図。

【図13】CFETを備えた半導体装置の構造を示す断面図。

#### 【発明を実施するための形態】

40

#### 【0018】

以下、実施の形態について、図面を参照して説明する。以下の実施の形態では、半導体記憶装置は複数のSRAMセル（本明細書では、適宜、単にセルという）を備えており、この複数のSRAMセルのうち少なくとも一部は、CFET、すなわち、立体構造のP型FETとN型FETを基板に対して垂直方向に積層した立体構造デバイスを備えるものとする。

#### 【0019】

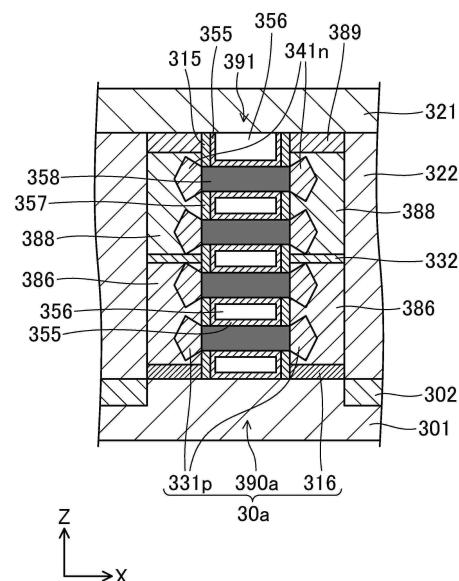

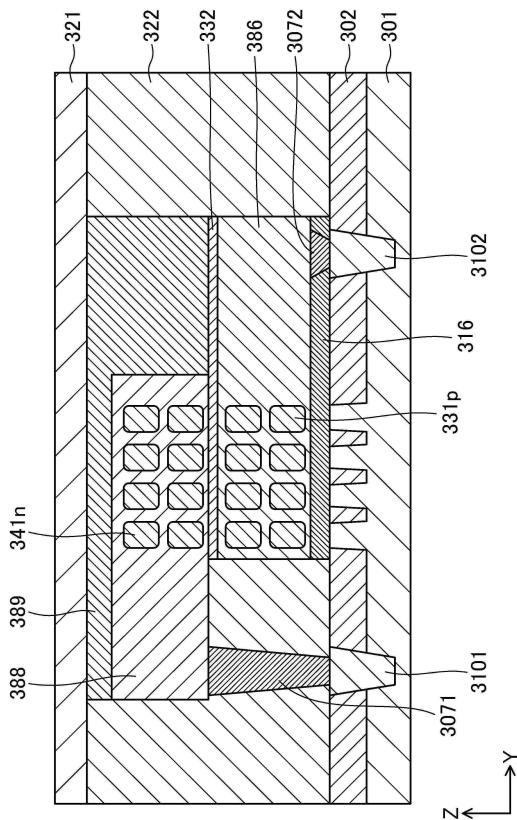

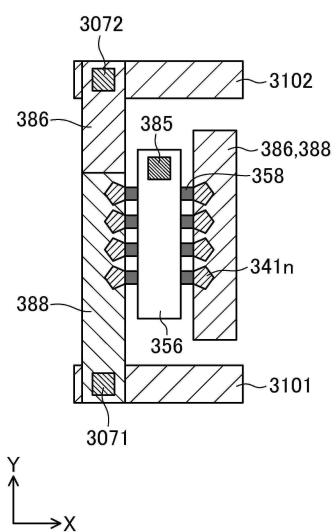

まず、CFETの基本構造について説明する。図10～図13はCFETを備えた半導体装置の構造を示す図であり、図10はX方向における断面図、図11はY方向におけるゲート部分の断面図、図12はY方向におけるソース・ドレイン部分の断面図、図13は

50

平面図である。なお、X方向はナノワイヤが延びる方向、Y方向はゲートが延びる方向、Z方向は基板面と垂直をなす方向としている。また、図10～図13は概略図であり、各部の寸法や位置等は必ずしも整合していない。

#### 【0020】

この半導体装置では、シリコン(Si)基板等の半導体基板301の表面に素子分離領域302が形成されており、素子分離領域302により、素子活性領域30aが画定されている。素子活性領域30aでは、P型FET上にN型FETが形成されている。

#### 【0021】

素子活性領域30aでは、半導体基板301上に積層トランジスタ構造390aが形成されている。積層トランジスタ構造390aは、半導体基板301上に形成されたゲート構造391を含む。ゲート構造391は、ゲート電極356、複数のナノワイヤ358、ゲート絶縁膜355、絶縁膜357を含む。ゲート電極356は、Y方向に延び、Z方向に立ち上がる。ナノワイヤ358は、X方向でゲート電極356を貫通し、Y方向及びZ方向に配列されている。ゲート絶縁膜355は、ゲート電極356とナノワイヤ358との間に形成されている。ゲート電極356及びゲート絶縁膜355は、X方向において、ナノワイヤ358の両端から後退した位置に形成されており、この後退した部分に絶縁膜357が形成されている。半導体基板301上に、絶縁膜357の両脇において、絶縁膜316が形成されている。321, 322は層間絶縁膜である。

10

#### 【0022】

また、図11に示すように、ゲート電極356は、開口部375に設けられたビア385によって、上層の配線と接続される。

20

#### 【0023】

例えば、ゲート電極356には、チタン、チタン窒化物又は多結晶シリコン等を用いることができる。例えば、ゲート絶縁膜355には、ハフニウム酸化物、アルミニウム酸化物又はハフニウム及びアルミニウムの酸化物等の高誘電率材料を用いることができる。例えば、ナノワイヤ358にはシリコン等を用いることができる。例えば、絶縁膜316、絶縁膜357には、シリコン酸化物又はシリコン窒化物等を用いることができる。

#### 【0024】

この半導体装置では、Z方向に配列するナノワイヤ358の本数は4であり、素子活性領域30aでは、半導体基板301側の2本のナノワイヤ358の各端部にP型半導体層331pが形成されている。P型半導体層331pに接する2つのローカル配線386がX方向でゲート構造391を挟むようにして形成されている。また、半導体基板101から離間する側の2本のナノワイヤ358の各端部にN型半導体層341nが形成されている。N型半導体層341nに接する2つのローカル配線388がX方向でゲート構造391を挟むようにして形成されている。ローカル配線386とローカル配線388との間に絶縁膜332が形成されている。ローカル配線388の上に絶縁膜389が形成されている。例えば、P型半導体層331pはP型SiGe層であり、N型半導体層341nはN型Si層である。例えば、絶縁膜332には、シリコン酸化物又はシリコン窒化物等を用いることができる。

30

#### 【0025】

また、図12に示すように、ローカル配線388は、ビア3071を介して、埋め込み配線3101と接続される。ローカル配線386は、ビア3072を介して、埋め込み配線3102と接続される。

40

#### 【0026】

このように、積層トランジスタ構造390aは、ゲート電極356、ナノワイヤ358、ゲート絶縁膜355及びP型半導体層331pを含むP型FETを有する。このP型FETでは、一方のP型半導体層331pがソース領域として機能し、他方のP型半導体層331pがドレイン領域として機能し、ナノワイヤ358がチャネルとして機能する。積層トランジスタ構造390aは、ゲート電極356、ナノワイヤ358、ゲート絶縁膜355及びN型半導体層341nを含むN型FETも有する。このN型FETでは、一方の

50

N型半導体層341nがソース領域として機能し、他方のN型半導体層341nがドレイン領域として機能し、ナノワイヤ358がチャネルとして機能する。

【0027】

なお、積層トランジスタ構造より上層については、ピアおよび金属配線によりトランジスタ間の配線等が行われるが、これらは既知の配線プロセスによって実現が可能である。

【0028】

なお、ここでは、P型FETおよびN型FETにおけるナノワイヤの本数は、それぞれ、Y方向に4本、Z方向に2本、計8本ずつであるものとしたが、ナノノワイヤの本数はこれに限られるものではない。また、P型FETとN型FETのナノワイヤの本数は、異なっていてもかまわない。

【0029】

また、本明細書では、ナノワイヤの両端に形成され、トランジスタのソースまたはドレインとなる端子を構成する半導体層部のことを「パッド」という。上述したCFETの基本構造例では、P型半導体層331pおよびN型半導体層341nが、パッドに相当する。

【0030】

また、以降の実施形態における平面図および断面図においては、各絶縁膜等の記載は省略することがある。また、以降の実施形態における平面図および断面図については、ナノワイヤおよびその両側のパッドを、簡易化した直線状の形状で記載することがある。また、本明細書において、「同一サイズ」等のように、サイズ等が同じであることを意味する表現は、製造上のばらつき範囲を含んでいるものとする。

【0031】

また、本明細書では、トランジスタのソースおよびドレインのことを、適宜、トランジスタの「ノード」と称する。すなわち、トランジスタの一方のノードとは、トランジスタのソースまたはドレインのことを指し、トランジスタの両方のノードとは、トランジスタのソースおよびドレインのことを指す。

【0032】

また、本明細書では、P型FETとN型FETとが積層されていることを基本とするが、一部において、上層（または下層）のみに、P型FETまたはN型FETが形成される。その形成方法として、例えば、上層（または下層）のデバイスを形成した後に、上層（または下層）のデバイスを部分的に除去する（例えば、パッド部の除去、または、ゲート配線およびパッド部の除去）ことにより、上層（または下層）のみに、P型FETまたはN型FETを形成することができる。また、上層（または下層）のデバイスのパッド部のエピタキシャル成長による形成時に、上層（または下層）を部分的に非形成とすることにより、上層（または下層）のみに、P型FETまたはN型FETを形成することができる。

【0033】

また、本明細書では、P型FETとN型FETとが積層されていることを基本とするが、一部において、上層および下層に、同一導電型のFET（P型FETまたはN型FET）が積層される。すなわち、上層および下層のうち少なくとも一方に、異なる導電型のFETが形成されることがある。その形成方法として、例えば、上層（または下層）の一部にN型FET（またはP型FET）を形成する場合、N型FET（またはP型FET）を形成する部分にマスクをして、他の部分をP導電型（またはN導電型）にドーピングする。その後、N型FETを形成する部分以外にマスクをして、N導電型（またはP導電型）にドーピングする。これにより、上層および下層のうち少なくとも一方に、異なる導電型のFETを形成できるため、同一導電型のFETを確実に積層することができる。

【0034】

また、以下の実施形態では、「VDD」、「VSS」は、電圧または電源自体を示すために用いるとする。

【0035】

また、以下の実施形態およびその変形例において、同様の部材等については、同じ符号を付して説明を省略することができる。

## 【0036】

## (第1実施形態)

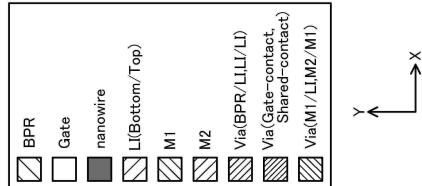

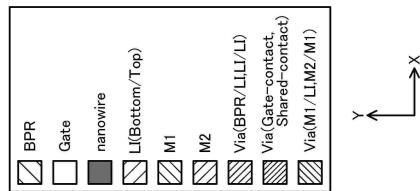

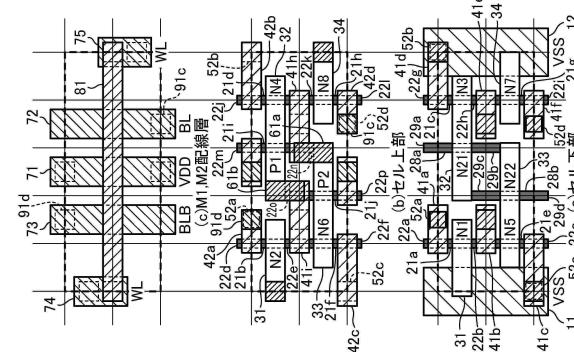

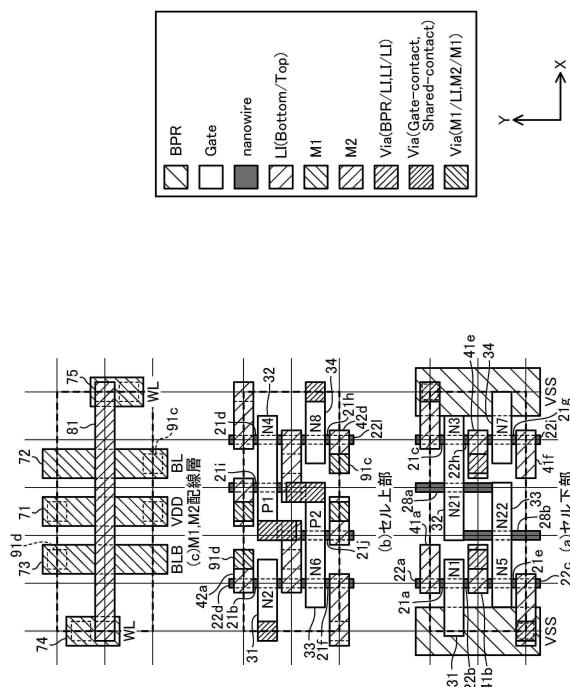

図1および図2は第1実施形態に係る1ポートSRAMセルのレイアウト構造の例を示す図であり、図1(a)～(c)は平面図、図2(a)～(c)は平面視横方向における断面図である。具体的には、図1(a)は下部、すなわち基板に近い側に形成された立体構造トランジスタ(ここではN型ナノワイヤFET)を含む部分を示し、図1(b)は上部、すなわち基板から遠い側に形成された立体構造トランジスタ(ここではP型ナノワイヤFET)を含む部分を示し、図1(c)はM1, M2配線層、すなわち立体構造トランジスタが形成された部分より上部の金属配線層を示す。図2(a)は線X1-X1'の断面、図2(b)は線X2-X2'の断面、図2(c)は線X3-X3'の断面である。

10

## 【0037】

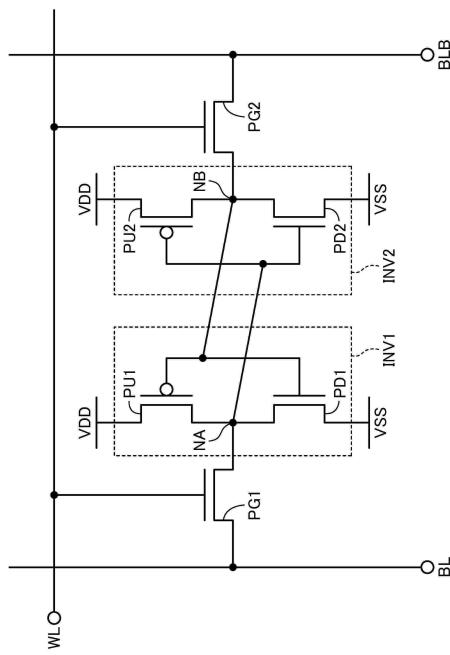

図3は第1実施形態に係る1ポートSRAMセルの構成を示す回路図である。図3に示すように、1ポートSRAMセルには、ロードトランジスタPU1, PU2と、ドライブトランジスタPD1, PD2と、アクセストランジスタPG1, PG2とにより構成される1ポートSRAM回路が構成されている。ロードトランジスタPU1, PU2は、P型FETであり、ドライブトランジスタPD1, PD2およびアクセストランジスタPG1, PG2は、N型FETである。

## 【0038】

ロードトランジスタPU1は、電源VDDと第1ノードNAとの間に設けられており、ドライブトランジスタPD1は、第1ノードNAと電源VSSとの間に設けられている。ロードトランジスタPU1およびドライブトランジスタPD1は、ゲートが第2ノードNBに接続されており、インバータINV1を構成している。ロードトランジスタPU2は、電源VDDと第2ノードNBとの間に設けられており、ドライブトランジスタPD2は、第2ノードNBと電源VSSとの間に設けられている。ロードトランジスタPU2およびドライブトランジスタPD2は、ゲートが第1ノードNAに接続されており、インバータINV2を構成している。すなわち、一方のインバータの出力は他方のインバータの入力に接続されており、これにより、ラッチが構成されている。

20

## 【0039】

アクセストランジスタPG1は、ビット線BLと第1ノードNAとの間に設けられており、ゲートがワード線WLに接続されている。アクセストランジスタPG2は、ビット線BLBと第2ノードNBとの間に設けられており、ゲートがワード線WLに接続されている。なお、ビット線BL, BLBは、相補ビット線対を構成する。

30

## 【0040】

1ポートSRAM回路では、相補ビット線対を構成するビット線BL, BLBを、ハイレベルおよびローレベルにそれぞれ駆動し、ワード線WLをハイレベルに駆動すると、第1ノードNAにハイレベルが書き込まれ、第2ノードNBにローレベルが書き込まれる。一方、ビット線BL, BLBを、ローレベルおよびハイレベルにそれぞれ駆動し、ワード線WLをハイレベルに駆動すると、第1ノードNAにローレベルが書き込まれ、第2ノードNBにハイレベルが書き込まれる。そして、第1および第2ノードNA, NBにデータがそれぞれ書き込まれている状態で、ワード線WLをローレベルに駆動すると、ラッチ状態が確定し、第1および第2ノードNA, NBに書き込まれているデータが保持される。

40

## 【0041】

また、ビット線BL, BLBを始めハイレベルにプリチャージしておき、ワード線WLをハイレベルに駆動すると、第1および第2ノードNA, NBに書き込まれたデータに応じてビット線BL, BLBの状態がそれぞれ確定するため、SRAMセルからのデータの読み出しを行うことができる。具体的に、第1ノードNAがハイレベルであり、第2ノードNBがローレベルであれば、ビット線BLはハイレベルを保持し、ビット線BLBはローレベルにディスチャージされる。一方、第1ノードNAがローレベルであり、第2ノードNBがハイレベルであれば、ビット線BLはローレベルにディスチャージされ、ビット線BLBはハイレベルを保持する。

50

**【 0 0 4 2 】**

以上に説明したように、1ポートSRAMセルは、ビット線BL, BLBおよびワード線WLを制御することによって、SRAMセルへのデータ書き込み、データ保持およびSRAMセルからのデータ読み出し機能を有する。

**【 0 0 4 3 】**

なお、以下の説明では、図1等の平面図において、図面横方向をX方向、図面縦方向をY方向、基板面に垂直な方向をZ方向としている。また、図1等の平面図において縦横に走る実線、および、図2等の断面図において縦に走る実線は、設計時に部品配置を行うために用いるグリッドを示す。グリッドは、X方向において等間隔に配置されており、またY方向において等間隔に配置されている。なお、グリッド間隔は、X方向とY方向とにおいて同じであってもよいし異なっていてもよい。また、グリッド間隔は、層ごとに異なっていてもかまわない。さらに、各部品は必ずしもグリッド上に配置される必要はない。ただし、製造ばらつきを抑制する観点から、部品はグリッド上に配置される方が好ましい。

10

**【 0 0 4 4 】**

また、図1等の平面図においてセルを取り囲むように表示された点線は、1ポートSRAMセルのセル枠（1ポートSRAMセルの外縁）を示す。1ポートSRAMセルは、セル枠が、X方向またはY方向に隣接するセルのセル枠と接するように配置される。

**【 0 0 4 5 】**

また、図1等では、X方向に1ポートSRAMセルを隣接して配置する場合、X方向に反転させて配置される。また、Y方向に1ポートSRAMセルを隣接して配置する場合、Y方向に反転させて配置される。

20

**【 0 0 4 6 】**

図1(a)に示すように、セル下部において、セル左右両端に、Y方向に延びる電源配線11, 12がそれぞれ設けられている。電源配線11, 12はともに、埋め込み配線層に形成された埋め込み電源配線（BPR: Buried Power Rail）である。電源配線11, 12は電圧VSSを供給する。なお、図1では、トランジスタP1, P2がロードトランジスタPU1, PU2にそれぞれ相当する。トランジスタN3, N4がドライブトランジスタPD1に相当する。トランジスタN5, N6がドライブトランジスタPD2に相当する。トランジスタN7, N8がアクセストランジスタPG1に相当する。トランジスタN1, N2がアクセストランジスタPG2に相当する。

30

**【 0 0 4 7 】**

セル下部に、Y方向に延びるナノワイヤ(nanowire)21a~21hが形成されており、セル上部には、Y方向に延びるナノワイヤ21i, 21j, 26a~26dが形成されている。

**【 0 0 4 8 】**

また、ナノワイヤ21a~21dは、X方向に並んで形成されている。ナノワイヤ21e~21hは、X方向に並んで形成されている。ナノワイヤ21i, 26a, 26bは、X方向に並んで形成されている。ナノワイヤ21j, 26c, 26dは、X方向に並んで形成されている。

40

**【 0 0 4 9 】**

また、ナノワイヤ21a~21d, 26a, 26bは、ナノワイヤ21e~21h, 26c, 26dとそれぞれY方向に並んで形成されている。

**【 0 0 5 0 】**

また、ナノワイヤ21a, 21c~21f, 21hは、ナノワイヤ26a, 21i, 26b, 26c, 21j, 26dとそれぞれ平面視で重なっている。

**【 0 0 5 1 】**

ゲート配線(Gate)31~34は、セル下部からセル上部にかけてZ方向に延びてあり、かつ、X方向に延びている。ゲート配線31, 32は、X方向に並んで形成されており、ゲート配線33, 34は、X方向に並んで形成されている。ゲート配線31は、トランジスタN1, N2およびダミートランジスタP21のゲートとなる。ゲート配線32は、

50

トランジスタN3, N4, P1およびダミートランジスタP22のゲートとなる。ゲート配線33は、トランジスタN5, N6, P2およびダミートランジスタP23のゲートとなる。ゲート配線34は、トランジスタN7, N8およびダミートランジスタP24のゲートとなる。

【0052】

ナノワイヤ21aの図面上端、ナノワイヤ21a, 21eの間、ナノワイヤ21eの図面下端、ナノワイヤ21bの図面上端、ナノワイヤ21b, 21fの間、ナノワイヤ21fの図面下端、ナノワイヤ21cの図面上端、ナノワイヤ21c, 21gの間、ナノワイヤ21gの図面下端、ナノワイヤ21dの図面上端、ナノワイヤ21d, 21hの間、および、ナノワイヤ21hの図面下端に、N型半導体がドーピングされたパッド22a～221がそれぞれ形成されている。ナノワイヤ21a～21hが、トランジスタN1～N8のチャネル部をそれぞれ構成する。パッド22a, 22bが、トランジスタN1のノードを構成する。パッド22d, 22eが、トランジスタN2のノードを構成する。パッド22g, 22hが、トランジスタN3のノードを構成する。パッド22j, 22kが、トランジスタN4のノードを構成する。パッド22b, 22cが、トランジスタN5のノードを構成する。パッド22e, 22fが、トランジスタN6のノードを構成する。パッド22h, 22iが、トランジスタN7のノードを構成する。パッド22k, 22lが、トランジスタN8のノードを構成する。

【0053】

すなわち、ナノワイヤ21a、ゲート配線31およびパッド22a, 22bによって、トランジスタN1が構成される。ナノワイヤ21b、ゲート配線31およびパッド22d, 22eによって、トランジスタN2が構成される。ナノワイヤ21c、ゲート配線32およびパッド22g, 22hによって、トランジスタN3が構成される。ナノワイヤ21d、ゲート配線32およびパッド22j, 22kによって、トランジスタN4が構成される。ナノワイヤ21e、ゲート配線33およびパッド22b, 22cによって、トランジスタN5が構成される。ナノワイヤ21f、ゲート配線33およびパッド22e, 22fによって、トランジスタN6が構成される。ナノワイヤ21g、ゲート配線34およびパッド22h, 22iによって、トランジスタN7が構成される。ナノワイヤ21h、ゲート配線34およびパッド22k, 22lによって、トランジスタN8が構成される。

【0054】

ナノワイヤ21iの図面上端、ナノワイヤ21iの図面下端、ナノワイヤ21jの図面上端、および、ナノワイヤ21jの図面下端に、P型半導体がドーピングされたパッド22m～22pがそれぞれ形成されている。ナノワイヤ21i, 21jが、トランジスタP1, P2のチャネル部をそれぞれ構成する。パッド22m, 22nが、トランジスタP1のノードを構成する。パッド22o, 22pが、トランジスタP2のノードを構成する。

【0055】

すなわち、ナノワイヤ21i、ゲート配線32およびパッド22m, 22nによって、トランジスタP1が構成される。ナノワイヤ21j、ゲート配線33およびパッド22o, 22pによって、トランジスタP2が構成される。

【0056】

ナノワイヤ26aの図面上端、ナノワイヤ26a, 26cの間、ナノワイヤ26cの図面下端、ナノワイヤ26bの図面上端、ナノワイヤ26b, 26dの間、および、ナノワイヤ26dの図面下端に、P型半導体がドーピングされたダミーパッド27a～27fがそれぞれ形成されている。ダミーパッド27a, 27bが、ダミートランジスタP21のノードを構成する。ダミーパッド27d, 27eが、ダミートランジスタP22のノードを構成する。ダミーパッド27b, 27cが、ダミートランジスタP23のノードを構成する。ダミーパッド27e, 27fが、ダミートランジスタP24のノードを構成する。ナノワイヤ26a～26dが、ダミートランジスタP21～P24のチャネル部をそれぞれ構成する。なお、ダミートランジスタP21～P24は、論理機能を有さないトランジスタである。また、図3の回路図では、ダミートランジスタP21～P24を省略して図

10

20

30

40

50

示している。なお、以降に説明する実施形態およびその変形例における1ポートS R A Mセルには、ダミートランジスタが含まれるものがあるが、各ダミートランジスタは、1ポートS R A Mセルの論理機能に影響しないため、回路図への図示は省略する。

#### 【0057】

したがって、トランジスタN 1, N 3 ~ N 6, N 8が、ダミートランジスタP 2 1、トランジスタP 1、ダミートランジスタP 2 2, P 2 3、トランジスタP 2およびダミートランジスタP 2 4とそれぞれ平面視において重なっている。

#### 【0058】

また、トランジスタN 1 ~ N 4がX方向に並んで形成されている。トランジスタN 5 ~ N 8がX方向に並んで形成されている。トランジスタP 1およびダミートランジスタP 2 1, P 2 2がX方向に並んで形成されている。トランジスタP 2およびダミートランジスタP 2 3, P 2 4がX方向に並んで形成されている。

10

#### 【0059】

また、トランジスタN 1 ~ N 4およびダミートランジスタP 2 1, P 2 2は、トランジスタN 5 ~ N 8およびダミートランジスタP 2 3, P 2 4とそれぞれY方向に並んで形成されている。

#### 【0060】

図1(a)に示すように、セル下部に、X方向に延びるローカル配線(LI: Local Interconnect)4 1 a ~ 4 1 fが形成されている。ローカル配線4 1 aは、パッド2 2 a, 2 2 dと接続されている。ローカル配線4 1 bは、パッド2 2 b, 2 2 eと接続されている。ローカル配線4 1 cは、パッド2 2 c, 2 2 fと接続されている。ローカル配線4 1 dは、パッド2 2 g, 2 2 jと接続されている。ローカル配線4 1 eは、パッド2 2 h, 2 2 kと接続されている。ローカル配線4 1 fは、パッド2 2 i, 2 2 lと接続されている。

20

#### 【0061】

すなわち、トランジスタN 1, N 2は互いのパッド同士がローカル配線により接続されており、ゲート配線を共有している。トランジスタN 3, N 4は互いのパッド同士がローカル配線により接続されており、ゲート配線を共有している。トランジスタN 5, N 6は互いのパッド同士がローカル配線により接続されており、ゲート配線を共有している。トランジスタN 7, N 8は互いのパッド同士がローカル配線により接続されており、ゲート配線を共有している。また、トランジスタN 1, N 2がアクセストランジスタP G 2に相当する。トランジスタN 3, N 4がドライブトランジスタP D 1に相当する。トランジスタN 5, N 6がドライブトランジスタP D 2に相当する。トランジスタN 7, N 8がアクセストランジスタP G 1に相当する。したがって、本実施形態に係る1ポートS R A Mセルにおいて、ドライブトランジスタP D 1, P D 2およびアクセストランジスタP G 1, P G 2は、それぞれ、並列接続された2つのN型F E Tにより構成されている。

30

#### 【0062】

図1(b)に示すように、セル上部に、X方向に延びるローカル配線4 1 g ~ 4 1 jが形成されている。ローカル配線4 1 gは、パッド2 2 mと接続されている。ローカル配線4 1 hは、パッド2 2 nと接続されている。ローカル配線4 1 iは、パッド2 2 oと接続されている。ローカル配線4 1 jは、パッド2 2 pと接続されている。

40

#### 【0063】

ローカル配線4 1 bは、コンタクト(via)5 1 aを介して、ローカル配線4 1 iと接続されている。ローカル配線4 1 cは、コンタクト5 1 bを介して、電源配線1 1と接続されている。ローカル配線4 1 dは、コンタクト5 1 cを介して、電源配線1 2と接続されている。ローカル配線4 1 eは、コンタクト5 1 dを介して、ローカル配線4 1 hと接続されている。

#### 【0064】

ローカル配線4 1 hは、シェアードコンタクト(Shared-contact)6 1 aを介して、ゲート配線3 3と接続されている。ローカル配線4 1 iは、シェアードコンタクト6 1 bを介して、ゲート配線3 2と接続されている。なお、ローカル配線4 1 e, 4 1 h、コンタク

50

ト 5 1 d、シェアードコンタクト 6 1 a およびゲート配線 3 3 が第 1 ノード N A に相当し、ローカル配線 4 1 b, 4 1 i、コンタクト 5 1 a、シェアードコンタクト 6 1 b およびゲート配線 3 2 が第 2 ノード N B に相当する。

【 0 0 6 5 】

図 1 ( c ) に示すように、金属配線層である M 1 配線層に、セル上下両端にかけて Y 方向に延びる配線 7 1 ~ 7 3 が形成されている。また、配線 7 4, 7 5 が形成されている。配線 7 1 は、電圧 V D D を供給する。配線 7 2, 7 3 が、ビット線 B L, B L B にそれぞれ相当する。

【 0 0 6 6 】

M 1 配線層の上層である M 2 配線層に、セル左右両端にかけて X 方向に延びる配線 8 1 が形成されている。配線 8 1 は、ワード線 W L に相当する。

10

【 0 0 6 7 】

配線 7 1 は、コンタクト 9 1 a を介して、ローカル配線 4 1 g と接続されており、コンタクト 9 1 b を介して、ローカル配線 4 1 j と接続されている。配線 7 2 は、コンタクト 9 1 c を介して、ローカル配線 4 1 f と接続されている。配線 7 3 は、コンタクト 9 1 d を介して、ローカル配線 4 1 a と接続されている。配線 7 4 は、コンタクト (Gate-contact) 6 1 c を介して、ゲート配線 3 1 と接続されており、コンタクト 9 1 e を介して、配線 8 1 と接続されている。配線 7 5 は、コンタクト 6 1 d を介して、ゲート配線 3 4 と接続されており、コンタクト 9 1 f を介して、配線 8 1 と接続されている。すなわち、配線 8 1 は、コンタクト 9 1 e、配線 7 4 およびコンタクト 6 1 c を介して、ゲート配線 3 1 と接続されており、コンタクト 9 1 f、配線 7 5 およびコンタクト 6 1 d を介して、ゲート配線 3 4 と接続されている。

20

【 0 0 6 8 】

以上の構成により、トランジスタ P 1 (ロードトランジスタ P U 1) は、パッド 2 2 m が電圧 V D D を供給する配線 7 1 に、パッド 2 2 n がローカル配線 4 1 h (第 1 ノード N A) に、ゲート配線 3 2 がシェアードコンタクト 6 1 b (第 2 ノード N B) にそれぞれ接続されている。トランジスタ P 2 (ロードトランジスタ P U 2) は、パッド 2 2 p が電圧 V D D を供給する配線 7 1 に、パッド 2 2 o がローカル配線 4 1 i (第 2 ノード N B) に、ゲート配線 3 3 がシェアードコンタクト 6 1 a (第 1 ノード N A) にそれぞれ接続されている。トランジスタ N 3, N 4 (ドライブトランジスタ P D 1) は、パッド 2 2 h, 2 2 k がローカル配線 4 1 e (第 1 ノード N A) に、パッド 2 2 g, 2 2 j が電圧 V S S を供給する電源配線 1 2 に、ゲート配線 3 2 がシェアードコンタクト 6 1 b (第 2 ノード N B) にそれぞれ接続されている。トランジスタ N 5, N 6 (ドライブトランジスタ P D 2) は、パッド 2 2 b, 2 2 e がローカル配線 4 1 b (第 2 ノード N B) に、パッド 2 2 c, 2 2 f が電圧 V S S を供給する電源配線 1 1 に、ゲート配線 3 3 がシェアードコンタクト 6 1 a (第 1 ノード N A) にそれぞれ接続されている。トランジスタ N 7, N 8 (アクセストランジスタ P G 1) は、パッド 2 2 i, 2 2 l が配線 7 2 (ビット線 B L) に、パッド 2 2 h, 2 2 k がローカル配線 4 1 e (第 1 ノード N A) に、ゲート配線 3 4 が配線 8 1 (ワード線 W L) にそれぞれ接続されている。トランジスタ N 1, N 2 (アクセストランジスタ P G 2) は、パッド 2 2 a, 2 2 d が配線 7 3 (ビット線 B L B) に、パッド 2 2 b, 2 2 e がローカル配線 4 1 b (第 2 ノード N B) に、ゲート配線 3 1 が配線 8 1 (ワード線 W L) にそれぞれ接続されている。

30

【 0 0 6 9 】

すなわち、トランジスタ N 1 ~ N 8, P 1, P 2 により 1 ポート S R A M 回路が構成される。また、トランジスタ N 1 ~ N 8, P 1, P 2 は、それぞれ、立体構造トランジスタである。

40

【 0 0 7 0 】

また、トランジスタ P 1, P 2 がロードトランジスタ P U 1, P U 2 にそれぞれ相当する。並列接続されたトランジスタ N 1, N 2 がアクセストランジスタ P G 2 に相当する。並列接続されたトランジスタ N 3, N 4 がドライブトランジスタ P D 1 に相当する。並列

50

接続されたトランジスタ N 5 , N 6 がドライブトランジスタ P D 2 に相当する。並列接続されたトランジスタ N 7 , N 8 がアクセストランジスタ P G 1 に相当する。すなわち、ロードトランジスタ P U 1 , P U 2 は、それぞれ、1つのトランジスタにより構成されており、ドライブトランジスタ P D 1 , P D 2 およびアクセストランジスタ P G 1 , P G 2 は、それぞれ、並列接続された2つのトランジスタにより構成されている。このため、ロードトランジスタ P U 1 , P U 2 を構成するトランジスタの数は、それぞれ、ドライブトランジスタ P D 1 を構成するトランジスタの数よりも少なく、かつ、ドライブトランジスタ P D 2 を構成するトランジスタの数よりも少ない。

#### 【 0 0 7 1 】

したがって、C F E T を用いた、1ポート S R A M セルのレイアウト構造において、1ポート S R A M 回路を構成する6つのトランジスタ（ロードトランジスタ P U 1 , P U 2 、ドライブトランジスタ P D 1 , P D 2 およびアクセストランジスタ P G 1 , P G 2 ）が、異なる数のナノワイヤトランジスタで構成された1ポート S R A M セルのレイアウト構造を実現することができる。これにより、半導体記憶装置の、動作速度および動作安定性の向上を図ることができる。

#### 【 0 0 7 2 】

また、トランジスタ P 1 , P 2 は、トランジスタ N 3 , N 6 とそれぞれ平面視で重なっている。すなわち、トランジスタ P 1 , P 2 は、トランジスタ N 3 , N 6 とそれぞれ積層される。これにより、1ポート S R A M セルの小面積化を行うことができる。

#### 【 0 0 7 3 】

また、ドライブトランジスタ P D 1 , P D 2 およびアクセストランジスタ P G 1 , P G 2 は、それぞれ、並列接続された2つのトランジスタにより構成されている。これにより、1ポート S R A M セルからのデータの読み出し、および、1ポート S R A M セルへのデータの書き込みを容易化するとともに、半導体記憶装置の動作の高速化を図ることができる。

#### 【 0 0 7 4 】

また、セル下部に、トランジスタ N 1 ~ N 8 が形成されており、セル上部に、トランジスタ P 1 , P 2 およびダミートランジスタ P 2 1 ~ P 2 4 が形成されている。すなわち、セル下部には、N型 F E T のみが形成され、セル上部には、ダミートランジスタを含むP型 F E T のみが形成されている。これにより、製造プロセスの複雑化を防止することができる。

#### 【 0 0 7 5 】

なお、ダミートランジスタ P 2 1 ~ P 2 4 の各ノードには、いずれもローカル配線が接続されていない。このため、ダミートランジスタ P 2 1 ~ P 2 4 は、1ポート S R A M セルの論理機能に影響を与えない。また、本実施形態に係る1ポート S R A M セルに、ダミートランジスタ P 2 1 ~ P 2 4 が形成されてもよい。ただし、ダミートランジスタ P 2 1 ~ P 2 4 を形成した方が、半導体記憶装置の製造ばらつきの抑制、歩留まりの向上、信頼性の向上を図ることができる。

#### 【 0 0 7 6 】

また、ローカル配線 4 1 h とゲート配線 3 3 とを接続するシェアードコンタクト 6 1 a 、および、ローカル配線 4 1 i とゲート配線 3 2 とを接続するシェアードコンタクト 6 1 b は、M 1 配線層に配置された配線とゲート配線とを接続するコンタクト 6 1 c , 6 1 d と同じプロセス工程において形成されてもよいし、別のプロセス工程において形成されてもよい。

#### 【 0 0 7 7 】

また、電圧 V D D を供給する配線 7 1 を M 1 配線層に設けているが、電圧 V D D を供給する電源配線は埋め込み配線層に設けてもよい。また、電圧 V D D を供給する電源配線を M 1 配線層および埋め込み配線層の両方に設けてもよい。この場合、電圧 V D D を供給する電源が強化されるため、電源の安定化を図ることができる。

#### 【 0 0 7 8 】

10

20

30

40

50

## (変形例 1 )

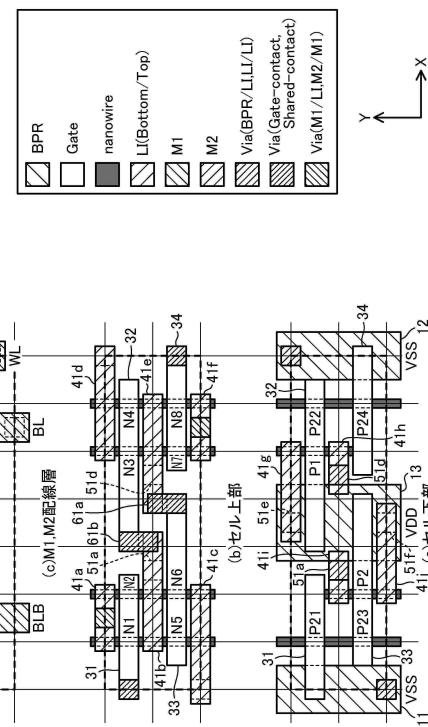

図 4 は第 1 実施形態に係る 1 ポート S R A M セルのレイアウト構造の他の例を示す平面図である。具体的に、図 4 ( a ) はセル下部を示し、図 4 ( b ) はセル上部を示し、図 4 ( c ) は M 1 , M 2 配線層を示す。図 4 では、セル上部に N 型 F E T が形成されており、セル下部に P 型 F E T が形成されている。すなわち、図 4 では、セル上部およびセル下部に形成されるトランジスタの導電型が、図 1 に示す 1 ポート S R A M セルと逆になっている。

## 【 0 0 7 9 】

具体的に、セル上部にトランジスタ N 1 ~ N 8 およびローカル配線 4 1 a ~ 4 1 f が形成されており、セル下部にトランジスタ P 1 , P 2 、ダミートランジスタ P 2 1 ~ P 2 4 およびローカル配線 4 1 g ~ 4 1 j が形成されている。

10

## 【 0 0 8 0 】

また、埋め込み配線層に、Y 方向に延びる電源配線 1 3 が形成されている。電源配線 1 3 は、電圧 V D D を供給する。

## 【 0 0 8 1 】

ローカル配線 4 1 g は、コンタクト 5 1 e を介して、電源配線 1 3 と接続されており、ローカル配線 4 1 j は、コンタクト 5 1 f を介して、電源配線 1 3 と接続されている。

20

## 【 0 0 8 2 】

ローカル配線 4 1 i は、コンタクト 5 1 a 、ローカル配線 4 1 b およびシェアードコンタクト 6 1 b を介して、ゲート配線 3 2 と接続されている。ローカル配線 4 1 h は、コンタクト 5 1 d 、ローカル配線 4 1 e およびシェアードコンタクト 6 1 a を介して、ゲート配線 3 3 と接続されている。

20

## 【 0 0 8 3 】

本変形例により、第 1 実施形態に係る 1 ポート S R A M セルと同様の効果を得ることができる。

## 【 0 0 8 4 】

## (変形例 2 )

図 5 は第 1 実施形態に係る 1 ポート S R A M セルのレイアウト構造の他の例を示す平面図である。具体的に、図 5 ( a ) はセル下部を示し、図 5 ( b ) はセル上部を示し、図 5 ( c ) は M 1 , M 2 配線層を示す。図 5 では、図 1 と対比すると、トランジスタ N 2 , N 7 がセル下部に形成されていない。すなわち、図 5 では、アクセストランジスタ P G 1 , P G 2 が、それぞれ、1 つのトランジスタで構成されている。

30

## 【 0 0 8 5 】

具体的に、セル下部に、ナノワイヤ 2 1 b , 2 1 g およびパッド 2 2 d , 2 2 i が形成されていない。また、ローカル配線 4 1 a は、パッド 2 2 a と接続されており、ローカル配線 4 1 f は、パッド 2 2 1 と接続されている。

## 【 0 0 8 6 】

本変形例により、第 1 実施形態に係る 1 ポート S R A M セルと同様の効果を得ることができる。

40

## 【 0 0 8 7 】

また、トランジスタ N 1 , N 3 ~ N 6 , N 8 は、ダミートランジスタ P 2 1 、トランジスタ P 1 、ダミートランジスタ P 2 2 , P 2 3 、トランジスタ P 2 およびダミートランジスタ P 2 4 とそれぞれ平面視で重なっている。すなわち、各トランジスタは、他のトランジスタと積層されているため、一部のトランジスタの除去等を行う必要がない。このため、製造プロセスの複雑化を抑制することができる。

## 【 0 0 8 8 】

なお、トランジスタ N 1 , N 3 ~ N 6 , N 8 をセル上部に形成し、トランジスタ P 1 , P 2 およびダミートランジスタ P 2 1 ~ P 2 4 をセル下部に形成してもよい。すなわち、セル上部およびセル下部に形成されるトランジスタの導電型を逆にしてもよい。この場合、1 ポート S R A M セルには、1 ポート S R A M 回路が構成されるように、ローカル配線

50

およびコンタクト等が形成される。

【0089】

(第2実施形態)

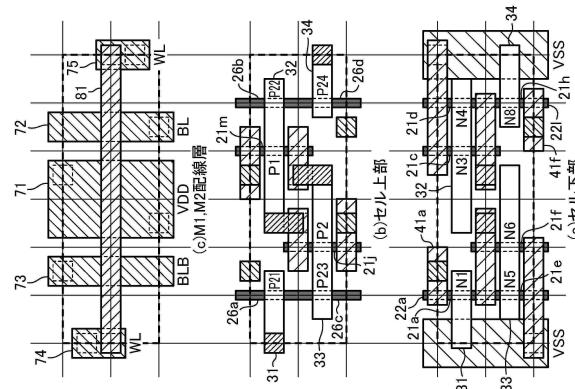

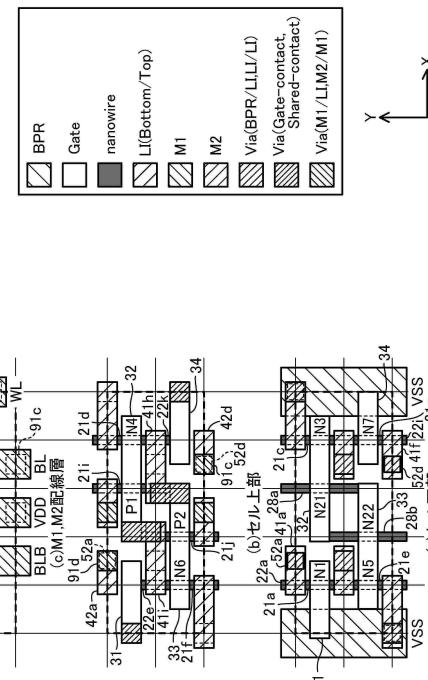

図6は第2実施形態に係る1ポートSRAMセルのレイアウト構造の例を示す平面図である。具体的に、図6(a)はセル下部を示し、図6(b)はセル上部を示し、図6(c)はM1,M2配線層を示す。第2実施形態に係る1ポートSRAMセルでは、セル下部に、トランジスタN1,N3,N5,N7およびダミートランジスタN21,N22が形成されており、セル上部に、トランジスタN2,N4,N6,N8,P1,P2が形成されている。なお、図6では、トランジスタP1,P2がロードトランジスタPU1,PU2にそれぞれ相当する。トランジスタN3,N4がドライブトランジスタPD1に相当する。トランジスタN5,N6がドライブトランジスタPD2に相当する。トランジスタN7,N8がアクセストランジスタPG1に相当する。トランジスタN1,N2がアクセストランジスタPG2に相当する。

10

【0090】

セル下部に、ナノワイヤ21a,21c,21e,21gが形成されている。また、セル下部に、Y方向に延びるナノワイヤ28a,28bが形成されている。セル上部に、ナノワイヤ21b,21d,21f,21h,21i,21jが形成されている。

【0091】

ナノワイヤ21a,21c,28aは、X方向に並んで形成されている。ナノワイヤ21e,21g,28bは、X方向に並んで形成されている。ナノワイヤ21b,21d,21iは、X方向に並んで形成されている。ナノワイヤ21f,21h,21jは、X方向に並んで形成されている。

20

【0092】

また、ナノワイヤ21a～21dは、ナノワイヤ21e～21hとそれぞれY方向に並んで形成されている。

【0093】

また、ナノワイヤ21a,21c,21e,21g,28a,28bは、ナノワイヤ21b,21d,21f,21h,21i,21jとそれぞれ平面視で重なっている。

【0094】

ゲート配線32は、ダミートランジスタN21のゲートとなり、ゲート配線33は、ダミートランジスタN22のゲートとなる。ナノワイヤ28aの図面上端、ナノワイヤ28aの図面下端、ナノワイヤ28bの図面上端、および、ナノワイヤ28bの図面下端に、N型半導体がドーピングされたダミーパッド29a～29dがそれぞれ形成されている。ナノワイヤ28a,28bがダミートランジスタN21,N22のチャネル部をそれぞれ構成する。ダミーパッド29a,29bがダミートランジスタN21のノードを構成し、ダミーパッド29c,29dがダミートランジスタN22のノードを構成する。なお、ダミートランジスタN21,N22は、論理機能を有さないトランジスタである。

30

【0095】

したがって、トランジスタN1,N3,N5,N7およびダミートランジスタN21,N22は、トランジスタN2,N4,N6,N8,P1,P2とそれぞれ平面視で重なっている。

40

【0096】

また、トランジスタN1,N3およびダミートランジスタN21は、X方向に並んで形成されている。トランジスタN5,N7およびダミートランジスタN22は、X方向に並んで形成されている。トランジスタN2,N4,P1は、X方向に並んで形成されている。トランジスタN6,N8,P2はX方向に並んで形成されている。

【0097】

セル下部において、ローカル配線41aは、パッド22aと接続されている。ローカル配線41bは、パッド22bと接続されている。ローカル配線41cは、パッド22cと接続されている。ローカル配線41dは、パッド22gと接続されている。ローカル配線

50

41eは、パッド22hと接続されている。ローカル配線41fは、パッド22iと接続されている。

【0098】

セル上部に、X方向に延びるローカル配線42a～42dが形成されている。ローカル配線42aは、パッド22dと接続されている。ローカル配線42bは、パッド22jと接続されている。ローカル配線42cは、パッド22fと接続されている。ローカル配線42dは、パッド22lと接続されている。また、ローカル配線41iは、パッド22e, 22oと接続されている。ローカル配線41hは、パッド22n, 22kと接続されている。

【0099】

ローカル配線42aは、コンタクト52aを介して、ローカル配線41aと接続されており、コンタクト91dを介して配線73と接続されている。ローカル配線42bは、コンタクト52bを介して、ローカル配線41dと接続されている。ローカル配線42cは、コンタクト52cを介して、ローカル配線41cと接続されている。ローカル配線42dは、コンタクト52dを介して、ローカル配線41fと接続されており、コンタクト91cを介して、配線72に接続されている。

【0100】

すなわち、トランジスタN1, N2は互いのパッド同士がローカル配線およびコンタクトにより接続されており、ゲート配線を共有している。トランジスタN3, N4は互いのパッド同士がローカル配線およびコンタクトにより接続されており、ゲート配線を共有している。トランジスタN5, N6は互いのパッド同士がローカル配線およびコンタクトにより接続されており、ゲート配線を共有している。トランジスタN7, N8は互いのパッド同士がローカル配線およびコンタクトにより接続されており、ゲート配線を共有している。また、トランジスタN1, N2がアクセストランジスタPG2に相当する。トランジスタN3, N4がドライブトランジスタPD1に相当する。トランジスタN5, N6がドライブトランジスタPD2に相当する。トランジスタN7, N8がアクセストランジスタPG1に相当する。したがって、本実施形態に係る1ポートSRAMセルにおいて、ドライブトランジスタPD1, PD2およびアクセストランジスタPG1, PG2は、それぞれ、並列接続された2つのN型FETにより構成されている。

【0101】

以上の構成により、トランジスタP1(ロードトランジスタPU1)は、パッド22mが電圧VDDを供給する配線71に、パッド22nがローカル配線41h(第1ノードNA)に、ゲート配線32がシェアードコンタクト61b(第2ノードNB)にそれぞれ接続されている。トランジスタP2(ロードトランジスタPU2)は、パッド22pが電圧VDDを供給する配線71に、パッド22oがローカル配線41i(第2ノードNB)に、ゲート配線33がシェアードコンタクト61a(第1ノードNA)にそれぞれ接続されている。トランジスタN3, N4(ドライブトランジスタPD1)は、パッド22h, 22kがローカル配線41e, 41h(第1ノードNA)に、パッド22g, 22jが電圧VSSを供給する電源配線12に、ゲート配線32がシェアードコンタクト61b(第2ノードNB)にそれぞれ接続されている。トランジスタN5, N6(ドライブトランジスタPD2)は、パッド22b, 22eがローカル配線41b, 41i(第2ノードNB)に、パッド22c, 22fが電圧VSSを供給する電源配線11に、ゲート配線33がシェアードコンタクト61a(第1ノードNA)にそれぞれ接続されている。トランジスタN7, N8(アクセストランジスタPG1)は、パッド22i, 22lが配線72(ビット線BL)に、パッド22h, 22kがローカル配線41e, 41h(第1ノードNA)に、ゲート配線34が配線81(ワード線WL)にそれぞれ接続されている。トランジスタN1, N2(アクセストランジスタPG2)は、パッド22a, 22dが配線73(ビット線BLB)に、パッド22b, 22eがローカル配線41b, 41i(第2ノードNB)に、ゲート配線31が配線81(ワード線WL)にそれぞれ接続されている。

【0102】

10

20

30

40

50

すなわち、トランジスタN1～N8, P1, P2により1ポートSRAM回路が構成される。また、トランジスタN1～N8, P1, P2は、それぞれ、立体構造トランジスタである。

#### 【0103】

また、トランジスタP1, P2がロードトランジスタPU1, PU2にそれぞれ相当する。並列接続されたトランジスタN1, N2がアクセストランジスタPG2に相当する。並列接続されたトランジスタN3, N4がドライブトランジスタPD1に相当する。並列接続されたトランジスタN5, N6がドライブトランジスタPD2に相当する。並列接続されたトランジスタN7, N8がアクセストランジスタPG1に相当する。すなわち、ロードトランジスタPU1, PU2は、それぞれ、1つのトランジスタにより構成されており、ドライブトランジスタPD1, PD2およびアクセストランジスタPG1, PG2は、それぞれ、並列接続された2つのトランジスタにより構成されている。このため、ロードトランジスタPU1, PU2を構成するトランジスタの数は、それぞれ、ドライブトランジスタPD1を構成するトランジスタの数よりも少なく、かつ、ドライブトランジスタPD2を構成するトランジスタの数よりも少ない。

10

#### 【0104】

したがって、CFETを用いた、1ポートSRAMセルのレイアウト構造において、1ポートSRAM回路を構成する6つのトランジスタ（ロードトランジスタPU1, PU2、ドライブトランジスタPD1, PD2およびアクセストランジスタPG1, PG2）が、異なる数のナノワイヤトランジスタで構成された1ポートSRAMセルのレイアウト構造を実現することができる。これにより、半導体記憶装置の、動作速度および動作安定性の向上を図ることができる。

20

#### 【0105】

また、トランジスタN1, N3, N5, N7は、トランジスタN2, N4, N6, N8とそれぞれ平面視で重なっている。すなわち、トランジスタN1, N3, N5, N7が、トランジスタN2, N4, N6, N8とそれぞれ積層される。これにより、1ポートSRAMセルの小面積化を行うことができる。

#### 【0106】

また、ドライブトランジスタPD1, PD2およびアクセストランジスタPG1, PG2は、それぞれ、並列接続された2つのトランジスタにより構成されている。これにより、1ポートSRAMセルからのデータの読み出し、および、1ポートSRAMセルへのデータの書き込みを容易化するとともに、半導体記憶装置の動作の高速化を図ることができる。

30

#### 【0107】

また、トランジスタN1, N3, N5, N7およびダミートランジスタN21, N22は、トランジスタN2, N4, N6, N8, P1, P2とそれぞれ平面視で重なっている。すなわち、トランジスタN1, N3, N5, N7およびダミートランジスタN21, N22が、トランジスタN2, N4, N6, N8, P1, P2とそれぞれ積層される。これにより、各トランジスタは、他のトランジスタと積層されているため、一部のトランジスタの除去等を行う必要がない。このため、製造プロセスの複雑化を抑制することができる。

40

#### 【0108】

また、セル下部に、トランジスタN1, N3, N5, N7およびダミートランジスタN21, N22が形成されており、セル上部に、トランジスタN2, N4, N6, N8, P1, P2が形成されている。すなわち、セル下部にN型FETのみが形成されており、セル上部に形成されるトランジスタの一部をN型FETに置き換えることで、上記構成を実現することができる。これにより、製造プロセスの複雑化を抑制することができる。

#### 【0109】

なお、ダミートランジスタN21, N22の各ノードには、いずれもローカル配線が接続されていない。このため、ダミートランジスタN21, N22は、1ポートSRAMセルの論理機能に影響を与えない。また、本実施形態に係る1ポートSRAMセルに、ダミ

50

トランジスタN21, N22が形成されていなくてもよい。ただし、ダミートランジスタN21, N22を形成した方が、半導体記憶装置の製造ばらつきの抑制、歩留まりの向上、信頼性の向上を図ることができる。

【0110】

また、電圧VDDを供給する配線71をM1配線層に設けているが、電圧VDDを供給する電源配線は埋め込み配線層に設けてよい。また、電圧VDDを供給する電源配線をM1配線層および埋め込み配線層の両方に設けてよい。この場合、電圧VDDを供給する電源が強化されるため、電源の安定化を図ることができる。

【0111】

(変形例1)

図7は第2実施形態に係る1ポートSRAMセルのレイアウト構造の他の例を示す平面図である。具体的に、図7(a)はセル下部を示し、図7(b)はセル上部を示し、図7(c)はM1, M2配線層を示す。図7では、図6と対比すると、コンタクト52a, 52dが形成されていない。すなわち、ローカル配線41aとローカル配線42aが接続されておらず、ローカル配線41fとローカル配線42dが接続されていない。したがって、図7では、アクセストランジスタPG1, PG2が、それぞれ、1つのトランジスタにより構成されている。

【0112】

具体的に、図7では、ローカル配線41a, 42aを接続するコンタクト52a、および、ローカル配線41f, 42dを接続するコンタクト52dが形成されていない。このため、トランジスタN1のパッド22aは、ローカル配線41aを介して、信号の入力を受けない。トランジスタN7のパッド22iは、ローカル配線41fを介して、信号の入力を受けない。すなわち、トランジスタN1, N7は、それぞれ、一方のノードがフローティング状態となるため、論理機能を有さないダミートランジスタとなる。したがって、図7では、アクセストランジスタPG1がトランジスタN8のみにより構成されており、アクセストランジスタPG1がトランジスタN2のみにより構成されている。

【0113】

本変形例により、第2実施形態に係る1ポートSRAMセルと同様の効果を得ることができる。

【0114】

また、トランジスタN1, N3, N5, N7およびダミートランジスタN21, N22は、トランジスタN2, N4, N6, N8, P1, P2とそれぞれ平面視で重なっている。すなわち、トランジスタN1, N3, N5, N7およびダミートランジスタN21, N22が、トランジスタN2, N4, N6, N8, P1, P2とそれぞれ積層される。これにより、各トランジスタは、他のトランジスタと積層されているため、一部のトランジスタの除去等を行う必要がない。このため、製造プロセスの複雑化を抑制することができる。

【0115】

(変形例2)

図8は第2実施形態に係る1ポートSRAMセルのレイアウト構造の他の例を示す平面図である。具体的に、図8(a)はセル下部を示し、図8(b)はセル上部を示し、図8(c)はM1, M2配線層を示す。図8では、図6と対比すると、トランジスタN2, N8がセル上部に形成されていない。すなわち、図8では、アクセストランジスタPG1, PG2が、それぞれ、1つのトランジスタにより構成されている。

【0116】

具体的に、セル上部にナノワイヤ21b, 21hおよびパッド22d, 22lが形成されていない。すなわち、図8では、アクセストランジスタPG1がトランジスタN7のみにより構成されており、アクセストランジスタPG2がトランジスタN1のみにより構成されている。

【0117】

本変形例により、第2実施形態に係る1ポートSRAMセルと同様の効果を得ることができる

できる。

【0118】

また、トランジスタN2, N8がセル上部に形成されていない。これにより、1ポートS R A Mセルの負荷容量を抑えることができる。

【0119】

なお、本変形例では、トランジスタN2, N8をセル上部に形成していないが、これに限られない。トランジスタN1, N7をセル下部に形成せずに、トランジスタN2, N8をセル上部に形成してもよい。

【0120】

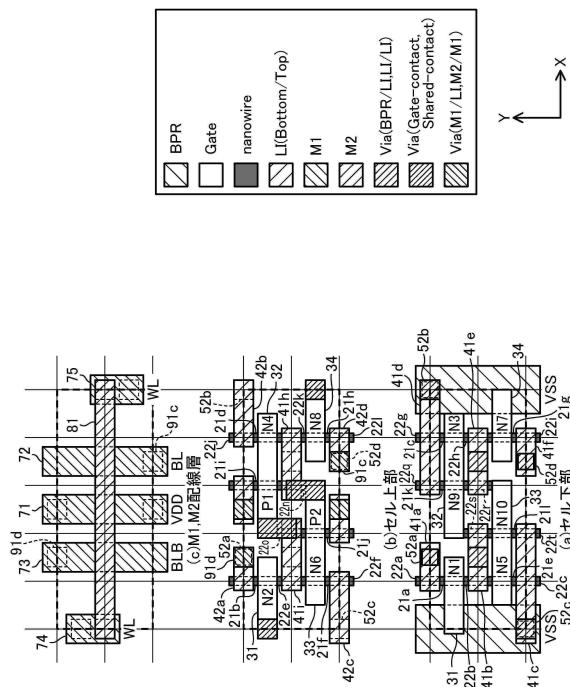

(変形例3)

10

図9は第2実施形態に係る1ポートS R A Mセルのレイアウト構造の他の例を示す平面図である。具体的に、図9(a)はセル下部を示し、図9(b)はセル上部を示し、図9(c)はM1, M2配線層を示す。図9では、図6と対比すると、ダミートランジスタN21, N22に代えて、トランジスタN9, N10がセル下部に形成されている。図9では、ドライブトランジスタPD1, PD2が、それぞれ、3つのトランジスタにより構成されている。

【0121】

具体的に、セル下部に、Y方向に延びるナノワイヤ21k, 21lが形成されている。ナノワイヤ21kは、ナノワイヤ21a, 21cとX方向に並んで形成されており、ナノワイヤ21lは、ナノワイヤ21e, 21gとX方向に並んで形成されている。また、ナノワイヤ21k, 21lは、ナノワイヤ21i, 21jとそれぞれ平面視で重なっている。

20

【0122】

ゲート配線32は、トランジスタN9のゲートとなり、ゲート配線33は、トランジスタN10のゲートとなる。ナノワイヤ21kの図面上端、ナノワイヤ21kの図面下端、ナノワイヤ21lの図面上端、および、ナノワイヤ21lの図面下端に、N型半導体にドーピングされたパッド22q~22tがそれぞれ形成されている。ナノワイヤ21k, 21lが、トランジスタN9, N10のチャネル部をそれぞれ構成する。パッド22q, 22rがトランジスタN9のノードを構成し、パッド22s, 22tがトランジスタN10のノードを構成する。

【0123】

30

すなわち、ナノワイヤ21k、ゲート配線32およびパッド22q, 22rによって、トランジスタN9が構成される。ナノワイヤ21l、ゲート配線33およびパッド22s, 22tによって、トランジスタN10が構成される。

【0124】

したがって、トランジスタN9, N10は、トランジスタPD1, PD2とそれぞれ平面視で重なっている。また、トランジスタN9は、トランジスタN1, N3とX方向に並んで形成されており、トランジスタN10は、トランジスタN5, N7とX方向に並んで形成されている。

【0125】

セル下部において、ローカル配線41bは、パッド22b, 22sと接続されている。ローカル配線41cは、パッド22c, 22tと接続されている。ローカル配線41dは、パッド22g, 22qと接続されている。ローカル配線41eは、パッド22h, 22rと接続されている。

40

【0126】

すなわち、トランジスタN3, N4, N9は互いのパッド同士がローカル配線により接続されており、ゲート配線を共有している。トランジスタN5, N6, N10は互いのパッド同士がローカル配線により接続されており、ゲート配線を共有している。また、図9では、トランジスタN3, N4, N9がドライブトランジスタPD1に相当し、トランジスタN5, N6, N10がドライブトランジスタPD2に相当する。したがって、図9では、ドライブトランジスタPD1, PD2が、それぞれ、並列接続された3つのN型F E

50

Tによって構成されている。

【0127】

本変形例により、第2実施形態に係る1ポートSRAMセルと同様の効果を得ることができる。

【0128】

また、ドライブトランジスタPD1は、並列接続されたトランジスタN3, N4, N9で構成されている。ドライブトランジスタPD2は、並列接続されたトランジスタN5, N6, N10で構成されている。これにより、1ポートSRAMセルの、駆動能力の向上、読み出し動作の高速化および動作の安定性の向上を図ることができる。

【0129】

また、トランジスタN9, N10は、ダミートランジスタN21, N22に代えて、1ポートSRAMセルにそれぞれ配置される。これにより、1ポートSRAMセルのセル幅(X方向におけるセルの幅)を変更せずに、1ポートSRAMセルの、駆動能力の向上、読み出し動作の高速化および動作の安定性の向上を図ることができる。

【0130】

なお、ロードトランジスタPU1, PU2、ドライブトランジスタPD1, PD2およびアクセストランジスタPG1, PG2を構成する立体構造トランジスタの数は、それぞれ、上述の各実施形態および変形例の数に限られない。例えば、上述の各実施形態よりも、ドライブトランジスタPD1, PD2およびアクセストランジスタPG1, PG2の数をそれぞれ増やしたい場合、上述の各実施形態で示したドライブトランジスタPD1, PD2およびアクセストランジスタPG1, PG2とそれぞれX方向に並ぶように立体構造トランジスタを形成すればよい。この場合、ドライブトランジスタ(ドライブトランジスタPD1, PD2)およびアクセストランジスタ(アクセストランジスタPG1, PG2)のいずれか一方を増やしてもよいし、ドライブトランジスタおよびアクセストランジスタの両方を増やしてもよい。

【0131】

また、上述の各実施形態では、各トランジスタはそれぞれ1本のナノワイヤを備えるものとしたが、トランジスタの一部または全部は、複数本のナノワイヤを備えてもよい。この場合、平面視でX方向において複数本のナノワイヤを設けてもよいし、Z方向において複数本のナノワイヤを設けてもよい。また、X方向およびZ方向の両方においてそれぞれ複数本のナノワイヤを設けてもよい。また、セルの上部と下部とにおいて、トランジスタが備えるナノワイヤの本数が異なっていてもよい。

【0132】

また、上述の各実施形態では、各トランジスタを、並列接続された複数のトランジスタで構成してもよい。

【0133】

また、上述の各実施形態では、ナノワイヤの断面形状はほぼ正方形としているが、これに限られるものではない。例えば、円形や長方形であってもよい。

【0134】

また、上述の各実施形態では、立体構造トランジスタとしてナノワイヤFETを例にとつて説明を行ったが、これに限られるものではない。例えば、セルの下部に形成されるトランジスタは、フィン型トランジスタであってもよい。

【産業上の利用可能性】

【0135】

本開示では、CFETを用いたSRAMセルを備えた半導体記憶装置に適用することができるので、CFETを用いた1ポートSRAMセルを実現することができるとともに、1ポートSRAMセルの小面積化を図ることができる。

【符号の説明】

【0136】

11, 12, 13 電源配線

10

20

30

40

50

2 1 a ~ 2 1 1 ナノワイヤ

2 2 a ~ 2 2 t パッド

## N1 ~ N10, P1, P2 トランジスタ

72 ~ 75, 81 配線

## P U 1 , P U 2 ロードトランジスタ

## P D 1 , P D 2 ドライブトランジスタ

## PG1, PG2 アクセストランジスタ

## W L ワード線

## BL, BLB ビット線

## 【四面】

〔 図 1 〕

【図2】

【図3】

【図4】

10

20

【図5】

【図6】

30

40

50

【図 7】

【図 8】

10

20

【図 9】

【図 10】

30

40

50

### 【図11】

【図12】

【図13】

---

フロントページの続き

(56)参考文献

国際公開第2014/185085 (WO, A1)

国際公開第2014/184933 (WO, A1)

特開平06-061452 (JP, A)

特開2013-143536 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H10B 10/00

G11C 11/412

H01L 21/8238