(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6826214号

(P6826214)

(45) 発行日 令和3年2月3日(2021.2.3)

(24) 登録日 令和3年1月18日(2021.1.18)

|               |               |

|---------------|---------------|

| (51) Int.Cl.  | F 1           |

| HO 1 L 25/065 | (2006.01)     |

| HO 1 L 25/07  | (2006.01)     |

| HO 1 L 25/18  | (2006.01)     |

| HO 1 L 23/06  | (2006.01)     |

| HO 1 L 23/36  | (2006.01)     |

|               | HO 1 L 25/08  |

|               | HO 1 L 25/08  |

|               | HO 1 L 23/06  |

|               | HO 1 L 23/36  |

|               | HO 1 L 21/607 |

|               | Z             |

|               | B             |

|               | Z             |

|               | D             |

|               | A             |

請求項の数 22 (全 17 頁) 最終頁に続く

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2019-563579 (P2019-563579)  |

| (86) (22) 出願日      | 平成29年11月16日 (2017.11.16)      |

| (65) 公表番号          | 特表2020-520128 (P2020-520128A) |

| (43) 公表日           | 令和2年7月2日 (2020.7.2)           |

| (86) 國際出願番号        | PCT/US2017/061922             |

| (87) 國際公開番号        | W02018/212785                 |

| (87) 國際公開日         | 平成30年11月22日 (2018.11.22)      |

| 審査請求日              | 令和1年11月15日 (2019.11.15)       |

| (31) 優先権主張番号       | 15/596,663                    |

| (32) 優先日           | 平成29年5月16日 (2017.5.16)        |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

早期審査対象出願

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 503455363<br>レイセオン カンパニー                   |

|           | アメリカ合衆国 マサチューセッツ州 O<br>2451-1449 ウォルサム ウィン |

|           | ター ストリート 870                               |

| (74) 代理人  | 100107766<br>弁理士 伊東 忠重                     |

| (74) 代理人  | 100070150<br>弁理士 伊東 忠彦                     |

| (74) 代理人  | 100091214<br>弁理士 大貫 進介                     |

最終頁に続く

(54) 【発明の名称】酸化物接合ウエハ STACKにおけるダイ封入

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体ウエハアセンブリであって、

第1表面及び集積回路を含む第1のウエハと、

第1表面及び第2表面を持つ第2のウエハであり、該第1表面が前記第1のウエハに接合され、前記第1のウエハと当該第2のウエハとでキャビティを画成する、第2のウエハと、

前記第1のウエハに機械的且つ電気的に接続された、前記キャビティ内の半導体ダイと、

集積回路を含むとともに、前記第2のウエハの前記第2表面に接合された第1表面を持ち、それにより、前記キャビティ内の前記半導体ダイを封入する第3のウエハと、

を有し、

当該半導体ウエハアセンブリは、1つ以上の積層集積回路を生産するように構成されており、当該半導体ウエハアセンブリがダイシングされたときに各積層集積回路が1つ以上の封入された半導体ダイを含むことになり、前記第2のウエハは、前記第1のウエハの前記集積回路及び前記第3のウエハの前記集積回路に相互接続された能動集積回路を含む、

半導体ウエハアセンブリ。

## 【請求項 2】

前記半導体ダイは、バンプボンド、ワイヤインターコネクト、超音波ボンド、及び酸化物ボンドのうちの少なくとも1つによって、前記第1のウエハに機械的且つ電気的に接続

10

20

されている、請求項 1 に記載の半導体ウエハアセンブリ。

【請求項 3】

前記キャビティは、前記半導体ダイを封入するように気密封止されている、請求項 1 に記載の半導体ウエハアセンブリ。

【請求項 4】

前記第 3 のウエハの前記集積回路は、前記第 3 のウエハの前記第 1 表面に近接しており、且つ前記第 1 及び第 2 のウエハに電気的に接続されている、請求項 1 に記載の半導体ウエハアセンブリ。

【請求項 5】

前記第 1 のウエハの前記集積回路は、前記第 2 及び第 3 のウエハに電気的に接続された前記第 1 のウエハの前記第 1 表面に近接している、請求項 1 に記載の半導体ウエハアセンブリ。 10

【請求項 6】

前記第 1 、第 2 及び第 3 のウエハのうちの少なくとも 1 つを通って当該半導体ウエハアセンブリの外表面に至る、前記半導体ダイへの少なくとも 1 つの電気経路、を更に有する請求項 1 に記載の半導体ウエハアセンブリ。

【請求項 7】

前記半導体ダイと前記第 1 、第 2 、及び第 3 のウエハのうちの 1 つ以上の間の 1 つ以上の熱インタフェース、を更に有する請求項 1 に記載の半導体ウエハアセンブリ。 20

【請求項 8】

前記第 2 のウエハと前記第 3 のウエハとが、前記キャビティからの熱的分離を提供するエアギャップを画成するようにバンプ接合されている、請求項 1 に記載の半導体ウエハアセンブリ。

【請求項 9】

前記第 1 のウエハの前記集積回路は、前記第 1 のウエハの前記第 1 表面に近接しており、前記第 1 のウエハは、当該第 1 のウエハを貫いて該集積回路に至る電気経路を含む、請求項 1 に記載の半導体ウエハアセンブリ。

【請求項 10】

前記第 2 のウエハの前記第 2 表面及び前記第 3 のウエハの前記第 1 表面は各々、酸化物層を含み、且つ 30

前記第 2 のウエハと前記第 3 のウエハとが、それぞれの酸化物層で酸化物接合されている、

請求項 1 に記載の半導体ウエハアセンブリ。

【請求項 11】

前記第 1 、第 2 、及び第 3 のウエハのうちの 1 つ以上が、当該半導体ウエハアセンブリの外部から前記キャビティへの導管を画成している、請求項 1 に記載の半導体ウエハアセンブリ。

【請求項 12】

前記導管及び前記キャビティが少なくとも部分的に熱伝導材料で充填されている、請求項 11 に記載の半導体ウエハアセンブリ。 40

【請求項 13】

前記導管及び前記キャビティが排気及び封止されて真空パッケージを提供している、請求項 11 に記載の半導体ウエハアセンブリ。

【請求項 14】

前記導管及び前記キャビティは、封止前に、排気され、液体又は気体で埋め戻されている、請求項 11 に記載の半導体ウエハアセンブリ。

【請求項 15】

前記半導体ダイは更に、前記第 1 のウエハ及び前記第 3 のウエハのうちの少なくとも一方に酸化物接合された少なくとも 1 つの酸化物層を有する、請求項 1 に記載の半導体ウエハアセンブリ。 50

## 【請求項 1 6】

集積回路及び第 1 表面を含む第 1 のウエハと、

第 1 表面及び第 2 表面を持つ第 2 のウエハであり、該第 1 表面が前記第 1 のウエハに接合され、前記第 1 のウエハと当該第 2 のウエハとでキャビティを画成する、第 2 のウエハと、

前記第 1 のウエハに機械的且つ電気的に接続された、前記キャビティ内の半導体ダイと

、

集積回路を含むとともに、前記第 2 のウエハの前記第 2 表面に接合された第 1 表面を持ち、それにより、前記キャビティ内の前記半導体ダイを封入する第 3 のウエハと、

を有し、

10

前記第 3 のウエハの前記集積回路は、前記第 3 のウエハの前記第 1 表面に近接しており、且つ前記第 1 及び第 2 のウエハに電気的に接続されている、

半導体ウエハアセンブリ。

## 【請求項 1 7】

集積回路及び第 1 表面を含む第 1 のウエハと、

前記第 1 のウエハに接合された第 2 のウエハであり、前記第 1 のウエハと当該第 2 のウエハとでキャビティを画成するように前記第 1 のウエハに接合された第 2 のウエハと、

前記第 1 のウエハに機械的且つ電気的に接続された、前記キャビティ内の半導体ダイと

、

集積回路を含むとともに、前記半導体ダイが前記キャビティ内に封入されるように前記第 2 のウエハに接合されている第 3 のウエハと、

を有し、

20

前記第 1 のウエハの前記集積回路は、前記第 2 及び第 3 のウエハに電気的に接続された前記第 1 のウエハの前記第 1 表面に近接している、

半導体ウエハアセンブリ。

## 【請求項 1 8】

第 1 のウエハと、

前記第 1 のウエハに酸化物接合された第 2 のウエハであり、前記第 1 のウエハと当該第 2 のウエハとでキャビティを画成するように前記第 1 のウエハに酸化物接合された第 2 のウエハと、

30

前記第 1 のウエハに機械的且つ電気的に接続された、前記キャビティ内の半導体ダイと

、

前記第 2 のウエハに接合され、それにより、前記キャビティ内の前記半導体ダイを封入する第 3 のウエハと、

前記半導体ダイと前記第 1 、第 2 、及び第 3 のウエハのうちの 1 つ以上との間の 1 つ以上の熱インタフェースと、

を有する半導体ウエハアセンブリ。

## 【請求項 1 9】

第 1 のウエハと、

前記第 1 のウエハに酸化物接合された第 2 のウエハであり、前記第 1 のウエハと当該第 2 のウエハとでキャビティを画成するように前記第 1 のウエハに酸化物接合された第 2 のウエハと、

40

前記第 1 のウエハに機械的且つ電気的に接続された、前記キャビティ内の半導体ダイと

、

前記第 2 のウエハに接合され、それにより、前記キャビティ内の前記半導体ダイを封入する第 3 のウエハと、

を有し、

前記第 2 のウエハと前記第 3 のウエハとが、前記キャビティからの熱的分離を提供するエアギャップを画成するようにバンプ接合されている、

半導体ウエハアセンブリ。

50

## 【請求項 2 0】

半導体ウエハアセンブリであって、

第 1 のウエハと、

前記第 1 のウエハに酸化物接合された第 2 のウエハであり、前記第 1 のウエハと当該第 2 のウエハとでキャビティを画成する、第 2 のウエハと、

前記第 1 のウエハに機械的且つ電気的に接続された、前記キャビティ内の半導体ダイと、

前記第 2 のウエハに接合され、それにより、前記キャビティ内の前記半導体ダイを封入する第 3 のウエハと、

を有し、

前記第 1 、第 2 、及び第 3 のウエハのうちの 1 つ以上が、当該半導体ウエハアセンブリの外部から前記キャビティへの導管を画成している、

半導体ウエハアセンブリ。

## 【請求項 2 1】

集積回路を含む第 1 のウエハと、

前記第 1 のウエハに接合された第 2 のウエハであり、前記第 1 のウエハと当該第 2 のウエハとでキャビティを画成する、第 2 のウエハと、

前記第 1 のウエハに機械的且つ電気的に接続された、前記キャビティ内の半導体ダイと、

集積回路を含むとともに、前記第 2 のウエハに接合され、それにより、前記キャビティ内の前記半導体ダイを封入する第 3 のウエハと、

を有し、

前記第 2 のウエハは、前記第 1 のウエハの前記集積回路及び前記第 3 のウエハの前記集積回路に相互接続された能動集積回路を含む、

半導体ウエハアセンブリ。

## 【請求項 2 2】

集積回路を含むとともに、酸化物層を含んだ第 1 表面を持つ第 1 のウエハと、

第 1 表面及び第 2 表面を持つ第 2 のウエハであり、該第 1 表面は、前記第 1 のウエハの前記酸化物層に接合された酸化物層を含み、前記第 1 のウエハと当該第 2 のウエハとでキャビティを画成する、第 2 のウエハと、

前記第 1 のウエハに機械的且つ電気的に接続された、前記キャビティ内の半導体ダイと、

集積回路を含むとともに、前記第 2 のウエハの前記第 2 表面に接合された第 1 表面を持ち、それにより、前記キャビティ内の前記半導体ダイを封入する第 3 のウエハと、

を有し、

前記半導体ダイは更に、前記第 1 のウエハ及び前記第 3 のウエハのうちの少なくとも一方に酸化物接合された少なくとも 1 つの酸化物層を有する、

半導体ウエハアセンブリ。

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本開示は、集積回路、半導体デバイス、及び他の小型デバイスの製造に関し、より具体的には、酸化物接合ウエハスタックに封入された半導体ダイを含む 3 次元集積回路 ( 3 D - I C ) の製造に関する。

## 【背景技術】

## 【0 0 0 2】

半導体デバイスサイズが縮小するにつれて、3 D デバイス集積が、集積回路及び / 又は半導体デバイスの密度を高めて、2 D 設計と比較して高い性能及び低い電力とともに遙か

10

20

30

40

50

に小さいフォームファクタを提供するのに望ましい方法となっている。3D - I Cアセンブリは、能動電子コンポーネント（例えば、センサ及び読み出し回路）の2層以上の積み重ねられた層からなり、それらが単一のデバイスとして振る舞うように、横方向の層内接続及び上下方向の層間接続（シリコン貫通ビア、T S V）を用いている。パッケージ・ツー・パッケージスタッキング及びダイ・ツー・ダイ（D 2 D）スタッキングは、スタッキングするのに“良品判明ダイ（known good die）”の選択を可能にして、より高い歩留まりを提供することができるが、3Dと比較して性能向上は限られる。2Dアプローチは、時々、長い接続を必要とするワイヤボンドを使用し、その長い接続が、速さを低下させるとともに、可能な接続の数を制限してしまう。より洗練された2.5Dソリューションは、回路間のルーティングを提供するインターボーザへのバンプボンドを使用するが、なおも、真の3D回路よりも高い電力及び低い性能をもたらす。また、ダイの極薄さに起因して、D 2 Dスタッキングはハンドリングが難しく、破損及び汚染の影響を受けやすい。ウエハ・ツー・ウエハ（W 2 W）3Dスタッキングは、より薄いウエハを用いてT S Vをより小さい直径に縮小することを可能にして、より高い3D接続密度を可能にし、より高い帯域幅、性能、電力改善につながるとともに、より低い製造コストを提供する。しかしながら、3Dスタッキングは、3D - I C内のN個のチップのうちいずれか1つに欠陥があると、3D - I C全体が欠陥になるため、歩留まりの低下に悩まされ得る。さらに、ウエハスタッキングは、同一サイズのウエハ同士で最適であり、非シリコン材料（例えば、I I I - V族）は典型的にシリコンC M O Sロジック又はD R A Mよりも小さいウエハ上に製造されるので、ウエハレベル異種集積は製造上及び歩留まり上の難題を突き付け得る。

10

20

#### 【0003】

処理がダイレベルでの接合ほどには成熟していないので、ウエハ全体同士を接合することには、酸化物接合を用いる3D集積が主に使用されてきた。キャビティを有するウエハの接合と同様に、はんだ封止ウエハレベルパッケージングが実際に試されている。シリコンウエハ上への集積回路ダイの直接メタル・ツー・メタル接合には既知の技術が利用可能であるが、それらの技術は、プロセス応力、歩留まり、インターフェクト密度、及び熱的制約のために、多数層のウエハスタッキングには限界がある。他の技術で、複数のダイをインターボーザ上に集積したものがあるが、2 - 3層より多くまでz軸方向にさらに積み重ねを延ばしてもいなければ、異種デバイスや密封デバイスを達成してもいない。

30

#### 【0004】

本開示は、現在の限界を克服するダイ封入を用いた3D - I Cの製造のための新たな改善された方法を企図する。一部の実施形態は、より高い電力消散及びより高いパッケージング密度を可能にするオンチップ熱マネジメントの必要性にも対処する。

#### 【発明の概要】

#### 【0005】

この開示は、1つ以上のデバイスダイを封入する酸化物接合された半導体ウエハアセンブリ、及びそれを形成するプロセスに向けられる。一実施形態において、ウエハアセンブリは、酸化物層を含んだ第1表面を持つ第1のウエハと、第1表面及び第2表面を持つ第2のウエハであり、該第1表面は、第1のウエハの酸化物層に接合された酸化物層を含み、第1のウエハと第2のウエハとでキャビティを形成する、第2のウエハと、を含む。キャビティ内で第1のウエハに半導体ダイが機械的且つ電気的に接続され、第2のウエハの第2表面に接合された第1表面を持つ第3のウエハが、ダイを封入する。ダイは、バンプボンド、ワイヤインターコネクト、超音波ボンド、及び/又は酸化物ボンドによって接続され得る。封入は気密シールを有し得る。これらのウエハの各々が、集積回路（I C）と、これらのウエハのI C及びダイを、そして外部のデバイス及びウエハへと、電気的に接続するためのシリコン貫通ビア（T S V）とを含み得る。

40

#### 【0006】

他の一実施形態において、半導体ダイとこれらのウエハのうちの1つ以上との間に熱界面が形成され得る。

#### 【0007】

50

他の一実施形態において、第2の（中間）ウエハと第3の（蓋）ウエハとが、キャビティからの熱的分離を提供するエアギャップを画成するようにバンプ接合される。

【0008】

他の一実施形態において、第2の（中間）ウエハの第2表面及び第3の（蓋）ウエハの第1表面は各々、酸化物層を含む。第2のウエハと第3のウエハとが、それらそれぞれの酸化物層で酸化物接合され得る。

【0009】

他の一実施形態において、第1、第2、及び第3のウエハのうちの1つ以上が、ウエハアセンブリの外部からキャビティへの導管を有し得る。導管及びキャビティは、少なくとも部分的に熱伝導材料又は他の機能材料で充填され得る。導管及びキャビティは、熱的分離を強化するために、排気及び封止されて真空パッケージを提供してもよい。導管及びキャビティは、キャビティが封止される前に、排気され、液体又は気体で埋め戻されてもよい。

10

【0010】

他の一態様において、酸化物接合された半導体ウエハ STACK 内にエッチングされたキャビティ内の1つ以上のダイを封止する半導体ウエハアセンブリを製造する方法が提供される。当該方法は概して、当該方法は概して、キャビティ内にダイを位置付ける工程と、ウエハ STACK にダイを機械的及び電気的に取り付ける工程と、複数ある手法のうちの1つにてウエハ STACK に蓋ウエハを接合することによってキャビティ内のダイを封入する工程とを含む。半導体処理工程を適用してアセンブリを構築し（例えば、フォトリソグラフィ、堆積、アニール、化学的及び機械的研磨、エッチングなど）、上述の実施形態に従ってダイを接続する（例えば、バンプ接合、ワイヤ相互接続、超音波接合、酸化物接合など）。

20

【0011】

開示される実施形態のその他の目的及び利点が、以下の詳細な説明から、よりよく理解されることになる。

【図面の簡単な説明】

【0012】

本開示の少なくとも1つの実施形態の様々な態様が、以下にて、添付の図面を参照して説明される。理解されることには、図示の単純化及び明瞭化のため、図面に示される要素は必ずしも正確に又は縮尺通りに描かれているわけではない。例えば、それら要素のうちの一部の寸法が、明瞭さのために、他の要素に比べて誇張されていることがあり、あるいは、幾つかの物理的コンポーネントが1つの機能ブロック又は要素に含められていることがある。適切と考えられる場合、対応する又は類似の要素を指し示すために、複数の図の間で参照符号を繰り返していることがある。明瞭化の目的で、全ての図で全てのコンポーネントにラベル付けしているわけではないことがある。図面は、例示及び説明の目的で提供されており、本発明の限定を規定するものとしては意図されていない。

30

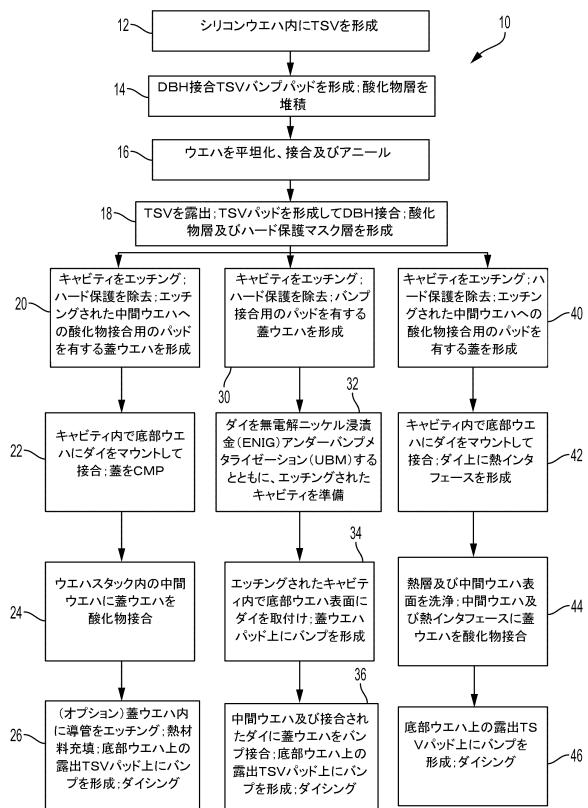

【図1】例示的な実施形態に従った、酸化物接合された3D - ICウエハ STACK 内に1つ以上のデバイスダイを封入するための代替的な3つの方法のフローチャートである。

【図2A】図2A - 2Fは、特定の実施形態に従った3D - ICウエハ STACK の組み立てられていないコンポーネント及び部分的に組み立てられたコンポーネントの概略断面図である。

40

【図2B】図2A - 2Fは、特定の実施形態に従った3D - ICウエハ STACK の組み立てられていないコンポーネント及び部分的に組み立てられたコンポーネントの概略断面図である。

【図2C】図2A - 2Fは、特定の実施形態に従った3D - ICウエハ STACK の組み立てられていないコンポーネント及び部分的に組み立てられたコンポーネントの概略断面図である。

【図2D】図2A - 2Fは、特定の実施形態に従った3D - ICウエハ STACK の組み立てられていないコンポーネント及び部分的に組み立てられたコンポーネントの概略断面図

50

である。

【図2E】図2A-2Fは、特定の実施形態に従った3D-ICウエハスタックの組み立てられていないコンポーネント及び部分的に組み立てられたコンポーネントの概略断面図である。

【図2F】図2A-2Fは、特定の実施形態に従った3D-ICウエハスタックの組み立てられていないコンポーネント及び部分的に組み立てられたコンポーネントの概略断面図である。

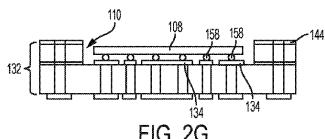

【図2G】図2G及び2Hは、特定の実施形態に従った3D-IC半導体ウエハアセンブリの概略断面図である。

【図2H】図2G及び2Hは、特定の実施形態に従った3D-IC半導体ウエハアセンブリの概略断面図である。 10

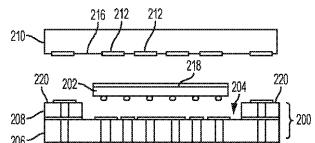

【図3A】図3A-3Cは、特定の実施形態に従った3D-ICウエハスタックの部分的に組み立てられたコンポーネントの概略断面図である。

【図3B】図3A-3Cは、特定の実施形態に従った3D-ICウエハスタックの部分的に組み立てられたコンポーネントの概略断面図である。 20

【図3C】図3A-3Cは、特定の実施形態に従った3D-ICウエハスタックの部分的に組み立てられたコンポーネントの概略断面図である。

【図3D】特定の実施形態に従った3D-ICウエハアセンブリの概略断面図である。

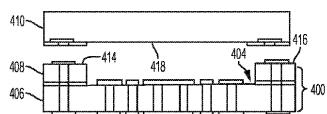

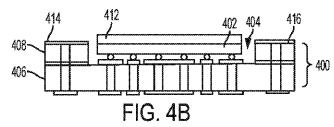

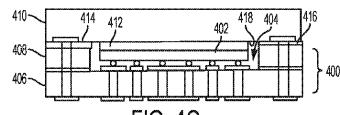

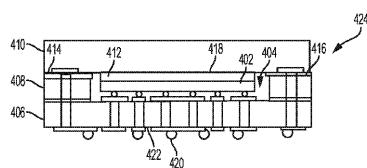

【図4A】図4A-4Cは、特定の実施形態に従った3D-ICウエハスタックの部分的に組み立てられたコンポーネントの概略断面図である。 20

【図4B】図4A-4Cは、特定の実施形態に従った3D-ICウエハスタックの部分的に組み立てられたコンポーネントの概略断面図である。

【図4C】図4A-4Cは、特定の実施形態に従った3D-ICウエハスタックの部分的に組み立てられたコンポーネントの概略断面図である。

【図4D】特定の実施形態に従った3D-ICウエハアセンブリの概略断面図である。

#### 【発明を実施するための形態】

##### 【0013】

以下の詳細な説明では、本開示の態様の完全なる理解を提供するために、数多くの具体的な説明が説明される。当業者によって理解されることには、これらは、それら具体的な説明のうちの一部なしでも独立して実施され得る。また、実施形態を不明瞭にしないよう、周知の方法、手順、コンポーネント、及び構造は詳細に説明されていないことがある。 30

##### 【0014】

以下の好適実施形態の説明は、本質的に単に例示的なものであり、開示、その適用、又は使用を限定することは全く意図していない。また、理解されるべきことには、ここで使用される語法及び用語は、単に説明の目的でのものであり、限定するものとして見なされるべきでない。理解されることには、複数の特定の特徴が、明瞭さのために、別々の実施形態の文脈で説明されるが、単一の実施形態において組み合わせて提供されてもよい。逆に、様々な特徴が、簡潔さのために、単一の実施形態の文脈で説明されるが、別々に提供されたり、又は任意の適切なサブコンビネーションで提供されたりしてもよい。

##### 【0015】

ここで使用される如何なる要素、アクト、又は命令も、明示的にそのように記載されない限り、重要又は必須であると解釈されるべきでない。ここで使用されるとき、冠詞“a”及び“a n”は、1つ又は複数のアイテムを含むことを意図しており、“1つ以上の”と交換可能に使用されることがある。また、“に基づく”なる言い回しは、別のことが明記されない限り、“少なくとも部分的に基づく”を意味することを意図している。更に理解されることには、用語“有する”、“持つ”、“含む”及び“含有する”、並びにこれらの用語の如何なる形式も、オープンエンドの連結動詞である。結果として、1つ以上の工程又は要素を“有する”、“持つ”、“含む”及び“含有する”方法又はデバイスは、それら1つ以上の工程又は要素を所有するが、それらの1つ以上の工程又は要素のみを所有することに限定されない。また、特定の手法で構成されると説明されるデバイス又はウ 40

ウエハの構造は、少なくともその手法で構成されるが、示されない手法で構成されてもよい。

【0016】

以下の説明の目的で、用語“上側”、“下側”、“頂部”、“底部”、“上下方向”、“横方向”、“前面”、“背面”、及びこれらの派生語は、図面中の向きとした開示構造及び方法に関するものである。用語“上に”、“隣接して”、“上に位置付けられ”又は“の上に位置付けられ”、は、例えば第1のデバイス構造又は層などの第1の要素が、例えば第2のデバイス構造又は層などの第2の要素の上に又は近くに存在することを意味し、例えばインタフェース構造又は層などの介在要素が存在してもよいのであって、例えば、第1のウエハ層と第2のウエハ層とが、これら2つの層の境界に如何なる中間の導電層、絶縁層又は半導体層もなく直に接触している、といったことを必ずしも意味するわけではない。

10

【0017】

例えばポールグリッドアレイ (BGA) などの半導体素子は、航空宇宙センサーキテクチャ及び/又は他の半導体アーキテクチャの一部として使用されることができる。フォトニクスドメインでは、インジウム燐 (InP) 及びガリウム砒素 (GaAs) に基づくIII-V族材料が、これらの材料の直接バンドギャップに関連する優れたフォトニック特性により、重要な実現要素となっている。大抵の場合、半導体素子の各々が、半導体アレイを作成する主回路基板（例えば、マザーボード、アレイなど）にはんだ付けされる。ここで使用されるとき、用語“ダイ”は、以下に限られないがCMOS、オプトエレクトロニクス、赤外線検出器、MEMS、及びこれらに類するものを含め、ICで製造されている半導体材料の小さいピース（小片）を指し、用語“ウエハ”は、基板層を有し得る且つ/或いはICの製造に使用され得る半導体材料の薄いスライスを指すために使用される。ウエハは、典型的に円形に構成されるが、以下に限られないが長方形のパネルサイズ又はダイシングされた形状及びサイズを含め、酸化物接合処理に適合する任意のサイズ又は形状とし得る。用語“バンプ”及び“バンピング”は、ウエハ又はダイのボンドパッド（例えば、TSVコネクタパッドの位置にある）にはんだボールを取り付けて、ウエハスタック又はアセンブリ内の他のデバイス及び/又はウエハへの接続点を形成する半導体パッケージング技術を指す。ボンドパッドは、例えばDBHボンディング、無電解ニッケル浸漬金アンダーバンプメタライゼーションなどを通じて、支持ウエハに酸化物接合され得る。単に明瞭さの目的で、用語“半導体ウエハアセンブリ”は、現在開示している方法の実施形態のうちのいずれかに従った製造の結果として得られる複数の半導体ウエハとその中に封入された少なくとも1つのダイとの複合構造を指し、用語“ウエハスタック”は、半導体ウエハアセンブリの製造の任意の中間段階におけるウエハとダイの構造を指すために使用される。

20

【0018】

大抵のD2W適用では、2枚の半導体ウエハ上に電子コンポーネントが構築される。一方のウエハがダイシングされ、そして、この個片化されたダイが、第2のウエハのダイ位置上にアライメントされ、（例えば、接合（ボンディング）、ワイヤ相互接続などによって）接続される。W2W法においてと同様に、D2W適用では、接合する前又は後に、薄化及びTSV相互接続形成が実行される。

30

【0019】

図1を参照するに、各々がICを含み得る3枚の半導体ウエハの中にデバイスダイが封入される半導体ウエハアセンブリを形成する方法10（複数の代替的な実施形態を有する）がフローチャートにて示されている。方法10のこれらの実施形態の個々の工程については、図2A-2H、3A-3D、及び4A-4Dを参照して詳細に後述する。これらの実施形態は、ウエハアセンブリを製造するのに使用される半導体ウエハのうちの1つ以上に従来のように回路（例えば、トレース、コンポーネント、電気ピア）を作成するための、図示しない工程を含む。方法10のこれらの実施形態は、共通の初期工程12（2枚のシリコンウエハの両面間に対応するTSVを形成する）、工程14（ウエハ上にダイレク

40

50

トボンドハイブリダイゼーション (direct bond hybridization ; DBH) 酸化物接合用の TSV バンプパッドを形成し、対向面に酸化物層を堆積させる) 、工程 16 (ウエハを平坦化して接合する) 、及び工程 18 (TSV を露出させ、TSV パッドを形成して DBH 酸化物接合し、ウエハスタックの頂面に酸化物層と、それに次ぐ、頂面をエッティングする準備としてのハード保護マスクとを堆積させて平坦化する) で開始する。その後、方法 10 のこれらの実施形態は僅かに分岐して、完成ウエハアセンブリの封入ダイとウエハとの間の異なる接続オプションを提供する。各実施形態が、ウエハスタック内に 1 つ以上のキャビティをエッティングし、ハード保護マスクを除去し、そして、キャビティ封止蓋として使用される異なる形態の第 3 のウエハを準備する工程 (例えば、それぞれ工程 20 、 30 、 40 ) を含む。

10

#### 【0020】

方法 10 の 3 つの例示的な実施形態の異なる最終工程を通じて、異なる構成の完成半導体ウエハアセンブリが達成される。第 1 の実施形態では、底部ウエハに接合された 1 つ以上のダイバンプが、エッティングされたキャビティ内で気密シールされるように、工程 22 (ダイをマウントして接合、蓋ウエハ研磨) 、工程 24 (蓋ウエハ接合) 、及びオプション工程 26 (導管エッティング、熱充填、ダイシング) がウエハアセンブリを形成する。第 2 の実施形態では、蓋ウエハが封入するとともに、マウントされたダイ及び中間ウエハにバンプ接合されるように、工程 32 (ダイ及びキャビティの準備) 、工程 34 (ダイ取り付け及び蓋ウエハバンピング) 、及び工程 36 (蓋ウエハ取り付け、底部ウエハ TSV バンピング、ダイシング) がウエハアセンブリを形成する。方法 10 の第 3 の実施形態は、工程 42 (ダイのマウント及び接合、熱インタフェース形成) 、工程 44 (洗浄、蓋ウエハを酸化物接合) 及び工程 46 (底部ウエハ TSV バンピング、ダイシング) が、封入されたダイに接合された熱インタフェースと蓋ウエハとの間に酸化物ボンドをもたらすことを除いて、第 1 の実施形態と同様である。オプションの導管 (又は通気口) のエッティング及び熱材料によるアンダーフィルは、工程 26 にのみ示されているが、理解されることは、このような処理はこれらの実施形態のいずれでも使用され得る。

20

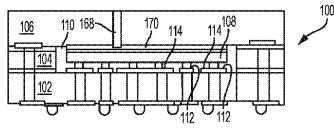

#### 【0021】

図 2A - 2H 、 3A - 3D 、及び 4A - 4D は、方法 10 の実施形態の連続した個々のプロセス工程に対応するウエハ構造を概略的に示している。図 2A に示す半導体ウエハアセンブリ 100 の第 1 の実施形態の概略断面図を参照するに、ここに開示されるのは、ウエハ (又は基板) 接合による 3D - IC 集積をデバイスパッケージにて実現する技術であり、この技術は、1 つ以上の半導体ウエハ (例えば、底部ウエハ 102 、中間ウエハ 104 、及び蓋ウエハ 106 ) の酸化物接合を用いて、例えばウエハ 102 、 104 、 106 のうちの 1 つ以上の中にエッティングされたキャビティ 110 などのシールされたボリューム内でダイ 108 を、そう望まれる場合に気密的に、包囲する。この技術は、従来の処理によってでは提供されることができないウエハスケール 3D - IC 集積に適した形式でのデバイスダイタイプの組み込みを可能にする。ダイ 108 は、典型的に、例えばシリコンなどの半導体材料で形成されるが、他の材料も使用され得ることが予測可能である。底部ウエハ 102 及びオプションで蓋ウエハ 106 へのダイ 108 の機械的且つ電気的な集積を、DBH 接合を通じて、又はバンプ 112 及びパッド 114 でのバンプ接合を使用することによって実行することができる。他の実施形態において、ダイ 108 は、ワイヤ若しくは同様の相互接続によって、及び / 又は酸化物ボンド若しくは超音波ボンドによって、機械的且つ電気的に接続されてもよい。

30

#### 【0022】

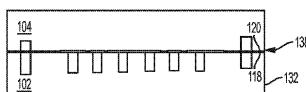

図 2B は、ウエハアセンブリ 100 のフロントエンド処理で使用される未組み立ての底部ウエハ 102 及び中間ウエハ 104 の概略断面図である (これは、方法 10 の工程 12 に対応する) 。中間ウエハ 104 は、シリコン又は他のエッティング可能な材料からなることができ、底部ウエハ 102 及び頂部ウエハ 106 は、シリコン、又は、例えば炭化ケイ素、溶融シリカ、ガラス、サファイア、ガリウム砒素、インジウム燐、シリコン・オン・インシュレータ (SOI) 、金属、セラミック、及び他の誘電材料、導電材料若しくは半

40

50

導体材料などの、異なる材料からなることができる。この実施形態において、ウエハ102、104は、例えばシリコン半導体ウエハなどの半導体ウエハを有し得るが、他の種類の材料が使用されてもよい。ウエハ102、104は概して平面状である。底部ウエハ102は、底面116とキャビティ側の頂面118とを含んでおり、中間ウエハ104は、キャビティ側の底面120と頂面122とを含んでいる。底部ウエハ102は、キャビティ側の表面118上又はそのすぐ下に配置されたIC124を含み得る。中間ウエハ104も、キャビティ側の底面120及び頂面122のいずれか又は双方上又はそのすぐ下に配置されたIC126、128を有し得る。

#### 【0023】

複数のTSV130a、130bなど(全般的に130)が、ウエハ102、104の各々内に形成され、導電性の材料(銅、アルミニウム、タンクステン、ドープトポリシリコンなど)で充填され得る。TSV130は、例えば、所与のウエハ内の電気コンポーネントに、及び/又は(図2Aの)デバイスダイ108との間で、ウエハ102、104が電気信号を電気部品に伝送することを可能にする複数の電気相互接続を提供するように選択的に配置される。TSV130は、多様な半導体処理方法を用いて形成されることができる。例えば、一部の実施形態において、ウエハ102、104から材料を除去してピア130が生成するように、一連のフォトリソグラフィプロセス及び化学的プロセスが実行される。一部の実施形態では、ウエハ102、104に追加の材料を付加してTSV130を生成するように、アディティブプロセスが使用される。

#### 【0024】

図2C(これは、方法10の工程14に対応する)を参照するに、中間ウエハ STACK132(図2Dに示す)を作り出すための接合用のウエハを準備するために、底部ウエハ102及び中間ウエハ104の当接し合う表面118、120が処理される。この実施形態において、表面118、120は、後のデバイスダイ102(図1Aに示す)との相互接続のための1つ以上のバンプパッド134を付加するように処理される。次いで、ウエハ102、104の対向し合う面118、120上に酸化物層136、138が形成され得る。シリコンが酸素(又は酸素を含む流体、例えば空気)に曝されるとき、シリコンウエハ表面上に二酸化シリコンが形成される。シリコンが周囲条件下で空気に曝されるとき、薄い酸化物の層(例えば、10)を表面118、120上に形成することができる。シリコン表面上に二酸化シリコンを作成することには、様々な半導体処理技術が使用されている。これらの技術は典型的に、シリコン上に制御可能に二酸化シリコンの層を成長させるために、より高い温度と様々な環境(例えば流体)を用いてシリコンウエハを処理することを伴う。例えば、O<sub>2</sub>又はH<sub>2</sub>O環境では、600°Cを超える温度がよく使用される。しかしながら、ウエハの性能を低下させることを避けるために、活性シリコンウエハに対しては、しばしば、350°Cが限度である。次いで、バンプパッド134と同一平面にある滑らかな酸化物層表面136、138を作り出すために、各表面118、120上に形成された酸化物層が研磨され得る。滑らかな表面を作り出すことには様々な技術を使用することができる。例えば、研磨、エッティング、又はこれら2つの組み合わせによって、ウエハ表面118、120の化学的又は機械的な平坦化を遂行して、滑らかな表面を生成することができる。一部の実施形態において、ウエハ102、104の表面118、120は、ウエハ表面118、120と接触するとともにウエハ表面に対して移動される研磨パッドと併せて、ウエハを研磨剤及び/又は腐食性化学物質にさらすことによって平滑化され得る。一部の実施形態において、表面118、120は、10オングストローム未満の表面ラフネスに平滑化される。

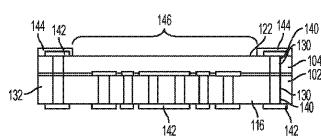

#### 【0025】

次いで、ウエハ102、104が共に接合されて、図2D(これは、方法10の工程16に対応する)に示すようなウエハ STACK132を形成し得る。図2Dは、ウエハ STACK132の断面図を示している。ウエハ102、104は、それらの平坦化された酸化物表面118、120を互いに接触させることによってDBHにより共に酸化物接合され且つアニールされて、ウエハ102、104間に共有ボンドライン139が生み出される

10

20

30

40

50

。共有ボンドライン 139 は、従来のウエハアセンブリにおいてウエハをつなぎ合わせるために現在使用されている有機接着剤結合よりも、概して薄く、低い熱抵抗を持つ。共有ボンドライン 139 は比較的薄い（例えば、はんだバンプ及びアンダーフィルよりも薄い）ので、遙かに高い間隔密度で相互接続をウエハ 102、104 上に配置することができる。

【0026】

図 2 E（これは、方法 10 の工程 18 に対応する）を参照するに、次いで、露出しているウエハスタック 132 の底部ウエハ 102 底面 116 及び頂部ウエハ 104 の頂面 122 が、TSV 130 の端部 140 を露出させるように薄化及び平坦化され、そして、露出された TSV 端 140 の位置で表面 116、122 上に相互接続パッド 142 が酸化物接合され得る。次いで、酸化物層（図示せず）が選択的に付加されて平坦化され、そして、後続のエッチングプロセスから保護されるべきウエハ表面 122 の領域を覆ってハードマスク 144 が形成される。

【0027】

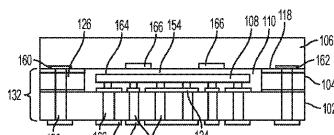

図 2 F（これは、方法 10 の工程 20 に対応する）を参照するに、次いで、ハード保護マスク 144 によって保護されていない中間ウエハ 104 の頂面 122 の領域 146（各々、図 2 E に示されている）のエッチングを通じて、ウエハスタック 132 内にキャビティ 110 が形成され得る。ハード保護マスク 144（例えば、TiW 合金からなる）の使用は、遙かに広い処理温度範囲を許容し、広範な技術を用いてキャビティ 110 内にデバイスダイ（図示せず）をマウントすることを可能にする。キャビティ 110 は、底部ウエハ 102 と中間ウエハ 104 との間に以前（工程 16）に形成された酸化物ボンドライン 139 の位置の埋め込み酸化物（BOX）層 148 まで下方に、中間ウエハ 104 内にエッチングされ得る。BOX 層 148 は、このキャビティエッチングプロセスのエッチストップとしての役割を果たし、ウエハ 102、104 の表面上に以前（工程 14）に形成された、デバイスダイ 108（図 2 G に示す）への接続のためのバンプパッド 134 が露出される。キャビティ 110 の外周は、キャビティ 110 の実質的に垂直な側壁 150、152 との、実質的に平面状の BOX 層 148 の交線によって画成され得る（そして、付加されることになる蓋ウエハ 106 の底面 154 によって更に画成されることになる）。キャビティ 110 は、BOX 層 148 に直交するほぼ垂直な側壁を生成するシリコンエッチング法、好ましくはディープ反応性イオンエッチング（DRIE）、を使用して、封入されるダイの個数及びサイズと熱マネジメント設計要求に基づく寸法でエッチングされ得る。それに代えて、キャビティ 110 は、反応性イオンエッチング（RIE）又は異方性化学エッチング（これは、傾いた又は傾斜した側壁をもたらし得る）を使用してエッチングされてもよい。キャビティ 110 の機能は、デバイスダイ 108 の環境保護、高密度の回路相互接続、物理的パッケージング及び熱インタフェースを提供すること、並びに、デバイス機能を覆い隠して、リバースエンジニアリングからのデバイスセキュリティを提供することを含む。同時に、蓋ウエハ 106 の底面 154（これは、下向きの IC156 を含み得る）が、酸化物層の形成及び平坦化を介した酸化物接合のために準備され得る。

【0028】

図 2 G（これは、方法 10 の工程 22 に対応する）を参照するに、次いで、キャビティ 110 内に露出したバンプパッド 134 に、1 つ以上の同一種又は異種のデバイスダイ 108 が、バンプ 158 を介して機械的且つ電気的に接続され得る。このダイマウントプロセスは、超音波接合、はんだバンピング（例えば、バンプボンド 134 を介する）、又は酸化物接合、ワイヤボンド、エポキシを含む多様な技術を有することができ、また、ダイが接合されるウエハ 102、104 とダイとの間の表面のうちのいずれか上の多様な構成をした電気的、機械的、又は熱的なインタフェースを含み得る。表 1 は、デバイスダイ 108 をマウントするのに使用され得る過渡液相はんだバンプテクノロジーの例を提示している。

10

20

30

30

40

## 【表1】

| 材料系          | 処理時間及び温度               | 再溶融温度            |

|--------------|------------------------|------------------|

| <u>Cu-In</u> | <u>4 min at 180C</u>   | <u>&gt; 307C</u> |

| <u>Cu-Sn</u> | <u>4 min at 280C</u>   | <u>&gt; 415C</u> |

| <u>Ag-Sn</u> | <u>60 min at 250C</u>  | <u>&gt; 600C</u> |

| <u>Ag-In</u> | <u>120 min at 175C</u> | <u>&gt; 880C</u> |

| <u>Au-Sn</u> | <u>15 min at 260C</u>  | <u>&gt; 278C</u> |

| <u>Au-In</u> | <u>0.5 min at 200C</u> | <u>&gt; 495C</u> |

| <u>Ni-Sn</u> | <u>6 min at 300C</u>   | <u>&gt; 400C</u> |

10

表1

## 【0029】

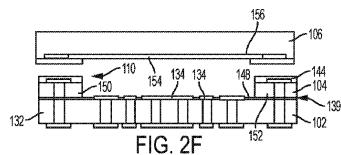

図2H(これは、方法10の工程24に対応する)を参照するに、キャビティ110内のバンプパッド134にダイ108がマウントされた後、ハードマスク層144(図2Gに示されている)が除去されて、ウェハ STACK 132に蓋ウエハ106を取り付けることが可能になる。図示した実施形態では、それにより、キャビティ110が、中間ウェハ104の頂面118の残存部分と蓋ウエハ106の底面154との間のウェハ界面160、162での極めて堅牢な酸化物ボンドで囲まれている。オプションで、ダイ108上に熱材料層164を形成して、ダイ108と蓋ウエハ106との間に熱インターフェースを提供してもよい。加えて、あるいは代わりに、3D-ICウェハアセンブリ100を熱マネジメントすることを支援するために、ダイ108と、他のウェハ102、104のうちの1つ以上及び/又は他のダイとの間に、同様の熱インターフェース(図示せず)を形成してもよい。蓋ウエハ106は、完全な半導体ウェハアセンブリ100を形成するために界面160、162で酸化物接合され得る。一部の実施形態において、蓋ウエハ106は、完全に独立した半導体製造プロセスから得られるウェハ・オン・ウェハ STACK の外部層を有し得る。TSV130の露出端140、及び底部ウェハ102の底面116上に形成された相互接続パッド142は、ダイ108及びウェハ102、104、106から外部デバイス及びウェハ(図示せず)の間の(1つ以上の)接続のための電気経路を提供し得る。他の実施形態において、中間ウェハ104の頂面118の残存部分及び蓋ウエハ106の底面154は、はんだ又は熱圧接を用いて界面162、164で接合されてもよい。述べたように、この接合プロセスは、デバイスダイ108を封入する気密シールを形成するように、界面160、162でキャビティ110を封止し得る。

20

30

30

## 【0030】

頂面118及び底面154は、外部圧力なしで界面160、162にて接合されることができる。しかしながら、例えば熱圧接などの一部の実施形態では、表面118、154を互いに接触させるために追加の圧力が印加される。ダイ108は、金属機構(例えば、バンプパッド、ビアなど)又はキャビティ110内で露出した回路を介して、3Dウェハアセンブリ100内のウェハ102、104、106のいずれか又は全てに相互接続され得ることができ、これらウェハの各々が、表面上で平面的であるかウェハ中に上下方向に配置されるかのいずれかとすることができます1つ以上の導電IC124、126(能動IC又は受動ICを含む)を含み得る。

40

## 【0031】

再び図2A(その一部の機構が処理工程26に対応する)を参照するに、例えば、封入されたダイ108と接触するように熱材料又は構造材料が侵入することを可能にするために、ウェハ102、104、106のいずれか又は全てを貫いて穴又は導管168がエッチングされ得る。それに代えて、この導管168は、内蔵ICの特定の特性を強化するために、キャビティ110を望ましい気体又は液体でバージする又は埋め戻すために使用されてもよい。熱伝導性の材料170(例えば、非導電性の冷却流体、又は熱的、電気的、

50

化学的、保護的な機能、又は機械的な目的のために使用される数多くの材料)がキャビティ110の一部又は全てを充填し、次いで、導管168が塞がれ(例えば、はんだなどで)又は熱伝導材料で充填され得る。それに代えて、導管168は、キャビティ110への及びキャビティ110からの熱ベントとして機能してもよい。3D-I Cウエハアセンブリ100のこの完成した第1の実施形態は、その後、従来からの手段によってダイシングされ得る。

### 【0032】

当業者が理解することには、開示される技術が提供する利点は、例えば上述したものなどの3D-I Cウエハアセンブリ100に接合され得るウエハスタックを形成するW2Wプロセスとは独立に、D2W歩留まり損失を管理できることを含む。ここに開示されるプロセスから得られるデバイスの歩留まりは、デバイス内に“良品判明ダイ(know good die)”のみを組み込み、それにより、スタッキング歩留まり損失を回避することによって改善され、全体的なコストが削減される。さらに、薄いダイを接合できることが、薄型のパッケージ及び短い電気経路長を維持しながら、TSVを使用して上下に接続された複数のデバイス層(異なるテクノロジーからのものを含めて)の積み重ねを可能にする。異なるデバイスダイは、違う厚さ(例えば、100μm-700μm)を持つことが多い。複数のダイを封入するウエハアセンブリの実施形態において、似ていないダイ厚を受け入れるために、中間ウエハ104を、相互接続される最も厚いダイ108の厚さよりも大きい厚さ(及びそれ故に、キャビティ深さ)を持つように製造することができ、III-V族デバイスの厚さを近く一致させる必要性が排除されるとともに、熱的分離も提供される。さらに、コストを抑えるために、D2Wアセンブリ100に接続するウエハにブラインド前面(フロントサイド)ビアプロセスを使用することができ、これは、ダイをマウントすること及び外部ウエハの接続のためのはんだバンプ処理でバックオフ位置を許容する。個々のダイを一緒にアンダーフィル付着させるのに使用される従来の有機ボンドは、個々のチップ/ダイがアレイから切り出された後に実行されるのに対し、ここに記載される技術は、その接合がウエハレベルで実行されることを可能にする。一部の実施形態において、共有ボンドラインは、有機ボンドラインよりも10倍薄くなり得る。

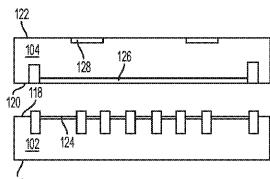

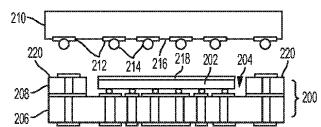

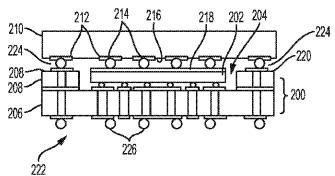

### 【0033】

図3A-3Dは、第2の方法実施形態(方法10の工程30-36に対応)に従った処理を受けているウエハスタック200の分解図及び統合図の概略断面図であり、底部ウエハ206、中間ウエハ208、及び蓋ウエハ210によって形成されるキャビティ204内にデバイスダイ202を封入する酸化物接合ウエハアセンブリの代替的な一実施形態を製造するものである。この代替的なウエハアセンブリを製造する際に使用されるフロントエンド半導体プロセスは、第1の方法実施形態の図2A-2Dに関連して説明したものと同じとし得る。図3A-3Dに示されるウエハ処理結果は、いくらかの類似点(例えば、全般的な半導体処理技術、ウエハの向き及び組成など)を有するが、幾つかの側面で図2E-2Hに示したものとは異なる。図3Aは、底部ウエハ206及び中間ウエハ208からなるウエハスタック200を示しており、その中に1つ以上のキャビティ204がエッチングされている。図3B-3Dに示すように、この第2の実施形態では、異なるバックエンドプロセスを使用して、蓋ウエハ210の底面216にバンプパッド212及びバンプ214(ダイ202に接続される場合、熱バンプとし得る)を形成し得る。蓋ウエハ210は、マウントされたダイ202の背面218にバンプ接合されるとともに、接続箇所220で中間ウエハ208にバンプ接合される。蓋ウエハ210を中間ウエハ208にバンプ接合(第1の方法実施形態の酸化物接合とは異なる)することは、気密封止されたキャビティ内にデバイスダイ202を封入するのではなく、例えば図3Dに示すものなどの、中間ウエハ208と蓋ウエハ210とがエアギャップ224を画成する3D-I C半導体ウエハアセンブリ222をもたらす。蓋ウエハ210は、例えばウエハアセンブリ222内でウエハ206、208、210、及びダイ202の間で電気信号を渡すことを可能にするはんだボールボンド214を通じて、中間ウエハ208に電気的及び機械的に結合され得る。蓋ウエハ210が接合されると、外部のデバイスやウエハなどに接続するため

10

20

30

40

50

に、完成した電気接続 226 がウエハアセンブリ 222 に付加され得るとともに、ウエハアセンブリが更に処理及び／又はダイシングされ得る。

【0034】

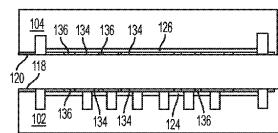

図 4 A - 4 D は、第 3 の方法実施形態（方法 10 の工程 40 - 46 に対応）に従った処理を受けているウエハスタック 400 の分解図及び統合図の概略断面図であり、底部ウエハ 406、中間ウエハ 408、及び蓋ウエハ 410 によって画成される包囲されたキャビティ 404 内にデバイスダイ 402 を封入する酸化物接合ウエハアセンブリの代替的な実施形態を製造するものである。この代替的なウエハアセンブリを製造する際に使用されるフロントエンド半導体プロセスは、第 1 の方法実施形態の図 2 A - 2 D に関連して説明したものと同じとし得る。図 4 A - 4 D に示されるウエハ処理結果は、いくらかの類似点（例えば、全般的な半導体処理技術、ウエハの向き及び組成など）を有するが、幾つかの側面で図 2 E - 2 H に示したものとは異なる。第 1 の実施形態からの 1 つのバリエーションが図 4 B に示されており、キャビティ 404 内にダイ 402 を取り付ける前又は後のいずれかに、デバイスダイ 402 上に熱インタフェース層 412（又は上述したような他の機能層）が形成され得る。次いで、熱インタフェース層 412 が、平坦化され、洗浄され、そして、対向する蓋ウエハ 410 の底面 418 と同時とし得るように、上述したのと同様にして酸化物接合され得る。図 4 D に示すように、底部ウエハ 406 の表面 422 に、他のウエハ（図示せず）への外部接続のための電気バンプ 420 が付加され得る。蓋ウエハ 410 は、中間ウエハ 408 に頂面領域 414、416 で電気的且つ機械的に結合され得るとともに、熱インタフェース層 412 に結合され得る。中間ウエハ 408 と蓋ウエハ 410 との間の接合は、デバイスダイ 402 を封入する気密封止キャビティ 404 を有する複合 3D - IC ウエハアセンブリ 424 をもたらす。表面 414、416、418 は、これらのウエハを共に接合するのに先立って、平坦化された酸化物表面であるように（例えば図 2 A - 2 H に関して説明したのと同様に）準備され得る。

【0035】

これら例示的な実施形態には、対応する図を参照して上述したように、本開示の範囲から逸脱することなく様々な変更が為され得るので、以上の説明に含まれ、添付の図面に示された全ての事項が、限定的なものではなく例示的なものとして解釈されることが意図される。従って、本開示の広さ及び範囲は、上述の例示的な実施形態のいずれによっても限定されるべきでなく、ここに添付の以下の請求項及びそれらに均等なもののみに従って定められるべきである。

10

20

30

【図1】

【 図 2 A 】

FIG. 2A

【図2B】

FIG. 2B

【 2 C 】

FIG. 2C

【 2 D 】

FIG. 2D

【图2E】

FIG. 2E

〔 図 2 H 〕

FIG. 2H

【図2F】

FIG. 2F

## 【図2G】

134

【 図 3 B 】

FIG. 3B

【図 3 C】

FIG. 3C

【図 3 D】

FIG. 3D

【図 4 A】

FIG. 4A

【図 4 B】

FIG. 4B

【図 4 C】

FIG. 4C

【図 4 D】

FIG. 4D

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/607 (2006.01)

(72)発明者 ドラブ, ジョン ジェイ .

アメリカ合衆国 マサチューセッツ州 02451-1449 ウォルサム, ウィンター・ストリ

ート 870 レイセオン カンパニー内

(72)発明者 ミルン, ジェイソン ジー .

アメリカ合衆国 マサチューセッツ州 02451-1449 ウォルサム, ウィンター・ストリ

ート 870 レイセオン カンパニー内

審査官 豊島 洋介

(56)参考文献 国際公開第2015/136998 (WO, A1)

特開2006-270098 (JP, A)

特開2004-071597 (JP, A)

特開平11-145381 (JP, A)

特開2007-123705 (JP, A)

特開2014-072469 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/447 - 21/449

21/54

21/60 - 21/607

23/00 - 23/04

23/06 - 23/10

23/16 - 23/26

23/29

23/34 - 23/36

23/373 - 23/427

23/44

23/467 - 23/473

25/00 - 25/07

25/10 - 25/11

25/16 - 25/18