(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-54873

(P2011-54873A)

(43) 公開日 平成23年3月17日(2011.3.17)

| (51) Int.Cl.                  | F 1            | テーマコード (参考) |

|-------------------------------|----------------|-------------|

| <b>H01L 27/105 (2006.01)</b>  | H01L 27/10 447 | 4M119       |

| <b>H01L 21/8246 (2006.01)</b> | H01L 43/12     | 5FO83       |

| <b>H01L 43/12 (2006.01)</b>   | H01L 27/10 451 | 5FO92       |

| <b>H01L 27/10 (2006.01)</b>   | H01L 43/08 Z   |             |

| <b>H01L 43/08 (2006.01)</b>   | H01L 27/10 448 |             |

審査請求 未請求 請求項の数 11 O L (全 26 頁) 最終頁に続く

|           |                              |          |                                        |

|-----------|------------------------------|----------|----------------------------------------|

| (21) 出願番号 | 特願2009-204528 (P2009-204528) | (71) 出願人 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (22) 出願日  | 平成21年9月4日 (2009.9.4)         | (74) 代理人 | 100094363<br>弁理士 山本 孝久                 |

|           |                              | (74) 代理人 | 100118290<br>弁理士 吉井 正明                 |

|           |                              | (74) 代理人 | 100120640<br>弁理士 森 幸一                  |

|           |                              | (72) 発明者 | 山岸 肇<br>東京都港区港南1丁目7番1号 ソニー株式会社内        |

|           |                              | (72) 発明者 | 庄子 光治<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

|           |                              |          | 最終頁に続く                                 |

(54) 【発明の名称】不揮発性メモリ素子の製造方法

## (57) 【要約】

【課題】短絡や電流リークを生じさせること無く、しかも、MTJ構造にダメージを生じさせること無く、不揮発性メモリ素子におけるMTJ構造のパターニングを行い得る不揮発性メモリ素子の製造方法を提供する。

【解決手段】第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53が、順次、積層された積層構造体50を有し、磁化反転状態に依存して電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子の製造方法は、第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53を順次形成し、次いで、第2磁性材料層53上にマスク層63を形成した後、マスク層63で覆われていない第2磁性材料層53の部分53'を酸化し、次いで、酸化された第2磁性材料層53の部分53'を還元する工程を備えている。

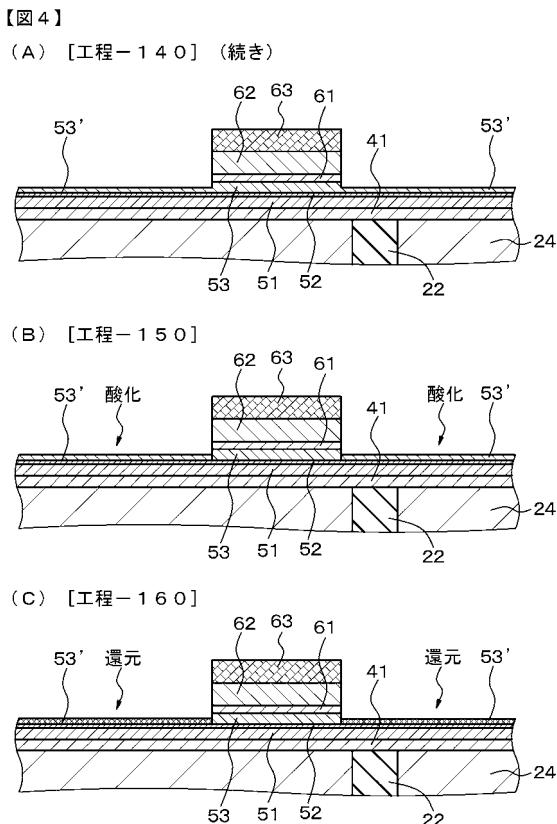

【選択図】 図4

【図4】

(A) [工程-140] (続き)

(B) [工程-150]

(C) [工程-160]

**【特許請求の範囲】****【請求項 1】**

第1磁性材料層、トンネル絶縁膜及び第2磁性材料層が、順次、積層されて成る積層構造体を有し、磁化反転状態に依存して電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子の製造方法であって、

第1磁性材料層、トンネル絶縁膜及び第2磁性材料層を順次形成し、次いで、第2磁性材料層上にマスク層を形成した後、マスク層で覆われていない第2磁性材料層の部分を酸化し、次いで、酸化された第2磁性材料層の部分を還元する工程を備えている不揮発性メモリ素子の製造方法。

**【請求項 2】**

第2磁性材料層上にマスク層を形成した後、マスク層で覆われていない第2磁性材料層の部分を酸化する前に、マスク層で覆われていない第2磁性材料層の部分を、厚さ方向に一部分、エッチングする請求項1に記載の不揮発性メモリ素子の製造方法。

**【請求項 3】**

第1磁性材料層は磁化参照層から構成され、第2磁性材料層は記録層から構成されている請求項1に記載の不揮発性メモリ素子の製造方法。

**【請求項 4】**

第1磁性材料層は記録層から構成され、第2磁性材料層は磁化参照層から構成されている請求項1に記載の不揮発性メモリ素子の製造方法。

**【請求項 5】**

マスク層で覆われていない第2磁性材料層の部分を、プラズマ酸化法、熱酸化法、又は、ラジカル酸化法に基づき酸化する請求項1に記載の不揮発性メモリ素子の製造方法。

**【請求項 6】**

酸化された第2磁性材料層の部分を、水素プラズマ法に基づき還元する請求項1に記載の不揮発性メモリ素子の製造方法。

**【請求項 7】**

抵抗変化層の電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子の製造方法であって、

抵抗変化層上にマスク層を形成した後、マスク層で覆われていない抵抗変化層の部分を酸化し、次いで、酸化された抵抗変化層の部分を還元する工程を備えている不揮発性メモリ素子の製造方法。

**【請求項 8】**

抵抗変化層は、金属を含むイオン導電体から成る請求項7に記載の不揮発性メモリ素子の製造方法。

**【請求項 9】**

抵抗変化層はカルコゲナイト系材料から成る請求項7に記載の不揮発性メモリ素子の製造方法。

**【請求項 10】**

抵抗変化層は電界誘起巨大抵抗変化効果を有する材料から成る請求項7に記載の不揮発性メモリ素子の製造方法。

**【請求項 11】**

抵抗変化層はペロブスカイト系材料から成る請求項10に記載の不揮発性メモリ素子の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、不揮発性メモリ素子の製造方法に関する。

**【背景技術】****【0002】**

情報通信機器、特に携帯端末等の個人用小型機器の飛躍的な普及に伴い、これらを構成

10

20

30

40

50

するメモリ素子やロジック素子の各種半導体装置には、高集積化、高速化、低電力化等、一層の高性能化が要求されている。特に不揮発性メモリは、ユビキタス時代に必要不可欠であると考えられている。電源の消耗やトラブル、サーバーとネットワークとが何らかの障害により切断された場合でも、不揮発性メモリによって重要な情報を保存、保護することができます。また、最近の携帯機器は不要の回路ロックをスタンバイ状態とし、出来る限り消費電力を抑えるように設計されているが、高速のワークメモリと大容量ストレージメモリを兼ねることができる不揮発性メモリが実現できれば、消費電力とメモリの無駄を無くすことができる。また、電源を投入すると瞬時に起動できる「インスタント・オン」機能も、高速、且つ、大容量の不揮発性メモリが実現できれば可能となる。

## 【0003】

10

不揮発性メモリとして、半導体材料を用いたフラッシュメモリや、強誘電体材料を用いた強誘電体型不揮発性半導体メモリ（F E R A M , Ferroelectric Random Access Memory）等を挙げることができる。しかしながら、フラッシュメモリは、書き込み速度がマイクロ秒のオーダーであり、書き込み速度が遅いという欠点がある。一方、F E R A Mにおいては、書き換え可能回数が $10^{12} \sim 10^{14}$ であり、S R A MやD R A MをF E R A Mに置き換えるにはF E R A Mの書き換え可能回数が十分とは云えず、また、強誘電体層の微細加工が難しいという問題が指摘されている。

## 【0004】

20

これらの欠点を有さない不揮発性メモリ素子として、M R A M (Magnetic Random Access Memory)と呼ばれる不揮発性メモリ素子が注目されている。このM R A Mの中でも、T M R (Tunnel Magnetoresistance)効果を用いたM R A Mは、近年のT M R材料の特性向上により注目を浴びている。T M RタイプのM R A Mは、構造が単純で、スケーリングも容易であり、また、磁気モーメントの回転により記録を行うために、書き換え可能回数が大である。更には、アクセス時間についても非常に高速であることが予想され、既に $100\text{MHz}$ で動作可能であると云われている。

## 【0005】

30

ところで、M R A Mにおいて、記録した情報を安定に保持するためには、情報を記録する記録層が一定の保磁力を有していることが必要である。一方、記録された情報を書き換えるためには、ビット線に或る程度の電流を流さなければならない。ところが、M R A Mの微細化に従い、ビット線も細くなるため、充分な電流を流すことが困難となりつつある。そこで、より少ない電流で磁化反転が可能な構成として、スピン注入による磁化反転を応用したスピン注入型磁気抵抗効果素子が注目されている（例えば、特開2003-017782参照）。ここで、スピン注入による磁化反転とは、磁性体の中を通過してスピン偏極させた電子が、他の磁性体に注入されることにより、他の磁性体において磁化反転が生じる現象である。スピン注入型磁気抵抗効果素子にあっては、M R A Mと比較して、デバイス構造を単純化することができる。また、スピン注入による磁化反転を利用することにより、外部磁界によって磁化反転を行うM R A Mと比較して、素子の微細化が進んでも書き込み電流が増大しないという利点、セル面積を縮小できるといった利点を有する。

## 【0006】

40

ところで、スピン注入磁化反転書き込み方式を含む不揮発性メモリ素子にあっては、厚さ $1\text{nm}$ 程度のトンネル絶縁膜を2層の磁性材料層（磁化自由層とも呼ばれる記録層、及び、磁化固定層とも呼ばれる磁化参照層）が挟んだ構造（『M T J構造』と呼ばれる）を有する。そして、M T J構造を有する不揮発性メモリ素子の実用化のためには、ダメージや短絡、電流リークの発生無しに、磁性材料層をパターニングするプロセス技術が必要とされる。しかしながら、磁性材料層を構成する材料には、屢々、遷移金属磁性体が用いられるため、広く用いられているシリコン系半導体装置のエッチングプロセスに用いられるハロゲン系ガスを用いたメタルエッティング技術では、磁性材料層を容易にエッティングすることができない。しかも、 $1\text{nm}$ 程度と極めて薄いトンネル絶縁膜に短絡や電流リークが発生すること無く、磁性材料層をエッティングすることは困難である。

## 【0007】

50

そのために、非ハロゲン系ガスを用いたリアクティブ・イオン・エッティング（R I E）法の検討が進められている。しかしながら、R I E 法は、物理エッティング要素を有するが故に、トンネル絶縁膜の側壁にエッティング加工物が再付着し、短絡や電流リークが生じる虞が大きい。また、不揮発性メモリ素子のM T J構造におけるダメージ発生の回避が困難であり、特性バラツキを引き起こす大きな要因となっている。

#### 【0008】

磁性材料層のパターニングには、従来からイオンビームエッティング法も使用されている。この方法にあっては、磁性材料層へのダメージは少ないが、エッティング加工物の再付着が一番の課題である。特に、トンネル絶縁膜が1 nm程度と極めて薄いので、エッティング加工物の再付着による短絡や電流リークが、或る一定割合で発生してしまうことが避けられないといった問題がある。10

#### 【0009】

以上の問題を解決する方策として、M T J構造のパターニング加工の際、トンネル絶縁膜の上に形成された磁性材料層（『上層磁性材料層』と呼ぶ）のエッティングを途中で中止し、上層磁性材料層の一部を残した状態で上層磁性材料層の一部を酸化させて導電性を劣化させる技術が、特表2003-505873や、特開2003-078185、特表2006-520105から周知である。これらの技術にあっては、エッティング面がトンネル絶縁膜にまで達しないので、トンネル絶縁膜の側壁にエッティング加工物が再付着することが無く、短絡や電流リークが生じるといった問題の発生を回避することができる。

#### 【0010】

あるいは又、不揮発性メモリ素子として、相変化型メモリ素子（Phase change RAM, P R A M）を含む抵抗変化型メモリ素子が提案されている。この不揮発性メモリ素子は、上下の電極間にメモリ部として機能する抵抗変化層を配置した構造を有し、メモリ構造が単純であり、容易に微細化することが可能である。抵抗変化型メモリ素子の一種である相変化型メモリ素子は、抵抗変化層を構成する相変化材料がアモルファス状態と結晶状態とで電気抵抗が数桁違うことを利用してメモリ素子として動作させる不揮発性メモリ素子である（例えば、特開2007-134676参照）。また、抵抗変化型メモリ素子の一種に、抵抗変化層を構成する材料の有する電界誘起巨大抵抗変化効果（C E R効果：Colossal Electro-Resistance効果）を利用してデータを記憶する不揮発性メモリ素子がある（例えば、特開2003-068983参照）。あるいは又、抵抗変化型メモリ素子の一種に、金属を含むイオン導電体から抵抗変化層が構成された不揮発性メモリ素子がある（例えば、特開2005-166976や特開2005-197634参照）。更には、抵抗変化型メモリ素子の一種に、P M C（Programmable metallization Cell）が知られている（例えば、特開2005-322942参照）。

#### 【0011】

抵抗変化型メモリ素子にあっても、抵抗変化層のパターニング加工において、抵抗変化層の側壁にエッティング加工物が再付着し、短絡や電流リークが生じる虞が大きい。

#### 【先行技術文献】

#### 【特許文献】

#### 【0012】

【特許文献1】特開2003-017782

【特許文献2】特表2003-505873

【特許文献3】特開2003-078185

【特許文献4】特表2006-520105

【特許文献5】特開2007-134676

【特許文献6】特開2003-068983

【特許文献7】特開2005-166976

【特許文献8】特開2005-197634

【特許文献9】特開2005-322942

#### 【発明の概要】

10

20

30

40

50

**【発明が解決しようとする課題】****【0013】**

しかしながら、上述した特許公開公報、特許公表公報に開示された酸化技術にあっては、酸化の深さ方向の制御が難しい。そして、酸化力と膜厚を適切に調整したとしても、MTJ構造を有する不揮発性メモリ素子の酸化工程後の製造工程におけるプロセス温度等により、上層磁性材料層に残存した過剰な酸素が熱拡散し、磁性材料層にダメージを与えてしまう虞がある。生産性を考慮すれば、必要、且つ、十分に酸化処理を施す必要があり、過剰な酸素が残存する状況は避けられない。

**【0014】**

抵抗変化型メモリ素子にあっても、抵抗変化層のパターニング加工において、上述した特許公開公報、特許公表公報に開示された酸化技術を適用することは可能であろう。しかしながら、酸化工程後の抵抗変化型メモリ素子の製造工程におけるプロセス温度等により、抵抗変化層に残存した過剰な酸素が熱拡散を起こし、抵抗変化層にダメージを与えてしまう虞がある。

**【0015】**

従って、本発明の第1の目的は、短絡や電流リークを生じさせること無く、しかも、MTJ構造にダメージを生じさせること無く、不揮発性メモリ素子におけるMTJ構造のパターニングを行い得る不揮発性メモリ素子の製造方法を提供することにある。また、本発明の第2の目的は、短絡や電流リークを生じさせること無く、しかも、抵抗変化層にダメージを生じさせること無く、抵抗変化型メモリ素子における抵抗変化層のパターニングを行い得る不揮発性メモリ素子の製造方法を提供することにある。

**【課題を解決するための手段】****【0016】**

上記の第1の目的を達成するための本発明の第1の態様に係る不揮発性メモリ素子の製造方法は、第1磁性材料層、トンネル絶縁膜及び第2磁性材料層が、順次、積層されて成る積層構造体を有し、磁化反転状態に依存して電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子の製造方法であって、

第1磁性材料層、トンネル絶縁膜及び第2磁性材料層を順次形成し、次いで、第2磁性材料層上にマスク層を形成した後、マスク層で覆われていない第2磁性材料層の部分を酸化し、次いで、酸化された第2磁性材料層の部分を還元する工程を備えている。

**【0017】**

上記の第2の目的を達成するための本発明の第2の態様に係る不揮発性メモリ素子の製造方法は、抵抗変化層の電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子の製造方法であって、

抵抗変化層上にマスク層を形成した後、マスク層で覆われていない抵抗変化層の部分を酸化し、次いで、酸化された抵抗変化層の部分を還元する工程を備えている。

**【発明の効果】****【0018】**

本発明の第1の態様に係る不揮発性メモリ素子の製造方法にあっては、マスク層で覆われていない第2磁性材料層の部分を酸化し、次いで、酸化された第2磁性材料層の部分を還元する工程を備えており、本発明の第2の態様に係る不揮発性メモリ素子の製造方法にあっては、マスク層で覆われていない抵抗変化層の部分を酸化し、次いで、酸化された抵抗変化層の部分を還元する工程を備えている。即ち、第2磁性材料層や抵抗変化層をエッティング法等によってパターニングして不要な部分を全て除去するのではなく、酸化によって第2磁性材料層や抵抗変化層の有する機能（導電性、磁気特性等）を劣化させる。それ故、機能を保持した第2磁性材料層や抵抗変化層の領域（機能領域）にダメージが生じ難い。そして、酸化された第2磁性材料層の部分や抵抗変化層の部分を還元するので、不揮発性メモリ素子の酸化工程後の製造工程におけるプロセス温度等により、第2磁性材料層や抵抗変化層に残存した過剰な酸素が熱拡散し、磁性材料層や抵抗変化層にダメージを与えててしまうといった問題が生じることもない。即ち、酸素に起因した機能領域の劣化発生

10

20

30

40

50

を防止することができる。尚、酸化によって機能（導電性、磁気特性等）が劣化した第2磁性材料層や抵抗変化層の部分においては、還元処理によつても、劣化した機能が復旧（回復）することはない。そして、以上の結果として、高特性、長期信頼性を有する不揮発性メモリ素子を提供することができる。

**【図面の簡単な説明】**

**【0019】**

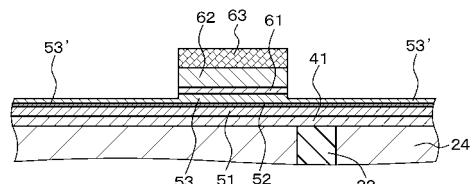

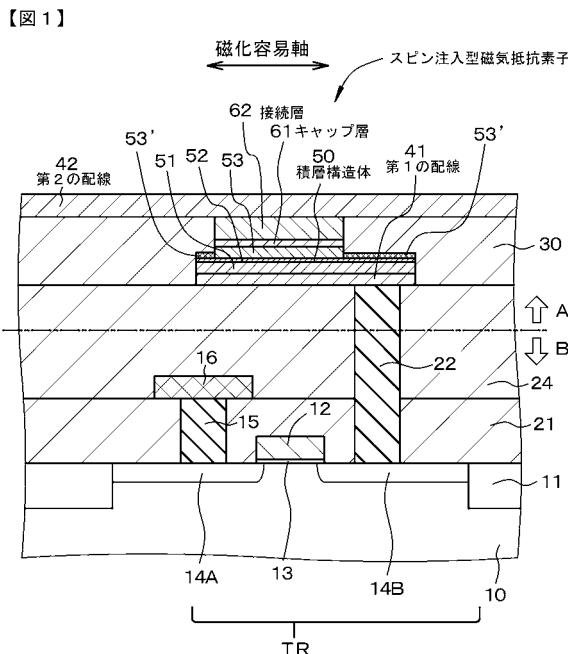

【図1】図1は、実施例1の不揮発性メモリ素子の製造方法によって得られた不揮発性メモリ素子の模式的な一部断面図である。

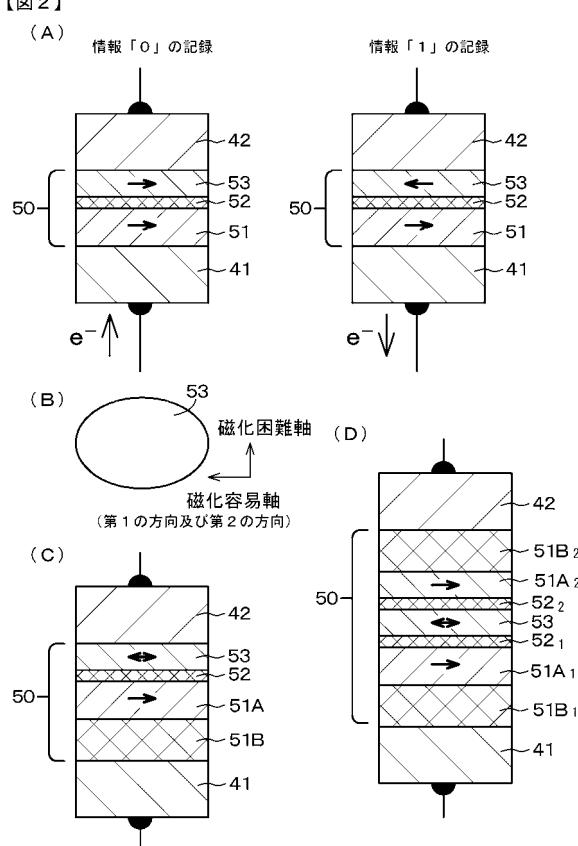

【図2】図2の(A)及び(B)は、実施例1における不揮発性メモリ素子を構成する積層構造体の断面構造を概念的に示す図である。

10

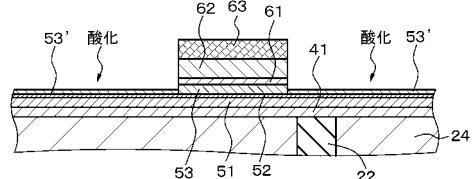

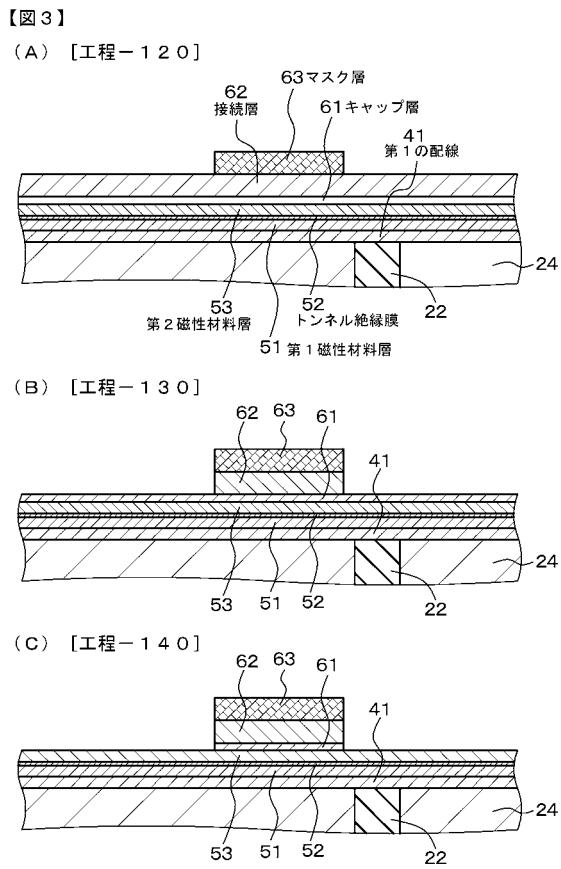

【図3】図3の(A)、(B)及び(C)は、実施例1の不揮発性メモリ素子の製造方法を説明するための、第1磁性材料層等の模式的な一部断面図である。

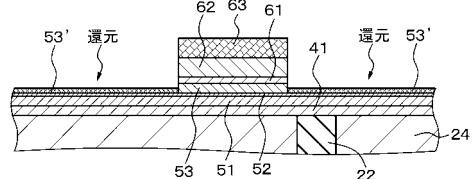

【図4】図4の(A)、(B)及び(C)は、図3の(C)に引き続き、実施例1の不揮発性メモリ素子の製造方法を説明するための、第1磁性材料層等の模式的な一部断面図である。

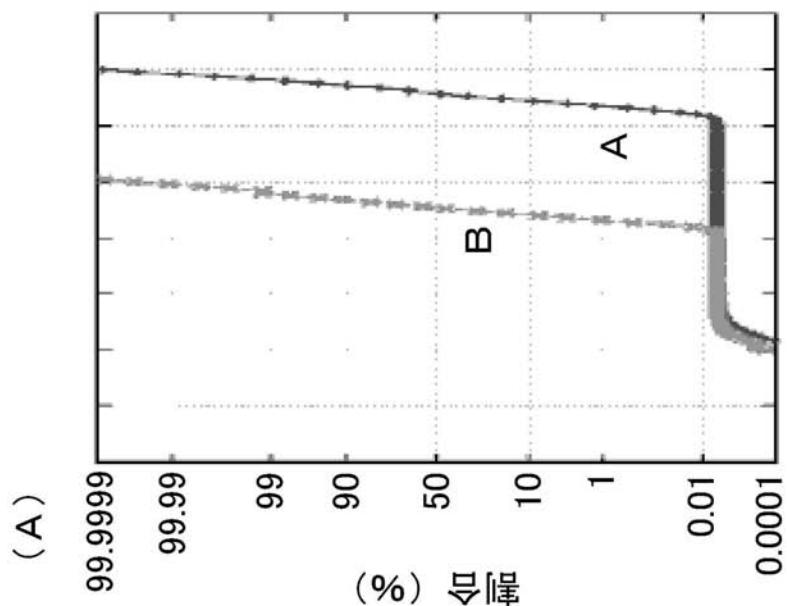

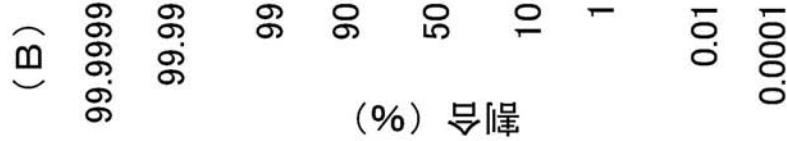

【図5】図5の(A)及び(B)は、それぞれ、実施例1の不揮発性メモリ素子、及び、第2磁性材料層、トンネル絶縁膜及び第1磁性材料層をイオンミーリング法にてパターニングして得られた従来の不揮発性メモリ素子における、高読出し抵抗値及び低読出し抵抗値の測定結果を示すグラフである。

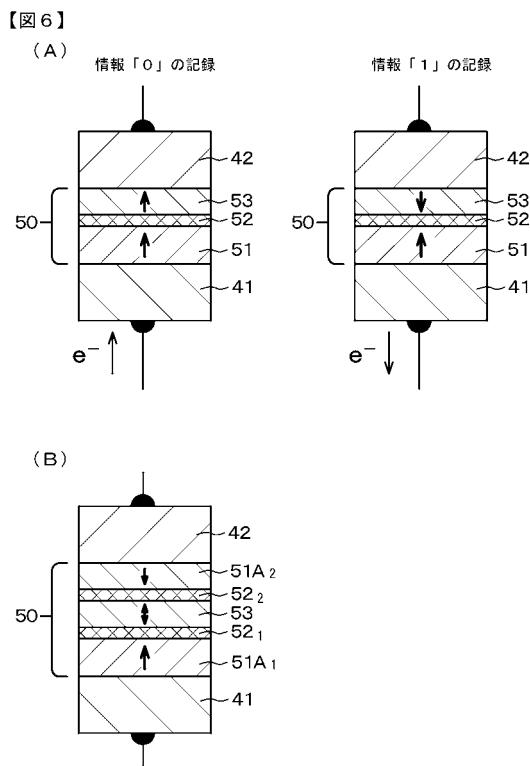

【図6】図6の(A)及び(B)は、実施例2における不揮発性メモリ素子を構成する積層構造体の断面構造を概念的に示す図である。

20

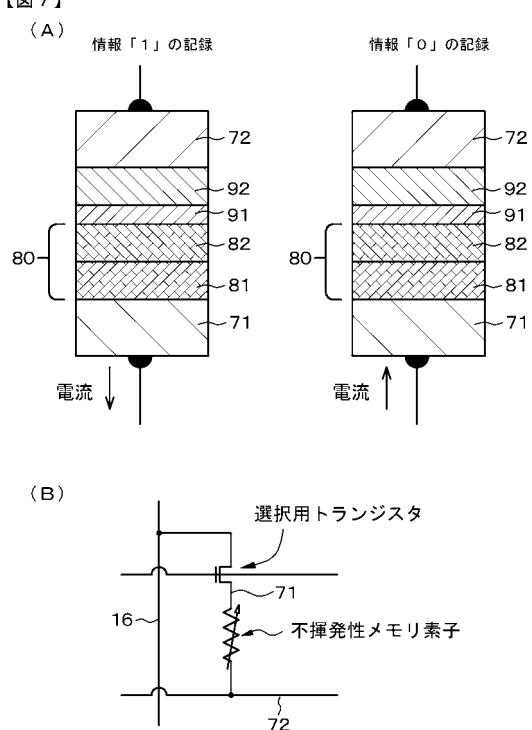

【図7】図7の(A)及び(B)は、それぞれ、実施例3の不揮発性メモリ素子の製造方法によって得られた不揮発性メモリ素子を構成する積層構造体の断面構造を概念的に示す図、及び、等価回路図である。

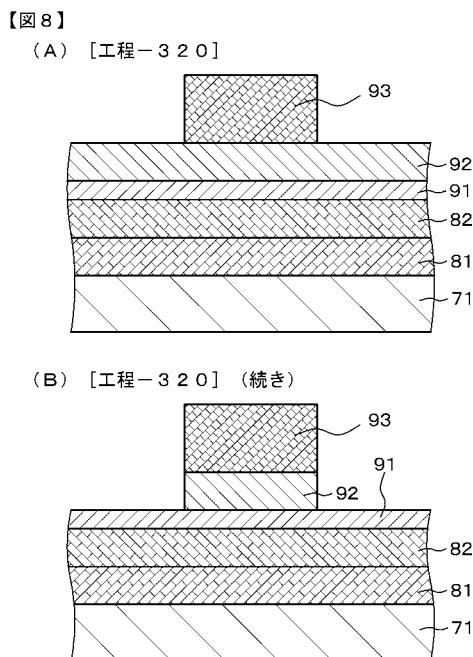

【図8】図8の(A)及び(B)は、実施例3の不揮発性メモリ素子の製造方法を説明するための、第1磁性材料層等の模式的な一部断面図である。

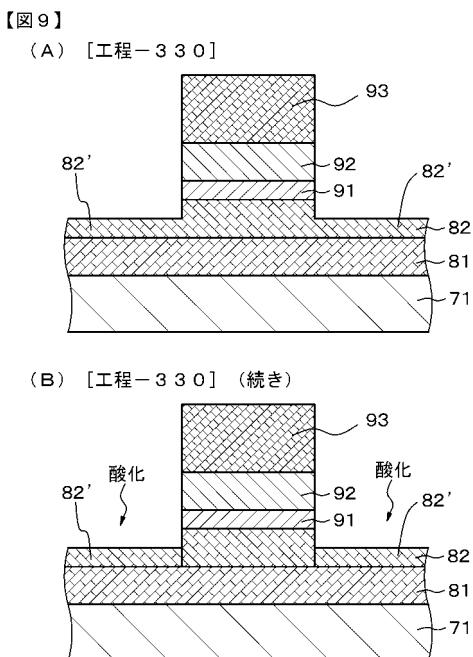

【図9】図9の(A)及び(B)は、図8の(B)に引き続き、実施例3の不揮発性メモリ素子の製造方法を説明するための、第1磁性材料層等の模式的な一部断面図である。

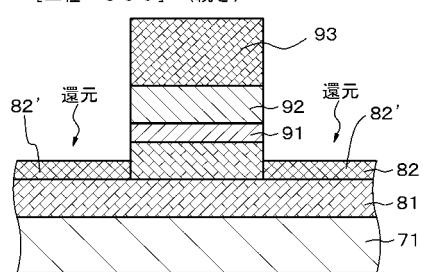

【図10】図10は、図9の(B)に引き続き、実施例3の不揮発性メモリ素子の製造方法を説明するための、第1磁性材料層等の模式的な一部断面図である。

30

**【発明を実施するための形態】**

**【0020】**

以下、図面を参照して、実施例に基づき本発明を説明するが、本発明は実施例に限定されるものではなく、実施例における種々の数値や材料は例示である。尚、説明は、以下の順序で行う。

1. 本発明の第1の態様及び第2の態様に係る不揮発性メモリ素子の製造方法、全般に関する説明

2. 実施例1（本発明の第1の態様に係る不揮発性メモリ素子の製造方法）

3. 実施例2（実施例1の変形）

4. 実施例3（本発明の第2の態様に係る不揮発性メモリ素子の製造方法）

40

5. 実施例4（実施例3の変形、その他）

**【0021】**

[本発明の第1の態様及び第2の態様に係る不揮発性メモリ素子の製造方法、全般に関する説明]

本発明の第1の態様に係る不揮発性メモリ素子の製造方法においては、第2磁性材料層上にマスク層を形成した後、マスク層で覆われていない第2磁性材料層の部分を酸化する前に、マスク層で覆われていない第2磁性材料層の部分を、厚さ方向に一部分、エッティングする形態とすることができます。但し、これに限定するものではなく、マスク層で覆われていない第2磁性材料層の部分をエッティングしなくともよい。第2磁性材料層の部分を、厚さ方向に一部分、エッティングする方法として、イオンミーリング法（イオンビームエッ

50

チング法とも呼ばれる)、反応性イオンエッティング法(RIE法)を例示することができる。尚、この場合、マスク層がエッティング用マスクとして機能する。

#### 【0022】

上記の好ましい形態を含む本発明の第1の態様に係る不揮発性メモリ素子の製造方法において、第1磁性材料層は磁化参照層から構成され、第2磁性材料層は記録層から構成されている形態とすることができますし、あるいは又、このような構成とは逆に、第1磁性材料層は記録層から構成され、第2磁性材料層は磁化参照層から構成されている形態とすることもできる。

#### 【0023】

更には、上記の各種好ましい形態を含む本発明の第1の態様に係る不揮発性メモリ素子の製造方法にあっては、マスク層で覆われていない第2磁性材料層の部分を、プラズマ酸化法、熱酸化法、又は、ラジカル酸化法に基づき酸化することができるし、イオン注入法に基づき酸素を注入してもよい。また、酸化された第2磁性材料層の部分を、水素プラズマ法に基づき還元することが好ましいが、その他、アンモニアガスを用いたプラズマ還元法、水素ガスやアンモニアガスを用いたラジカル還元法、水素ガスやアンモニアガス雰囲気中で加熱処理を行う方法を採用してもよい。これらの酸化法と還元法の組合せは、本質的に任意である。

10

#### 【0024】

本発明の第2の態様に係る不揮発性メモリ素子の製造方法において、抵抗変化層は、金属を含むイオン導電体から成る形態とすることができますし、あるいは又、抵抗変化層はカルコゲナイト系材料から成る形態とすることができます。あるいは又、抵抗変化層は電界誘起巨大抵抗変化効果(CER効果)を有する材料から成る形態とすることができますし、この場合、具体的には、抵抗変化層はペロブスカイト系材料から成る構成とすることができます。

20

#### 【0025】

本発明の第1の態様あるいは第2の態様に係る不揮発性メモリ素子の製造方法にあっては、マスク層を構成する材料として、SiO<sub>2</sub>、SiN、SiC、SiON、SiCNを例示することができる。尚、マスク層を積層構成とすることもできる。マスク層は、リソグラフィ工程における反射防止効果や、エッティングストップ、メタル拡散防止等の機能を兼ねて形成される場合もある。マスク層は、例えば、CVD法で形成すればよいし、マスク層のパターニングは、リソグラフィ技術とエッティング技術との組合せに基づき行うことができる。

30

#### 【0026】

以上に説明した好ましい形態、構成を含む本発明の第1の態様に係る不揮発性メモリ素子の製造方法において得られる不揮発性メモリ素子は、所謂、磁気抵抗効果を有する不揮発性磁気メモリ素子である。尚、このような不揮発性メモリ素子を、便宜上、『第1の態様の不揮発性メモリ素子』と呼ぶ。ここで、第1の態様の不揮発性メモリ素子を、電流磁場反転方式のトンネル磁気抵抗効果素子(MRAM)から構成することもできるし、スピノ注入による磁化反転を応用したスピノ注入型磁気抵抗効果素子(スピノRAM)から構成することもできる。後者においては、面内磁化方式及び垂直磁化方式が含まれる。

40

#### 【0027】

第1の態様の不揮発性メモリ素子の内、電流磁場反転方式のトンネル磁気抵抗効果素子にあっては、酸化を受けなかった第2磁性材料層の平面形状として、楕円形、長円形(2つの半円と2つの線分とが組み合わされた图形)、放物線や双曲線によって囲まれた形状、広くは2次関数あるいは3次以上の関数で表現し得る图形から構成された形状、正多角形(長方形、正5角形以上の正多角形、頂点が丸みを帯びた長方形、頂点が丸みを帯びた正5角形以上の正多角形が含まれる)、扁平な円形(円形を一方向から押し潰したような图形)を挙げることができるし、楕円形と線分との組合せ、放物線と線分との組合せ、双曲線と線分との組合せ、広くは、2次関数と1次関数との組合せ、あるいは3次以上の関数と1次関数との組合せを含むことができる。あるいは又、湾曲した形状とすることが一層好ましい(具体的には、例えば、特開2005-353788参照)。一方、第1の態

50

様の不揮発性メモリ素子の内、スピニ注入型磁気抵抗効果素子にあっては、酸化を受けなかつた第2磁性材料層の平面形状として、円形を挙げることができる。

#### 【0028】

第1の態様の不揮発性メモリ素子あるいは後述する第2の態様の不揮発性メモリ素子にあっては、一般に、積層構造体あるいは抵抗変化層の下に第1の配線あるいは第1電極を備えており、また、積層構造体あるいは抵抗変化層の上方に電気的に接続された第2の配線あるいは第2電極を備えている。そして、積層構造体あるいは抵抗変化層の下方に、電界効果型トランジスタ(FET)から成る選択用トランジスタを更に有しており、第2の配線(例えば、ピット線)の延びる方向は、電界効果型トランジスタを構成するゲート電極の延びる方向と平行である形態とすることができますが、これに限定するものではなく、第2の配線の延びる方向の射影像は、電界効果型トランジスタを構成するゲート電極の延びる方向の射影像と直交する形態とすることもできる。また、場合によっては、選択用トランジスタは不要である。

10

#### 【0029】

ここで、スピニ注入型磁気抵抗効果素子にあっては、磁化参照層(固着層あるいは磁化固定層とも呼ばれる)、トンネル絶縁膜、及び、情報を記憶する記録層(磁化反転層あるいは自由層とも呼ばれる)によって、TMR効果を有する積層構造体が構成されている。尚、磁化参照層、トンネル絶縁膜、記録層、トンネル絶縁膜、磁化参照層によって、TMR効果を有する積層構造体が構成されている構造とすることもできる。このような構造にあっては、記録層の上下に位置する2つのトンネル絶縁膜の磁気抵抗の変化に差を付けておく必要がある。トンネル絶縁膜は、記録層と磁化参照層との間の磁気的結合を切ると共に、トンネル電流を流すための役割を担う。そして、スピニ偏極電流を記録層内に注入することにより、記録層における磁化の方向を第1の方向(磁化容易軸と平行な方向)あるいは第2の方向(第1の方向とは反対の方向)とすることで、記録層に情報が書き込まれる(面内磁化方式)。あるいは又、スピニ偏極電流を記録層から磁化参照層へ流すと、スピニ偏極電子は磁化参照層から記録層へ注入され、磁化参照層の磁化方向と記録層の磁化方向が平行配列となり、スピニ偏極電流を磁化参照層から記録層へ流すと、スピニ偏極電子は記録層から磁化参照層へ流れ、磁化参照層と平行なスピニを持つ電子は透過し、反平行のスピニを持つ電子が反射され、結果として、記録層の磁化方向と磁化参照層の磁化方向が反平行配列となる(垂直磁化方式)。

20

#### 【0030】

第1の態様の不揮発性メモリ素子における記録層、磁化参照層を構成する材料として、ニッケル(Ni)、鉄(Fe)、コバルト(Co)といった強磁性材料、これらの強磁性材料の合金(例えば、Co-Fe、Co-Fe-Ni、Fe-Pt、Ni-Fe等)、これらの合金に非磁性元素(例えば、タンタル、ホウ素、クロム、白金、シリコン、炭素、窒素等)を混ぜた合金(例えば、Co-Fe-B等)、Co、Fe、Niの内の1種類以上を含む酸化物(例えば、フェライト:Fe-MnO等)、ハーフメタリック強磁性材料と呼ばれる一群の金属間化合物(ホイスラー合金:NiMnSb、Co<sub>2</sub>MnGe、Co<sub>2</sub>MnSi、Co<sub>2</sub>CrAl等)、酸化物(例えば、(La, Sr)MnO<sub>3</sub>、CrO<sub>2</sub>、Fe<sub>3</sub>O<sub>4</sub>等)を挙げることができる。あるいは、これらの合金にガドリニウム(Gd)が添加された合金を例示することができる。更には、垂直磁気異方性を一層増加させるために、係る合金にテルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)等の重希土類を添加してもよいし、これらを含む合金を積層してもよい。記録層、磁化参照層の結晶性は、本質的に任意であり、多結晶であってもよいし、単結晶であってもよいし、非晶質であってもよい。また、磁化参照層を構成する材料として、上述した材料以外にも、例えば、Co-Tb、Co-Ptを挙げることができる。更には、積層フェリ構造[反強磁性的結合を有する積層構造であり、合成反強磁性結合(SAF:Synthetic Antiferromagnet)とも呼ばれる]を有する構成とすることができますが、静磁結合構造を有する構成とすることができますし、磁化参照層に隣接して反強磁性体層を配置してもよい。磁化参照層に隣接して反強磁性体層を配置することで、これらの2層の間に働く交換相互作用によ

30

40

50

って強い一方向の磁気的異方性を得ることができる。積層フェリ構造は、例えば、磁性体層／ルテニウム（Ru）層／磁性体層の3層構造（具体的には、例えば、CoFe/Ru/CoFeの3層構造、CoFeB/Ru/CoFeBの3層構造）を有し、ルテニウム層の厚さによって、2つの磁性体層の層間交換結合が、反強磁性的あるいは強磁性的になる構造を指し、例えば、S. S. Parkin et. al, Physical Review Letters, 7 May, pp 2304-2307 (1990) に報告されている。また、2つの磁性体層において、磁性体層の端面からの漏洩磁界によって反強磁性的結合が得られる構造を、静磁結合構造と呼ぶ。反強磁性体層を構成する材料として、鉄-マンガン合金、ニッケル-マンガン合金、白金-マンガン合金、イリジウム-マンガン合金、ロジウム-マンガン合金、コバルト酸化物、ニッケル酸化物を挙げることができる。第1の配線（あるいは第2の配線）と反強磁性体層との間には、反強磁性体層の結晶性向上のために、Ta、Cr、Ru、Ti等から成る下地膜を形成してもよい。更には、各種磁性半導体の使用も可能であるし、軟磁性（ソフト膜）であっても硬磁性（ハード膜）であってもよい。記録層は、単層構成とすることもできるし、上述したとおり複数の異なる強磁性体層を積層した積層構成とすることもできるし、強磁性体層と非磁性体層を積層した積層構成とすることもできる。

10

## 【0031】

第1の態様の不揮発性メモリ素子におけるトンネル絶縁膜を構成する材料として、アルミニウム酸化物（Al<sub>2</sub>O<sub>x</sub>）、アルミニウム窒化物（AlN）、マグネシウム酸化物（MgO）、マグネシウム窒化物、シリコン酸化物、シリコン窒化物、TiO<sub>2</sub>あるいはCr<sub>2</sub>O<sub>3</sub>、Ge、NiO、CdO<sub>x</sub>、HfO<sub>2</sub>、Ta<sub>2</sub>O<sub>5</sub>、BN、ZnS等の絶縁材料を挙げることができる。トンネル絶縁膜は、例えば、スパッタリング法にて形成された金属膜を酸化若しくは窒化することにより得ることができる。より具体的には、トンネル絶縁膜を構成する絶縁材料としてアルミニウム酸化物（Al<sub>2</sub>O<sub>x</sub>）、マグネシウム酸化物（MgO）を用いる場合、例えば、スパッタリング法にて形成されたアルミニウムやマグネシウムを大気中で酸化する方法、スパッタリング法にて形成されたアルミニウムやマグネシウムをプラズマ酸化する方法、スパッタリング法にて形成されたアルミニウムやマグネシウムをICPプラズマで酸化する方法、スパッタリング法にて形成されたアルミニウムやマグネシウムを酸素中で自然酸化する方法、スパッタリング法にて形成されたアルミニウムやマグネシウムを酸素ラジカルで酸化する方法、スパッタリング法にて形成されたアルミニウムやマグネシウムを酸素中で自然酸化させるときに紫外線を照射する方法、アルミニウムやマグネシウムを反応性スパッタリング法にて成膜する方法、アルミニウム酸化物（Al<sub>2</sub>O<sub>x</sub>）やマグネシウム酸化物（MgO）をスパッタリング法にて成膜する方法を例示することができる。

20

## 【0032】

これらの層は、例えば、スパッタリング法、イオンビーム堆積法、真空蒸着法に例示される物理的気相成長法（PVD法）、ALD（Atomic Layer Deposition）法に代表される化学的気相成長法（CVD法）にて形成することができる。

30

## 【0033】

第1の配線や第2の配線、第1電極、第2電極は、銅（Cu）、アルミニウム（Al）、金（Au）、白金（Pt）、チタン（Ti）、モリブデン（Mo）、タンタル（Ta）、タンゲステン（W）、TiN、TiW、WN、シリサイド等の単層構造から成り、あるいは又、CrやTi等から成る下地層と、その上に形成されたCu層、Au層、Pt層等の積層構造を有していてもよい。更には、Ta等の単層あるいはCu、Ti等との積層構造から構成することもできる。これらの配線は、例えば、スパッタリング法に例示されるPVD法にて形成することができる。

40

## 【0034】

以上に説明した好ましい形態を含む本発明の第2の態様に係る不揮発性メモリ素子の製造方法において得られる不揮発性メモリ素子は、所謂、抵抗変化型メモリ素子である。尚、このような不揮発性メモリ素子を、便宜上、『第2の態様の不揮発性メモリ素子』と呼ぶ。

50

## 【0035】

第2の態様の不揮発性メモリ素子にあっては、上述したとおり、抵抗変化層は、金属を含むイオン導電体から成る形態とすることができます、具体的には、抵抗変化層を、Cu、Ag、Znから選ばれるいずれかの元素(原子)と、Te、S、Seといったカルコゲナイト元素(原子)から選ばれるいずれかの元素(原子)とが含まれている導電性又は半導電性の薄膜(例えば、GeSbTe、GeTe、GeSe、GeS、SiGeTe、SiGeSbTeから成る薄膜や、これらの薄膜と、例えば、Ag、Ag合金、Cu、Cu合金、Zn、Zn合金から成る薄膜の積層構造)から構成することができるし、あるいは又、全体あるいは膜厚方向の一部分に、希土類元素のうち、La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Yb、Yから選ばれる、1種類、若しくは、複数種類の希土類元素の酸化物から成る膜(希土類酸化物薄膜)や、Hf、Ta、W等の酸化膜が形成された構成とすることができる。尚、この場合、具体的には、第1電極、高抵抗層、抵抗変化層及び第2電極の積層構造を有する構成とすることができる。あるいは又、第2の態様の不揮発性メモリ素子にあっては、上述したとおり、抵抗変化層はカルコゲナイト系材料から成る形態とすることができますが、ここで、抵抗変化層を構成するカルコゲナイト系材料として、GeSbTe、ZnSe、GaSnTe等の、金属とSeやTeとの化合物を挙げることができる。あるいは又、第2の態様の不揮発性メモリ素子にあっては、上述したとおり、抵抗変化層は電界誘起巨大抵抗変化効果(CER効果)を有する材料から形態とすることができますが、係る材料として、3元系ペロブスカイト型遷移金属酸化物(PrCaMnO<sub>3</sub>やSrTiO<sub>3</sub>)を挙げができるし、2元系遷移金属酸化物(CiO、NiO、CuO、TiO<sub>2</sub>、Fe<sub>3</sub>O<sub>4</sub>)を挙げることもできる。

10

20

30

30

## 【0036】

第1の態様の不揮発性メモリ素子あるいは第2の態様の不揮発性メモリ素子における好ましい構成にあっては、上述したとおり、積層構造体の下方に、電界効果型トランジスタから成る選択用トランジスタを更に有しているが、より具体的な構成として、例えば、限定するものではないが、

半導体基板に形成された選択用トランジスタ、及び、

選択用トランジスタを覆う下層絶縁層、

を備え、

下層絶縁層上に第1の配線あるいは第1電極が形成されており、

第1の配線あるいは第1電極が、下層絶縁層に設けられた接続孔(あるいは接続孔とランディングパッド部や下層配線)を介して選択用トランジスタに電気的に接続されており、

上層絶縁層は、下層絶縁層及び第1の配線あるいは第1電極を覆い、積層構造体を取り囲んでおり、

第2の配線あるいは第2電極は上層絶縁層上に形成されている構成を例示することができる。

40

## 【0037】

選択用トランジスタは、例えば、周知のMIS型FETやMOS型FETから構成することができる。第1の配線あるいは第1電極と選択用トランジスタとを電気的に接続する接続孔は、不純物がドーピングされたポリシリコンや、タンゲステン、Ti、Pt、Pd、Cu、TiW、TiNW、WSi<sub>2</sub>、MoSi<sub>2</sub>等の高融点金属や金属シリサイドから構成することができ、CVD法や、スパッタリング法に例示されるPVD法に基づき形成することができる。また、下層絶縁層や上層絶縁層を構成する材料として、酸化シリコン(SiO<sub>2</sub>)、窒化シリコン(SiN)、SiON、SOG、NSG、BPSG、PSG、BSGあるいはLTOを例示することができる。

50

## 【実施例1】

## 【0038】

実施例1は、本発明の第1の態様に係る不揮発性メモリ素子の製造方法に関する。実施例1の不揮発性メモリ素子の製造方法にて得られた第1の態様の不揮発性メモリ素子の模

50

式的な一部断面図を図1に示す。

【0039】

実施例1あるいは後述する実施例2の不揮発性メモリ素子は、第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53が、順次、積層されて成る積層構造体50を有し、磁化反転状態に依存して電気抵抗値が変化することで情報を記憶する不揮発性メモリ素子である。実施例1あるいは後述する実施例2の不揮発性メモリ素子にあっては、積層構造体50の下部に電気的に接続された第1の配線41、及び、積層構造体50の上部に電気的に接続された第2の配線42を更に備えている。

【0040】

尚、実施例1の不揮発性メモリ素子は、スピノ注入による磁化反転を応用したスピノ注入型磁気抵抗効果素子(スピノRAM)から成り、面内磁化方式である。また、実施例1の不揮発性メモリ素子にあっては、第2磁性材料層(記録層)における酸化されていない領域分の平面形状を長橈円形状とした。

【0041】

実施例1あるいは後述する実施例2の不揮発性メモリ素子にあっては、積層構造体50の上部と第2の配線42との間に、厚さ80nmのTiN層から成る接続層(トップ層)62が設けられている。また、積層構造体50と接続層62との間には、厚さ約5nmのTa層から成るキャップ層61がスパッタリング法にて形成されている。キャップ層61は、第2の配線42や接続層62を構成する原子と第2磁性材料層53を構成する原子の相互拡散の防止、接触抵抗の低減、及び、第2磁性材料層53の酸化防止を担っている。尚、キャップ層として、その他、Ru層、Pt層、MgO層、Ru膜/Ta膜の積層構造を挙げることができる。

【0042】

更には、実施例1あるいは後述する実施例2の不揮発性メモリ素子にあっては、積層構造体50の下方(より具体的には、第1の配線41の下方)に、電界効果型トランジスタから成る選択用トランジスタTRが設けられている。そして、第2の配線(ピット線)42の延びる方向は、電界効果型トランジスタを構成するゲート電極12(所謂ワード線として機能する)の延びる方向と平行である。具体的には、選択用トランジスタTRは、素子分離領域11によって囲まれたシリコン半導体基板10の部分に形成されており、下層絶縁層21, 23によって覆われている。そして、一方のソース/ドレイン領域14Bは、タングステンプラグから成る接続孔22を介して、第1の配線41に接続されている。また、他方のソース/ドレイン領域14Aは、タングステンプラグ15を介してセンス線16に接続されている。図中、参照番号13はゲート絶縁膜を示す。

【0043】

図1の不揮発性メモリ素子の模式的な一部断面図において、図面の関係上、一点鎖線の上側の「A」の領域と、下側の「B」の領域では、不揮発性メモリ素子の断面を眺める方向が90度異なっている。即ち、「A」の領域は、不揮発性メモリ素子の断面を第1の方向から眺めており、「B」の領域は、不揮発性メモリ素子の断面を第1の方向と直交する方向から眺めている。従って、係る図面では、第2の配線(ピット線)42の延びる方向の射影像と、電界効果型トランジスタを構成するゲート電極12の延びる方向の射影像とは直交しているように図示しているが、実際には、平行である。

【0044】

図2の(A)に概念図を示すように、実施例1において、積層構造体50は、以下に説明する構成、構造を有しており、スパッタリング法にて形成されている。尚、磁化参照層51Aにおいては、反強磁性体層51BのPt-Mn合金層との交換結合によって、磁化の方向がピニング(pinning)される。また、第2磁性材料層(記録層)53においては、スピノ偏極電流の流れる方向により、その磁化の方向が、磁化固定に対して平行又は反平行に変えられる。

【0045】

具体的には、実施例1におけるスピノ注入型磁気抵抗効果素子は、TMR効果を有する

10

20

30

40

50

積層膜から成る磁気抵抗効果積層膜が2つの配線41, 42で挟まれた構造を有する。即ち、情報を記録する機能を担う記録層（磁化反転層あるいは自由層とも呼ばれる第2磁性材料層53）と、磁化方向が固定されており、スピニルフィルターとして機能する磁化参照層（固着層あるいは磁化固定層とも呼ばれ、第1磁性材料層51を構成する）が、トンネル絶縁膜52を介して積層された構造を有し、スピニル偏極電流は膜面に垂直に流れる（図2の(A)参照）。第2磁性材料層53の大きさは、模式的な平面図を図2の(B)に示すが、第2磁性材料層53を構成する磁性材料の種類や膜厚に依るが、単磁区化を促進し、且つ、スピニル注入磁化反転の臨界電流 $I_c$ を低減するため、概ね200nm以下である。記録層53は、適当な磁気異方性により2以上の複数の磁化方向（例えば、図2の(A)に水平方向の矢印にて示す2方向である第1の方向及び第2の方向）を取ることができ、各磁化方向は記録される情報に対応する。第2磁性材料層（記録層）53の平面形状を、例えば、長方形形状にすることによって、形状磁気異方性を付与することができる。即ち、記録層53は、第1の方向及び第2の方向に平行な磁化容易軸と、磁化困難軸とをしており、磁化容易軸に沿った記録層53の長さは、磁化困難軸に沿った記録層53の長さよりも長い。

10

## 【0046】

第1磁性材料層51を構成する磁化参照層51Aは、第1磁性材料層51を構成する反強磁性体層51Bとの交換結合により、その磁化方向が固定されている（図2の(C)参照）。磁化参照層51A<sub>1</sub>, 51A<sub>2</sub>を、第2磁性材料層（記録層）53の上下に、トンネル絶縁膜52<sub>1</sub>, 52<sub>2</sub>を介して配置して、スピニル注入磁化反転の効率を向上させたダブル・スピニルフィルター構造も知られている（図2の(D)参照）。ここで、参考番号51B<sub>1</sub>, 51B<sub>2</sub>は、反強磁性体層である。尚、図2の(A)、(C)及び(D)に示した例においては、第2磁性材料層（記録層）53、第1磁性材料層51、磁化参照層51A（磁化参照層が2層51A<sub>1</sub>, 51A<sub>2</sub>の場合には、いずれか一方の層）を、積層フェリ構造としてもよい。いずれにしても、スピニル注入磁化反転を適用した不揮発性磁気メモリ素子（スピニル注入型磁気抵抗効果素子）は、磁気抵抗効果積層膜の上下を配線で挟んだ、2端子スピントランジスタ構造を有する。

20

## 【0047】

実施例1における積層構造体50の具体的な構成例を以下に例示する。

30

## 【0048】

## [第2磁性材料層53]

Co - Fe - B層（厚さ：2~5nm程度）

## [トンネル絶縁膜52]

MgO層（厚さ：1.0nm）

## [第1磁性材料層51]

磁化参照層51A（SAFを持つ多層膜）

Co - Fe - B層（上層）/Ru層（中層）/Co - Fe層（下層）の3層構成

反強磁性体層51B

上層 Pt - Mn合金層（厚さ：20nm）

下層 Ta層（厚さ：5nm）

40

## 【0049】

以下、実施例1の不揮発性メモリ素子の製造方法を、図3の(A)、(B)、(C)、図4の(A)、(B)を参照して説明する。尚、これらの図面において、第1の配線41よりも下に位置する不揮発性メモリ素子の構成要素（選択用トランジスタTR等）の図示は省略した。

## 【0050】

## [工程-100]

先ず、周知の方法に基づき、シリコン半導体基板10に素子分離領域11を形成し、素子分離領域11によって囲まれたシリコン半導体基板10の部分に、ゲート酸化膜13、ゲート電極12、ソース/ドレイン領域14A, 14Bから成る選択用トランジスタTR

50

を形成する。次いで、第1下層絶縁層21を形成し、ソース／ドレイン領域14Aの上方の第1下層絶縁層21の部分にタングステンプラグ15を形成し、更には、第1下層絶縁層21上にセンス線16を形成する。その後、全面に第2下層絶縁層23を形成し、ソース／ドレイン領域14Bの上方の下層絶縁層21, 23の部分にタングステンプラグから成る接続孔22を形成する。こうして、下層絶縁層21, 23で覆われた選択用トランジスタTRを得ることができる。その後、スパッタリング法にて、下層絶縁層23の上に、接続孔22に接続された第1の配線41を形成する（以上は、図1を参照）。

## 【0051】

## [工程 - 110]

その後、以下に例示する条件のスパッタリング法に基づき、真空中での連続成膜にて、全面に、第1磁性材料層51、トンネル絶縁膜52及び第2磁性材料層53を、順次、形成し、更には、キャップ層61、接続層62を形成する。

10

## 【0052】

## [第1磁性材料層]

## 反強磁性体層の下層（Ta層）の成膜条件

プロセスガス：アルゴン = 100 sccm

成膜雰囲気圧力：0.6 Pa

DCパワー：200 W

## 反強磁性体層の上層（Pt-Mn合金層）の成膜条件

プロセスガス：アルゴン = 100 sccm

20

成膜雰囲気圧力：0.6 Pa

DCパワー：200 W

## 磁化参照層の成膜条件

## 最下層：厚さ2nmのCo-Fe合金層

プロセスガス：アルゴン = 50 sccm

成膜雰囲気圧力：0.3 Pa

DCパワー：100 W

## 中間層：厚さ1nmのRu層

プロセスガス：アルゴン = 50 sccm

30

成膜雰囲気圧力：0.3 Pa

DCパワー：50 W

## 最上層：厚さ2nmのCo-Fe-B合金層

プロセスガス：アルゴン = 50 sccm

成膜雰囲気圧力：0.3 Pa

DCパワー：100 W

## [トンネル絶縁膜（厚さ1nmのMgO膜）の成膜条件]

プロセスガス：アルゴン = 100 sccm

成膜雰囲気圧力：1.0 Pa

RFパワー：500 W

40

## [第2磁性材料層（厚さ4nmのCo-Fe-B合金）の成膜条件]

プロセスガス：アルゴン = 50 sccm

成膜雰囲気圧力：0.3 Pa

DCパワー：200 W

## [キャップ層（厚さ5nmのTa層）の成膜条件]

プロセスガス：アルゴン = 100 sccm

成膜雰囲気圧力：0.6 Pa

DCパワー：200 W

## [接続層（厚さ80nmのTiN層）の成膜条件]

プロセスガス：アルゴン = 30 sccm

50

反応性ガス：N<sub>2</sub> = 70 sccm

成膜雰囲気圧力 : 0 . 7 P a

D C パワー : 1 0 k W

## 【 0 0 5 3 】

## [ 工程 - 1 2 0 ]

次いで、第 2 磁性材料層 5 3 上にマスク層 6 3 を形成する。具体的には、接続層 6 2 上にマスク層 6 3 を形成する。より具体的には、接続層 6 2 の上に、マスク層 6 3 を形成するためには、厚さ 5 0 n m の Si O<sub>2</sub> 層を、以下に例示する条件のバイアス高密度プラズマ C V D ( H D P - C V D ) 法にて形成する。次いで、Si O<sub>2</sub> 層上にパターニングされたレジスト層を形成して、リソグラフィ技術及びドライエッチング法にて Si O<sub>2</sub> 層をエッチングしてパターニングされたマスク層 6 3 を得た後、レジスト層を酸素プラズマアッシング処理及び有機洗浄後処理にて除去する。こうして、図 3 の ( A ) に示す構造を得ることができる。10

## 【 0 0 5 4 】

[ マスク層を構成する Si O<sub>2</sub> 層の成膜条件 ]

プロセスガス : モノシラン / O<sub>2</sub> / アルゴン = 6 0 sccm / 1 2 0 sccm / 1 3 0 sccm

R F パワー

トップ : 1 . 5 k W

サイド : 3 k W

[ マスク層を構成する Si O<sub>2</sub> 層のドライエッチング条件 ]

使用ガス : C<sub>4</sub>F<sub>8</sub> / CO / Ar / O<sub>2</sub> = 1 0 sccm / 5 0 sccm / 2 0 0 sccm / 4 sccm

R F パワー : 1 k W

圧力 : 5 P a

温度 : 2 0 ° C20

## 【 0 0 5 5 】

## [ 工程 - 1 3 0 ]

次に、マスク層 6 3 をマスクとして用いて、接続層 6 2 を、以下に例示する条件の R I E 法に基づきパターニングする ( 図 3 の ( B ) 参照 )。

## 【 0 0 5 6 】

## [ 接続層のエッチング条件 ]

使用ガス : Cl<sub>2</sub> / BC l<sub>3</sub> / N<sub>2</sub> = 6 0 sccm / 8 0 sccm / 1 0 sccm

ソースパワー : 1 k W

バイアスパワー : 1 5 0 W

圧力 : 1 P a30

## 【 0 0 5 7 】

## [ 工程 - 1 4 0 ]

その後、マスク層 6 3 で覆われていない第 2 磁性材料層 ( 記録層 ) 5 3 の部分を、厚さ方向に一部分、エッチングする。具体的には、キャップ層 6 1 と第 2 磁性材料層 ( 記録層 ) 5 3 の半分の厚さ程度を、以下に例示する条件のイオンミーリング法に基づきエッチングする ( 図 3 の ( C ) 及び図 4 の ( A ) 参照 )。

## 【 0 0 5 8 】

## [ キャップ層と第 2 磁性材料層のエッチング条件 ]

使用ガス : Ar = 1 2 sccm

圧力 : 0 . 0 3 P a

加速電圧 : 4 0 0 V

加速電流 : 1 0 0 m A

減速電圧 : - 3 0 0 V

ビーム角度 : - 1 2 °

## 【 0 0 5 9 】

ここで、第 2 磁性材料層 5 3 のエッチング工程では、ウエハ全面において、第 2 磁性材料層 5 3 の一部が残存するようにエッチング条件を調整することが望ましい。但し、部分40

10

20

30

40

50

的に、下層であるトンネル絶縁膜 5 2 が露出したり、キャップ層 6 1 が残ったりしても、特段に問題が生じる訳ではない。また、キャップ層 6 1 及び第 2 磁性材料層 5 3 を、イオンミーリング法によってパターニングする代わりに、RIE 法に基づきパターニングしてもよい。

#### 【0060】

##### [工程 - 150]

次いで、マスク層 6 3 で覆われていない第 2 磁性材料層（記録層）5 3 の部分 5 3' を、以下に例示する条件のプラズマ酸化法に基づき酸化する第 2 磁性材料層無効化処理を行う（図 4 の（B）参照）。

#### 【0061】

10

##### [プラズマ酸化の条件]

R F パワー : 200 W

使用ガス : Ar / O<sub>2</sub> = 50 sccm / 150 sccm

#### 【0062】

##### [工程 - 160]

その後、酸化された第 2 磁性材料層（記録層）5 3 の部分 5 3' を、以下に例示する条件の水素プラズマ法（H<sub>2</sub> プラズマ還元処理法）に基づき還元処理を実行する（図 4 の（C）参照）。尚、酸化された第 2 磁性材料層（記録層）5 3 の部分 5 3' 中の水素原子の量は、例えば、原子プローブを用いて測定することが可能である。

#### 【0063】

20

##### [H<sub>2</sub> プラズマ還元処理の条件]

R F パワー : 200 W

基板温度 : 350 度

導入ガス : H<sub>2</sub> = 500 sccm

圧力 : 8 × 10<sup>2</sup> Pa

#### 【0064】

##### [工程 - 170]

次いで、第 2 磁性材料層（記録層）5 3 の部分 5 3' 及びマスク層 6 3 上に、リソグラフィ技術に基づきレジスト層（図示せず）を形成した後、このレジスト層をエッティング用マスクとして用いて、第 2 磁性材料層（記録層）5 3 の部分 5 3' 、トンネル絶縁膜 5 2 、第 1 磁性材料層 5 1 及び第 1 の配線 4 1 をパターニング（エッティング）し、レジスト層を除去する。次に、全面に、プラズマ CVD 法にて SiN から成る上層絶縁層 3 0 を成膜した後、上層絶縁層 3 0 及びマスク層 6 3 を化学的機械的研磨法（CMP 法）にて平坦化し、接続層 6 2 を露出させる。その後、周知の方法に基づき、上層絶縁層 3 0 上に第 2 の配線 4 2 を形成する。こうして、図 1 に示した構造の不揮発性メモリ素子を得ることができる。

30

#### 【0065】

実施例 1 の不揮発性メモリ素子の製造方法にあっては、マスク層 6 3 で覆われていない第 2 磁性材料層 5 3 の部分 5 3' を酸化し、次いで、酸化された第 2 磁性材料層 5 3 の部分 5 3' を還元する。即ち、第 2 磁性材料層 5 3 をエッティング法等によってパターニングして不要な部分を全て除去するのではなく、酸化によって第 2 磁性材料層 5 3 の有する機能（導電性、磁気特性等）を劣化させる。従って、機能を保持した第 2 磁性材料層の領域にダメージが生じ難い。しかも、酸化された第 2 磁性材料層 5 3 の部分 5 3' を還元するので、不揮発性メモリ素子の酸化工程後の製造工程におけるプロセス温度等により、第 2 磁性材料層 5 3 の部分 5 3' に残存した過剰な酸素が熱拡散し、第 2 磁性材料層 5 3 にダメージを与えてしまうといった問題が生じることもない。即ち、酸素に起因した機能領域の劣化発生を防止することができる。それ故、不揮発性メモリ素子の読出し抵抗値のバラツキを低減することができるため、高読出し抵抗値と低読出し抵抗値の分離幅を十分に取ることができ、短絡が生じた不揮発性メモリ素子の発生を非常に低く抑えることが可能となる。従って、高特性、長期信頼性を有する不揮発性メモリ素子を提供することができる

40

50

。

## 【0066】

図5の(A)及び(B)に、実施例1の不揮発性メモリ素子、並びに、従来の不揮発性メモリ素子(第2磁性材料層、トンネル絶縁膜及び第1磁性材料層をイオンミーリング法にてパターニングして得られた不揮発性メモリ素子)のそれぞれにおける、高読出し抵抗値(図5の(A)及び(B)では、「A」にて示す)及び低読出し抵抗値(図5の(A)及び(B)では、「B」にて示す)の測定結果を示す。尚、横軸は、抵抗値(単位:任意)であり、縦軸は、テストに供した不揮発性メモリ素子における百分率(%)を対数で表示したものである。図5の(A)及び(B)から、実施例1の不揮発性メモリ素子は、従来の不揮発性メモリ素子よりも、高読出し抵抗値と低読出し抵抗値の分離幅が小さいものの割合が小さい。即ち、短絡や電流リークの発生が少なくなっている。10

## 【0067】

尚、第1磁性材料層51を磁化参照層から構成し、第2磁性材料層53を記録層から構成したが、代替的に、第1磁性材料層51を記録層から構成し、第2磁性材料層53を磁化参照層から構成することもできる。次に述べる実施例2においても同様である。

## 【実施例2】

## 【0068】

実施例2は、実施例1の変形である。実施例1にあっては、第1の態様の不揮発性メモリ素子を、面内磁化方式のスピン注入型磁気抵抗効果素子とした。一方、実施例2にあっては、垂直磁化方式のスピン注入型磁気抵抗効果素子とした。実施例2にあっては、加工の容易性、第2磁性材料層(記録層)における磁化容易軸の方向の均一性を確保するといった観点から、第2磁性材料層(記録層)における酸化されていない領域の平面形状を円形とした。20

## 【0069】

具体的には、積層構造体の構成を以下のとおりとする。

## 【0070】

## 第2磁性材料層(記録層)

厚さ約1nmのCoFeB層と厚さ約3nmのTbFeCo層の積層構造

トンネル絶縁膜

厚さ1.0nmのMgO膜

## 第1磁性材料層(磁化参照層)

厚さ約1nmのCoFeB層と厚さ約30nmのGdFeCo層の積層構造

## 【0071】

尚、第1磁性材料層、第2磁性材料層は、例えば、以下に例示する条件のスパッタリング条件にて成膜することができる。

## 【0072】

## [第1磁性材料層]

プロセスガス：アルゴン = 50 sccm

成膜雰囲気圧力：0.3 Pa

D C パワー：100 W

## [第2磁性材料層]

プロセスガス：アルゴン = 50 sccm

成膜雰囲気圧力：0.3 Pa

D C パワー：200 W

## 【0073】

実施例2においても、情報を記録する機能を担う記録層(第2磁性材料層53)と、磁化方向が固定されており、スピンフィルターとして機能する磁化参照層(第1磁性材料層51を構成する)が、トンネル絶縁膜52を介して積層された構造を有し、スピン偏極電流は膜面に垂直に流れる(図6の(A)参照)。第2磁性材料層53は、適当な磁気異方性により2以上の複数の磁化方向(例えば、図6の(A)に垂直方向の矢印にて示す2方

10

20

30

40

50

向である上向きの方向及び下向きの方向)を取ることができ、各磁化方向は記録される情報に対応する。第2磁性材料層53は、上向きの方向及び下向きの方向に平行な磁化容易軸を有し、上向きの方向及び下向きの方向に直交する方向に磁化困難軸を有している。磁化参照層51Aは、その磁化方向が固定されている。そして、第2磁性材料層53においては、スピン偏極電流の流れる方向により、その磁化の方向が、上向き(第2の配線42に向かう方向)又は下向き(第1の配線41に向かう方向)に変えられる。磁化参照層51A<sub>1</sub>, 51A<sub>2</sub>を、第2磁性材料層53の上下に、トンネル絶縁膜52<sub>1</sub>, 52<sub>2</sub>を介して配置して、スピン注入磁化反転の効率を向上させたダブル・スピニルフィルター構造も知られている(図6の(B)参照)。

## 【0074】

10

以上の点を除き、実施例2の不揮発性メモリ素子の構成、構造、実施例2の不揮発性メモリ素子の製造方法は、実施例1の不揮発性メモリ素子の構成、構造、実施例1の不揮発性メモリ素子の製造方法と同様とすることができるので、詳細な説明は省略する。

## 【実施例3】

## 【0075】

実施例3は、本発明の第2の態様に係る不揮発性メモリ素子の製造方法に関する。実施例3の不揮発性メモリ素子の製造方法にて得られた第2の態様の不揮発性メモリ素子における抵抗変化層の断面構造を概念的に示す図7の(A)に示し、等価回路図を図7の(B)に示す。実施例3の不揮発性メモリ素子において、抵抗変化層80は、金属を含むイオン導電体から成る。また、実施例3の不揮発性メモリ素子には、選択用トランジスタTRが備えられている。尚、実施例3の不揮発性メモリ素子における選択用トランジスタの構成、構造は、実施例1の不揮発性メモリ素子における選択用トランジスタの構成、構造と同様とすることができるし、実施例3の不揮発性メモリ素子と選択用トランジスタとの配置関係も、実施例1の不揮発性メモリ素子と選択用トランジスタとの配置関係と同様とすることができる。即ち、選択用トランジスタを含む実施例3の不揮発性メモリ素子の構成、構造は、不揮発性メモリ素子の構成、構造が実施例1と異なる点を除き、選択用トランジスタを含む実施例1の不揮発性メモリ素子の構成、構造と同様とすることができる。

20

## 【0076】

実施例3において、抵抗変化層80は、第1電極(下部電極)71と第2電極(上部電極)72の間に挟まれており、第1電極側から、高抵抗層81及びイオン源層82から構成されている。ここで、イオン源層82は、金属を含むイオン導電体から成る。また、イオン源層82の上には、キャップ層91及び接続層(トップ層)92が形成されている。尚、キャップ層と接続層とを機能的に兼ねる層を形成してもよい。第1電極(下部電極)71は選択用トランジスタTRのソース/ドレイン領域14Bに電気的に接続されている。

30

## 【0077】

イオン源層82は、Cu、Ag、Znから選ばれるいずれかの金属元素(原子)と、Te、S、Seといったカルコゲナイト元素(原子)から選ばれるいずれかの元素(原子)とが含まれている導電性又は半導電性の薄膜(例えば、GeSbTe、GeTe、GeSe、GeS、SiGeTe、SiGeSbTeから成る薄膜や、これらの薄膜と、例えば、Ag、Ag合金、Cu、Cu合金、Zn、Zn合金から成る薄膜の積層構造)から成る。そして、一方の電極に、イオン源層82に含まれる金属原子が含まれている。ここで、Cu、Ag、Znは、陽イオンとなったときに、イオン源層82内や高抵抗層81内を移動し易い元素(原子)である。一方、Te、S、Seは、抵抗変化層80に電流を流したとき、イオン源層82の抵抗値を高抵抗層81の抵抗値よりも小さくすることが可能な元素(原子)である。イオン源層82において、陽イオンとなる元素としてCu等を用い、更に、カルコゲナイト元素(原子)としてTe等を用いた場合、抵抗変化層80に電流を流したとき、イオン源層82の抵抗値を高抵抗層81の抵抗値よりも十分に小さくすることができ、しかも、抵抗値が大きく変化する部分をイオン源層82に限定することができるので、メモリ動作の安定性を向上させることができる。イオン源層82は、2層以上の

40

50

積層構造から構成されていてもよい。例えば、2層から成る場合、Cu、Ag、Znから選ばれるいずれかの金属元素（原子）を含まれている薄層と、Te、S、Seといったカルコゲナイト元素（原子）から選ばれるいずれかの元素（原子）が含まれている導電性又は半導電性の薄膜の2層構成であって、高抵抗層側の薄膜は金属元素（原子）が含まれている薄層から成る構成とすることができる。

#### 【0078】

実施例3の不揮発性メモリ素子にあっては、2つの電極間に電圧が印加されると、一方の電極に含まれる金属原子がイオン源層82の中にイオンとして拡散し、イオン源層82の抵抗値あるいは容量値等の電気特性が変化するので、その電気特性の変化を利用して、メモリ機能を発現させることができる。あるいは又、イオン源層82中の金属原子がイオン化して高抵抗層81を拡散していき、マイナスの電極側で電子と結合して析出したり、あるいは、高抵抗層81の内部に拡散した状態で留まる。その結果、高抵抗層81の内部に、金属原子を多量に含む電流パスが形成され、若しくは、高抵抗層81の内部に、金属原子による欠陥が多数形成され、高抵抗層81の抵抗値が低くなる。このとき、イオン源層82の抵抗値は、高抵抗層81の情報（データ）記憶前の抵抗値に比べて元々低いので、高抵抗層81の抵抗値が低くなることにより、不揮発性メモリ素子全体の抵抗値も低くなり、メモリ機能を発現させることができる。高抵抗層81は、金属材料、希土類元素、これらの混合物の酸化物あるいは窒化物、半導体材料から構成することができる。第1電極（下部電極）71及び第2電極（上部電極）72は、例えば、アルミニウム（Al）、銅（Cu）、タンゲステン（W）等の金属材料から構成することができる。

10

20

#### 【0079】

以下、実施例3の不揮発性メモリ素子の製造方法を、図8の（A）、（B）、図9の（A）、（B）、図10を参照して説明する。尚、これらの図面において、第1電極71よりも下に位置する不揮発性メモリ素子の構成要素（選択用トランジスタTR等）の図示は省略した。

30

#### 【0080】

##### [工程 - 300]

先ず、実施例1と同様に、選択用トランジスタTRを半導体基板に形成し、下層絶縁層23の上に、接続孔22に接続された第1電極71を、スパッタリング法に基づき形成する。尚、第1電極71は、厚さ20nmのWN（窒化タンゲステン）層から成る。

30

#### 【0081】

##### [工程 - 310]

その後、第1電極71上に、厚さ3nmのガドリニウム（Gd）酸化物から成る高抵抗層81、厚さ10nmのCu及びTeを含むイオン源層82、厚さ5nmのタンゲステン（W）から成るキャップ層91、厚さ40nmのTiN（窒化チタン）から成る接続層92を、順次、スパッタリング法にて形成する。

40

#### 【0082】

##### [工程 - 320]

次いで、実施例1の[工程 - 120]と同様にして、抵抗変化層80上にマスク層93を形成する（図8の（A）参照）。具体的には、接続層92上にマスク層93を形成する。その後、マスク層93をマスクとして用いて、接続層92をRIE法に基づきパターニングする（図8の（B）参照）。

40

#### 【0083】

##### [工程 - 330]

その後、マスク層93で覆われていない抵抗変化層80の部分82'を酸化し（抵抗変化層無効化処理）、次いで、酸化された抵抗変化層80の部分82'を還元する。

#### 【0084】

具体的には、先ず、キャップ層91と、イオン源層82の半分程度をイオンミーリング法に基づきエッチングする（図9の（A）参照）。ここで、イオン源層82のエッチング工程では、ウェハ全面において、イオン源層82の一部が残存するように加工条件を調整

50

することが望ましい。但し、部分的に、下層である高抵抗層 8 1 が露出したり、キャップ層 9 1 が残ったりしても、特段に問題が生じる訳ではない。また、キャップ層 9 1 とイオン源層 8 2 を、イオンミーリング法によってパターニングする代わりに、R I E 法に基づきパターニングしてもよい。

#### 【 0 0 8 5 】

次に、イオン源層 8 2 の残存層 8 2' を、以下に例示する条件のプラズマ酸化法に基づき酸化させる（図 9 の（B）参照）。

#### 【 0 0 8 6 】

##### [ イオン源層のプラズマ酸化 ]

R F パワー : 2 0 0 W

使用ガス : Ar / O<sub>2</sub> = 5 0 / 1 5 0 sccm

10

#### 【 0 0 8 7 】

その後、イオン源層 8 2 の残存層 8 2' に対して還元処理を実行する（図 10 参照）。具体的には、以下に例示する水素プラズマ法（H<sub>2</sub> プラズマ還元処理法）を実行する。

#### 【 0 0 8 8 】

##### [ イオン源層の残存層に対する H<sub>2</sub> プラズマ還元処理 ]

R F パワー : 2 0 0 W

基板温度 : 3 5 0 ° C

導入ガス : H<sub>2</sub> = 5 0 0 sccm

圧力 : 8 × 1 0<sup>2</sup> Pa

20

#### 【 0 0 8 9 】

##### [ 工程 - 3 4 0 ]

次いで、実施例 1 の [ 工程 - 1 7 0 ] と同様にして、イオン源層 8 2 の残存層 8 2' 及びマスク層 9 3 上に、リソグラフィ技術に基づきレジスト層（図示せず）を形成した後、このレジスト層をエッチング用マスクとして用いて、イオン源層 8 2 の残存層 8 2' 及び第 1 電極 7 1 をパターニング（エッチング）し、レジスト層を除去する。次に、全面に、プラズマ C V D 法にて Si N 層から成る上層絶縁層 3 0 を成膜した後、上層絶縁層 3 0 及びマスク層 9 3 を化学的機械的研磨法（C M P 法）にて平坦化し、接続層 9 2 を露出させる。その後、上層絶縁層 3 0 上に、周知の方法に基づき、第 2 電極（上部電極）7 2 を形成する。こうして、実施例 3 の不揮発性メモリ素子を得ることができる。

30

#### 【 0 0 9 0 】

実施例 3 の不揮発性メモリ素子の製造方法にあっては、マスク層 9 3 で覆われていない抵抗変化層 8 0 の部分 8 2' を酸化し、次いで、酸化された抵抗変化層 8 0 の部分 8 2' を還元する。即ち、抵抗変化層 8 0 をエッチング法等によってパターニングして不要な部分を除去するのではなく、酸化によって抵抗変化層 8 0 の有する機能（導電性等）を劣化させる。従って、機能を保持した抵抗変化層 8 0 の領域にダメージが生じ難い。しかも、酸化された抵抗変化層 8 0 の部分 8 2' を還元するので、不揮発性メモリ素子の酸化工程後の製造工程におけるプロセス温度等により、抵抗変化層の部分 8 2' に残存した過剰な酸素が熱拡散し、抵抗変化層 8 0 にダメージを与えるといった問題が生じることもない。即ち、酸素に起因した機能領域の劣化発生を防止することができる。それ故、不揮発性メモリ素子の抵抗値変化のバラツキを低減することができ、高特性、長期信頼性を有する不揮発性メモリ素子を提供することができる。

40

#### 【 0 0 9 1 】

次に、実施例 3 の不揮発性メモリ素子の動作について説明する。

#### 【 0 0 9 2 】

##### [ 情報の書き込み ]

第 2 電極 7 2 に正電位（+ 電位）を印加すると共に、第 1 電極 7 1 に負電位（- 電位）またはゼロ電位を印加すると、イオン源層 8 2 から金属原子がイオン化して高抵抗層 8 1 内を拡散していく、第 1 電極側で電子と結合して析出したり、あるいは、高抵抗層 8 1 の内部に拡散した状態で留まる。その結果、高抵抗層 8 1 の内部に金属原子を多量に含む電

50

流パスが形成され、若しくは、高抵抗層81の内部に金属原子による欠陥が多数形成され、高抵抗層81の抵抗値が低くなる。このとき、イオン源層82の抵抗値は、高抵抗層81の情報（データ）記録前の抵抗値に比べて元々低いので、高抵抗層81の抵抗値が低くなることにより、不揮発性メモリ素子全体の抵抗値も低くなる。つまり、不揮発性メモリ素子がオン状態（導通状態）となる。このときの不揮発性メモリ素子全体の抵抗が書き込み抵抗となる。

#### 【0093】

その後、第1電極71及び第2電極72への電圧の印加を中止し、不揮発性メモリ素子に電圧が印加されていない状態とすると、不揮発性メモリ素子の抵抗値が低くなった状態で保持される。このようにして、情報（データ）の記録（書き込み）が行われる。10

#### 【0094】

##### [情報の消去]

第2電極72に負電位（-電位）を印加すると共に、下部電極71に正電位（+電位）又はゼロ電位を印加すると、高抵抗層81内に形成されていた電流パス、あるいは、不純物準位を構成する金属原子がイオン化して、高抵抗層81内を移動してイオン源層82へと戻る。その結果、高抵抗層81内から電流パス若しくは欠陥が消滅して、高抵抗層81の抵抗値が高くなる。このとき、イオン源層82の抵抗値は元々低いので、高抵抗層81の抵抗値が高くなることにより、不揮発性メモリ素子全体の抵抗値も高くなる。つまり、不揮発性メモリ素子がオフ状態（非導通状態）となる。このときの不揮発性メモリ素子全体の抵抗が消去抵抗となる。20

#### 【0095】

その後、第1電極71及び第2電極72への電圧の印加を中止し、不揮発性メモリ素子に電圧が印加されていない状態とすると、不揮発性メモリ素子の抵抗値が高くなった状態で保持される。このようにして、記録された情報（データ）の消去が行われる。

#### 【0096】

そして、このような過程を繰返し行うことにより、不揮発性メモリ素子に情報の記録（書き込み）と、記録された情報の消去を繰り返し行うことができる。

#### 【0097】

このとき、例えば、不揮発性メモリ素子全体の抵抗が書き込み抵抗となっている状態（抵抗値の低い状態）を「1」の情報に、不揮発性メモリ素子全体の抵抗が消去抵抗となっている状態（抵抗値の高い状態）を「0」の情報に、それぞれ対応させると、第2電極72に正電位（+電位）を印加することによって、不揮発性メモリ素子に記憶させた情報を「0」から「1」に変えることができ、また、第2電極72に負電位（-電位）を印加することによって、不揮発性メモリ素子に記憶させた情報を「1」から「0」に変えることができる。30

#### 【0098】

このように、実施例3にあっては、第1電極71、高抵抗層81、イオン源層82、及び、第2電極72を、この順に積層しただけの簡素な構造から成る不揮発性メモリ素子を用いて、情報の記録及び消去を行うようにしたので、不揮発性メモリ素子を微細化していった場合であっても、情報の記録及び消去を容易に行うことができる。また、電力の供給がなくとも、抵抗変化層80の抵抗値を保持することができるので、情報を長期に亘って保存することができる。また、読み出しによって抵抗変化層80の抵抗値が変化することはなく、フレッシュ動作を行う必要がないので、その分だけ消費電力を低減することができる。40

#### 【実施例4】

#### 【0099】

実施例4は、実施例3の変形である。実施例4にあっては、不揮発性メモリ素子を、相変化型メモリ素子（P R A M）から構成した。即ち、実施例4にあっては、抵抗変化層をカルコゲナイト系材料から構成した。そして、メモリ部である抵抗変化層を構成する相変化材料がアモルファス状態と結晶状態とで電気抵抗が数桁違うことを利用して、不揮発性

メモリ素子として動作させる。具体的には、メモリ部に短時間、パルス状の大電流（例えば、200マイクロアンペア，20ナノ秒）を流した後、急冷すると、抵抗変化層を構成する相変化材料はアモルファス状態となり、高抵抗を示す。一方、抵抗変化層に比較的長時間、パルス状の小電流（例えば、100マイクロアンペア，100ナノ秒）を流した後、徐冷すると、抵抗変化層を構成する相変化材料は結晶状態となり、低抵抗を示す。

#### 【0100】

尚、抵抗変化層をカルコゲナイト系材料から構成する代わりに、例えば、電界誘起巨大抵抗変化効果（CER効果）を有する材料、例えば、3元系ペロブスカイト型遷移金属酸化物（ $\text{PrCaMnO}_3$ や $\text{SrTiO}_3$ ）や2元系遷移金属酸化物（ $\text{CrO}$ 、 $\text{NiO}$ 、 $\text{CuO}$ 、 $\text{TiO}_2$ 、 $\text{Fe}_3\text{O}_4$ ）から構成することもできる。10

#### 【0101】

例えば、抵抗変化層を $\text{TiO}_2$ から構成する場合、不揮発性メモリ素子に最初に大きな電圧を印加する「フォーミング」過程を実行すると、抵抗変化層中に抵抗が低い電流路（フィラメント）が局的に複数形成される。「リセット」過程では、印加電圧によってフィラメントの陽極側（正の電圧を加える側）が酸化されて抵抗値が上昇し、高抵抗状態になる。その結果、不揮発性メモリ素子全体の抵抗値も高くなる。つまり、不揮発性メモリ素子がオフ状態（非導通状態）となる。尚、このときの不揮発性メモリ素子全体の抵抗が消去抵抗となる。「セット」過程にあっては、フィラメントの陽極側がジュール熱によって還元されて再び抵抗値が下がり、低抵抗状態になる。その結果、不揮発性メモリ素子全体の抵抗値も低くなる。つまり、不揮発性メモリ素子がオン状態（導通状態）となる。尚、このときの不揮発性メモリ素子全体の抵抗が書き込み抵抗となる。そして、このような過程を繰返し行うことにより、不揮発性メモリ素子に情報の記録（書き込み）と、記録された情報の消去を繰り返し行うことができる。20

#### 【0102】

以上、本発明を好ましい実施例に基づき説明したが、本発明はこれらの実施例に限定されるものではない。実施例において説明した各種の積層構造、使用した材料等は例示であり、適宜、変更することができる。

#### 【0103】

実施例1～実施例2の不揮発性メモリ素子にあっては、磁化参照層51Aとトンネル絶縁膜52との間に高分極率層を設けてもよいし、記録層53とトンネル絶縁膜52との間に高分極率層を設けてもよい。高分極率層は、例えば、Fe、Co及びNiから成る群から選択された少なくとも1種類の元素を含む磁性金属層から成る。磁化参照層51Aとトンネル絶縁膜52との間に設けられた高分極率層は、磁化参照層51Aと交換結合する。一方、記録層53とトンネル絶縁膜52との間に設けられた高分極率層は、記録層53と交換結合する。このように高分極率層を設けることで、磁気抵抗比を上昇させることができる。尚、通常、高分極率層は単層では面内磁化となるため、垂直磁化方式を採用する場合、垂直磁化の安定性を損なわないように、磁化参照層51Aや記録層53との磁気的な膜厚比を調整する必要がある。30

#### 【符号の説明】

#### 【0104】

TR・・・選択用トランジスタ、10・・・半導体基板、11・・・素子分離領域、12・・・ゲート電極、13・・・ゲート絶縁膜、14A、14B・・・ソース／ドレイン領域、15・・・コンタクトホール、16・・・センス線、21、23・・・下層絶縁層、22・・・接続孔、30・・・上層絶縁層、31・・・上層絶縁層、41・・・第1の配線、42・・・第2の配線、50・・・積層構造体、51・・・第1磁性材料層、51A・・・磁化参照層、51B・・・反強磁性体層、52・・・トンネル絶縁膜、53・・・第2磁性材料層、53'・・・第2磁性材料層の酸化／還元された部分、61、91・・・キャップ層、62、92・・・接続層、63、93・・・マスク層、71・・・第1電極（下部電極）、72・・・第2電極（上部電極）、80・・・抵抗変化層、81・・・高抵抗層、82・・・イオン源層、82'・・・抵抗変化層の酸化／還元された部分4050

## 【図1】

## 【図2】

## 【図3】

## 【図4】

【図6】

【図7】

【図8】

【図9】

## 【図 10】

【図 10】

[工程-330] (続き)

【図5】

【図5】

---

フロントページの続き

| (51) Int.Cl.              | F I                          | テーマコード(参考) |

|---------------------------|------------------------------|------------|

| H 01 L 45/00<br>(2006.01) | H 01 L 45/00                 | A          |

| H 01 L 49/00<br>(2006.01) | H 01 L 45/00<br>H 01 L 49/00 | Z<br>Z     |

(72)発明者 田渕 清隆

東京都港区港南1丁目7番1号 ソニー株式会社内

F ターム(参考) 4M119 AA17 AA19 BB01 CC05 DD05 DD06 DD08 DD09 DD10 DD17

DD24 DD25 DD33 DD45 EE22 EE27 FF05 FF13 FF15 FF17

JJ02 JJ03 JJ04 JJ12 JJ20

5F083 FZ10 GA11 GA27 JA35 JA36 JA37 JA38 JA39 JA40 JA56

JA60 PR04 PR12 PR18 PR40

5F092 AA11 AA15 AB08 AC12 AD23 AD25 BB04 BB10 BB17 BB22

BB23 BB24 BB25 BB33 BB34 BB35 BB36 BB42 BB43 BB44

BB45 BB53 BB55 BB81 BB82 BC04 BC07 BC12 BC13 BC22

BC42 BC46 CA02 CA03 CA08 CA15 CA40