(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6183886号

(P6183886)

(45) 発行日 平成29年8月23日(2017.8.23)

(24) 登録日 平成29年8月4日(2017.8.4)

(51) Int.Cl.

F 1

H02M 3/28 (2006.01)

H02M 7/48 (2007.01)H02M 3/28

H02M 7/48H

S

請求項の数 17 (全 14 頁)

(21) 出願番号 特願2013-77309 (P2013-77309)

(22) 出願日 平成25年4月3日 (2013.4.3)

(65) 公開番号 特開2013-220012 (P2013-220012A)

(43) 公開日 平成25年10月24日 (2013.10.24)

審査請求日 平成28年3月24日 (2016.3.24)

(31) 優先権主張番号 13/440,110

(32) 優先日 平成24年4月5日 (2012.4.5)

(33) 優先権主張国 米国(US)

(73) 特許権者 390041542

ゼネラル・エレクトリック・カンパニー

アメリカ合衆国、ニューヨーク州 123

45、スケネクタディ、リバーロード、1

番

(74) 代理人 100137545

弁理士 荒川 聰志

(74) 代理人 100105588

弁理士 小倉 博

(74) 代理人 100129779

弁理士 黒川 俊久

(74) 代理人 100113974

弁理士 田中 拓人

最終頁に続く

(54) 【発明の名称】圧電負荷を駆動するためのシステム及びそれを製作する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

直流(DC)電圧源と、

前記DC電圧源に結合された一次側を持つと共に二次側を持つ第1の両方向DC-DC変換器であって、更に当該第1の両方向DC-DC変換器の前記一次側の第1の電圧から当該第1の両方向DC-DC変換器の前記二次側の第2の電圧への変換を制御するように構成された第1の制御信号を受け取るように構成されている制御入力を持つ第1の両方向DC-DC変換器と、

前記DC電圧源に結合された一次側を持つと共に前記第1の両方向DC-DC変換器の前記二次側に結合された二次側を持つ第2の両方向DC-DC変換器であって、更に当該第2の両方向DC-DC変換器の前記一次側の第1の電圧から当該第2の両方向DC-DC変換器の前記二次側の第3の電圧への変換を制御するように構成された第2の制御信号を受け取るように構成されている制御入力を持つ第2の両方向DC-DC変換器と、

前記第1及び第2の両方向DC-DC変換器に結合されていて、交流電圧源により生成された基準信号に基づいて前記第1及び第2の制御信号を発生し且つ前記第1及び第2の制御信号を前記第1及び第2の両方向DC-DC変換器にそれぞれ供給するように構成された制御システムと、

を有し、

前記第1及び第2の両方向DC-DC変換器が前記第1の電圧を昇圧することができ、前記第2の制御信号が前記第1の制御信号と相補的であり、

10

20

前記第2及び第3の電圧の間の電圧差が出力電圧を構成し、且つ

前記出力電圧が前記第1の制御信号の増幅により構成され、

前記制御システムは、

関数発生器及びルックアップ・テーブルの内の方により決定された複数のディジタル値からアナログ信号を生成するディジタル・アナログ変換器と、

前記アナログ信号をオーバーサンプリングするように構成されている、シグマ・デルタ変調器であって、前記オーバーサンプリングは、前記アナログ信号が生成される際に生じたアーティファクトを、より高い周波数へシフトする、前記シグマ・デルタ変調器と、

前記シグマ・デルタ変調器の出力を濾波して不所望の周波数成分を除去するように構成されている、フィルタと、

濾波された前記出力から前記第1及び第2の制御信号を生成するための変調器と、

を備えることを特徴とする駆動システム。

【請求項2】

前記駆動システムは更に、第1の端子及び第2の端子を持つリアクタンス負荷を有しており、この場合、

前記第1の両方向DC-D C変換器が、前記リアクタンス負荷の前記第1の端子に結合された第1の二次側端子、及び第2の二次側端子を有し、

前記第2の両方向DC-D C変換器が、前記リアクタンス負荷の前記第2の端子に結合された第1の二次側端子、及び前記第1の両方向DC-D C変換器の前記第2の二次側端子に結合された第2の二次側端子を有している、請求項1記載の駆動システム。

【請求項3】

前記リアクタンス負荷は圧電負荷を有している、請求項2記載の駆動システム。

【請求項4】

前記第1の両方向DC-D C変換器は更に、前記DC電圧源に結合された一対の一次側端子を有し、また

前記第2の両方向DC-D C変換器は更に、前記DC電圧源に結合された一対の一次側端子を有している、請求項2または3に記載の駆動システム。

【請求項5】

前記第1の両方向DC-D C変換器の前記第2の二次側端子は、前記第1の両方向DC-D C変換器の前記一対の一次側端子の内の方に且つ前記第2の両方向DC-D C変換器の前記一対の一次側端子の内の方に結合されている、請求項4記載の駆動システム。

【請求項6】

前記第1及び第2の両方向DC-D C変換器の各々は、

一次側巻線及び二次側巻線を持つ変圧器と、

前記一次側巻線に結合された第1のスイッチと、

前記二次側巻線に結合された第2のスイッチと、

を有している、請求項2乃至5のいずれかに記載の駆動システム。

【請求項7】

前記第1の両方向DC-D C変換器の前記二次側巻線が、前記リアクタンス負荷の前記第1の端子に結合され、

前記第2の両方向DC-D C変換器の前記二次側巻線が、前記リアクタンス負荷の前記第2の端子に結合され、更に

前記第1の両方向DC-D C変換器の前記第2のスイッチが、前記第2の両方向DC-D C変換器の前記第2のスイッチに結合されている、請求項6記載の駆動システム。

【請求項8】

前記出力電圧は、前記第1の制御信号の実質的に線形増幅により構成される、請求項1乃至7のいずれかに記載の駆動システム。

【請求項9】

前記第2の電圧は前記第1の制御信号の非線形増幅であり、また

前記第3の電圧は前記第1の制御信号の非線形増幅である、請求項8記載の駆動システム

ム。

【請求項 10】

前記変調器はパルス幅変調器である、請求項 1 乃至 9 のいずれかに記載の駆動システム。

【請求項 11】

前記制御システムは更に、前記第 2 及び第 3 の電圧に基づいてフィードバック電圧を測定するように構成されたフィードバック回路を有しており、また

前記制御システムは更に、前記第 2 及び第 3 の電圧が一組の目標の電圧値に実質的に一致するように前記フィードバック電圧に基づいて前記第 1 及び第 2 の制御信号を修正するように構成されている、請求項 1 乃至 10 のいずれかに記載の駆動システム。

10

【請求項 12】

前記制御システムは更に、前記出力電圧が前記第 1 及び第 2 の制御信号の線形昇圧変換を近似するように前記第 1 及び第 2 の制御信号を修正する様に構成された逆歪み制御器を有している、請求項 1 乃至 11 のいずれかに記載の駆動システム。

【請求項 13】

前記第 1 及び第 2 の両方向 D C - D C 変換器は單一段変換器を有している、請求項 1 乃至 12 のいずれかに記載の駆動システム。

【請求項 14】

低電圧側及び高電圧側を持つ第 1 の両方向 D C - D C 電圧変換器であって、第 1 の高電圧側端子及び第 2 の高電圧側端子を有し、また該第 1 の高電圧側端子の電圧を昇圧することができる第 1 の両方向 D C - D C 電圧変換器と、

20

低電圧側及び高電圧側を持つ第 2 の両方向 D C - D C 電圧変換器であって、第 1 の高電圧側端子、及び前記第 1 の電圧変換器の前記第 2 の高電圧側端子に結合された第 2 の高電圧側端子を有し、またその前記第 1 の高電圧側端子の電圧を昇圧することができる第 2 の両方向 D C - D C 電圧変換器と、

前記第 1 及び第 2 の両方向 D C - D C 電圧変換器の前記低電圧側に結合された直流 ( D C ) 電圧源と、

前記第 1 の両方向 D C - D C 電圧変換器の前記第 1 の高電圧側端子に結合され且つ前記第 2 の両方向 D C - D C 電圧変換器の前記第 1 の高電圧側端子に結合された圧電アクチュエータと、

30

前記第 1 及び第 2 の電圧変換器に結合された制御システムと、を有し、

前記制御システムは、第 1 の制御信号を前記第 1 の両方向 D C - D C 電圧変換器に供給するように構成されており、前記第 1 の制御信号は、前記第 1 の両方向 D C - D C 電圧変換器を制御して、前記第 1 の両方向 D C - D C 電圧変換器の前記低電圧側の電圧を前記第 1 の両方向 D C - D C 電圧変換器の前記高電圧側の第 1 の出力電圧へ変換するように構成されており、

前記制御システムはまた、第 2 の制御信号を前記第 2 の両方向 D C - D C 電圧変換器に供給するように構成されており、前記第 2 の制御信号は、前記第 1 の制御信号とは相補的であり、且つ前記第 2 の両方向 D C - D C 電圧変換器を制御して、前記第 2 の両方向 D C - D C 電圧変換器の前記低電圧側の電圧を前記第 2 の両方向 D C - D C 電圧変換器の前記高電圧側の第 2 の出力電圧へ変換し、交流電圧源により生成された基準信号に基づいて前記第 1 及び第 2 の制御信号を発生するように構成されており、

40

前記第 1 及び第 2 の出力電圧の電圧差は、前記第 1 の制御信号の増幅により構成される差電圧を構成し、

前記制御システムは、

関数発生器及びルックアップ・テーブルの内の方により決定された複数のディジタル値からアナログ信号を生成するディジタル - アナログ変換器と、

前記アナログ信号をオーバーサンプリングするように構成されている、シグマ・デルタ変調器であって、前記オーバーサンプリングは、前記アナログ信号が生成される際に生じたアーティファクトを、より高い周波数へシフトする、前記シグマ・デルタ変調器と、

50

前記シグマ・デルタ変調器の出力を濾波して不所望の周波数成分を除去するように構成されている、フィルタと、

濾波された前記出力から前記第1及び第2の制御信号を生成するための変調器と、

を備えることを特徴とする圧電駆動装置。

【請求項15】

前記第1及び第2の両方向DC-D C変換器の各々は、

低電圧側に一次側巻線及び高電圧側に二次側巻線を持つ変圧器と、

前記一次側巻線に結合された第1のスイッチと、

前記二次側巻線に結合された第2のスイッチと、

を有している、請求項1\_4記載の圧電駆動装置。

10

【請求項16】

前記圧電駆動装置は更に、前記第1及び第2の両方向DC-D C電圧変換器の前記第1の高電圧側端子に基づいて出力電圧を測定するように構成されたフィードバック回路を有しております、

前記制御システムは更に、前記出力電圧の波形が所望の波形に実質的に一致するようにフィードバック電圧に基づいて前記第1及び第2の制御信号を修正するように構成されている、請求項1\_4または1\_5に記載の圧電駆動装置。

【請求項17】

更に、前記第1及び第2の両方向DC-D C電圧変換器の前記低電圧側から前記第1及び第2の両方向DC-D C電圧変換器の前記高電圧側への電圧の変換が、前記第1及び第2の制御信号の線形昇圧変換を近似するように、前記第1及び第2の制御信号を修正するように構成された逆歪み制御器を有している請求項1\_4乃至1\_6のいずれかに記載の圧電駆動装置。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明の様々な実施形態は、一般的に云えば、圧電アクチュエータに関し、より詳しく云えば、圧電アクチュエータ用の駆動回路に関するものである。

【背景技術】

30

【0002】

圧電材料は、知られているように、電界の印加時に寸法を変える。この現象により、圧電材料は超小形電気機械システム(MEMS)装置内のアクチュエータとして用いることができる。例えば、このようなアクチュエータは、表面上の流体の流れに影響を及ぼすために流体のシンセティック・ジェット(synthetic jet)を発生するシンセティック・ジェット・アクチュエータに用いられている。典型的なシンセティック・ジェット・アクチュエータは、内室を画成するハウジングを有する。ハウジングの壁にはオリフィスが存在する。アクチュエータは更に、一連の流体渦が発生されてハウジングのオリフィスから外部環境内へ放出されるように、内室の容積を周期的に変化させるための機構を、ハウジングの中に又は周囲に含む。体積変化機構の例としては、往復運動中に流体をオリフィスの中へ及びそれから外へ動かすためにジェット・ハウジング内に配置されたピストン、或いは該ハウジングの1つの壁としての可撓性の隔壁が挙げられる。可撓性の隔壁は、典型的には、圧電アクチュエータ又は他の適切な手段によって作動される。

40

【0003】

典型的には、圧電アクチュエータは屢々適切な動作のために数十ボルト以上の電圧を必要とし、アクチュエータの種類によっては、周波数及び振幅を変えることのできるAC電圧を必要とする。圧電アクチュエータが携帯用、消費者用、航行用又は輸送用電子装置のような低電圧回路と結合される用途では、これらのアクチュエータを駆動するのが困難なことがある。例えば、圧電アクチュエータをAC電圧波形で駆動し又は電源から利用できる電圧よりも高いピーク電圧を持つ可変の値の電圧で駆動しようとするとき、既知の方法

50

はこの目的を達成するために、屢々、複雑で、効率の悪い、大きな及び／又は高価な駆動装置を使用している。これに加えて、圧電アクチュエータを使用する多くの用途では、使用する電力消費を最小にすることを要求しており、低い効率を持つ効率の悪い圧電アクチュエータ駆動装置は屢々このような最小電力消費要件を満たしていない。

【0004】

従って、低電圧源で動作させることができ且つ可変の周波数及び振幅を持つ制御可能な高電圧AC波形を効率よく生成することのできる高効率の駆動回路を提供するように、圧電負荷を駆動するためのシステムが必要である。

【先行技術文献】

【特許文献】

10

【0005】

【特許文献1】米国特許第8023297号

【発明の概要】

【0006】

本発明の一面によれば、駆動システムが提供される。本駆動システムは、直流(DC)電圧源と、前記DC電圧源に結合された一次側を持つと共に二次側を持つ第1の両方向DC-DC変換器であって、当該第1の両方向DC-DC変換器の前記一次側の第1の電圧から当該第1の両方向DC-DC変換器の前記二次側の第2の電圧への変換を制御するように構成された第1の制御信号を受け取るように構成されている制御入力を持つ第1の両方向DC-DC変換器とを有する。本駆動システムはまた、前記DC電圧源に結合された一次側を持つと共に前記第1の両方向DC-DC変換器の前記二次側に結合された二次側を持つ第2の両方向DC-DC変換器であって、当該第2の両方向DC-DC変換器の前記一次側の第1の電圧から当該第2の両方向DC-DC変換器の前記二次側の第3の電圧への変換を制御するように構成された第2の制御信号を受け取るように構成されている制御入力を持つ第2の両方向DC-DC変換器を有する。前記第1及び第2の両方向DC-DC変換器は前記第1の電圧を昇圧することができ、また前記第2の制御信号は前記第1の制御信号と相補的である。前記第2及び第3の電圧の間の電圧差は出力電圧を構成し、該出力電圧は前記第1の制御信号の増幅により構成される。

20

【0007】

本発明の別の面によれば、圧電駆動装置を製作する方法が提供される。本方法は、直流(DC)電圧源を第1の電圧変換器の低電圧側と第2の電圧変換器の低電圧側とに結合して、前記第1及び第2の電圧変換器により、前記DC電圧源からの電圧を昇圧することができる両方向DC-DC電圧変換器を構成する段階を有する。本方法はまた、前記第1の電圧変換器の高電圧側の第1の高電圧側端子を圧電アクチュエータの第1の側に結合する段階と、前記第2の電圧変換器の高電圧側の第1の高電圧側端子を前記圧電アクチュエータの第2の側に結合する段階と、前記第1の電圧変換器の第2の高電圧側端子を前記第2の電圧変換器の第2の高電圧側端子に結合する段階とを有する。本方法はまた、制御システムを前記第1及び第2の電圧変換器に結合する段階と、前記第1の電圧変換器に第1の制御信号を供給し且つ前記第2の電圧変換器に第2の制御信号を供給するように前記制御システムを構成する段階とを有する。前記第1の制御信号は、前記第1の電圧変換器を制御して、前記第1の電圧変換器の前記低電圧側における前記DC電圧源からの電圧を前記第1の電圧変換器の前記高電圧側における第1の出力電圧へ変換するように構成されており、また前記第2の制御信号は、前記第1の制御信号とは相補的であり、且つ前記第2の電圧変換器を制御して、前記第2の電圧変換器の前記低電圧側における前記DC電圧源からの電圧を、前記第2の電圧変換器の前記高電圧側における第2の出力電圧へ変換するように構成されている。前記第1及び第2の出力電圧の電圧差は、前記第1の制御信号の増幅により構成される差電圧を構成する。

30

【0008】

本発明の更に別の面によれば、圧電駆動装置が提供される。この圧電駆動装置は、低電圧側及び高電圧側を持つ第1の両方向DC-DC電圧変換器と、低電圧側及び高電圧側を

40

50

持つ第2の両方向DC-DC電圧変換器とを有する。前記第1の両方向DC-DC電圧変換器は第1の高電圧側端子及び第2の高電圧側端子を有し、また前記第1の両方向DC-DC変換器は、その前記第1の高電圧側端子の電圧を昇圧することができる。前記第2の両方向DC-DC電圧変換器は、第1の高電圧側端子と、前記第1の電圧変換器の前記第2の高電圧側端子に結合された第2の高電圧側端子とを有し、また前記第2の両方向DC-DC変換器は、その前記第1の高電圧側端子の電圧を昇圧することができる。前記圧電駆動装置はまた、前記第1及び第2の両方向DC-DC電圧変換器の前記低電圧側に結合された直流(DC)電圧源と、前記第1の両方向DC-DC電圧変換器の前記第1の高電圧側端子に結合された圧電アクチュエータと、前記第1及び第2の電圧変換器に結合された制御システムとを有する。前記制御システムは、第1の制御信号を前記第1の両方向DC-DC電圧変換器に供給するように構成されており、前記第1の制御信号は、前記第1の両方向DC-DC電圧変換器を制御して、前記第1の両方向DC-DC電圧変換器の前記低電圧側の第1の出力電圧へ変換するように構成されている。前記制御システムはまた、第2の制御信号を前記第2の両方向DC-DC電圧変換器に供給するように構成されており、前記第2の制御信号は、前記第1の制御信号とは相補的であり、且つ前記第2の両方向DC-DC電圧変換器を制御して、前記第2の両方向DC-DC電圧変換器の前記低電圧側の電圧を前記第2の両方向DC-DC電圧変換器の前記高電圧側の第2の出力電圧へ変換するように構成されている。前記第1及び第2の出力電圧の電圧差は、前記第1の制御信号の増幅により構成される差電圧を構成する。

10

【0009】

これらの及び他の利点及び特徴は、添付の図面と共に提供する本発明の好ましい実施形態についての以下の詳しい説明から容易に理解されよう。

【0010】

図面は、本発明を実施するために現在考えられる実施形態を例示する。

【図面の簡単な説明】

【0011】

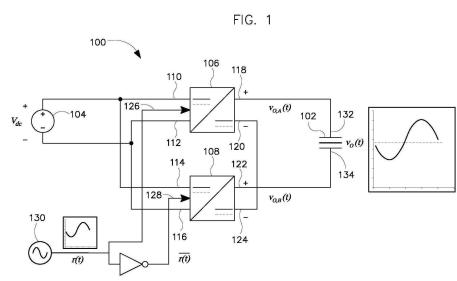

【図1】図1は、本発明の一実施形態に従った圧電負荷のための圧電駆動装置を例示するブロック図である。

30

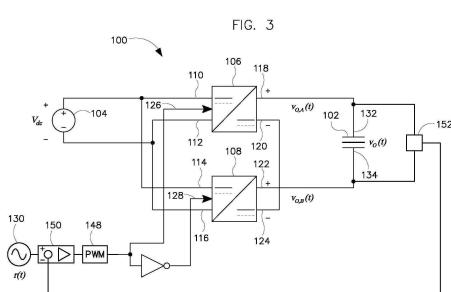

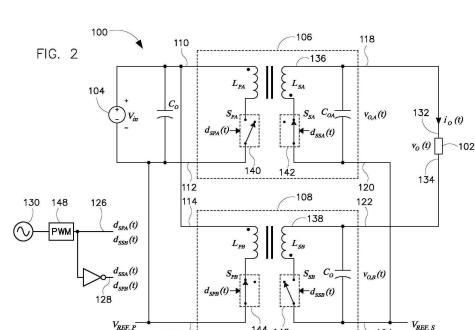

【図2】図2は、本発明の一実施形態に従った圧電負荷のための圧電駆動装置の回路を例示するブロック図である。

【図3】図3は、本発明の別の実施形態に従った圧電駆動装置を例示するブロック図である。

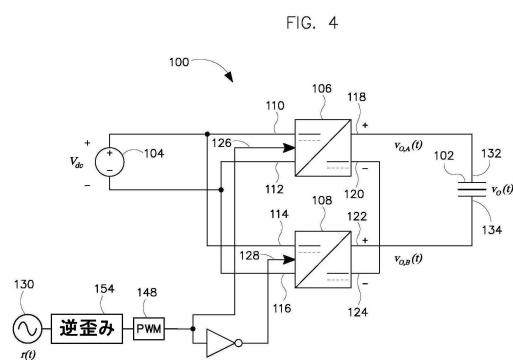

【図4】図4は、本発明の別の実施形態に従った圧電駆動装置を例示するブロック図である。

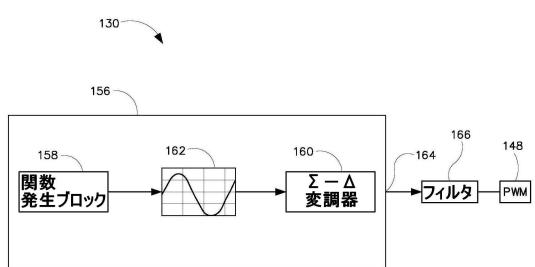

【図5】図5は、本発明の一実施形態に従った基準信号発生器を例示するブロック図である。

【発明を実施するための形態】

【0012】

図1について説明すると、ブロック図は圧電負荷又はアクチュエータ102に結合された圧電駆動装置100を例示する。圧電負荷102は容量性又はリアクタンス負荷である。

【0013】

圧電駆動装置100は、電圧源104と、第1及び第2の変換器106及び108とを含む。第1及び第2の変換器106及び108は、それぞれの対の低電圧側変換器端子110, 112及び114, 116へ供給される電圧源104からの電圧を受け取って、該供給された電圧を昇圧してそれぞれの対の高電圧側変換器端子118, 120及び122, 124へ供給するように構成されたDC-DC両方向変換器/増幅器を含む。第1及び第2の変換器106, 108はまた、それぞれの端子118, 120及び122, 124

10

20

30

40

50

からそれぞれの端子 110, 112 及び 114, 116 へ電圧を降圧する。第 1 の変換器 106 は電圧源 104 からの電圧  $V_{dc}$  を出力電圧  $V_{OA}$  へ変換するように構成され、また第 2 の変換器 108 は電圧源 104 からの電圧  $V_{dc}$  を出力電圧  $V_{OB}$  へ変換するように構成される。一実施形態では、出力電圧  $V_{OA}$  及び  $V_{OB}$  は電圧  $V_{dc}$  の非線形増幅電圧である。しかしながら、出力電圧  $V_{OA}$  及び  $V_{OB}$  の間の電圧差は、電圧  $V_{dc}$  をほぼ線形に拡大縮小(scaling) 又は昇圧した電圧である。

#### 【0014】

一実施形態では、第 1 及び第 2 の変換器 106, 108 は、実質的に同じ單一段両方向切換え型電力変換器である。本書で用いられる「單一段変換器」とは、入力電圧を出力電圧より前に中間電圧へ変換することなく、單一段で入力電圧を出力電圧へ変換する変換器である。

10

#### 【0015】

第 1 及び第 2 の変換器 106, 108 は、AC 電圧源 130 によって供給される一対の制御入力 126, 128 に基づいて電圧を昇圧・降圧する。AC 電圧源 130 は、その増幅した信号で圧電負荷 102 を駆動することを目的として基準信号「 $r(t)$ 」を発生して、制御入力 126 へ供給する。基準信号「 $r(t)$ 」と相補的である基準信号「反転  $r(t)$ 」が制御入力 128 に供給される。

#### 【0016】

第 1 の変換器 106 の変換器端子 118 が圧電負荷 102 の第 1 の端子 132 に結合され、また第 2 の変換器 108 の変換器端子 122 が圧電負荷 102 の第 2 の端子 134 に結合される。更に、変換器端子 120 が変換器端子 124 に結合される。この構成では、変換器端子 118 ~ 124 は圧電負荷 102 を差動的に駆動する。図 1 に示されているように、変換器 106, 108 の出力電圧  $V_{OA}$  及び  $V_{OB}$  は、それぞれ、圧電負荷 102 に供給され、端子 132, 134 間の電圧は  $V_o = V_{OA} - V_{OB}$  として現れる。多くの場合、 $V_o = k * r(t)$  であることが望ましい。ここで、 $k$  は一定の利得である。この態様では、出力電圧  $V_o$  は、実質的に基準信号に一定の利得を掛けたものに等しい。

20

#### 【0017】

多くの周波数で、アクチュエータ 102 のような圧電負荷のインピーダンスはかなりのリアクタンス成分を持つ。このような場合、AC 駆動条件下では、電力が各サイクル毎に負荷に流入して流出する。従って、第 1 及び第 2 の変換器 106, 108 は、この両方向の電力の流れに対処するために、上述したように、両方向変換器である。

30

#### 【0018】

第 1 及び第 2 の変換器 106, 108 は電圧の昇圧及び降圧を行うことのできる任意の種類の両方向変換器であってよいが、図 2 は本発明の一実施形態に従った両方向フライバック型昇圧 / 降圧変換器の実施形態を例示する。このようなフライバック型変換器は、大きな電圧昇圧が必要とされるとき及び / 又は絶縁分離が必要とされるときに適している。しかしながら、本発明の様々な実施形態では、スイッチング損失を低減するためにソフト・スイッチング又は能動クランプのような、変換器についての変形も、本書で述べる回路に用いることができると考えられる。

#### 【0019】

40

図示のように、第 1 及び第 2 の変換器 106, 108 は、変圧器 136, 138 と、スイッチ 140, 142 及び 144, 146 とをそれぞれ含む。スイッチ 140 ~ 146 は電力スイッチであり、例えば、MOSFET、IGT、SCR、及び当該技術分野で知られている他の電力スイッチであってよい。

#### 【0020】

一実施形態では、パルス幅変調器 (PWM) 148 が、変換器 106, 108 における変換処理を制御するために AC 又は正弦波基準信号  $r(t)$  を供給するように制御される。PWM 148 の制御入力 126 がスイッチ 140, 146 に接続されていて、これらのスイッチに制御信号  $d_{SPA}(t)$  及び  $d_{SSB}(t)$  に供給するように構成される。(制御入力 126 の反転したものである) 制御入力 128 が、スイッチ 142, 144 に接続されてい

50

て、これらのスイッチに制御信号  $d_{SPB}(t)$  及び  $d_{SSA}(t)$  に供給するように構成される。模範的な事例では、 $d_{SPA}(t) = d_{SSB}(t) = k_1 * r(t)$  、及び  $d_{SPB}(t) = d_{SBA}(t) = 1 - k_1 * r(t)$  であり、ここで、 $d_x(t)$  はスイッチのデューティ・サイクルであり、 $k_1$  は定数であり、また  $r(t)$  は基準信号である。

#### 【0021】

一対のノード  $V_{REF.P}$  及び  $V_{REF.S}$  が圧電駆動装置 100 の一次 (P) 側及び二次 (S) 側にそれぞれ形成される。ノード  $V_{REF.P}$  及び  $V_{REF.S}$  は、例えば、それぞれの接地面に結合することができ、或いは単一の接地面により一緒に結合することができる。単一の接地面によりノード  $V_{REF.P}$  及び  $V_{REF.S}$  を一緒に結合することは、圧電駆動装置 100 の構成コストを低減すると共に、圧電負荷 102 の駆動を簡単化するのに役立つことができる。共通の単一の接地面に結合されたとき、変換器端子 120 及び 124 は変換器端子 112 及び 116 に結合される。

10

#### 【0022】

第 1 及び第 2 の変換器 106, 108 の制御入力対出力関数が線形でない又は許容可能な線形近似でない場合、誤差訂正又は低減方法を用いて、より線形の出力に近づくように第 1 及び第 2 の変換器 106, 108 の出力を修正することができる。図 3 は、本発明の一実施形態に従って誤差訂正の方法としてフィードバックを用いる例を示すブロック図である。図 3 は、図 1 の圧電駆動装置 100 の構成部品を図 2 の PWM 148 と一緒に示す。また、AC 電圧源 130 と PWM 148 との間に結合された補償器 150 も示されている。補償器 150 は、電圧センサ 152 により圧電負荷 102 の両端間で測定された出力電圧  $V_o(t)$  を受け取る。電圧センサ 152 から受け取った実際の出力波形電圧  $V_o(t)$  を用いて、入力波形電圧  $r(t)$  を修正し、この修正された入力波形電圧に基づいた第 1 及び第 2 の変換器 106, 108 の PWM 制御により所望の出力電圧が生成されるようとする。この態様では、入力波形電圧  $r(t)$  はフィードバックを用いて修正されて、広い変換範囲全体にわたって線形変換を近似するよう第 1 及び第 2 の変換器 106, 108 を制御する。

20

#### 【0023】

図 4 は、本発明の別の実施形態に従って誤差訂正の方法として逆歪み (pre-distortion) 法を用いる例を示すブロック図である。図 4 は、図 1 の圧電駆動装置 100 の構成部品を図 2 の PWM 148 と一緒に示す。また、AC 電圧源 130 と PWM 148 との間に結合された逆歪みブロック 154 も示されている。逆歪みブロック 154 は、入力波形電圧  $r(t)$  を修正して、該修正された入力波形電圧に基づいた第 1 及び第 2 の変換器 106, 108 の PWM 制御により所望の出力電圧波形  $V_o(t)$  を生成するように構成されている制御器又は他のハードウェア構成部品を用いて遂行することができる。例えば、逆歪み制御器はルックアップ・テーブルにより又は逆歪みアルゴリズムによりプログラムすることができ、該逆歪みアルゴリズムは、入力波形電圧  $r(t)$  によってその波形範囲の全体にわたって制御されるときの第 1 及び第 2 の変換器 106, 108 の既知の昇圧変換関数の作用に基づいて入力波形電圧  $r(t)$  を歪ませるように構成される。この態様では、入力波形電圧  $r(t)$  は、所定の歪み修正法を用いて修正されて、広い変換範囲にわたって線形変換を近似するよう第 1 及び第 2 の変換器 106, 108 を制御する。

30

#### 【0024】

図 5 は、本発明の一実施形態に従って図 1 ~ 図 4 に示された基準信号  $r(t)$  を発生する発生源 130 の例を示すブロック図である。この態様での  $r(t)$  の発生は、圧電駆動装置出力に高い忠実度を生じさせることができる。

40

#### 【0025】

基準信号  $r(t)$  の発生は、アナログ回路により、或いは基準信号  $r(t)$  を合成するデジタル手段を用いて、達成することができる。簡単な事例では、基準信号  $r(t)$  の発生は、アナログ回路で行うことができる。例えば、正弦波の発生をウェーン・ブリッジなどの発振器により行うことができる。しかしながら、より複雑なパターンを発生するためには、又は変換器によって導入された非線形効果及び歪みを補償するためには、デジタル手

50

段の方がより便利である。この目的のために、FPGA、DSP又はマイクロコントローラのようなシングルボード・コンピュータを使用することができる。デジタル手段では、図4で述べたような逆歪みを含めることもできる。

#### 【0026】

図5は、PWM148を駆動することのできる特定の指令信号を発生するために使用される制御器156を例示する。制御器156は、関数発生ブロック158及び $\Sigma - \Delta$ （シグマ・デルタ）変調器ブロック160を含む。関数発生ブロック158では、所望の波形を関数として又はルックアップ・テーブルとしてプログラムすることができる。例えば、関数発生器では、使用するデジタル値を決定するアルゴリズムを実行することができる。この代わりに、ルックアップ・テーブルでは、デジタル値を予め計算して、その中に保存することができる。デジタル制御器又はDSP（図示せず）で、これらのデジタル値を利用して、様々なやり方に従って基準信号 $r(t)$ を更に発生することができる。一実施形態では、デジタル値はデジタル-アナログ変換器（DAC）162に供給して、DAC162によりアナログ波形を発生することができる。別の実施形態では、デジタル値はデジタル制御器156の内部のパルス幅変調器（図示せず）を駆動することができる、その出力は次いでフィルタ（図示せず）により濾波して不所望の周波数成分を除去することができる。更に別の実施形態では、デジタル値は、電力スイッチ制御波形を直接発生するデジタルPWM148を駆動することができる。

10

#### 【0027】

デジタル波形発生方法を用いるときの「量子化(quantization)」に起因して、典型的には低コストのマイクロコントローラで利用できるビットの数が制限されており、これは通常、基準波形の構成中に目に見える多数の「ステップ（段差）」又は量子があることを意味する。これらのアーティファクトは、制御器156の出力164に歪み又は低忠実度の波形として現れることがある。場合によっては、これらのアーティファクトは、望ましくない動作を生じさせる、例えば、可聴ノイズを発生させることがある。基本的なアナログ波形は低い周波数の波形であることがあるので、これらのアーティファクトを除去するには、通常、出力164に嵩張るフィルタを使用して高次の高調波を濾波することを必要とする。フィルタ・ブロック166が、制御器156とPWM148との間のインターフェースとして設けられる。上記の量子化効果に対処するために何も行われていない場合、量子化効果が駆動装置又は変換器の出力に悪影響を与えないようにするために、重量のある低域通過フィルタが使用されることがある。制御器156がより低い分解能を持っている場合、フィルタの遮断周波数が余りにも低くなってしまって、基準信号 $r(t)$ が減衰することができる。この効果（影響）を補償するには、電力消費の増大が必要とされよう。

20

#### 【0028】

逆歪み(pre-distortion)法を用いるとき、低域通過フィルタが基本周波数に近い遮断周波数を持つと、これにより第1及び第2の変換器106, 108において $r(t)$ の不正確な拡大縮小された表現が生じる虞がある。例えば、変換器106, 108からの望ましい出力信号は $r(t)$ の拡大縮小された表現であるので、変換器106, 108が非線形である場合、 $r(t)$ は、PWM148に入力する前に、変換器106, 108の非線形動作を補償するように信号 $r'(t)$ として予め歪ませることができる。この予め歪ませた信号 $r'(t)$ は $r(t)$ の高調波を変更すると考えられる。もし低域通過フィルタの作用により、これらの高調波が減衰し又はそれらの高調波の位相が互いにに対して且つ基本波に対して変化した場合、望ましくない歪みが付加され、また変換器106, 108の出力はもはや基準信号 $r(t)$ の正確な拡大縮小された表現ではなくなる。

30

#### 【0029】

フィルタ動作の制約を避け且つ量子化に関連した効果（影響）を軽減するために、有効なサンプリング分解能の増大が用いられる。分解能を増大し且つ量子化の影響を低減するために、シグマ・デルタ技術を制御器156で具現化することができる。制御器156が充分高いサンプリング速度を持っている場合、制御器156のより高いサンプリング及び計算速度を基準信号 $r(t)$ の様々な周波数成分に対して折り合いを付けて、該信号をオーバー

40

50

バーサンプリングすることができる。これはまたルックアップ・テーブルとして具現化することができ、この場合、基準信号  $r(t)$  がオーバーサンプリングされ、また様々な項目が制御器 156 においてルックアップ・テーブルとしてプログラムされる。

【0030】

このようなオーバーサンプリングの利点は、サンプリングされる波形において生じる何らかの不正確さ又は歪みが、信号をオーバーサンプリング又は過大表現する周波数に依存することである。量子化により以前に生じたアーティファクトが、より高い周波数へシフトされる。これにより、シグマ・デルタ技術 160 がアーティファクトの周波数を基本波の基準成分よりも遙かに高い値へシフトするので、制御器 156 から出力されるアナログ波形についてのフィルタ動作を、従来の D A C で可能であったものより高い遮断周波数で具現化することが可能になる。この事は少なくとも 2 つの利益を持つ。第 1 に、フィルタのサイズ及びコストを低減できる。第 2 に、より高いフィルタ遮断周波数を可能にしたことが、逆歪み法によって発生され又は変更された高調波成分についてのフィルタの効果(影響)を最小にして、逆歪み法の利用を実用的にすることを意味する。

【0031】

PWM 148 に対してきれいな指令を発生するこの方法は、出力波形  $V_o(t)$  の忠実度を維持するために重要である。実際、実施例によっては、一連の回路全体を、フィルタ 166 及び PWM 148 も含めて、マイクロコントローラ・ブロック又はデジタル・プロセッサで具現化することができる。

【0032】

本発明の様々な実施形態は、高い効率、低いコスト、小さいサイズ及び良好な波形忠実度を持つ圧電駆動装置を可能にする。更に、実施形態によっては、図 2 について説明したようなフライバック型変換器を用いることにより、直流絶縁分離、広い電圧範囲、及び全ての電力スイッチについての共通の基準接地を可能にする。更に、フィードバック、逆歪み、又はフィードフォワード誤差訂正技術のような誤差訂正技術を用いて非線形 D C - D C 変換を補償することにより、圧電アクチュエータの両端間の電圧が、昇圧変換プロセスを制御するために用いられる制御信号の線形近似になるようにすることができる。

【0033】

従って、本発明の一実施形態によれば、駆動システムは、直流 (D C) 電圧源と、前記 D C 電圧源に結合された一次側を持つと共に二次側を持つ第 1 の両方向 D C - D C 変換器であって、更に当該第 1 の両方向 D C - D C 変換器の前記一次側の第 1 の電圧から当該第 1 の両方向 D C - D C 変換器の前記二次側の第 2 の電圧への変換を制御するように構成された第 1 の制御信号を受け取るように構成されている制御入力を持つ第 1 の両方向 D C - D C 変換器とを有する。駆動システムはまた、前記 D C 電圧源に結合された一次側を持つと共に前記第 1 の両方向 D C - D C 変換器の前記二次側に結合された二次側を持つ第 2 の両方向 D C - D C 変換器であって、更に当該第 2 の両方向 D C - D C 変換器の前記一次側の第 1 の電圧から当該第 2 の両方向 D C - D C 変換器の前記二次側の第 3 の電圧への変換を制御するように構成された第 2 の制御信号を受け取るように構成されている制御入力を有する。前記第 1 及び第 2 の両方向 D C - D C 変換器は前記第 1 の電圧を昇圧することができ、また前記第 2 の制御信号は前記第 1 の制御信号と相補的である。前記第 2 及び第 3 の電圧の間の電圧差は出力電圧を構成し、該出力電圧は前記第 1 の制御信号の増幅により構成される。

【0034】

本発明の別の実施形態によれば、圧電駆動装置を製作する方法は、直流 (D C) 電圧源を第 1 の電圧変換器の低電圧側と第 2 の電圧変換器の低電圧側とに結合し、前記第 1 及び第 2 の電圧変換器により、前記 D C 電圧源からの電圧を昇圧することができる両方向 D C - D C 電圧変換器を構成する段階を有する。本方法はまた、前記第 1 の電圧変換器の高電圧側の第 1 の高電圧側端子を圧電アクチュエータの第 1 の側に結合する段階と、前記第 2 の電圧変換器の高電圧側の第 1 の高電圧側端子を前記圧電アクチュエータの第 2 の側に結合する段階と、前記第 1 の電圧変換器の第 2 の高電圧側端子を前記第 2 の電圧変換器の第

10

20

30

40

50

2 の高電圧側端子に結合する段階とを有する。本方法はまた、制御システムを前記第 1 及び第 2 の電圧変換器に結合する段階と、前記第 1 の電圧変換器に第 1 の制御信号を供給し且つ前記第 2 の電圧変換器に第 2 の制御信号を供給するように前記制御システムを構成する段階とを有する。前記第 1 の制御信号は、前記第 1 の電圧変換器を制御して、前記第 1 の電圧変換器の前記低電圧側における前記 DC 電圧源からの電圧を前記第 1 の電圧変換器の前記高電圧側における第 1 の出力電圧へ変換するように構成されており、また前記第 2 の制御信号は、前記第 1 の制御信号とは相補的であり、且つ前記第 2 の電圧変換器を制御して、前記第 2 の電圧変換器の前記低電圧側における前記 DC 電圧源からの電圧を、前記第 2 の電圧変換器の前記高電圧側における第 2 の出力電圧へ変換するように構成されている。前記第 1 及び第 2 の出力電圧の電圧差は、前記第 1 の制御信号の増幅により構成される差電圧を構成する。

【 0 0 3 5 】

本発明の更に別の実施形態によれば、圧電駆動装置は、低電圧側及び高電圧側を持つ第 1 の両方向 DC - DC 電圧変換器と、低電圧側及び高電圧側を持つ第 2 の両方向 DC - DC 電圧変換器とを有する。前記第 1 の両方向 DC - DC 電圧変換器は第 1 の高電圧側端子及び第 2 の高電圧側端子を有し、また前記第 1 の両方向 DC - DC 变換器は、その前記第 1 の高電圧側端子の電圧を昇圧することができる。前記第 2 の両方向 DC - DC 電圧変換器は、第 1 の高電圧側端子と、前記第 1 の電圧変換器の前記第 2 の高電圧側端子に結合された第 2 の高電圧側端子とを有し、また前記第 2 の両方向 DC - DC 变換器は、その前記第 1 の高電圧側端子の電圧を昇圧することができる。前記圧電駆動装置はまた、前記第 1 及び第 2 の両方向 DC - DC 電圧変換器の前記低電圧側に結合された直流 (DC) 電圧源と、前記第 1 の両方向 DC - DC 電圧変換器の前記第 1 の高電圧側端子に結合され且つ前記第 2 の両方向 DC - DC 電圧変換器の前記第 1 の高電圧側端子に結合された圧電アクチュエータと、前記第 1 及び第 2 の電圧変換器に結合された制御システムとを有する。前記制御システムは、第 1 の制御信号を前記第 1 の両方向 DC - DC 電圧変換器に供給するように構成されており、前記第 1 の制御信号は、前記第 1 の両方向 DC - DC 電圧変換器を制御して、前記第 1 の両方向 DC - DC 電圧変換器の前記低電圧側の電圧を前記第 1 の両方向 DC - DC 電圧変換器の前記高電圧側の第 1 の出力電圧へ変換するように構成されている。前記制御システムはまた、第 2 の制御信号を前記第 2 の両方向 DC - DC 電圧変換器に供給するように構成されており、前記第 2 の制御信号は、前記第 1 の制御信号とは相補的であり、且つ前記第 2 の両方向 DC - DC 電圧変換器を制御して、前記第 2 の両方向 DC - DC 電圧変換器の前記低電圧側の電圧を前記第 2 の両方向 DC - DC 電圧変換器の前記高電圧側の第 2 の出力電圧へ変換するように構成されている。前記第 1 及び第 2 の出力電圧の電圧差は、前記第 1 の制御信号の増幅により構成される差電圧を構成する。

【 0 0 3 6 】

本明細書は、最良の実施形態を含めて、本発明を開示するために、また当業者が任意の装置又はシステムを作成し使用し、任意の採用した方法を遂行すること含めて、本発明を実施できるようにするために、様々な例を使用した。本発明の特許可能な範囲は「特許請求の範囲」の記載に定めており、また当業者に考えられる他の例を含み得る。このような他の例は、それらが「特許請求の範囲」の文字通りの記載から差異のない構造的要素を持つ場合、或いはそれらが「特許請求の範囲」の文字通りの記載から実質的に差異のない等価な構造的要素を含む場合、特許請求の範囲内にあるものとする。

【 符号の説明 】

【 0 0 3 7 】

1 0 0 圧電駆動装置

1 0 2 圧電負荷 (又は、圧電アクチュエータ)

1 0 4 電圧源

1 0 6 第 1 の変換器

1 0 8 第 2 の変換器

1 1 0 、 1 1 2 第 1 の変換器の低電圧側変換器端子

10

20

30

40

50

|                            |                          |    |

|----------------------------|--------------------------|----|

| 1 1 4、 1 1 6               | 第 2 の変換器の低電圧側変換器端子       |    |

| 1 1 8、 1 2 0               | 第 1 の変換器の高電圧側変換器端子       |    |

| 1 2 2、 1 2 4               | 第 2 の変換器の高電圧側変換器端子       |    |

| 1 2 6                      | 制御入力                     |    |

| 1 2 8                      | 制御入力                     |    |

| 1 3 0                      | A C 電圧源                  |    |

| 1 3 2                      | 圧電負荷の第 1 の端子             |    |

| 1 3 4                      | 圧電負荷の第 2 の端子             |    |

| 1 3 6、 1 3 8               | 変圧器                      |    |

| 1 4 0、 1 4 2、 1 4 4、 1 4 6 | スイッチ                     | 10 |

| 1 4 8                      | パルス幅変調器 ( P W M )        |    |

| 1 5 0                      | 補償器                      |    |

| 1 5 2                      | 電圧センサ                    |    |

| 1 5 4                      | 逆歪みブロック                  |    |

| 1 5 6                      | 制御器                      |    |

| 1 5 8                      | 関数発生ブロック                 |    |

| 1 6 0                      | - (シグマ・デルタ) 变調器ブロック      |    |

| 1 6 2                      | デジタル - アナログ変換器 ( D A C ) |    |

| 1 6 4                      | 制御器の出力                   |    |

| 1 6 6                      | フィルタ                     | 20 |

【図 1】

【図 3】

【図 2】

【図 4】

【図5】

FIG. 5

---

フロントページの続き

(72)発明者 ジョン・スタンレー・グレイサー

アメリカ合衆国、ニューヨーク州・12309、ニスカユナ、リサーチ・サークル、1番

(72)発明者 ラマヌジャム・ラマバドラン

アメリカ合衆国、ニューヨーク州・12309、ニスカユナ、リサーチ・サークル、1番

審査官 東 昌秋

(56)参考文献 特開2010-220466(JP,A)

特開平6-62585(JP,A)

特開2005-253230(JP,A)

特開平6-237583(JP,A)

特開2006-333678(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 1/00-7/98

H02N 2/00-2/18