등록특허 10-2303586

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년09월17일

(11) 등록번호 10-2303586

(24) 등록일자 2021년09월13일

- (51) 국제특허분류(Int. Cl.)

*G01N 29/11* (2006.01) *G01N 29/06* (2006.01)

*G01N 29/44* (2006.01)

- (52) CPC특허분류

*G01N 29/11* (2013.01)

*G01N 29/0654* (2013.01)

- (21) 출원번호 10-2018-7018290

- (22) 출원일자(국제) 2016년12월01일

심사청구일자 2019년01월09일

- (85) 번역문제출일자 2018년06월27일

- (65) 공개번호 10-2018-0089454

- (43) 공개일자 2018년08월08일

- (86) 국제출원번호 PCT/US2016/064322

- (87) 국제공개번호 WO 2017/095985

국제공개일자 2017년06월08일

(30) 우선권주장

14/957,443 2015년12월02일 미국(US)

## (56) 선행기술조사문현

US20130043962 A1\*

US20140184330 A1\*

KR101024849 B1\*

\*는 심사관에 의하여 인용된 문현

- (73) 특허권자

버터플라이 네트워크, 인크.

미국 06437 코네티컷주 길포드 올드 웨필드 스트리트 530

- (72) 발명자

챈, 카이리昂

미국 06437 코네티컷주 길포드 리버 콜로니 7

랜스턴, 타일러, 에스.

- (74) 대리인

양영준, 김연송, 백만기

전체 청구항 수 : 총 20 항

심사관 : 김민석

## (54) 발명의 명칭 시간 이득 보상 회로 및 관련 장치 및 방법들

**(57) 요약**

초음파 디바이스는 프로파일 생성기, 프로파일 생성기로부터 프로파일 신호를 수신하도록 구성되는 인코더, 및 초음파 센서의 출력을 나타내는 신호를 수신하도록 구성되고 인코더로부터 제어 신호를 수신하기 위해 인코더에 결합되는 감쇠기를 포함하고, 감쇠기는 복수의 감쇠기 스테이지들을 포함하며, 감쇠기는 입력 신호의 감쇠된 버전인 출력 신호를 생성하도록 구성된다.

**대 표 도**

(52) CPC특허분류

*G01N 29/44* (2013.01)

*G01N 2291/015* (2013.01)

*G01N 2291/02475* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

초음파 디바이스로서,

프로파일 생성기(profile generator);

상기 프로파일 생성기로부터 프로파일 신호를 수신하도록 구성되는 인코더;

초음파 센서의 출력을 나타내는 입력 신호를 수신하도록 구성되고 상기 인코더로부터 제어 신호를 수신하기 위해 상기 인코더에 결합되는 감쇠기 - 상기 감쇠기는 복수의 2진 감쇠 스테이지들(binary attenuation stages)을 포함하고, 상기 감쇠기는 상기 입력 신호의 감쇠된 버전인 출력 신호를 생성하도록 구성됨 -; 및

0dB보다 큰 이득을 가지며 상기 감쇠기로부터 상기 출력 신호를 수신하고 상기 출력 신호를 증폭하도록 구성되는 고정 이득 증폭기

를 포함하고,

상기 프로파일 생성기는 다중 층들로부터의 반사들에 기초한 곡률을 갖는 타겟 감쇠 프로파일(target attenuation profile)을 제공하는, 초음파 디바이스.

#### 청구항 2

삭제

#### 청구항 3

제1항에 있어서, 상기 복수의 2진 감쇠 스테이지들의 각각은 0.2dB의 감쇠를 제공하는, 초음파 디바이스.

#### 청구항 4

제1항에 있어서, 상기 복수의 2진 감쇠 스테이지들의 각각은 적어도 하나의 상보형 스위치(complementary switch)를 포함하는, 초음파 디바이스.

#### 청구항 5

제1항에 있어서, 상기 복수의 2진 감쇠 스테이지들의 각각은 단일 종단(single-ended)인, 초음파 디바이스.

#### 청구항 6

제1항에 있어서, 상기 복수의 2진 감쇠 스테이지들의 각각은 차동(differential)인, 초음파 디바이스.

#### 청구항 7

제1항에 있어서, 상기 복수의 2진 감쇠 스테이지들은 상기 감쇠기를 형성하기 위해 병렬로 연결되는, 초음파 디바이스.

#### 청구항 8

제1항에 있어서, 상기 복수의 2진 감쇠 스테이지들은 상기 감쇠기를 형성하기 위해 직렬로 연결되는, 초음파 디바이스.

#### 청구항 9

제1항에 있어서, 상기 복수의 2진 감쇠 스테이지들은 상기 감쇠기를 형성하기 위해 직렬 및 병렬로 연결되는, 초음파 디바이스.

#### 청구항 10

초음파 디바이스로서,

프로파일 생성기;

상기 프로파일 생성기로부터 프로파일을 수신하도록 구성되는 인코더;

초음파 센서의 출력을 나타내는 입력 신호를 수신하도록 구성되고 상기 인코더로부터 제어 신호를 수신하기 위해 상기 인코더에 결합되는 감쇠기- 상기 감쇠기는 복수의 스테이지들을 포함하고, 상기 복수의 스테이지들에서 각각의 스테이지는 미리 결정된 감쇠를 가지며, 상기 감쇠기는 상기 입력 신호의 감쇠된 버전인 감쇠된 출력 신호를 생성하도록 구성됨 -; 및

0dB보다 큰 이득을 가지며 상기 감쇠기로부터 상기 출력 신호를 수신하고 상기 출력 신호를 증폭하도록 구성되는 고정 이득 증폭기

를 포함하고,

상기 프로파일 생성기는 다중 층들로부터의 반사들에 기초한 곡률을 갖는 타겟 감쇠 프로파일을 제공하는, 초음파 디바이스.

#### 청구항 11

삭제

#### 청구항 12

제10항에 있어서, 상기 복수의 스테이지들의 각각은 0.2dB의 감쇠를 제공하는, 초음파 디바이스.

#### 청구항 13

제10항에 있어서, 상기 복수의 스테이지들의 각각은 적어도 하나의 상보형 스위치를 포함하는, 초음파 디바이스.

#### 청구항 14

제10항에 있어서, 상기 복수의 스테이지들의 각각은 단일 종단인, 초음파 디바이스.

#### 청구항 15

제10항에 있어서, 상기 복수의 스테이지들의 각각은 차동인, 초음파 디바이스.

#### 청구항 16

제10항에 있어서, 상기 복수의 스테이지들은 상기 감쇠기를 형성하기 위해 병렬로 연결되는, 초음파 디바이스.

#### 청구항 17

제10항에 있어서, 상기 복수의 스테이지들은 상기 감쇠기를 형성하기 위해 직렬로 연결되는, 초음파 디바이스.

#### 청구항 18

제10항에 있어서, 상기 복수의 스테이지들은 상기 감쇠기를 형성하기 위해 직렬 및 병렬로 연결되는, 초음파 디바이스.

#### 청구항 19

제1항에 있어서, 상기 고정 이득 증폭기는 1dB과 100dB 사이의 이득을 갖는, 초음파 디바이스.

#### 청구항 20

제1항에 있어서, 상기 감쇠기 및 상기 고정 이득 증폭기는 상기 입력 신호에 대해 시간 이득 보상을 수행하도록 구성되는, 초음파 디바이스.

#### 청구항 21

제10항에 있어서, 상기 고정 이득 증폭기는 1dB과 100dB 사이의 이득을 갖는, 초음파 디바이스.

## 청구항 22

제10항에 있어서, 상기 감쇠기 및 상기 고정 이득 증폭기는 상기 입력 신호에 대해 시간 이득 보상을 수행하도록 구성되는, 초음파 디바이스.

### 발명의 설명

#### 기술 분야

[0001] 관련 출원에 대한 상호 참조

[0002] 본 출원은 발명의 명칭이 "TIME GAIN COMPENSATION CIRCUIT AND RELATED APPARATUS AND METHODS"이고 대리인 관리 번호는 B1348.70022US00인, 2015년 12월 2일자로 출원된 미국 특허 출원 일련 번호 제14/957,443호의 35 U.S.C. § 120 하에서의 이익을 주장하는 연속출원이며, 이는 그 전체가 참조로서 본 명세서에 통합된다.

[0003] 기술분야

[0004] 본 출원은 시간 이득 보상 회로(time gain compensation circuit)를 갖는 초음파 디바이스들에 관한 것이다.

### 배경 기술

[0005] 초음파 디바이스들은 진단 영상(diagnostic imaging) 및/또는 치료를 수행하기 위해 사용될 수 있다. 초음파 영상은 내부 연조직 신체 구조들을 보기 위해 사용될 수 있다. 초음파 영상은 질병의 원인을 찾거나 임의의 병리학을 배제하기 위해 사용될 수 있다. 초음파 디바이스들은 사람들이 들을 수 있는 것보다 높은 주파수들의 음파들을 사용한다. 초음파 이미지들은 프로브를 사용하여 초음파의 펄스들을 조직으로 보냄으로써 만들어진다. 음파들은 조직에서 반사되고, 상이한 조직들은 소리의 정도가 서로 다르다. 이러한 반사된 음파들은 이미지로서 오퍼레이터에게 기록 및 디스플레이될 수 있다. 소리 신호의 강도(진폭), 및 파동이 몸을 통과하는 데 걸리는 시간은 이미지를 생성하기 위해 사용되는 정보를 제공한다.

[0006] 많은 상이한 유형들이 이미지들이 초음파 디바이스들을 사용하여 형성될 수 있다. 이미지들은 실시간 이미지를 일 수 있다. 예를 들어, 조직의 2차원 단면들, 혈류, 시간에 따른 조직의 움직임, 혈액의 위치, 특정 분자들의 존재, 조직의 강성(stiffness), 또는 3차원 영역의 해부학적 구조를 보여주는 이미지들이 생성될 수 있다.

### 발명의 내용

[0007] 본 출원의 일 양태에 따르면, 프로파일 생성기, 프로파일 생성기로부터 프로파일 신호를 수신하도록 구성되는 인코더, 및 초음파 센서의 출력을 나타내는 신호를 수신하도록 구성되고 인코더로부터 제어 신호를 수신하기 위해 인코더에 결합되는 감쇠기를 포함하는 초음파 디바이스가 제공되고, 감쇠기는 복수의 2진 감쇠기 스테이지들을 포함하며, 감쇠기는 입력 신호의 감쇠된 버전인 출력 신호를 생성하도록 구성된다.

[0008] 본 출원의 일 양태에 따르면, 프로파일 생성기, 프로파일 생성기로부터 프로파일 신호를 수신하도록 구성되는 인코더, 및 초음파 센서의 출력을 나타내는 신호를 수신하도록 구성되고 인코더로부터 제어 신호를 수신하기 위해 인코더에 결합되는 감쇠기를 포함하는 초음파 디바이스가 제공되고, 감쇠기는 복수의 스테이지들을 포함하며, 복수의 스테이지들 중 각각의 스테이지는 미리 결정된 감쇠를 가지고, 감쇠기는 입력 신호의 감쇠된 버전인 출력 신호를 생성하도록 구성된다.

### 도면의 간단한 설명

[0009] 본 출원의 다양한 양태들 및 실시예들이 다음의 도면들을 참조하여 기술될 것이다. 도면들은 반드시 일정한 비율로 그려진 것은 아니라는 것을 이해해야 한다. 다수의 도면들에서 나타나는 항목들은 그것들이 나타나는 모든 도면들에서 동일한 참조 번호로 표시된다.

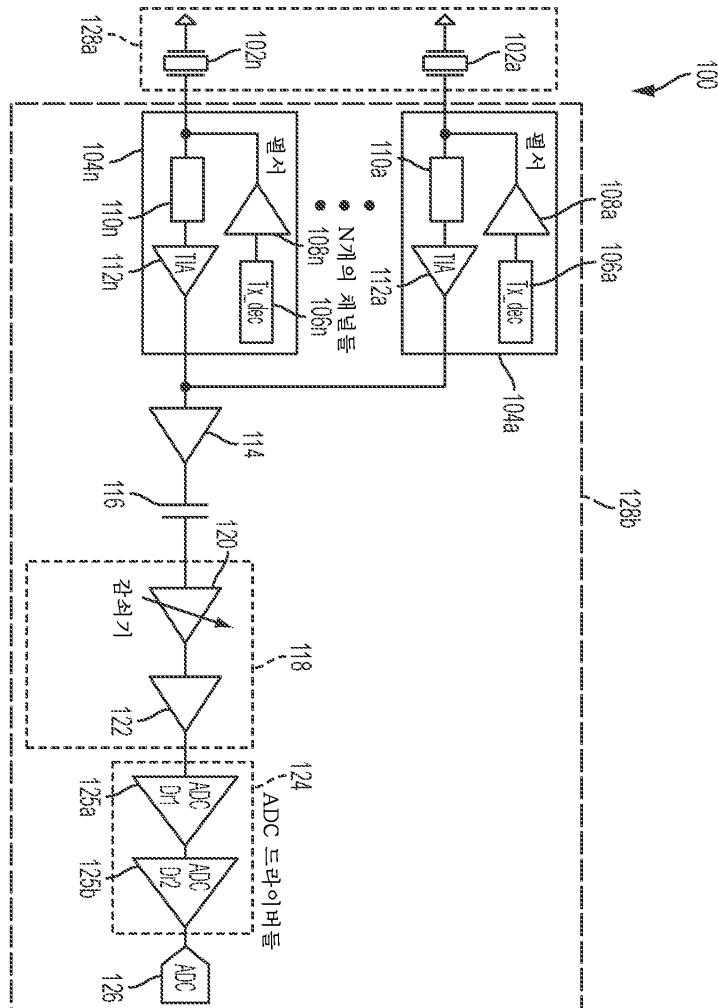

도 1은 본 출원의 제한이 아닌 실시예에 따른 시간 이득 보상 회로를 포함하는 초음파 디바이스의 블록도이다.

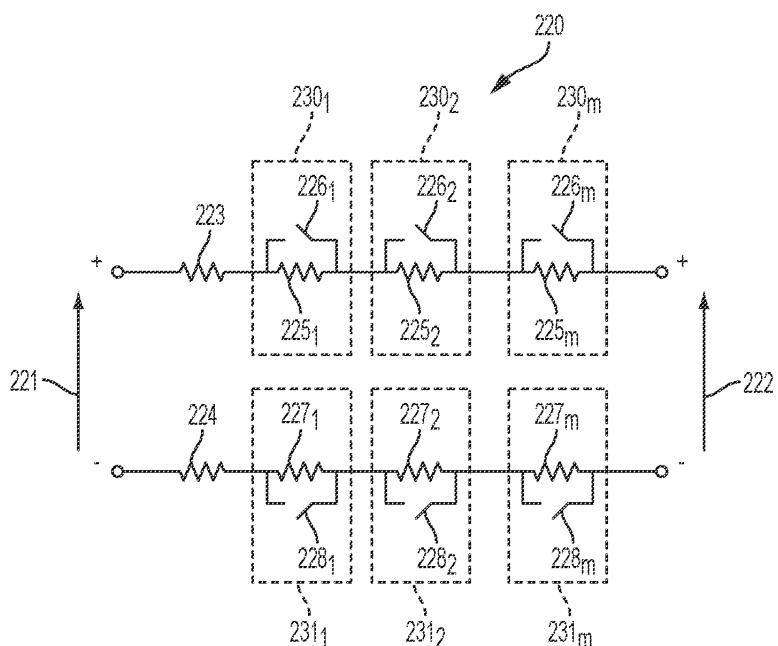

도 2a는 본 출원의 제한이 아닌 실시예에 따른 도 1의 감쇠기의 차동 병렬 구현(differential parallel implementation)을 도시하는 회로도이다.

도 2b는 본 출원의 제한이 아닌 실시예에 따른 도 1의 감쇠기의 차동 직렬 구현(differential series

implementation)을 도시하는 회로도이다.

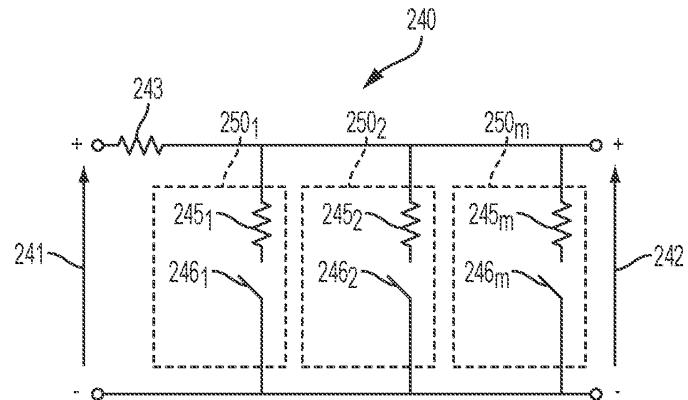

도 2c는 본 출원의 제한이 아닌 실시예에 따른 도 1의 감쇠기의 단일 종단 병렬 구현(single-ended parallel implementation)을 도시하는 회로도이다.

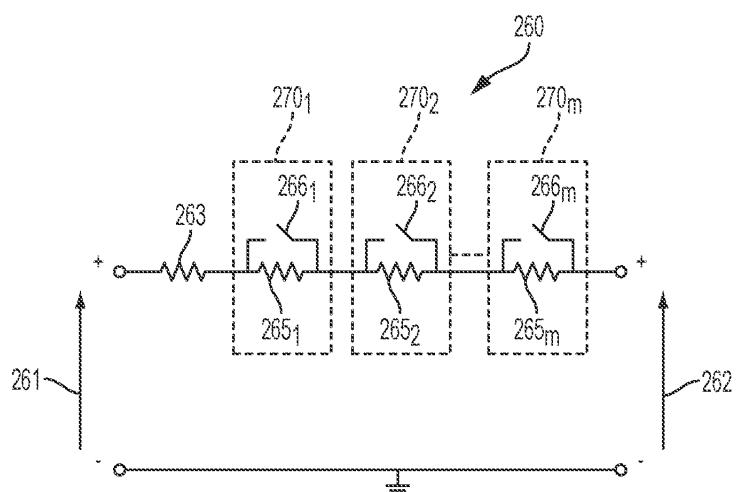

도 2d는 본 출원의 제한이 아닌 실시예에 따른 도 1의 감쇠기의 단일 종단 직렬 구현(single-ended series implementation)을 도시하는 회로도이다.

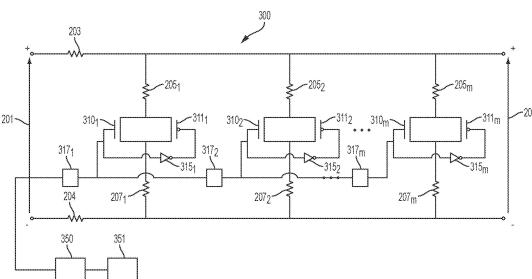

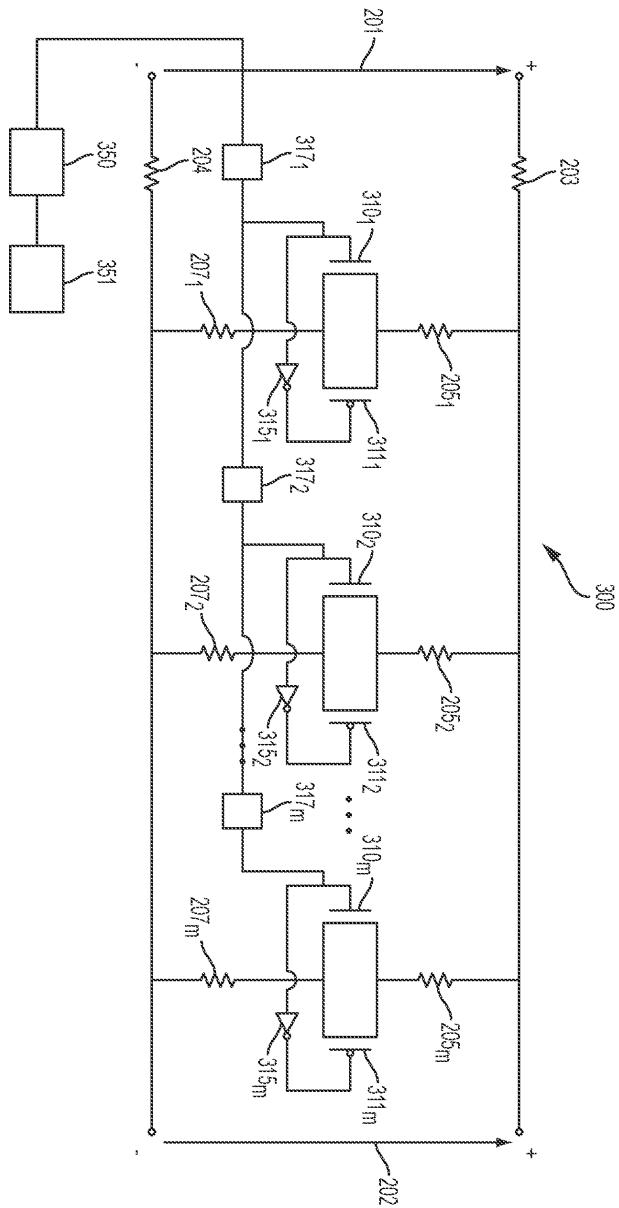

도 3은 본 출원의 제한이 아닌 실시예에 따른 상보형 스위치들(complementary switches)을 포함하는 도 1의 감쇠기의 구현을 도시하는 회로도이다.

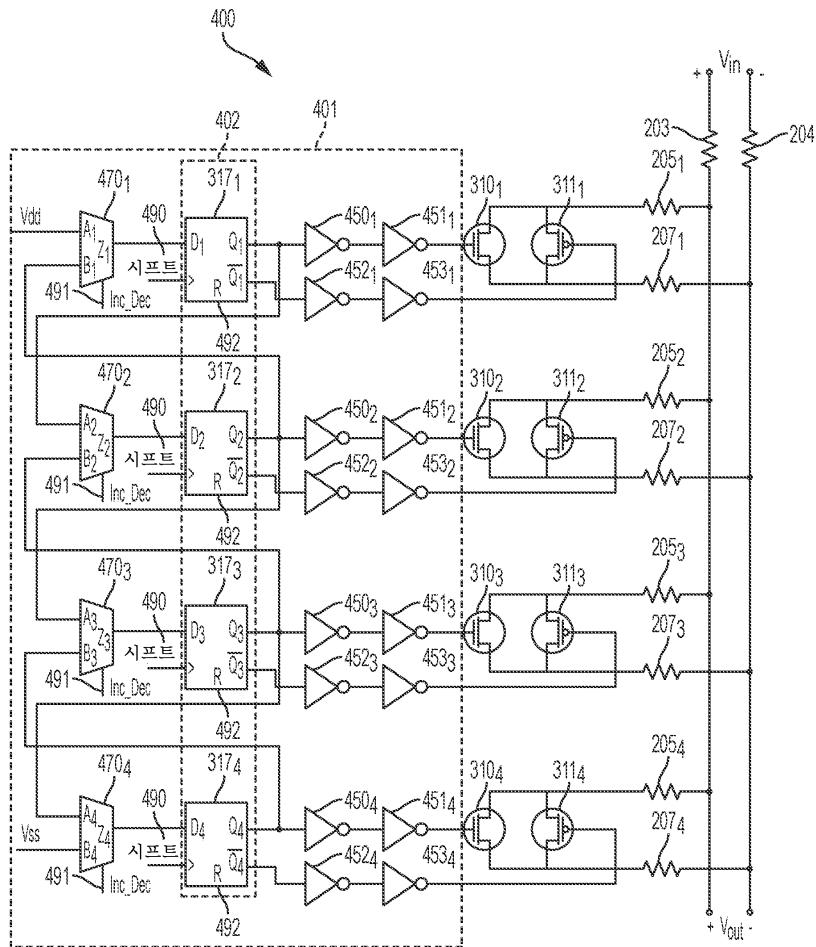

도 4는 본 출원의 제한이 아닌 실시예에 따른 도 3의 상보형 스위치들의 상태를 결정하기 위해 사용되는 디지털 인코더 및 시프트 레지스터를 도시하는 회로도이다.

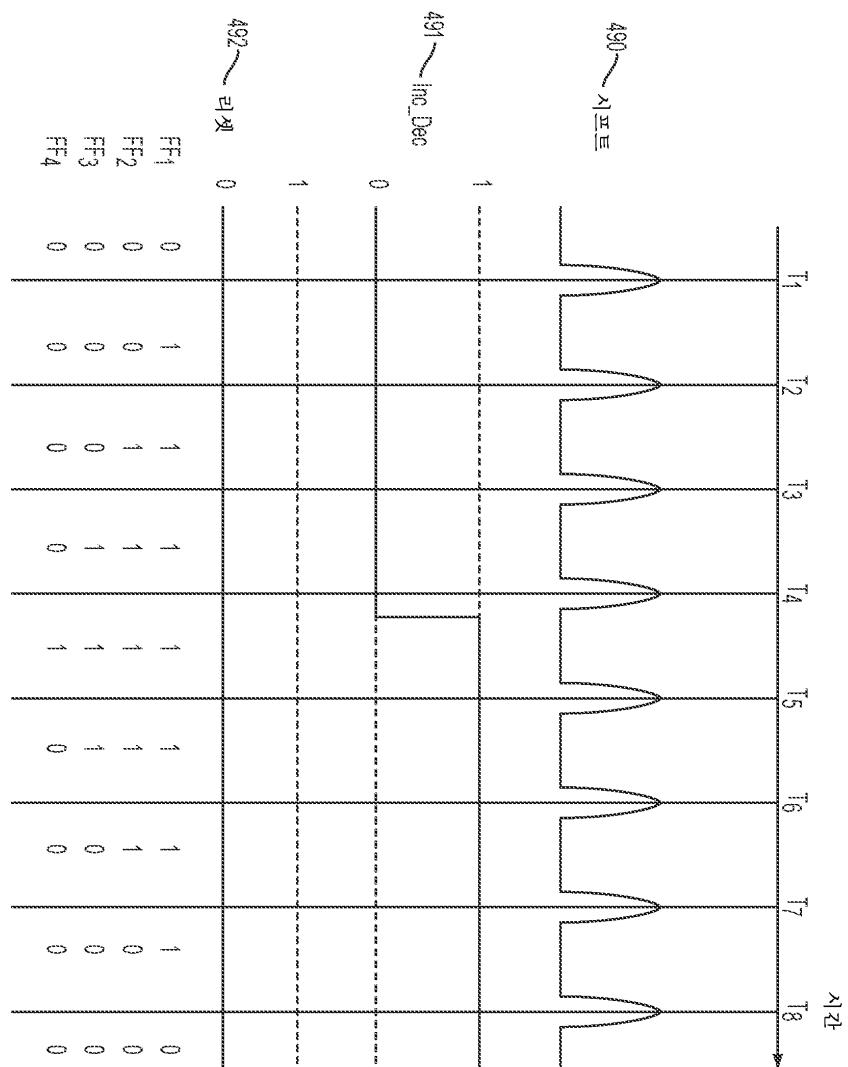

도 5는 본 출원의 제한이 아닌 실시예에 따른 3개의 제어 신호들 및 도 4의 시프트 레지스터의 상태의 시간 진화(temporal evolution)를 도시하는 그래프이다.

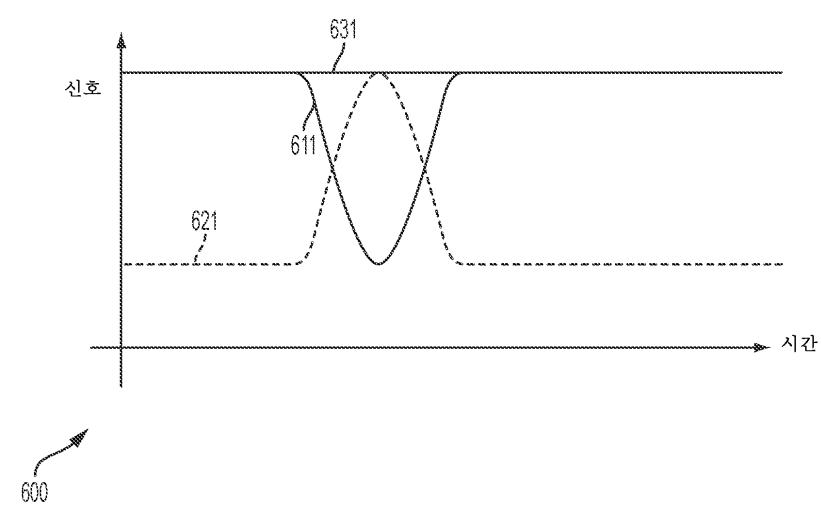

도 6은 본 출원의 제한이 아닌 실시예에 따른 딥(dip)을 특징으로 하는 신호의 수신에 의해 트리거되는 시간 이득 보상 응답을 도시하는 그래프이다.

### 발명을 실시하기 위한 구체적인 내용

[0010]

본 발명자들은 시간 이득 보상 회로들과 연관된 전력 소비 및 정확도가 가변 회로들을 가변 감쇠기들 및 고정 이득 증폭기들을 포함하는 증폭 회로들로 대체함으로써 개선될 수 있음을 인식 및 이해했다. 이러한 접근은 문제를 능동 회로의 설계에서 수동 회로의 설계로 시프트하는 증폭기 설계를 상당히 단순화할 수 있다.

[0011]

본 출원의 양태들은 개별적으로 디지털적으로 인에이블되는 복수의 저항기들을 포함하는 시간 이득 보상을 위한 가변 감쇠기 회로들에 관한 것이다. 회로들이 고정 저항기들을 포함하기 때문에, 높은 감쇠 정확도, 및 결과적으로 높은 이득 정확도가 달성될 수 있다. 또한, 가변 감쇠기와 연관된 전력 소비의 원천은 저항기들을 인에이블하는 디지털 회로들이다.

[0012]

상기 기술된 양태들 및 실시예들뿐만 아니라 추가적인 양태들 및 실시예들이 아래에 더 기술된다. 본 출원이 이러한 측면에서 제한되지 않기 때문에, 이러한 양태들 및/또는 실시예들은 개별적으로, 모두 함께, 또는 둘 이상의 임의의 조합으로 사용될 수 있다.

[0013]

도 1은 본 출원의 제한이 아닌 실시예에 따른 수신된 초음파 신호들을 처리하기 위한 회로를 도시한다. 회로(100)는  $N$ 개의 초음파 트랜스듀서들(102a...102n)을 포함하며, 여기서  $N$ 은 정수이다. 일부 실시예들에서 초음파 트랜스듀서들은 센서들이며, 수신된 초음파 신호들을 나타내는 전기적 신호들을 생성한다. 일부 실시예들에서 초음파 트랜스듀서들은 또한 초음파 신호들을 전송할 수 있다. 일부 실시예들에서 초음파 트랜스듀서들은 용량성 마이크로머신 초음파 트랜스듀서들(capacitive micromachined ultrasonic transducers)(CMUT들)일 수 있다. 일부 실시예들에서 초음파 트랜스듀서들은 압전 마이크로머신 초음파 트랜스듀서들(piezoelectric micromachined ultrasonic transducers)(PMUT들)일 수 있다. 다른 실시예들에서 초음파 트랜스듀서들의 추가의 대안의 유형들이 사용될 수 있다.

[0014]

회로(100)는 또한  $N$ 개의 회로 채널들(104a...104n)을 포함한다. 회로 채널들은 각각의 초음파 트랜스듀서(102a...102n)에 대응할 수 있다. 예를 들어, 8개의 초음파 트랜스듀서들(102a...102n) 및 8개의 대응하는 회로 채널들(104a...104n)이 있을 수 있다. 일부 실시예들에서, 초음파 트랜스듀서들(102a...102n)의 수는 회로 채널들의 수보다 클 수 있다.

[0015]

회로 채널들(104a...104n)은 전송 회로(transmit circuitry), 수신 회로(receive circuitry), 또는 둘 모두를 포함할 수 있다. 전송 회로는 각각의 펄서들(pulsers)(108a...108n)에 결합되는 전송 디코더들(106a...106n)을 포함할 수 있다. 펄서들(108a...108n)은 초음파 신호들을 방출하기 위해 각각의 초음파 트랜스듀서들(102a...102n)을 제어할 수 있다.

[0016]

회로 채널들(104a...104n)의 수신 회로는 각각의 초음파 트랜스듀서들(102a...102n)로부터 출력되는 전기적인 신호들을 수신할 수 있다. 도시된 예시에서, 각각의 회로 채널(104a...104n)은 각각의 수신 스위치(110a...110n) 및 증폭기(112a...112n)를 포함한다. 수신 스위치들(110a...110n)은 주어진 초음파 트랜스듀서(102a...102n)로부터의 전기적인 신호의 판독(readout)을 활성화/비활성화하도록 제어될 수 있다. 보다 일반적으로는, 스위치들에 대한 대안들이 동일한 기능을 수행하기 위해 사용될 수 있기 때문에, 수신 스위치들

(110a...110n)은 수신 회로들일 수 있다. 증폭기들(112a...112n)은 트랜스 임피던스 증폭기들(trans-impedance amplifiers(TIA들))일 수 있다.

[0017] 회로(100)는 본 명세서에서 합산기(summer) 또는 합산 증폭기(summing amplifier)라고도 지칭되는, 평균화 회로(averaging circuit)(114)를 더 포함한다. 일부 실시예들에서, 평균화 회로(114)는 버퍼(buffer) 또는 증폭기이다. 평균화 회로(114)는 증폭기들(112a...112n) 중 하나 이상으로부터 출력 신호들을 수신할 수 있고, 평균화된 출력 신호를 제공할 수 있다. 평균화된 출력 신호는 다양한 증폭기들(112a...112n)로부터의 신호들을 가산 또는 감산함으로써 부분적으로 형성될 수 있다. 평균화 회로(114)는 가변 피드백 저항(variable feedback resistance)을 포함할 수 있다. 가변 피드백 저항의 값은 평균화 회로가 신호를 수신하는 증폭기들(112a...112n)의 수에 기초하여 동적으로 조절될 수 있다. 평균화 회로(114)는 오토-제로 블록(auto-zero block)(116)에 결합된다.

[0018] 오토-제로 블록(116)은 감쇠기(attenuator)(120) 및 고정 이득 증폭기(fixed gain amplifier)(122)를 포함하는 시간 이득 보상 회로(time gain compensation circuit)(118)에 결합된다. 일부 실시예들에서, 감쇠기(120), 뿐만 아니라 도 2a의 감쇠기(200), 도 2b의 감쇠기(220), 도 2c의 감쇠기(240), 및 도 2d의 감쇠기(260)는 가변 감쇠기일 수 있다. 아래에 더 설명될 바와 같이, 하나 이상의 저항기는 인에이블/디스에이블될 수 있고, 그에 따라 감쇠기와 연관된 감쇠를 조정한다.

[0019] 시간 이득 보상 회로(118)는 ADC 드라이버들(124)을 통해 ADC(126)에 결합된다. 도시된 예시에서, ADC 드라이버들(124)은 제1 ADC 드라이버(125a) 및 제2 ADC 드라이버(125b)를 포함한다. ADC(126)는 평균화 회로(114)로부터의 신호(들)를 디지털화한다.

[0020] 도 1이 초음파 디바이스의 회로의 일부로서 다수의 컴포넌트들을 도시하지만, 본 명세서에 기술된 다양한 양태들은 도시된 그대로의 컴포넌트들 또는 컴포넌트들의 구성에 제한되지 않는다는 것을 이해해야 한다. 예를 들어, 본 출원의 양태들은 시간 이득 보상 회로(118)에 관한 것이다.

[0021] 도 1의 컴포넌트들은 단일 기판 상에, 또는 상이한 기판들 상에 위치할 수 있다. 예를 들어, 도시된 바와 같이, 초음파 트랜스듀서들(102a...102n)은 제1 기판(128a) 상에 있을 수 있고, 나머지 도시된 컴포넌트들은 제2 기판(128b) 상에 있을 수 있다. 제1 및/또는 제2 기판들은 실리콘 기판들과 같은 반도체 기판들일 수 있다. 대안의 실시예에서, 도 1의 컴포넌트들은 단일 기판 상에 있을 수 있다. 예를 들어, 초음파 트랜스듀서들(102a...102n) 및 도시된 회로는 동일한 반도체 다이(semiconductor die) 상에 모노리식 집적될(monolithically integrated) 수 있다. 그러한 집적은 초음파 트랜스듀서들로서 CMUT들을 사용함으로써 용이해질 수 있다.

[0022] 실시예에 따르면, 도 1의 컴포넌트들은 초음파 프로브(ultrasound probe)의 일부를 형성한다. 초음파 프로브는 핸드헬드일 수 있다. 일부 실시예들에서, 도 1의 컴포넌트들은 환자가 착용하도록 구성되는 초음파 패치의 일부를 형성한다.

[0023] 고정 이득 증폭기(122)의 이득은 대략 1dB과 100dB 사이의 값들, 대략 3dB과 30dB 사이의 값들, 대략 5dB과 20dB 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

[0024] 일부 실시예들에서, 고정 이득 증폭기(122)는 20dB의 이득을 갖는다.

[0025] 가변 감쇠기(120)의 감쇠는 대략 1dB과 100dB 사이의 값들, 대략 3dB과 30dB 사이의 값들, 대략 5dB과 20dB 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

[0026] 도 2a에 도시되는 회로(200)는 감쇠기(120)의 제한이 아닌 실시예를 나타낸다. 회로(200)는 차동 구성으로 배열된다. 회로(200)는 차동 입력 전압(201) 및 차동 출력 전압(202)을 갖는다. 저항기(203)는 차동 회로의 "+"측과 연관된다. 반면, 직렬 저항기들(204)은 차동 회로의 "-"측과 연관된다. 저항기(203)는 저항기(204)의 저항과 동일한 저항을 가질 수도 있고 가지지 않을 수도 있다. 회로들(201<sub>i</sub>)은 저항기들(203 및 204)의 출력과 출력 전압(202) 사이에 병렬로 배치되고, i는 1과 m 사이의 값들을 취할 수 있다. 일부 실시예들에 따르면, 각각의 회로(210<sub>i</sub>)는 저항기(205<sub>i</sub>), 스위치(206<sub>i</sub>), 및 저항기(207<sub>i</sub>)의 직렬을 포함한다. 저항기(205<sub>i</sub>)는 저항기(207<sub>i</sub>)의 저항과 동일한 저항을 가질 수도 있고 가지지 않을 수도 있다.

[0027] 각각의 스위치(206<sub>i</sub>)는 2개의 가능한 상태들: 닫힘(closed) 또는 열림(open)을 가질 수 있다. 스위치(206<sub>i</sub>)가 닫힌 상태일 때, 회로(210<sub>i</sub>)는 저항기들(205<sub>i</sub> 및 207<sub>i</sub>)의 합과 동일한 저항을 가지는 저항기를 나타낸다. 반대

로, 스위치(206<sub>i</sub>)가 열린 상태일 때, 회로(210<sub>i</sub>)는 무한대의 저항을 갖는다. 일부 실시예들에 따르면, 입력 신호가 보는 전체 저항은 스위치들(206<sub>i</sub>)의 상태를 변경함으로써 달라질 수 있다. 이러한 구성에서, 전체 저항은 길이가  $m$  비트인 디지털 코드에 의해 정의될 수 있고, 여기서 1과 동일한 비트는 닫힌 스위치를 나타내고 0과 동일한 비트는 열린 스위치를 나타낸다. 각각의 스위치(206<sub>i</sub>)는 다른 스위치들의 상태와 독립적으로, 닫힘 또는 열림 상태를 취할 수 있다.

[0028] 저항기들(203 및 204), 및 각각의 저항기(205<sub>i</sub> 및 207<sub>i</sub>)는 대략 1Ω과 10GΩ 사이의 값들, 대략 100Ω과 100MΩ 사이의 값들, 대략 1KΩ과 1MΩ 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

[0029] 일부 실시예들에서, 저항기들(205<sub>i</sub> 및 207<sub>i</sub>)은  $i$ 의 함수로서 상수 인자  $x$ 만큼 점점 증가 또는 감소하도록 선택될 수 있다. 예를 들어, 저항기(205<sub>1</sub>)가  $R$ 로 설정되면, 저항기(205<sub>2</sub>)는  $xR$ 과 같을 수 있고, 저항기(205<sub>3</sub>)는  $x^2R$ 과 같을 수 있으며, 저항기(205<sub>m</sub>)는  $x^{m-1}R$ 과 같을 수 있다. 인자  $x$ 는 대략 0.001과 1000 사이의 값들, 대략 0.1과 10 사이의 값들, 대략 0.5와 2 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

[0030] 일부 실시예들에서,  $i$ 의 임의의 값에 대해, 저항기들(205<sub>i</sub>)은 모두 서로 동일하고, 저항기들(207<sub>i</sub>)은 모두 서로 동일하다.

[0031] 일부 실시예들에서, 고정 감쇠 스테이지(fixed attenuation stage)는 스위치들(206<sub>i</sub>) 중 일부 또는 전부를 닫음으로써, 및 저항기들(203 및 204) 및 각각의 저항기들(205<sub>i</sub> 및 207<sub>i</sub>)을 미리 정의된 값으로 설정함으로써 획득될 수 있다.

[0032] 도 2b에 도시된 회로(220)는 감쇠기(120)의 다른 제한이 아닌 실시예를 나타낸다. 회로(220)는 또한 차동 구성으로 배열된다. 회로(220)는 차동 입력 전압(221) 및 차동 출력 전압(222)을 가진다. 저항기(223)는 차동 회로의 "+"측과 연관된다. 반면, 직렬 저항기(224)는 차동 회로의 "-"측과 연관된다. 저항기(223)는 저항기(224)의 저항과 동일한 저항을 가질 수도 있고 가지지 않을 수도 있다. 회로들(230<sub>i</sub>)의 직렬이 저항기(223)에 직렬로 있고, 여기서  $i$ 는 1과  $m$  사이의 임의의 값을 취할 수 있다. 유사하게, 회로들(231<sub>i</sub>)의 직렬이 저항기(224)에 직렬로 있다. 각각의 회로(230<sub>i</sub>)는 스위치(226<sub>i</sub>)에 병렬로 구성되는 저항기(225<sub>i</sub>)를 포함하고, 회로(231<sub>i</sub>)는 스위치(228<sub>i</sub>)에 병렬로 구성되는 저항기(227<sub>i</sub>)를 포함한다. 저항기들(225<sub>i</sub>)은 저항기(227<sub>i</sub>)의 저항과 동일한 저항을 가질 수도 있고 가지지 않을 수도 있다.

[0033] 각각의 스위치(226<sub>i</sub> 및 228<sub>i</sub>)는 2개의 가능한 상태들: 닫힘 또는 열림을 가질 수 있다. 일부 실시예들에 따르면, 입력 신호가 보는 전체 저항은 각각의 스위치(226<sub>i</sub> 및 228<sub>i</sub>)의 상태를 독립적으로 조정함으로써 달라질 수 있다. 이전에 설명된 병렬 회로에서와 같이, 각각의 스위치의 상태를 결정하기 위해 비트 시퀀스가 사용될 수 있다.

[0034] 저항기들(223 및 224), 및 각각의 저항기(225<sub>i</sub> 및 227<sub>i</sub>)는 대략 1Ω과 10GΩ 사이의 값들, 대략 100Ω과 100MΩ 사이의 값들, 대략 1KΩ과 1MΩ 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

[0035] 일부 실시예들에서, 저항기들(225<sub>i</sub> 및 227<sub>i</sub>)은  $i$ 의 함수로서 상수 인자  $x$ 만큼 점점 증가 또는 감소하도록 선택될 수 있다. 예를 들어, 저항기(225<sub>1</sub>)가  $R$ 로 설정되면, 저항기(225<sub>2</sub>)는  $xR$ 과 같을 수 있고, 저항기(225<sub>3</sub>)는  $x^2R$ 과 같을 수 있으며, 저항기(225<sub>m</sub>)는  $x^{m-1}R$ 과 같을 수 있다. 인자  $x$ 는 대략 0.001과 1000 사이의 값들, 대략 0.1과 10 사이의 값들, 대략 0.5와 2 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

[0036] 일부 실시예들에서,  $i$ 의 임의의 값에 대해, 저항기들(225<sub>i</sub>)은 모두 서로 동일하고, 저항기들(227<sub>i</sub>)은 모두 서로 동일하다.

- [0037] 일부 실시예들에서, 고정 감쇠 스테이지는 스위치들(226<sub>i</sub> 및 228<sub>i</sub>) 중 일부 또는 전부를 단음으로써, 및 저항기들(223 및 224) 및 각각의 저항기들(225<sub>i</sub> 및 227<sub>i</sub>)을 미리 정의된 값으로 설정함으로써 획득될 수 있다.

- [0038] 회로(200)가 감쇠기(120)의 차동 병렬 실시예를 나타내는 반면, 회로(220)는 감쇠기(120)의 차동 직렬 실시예를 나타낸다. 본 기술분야의 통상의 기술자에 의해 이해될 수 있는 바와 같이, 병렬 및 직렬 배열들의 임의의 적합한 조합이 사용될 수 있다.

- [0039] 도 2c에 도시된 회로(240)는 감쇠기(120)의 다른 제한이 아닌 실시예를 나타낸다. 회로(240)는 회로의 -측이 접지에 연결되기 때문에, 단일 종단 구성(single-ended configuration)으로 배열된다. 회로(240)는 단일 종단 입력 전압(241) 및 단일 종단 출력 전압(242)을 갖는다. 회로(240)는 직렬 저항기(243), 및 병렬 회로들(250<sub>i</sub>)을 포함하며, 여기서  $i$ 는 1과  $m$  사이의 임의의 값을 취할 수 있다. 각각의 회로(250<sub>i</sub>)는 스위치(246<sub>i</sub>)에 직렬로 연결되는 저항기(245<sub>i</sub>)를 포함한다.

- [0040] 각각의 스위치(246<sub>i</sub>)는 2개의 가능한 상태들: 닫힘 또는 열림을 가질 수 있다. 일부 실시예들에 따르면, 입력 신호가 보는 전체 저항은 각각의 스위치(246<sub>i</sub>)의 상태를 독립적으로 조정함으로써 달라질 수 있다. 이전에 설명된 병렬 회로들에서와 같이, 각각의 스위치의 상태를 결정하기 위해 비트 시퀀스가 사용될 수 있다.

- [0041] 저항기들(243), 및 각각의 저항기(245<sub>i</sub>)는 대략 1Ω과 10GΩ 사이의 값들, 대략 100Ω과 100MΩ 사이의 값들, 대략 1KΩ과 1MΩ 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

- [0042] 일부 실시예들에서, 저항기들(245<sub>i</sub>)은  $i$ 의 함수로서 상수 인자  $x$ 만큼 점점 증가 또는 감소하도록 선택될 수 있다. 예를 들어, 저항기(245<sub>1</sub>)가  $R$ 로 설정되면, 저항기(245<sub>2</sub>)는  $xR$ 과 같을 수 있고, 저항기(245<sub>3</sub>)는  $x^2R$ 과 같을 수 있으며, 저항기(245<sub>m</sub>)는  $x^{m-1}R$ 과 같을 수 있다. 인자  $x$ 는 대략 0.001과 1000 사이의 값들, 대략 0.1과 10 사이의 값들, 대략 0.5와 2 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

- [0043] 일부 실시예들에서, 저항기들(245<sub>i</sub>)은 모두 서로 동일하다.

- [0044] 일부 실시예들에서,  $i$ 의 임의의 값에 대하여, 고정 감쇠 스테이지는 각각의 스위치(246<sub>i</sub>)를 단음으로써, 및 저항기들(243) 및 각각의 저항기들(245<sub>i</sub>)을 미리 정의된 값으로 설정함으로써 획득될 수 있다.

- [0045] 도 2d에 도시된 회로(260)는 감쇠기(120)의 다른 제한이 아닌 실시예를 나타낸다. 회로(260)는 또한 단일 종단 구성으로 배열된다. 회로(260)는 단일 종단 입력 전압(261) 및 단일 종단 출력 전압(262)을 갖는다. 회로(260)는 회로들(270<sub>i</sub>)에 직렬로 연결된 직렬 저항기(263)를 포함하며, 여기서  $i$ 는 1과  $m$  사이의 임의의 값을 취할 수 있다. 각각의 회로(270<sub>i</sub>)는 스위치(266<sub>i</sub>)에 병렬로 연결되는 저항기(265<sub>i</sub>)를 포함한다.

- [0046] 각각의 스위치(266<sub>i</sub>)는 2개의 가능한 상태들: 닫힘 또는 열림을 가질 수 있다. 일부 실시예들에 따르면, 입력 신호가 보는 전체 저항은 각각의 스위치(266<sub>i</sub>)의 상태를 독립적으로 조정함으로써 달라질 수 있다. 이전에 설명된 병렬 회로들에서와 같이, 각각의 스위치의 상태를 결정하기 위해 비트 시퀀스가 사용될 수 있다.

- [0047] 저항기들(263), 및 각각의 저항기(265<sub>i</sub>)는 대략 1Ω과 10GΩ 사이의 값들, 대략 100Ω과 100MΩ 사이의 값들, 대략 1KΩ과 1MΩ 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

- [0048] 일부 실시예들에서, 저항기들(265<sub>i</sub>)은  $i$ 의 함수로서 상수 인자  $x$ 만큼 점점 증가 또는 감소하도록 선택될 수 있다. 예를 들어, 저항기(265<sub>1</sub>)가  $R$ 로 설정되면, 저항기(265<sub>2</sub>)는  $xR$ 과 같을 수 있고, 저항기(265<sub>3</sub>)는  $x^2R$ 과 같을 수 있으며, 저항기(265<sub>m</sub>)는  $x^{m-1}R$ 과 같을 수 있다. 인자  $x$ 는 대략 0.001과 1000 사이의 값들, 대략 0.1과 10 사이의 값들, 대략 0.5와 2 사이의 값들, 또는 임의의 다른 값 또는 값들의 범위를 가질 수 있다. 다른 값들도 가능하다.

- [0049] 일부 실시예들에서, 저항기들(265<sub>i</sub>)은 모두 서로 동일하다.

- [0050] 일부 실시예들에 따르면, i의 임의의 값에 대하여, 고정 감쇠 스테이지는 스위치들(266<sub>i</sub>) 중 전부 또는 일부를 단음으로써, 및 저항기들(263) 및 각각의 저항기들(265<sub>i</sub>)을 미리 정의된 값으로 설정함으로써 획득될 수 있다.

- [0051] 회로(240)가 감쇠기(120)의 단일 종단 병렬 실시예를 나타내는 반면, 회로(260)는 감쇠기(120)의 단일 종단 직렬 실시예를 나타낸다. 본 기술분야의 통상의 기술자에 의해 이해될 수 있는 바와 같이, 병렬 및 직렬 배열들의 임의의 적합한 조합이 사용될 수 있다.

- [0052] 도 3은 감쇠기(120)의 제한이 아닌 실시예를 도시한다. 회로(300)가 차동 병렬 구성으로 제시되지만, 다른 구성들이 사용될 수 있다. 예를 들어, 차동 직렬 구성, 또는 단일 종단 병렬 구성, 또는 단일 종단 직렬 구성, 또는 그것들의 임의의 다른 적합한 조합이 사용될 수 있다. 본 출원의 일부 제한이 아닌 양태들에 따르면, 스위치들(206<sub>i</sub>)은 도 3에 도시된 바와 같이 상보형 스위치들(complementary switches)에 의해 구현될 수 있다. 상보형 스위치들은 nMOS 트랜지스터(310<sub>i</sub>) 및 pMOS 트랜지스터(311<sub>i</sub>)를 포함할 수 있다. nMOS 트랜지스터(310<sub>i</sub>)의 드레인은 pMOS 트랜지스터(311<sub>i</sub>)의 소스에 연결될 수 있다. nMOS 트랜지스터(310<sub>i</sub>)의 소스는 pMOS 트랜지스터(311<sub>i</sub>)의 드레인에 연결될 수 있다. nMOS 트랜지스터(310<sub>i</sub>)의 게이트는 인버터(315<sub>i</sub>)의 입력 포트에 연결될 수 있고, 인버터의 출력 포트는 pMOS 트랜지스터(311<sub>i</sub>)의 게이트에 연결될 수 있다.

- [0053] 본 기술분야의 통상의 기술자에 의해 쉽게 이해될 수 있는 바와 같이, 도 3이 하나의 pMOS 트랜지스터 및 하나의 nMOS 트랜지스터에 기초한 상보형 스위치들을 도시하지만, 임의의 다른 유형의 트랜지스터들이 사용될 수 있다. 또한, nMOS 트랜지스터만(또는 pMOS 트랜지스터만)을 사용하는 비상보형 스위치가 사용될 수 있다.

- [0054] 본 기술분야의 통상의 기술자에 의해 더 이해될 수 있는 바와 같이, 도 3이 금속 산화물 반도체(metal-oxide-semiconductor)(MOSFET) 트랜지스터들에 기초한 상보형 스위치들을 도시하지만, 임의의 다른 유형의 트랜지스터들이 사용될 수 있다. 트랜지스터들(310<sub>i</sub> 및 311<sub>i</sub>)은 BJT, BiCMOS, JFET, IGFET, MESFET, 또는 임의의 다른 적합한 유형의 트랜지스터에 의해 구현될 수 있다.

- [0055] 일부 실시예들에서, 플립플롭들(flip-flops)(317<sub>i</sub>) - 여기서, i는 1과 m 사이의 임의의 값을 취할 수 있음 - 은 상보형 스위치들(206<sub>i</sub>)의 상태를 설정하기 위해 사용될 수 있다. 각각의 플립플롭(317<sub>i</sub>)의 출력 포트는 각각의 nMOS 트랜지스터(310<sub>i</sub>)의 게이트에 연결될 수 있다. 아래에 더 설명되는 바와 같이, 일부 실시예들에서, 2개의 트랜지스터들의 게이트들을 인버터들(315<sub>i</sub>)을 통해 연결하는 것 대신에, 각각의 플립플롭(317<sub>i</sub>)의 Q 포트는 각각의 nMOS 트랜지스터(310<sub>i</sub>)의 게이트에 연결될 수 있지만, 각각의 플립플롭(317<sub>i</sub>)의  $\overline{Q}$  (Q not) 포트는 각각의 pMOS 트랜지스터(311<sub>i</sub>)의 게이트에 연결될 수 있다. 또한, 각각의 플립플롭(317<sub>i</sub>)의 출력 포트는 후속하는 플립플롭(317<sub>i+1</sub>)의 입력 포트에 연결될 수 있으며, 여기서 i는 1과 m-1 사이의 임의의 값을 취할 수 있다. 본 출원의 일부 양태들에 따르면, 플립플롭들(317<sub>i</sub>)은 집합적으로(collectively) 시프트 레지스터를 나타낸다.

- [0056] 일부 실시예들에서, 플립플롭들(317<sub>i</sub>)은 인코더(350)에 의해 제어될 수 있다. 차례로, 인코더(350)는 프로파일 생성기(profile generator)(351)에 의해 제어될 수 있다. 본 출원의 일부 양태들에 따르면, 프로파일 생성기(351)는 타겟 시간 이득 보상 응답(target time gain compensation response)을 생성하고 원하는 프로파일을 트래킹하기 위해 필요한 제어 신호들을 얻는 회로일 수 있다. 타겟 시간 이득 보상 응답은 사용자에 의해 수동으로 정의되거나, 컴퓨터에 의해 자동으로 정의되거나, 또는 임의의 다른 적합한 방식으로 정의될 수 있다.

- [0057] 도 4는 감쇠기 회로(300)의 제한이 아닌 실시예를 도시한다. 감쇠기(400)가 각각 하나의 상보형 스위치에 대응하는 4개의 감쇠 스테이지를 포함하지만, 임의의 다른 적합한 수의 스테이지들이 사용될 수 있다. 본 출원의 일부 양태들에 따르면, 회로(400) 내에 디지털 회로(401)가 있다. 제한이 아닌 예시에서, 디지털 회로(401)는 4개의 2:1 멀티플렉서들(2-to-1 multiplexers)(470<sub>i</sub>), 4개의 플립플롭들(317<sub>i</sub>)로 구성되는 시프트 레지스터(402)(도 3에서도 도시됨), 4개의 인버터 쌍들(450<sub>i</sub> 및 452<sub>i</sub>), 및 4개의 인버터 쌍들(453<sub>i</sub> 및 454<sub>i</sub>)을 포함한다. 임의의 시점에서, 각각의 플립플롭들(317<sub>i</sub>)은 입력 포트(D<sub>i</sub>)를 통해 1 또는 0의 상태로 설정될 수 있다. 플립플

롭(317<sub>i</sub>)이 시프트 신호(490)에 의해 트리거될 때, 출력 포트(Q<sub>i</sub>)는 D<sub>i</sub>와 동일한 값으로 설정되지만, 출력 포트( $\overline{Q}_i$ )는 반대의 값으로 설정된다. 일부 실시예들에서, 플립플롭(317<sub>i</sub>)은 상승 에지 또는 하강 에지에 의해 트리거될 수 있다. 일부 다른 실시예들에서, 플립플롭(317<sub>i</sub>)은 1 펠스 또는 0 펠스에 의해 트리거될 수 있다. 리셋 신호(492)는 모든 플립플롭들의 상태를 0으로 설정하기 위해 사용될 수 있다. 각각의 포트(Q<sub>i</sub>)는 인버터 쌍(450<sub>i</sub> 및 451<sub>i</sub>)을 통해 각각의 nMOS 트랜지스터(310<sub>i</sub>)의 게이트에 연결될 수 있다. 유사하게, 각각의 포트( $\overline{Q}_i$ )는 인버터 쌍(451<sub>i</sub> 및 452<sub>i</sub>)을 통해 각각의 pMOS 트랜지스터(311<sub>i</sub>)의 게이트에 연결될 수 있다. 인버터 쌍들은 원하지 않은 전압 스파이크들(voltage spikes)이 상보형 스위치들을 작동시키는 것(hitting)을 방지하기 위해 사용될 수 있다.

[0058] 일부 실시예들에서, 2:1 멀티플렉서들(470<sub>i</sub>)은 시프트 레지스터(402)의 각각의 비트의 상태를 설정하기 위해 사용될 수 있다. 각각의 멀티플렉서(470<sub>i</sub>)는 2개의 입력 포트들(A<sub>i</sub> 및 B<sub>i</sub>) 및 하나의 출력 포트(Z<sub>i</sub>)를 가질 수 있다. Inc\_Dec의 값이 0으로 설정될 때, Z<sub>i</sub>는 B<sub>i</sub>의 값과 독립적으로 A<sub>i</sub>의 값을 취할 수 있다. 대조적으로, Inc\_Dec의 값이 1로 설정될 때, Z<sub>i</sub>는 A<sub>i</sub>의 값과 독립적으로 B<sub>i</sub>의 값을 취할 수 있다. 그러나, 임의의 다른 적합한 로직이 사용될 수 있다. 일부 실시예들에서, 포트들(A<sub>i</sub> 및 B<sub>i</sub>)은 프로파일 생성기에 의해 설정될 수 있지만, 모든 다른 포트(A<sub>i</sub> 및 B<sub>i</sub>)는 인접 플립플롭의 출력(Q)에 의해 설정된다. 제한이 아닌 예시에서, A<sub>i</sub>는 Q<sub>i-1</sub>에 의해 설정될 수 있고, B<sub>i</sub>는 Q<sub>i+1</sub>에 의해 설정될 수 있다.

[0059] 일부 실시예들에서, Inc\_Dec 신호(491)가 0으로 설정되고 레지스터가 시프트 신호(490)에 의해 트리거될 때, 레지스터 내에 저장되는 비트들은 최하위 플립플롭(the least significant flip-flop)(317<sub>1</sub>)으로부터 최상위 플립플롭(the most significant flip-flop)(317<sub>4</sub>)으로 시프트할 수 있다. 대조적으로, Inc\_Dec이 1로 설정되고 레지스터가 시프트 신호(490)에 의해 트리거될 때, 레지스터 내에 저장되는 비트들은 최상위 플립플롭(317<sub>4</sub>)으로부터 최하위 플립플롭(317<sub>1</sub>)으로 시프트할 수 있다.

[0060] 도 5는 디지털 회로(401)의 동작의 제한이 아닌 예시를 도시한다. 차트의 상부는 3개의 제어 신호들: 시프트 신호(490), Inc\_Dec 신호(491), 및 리셋 신호(492)를 도시한다. 차트의 하부는 3개의 제어 신호들에 대한 응답으로 시프트 레지스터의 각각의 플립플롭의 상태를 도시하며, 여기서 FF<sub>i</sub>는 도 4의 플립플롭(317<sub>i</sub>)을 나타낸다. T<sub>1</sub>에서 T<sub>4</sub>까지, 제어 신호 Inc\_Dec이 0으로 설정되는 것에 응답하여, 레지스터는 비트들을 FF<sub>4</sub>를 향해 시프트한다. 회로가 시프트 신호(490)에 의해 트리거될 때 시프트가 발생한다. T<sub>5</sub>에서 T<sub>8</sub>까지, 제어 신호 Inc\_Dec이 1로 설정되는 것에 응답하여, 레지스터는 비트들을 FF<sub>1</sub>을 향해 시프트한다. 제한이 아닌 예시에서, 리셋이 항상 0으로 설정되지만, 언제든지 1로 설정되어 각각의 플립플롭의 상태를 0으로 설정할 수 있다.

[0061] 도 6은 가변 감쇠기(120) 및 고정 이득 증폭기(122)를 포함할 수 있는 시간 이득 보상 회로(118)에 의해 생성되는 시간 의존 응답의 제한이 아닌 예시를 도시한다. 차트(600)는 시간의 함수로서 3개의 신호들을 도시한다. 콕선(611)은 하나 이상의 트랜스듀서(102<sub>i</sub>)에 의해 수신되고, 타겟을 향해 초음파를 송신함으로써 획득되는 응답을 도시한다. 타겟은 깊이의 함수로서 다양한 크기를 갖는 다중 반사들을 야기하는 다중 층들을 포함할 수 있다. 커브(611)는 다층(multilayered) 타겟에 의해 야기될 수 있는 딥(dip)을 도시한다. 일부 실시예들에서, 명확한 초음파 이미지를 획득하기 위해서, 커브(631)에 의해 도시되는 바와 같이 시간의 함수로서 균일한 응답을 갖는 것이 바람직할 수 있다. 결과적으로, 프로파일 생성기(351)는 깊이 의존 반사들에 의해 야기되는 손실들을 보상하는 이득 응답을 제공하기 위해 제어 신호들을 얻을 수 있다. 커브(621)는 그러한 이득 응답의 제한이 아닌 예시이다.

[0062] 일부 실시예들에서, 각각의 2진 감쇠 스테이지는 약 0.2dB의 감쇠를 제공할 수 있다.

[0063] 일부 다른 실시예들에서, 보상된 신호가 임의의 적합한 시간 의존 동작을 가지도록 야기하는 이득 응답을 생성하는 것이 바람직할 수 있다. 예를 들어, 초음파 이미지의 콘트라스트를 개선하기 위해, 타겟의 하나의 층의 응답을 확대하면서 다른 층의 응답을 감쇠하는 것이 바람직할 수 있다. 시간 이득 보상 응답은 사용자에 의해 수동으로 정의되거나, 컴퓨터에 의해 자동으로 정의되거나, 또는 임의의 다른 적합한 방식으로 정의될 수 있다.

- [0064] 이와 같이 본 출원의 기술의 여러 양태들 및 실시예들을 설명하면서, 본 기술분야의 통상의 기술자에게 다양한 변경들, 수정들, 및 개선들이 쉽게 떠오를 수 있다는 것을 이해할 것이다. 그러한 변경들, 수정들, 및 개선들은 본 출원에 설명된 기술의 사상 및 범주 내에 있는 것으로 의도된다. 따라서, 전술한 실시예들은 단지 예로서 제시되고, 첨부된 청구범위 및 그 등가물의 범주 내에서 발명의 실시예들은 구체적으로 설명된 것과 달리 실시될 수 있음이 이해될 것이다.

- [0065] 기술된 바와 같이, 일부 양태들이 하나 이상의 방법으로서 구현될 수 있다. 방법(들)의 일부로서 수행되는 액트들은 임의의 적합한 방식으로 순서가 정해질 수 있다. 따라서, 예시된 실시예들에서 순차적인 액트들로 도시되어 있지만, 일부 액트들을 동시에 수행하는 것을 포함할 수 있는, 도시된 것과 상이한 순서로 액트들이 수행되는 실시예들이 구성될 수 있다.

- [0066] 본 명세서에서 정의되고 사용된 바와 같이, 모든 정의들은 사전적 정의들, 참조로 통합된 문헌들 내의 정의들, 및/또는 정의된 용어들의 통상적 의미들을 제어하는 것으로 이해되어야 한다.

- [0067] 본 명세서 및 청구범위에서 사용되는 바와 같은 문구 "및/또는(and/or)"은 이와 같이 결합된 요소들, 즉 일부 경우들에서 결합적으로 존재하고 다른 경우들에서는 분리적으로 존재하는 요소들의 "어느 하나 또는 둘 모두(either or both)"를 의미하는 것으로 이해되어야 한다.

- [0068] 본 명세서 및 청구범위에서 사용되는 바와 같이, 하나 이상의 요소들의 리스트와 관련하여 문구 "적어도 하나(at least one)"는 요소들의 리스트 내의 임의의 하나 이상의 요소로부터 선택되는 적어도 하나의 요소를 의미하지만, 요소들의 리스트 내의 구체적으로 나열된 각각의 모든 요소 중 적어도 하나를 반드시 포함하지 않으며, 요소들의 리스트 내의 요소들의 임의의 조합을 반드시 제외하지 않는다는 점이 이해되어야 한다.

- [0069] 본 명세서에서 사용된 바와 같이, 수치적 맥락에서 사용되는 용어 "사이(between)"는 달리 지시되지 않는 한 포함적이다. 예를 들어, "A와 B 사이"는 달리 지시되지 않는 한 A 및 B를 포함한다.

- [0070] 청구항에서는 물론 위의 명세서에서, "포함하는(comprising)", "포함하는(including)", "반송하는", "가지는", "함유하는", "수반하는", "보유하는", "~로 구성된" 등과 같은 모든 과도적 구문(transitional phrases)들은 개방형인 것으로, 즉, 이를 포함하지만 이에 제한되지 않음을 의미하는 것으로 이해될 것이다. 과도적 구문들 "~로 구성된" 및 "본질적으로 ~로 구성된"만이, 각자 폐쇄형 또는 반-폐쇄형(semi-closed) 과도적 구문들일 것이다.

도면

도면1

도면2a

도면2b

도면2c

도면2d

도면3

## 도면4

도면5

도면6