(12) 发明专利

(10) 授权公告号 CN 109155255 B

(45) 授权公告日 2021.08.27

(21) 申请号 201780031618.6

星真一

(22) 申请日 2017.04.06

(74) 专利代理机构 永新专利商标代理有限公司

72002

(65) 同一申请的已公布的文献号

代理人 吕文卓

申请公布号 CN 109155255 A

(51) Int.CI.

H01L 21/338 (2006.01)

H01L 21/336 (2006.01)

H01L 21/337 (2006.01)

H01L 29/778 (2006.01)

H01L 29/78 (2006.01)

H01L 29/808 (2006.01)

H01L 29/812 (2006.01)

(43) 申请公布日 2019.01.04

(30) 优先权数据

2016-103352 2016.05.24 JP

2016-237723 2016.12.07 JP

(85) PCT国际申请进入国家阶段日

2018.11.22

(86) PCT国际申请的申请数据

PCT/JP2017/014410 2017.04.06

(87) PCT国际申请的公布数据

W02017/203849 JA 2017.11.30

(73) 专利权人 株式会社电装

地址 日本爱知县

(72) 发明人 樽见浩幸 小山和博 阴泳信

(56) 对比文件

CN 102629866 A, 2012.08.08

CN 103022121 A, 2013.04.03

US 2016/0093691 A1, 2016.03.31

CN 103314438 A, 2013.09.18

审查员 张玉萍

权利要求书2页 说明书11页 附图14页

(54) 发明名称

半导体装置

(57) 摘要

将JG电极(11)与源极电极(8)经由电极层(13)直接连结。由此，能够减小寄生阻抗(50)的电阻值，实现JG电极(11)与源极电极(8)之间的阻抗减小。此外，将u-GaN层(4)及p-GaN层(10)从漏极电极(9)离开而配置。由此，能够使u-GaN层(4)与2DEG的对置面积变小，能够减小反馈电容(C1)。这样，通过实现JG电极(11)与源极电极(8)之间的阻抗减小及反馈电容(C1)的减小，能够使将反馈电容(C1)充电时流动的电流(I<sub>jg</sub>)变大。由此，能够将反馈电容(C1)以高速充电，能够使JFET部(40)高速截止，所以能够使开关器件的关断更高速化。

1. 一种半导体装置，具有横型的开关器件，其特征在于，

该开关器件具备：

沟道形成层(2、3)，形成在由导电性材料构成的基板上，具有由第1半导体层(2)及第2半导体层(3)构成的异质结构，在上述第2半导体层形成有凹口部(5)，上述第1半导体层(2)由构成漂移区域的第1GaN类半导体构成，上述第2半导体层(3)由与上述第1GaN类半导体相比带隙能量大的第2GaN类半导体构成；

栅极构造部，具有形成在上述凹口部内的栅极绝缘膜(6)及形成在该栅极绝缘膜之上的作为MOS构造的栅极电极的MOS栅极电极(7)；

源极电极(8)及漏极电极(9)，在上述第2半导体层之上配置在夹着上述栅极构造部的两侧；

第3半导体层(4)，在上述第2半导体层之上配置在上述栅极构造部与上述漏极电极之间的从上述漏极电极离开了的位置，由没有被掺加杂质的第3GaN类半导体构成；

第4半导体层(10)，由形成在上述第3半导体层之上的p型的第4GaN类半导体构成；以及

结型栅极电极(11)，与上述第4半导体层接触；

上述源极电极与上述结型栅极电极经由在将上述MOS栅极电极覆盖的层间绝缘膜(12)

之上形成的电极层(13)而连结；

相对于上述第4半导体层的上述漏极电极侧的端部，上述第3半导体层的上述漏极电极侧的端部向上述漏极电极侧突出的距离为1μm以上且5μm以下。

2. 如权利要求1所述的半导体装置，其特征在于，

将形成有上述开关器件的区域作为有源区域(14)；

上述电极层至少形成在上述有源区域，在上述有源区域中上述源极电极与上述结型栅极电极经由上述电极层而连结。

3. 如权利要求2所述的半导体装置，其特征在于，

上述MOS栅极电极将一个方向作为较长方向而延伸设置；

上述电极层在上述有源区域内沿着上述MOS栅极电极的延伸设置方向分为多个而配置为梯子状；

在分为多个而配置为梯子状的上述电极层之间，上述MOS栅极电极连接到栅极焊盘(17)。

4. 如权利要求1所述的半导体装置，其特征在于，

上述第3半导体层与上述栅极构造部相接，与上述栅极构造部相比配置在更靠上述漏极电极侧并且还配置在更靠上述源极电极侧。

5. 如权利要求1所述的半导体装置，其特征在于，

将在上述开关器件关断时、经过上述结型栅极电极及上述源极电极而流动的电流路径的电阻成分的电阻值作为结型栅极一源极间电阻值；

上述结型栅极一源极间电阻值为200Ωmm以下。

6. 如权利要求1所述的半导体装置，其特征在于，

将在上述开关器件关断时、经过上述结型栅极电极及上述源极电极而流动的电流路径的电阻成分的电阻值作为结型栅极一源极间电阻值；

上述结型栅极一源极间电阻值为100Ωmm以下。

7. 如权利要求5或6所述的半导体装置,其特征在于,

上述结型栅极一源极间电阻值是上述第3半导体层的内部电阻、上述第4半导体层的内部电阻、上述第4半导体层与上述结型栅极电极的接触电阻、和从上述结型栅极电极到上述源极电极之间的电极电阻的合计电阻值。

8. 如权利要求1~4中任一项所述的半导体装置,其特征在于,

上述第4半导体层与上述结型栅极电极的接触电阻为 $100 \Omega \text{ mm}$ 以下。

## 半导体装置

[0001] 相关申请的相互参照

[0002] 本申请基于2016年5月24日提出的日本专利申请第2016-103352号和2016年12月7日提出的日本专利申请第2016-237723号主张优先权,这里通过参照而引用其记载内容。

### 技术领域

[0003] 本发明涉及在基板之上层叠氮化镓(以下称作GaN)、氮化铝镓(以下称作AlGaN)等、具备由第1GaN类半导体层和第2GaN类半导体层形成的异质结构造的半导体装置。

### 背景技术

[0004] 以往,在非专利文献1中,作为具备异质结构造的横型的开关器件,提出了4端子构造的HEMT(High electron mobility transistor:高电子迁移率晶体管)。

[0005] 在该开关器件中,通过在蓝宝石等基板之上层叠i-GaN层和i-AlGaN层而构成异质结构造。以将i-AlGaN层贯通而到达i-GaN层的方式,形成有MOS构造的栅极电极(以下称作MOS栅极电极),在i-AlGaN层的表面上的夹着MOS栅极电极的两侧形成有源极电极和漏极电极。此外,在MOS栅极电极与漏极电极之间,在i-AlGaN层的表面形成有i-GaN层和p-GaN层的层叠构造,进而在p-GaN层的表面形成有结型栅极电极(以下称作JG电极)。形成在i-AlGaN层上的i-GaN层及p-GaN层比JG电极更向漏极电极方向伸出而形成到漏极电极附近。

[0006] 这样,通过在源极电极与漏极电极之间配置JG电极和MOS栅极电极而做成4端子构造的开关器件。

[0007] 现有技术文献

[0008] 非专利文献

[0009] 非专利文献1:河合弘治、共同研究者中島昭、“GaN功率器件—通过新技术实现低成本化”、NE电子技术研讨会“GaN功率器件”,2011年11月8日、化学会馆(河合弘治、共同研究者中島昭、「GaNパワーデバイス—新技術により低コスト化を目指すー」、NEエレクトロニクスセミナー“GaNパワーデバイス”2011年11月8日、化学会館)

### 发明概要

[0010] 但是,在上述那样的构造的半导体装置中,在JG电极与漏极电极之间形成的寄生电容、更详细地讲通过偏振结(Polarization Junction)构成的寄生电容较大。因此,开关器件截止时向寄生电容充电会花费时间,使在JG电极侧构成的JFET截止变慢,有不利于高速开关的问题。

[0011] 此外,在构成4端子构造的开关器件的情况下,可以考虑将JG电极与源极电极用键合线电连接从而使它们成为相同电位,但如果做成这样的连接形态,则JG电极与源极电极之间的阻抗变大,不利于高速开关。

### 发明内容

[0012] 本发明鉴于上述问题，目的在于提供具有实现高速开关的开关器件的具备结型构造的半导体装置。

[0013] 本发明的一个技术方案的具有横型的开关器件的半导体装置，具备：沟道形成层，形成在基板上，具有由第1半导体层及第2半导体层构成的异质结构，在第2半导体层形成有凹口部，上述第1半导体层由构成漂移区域的第1GaN类半导体构成，上述第2半导体层由与第1GaN类半导体相比带隙能量大的第2GaN类半导体构成；栅极构造部，具有形成在凹口部内的栅极绝缘膜及形成在该栅极绝缘膜之上的作为MOS构造的栅极电极的MOS栅极电极；源极电极及漏极电极，在第2半导体层之上配置在夹着栅极构造部的两侧；第3半导体层，在第2半导体层之上配置在栅极构造部与漏极电极之间的从漏极电极离开了的位置，由没有被刻意掺加杂质的第3GaN类半导体构成；第4半导体层，形成在第3半导体层之上，由p型的第4GaN类半导体构成；以及JG电极，与第4半导体层接触。在这样的结构中，源极电极与JG电极经由在将MOS栅极电极覆盖的层间绝缘膜之上形成的电极层而连结；相对于第4半导体层的漏极电极侧的端部，第3半导体层的漏极电极侧的端部向漏极电极侧突出的距离为 $0\mu\text{m}$ 以上且 $5\mu\text{m}$ 以下。

[0014] 这样，将JG电极与源极电极经由电极层直接连结。因此，能够使寄生电阻及寄生电感降低。此外，通过将第3半导体层及第4半导体层从漏极电极离开而配置，使第3半导体层与2DEG的对置面积尽可能变小。因此，能够减小寄生电容。

[0015] 这样，通过经由结型栅极实现JFET部的漏极与源极电极之间的L、C、R的阻抗减小，能够将寄生电容以高速充电。并且，由于能够使JFET部高速截止，所以能够使开关器件的关断更高速化。因而，得到实现更高速开关的开关器件。

## 附图说明

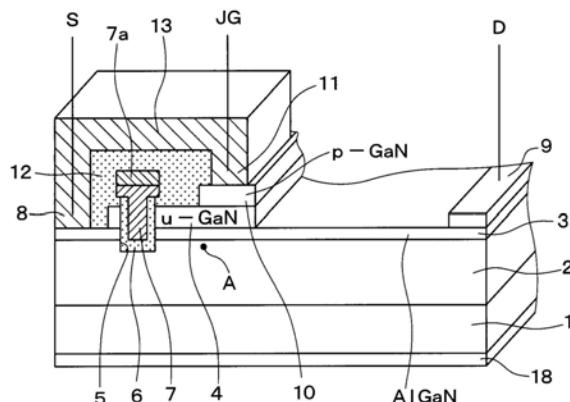

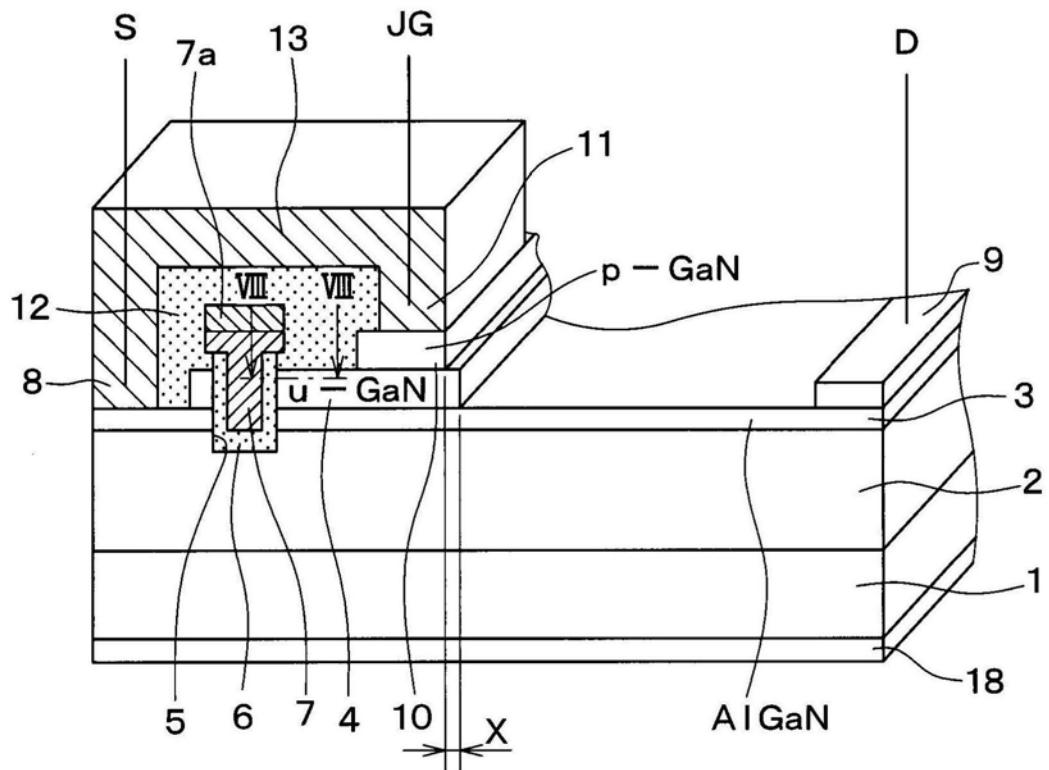

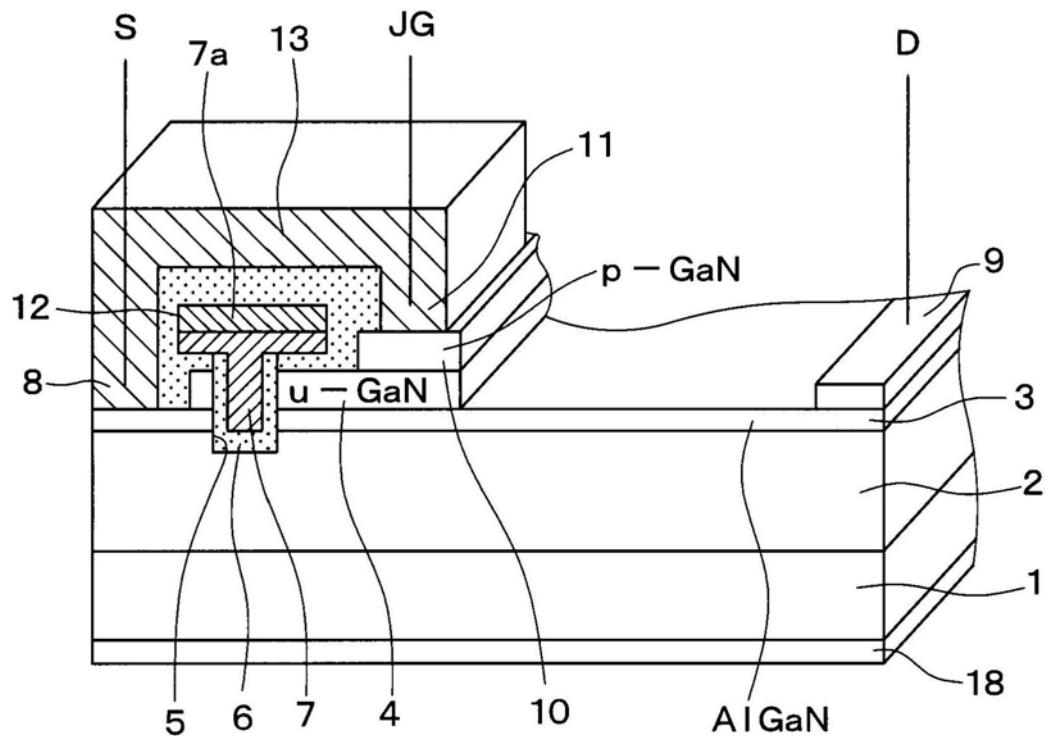

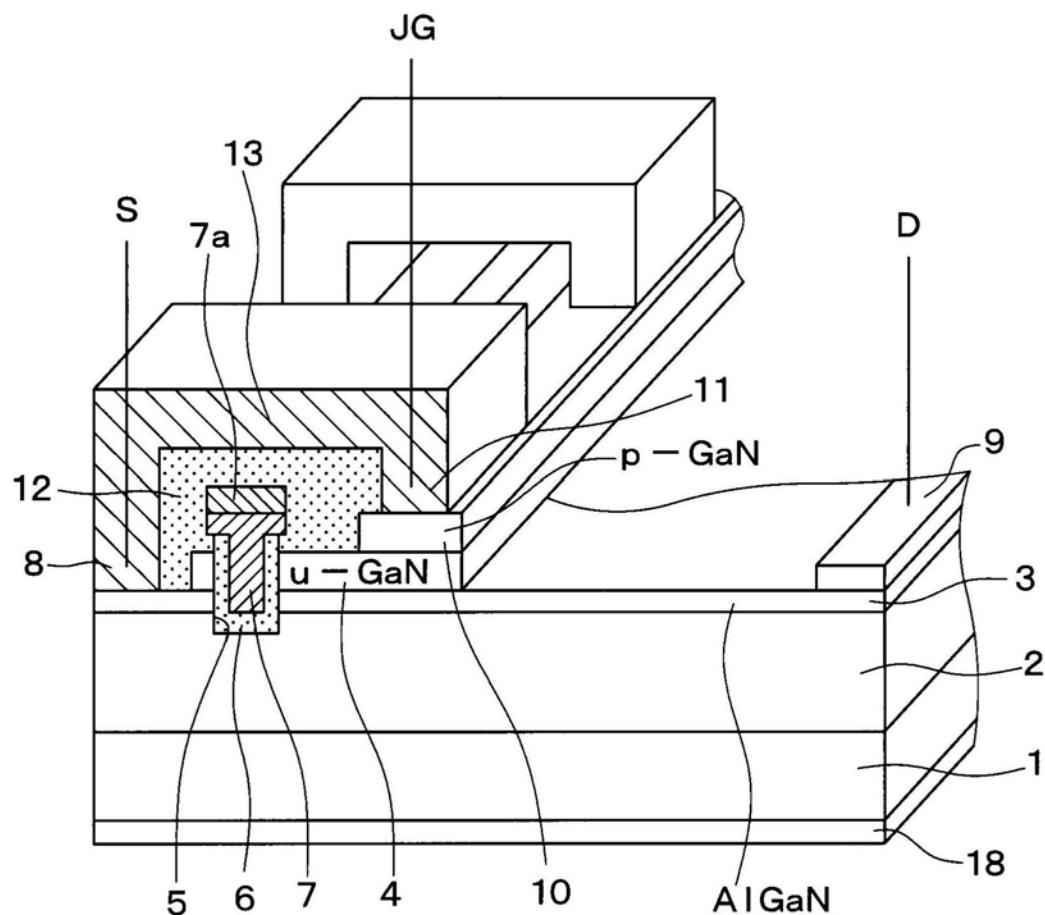

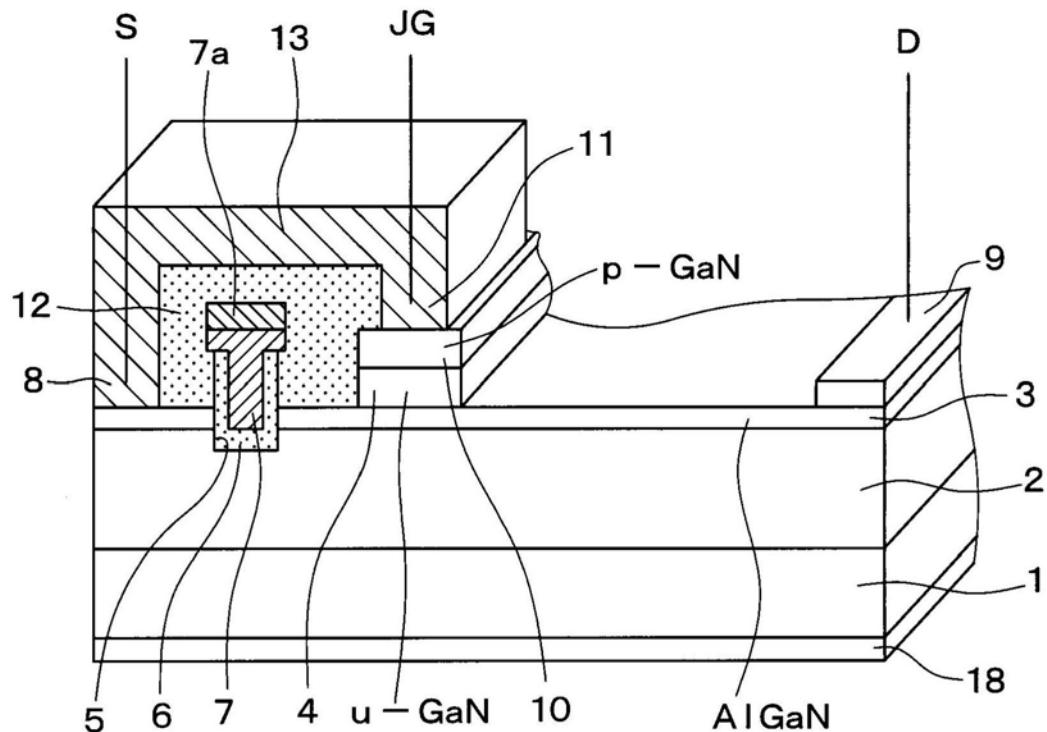

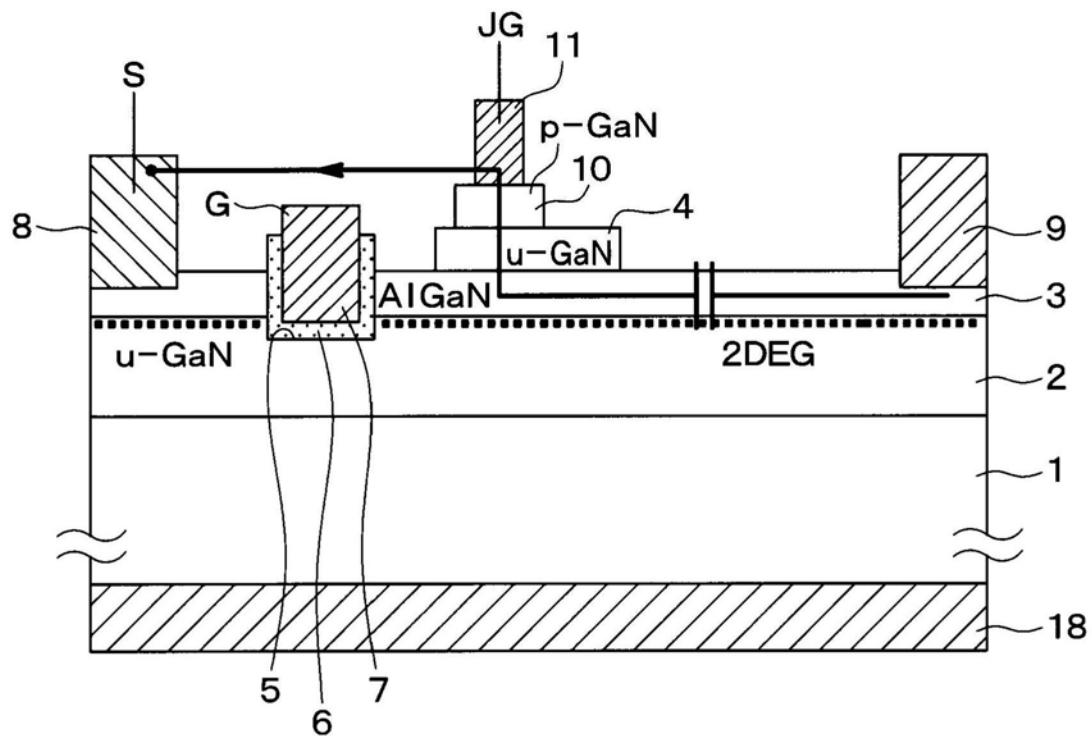

- [0016] 图1是第1实施方式的半导体装置的截面立体图。

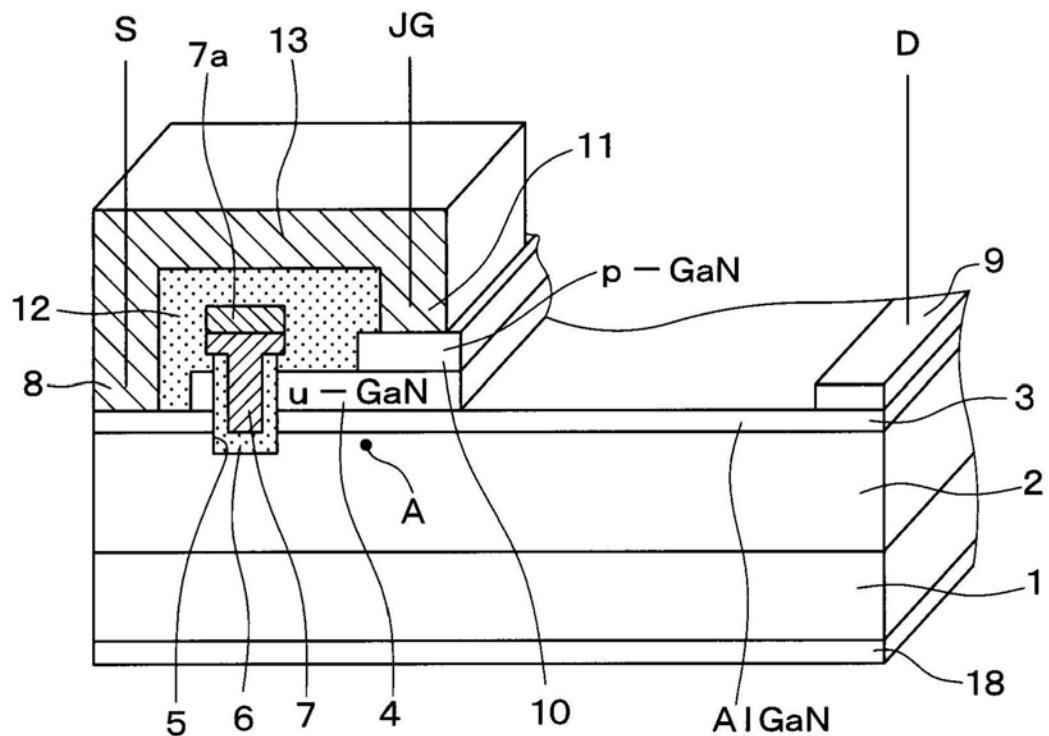

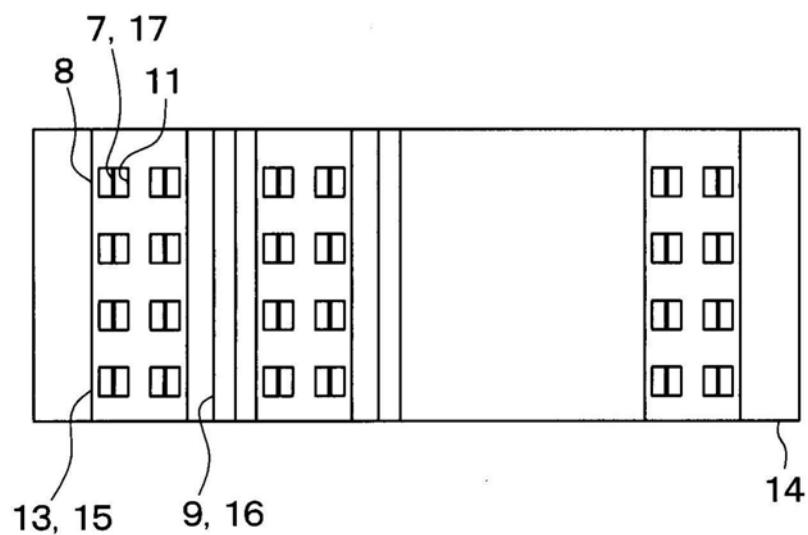

- [0017] 图2是图1所示的半导体装置的上表面布局图。

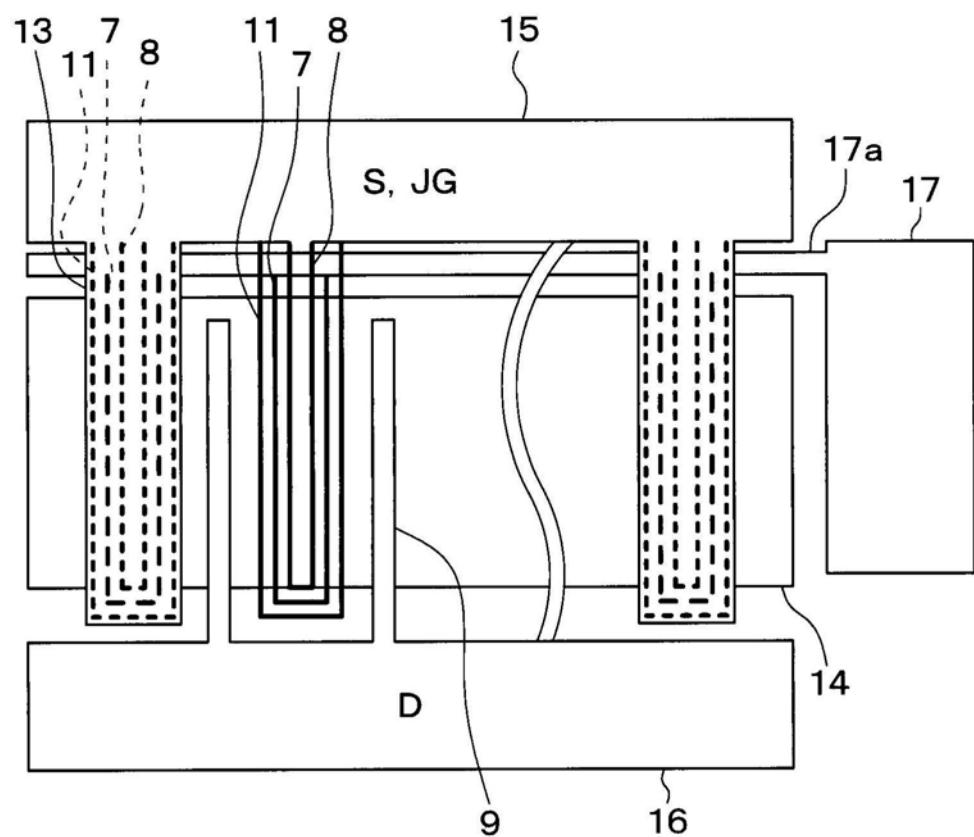

- [0018] 图3是图1所示的开关器件的等价电路。

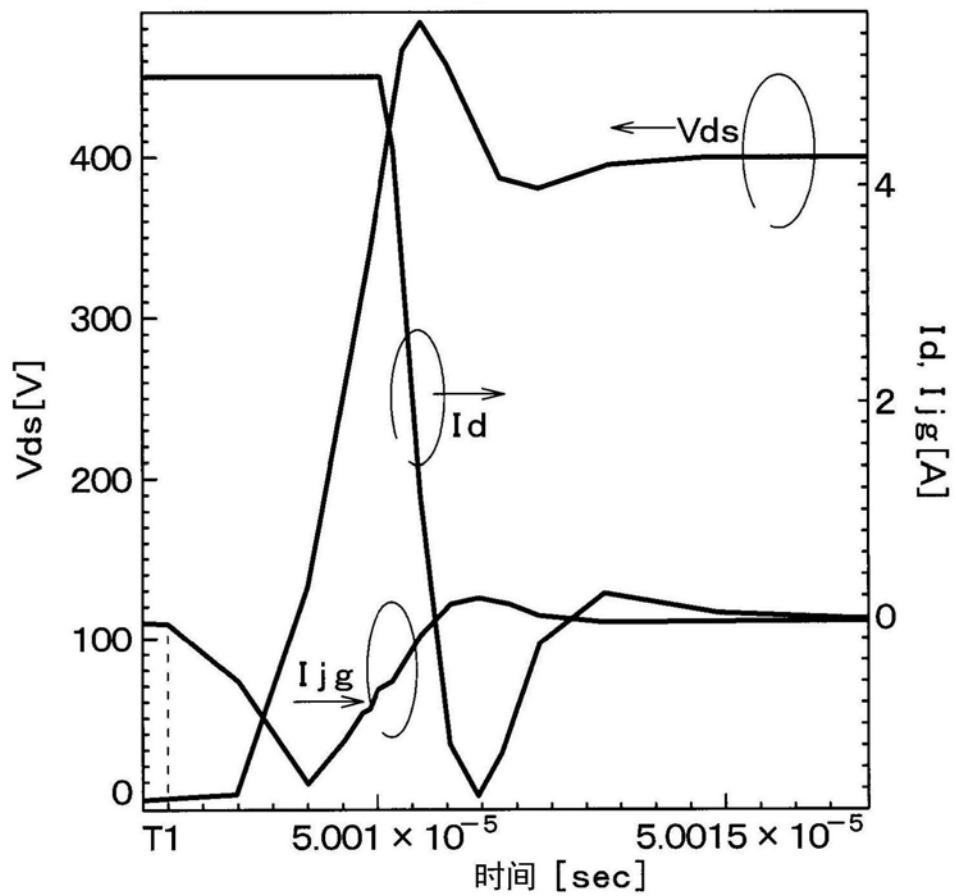

- [0019] 图4是表示关断(turn off)时的各部的电流值及电压值的变化的图。

- [0020] 图5是表示图1所示的半导体装置中的距离X的图。

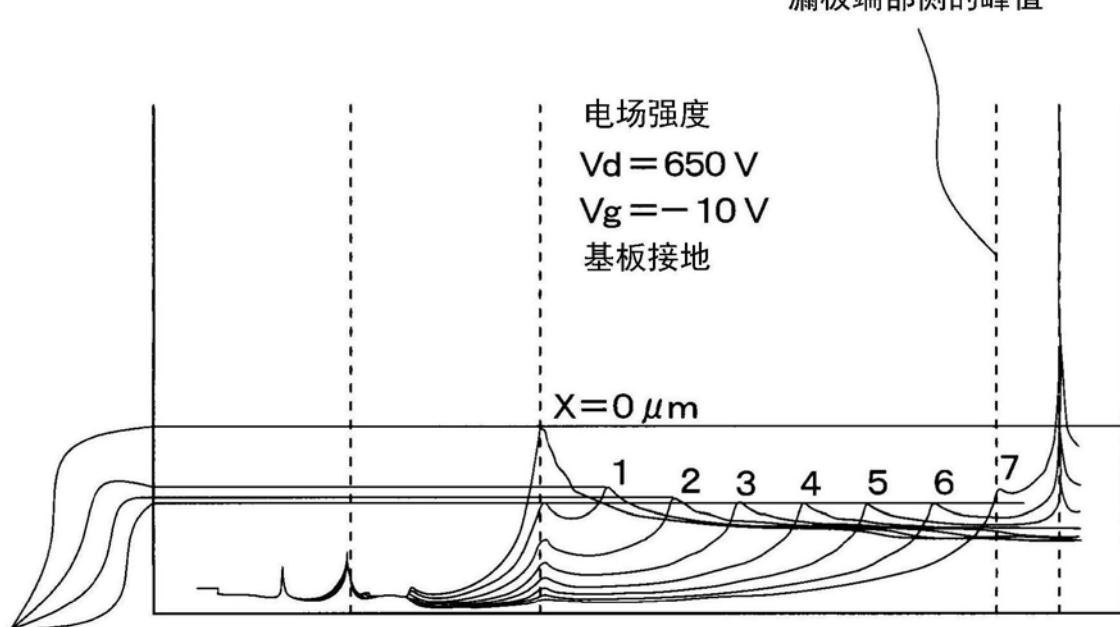

- [0021] 图6是表示将距离X改变而进行了模拟时的电场强度分布的图。

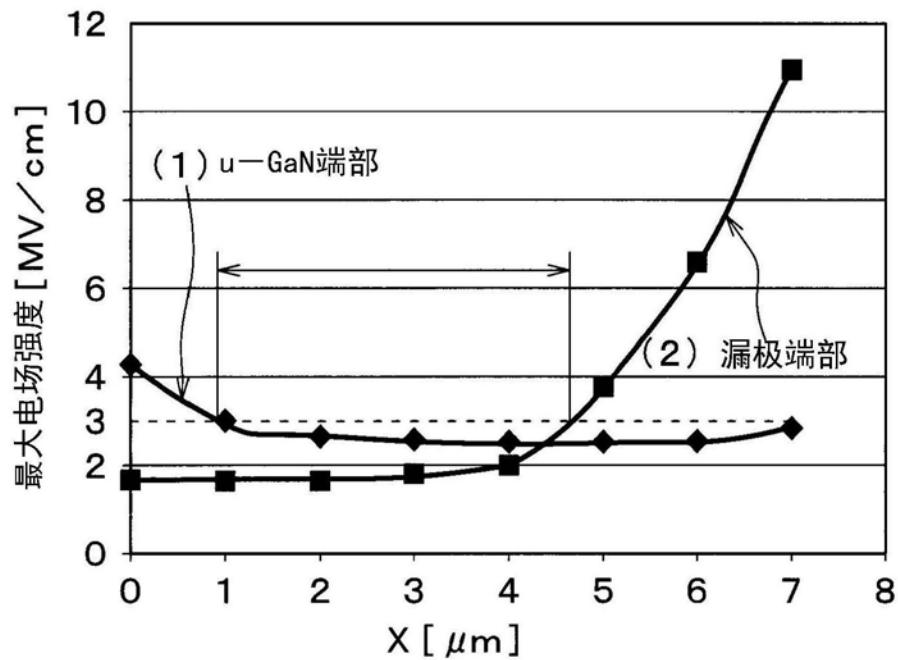

- [0022] 图7是标绘了对应于距离X的电场强度的变化的图。

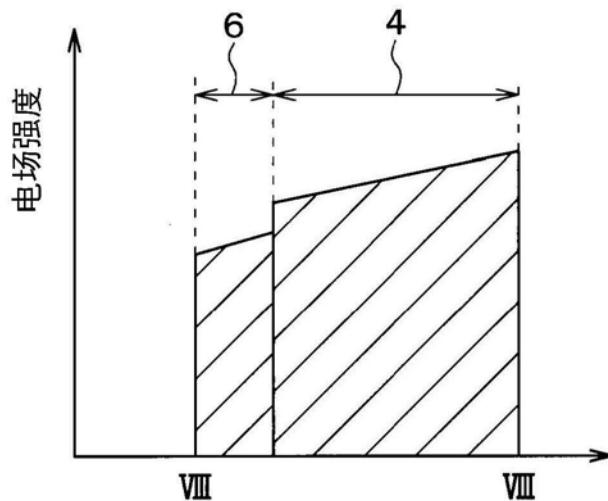

- [0023] 图8是表示图5中的VIII—VIII线上的电场强度分布的图。

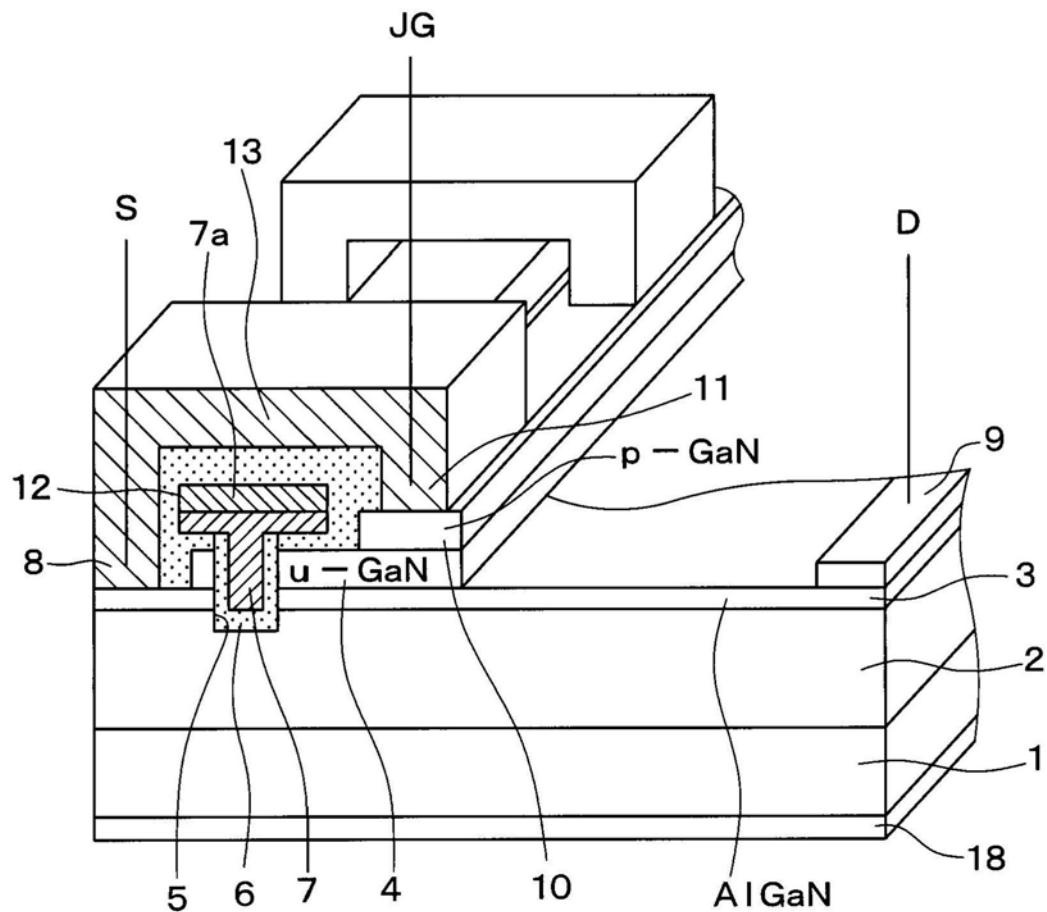

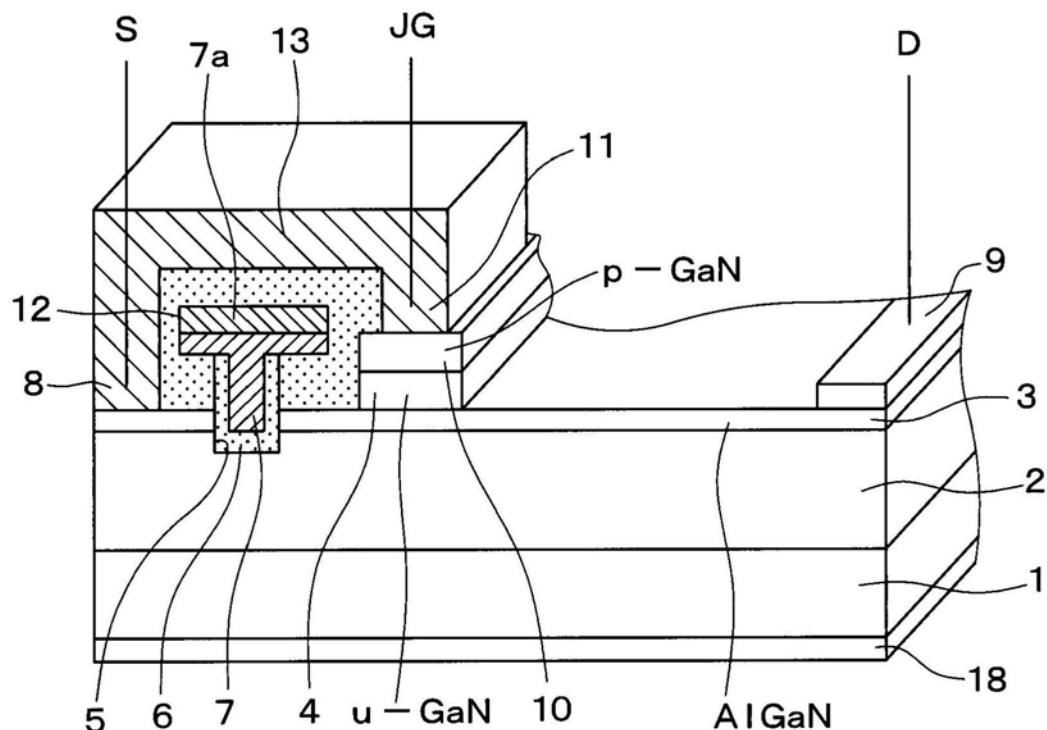

- [0024] 图9是第2实施方式的半导体装置的截面立体图。

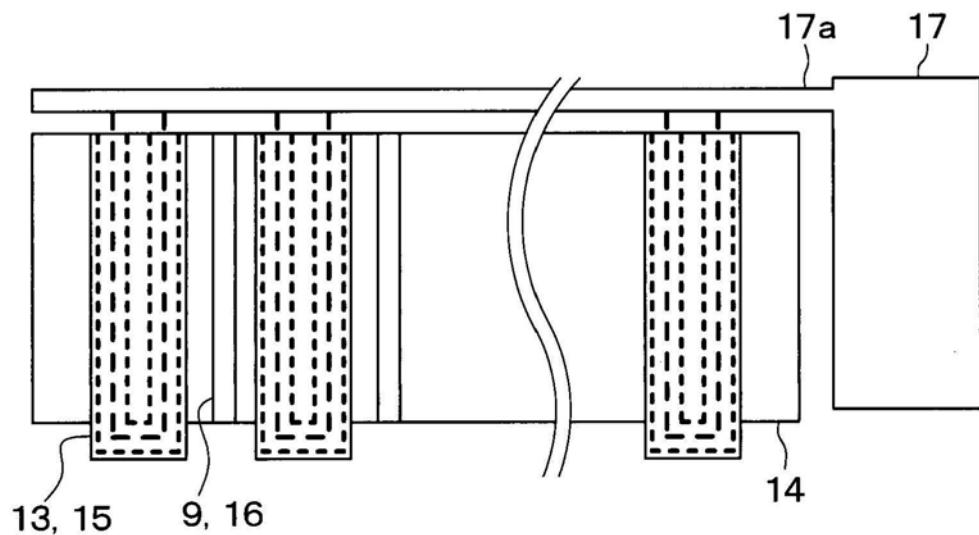

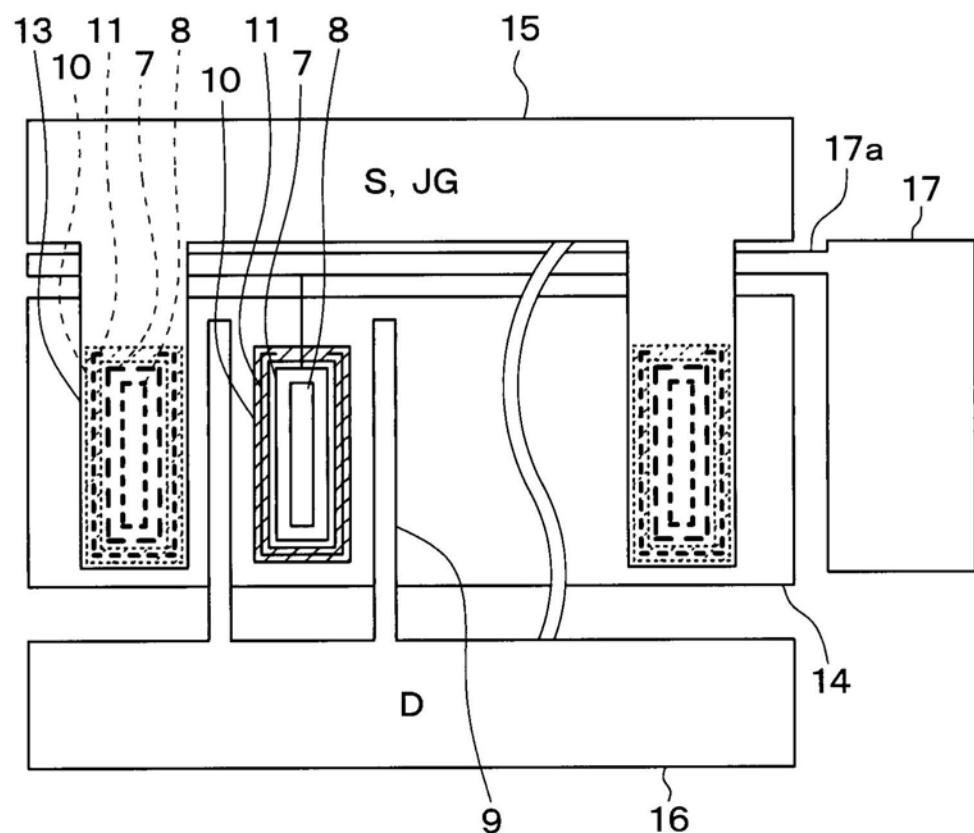

- [0025] 图10是第3实施方式的半导体装置的上表面布局图。

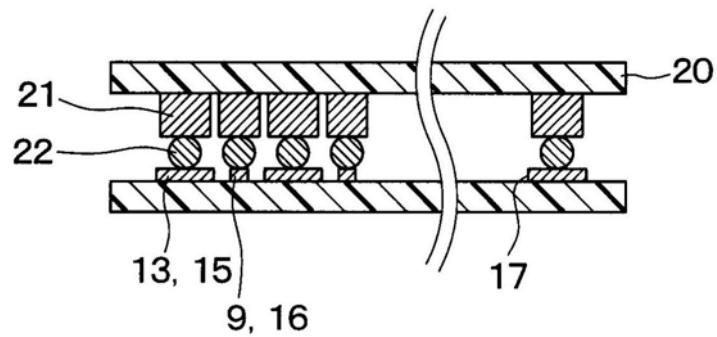

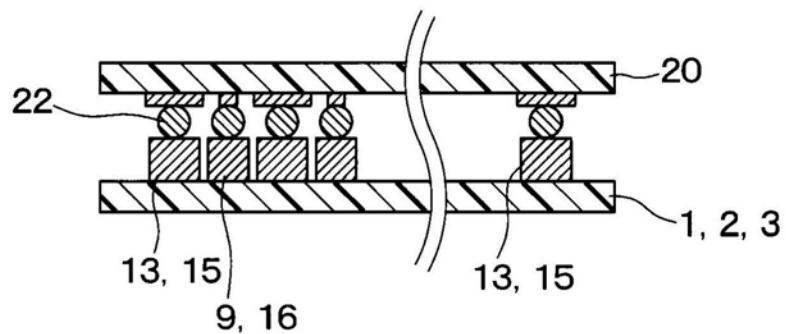

- [0026] 图11A是表示图10所示的半导体装置的凸块连接构造的一例的剖视图。

- [0027] 图11B是表示图10所示的半导体装置的凸块连接构造的另一例的剖视图。

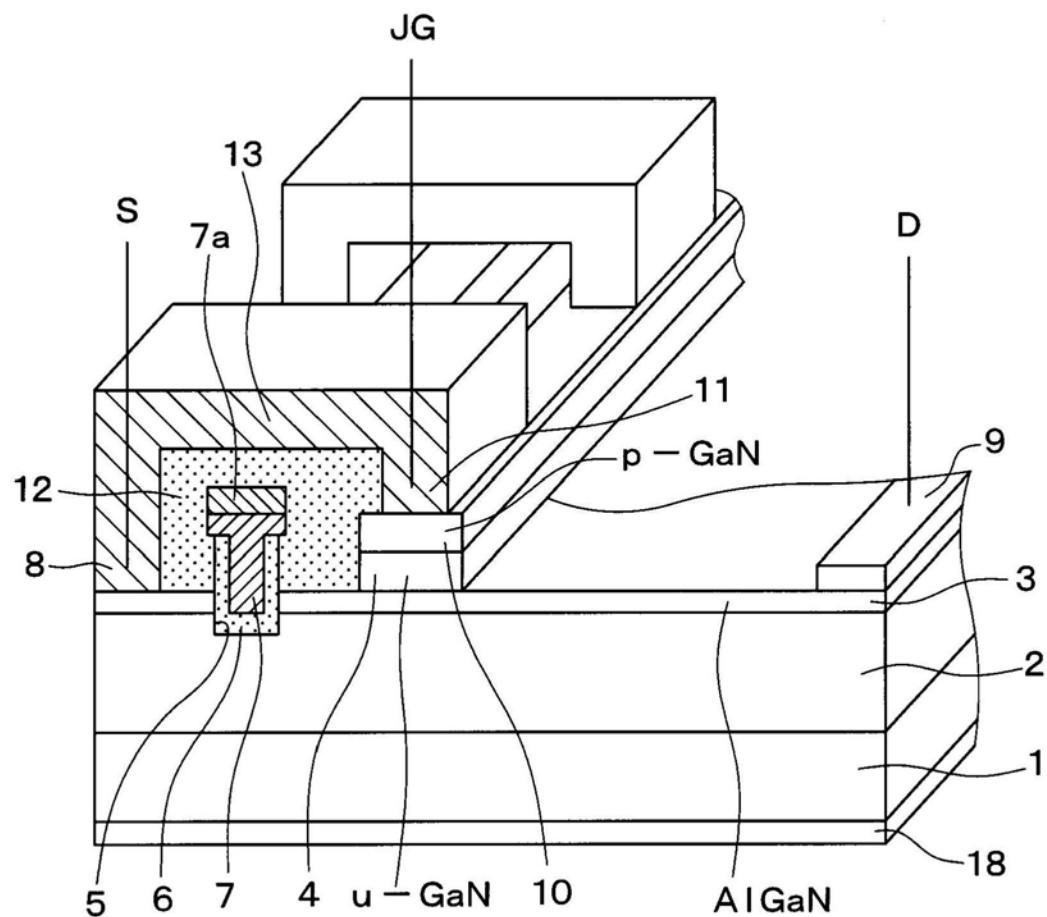

- [0028] 图12是第4实施方式的半导体装置的截面立体图。

- [0029] 图13是第4实施方式的半导体装置的上表面布局图。

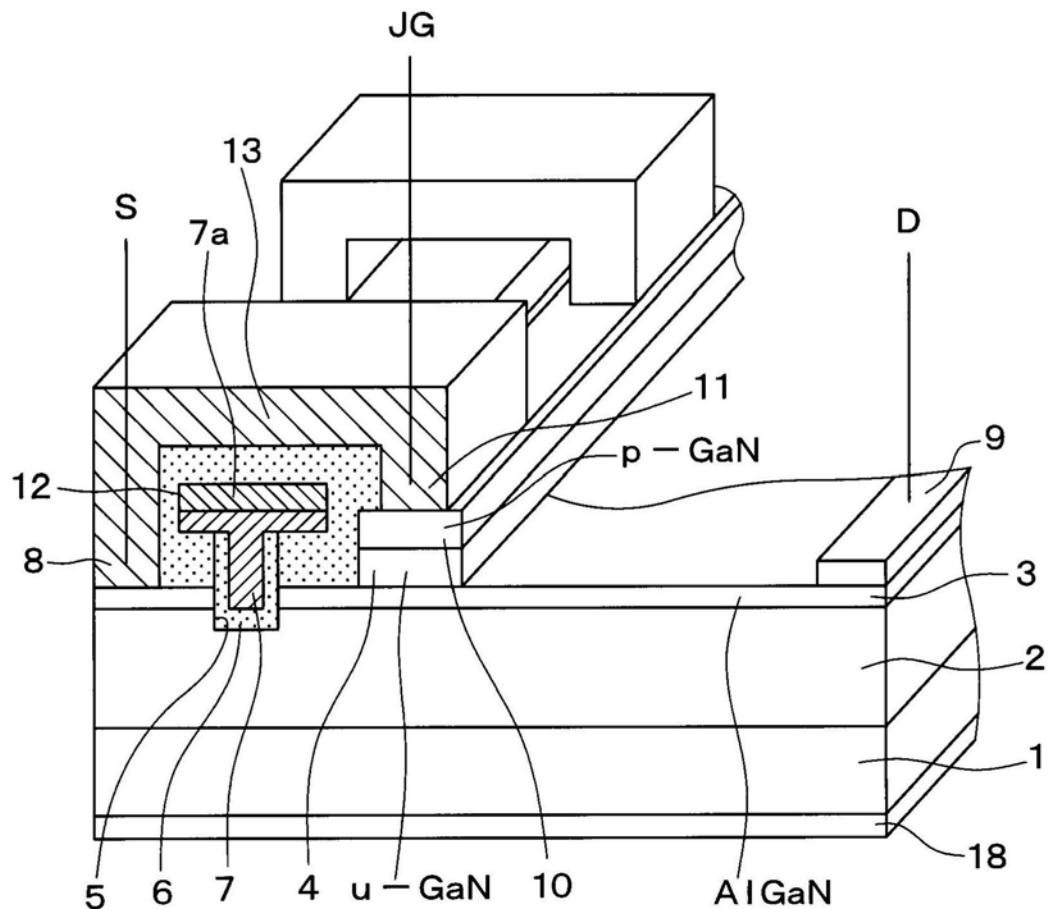

- [0030] 图14是作为第4实施方式的变形例而表示的半导体装置的截面立体图。

- [0031] 图15是第5实施方式的半导体装置的截面立体图。

- [0032] 图16是作为第5实施方式的变形例而表示的半导体装置的截面立体图。

- [0033] 图17是作为第5实施方式的变形例而表示的半导体装置的截面立体图。

- [0034] 图18是作为第5实施方式的变形例而表示的半导体装置的截面立体图。

- [0035] 图19是表示关断时在开关器件中流动的电流路径的图。

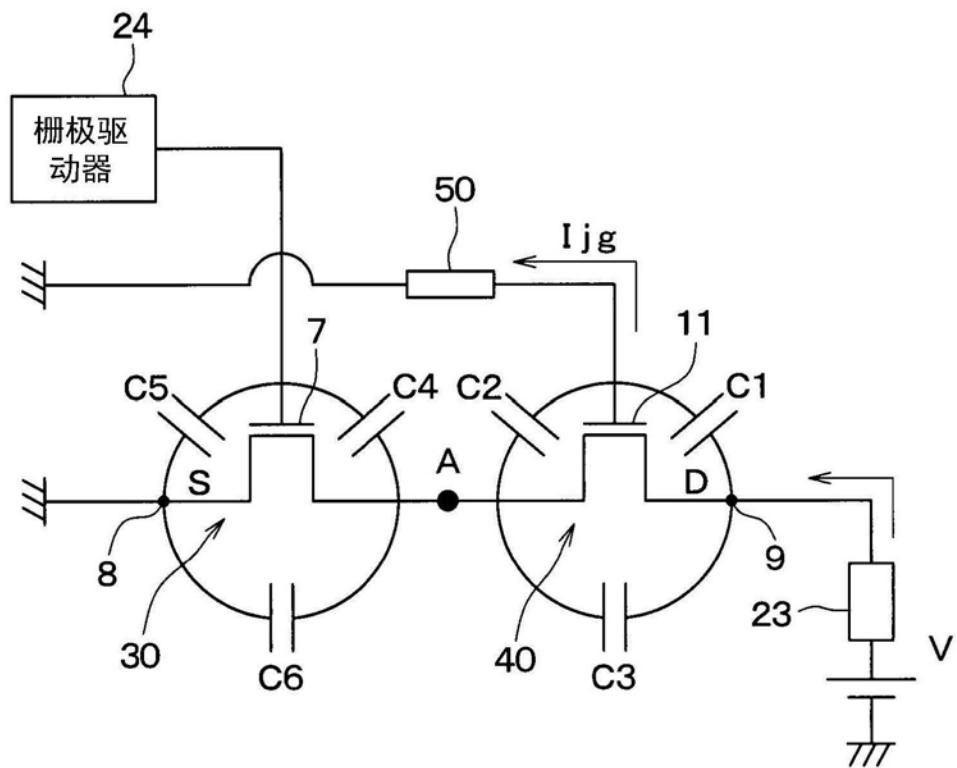

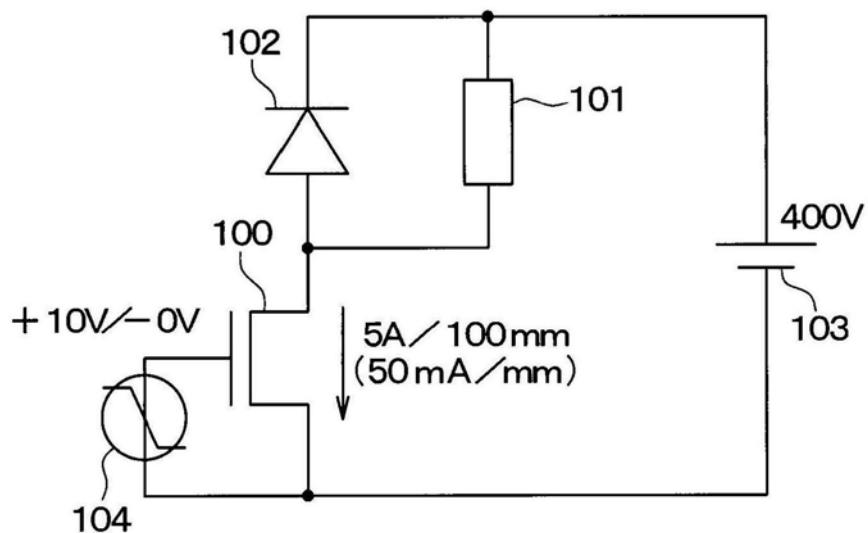

- [0036] 图20是在模拟中使用的计算构造电路图。

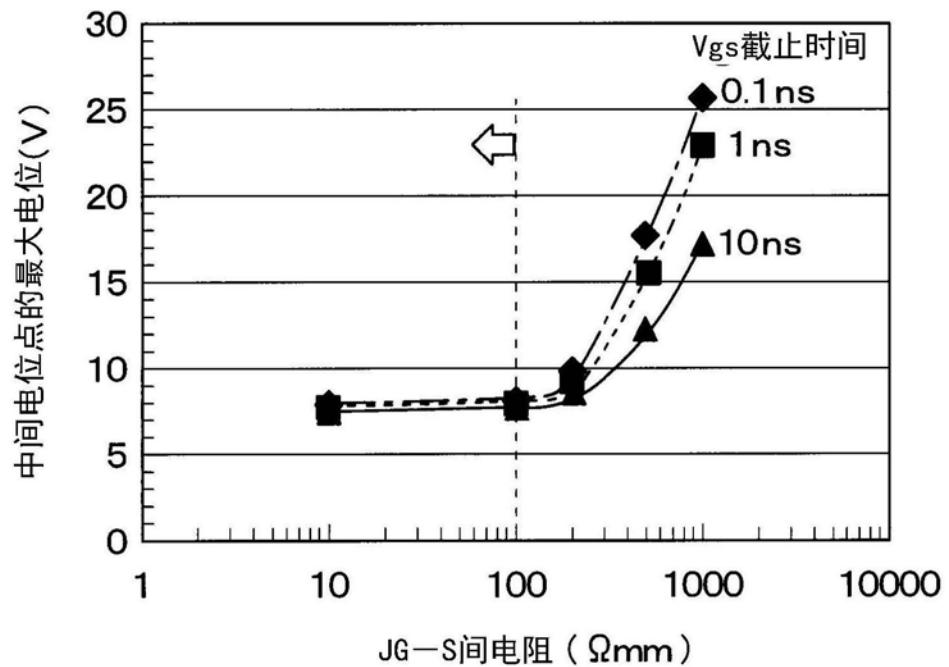

- [0037] 图21是表示通过模拟求出了JG—S间电阻值与中间电位点的最大电压值之间的关系时的结果的图。

- [0038] 图22是在其他实施方式中说明的半导体装置的上表面布局图。

## 具体实施方式

[0039] 以下，基于附图对本发明的实施方式进行说明。另外，在以下的各个实施方式中，对相互相同或等同的部分赋予相同的标号而进行说明。

- [0040] (第1实施方式)

[0041] 参照图1～图8对第1实施方式的半导体装置进行说明。另外，图1是表示在本实施方式的半导体装置中具备的1个单元的元件的剖视图，通过具备多个该单元而构成半导体装置。

[0042] 如图1所示，本实施方式的半导体装置是作为横型的开关器件而具备4端子的HEMT的结构。

[0043] 本实施方式的开关器件使用在基板1的表面形成有无掺杂的GaN(以下称作u—GaN)层2的结构作为化合物半导体基板。在u—GaN层2的表面，形成有无掺杂的AlGaN(以下称作u—AlGaN)层3，由u—GaN层2和u—AlGaN层3构成异质结构。开关器件将这些u—GaN层2及u—AlGaN层3作为沟道形成层，在AlGaN/GaN界面的u—GaN层2侧通过压电效应及自发极化效应而感应出2DEG载流子，该区域成为载流子流动的沟道从而开关器件进行动作。

[0044] 基板1由Si(111)、SiC这样的半导体材料等导电性材料构成。可以在基板1之上直接形成u—GaN层2，但为了将u—GaN层2结晶性良好地成膜，根据需要也可以形成作为基底膜的缓冲层。在能够在基板1之上结晶性良好地成膜u—GaN层2的情况下，也可以没有缓冲层。另外，这里的结晶性，是u—GaN层2中的缺陷及位错等，是指对电气特性及光学特性带来影响的因素。

[0045] u—GaN层2是构成作为漂移区域来工作的电子渡越层的部分，相当于第1GaN类半导体层。u—GaN层2由GaN类半导体材料形成，在u—AlGaN层3侧的表层部形成2DEG。

[0046] u—AlGaN层3相当于第2GaN类半导体层，由与构成u—GaN层2的GaN类半导体材料相比带隙能量大的GaN类半导体材料构成，构成电子供给部。

[0047] u—AlGaN层3将Al混晶比设为x而由 $\text{Al}_x\text{Ga}_{1-x}\text{N}$ 构成。根据该u—AlGaN层3的Al混晶比x及膜厚，决定在u—GaN层2的表面附近形成的2DEG的浓度。因而，通过调整u—AlGaN层3的Al混晶比x及膜厚来调整2DEG的浓度，调整成不是2DEG浓度根据厚度而较大地变动的范围、而是由Al混晶比x唯一地决定2DEG浓度的范围。

[0048] 此外，在u—AlGaN层3的表面，局部地形成有没有掺加杂质的u—GaN层4。

[0049] u—AlGaN层3形成在基板1上表面的整面，u—GaN层4形成在u—AlGaN层3中的后述的MOS栅极电极7的附近，朝向后述的漏极电极9侧伸出而延伸设置。这些u—AlGaN层3及u—GaN层4在凹口部5中被除去。凹口部5将一个方向、具体而言是相对于图1的截面的法线方向

作为较长方向而延伸设置。

[0050] 在凹口部5内,作为栅极构造部,隔着栅极绝缘膜6埋入有MOS栅极电极7。具体而言,在凹口部5的内壁面成膜有规定膜厚的栅极绝缘膜6,在该栅极绝缘膜6之上进一步形成MOS栅极电极7从而构成栅极构造部。包括MOS栅极电极7的栅极构造部沿着凹口部5形成,所以与凹口部5同样,成为沿着一个方向延伸设置的状态。

[0051] 栅极绝缘膜6由硅氧化膜( $\text{SiO}_2$ )、氧化铝( $\text{Al}_2\text{O}_3$ )等构成,MOS栅极电极7由铝、铂等金属或掺加了杂质的Poly一半导体等构成。通过将这些栅极绝缘膜6及MOS栅极电极7形成在凹口部5内而构成了MOS构造的栅极构造部。另外,也能够将MOS栅极电极7整体地用Poly一半导体等构成,但为了减小MOS栅极电极7的布线电阻,在MOS栅极电极7的表面部配置有金属层7a。

[0052] 另一方面,在u—AlGaN层3的表面中的夹着栅极构造部的两侧分别形成有源极电极8和漏极电极9。源极电极8及漏极电极9都配置在从u—GaN层4离开了的位置,从u—GaN层4的端部到漏极电极9的距离为规定长度。这些源极电极8及漏极电极9分别为欧姆接触。

[0053] 此外,在u—GaN层4中的位于MOS栅极电极7与漏极电极9之间的部分的表面,形成有p—GaN层10。p—GaN层10配置为,漏极电极9侧的端面与u—GaN层4中的漏极电极9侧的端面共面、或比其更靠MOS栅极电极7侧。在本实施方式中,从p—GaN层10中的漏极电极9侧的端面到u—GaN层4中的漏极电极9侧的端面的距离为 $1\mu\text{m}$ 以上且 $5\mu\text{m}$ 以下的范围。

[0054] 进而,在p—GaN层10的表面形成有JG电极11。JG电极11与上述源极电极8连结,与源极电极8为相同电位。

[0055] 具体而言,以将MOS栅极电极7及u—GaN层4等覆盖的方式配置有层间绝缘膜12,以将层间绝缘膜12覆盖的方式形成有电极层13。该电极层13经由形成于层间绝缘膜12的接触孔而与u—AlGaN层3接触,并且与p—GaN层10接触。该电极层13之中,由与u—AlGaN层3接触的部分构成源极电极8,由与p—GaN层10接触的部分构成JG电极11。这样,将源极电极8及JG电极11用相同的电极层13构成。因此,与将它们之间用键合线等连接的情况相比,能够减小布线电阻和电感。

[0056] 通过这样的构造,构成了具备MOS栅极电极7、源极电极8、漏极电极9及JG电极11这4个端子的开关器件。并且,通过具备这样的开关器件,构成了本实施方式的半导体装置。另外,形成在基板1的背面侧的是背面电极18,例如经由未图示的布线而与源极电极8电连接等,从而与源极电极8电位相同。

[0057] 在这样构成的半导体装置中,如图2所示,形成开关器件的区域为有源区域14。另外,在图2中,为了容易知道各部的布局,省略了左起第2个电极层13,将配置在其下方的MOS栅极电极7、源极电极8及JG电极11用实线表示。

[0058] 如图2所示,在本实施方式中,将有源区域14设为例如长方形,将相互线对称地相向配置的各2个单元的组沿着有源区域14的较长方向排列有多组。

[0059] 在各组中,设置在2个单元中的2条源极电极8平行地延伸设置,在以该两条源极电极8为中心的两侧配置有MOS栅极电极7,进而在夹着源极电极8及MOS栅极电极7的两侧配置有JG电极11。此外,夹着源极电极8、MOS栅极电极7及JG电极11而形成有漏极电极9。另外,在图2中将源极电极8和JG电极11分别地记载,但它们都由如图1所示那样悬架在MOS栅极电极7之上而配置的电极层13构成,成为一体化的构造。此外,在图2中,没有表示p—GaN层10,但

例如设为与JG电极11同样的布局。

[0060] 上述的电极层13至少配置在有源区域14内，源极电极8和JG电极11在有源区域14内经由电极层13相连结。这样，由于在有源区域14内源极电极8和JG电极11相连结，所以如上述那样能够减小阻抗。

[0061] 此外，各电极7～9、11分别在与有源区域14的较长方向交叉的方向上延伸设置，并延伸设置到比有源区域14靠外侧。并且，源极电极8及JG电极11连接于源极焊盘15，漏极电极9连接于漏极焊盘16。MOS栅极电极7经由栅极引出布线17a连接于栅极焊盘17。

[0062] 另外，各组的2条源极电极8在与源极焊盘15相反的一侧连结。此外，各组的2条MOS栅极电极7也在与栅极引出布线17a相反的一侧连结。同样，各组的2条JG电极11也在与源极焊盘15相反的一侧连结。因此，源极电极8及JG电极11在从源极焊盘15离开了的位置的部位也为大致均等的电位，MOS栅极电极7在从栅极引出布线17a离开了的位置的部位也为大致均等的电位。

[0063] 接着，对具备本实施方式的开关器件的半导体装置的动作及效果进行说明。

[0064] 如上述那样，具备MOS栅极电极7和JG电极11双方的开关器件通过MOS栅极电极7进行通常的MOSFET动作，通过JG电极11进行JFET动作。因此，图1所示的开关器件的等价电路为图3所示的电路结构。

[0065] 如图3所示，开关器件连接于负载23，栅极驱动器24控制栅极电压而使本开关器件通断，从而进行负载23的驱动。

[0066] 这里，开关器件是将基于MOS栅极电极7的增强型(normaly off) MOSFET部30与基于JG电极11的耗尽型(normaly on) JFET部40串联连接的构造。这些MOSFET部30与JFET部40之间的中间电位点A如图1所示那样，是指u-GaN层2的表面部中的位于JG电极11的下方的成为中间电位的部分。

[0067] JG电极11连接于源极电极8而成为相同电位。在它们之间存在由布线带来的寄生阻抗50，但由于它们之间经由电极层13而被直接连结，所以寄生阻抗50的值变低。此外，在这样的结构的开关器件中，在JFET部40，在JG电极11与漏极电极9及中间电位点A之间、以及漏极电极9与中间电位点A之间，构成电容C1～C3。此外，在MOSFET部30，在MOS栅极电极7与中间电位点A及源极电极8之间、以及中间电位点A与源极电极8之间，构成电容C4～C6。

[0068] 关于具有这样的电路结构的开关器件，关断时的动作如下这样。

[0069] 图4表示具有感性负载的H电桥电路中的本开关器件的关断的波形。首先，在图4的时点T1，当停止向MOS栅极电极7的栅极电压的施加，则MOSFET部30的截止过程开始，从而在图4中虽未表示，但中间电位点A的电位上升。通过该中间电位点A的电位的上升，JFET的栅极的截止过程开始。即，在从漏极电极9侧经过JG电极11向GND侧排出的路径中流过位移电流I<sub>jg</sub>，从而将JFET的反馈电容C1充电。

[0070] 并且，通过反馈电容C1的充电，漏极电极9的电位V<sub>ds</sub>变高。此外，漏极电流I<sub>d</sub>下降。如果中间电位点A的电位超过JFET部40的阈值电压，则JFET部40截止。由此，开关器件整体截止。

[0071] 为了使这样的关断动作高速化，需要能够高速地进行向反馈电容C1的充电。并且，为了高速地进行向反馈电容C1的充电，JG电极11与源极电极8之间的阻抗减小和反馈电容C1的减小是重要的。

[0072] 对此,在本实施方式中,由于JG电极11与源极电极8之间经由电极层13而被直接连接,所以能够将存在于它们之间的由布线电阻带来的寄生阻抗50的电阻值抑制得较低。因而,能够实现JG电极11与源极电极8之间的阻抗减小。

[0073] 进而,在本实施方式中,关于u—GaN层4与p—GaN层10的层叠构造,从漏极电极9离开而配置,使得p—GaN层10的形成面积尽可能小。这样,能够降低在p—GaN层10与u—AlGaN层3的表面部之间构成的反馈电容C1。并且,使得p—GaN层10中的漏极电极9侧的端面与u—GaN层4中的漏极电极9侧的端面共面、或位于比其更靠MOS栅极电极7侧。由此,还能够确保耐压。对此,参照图5～图8进行说明。

[0074] 为了减小反馈电容C1,减小p—GaN层10与u—AlGaN层3的对置面积即可。并且,为了尽可能减小p—GaN层10的面积,使得p—GaN层10中的漏极电极9侧的端面与u—GaN层4中的漏极电极9侧的端面共面是最有效的。

[0075] 但是,已确认到,如果使p—GaN层10及u—AlGaN层3的漏极电极9侧的端面共面,则会发生因电场集中造成的耐压下降。

[0076] 具体而言,如图5所示,将从p—GaN层10中的漏极电极9侧的端面到u—GaN层4中的漏极电极9侧的端面的距离、即u—GaN层4相对于p—GaN层10的突出量设为距离X,改变距离X而调查了电场强度分布。这里,将从p—GaN层10到漏极电极9的距离设定为8μm,将距离X改变为0～7μm而进行了模拟。结果,得到了图6所示的电场强度分布。此外,图6中的电场强度的峰值位置分别是u—GaN层4中的漏极电极9侧的端部(以下称作u—GaN端部)的位置、和漏极电极9中的u—GaN层4侧的端部(以下称作漏极端部)。将与距离X对应的u—GaN端部和漏极端部处的电场强度进行标绘,则成为图7所示的结果。

[0077] 如这些图所示,关于u—GaN端部的电场强度,如果使得p—GaN层10中的漏极电极9侧的端面与u—GaN层4中的漏极电极9侧的端面共面,则与将距离X设为1μm以上的情况相比急剧地上升。这是因为,在阻止状态下,在距离X是1μm以上的情况下,从漏极电极9到JG电极11的空间电荷量的变化变得急剧,因此,在变化大的部分发生强电场。即,从漏极电极9到u—GaN层4,由于极化而存在正的充电,从u—GaN层4到p—GaN层10,由极化带来的正电荷与负电荷抵消而充电是零。此外,比p—GaN层10更靠源极电极8侧由于p—GaN层10的耗尽而存在负的充电,空间电荷量逐渐变化。这是因为,如果不到X=1μm,则p—GaN层10与u—GaN层4共面或与其接近,空间电荷为零的区域变窄或消失,所以正的充电以较短的距离急剧地变化为负的充电。在本发明者们的研究中,调整距离X,以使u—GaN层4中的漏极电极9侧的端部从p—GaN层10中的漏极电极9侧的端部突出,具体而言,如果使距离X至少成为1μm以上,则能够使u—GaN端部的电场强度下降。

[0078] 另一方面,在漏极端部,与u—GaN层4的距离越短,越受到其影响而发生电场集中,电场强度增加。具体而言,成为如下结果:如果距离X超过5μm,则最大电场强度急剧地上升。

[0079] 考虑到开关器件的耐压,优选的是最大电场强度较小。并且,为了使最大电场强度变小,可以将距离X设为4.5μm以下。进而,如图7所示那样使距离X为1μm以上且4μm以下,在进行用来得到稳定的耐压的设计方面更为优选。

[0080] 因而,通过使距离X成为1μm以上且4.5μm以下的范围,能够将反馈电容C1抑制得较低并且使最大电场强度较小。关于开关器件的耐压,基本上取决于从p—GaN层10的端面到漏极电极9的间隔,该间隔越大则耐压越高。相对于此,关于能够使最大电场强度较小的距

离X的范围,不论从p—GaN层10的端面到漏极电极9的间隔如何都保持上述的范围,即在1μm以上且4.5μm以下不变。因而,即使从u—GaN层10的端面到漏极电极9的间隔发生了变化,通过将距离X设为1μm以上且4.5μm以下、优选4μm以下,也能够得到上述效果。

[0081] 进而,在本实施方式中,以将u—GaN层4贯通的方式形成有MOS栅极电极7。即,以与包括MOS栅极电极7的栅极构造部接触的方式形成有u—GaN层4。在做成这样的构造的情况下,例如,图5中的VIII—VIII线上的栅极绝缘膜6及u—GaN层4中的电场强度分布成为图8所示的分布,随着向MOS栅极构造接近,电场强度变弱。这是因为,虽然通过u—GaN层4取得充电平衡而成为中性状态,但由于负电荷被从导电性的基板供给,所以整体上带有负的充电。

[0082] 这样,u—GaN层4中的电场强度随着向MOS栅极电极7行进而变小,所以栅极绝缘膜6的电场强度变小,从而可靠性提高。

[0083] 如以上说明的那样,在本实施方式中,将JG电极11与源极电极8经由电极层13直接连结。因此,能够使寄生阻抗50的电阻值变低,能够实现JG电极11与源极电极8之间的阻抗减小。此外,通过将u—GaN层4及p—GaN层10从漏极电极9离开而配置,从而尽可能地减小了u—GaN层4与2DEG之间的对置面积。因此,还能够减小反馈电容C1。

[0084] 这样,实现JG电极11与源极电极8之间的电阻、电感减小以及反馈电容C1的减小,从而能够将反馈电容C1以高速充电,能够使JFET部40高速截止。因此,能够使开关器件的关断更高速化。因而,能够得到实现更高速开关的开关器件。

[0085] 此外,为了得到上述效果,可以将距离X设定为0μm以上且5μm的范围,但进一步以使u—GaN层4的端部比p—GaN层10更向漏极电极9侧突出的方式设定距离X,使距离X成为1μm以上且5μm以下。由此,能够使最大电场强度变小,还能够实现半导体装置的耐压提高。

[0086] 进而,以将u—GaN层4贯通的方式形成有MOS栅极电极7。因而,u—GaN层4中的电场强度朝向MOS栅极电极7变小,栅极绝缘膜6的电场强度变小,所以可靠性提高。

[0087] (第2实施方式)

[0088] 对第2实施方式进行说明。本实施方式相对于第1实施方式变更了栅极构造部,其他与第1实施方式是同样的,所以仅对与第1实施方式不同的部分进行说明。

[0089] 如图9所示,在本实施方式中,为了实现栅极构造部中的MOS栅极电极7的低电阻化,将MOS栅极电极7做成了T字形状。即,做出了在电流在源极—漏极间流动的方向上、使MOS栅极电极7的上部比下部宽度宽的T栅极构造。换言之,做成了在凹口部5的外部、以比凹口部5更向源极电极8侧及漏极电极9侧伸出的方式将MOS栅极电极7延伸设置的构造。此外,关于在MOS栅极电极7的表面部形成的金属层7a,也与MOS栅极电极7同样,以比凹口部5更向源极电极8侧及漏极电极9侧伸出的方式延伸设置。

[0090] 通过做成这样的结构,能够将电流流动的截面积扩大。即,在MOS栅极电极7内,电流在图9的纸面垂直方向上流动。因而,能够扩大以纸面垂直方向为法线方向的截面的截面积,即扩大电流流动的截面积。由此,能够将MOS栅极电极7的电阻减小,能够更高速化。

[0091] (第3实施方式)

[0092] 对第3实施方式进行说明。本实施方式相对于第1实施方式变更了焊盘布局,其他与第1实施方式是同样的,所以仅对与第1实施方式不同的部分进行说明。

[0093] 如图10所示,在本实施方式中,在有源区域14内配置了源极焊盘15及漏极焊盘16。

关于源极焊盘15，通过扩大将源极电极8与JG电极11连结的电极层13的面积而构成。在本实施方式的情况下，通过在相邻的单元间将电极层13相连，能够将面积取得更大。

[0094] 这样，通过将源极焊盘15配置在有源区域14内，能够使从源极电极8及JG电极11到源极焊盘15的布线长变短，能够减小布线电阻，所以能够进一步实现阻抗减小。由此，得到进一步实现高速开关的开关器件。

[0095] 关于在有源区域14设置漏极焊盘16，也能够使从漏极电极9到漏极焊盘16的布线长变短，能够减小布线电阻。

[0096] 对于这样配置的栅极焊盘17、源极焊盘15、漏极焊盘16，例如通过用键合线与外部电连接，能够对各部施加任意的电压，但还能够做成图11A及图11B那样的凸块连接构造。

[0097] 具体而言，准备形成有未图示的所希望的电路图案以及用于与电路图案的希望部位进行连接的电极部21的电极连接基板20。并且，将电极部21侧朝向半导体装置，将各电极部21与栅极焊盘17、源极焊盘15、漏极焊盘16之间通过由焊料等构成的导体凸块22连接。这样，能够实现能够同时进行形成于电极连接基板20的电路图案与MOS栅极电极7、JG电极11和源极电极8、以及漏极电极9的电连接的连接构造。

[0098] 另外，在图11A中，使电极部21形成为比栅极焊盘17、源极焊盘15、漏极焊盘16厚的厚膜电极，在图11B中，使栅极焊盘17、源极焊盘15、漏极焊盘16形成为比电极部21厚的厚膜电极。应用它们中的哪种构造都可以，还能够使电极部21及栅极焊盘17、源极焊盘15、漏极焊盘16为同等厚度。

[0099] (第4实施方式)

[0100] 对第4实施方式进行说明。本实施方式相对于第3实施方式变更了焊盘布局，其他与第3实施方式是同样的，所以仅对与第3实施方式不同的部分进行说明。

[0101] 如图12所示，在本实施方式中，使将源极电极8与JG电极11连结的电极层13为梯子状的布局。具体而言，在MOS栅极电极7的延伸设置方向上分为多个、或者在MOS栅极电极7的延伸设置方向上对电极层13设置多个开口部，从而将电极层13布局为梯子状。例如，通过在将构成电极层13的电极材料成膜后，利用蚀刻布图为梯子状，从而能够形成图12所示的构造的电极层13。

[0102] 在做成这样的构造的情况下，如图13所示，在有源区域14内，在栅极构造部之上局部地存在没有形成电极层13的部分，所以还能够将该部分用作栅极焊盘17。此外，关于作为栅极焊盘17的部分以外，做成将源极电极8、JG电极11及电极层13连结的构造，能够作为源极焊盘15来使用。

[0103] 通过做成这样的构造，也能够使从MOS栅极电极7到栅极焊盘17的布线长变短，能够减小布线电阻。

[0104] 另外，在这样做成将电极层13分为多个、在其之间配置栅极焊盘17的构造的情况下，如图14所示，也能够与第2实施方式同样，将MOS栅极电极7做成T字形状。由此，也能够得到与第2实施方式同样的效果。

[0105] (第5实施方式)

[0106] 对第5实施方式进行说明。本实施方式相对于第1实施方式变更了u-GaN层4的布局，其他与第1实施方式是同样的，所以仅对与第1实施方式不同的部分进行说明。

[0107] 如图15所示，在本实施方式中，做成了使u-GaN层4从栅极构造部离开了的构造，

并做成了仅配置在栅极构造部与漏极电极9之间的构造。

[0108] 这样,如果做成使u—GaN层4从栅极构造部离开了的构造,则相应于u—GaN层4的减少面积,2DEG增加。由此,能够减小导通电阻Ron。

[0109] 另外,在图15中,说明了相对于第1实施方式的构造变更u—GaN层4的布局的情况,但关于其他实施方式也能够采用同样的构造。例如,如图16所示,在与第2实施方式同样地将MOS栅极电极7做成T字形状的情况下,能够做成使u—GaN层4从栅极构造部离开了的构造。此外,如图17所示,在与第4实施方式同样地做成将电极层13分为多个的构造的情况下,也能够做成使u—GaN层4从栅极构造部离开了的构造。在此情况下,如图18所示,也能够与第2实施方式同样地将MOS栅极电极7做成T字形状。

[0110] (第6实施方式)

[0111] 对第6实施方式进行说明。本实施方式相对于第1～第5实施方式规定了JG—S间电阻值,其他与第1～第5实施方式是同样的,所以仅对与第1～第5实施方式不同的部分进行说明。另外,这里,以第1实施方式的结构的半导体装置为例进行说明,但关于第2～第5实施方式的结构的半导体装置可以说也是同样的。

[0112] 在上述第1～第5实施方式那样的结构的具有横型开关器件的半导体装置中,通过抑制栅极绝缘膜6的破坏及劣化来提高可靠性是重要的。关于栅极绝缘膜6的破坏,通过减小关断时的中间电位点A处的最大电压值而能够抑制。关于该关断时的中间电位点A处的最大电压值,本发明者们进行了仔细研究,确认到取决于JG—S间电阻值。

[0113] 这里,对JG—S间电阻值进行说明。在关断时从漏极侧流动的电流如图19所示,将漏极电极9和u—GaN层4看作电极,经过在它们之间夹着AlGaN层3而构成的电容器向源极侧流动。JG—S间电阻值是指在该关断时经过JG电极11及源极电极8而流动电流的电流路径的电阻成分的合计。

[0114] 即,来自漏极侧的电流采取从u—GaN层4、p—GaN层10进而经过JG电极11而向源极电极8流动的电流路径,将该电流路径中的电阻成分的合计称作JG—S间电阻值。具体而言,作为该通电路径中的电阻成分,有u—GaN层4的内部电阻Ru、p—GaN层10的内部电阻Rp、p—GaN层10与JG电极11的接触电阻Rp,jg、从JG电极11到源极电极8之间的电极电阻Rm。因而,JG—S间电阻值Rjgs由以下的数学式1表示。

[0115] (数学式1)

$$R_{jgs} = R_u + R_p + R_{p,jg} + R_m$$

[0117] 并且,如第1～第5实施方式那样,做成将JG电极11与源极电极8相连结的构造,由于它们由电阻值小的金属构成,所以电极电阻Rm小到能够忽视的程度。因而,在将数学式1简化的情况下,如数学式2那样表示。

[0118] (数学式2)

$$R_{jgs} = R_u + R_p + R_{p,jg}$$

[0120] 此外,在关断时,在u—GaN层4及p—GaN层10中,在纵向即基板1的法线方向上流过电流。并且,关于p—GaN层10,由于厚度较薄例如为100nm以下且Mg等的杂质密度变大,所以p—GaN层10的内部电阻Rp相比于p—GaN层10与JG电极11的接触电阻Rp,jg而言充分小。进而,关于u—GaN层4,除了厚度较薄以外,由于与p—GaN层10相接,所以由于来自p—GaN层10的空穴的扩散而电阻值下降。因此,u—GaN层4的内部电阻Rp也相比于p—GaN层10与JG电极

11的接触电阻 $R_{pjg}$ 而言充分小。因而,在将数学式2进一步简化的情况下,如数学式3那样表示。

[0121] (数学式3)

[0122]  $R_{jgs} \approx R_{pjg}$

[0123] 因此,虽然JG-S间电阻值基本上是指由数学式1表示的电阻值,但在简化的情况下,如数学式3那样表示为p-GaN层10与JG电极11的接触电阻 $R_{pjg}$ 。

[0124] 接着,关于关断时的中间电位点A处的最大电压值,基于图20所示的计算构造用电路进行了模拟。具体而言,在开关器件100的源极-漏极的电流路径内配置感性负载101,并且相对于感性负载101并联连接续流二极管102,使得从例如400V的电源103进行电力供给。并且,由栅极驱动部104控制开关器件100的栅极电压,从施加+10V的状态将栅极电压的施加解除,设为0V。由此,在设想开关器件100的沟道宽度为100mm的情况下,能够流过50mA的漏极电流。

[0125] 进行这样的模拟后确认到,不取决于栅极电压 $V_{gs}$ 的截止时间、换言之栅极电压的切断速度 $dV/dt$ ,当JG-S间电阻值成为规定值,则中间电位点A的最大电压值大致收敛为一定值。具体而言,如图21所示,当JG-S间电阻值为 $200\Omega\text{ mm}$ 以下,则中间电位点A的最大电压值为10V以下的大致一定的值,进而当JG-S间电阻值为 $100\Omega\text{ mm}$ 以下,则成为8V左右的大致一定的值。

[0126] 这样,确认到在关断时的JG-S间电阻值与中间电位点A的最大电压值之间具有临界性。该临界性不取决于栅极电压的切断速度 $dV/dt$ ,当JG-S间电阻值为 $200\Omega\text{ mm}$ 以下、更优选为 $100\Omega\text{ mm}$ 以下,则中间电位点A的最大电压值能够成为最小的值。此外,在模拟中,作为漏极电流的一例而以5A为例,但即使是其他电流值也成为同样的趋向,上述临界性也不取决于漏极电流,而仅取决于JG-S间电阻值。

[0127] 由此,通过将JG-S间电阻值设为 $200\Omega\text{ mm}$ 以下,优选的是设为 $100\Omega\text{ mm}$ 以下,能够使关断时的中间电位点A的最大电压变小,能够使得与DC截止状态相比不变大。由此,能够抑制作用于栅极绝缘膜6的电场强度的增大,能够抑制栅极绝缘膜6的破坏,所以能够实现栅极绝缘膜6的可靠性提高。并且,能够防止因栅极绝缘膜6被破坏而开关器件击穿的破坏。

[0128] 另外,当JG-S间电阻值、即由数学式1表示的各电阻成分的合计值为 $200\Omega\text{ mm}$ 以下、优选的是 $100\Omega\text{ mm}$ 以下,则能得到上述效果。此外,在如数学式3那样将JG-S间电阻值表示为p-GaN层10与JG电极11的接触电阻 $R_{pjg}$ 的情况下,当至少接触电阻 $R_{pjg}$ 是 $200\Omega\text{ mm}$ 以下,则能得到上述效果。

[0129] (其他实施方式)

[0130] 将本发明依据上述实施方式进行了记述,但并不限定于该实施方式,也包含各种各样的变形例及等价范围内的变形。除此以外,各种各样的组合或形态、进而在它们中仅包含一要素、其以上或其以下的其他组合及形态也包含在本发明的范畴或思想范围内。

[0131] 例如,在上述各实施方式中,将凹口部5的深度设为到u-GaN层2的表层部被部分除去为止的深度,但这不过是表示一例。例如,也可以将凹口部5设为到u-GaN层2的表面露出为止的深度,也可以设为在凹口部5的底面以不形成2DEG载流子的程度留下u-AlGaN层3的一部分的程度的深度。

[0132] 此外,关于在图2等中表示的上述各实施方式的开关器件的上表面布局,也只不过

表示了一例,能够适当变更。

[0133] 此外,在上述各实施方式中,以构成沟道形成层的第1、第2GaN类半导体层由u—GaN层2和u—AlGaN层3构成的情况为例进行了说明。但是,它们表示一个例子,只要由第1GaN类半导体层及带隙能量比其大的第2GaN类半导体层构成沟道形成层,也可以是其他材料。

[0134] 进而,在第2实施方式中,说明了将与半导体装置的各焊盘的电连接做成在图11A和图11B中说明的那样的凸块连接构造,但当然关于第1、第3~第5实施方式也能够采用同样的连接构造。

[0135] 此外,在上述各实施方式中,说明了例如如图2所示那样做成MOS栅极电极7、JG电极11伸出到有源区域14的外侧那样的构造的情况。此外,例如关于与JG电极11同样的布局的p—GaN层10,也做成了伸出到有源区域14的外侧那样的构造。但是,这也只不过表示一例,例如也可以如图22所示那样,做成将MOS栅极电极7、JG电极11及p—GaN层10仅配置在有源区域14的内侧那样的构造。

图1

图2

图3

图4

图5

u—GaN端部侧的峰值

图6

图7

图8

图9

图10

图11A

图11B

图12

图13

图14

图15

图16

图17

图18

图19

图20

图21

图22