(12)发明专利

(10)授权公告号 CN 106797202 B

(45)授权公告日 2020.01.14

(21)申请号 201580047408.7

(73)专利权人 高通股份有限公司

(22)申请日 2015.08.25

地址 美国加利福尼亚州

(65)同一申请的已公布的文献号

(72)发明人 林赛华

申请公布号 CN 106797202 A

(74)专利代理机构 北京市金杜律师事务所

(43)申请公布日 2017.05.31

11256

(30)优先权数据

代理人 王茂华 张宁

14/478,691 2014.09.05 US

(51)Int.Cl.

H03F 1/22(2006.01)

(85)PCT国际申请进入国家阶段日

H03F 1/32(2006.01)

2017.03.03

H03F 3/193(2006.01)

(86)PCT国际申请的申请数据

H03F 3/24(2006.01)

PCT/US2015/046724 2015.08.25

H03F 3/68(2006.01)

(87)PCT国际申请的公布数据

审查员 吴一帆

W02016/036537 EN 2016.03.10

权利要求书3页 说明书12页 附图6页

(54)发明名称

多频带低噪声放大器

(57)摘要

一种设备包括被调谐至第一频带的第一路径和被调谐至第二频带的第二路径。设备也包括交叉耦合电路，具有耦合至第一路径的第一输入端和耦合至第二路径的第二输入端，以及具有耦合至第二路径的第一输出端和耦合至第一路径的第二输出端。

1. 一种电子设备,包括:

第一路径,被调谐至第一频带;

第二路径,被调谐至第二频带;以及

交叉耦合电路装置,具有耦合至所述第一路径的第一输入端以及耦合至所述第二路径的第二输入端,并且具有耦合至所述第二路径的第一输出端以及耦合至所述第一路径的第二输出端,其中,所述交叉耦合电路装置包括:

第一组晶体管,所述第一组晶体管中的第一晶体管具有耦合至所述第一路径的栅极并且所述第一组晶体管中的第二晶体管具有耦合至所述第二路径的漏极;以及

第二组晶体管,所述第二组晶体管中的第一晶体管具有耦合至所述第二路径的栅极并且所述第二组晶体管中的第二晶体管具有耦合至所述第一路径的漏极。

2. 根据权利要求1所述的电子设备,其中,所述第一路径、所述第二路径、和所述交叉耦合电路装置被包括在低噪声放大器中。

3. 根据权利要求1所述的电子设备,其中,所述第一组晶体管中的所述第一晶体管被配置为接收信号并且将所述信号相移180度。

4. 根据权利要求1所述的电子设备,其中,所述第一组晶体管中的第一晶体管和所述第二组晶体管中的第一晶体管是共源极晶体管。

5. 根据权利要求1所述的电子设备,其中,所述第一频带是2.4吉赫兹(GHz)频带,以及其中所述第二频带是5.6GHz频带。

6. 根据权利要求1所述的电子设备,进一步包括耦合至所述第一路径的第一电感-电容电路,其中所述第一电感-电容电路在所述第一频带内的频率处谐振。

7. 根据权利要求6所述的电子设备,其中,所述第一电感-电容电路的第一电感器被包括在第一变压器中。

8. 根据权利要求1所述的电子设备,进一步包括耦合至所述第二路径的第二电感-电容电路,其中所述第二电感-电容电路在所述第二频带内的频率处谐振。

9. 根据权利要求8所述的电子设备,其中,所述第二电感-电容电路的第二电感器被包括在第二变压器中。

10. 根据权利要求1所述的电子设备,进一步包括:

第三路径,被调谐至第三频带;

第二交叉耦合电路装置,具有耦合至所述第二路径的第一输入端和耦合至所述第三路径的第二输入端,并且具有耦合至所述第三路径的第一输出端和耦合至所述第二路径的第二输出端;以及

第三交叉耦合电路装置,具有耦合至所述第一路径的第一输入端和耦合至所述第三路径的第二输入端,并且具有耦合至所述第三路径的第一输出端和耦合至所述第一路径的第二输出端。

11. 根据权利要求10所述的电子设备,其中,所述第三频带是800兆赫兹(MHz)频带。

12. 根据权利要求10所述的电子设备,进一步包括耦合至所述第三路径的第三电感-电容电路,其中所述第三电感-电容电路在所述第三频带内的频率处谐振。

13. 根据权利要求1所述的电子设备,其中,所述第一频带和所述第二频带符合电气和电子工程师协会(IEEE)802.11标准。

14. 根据权利要求1所述的电子设备,进一步包括:

晶体管,具有耦合至所述第一路径并耦合至所述第二路径的漏极;以及

双频带匹配网络,具有被配置用于接收射频(RF)信号的输入端以及耦合至所述晶体管的栅极的输出端。

15. 根据权利要求1所述的电子设备,进一步包括:

第一晶体管,具有耦合至所述第一路径的漏极;

第二晶体管,具有耦合至所述第二路径的漏极;以及

双频带匹配网络,具有被配置用于接收射频(RF)信号的输入端以及耦合至所述第一晶体管的栅极和所述第二晶体管的栅极的输出端。

16. 一种电子设备,包括:

用于放大第一信号分量的装置,其中所述用于放大第一信号分量的装置被调谐至第一频带;

用于放大第二信号分量的装置,其中所述用于放大第二信号分量的装置被调谐至第二频带;

用于产生一个或多个抵消信号的装置,具有耦合至所述用于放大第一信号分量的装置的第一输入端和耦合至所述用于放大第二信号分量的装置的第二输入端,并且具有耦合至所述用于放大第二信号分量的装置的第一输出端和耦合至所述用于放大第一信号分量的装置的第二输出端,其中,用于生成的装置包括:

用于放大信号的第一装置,具有耦合至所述用于放大第一信号分量的装置的栅极,以及用于放大信号的第二装置,具有耦合至所述用于放大第二信号分量的装置的漏极;以及

用于放大信号的第三装置,具有耦合至所述用于放大第二信号分量的装置的栅极,用于放大信号的第四装置,具有耦合至所述用于放大第一信号分量的装置的漏极。

17. 根据权利要求16所述的电子设备,其中,所述用于放大第一信号分量的装置、所述用于放大第二信号分量的装置、以及所述用于产生一个或多个消除信号的装置被包括在低噪声放大器中。

18. 根据权利要求16所述的电子设备,其中,所述第一频带是2.4吉赫兹(GHz)频带,以及其中所述第二频带是5.6GHz频带。

19. 一种用于操作多频带放大器的方法,包括:

放大在被调谐至第一频带的第一路径处的第一信号分量;

放大在被调谐至第二频带的第二路径处的第二信号分量;以及

在交叉耦合电路装置处产生一个或多个抵消信号,所述交叉耦合电路装置具有耦合至所述第一路径的第一输入端和耦合至所述第二路径的第二输入端,并且具有耦合至所述第二路径的第一输出端和耦合至所述第一路径的第二输出端,其中,所述交叉耦合电路装置包括:

第一组晶体管,所述第一组晶体管中的第一晶体管具有耦合至所述第一路径的栅极并且所述第一组晶体管中的第二晶体管具有耦合至所述第二路径的漏极;以及

第二组晶体管,所述第二组晶体管中的第一晶体管具有耦合至所述第二路径的栅极并且所述第二组晶体管中的第二晶体管具有耦合至所述第一路径的漏极。

20. 根据权利要求19所述的方法,其中,所述第一频带是2.4吉赫兹(GHz)频带,以及其

中所述第二频带是5.6GHz频带。

## 多频带低噪声放大器

[0001] 相关申请的交叉引用

[0002] 本申请要求于2014年9月5日提交的、共同拥有的美国非临时专利申请No.14/478,691的优先权，该申请的内容在此通过引用的方式明确并入本文。

### 技术领域

[0003] 本公开总体涉及一种多频带低噪声放大器。

### 背景技术

[0004] 技术的进步已经导致更小和更强大的计算装置。例如，当前存在小型、重量轻并且易于由用户携带的各种便携式个人计算装置，包括无线计算装置，诸如便携式无线电话、个人数字助理 (PDA)、以及呼叫装置。更具体地，诸如蜂窝电话和互联网协议 (IP) 电话之类的便携式无线电话可以通过无线网络传输语音和数据包。进一步，许多这种无线电话包括包含在其中的其他类型装置。例如，无线电话也可以包括数字照相机、数字摄像机、数字录音机、以及音频文件播放器。此外，这种无线电话可以处理可执行指令，包括软件应用程序，诸如可以用于访问互联网的网络浏览器应用程序。同样地，这些无线电话可以包括重要的计算性能。

[0005] 无线装置可以包括多个低噪声放大器以在多个频带之上接收信号。例如，第一低噪声放大器可以可配置用于在第一频带 (例如2.4吉赫兹 (GHz) 频带) 之上接收信号，以及第二低噪声放大器可以可配置用于在第二频带 (例如5.6GHz频带) 之上接收信号。使用多个低噪声放大器用于多频带接收 (例如双频带接收) 可以增大裸片面积。例如，对于每个低噪声放大器的晶体管内核可以相对较大 (例如在毫米 (mm) 范围中)，这可以增大低噪声放大器的芯片尺寸、裸片面积以及成本。此外，尽管可以由第一频带和第二频带支持用于无线局域网 (WLAN) 的电气和电子工程师协会 (IEEE) 802.11 (“WiFi”) 标准，来自同时接收的多频带信号的带间干扰可以降低对于WLAN的吞吐量。

### 附图说明

[0006] 图1示出了与无线系统通信的无线装置；

[0007] 图2示出了图1中的无线装置的方框图；

[0008] 图3是示出了双频带低噪声放大器的示例性实施例的视图；

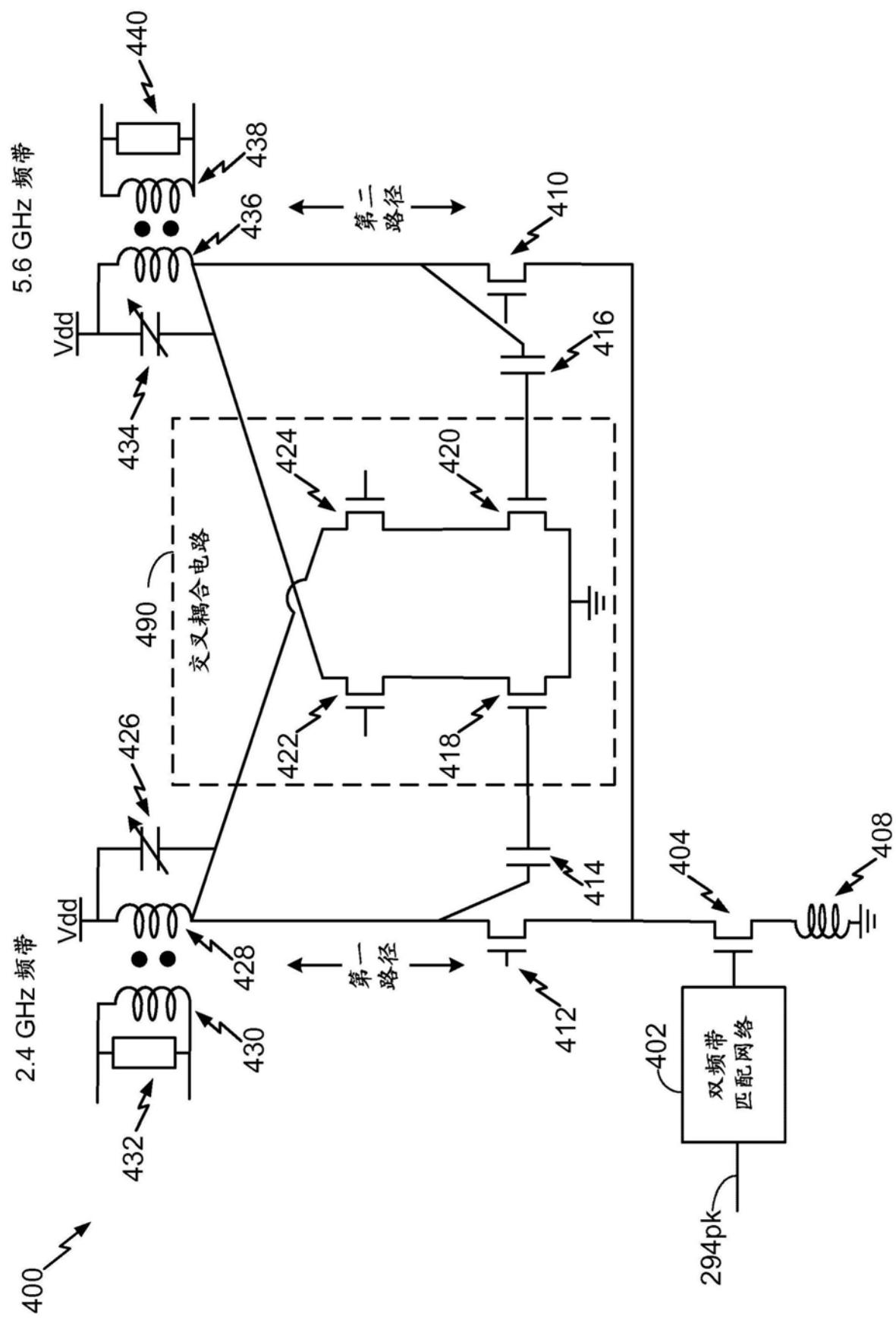

[0009] 图4是示出了双频带低噪声放大器的另一示例性实施例的视图；

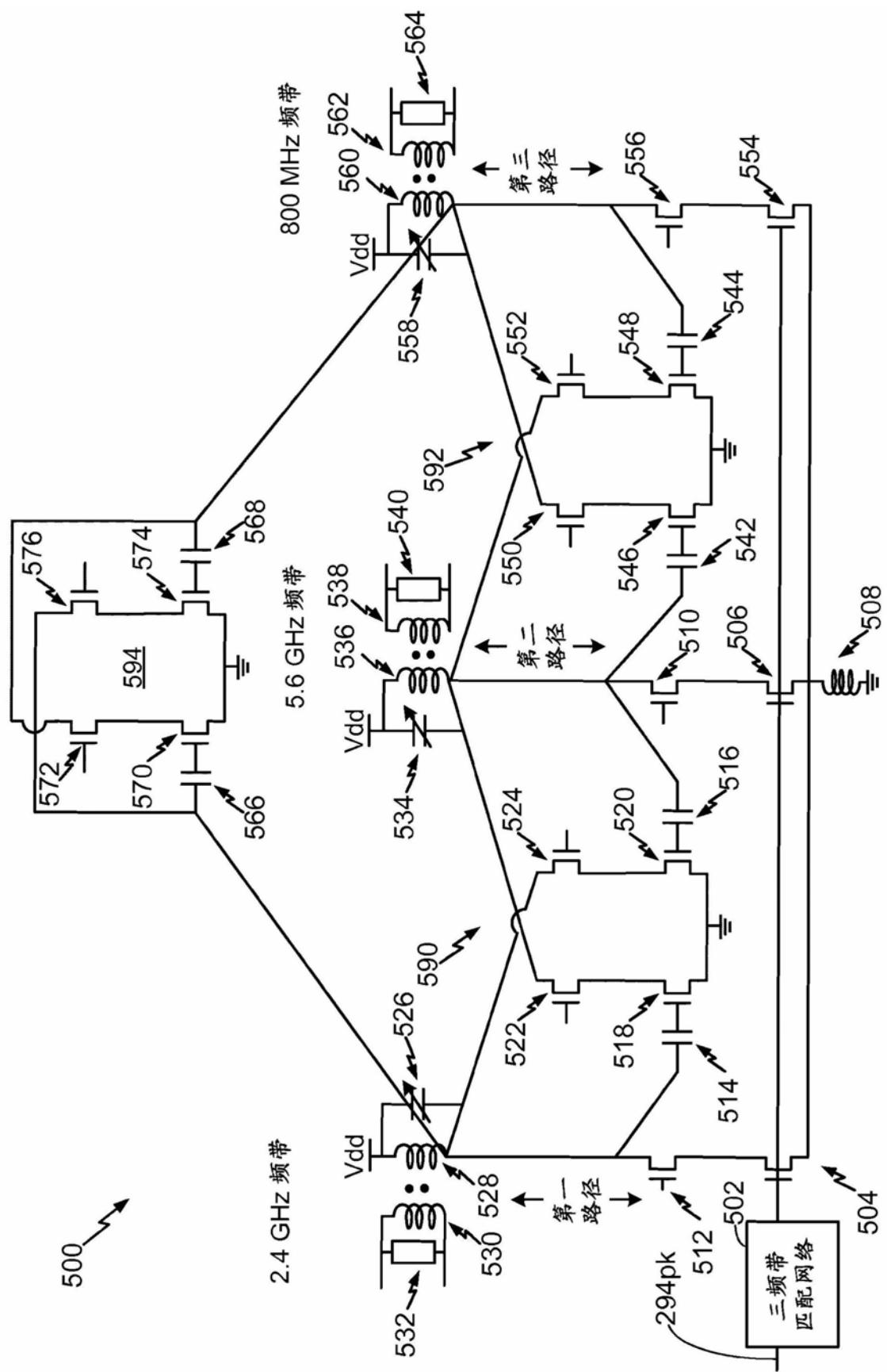

[0010] 图5是示出了三频带低噪声放大器的示例性实施例的视图；以及

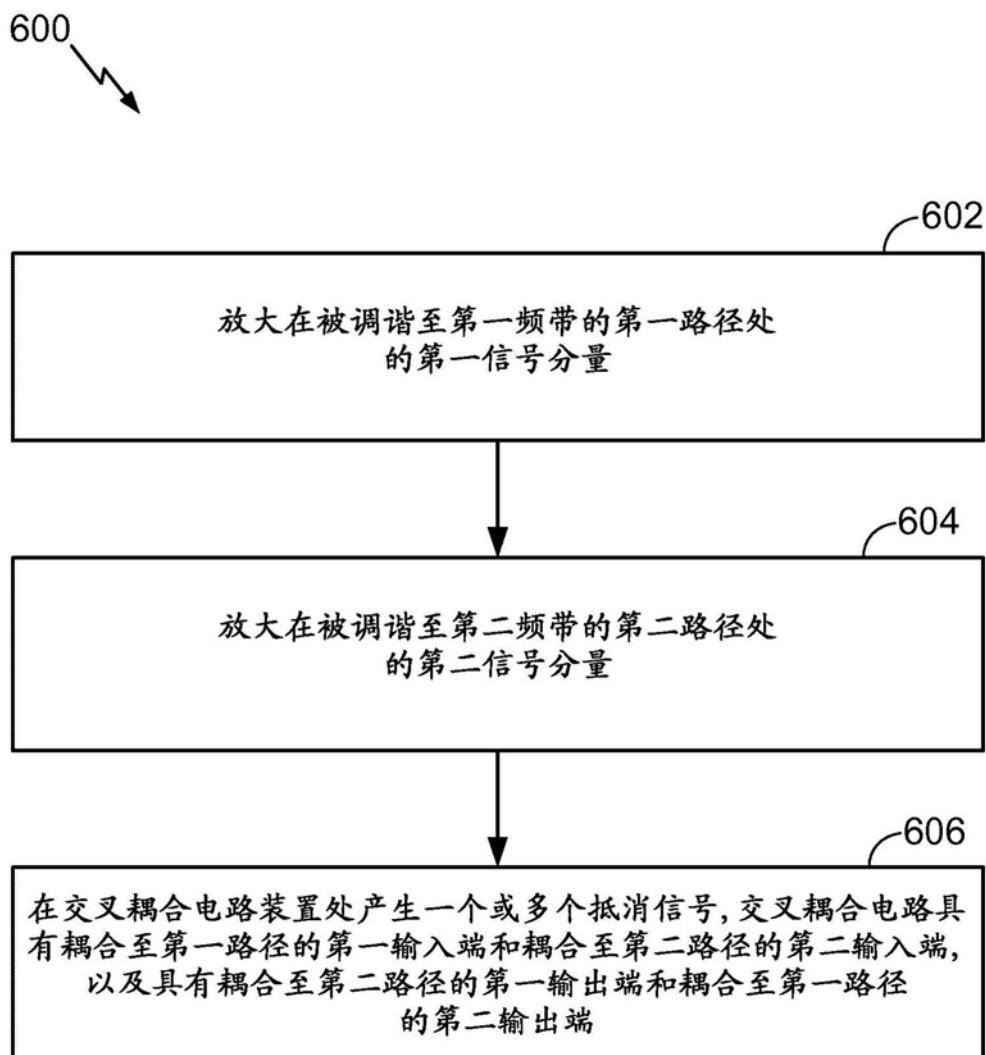

[0011] 图6是示出了操作多频带低噪声放大器的方法的示例性实施例的流程图。

### 具体实施方式

[0012] 以下阐述的详细说明书意在作为本公开的示例性设计的说明并且并非意在仅展示其中可以实施本公开的设计。术语“示例性”在此用于意味着“用作示例、实例或说明”。在

此描述为“示例性”的任何设计不必构造为在其他设计之上的优选或有利的。详细说明书为了提供本公开的示例性设计的全面理解的目的而包括具体细节。对于本领域技术人员明显的是可以不采用这些具体细节而实施在此所述的示例性设计。在一些情形中,以方框图形式示出广泛已知的结构和装置以便于避免模糊在此所展示的示例性设计的创新性。

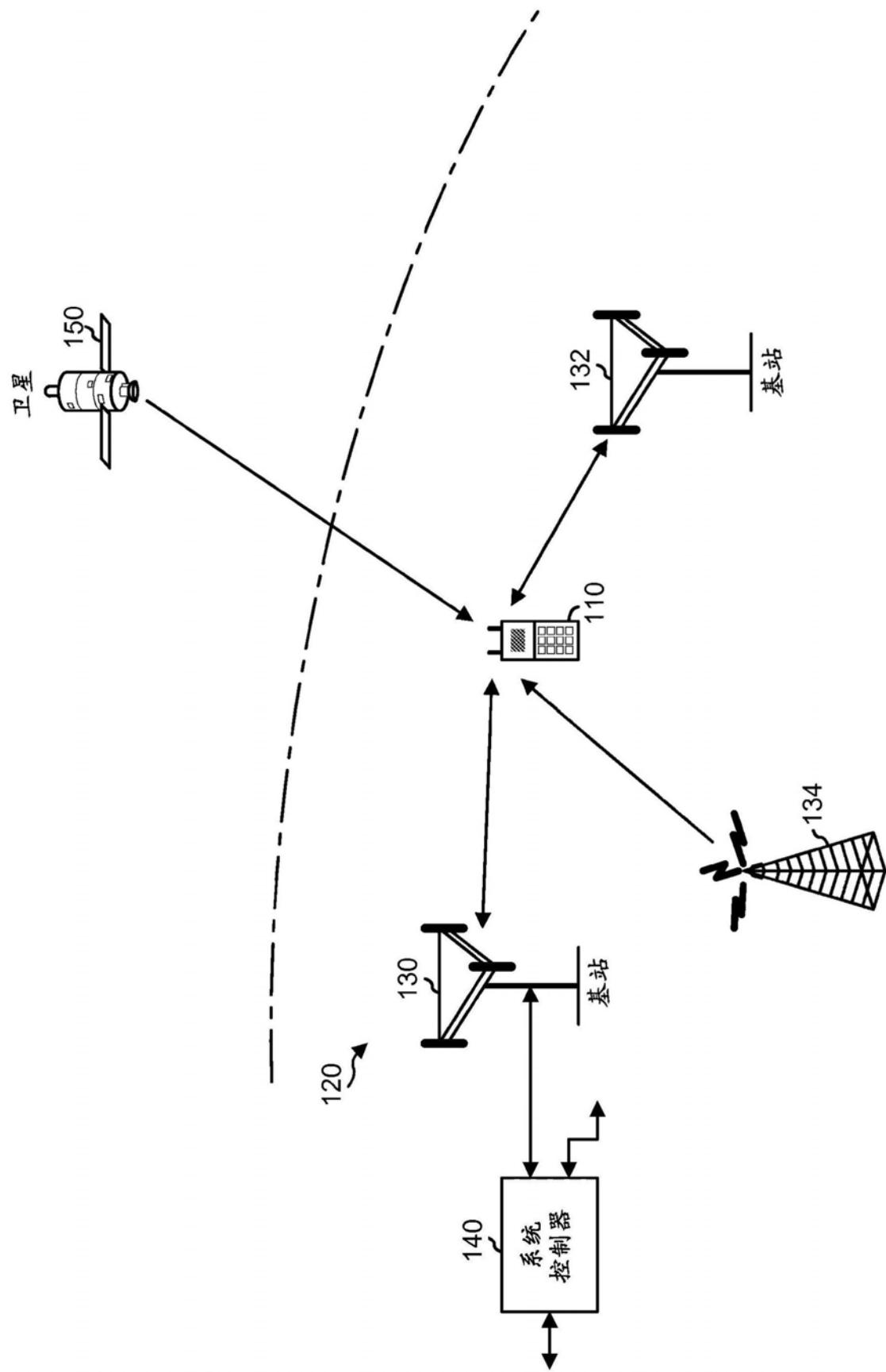

[0013] 图1示出了与无线通信系统120通信的无线装置110。无线通信系统120可以是长期演进 (LTE) 系统、码分多址 (CDMA) 系统、用于移动通信的全球系统 (GSM) 系统、无线局域网 (WLAN) 系统、或一些其他无线系统。CDMA系统可以实施宽带CDMA (WCDMA)、CDMA 1X、演进数据优化 (EVDO)、时分同步CDMA (TD-SCDMA)、或CDMA的一些其他版本。为了简便,图1示出了包括两个基站130和132以及一个系统控制器140的无线通信系统120。通常,无线系统可以包括任意数目的基站和网络实体的任意集合。

[0014] 无线装置110也可以称作用户设备 (UE)、移动站点、终端、访问终端、订户单元、站点等。无线装置110可以是蜂窝电话、智能电话、平板、无线调制解调器、个人数字助理 (PDA)、手持式装置、膝上型计算机、智能本、上网本、无绳电话、无线本地回路 (WLL) 站点、蓝牙装置等。无线装置110可以与无线系统120通信。无线装置110也可以接收来自广播站 (例如广播站134) 的信号,来自一个或多个全球导航卫星系统 (GNSS) 中卫星 (例如卫星150) 的信号等。无线装置110可以支持用于无线通信的一个或多个无线电技术诸如LTE、WCDMA、CDMA 1X、EVDO、TD-SCDMA、GSM、802.11等。

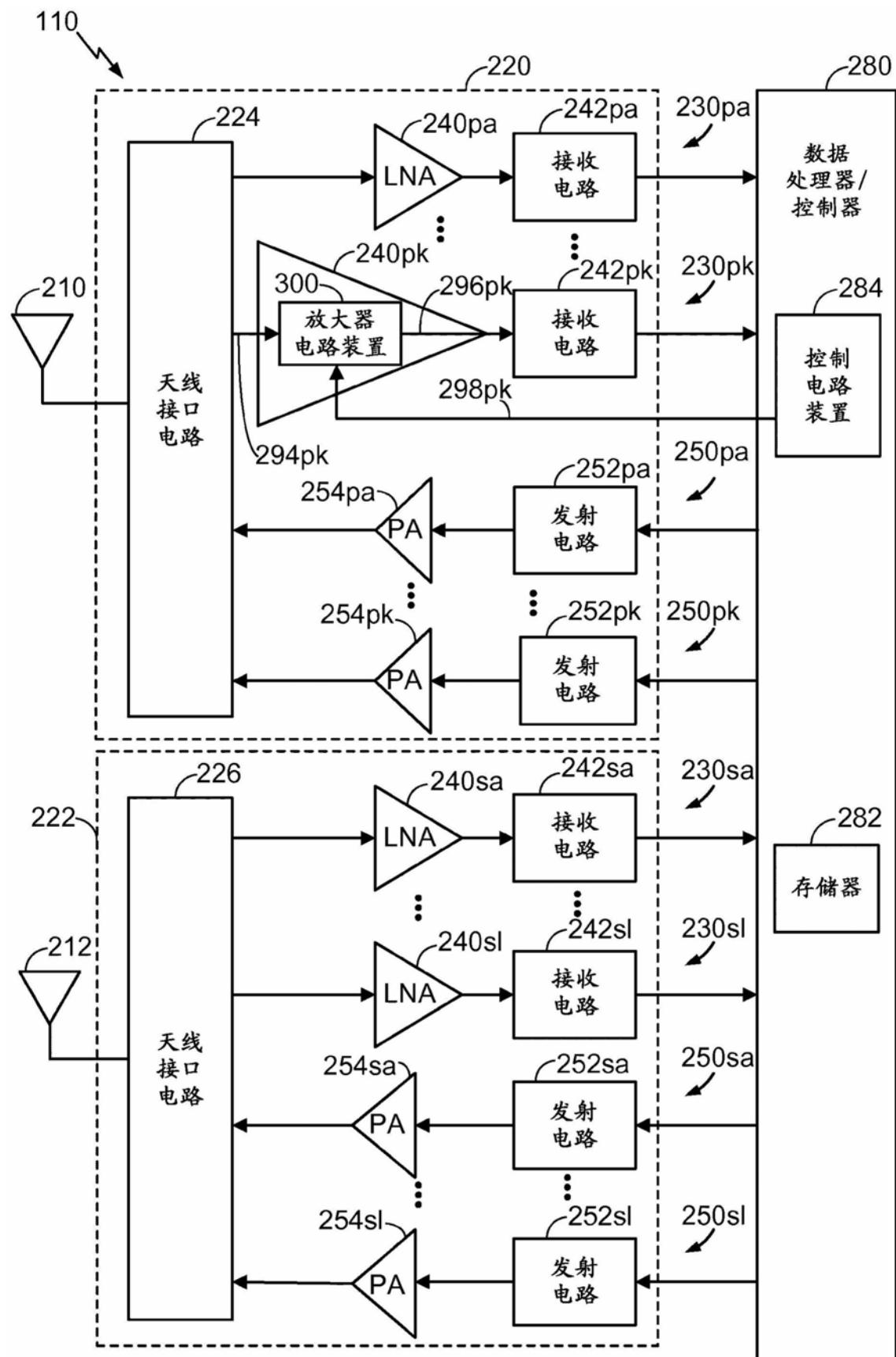

[0015] 图2示出了图1中无线装置110的示例性设计的方框图。在该示例性设计中,无线装置110包括耦合至初级天线210的收发器220,耦合至次级天线212的收发器222,以及数据处理器/控制器280。收发器220包括多个 (K) 接收器230pa至230pk以及多个 (K) 发射器250pa至250pk以支持多频带、多无线电技术、载波聚集等。收发器222包括多个 (L) 接收器230sa至230s1以及多个 (L) 收发器250sa至250s1以支持多频带、多无线电技术、载波聚集、接收多样性、从多个发射天线至多个接收天线的多输入多输出 (MIMO) 传输等。

[0016] 在图2中所示的示例性设计中,每个接收器230pa至230p1以及230sa至230s1分别包括多频带LNA 240pa至240pk和240sa至240s1以及接收电路242pa至242pk和242sa至242s1。为了数据接收,初级天线210从基站和/或其他发射器站点接收信号并且提供接收到的RF信号,其通过天线接口电路224发送并且作为输入RF信号294pk向所选择的接收器 (例如接收器230pk) 展示。以类似方式,次级天线212从基站和/或其他发射器站点接收信号并且提供已接收RF信号,其通过天线接口电路226发送,并且向所选择接收器展示输入RF信号。

[0017] 在示例性实施例中,输入RF信号294pk可以是具有在第一频带 (例如2.4吉赫兹 (GHz) 频带) 中的信号分量、在第二频带 (例如5.6GHz频带) 中的信号分量、和/或在第三频带 (例如800兆赫兹 (MHz) 频带) 中的信号分量的多频带信号。天线接口电路224可以包括开关、双工器、发射滤波器、接收滤波器、匹配电路等。以下说明书假设接收器230pk是所选择的接收器。在接收器230pk内,LNA 240pk放大输入RF信号294pk,并提供输出RF信号296pk。例如,LNA 240pk可以包括放大器电路装置300,如进一步参照图3所述,以放大输入RF信号294pk。在另一示例性实施例中,LNA 240pk可以包括放大器电路装置400 (如参照图4所述) 或放大器电路装置500 (如参照图5所述)。

[0018] 接收电路242pk可以将输出RF信号296pk从RF下变频转换至基带,放大并且滤波已

下变频信号，并且提供模拟输入信号至数据处理器/控制器280。接收电路242pk可以包括混频器、滤波器、放大器、匹配电路、振荡器、本地振荡器(LO)发生器、锁相环(PLL)等。收发器220、222中每个剩余的接收器可以与接收器230pk类似方式而工作。

[0019] 在图2中所示的示例性设计中，每个发射器250pa至250pk以及250sa至250s1分别包括发射电路252pa至252pk和252sa至252s1、以及功率放大器(PA) 254pa至254pk和254sa至254s1。为了数据传输，数据处理器/控制器280处理(例如编码并调制)待发射的数据并且向所选择发射器提供模拟输出信号。以下说明书假设发射器250pa是所选择的发射器。在发射器250pa内，发射电路252pa放大、滤波模拟输出信号并且将其从基带上变频转换至RF以及提供已调制的RF信号。发射电路252pa可以包括放大器、滤波器、混频器、匹配电路、振荡器、LO发生器、PLL等。PA 254pa接收并放大已调制的RF信号，并且提供具有合适的输出功率水平的发射RF信号。发射RF信号通过天线接口电路224发送并且经由初级天线210发射。收发器220、222中每个剩余发射器250pk、250sa、250s1可以与发射器250pa类似的方式工作。

[0020] 图2示出了接收器230pa至230pk和230sa至230s1以及发射器250pa至250pk和250sa至250s1的示例性设计。接收器和发射器也可以包括图2中未示出的其他电路，诸如滤波器、匹配电路等。收发器220和222的所有或一部分可以实施在一个或多个模拟集成电路(IC)、RF IC(RFIC)、混合信号IC等上。例如，LNAs 240pa至240pk和240sa至240s1以及接收电路242pa至242pk和242sa至242s1可以实施在一个模块上，其可以是RFIC等。收发器220和222中电路也可以以其他方式实施。

[0021] 在示例性实施例中，多频带LNAs 240pa至240pk以及240sa至240s1可以从数据处理器/控制器280中控制电路284接收控制信号(例如控制信号298pk)以同时多频带配置而操作在第一频带(例如2.4GHz频带)、第二频带(例如5.6GHz频带)、第三频带(例如800MHz频带)或其组合中的对应的多频带LNA(例如LNA 240pk)，如进一步参照图3-图5所述。

[0022] 数据处理器/控制器280可以执行用于无线装置110的各种功能。例如，数据处理器/控制器280可以执行对于经由接收器230pa至230pk和230sa至230s1所接收的数据，以及经由发射器250pa至250pk和250sa至250s1所发射的数据进行处理。数据处理器/控制器280可以控制收发器220和222内各个电路的工作。例如，数据处理器/控制器280可以包括控制电路284以同时多频带配置而在第一频带(例如2.4GHz频带)、第二频带(例如5.6GHz频带)、第三频带(例如800MHz频带)或其组合中操作多频带LNA(例如LNA 240pk)，如进一步参照图3-图5所述。存储器282可以存储用于数据处理器/控制器280的程序代码和数据。数据处理器/控制器280可以实施在一个或多个专用集成电路(ASICs)和/或其他IC上。

[0023] 无线装置110可以支持多频带群组、多个无线电技术、和/或多个天线。无线装置110可以包括许多LNA以支持经由多频带群组、多无线电技术、和/或多个天线而接收。

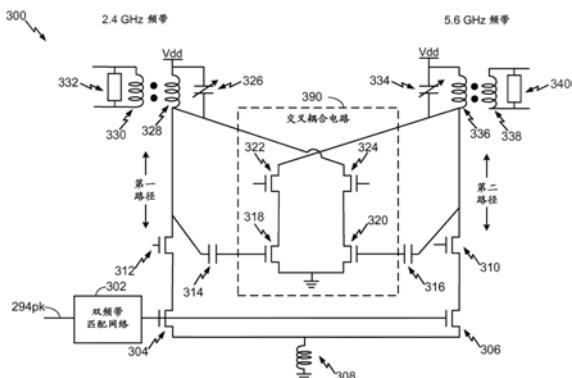

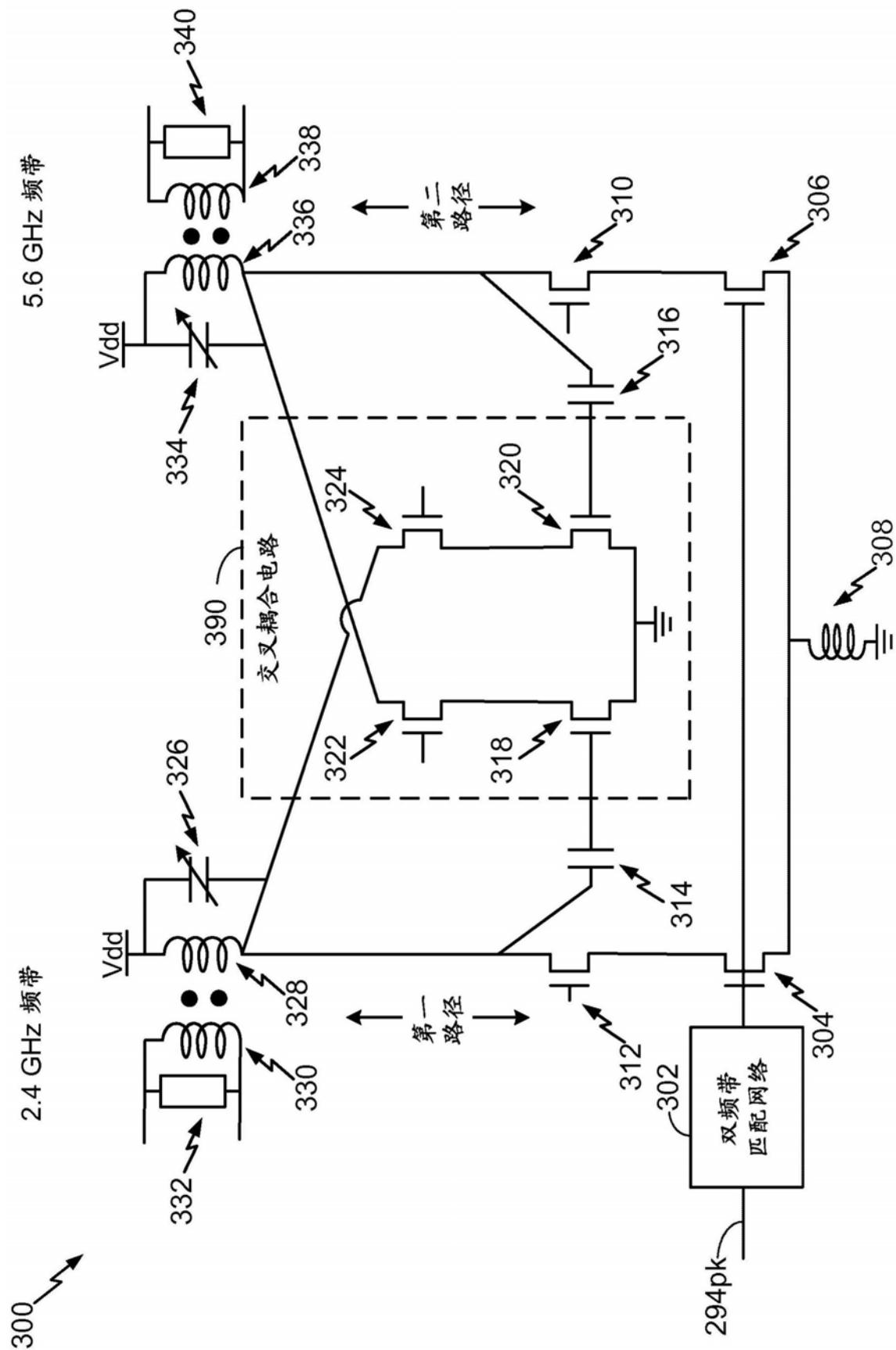

[0024] 参照图3，示出了双频带低噪声放大器的示例性实施例的视图。图3示出了在图2的LNA 240pk中放大器电路装置300的示例性实施例。

[0025] 放大器电路装置300包括耦合至晶体管304和晶体管306的双频带匹配网络302。双频带匹配网络302的输入被配置为接收图2的输入RF信号294pk，以及双频带匹配网络302的输出端可以耦合至晶体管304的栅极和晶体管306的栅极。在示例性实施例中，晶体管304和晶体管306是n型金属氧化物半导体(NMOS)晶体管。晶体管304的源极可以耦合至电感器308

的第一端子(例如负反馈电感器),以及晶体管306的源极也可以耦合至电感器308的第一端子。电感器308的第二端子可以耦合接地。在示例性实施例中,双频带匹配网络302(例如电感性-电容性(LC)网络)和电感器308可以在放大器300与图2的天线接口电路224之间提供输入阻抗匹配。

[0026] 晶体管304的漏极可以耦合至晶体管312的源极,从而晶体管304、312对应于级联晶体管的配对。晶体管312的漏极可以耦合至被调谐至第一频带(例如2.4GHz频带)或者在第一频带内频率下谐振的LC电路(例如电感器328和可调谐电容器326)。例如,晶体管312的漏极可以耦合至电感器328的第一端子以及可调谐电容器326的第一端子。电感器328的第二端子和可调谐电容器326的第二端子可以耦合至电源电压(Vdd),从而电感器328和可调谐电容器326并联耦合在一起。

[0027] 以类似方式,晶体管306的漏极可以耦合至晶体管310的源极,从而晶体管306、310对应于级联晶体管的配对。晶体管310的漏极可以耦合至被调谐至第二频带(例如5.6GHz频带)或者在第二频带内频率下谐振的LC电路(例如电感器336和可调谐电容器334)。例如,晶体管310的漏极可以耦合至第一电感器336的第一端子以及可调谐电容器334的第一端子。电感器336的第二端子和可调谐电容器334的第二端子可以耦合至电源电压(Vdd),从而电感器336和可调谐电容器334并联耦合在一起。

[0028] 电感器328的电感和可调谐电容器326的电容可以分别大于电感器336的电感和可调谐电容器334的电容,从而将第一路径(包括晶体管304、312)调谐至第一频带,并且将第二路径(包括晶体管306、310)调谐至第二频带。例如,晶体管304、312可以被配置用于放大输入RF信号294pk的2.4GHz信号分量,并且晶体管306、310可以被配置用于放大输入RF信号294pk的5.6GHz分量。

[0029] 电容器314的第一端子可以耦合至晶体管312的漏极(例如电容器314可以耦合至第一路径),以及电容器316的第一端子可以耦合至晶体管310的漏极(例如电容器316可以耦合至第二路径)。电容器314的第二端子可以耦合至交叉耦合电路390,以及电容器316的第二端子可以耦合至交叉耦合电路390。电容器314可以阻断(或基本上阻断)沿着来自交叉耦合电路390的第一路径的信号的直流(DC)分量,并且电容器316可以阻断(或基本上阻断)沿着来自交叉耦合电路390的第二路径的信号的DC分量。

[0030] 交叉耦合电路390可以包括晶体管318、晶体管320、晶体管322和晶体管324。在示例性实施例中,晶体管318-324是NMOS晶体管。晶体管318的栅极可以耦合至电容器314的第二端子,以及晶体管320的栅极可以耦合至电容器316的第二端子。晶体管318的源极和晶体管320的源极可以耦合接地,从而晶体管318、320是共源极晶体管。

[0031] 晶体管318的漏极可以耦合至晶体管322的源极,从而晶体管318、322对应于级联晶体管的配对。晶体管322的漏极可以耦合至可调谐电容器334的第一端子以及电感器336的第一端子(例如耦合至被调谐至5.6GHz频带的LC电路)。晶体管318、322可以被配置用于移相并放大2.4GHz信号分量以基本上消除(例如破坏性干扰)在第二路径处的第一信号分量(例如2.4GHz信号分量)。为了说明,晶体管318的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度来偏移2.4GHz信号分量的相位。可以由晶体管318、322放大移相的2.4GHz信号分量并且提供至LC电路334、336以基本上消除在第二路径处的2.4GHz分量(例如可以在LC电路334、336处产生2.4GHz缺口)。

[0032] 晶体管320的漏极可以耦合至晶体管324的源极,从而晶体管320、324对应于级联晶体管的第二配对。晶体管324的漏极可以耦合至可调谐电容器326的第一端子以及电感器328的第一端子(例如耦合至被调谐至2.4GHz频带的LC电路326、328)。晶体管320、324可以被配置用于相移并放大5.6GHz信号分量以基本上消除(例如破坏性干扰)在第一路径处第二信号分量(例如5.6GHz信号分量)。为了说明,晶体管320的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度偏移5.6GHz信号分量的相位。移相的5.6GHz信号分量可以由晶体管320、324放大并且提供至LC电路328、326以基本上消除在第一路径处5.6GHz分量(例如可以在LC电路328、326处产生5.6GHz缺口)。

[0033] 电感器328(例如初级线圈或初级绕组)可以电磁地耦合至电感器330(例如次级线圈或次级绕组)以形成变压器。例如,由电感器328从晶体管304、312接收的2.4GHz信号可以从电感器328“转移”(例如能量经由电感器328、330的电磁感应而转移)至电感器330。负跨导单元332可以与电感器330并联耦合,并且具有2.4GHz信号分量(例如输出RF信号296pk的第一部分)的差分输出信号可以跨负跨导单元332而产生。使用负跨导单元332可以增强LC电路328、326的品质因子。

[0034] 电感器336(例如初级线圈或初级绕组)可以电磁地耦合至电感器338(例如次级线圈或次级绕组)以形成变压器。例如,从晶体管306、310在电感器336处接收的5.6GHz信号分量可以从电感器336“转移”(例如能量经由电感器336、338的电磁感应而转移)至电感器338。负跨导单元340的使用可以与电感器338并联耦合,并且可以跨负跨导单元340而产生具有5.6GHz信号分量(例如输出RF信号296pk的第二部分)的差分输出信号。负跨导单元340的使用可以增强LC电路334、336的品质因子。

[0035] 放大器电路装置300可以基本上抵消在2.4GHz频率分量与5.6GHz频率分量之间的干扰,以改进对于多频带信号(例如输入RF信号294pk)的放大的吞吐量。例如,交叉耦合的电路390(例如晶体管318、322)可以基本上消除在第二路径处2.4GHz信号分量以使能第二路径以“隔离”5.6GHz信号分量,并且交叉耦合的电路390(例如晶体管320、324)可以基本上消除在第一路径处5.6GHz信号分量以使能第一路径以“隔离”2.4GHz信号分量。消除效果可以取决于两个路径的相移和幅度(例如取决于在晶体管318、320处相移并且取决于在第一路径、第二路径和交叉耦合电路处的信号放大)。

[0036] 因此,放大器电路装置300可以减小在输入信号294pk的2.4GHz信号分量和5.6GHz信号分量之间的带间干扰。减小带间干扰可以增强对于遵照用于无线局域网(WLAN)的电气和电子工程师协会(IEEE)802.11(“WiFi”)标准的系统的吞吐量。例如,可以减小在低噪声放大器处2G WiFi信号(例如2.4GHz信号分量)与5G WiFi信号(例如5.6GHz信号分量)之间的干扰。

[0037] 参照图4,示出了双频带低噪声放大器的另一示例性实施例的示图。例如,图4示出了放大器电路装置400的示例性实施例。放大器电路装置400是在图2的LNA 240pk中放大器电路装置300的备选实施例。

[0038] 放大器电路装置400包括耦合至晶体管401的双频带匹配网络402。例如,双频带匹配网络402的输入端配置用于接收图2的输入RF信号294pk,并且双频带匹配网络402的输出端可以耦合至晶体管404的栅极。在示例性实施例中,晶体管404是NMOS晶体管。晶体管404的源极可以耦合至电感器408(例如衰减电感器)的第一端子,并且电感器408的端子可以耦

合接地。在示例性实施例中,双频带匹配网络402(例如电感-电容(LC)网络)和408可以在放大器电路装置400与图2的天线接口电路224之间提供输入阻抗匹配。

[0039] 晶体管404的漏极可以耦合至晶体管412的源极和晶体管410的源极,从而晶体管412、410是共源极晶体管。晶体管412的漏极可以耦合至被调谐至第一频带(例如2.4GHz频带)的LC电路(例如电感器328和可调谐电容器426)。例如,晶体管412的漏极可以耦合至电感器428的第一端子和可调谐电容器426的第一端子。电感器428的第二端子和可调谐电容器426的第二端子可以耦合至电源电压(Vdd),从而电感器428和可调谐电容器426并联耦合在一起。晶体管410的漏极可以耦合至被调谐至第二频带(例如5.6GHz频带)的LC电路(例如电感器436和可调谐电容器434)。例如,晶体管410的漏极可以耦合至电感器436的第一端子和可调谐电容器434的第一端子。电感器436的第二端子和可调谐电容器434的第二端子可以耦合至电源电压(Vdd),从而电感器436和可调谐电容器434并联耦合在一起。

[0040] 电感器428的电感和可调谐电容器426的电容可以分别大于电感器436的电感和可调谐电容器434的电容,从而第一路径(包括晶体管412)被调谐至第一频带并且第二路径(包括晶体管410)被调谐至第二频带。例如,晶体管404、412可以配置用于放大输入RF信号294pk的2.4GHz信号分量,并且晶体管404、410可以被配置用于放大输入RF信号294pk的5.6GHz分量。

[0041] 电容器414的第一端子可以耦合至晶体管412的漏极(例如耦合至第一路径),并且电容器416的第一端子可以耦合至晶体管410的漏极(例如耦合至第二路径)。电容器414的第二端子可以耦合至交叉耦合的电路490,并且电容器416的第二端子可以耦合至交叉耦合的电路490。电容器414可以阻断(或基本上阻断)来自交叉耦合电路490的第一路径的DC分量,并且电容器416可以阻断(或基本上阻断)来自交叉耦合电路490的第二路径的DC分量。

[0042] 交叉耦合电路490可以包括晶体管418、晶体管420、晶体管422和晶体管424。在示例性实施例中,晶体管418-424是NMOS晶体管。晶体管418的栅极可以耦合至电容器414的第二端子,以及晶体管420的栅极可以耦合至电容器416的第二端子。晶体管418的源极和晶体管420的源极可以耦合接地以使得晶体管418、420是共源极晶体管。

[0043] 晶体管418的漏极可以耦合至晶体管422的源极,从而晶体管418、422对应于级联晶体管的第一配对。晶体管422的漏极可以耦合至可调谐电容器434的第一端子和电感器436的第一端子(例如耦合至被调谐至5.6GHz频带的LC电路434、436)。晶体管418、422可以配置用于相移并放大2.4GHz信号分量以基本上消除(例如破坏性干扰)在第二路径处第一信号分量(例如2.4GHz信号分量)。为了说明,晶体管418的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度偏移2.4GHz信号分量的相位。相移的2.4GHz信号分量可以由晶体管418、422放大并且提供至LC电路434、436以基本上消除在第二路径处2.4GHz分量(例如可以在LC电路434、436处产生2.4GHz缺口)。

[0044] 晶体管420的漏极可以耦合至晶体管424的源极,从而晶体管420、424对应于级联晶体管的第二配对。晶体管424的漏极可以耦合至可调谐电容器426的第一端子和电感器428的第一端子(例如耦合至被调谐至2.4GHz频带的LC电路426、428)。晶体管420、424可以被配置用于相移并放大5.6GHz信号分量以基本上抵消(例如破坏性干扰)在第一路径处第二信号分量(例如5.6GHz信号分量)。为了说明,晶体管420的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度偏移5.6GHz信号分量的相位。移相的5.6GHz信号分量可以由晶

体管420、424放大并且提供至LC电路428、426以基本上消除在第一路径处5.6GHz分量(例如可以在LC电路428、426处产生5.6GHz缺口)。

[0045] 电感器428(例如初级线圈或初级绕组)可以电磁地耦合至电感器430(例如次级线圈或次级绕组)以形成变压器。例如,在电感器428处从晶体管404、412接收的2.4GHz信号分量可以从电感器428“转移”(例如能量经由电感器428、430的电磁感应而转移)至电感器430。负跨导单元432可以与电感器430并联耦合,并且可以跨负跨导单元432产生具有2.4GHz信号分量(例如输出RF信号296pk的第一部分)的差分输出信号。负跨导单元432也可以增强LC电路428、426的品质因子。

[0046] 电感器436(例如初级线圈或初级绕组)可以电磁地耦合至电感器438(例如次级线圈或次级绕组)以形成变压器。例如,在电感器436处从晶体管406、410接收的5.6GHz信号分量可以从电感器436“转移”(例如能量经由电感器436、438的电磁感应而转移)至电感器438。负跨导单元440可以与电感器438并联耦合,可以跨负跨导单元440产生具有5.6GHz信号分量(例如输出RF信号296pk的第二部分)的差分输出信号。负跨导单元440也可以增强LC电路434、436的品质因子。

[0047] 放大器电路装置400可以基本上抵消在低噪声放大器中2.4GHz频率分量和5.6GHz频率分量之间的干扰以改进对于多频带信号(例如输入RF信号294pk)的放大的吞吐量。例如,交叉耦合电路490(例如晶体管418、422)可以基本上抵消在第二路径处2.4GHz信号分量,以使能第二路径以“隔离”5.6GHz信号分量,并且交叉耦合的电路490(例如晶体管420、422)可以基本上抵消在第一路径处5.6GHz信号分量,以使能第一路径以“隔离”2.4GHz信号分量。抵消效果可以取决于两个路径的相移和幅度(例如取决于在晶体管418、420处相移并取决于在第一路径、第二路径和交叉耦合电路处的信号放大)。因此,放大器电路装置400可以减小在2.4GHz信号分量和5.6GHz信号分量之间的带间干扰。减小带间干扰可以增强对于遵照用于无线局域网(WLAN)的WiFi标准的系统的吞吐量。例如,可以减小在2G WiFi信号和5G WiFi信号之间的干扰。

[0048] 参照图5,示出了三频带低噪声放大器的示例性实施例的示图。例如,图5示出了放大器电路装置500的示例性实施例。放大器电路装置500可以是在图2的LNA 240pk中放大器电路装置300的备选实施例,以及放大器电路装置500可以对应于三频带低噪声放大器。

[0049] 放大器电路装置500可以包括耦合至晶体管504、晶体管506和晶体管554的三频带匹配网络502。例如,三频带匹配网络502的输入端被配置用于接收图2的输入RF信号294pk,并且三频带匹配网络502的输出端可以耦合至晶体管504的栅极、晶体管506的栅极、以及晶体管554的栅极。在示例性实施例中,晶体管504、晶体管506和晶体管554是NMOS晶体管。晶体管504的源极可以耦合至电感器508(例如衰减电感器)的第一端子,以及晶体管554的源极也可以耦合至电感器508的第一端子。电感器508的第二端子可以耦合接地。在示例性实施例中,三频带匹配网络502(例如电感-电容(LC)网络)和电感器508可以在放大器电路装置500和图2的天线接口电路224之间提供输入阻抗匹配。

[0050] 晶体管504的漏极可以耦合至晶体管512的源极,从而晶体管504、512对应于级联晶体管的配对。晶体管512的漏极可以耦合至被调谐至第一频带(例如2.4GHz频带)的LC电路(例如电感器528和可调谐电容器526)。例如,晶体管512的漏极可以耦合至电感器528的第一端子和可调谐电容器526的第一端子。电感器528的第二端子和可调谐电容器526的第

二端子可以耦合至电源电压 (Vdd) , 从而电感器528和可调谐电容器526并联耦合在一起。

[0051] 晶体管506的漏极可以耦合至晶体管510的源极, 从而晶体管506、510对应于级联晶体管的配对。晶体管510的漏极可以耦合至被调谐至第二频带 (例如5.6GHz频带) 的LC电路 (例如电感器536和可调谐电容器534)。例如, 晶体管510的漏极可以耦合至电感器536的第一端子和可调谐电容器534的第一端子。电感器536的第二端子和可调谐电容器534的第二端子可以耦合至电源电压 (Vdd) , 从而电感器536和可调谐电容器534并联耦合在一起。

[0052] 晶体管554的漏极可以耦合至晶体管556的源极, 从而晶体管554、556对应于级联晶体管的配对。晶体管556的漏极可以耦合至被调谐至第三频带 (例如800MHz频带) 的LC电路 (例如电感器560和可调谐电容器558)。电感器560和可调谐电容器558可以包括在耦合至第三路径的第三LC电路中。第三LC电路可以在第三频带内的频率进行谐振。晶体管556的漏极可以耦合至电感器560的第一端子和可调谐电容器558的第一端子。电感器560的第二端子和可调谐电容器558的第二端子可以耦合至电源电压 (Vdd) , 从而电感器560和可调谐电容器558并联耦合在一起。

[0053] 电感器528的电感和可调谐电容器526的电容可以分别大于电感器526的电感和可调谐电容器534的电容, 从而第一路径 (包括晶体管504、512) 被调谐至第一频带并且第二路径 (包括晶体管506、510) 被调谐至第二频带。例如, 晶体管504、512可以被配置用于放大输入RF信号294pk的2.4GHz信号分量, 并且晶体管506、510可以被配置用于放大输入RF信号294pk的5.6GHz分量。电感器560的电感和可调谐电容器558的电感可以分别大于电感器536的电感和可调谐电容器534的电容, 从而第三路径 (包括晶体管554、556) 被调谐至第三频带。例如, 晶体管554、556可以被配置用于放大输入RF信号294pk的800MHz信号分量。

[0054] 电容器514的第一端子可以耦合至晶体管512的漏极 (例如耦合至第一路径) , 以及电容器516的第一端子可以耦合至晶体管510的漏极 (例如耦合至第二路径)。电容器514的第二端子可以耦合至交叉耦合的电路590, 以及电容器516的第二端子可以耦合至交叉耦合的电路590。电容器514可以阻断 (或基本上阻断) 来自交叉耦合电路590的第一路径的DC分量, 并且电容器516可以阻断 (或基本上阻断) 来自交叉耦合电路590的第二路径的DC分量。

[0055] 电容器542的第一端子可以耦合至晶体管510的漏极 (例如耦合至第二路径) , 以及电容器544的第一端子可以耦合至晶体管556的漏极 (例如耦合至第三路径)。电容器542的第二端子可以耦合至交叉耦合电路592, 并且电容器544的第二端子可以耦合至第二交叉耦合电路592。电容器542可以阻断 (或基本上阻断) 来自交叉耦合电路592的第二路径的DC分量, 并且电容器544可以阻断 (或基本上阻断) 来自交叉耦合电路592的第三路径的DC分量。

[0056] 电容器566的第一端子可以耦合至晶体管512的漏极 (例如耦合至第一路径) , 并且电容器568的第一端子可以耦合至晶体管556的漏极 (例如耦合至第三路径)。电容器566的第二端子可以耦合至交叉耦合电路594, 并且电容器568的第二端子可以耦合至交叉耦合电路594。电容器566可以阻断 (或基本上阻断) 来自交叉耦合电路594的第三路径的DC分量, 并且电容器568可以阻断 (或基本上阻断) 来自交叉耦合电路594的第三路径的DC分量。

[0057] 交叉耦合电路590可以包括晶体管518、晶体管520、晶体管522和晶体管524。在示例性实施例中, 晶体管518-524是NMOS晶体管。晶体管518的栅极可以耦合至电容器514的第二端子, 以及晶体管520的栅极可以耦合至电容器516的第二端子。晶体管518的源极和晶体管520的源极可以耦合接地, 从而晶体管518、520是共源极晶体管。

[0058] 晶体管518的漏极可以耦合至晶体管522的源极,从而晶体管518、522对应于级联晶体管的配对。晶体管522的漏极可以对应于可调谐电容器534的第一端子和电感器536的第一端子(例如耦合至被调谐至5.6GHz频带的LC电路534、536)。晶体管518、522可以被配置用于相移并放大2.4GHz信号分量,以基本上抵消(例如破坏性干扰)在第二路径处第一信号分量(例如2.4GHz信号分量)。为了说明,晶体管518的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度来偏移2.4GHz信号分量的相位。相移的2.4GHz信号分量可以由晶体管518、522放大,并提供至LC电路534、536,以基本上消除在第二路径处2.4GHz分量(例如可以在LC电路534、536处产生2.4GHz缺口)。

[0059] 晶体管520的漏极可以耦合至晶体管524的源极,从而晶体管520、524对应于级联晶体管的配对。晶体管524的漏极可以耦合至可调谐电容器526的第一端子和电感器528的第一端子(例如耦合至被调谐至2.4GHz频带的LC电路)。晶体管520、524可以被配置用于相移并放大5.6GHz信号分量以基本上抵消(例如破坏性干扰)在第一路径处的第二信号分量(例如5.6GHz信号分量)。为了说明,晶体管520的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度来偏移5.6GHz信号分量的相位。相移的5.6GHz信号分量可以由晶体管520、524放大,并提供至LC电路528、516,以基本上消除在第一路径处5.6GHz分量(例如可以在LC电路528、526处产生5.6GHz缺口)。

[0060] 交叉耦合的电路592可以包括晶体管546、晶体管548、晶体管550和晶体管552。在示例性实施例中,晶体管546-552是NMOS晶体管。晶体管516的栅极可以耦合至电容器542的第二端子,以及晶体管548的栅极可以耦合至电容器544的第二端子。晶体管546的源极和晶体管548的源极可以耦合接地,从而晶体管546、548是共源极晶体管。

[0061] 晶体管546的漏极可以耦合至晶体管550的源极,从而晶体管546、550对应于级联晶体管的配对。晶体管550的漏极可以耦合至可调谐电容器560的第一端子和电感器558的第一端子(例如耦合至被调谐至800MHz频带的LC电路)。晶体管546、550可以被配置用于相移并放大5.6GHz信号分量以基本上抵消(例如破坏性干扰)在第三路径处第二信号分量(例如5.6GHz信号分量)。为了说明,晶体管546的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度来偏移5.6GHz信号分量的相位。相移的5.6GHz信号分量可以由晶体管546、550放大,并提供至LC电路558、569以基本上消除在第三路径处5.6GHz分量(例如可以在LC电路558、560处产生5.6GHz缺口)。

[0062] 晶体管548的漏极可以耦合至晶体管552的源极,从而晶体管548、552对应于级联晶体管的配对。晶体管552的漏极可以耦合至可调谐电容器534的第一端子和电感器536的第一端子(例如耦合至被调谐至5.6GHz频带的LC电路)。晶体管548、552可以被配置用于相移并放大800MHz信号分量,以基本上抵消(例如破坏性干扰)在第二路径处第三信号分量(例如800MHz信号分量)。为了说明,晶体管548的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度来偏移800MHz信号分量的相位。相移的800MHz信号分量可以由晶体管548、552放大并且提供至LC电路534、536,以基本上消除在第二路径处800MHz(例如可以在LC电路534、536处产生800MHz缺口)。

[0063] 交叉耦合电路594可以包括晶体管570、晶体管574、晶体管572和晶体管576。在示例性实施例中,晶体管570-576是NMOS晶体管。晶体管570的栅极可以耦合至电容器566的第二端子,以及晶体管574的栅极可以耦合至电容器568的第二端子。晶体管570的源极和晶体

管574的源极可以耦合接地,从而晶体管570、574是共源极晶体管。

[0064] 晶体管570的漏极可以耦合至晶体管572的源极,从而晶体管570、572对应于级联晶体管的配对。晶体管572的漏极可以耦合至可调谐电容器558的第一端子和电感器560的第一端子(例如耦合至被调谐至800MHz频带的LC电路)。晶体管570、572可以被配置用于相移并放大2.4GHz信号分量,以基本上抵消(例如破坏性干扰)在第三路径处第一信号分量(例如2.4GHz信号分量)。为了说明,晶体管570的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度来偏移2.4GHz信号分量的相位。经相移的2.4GHz信号分量可以由晶体管570、572放大并提供至LC电路558、560,以基本上消除在第三路径处2.4GHz分量(例如可以在LC电路558、560处产生2.4GHz缺口)。

[0065] 晶体管574的漏极可以耦合至晶体管576的源极,从而晶体管574、576对应于级联晶体管的配对。晶体管576的漏极可以耦合至可调谐电容器526的第一端子和电感器528的第一端子(例如耦合至被调谐至2.4GHz频带的LC电路)。晶体管574、576可以被配置用于相移并放大800MHz信号分量,以基本上抵消(例如破坏性干扰)在第一路径处第三信号分量(例如800MHz信号分量)。为了说明,晶体管574的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度来偏移800MHz信号分量的相位。经相移的800MHz信号分量可以由晶体管575、576放大并提供至LC电路528、526,以基本上消除在第一路径处的800MHz分量(例如可以在LC电路528、526处产生800MHz缺口)。

[0066] 电感器528(例如初级线圈或初级绕组)可以电磁地耦合至电感器530(例如次级线圈或次级绕组)以形成变压器。例如,在电感器528处从晶体管504、512接收的2.4GHz信号分量可以从电感器528“转移”(例如能量经由电感器528、530的电磁感应而转移)至电感器530。负跨导单元532可以与电感器530并联耦合,并且可以跨负跨导单元532而产生具有2.4GHz信号分量(例如输出RF信号296pk的一部分)的差分输出信号。负跨导单元532也可以增强LC电路528、526的品质因子。

[0067] 电感器536(例如初级线圈或初级绕组)可以电磁地耦合至电感器538(例如次级线圈或次级绕组)以形成变压器。例如,由电感器536从晶体管506、510接收的5.6GHz信号分量可以从电感器536“转移”(例如能量经由电感器536、538的电磁感应而转移)至电感器538。负跨导单元540可以与电感器538并联耦合,以及可以跨负跨导单元540而产生具有5.6GHz信号分量(例如输出RF信号296pk的一部分)的差分输出信号。负跨导单元540也可以增强LC电路534、536的品质因子。

[0068] 电感器560(例如初级线圈或初级绕组)可以电磁地耦合至电感器562(例如次级线圈或次级绕组)以形成变压器。例如,由电感器560从晶体管554、556接收的800MHz信号分量可以从电感器560“转移”(例如能量经由电感器560、562的电磁感应而转移)至电感器562。负跨导单元564可以与电感器562并联耦合,以及可以跨负跨导单元564产生具有800MHz信号分量(例如输出RF信号296pk的一部分)的差分输出信号。负跨导单元564也可以增强LC电路558、560的品质因子。

[0069] 因此,放大器电路装置500可以减小在800MHz分量、2.4GHz信号分量与5.6GHz信号分量之间的带间干扰。减小带间干扰可以增强对于遵照用于WLAN的WiFi标准的系统的吞吐量。例如,可以减小在蜂窝信号、2G WiFi信号和5G WiFi信号之间的干扰。放大器电路装置500也可以减小在第一频带(例如2.4GHz频带)和第三频带(例如800MHz频带)之间的干扰以

增强对于广域网 (WAN) 的吞吐量。

[0070] 参照图6,流程图示出了操作多频带低噪声放大器的方法600的示例性实施例。在示例性实施例中,可以使用图1-图2的无线装置110、图2的多频带低噪声放大器240pk、图2-图3的放大器电路装置300、图4的放大器电路装置400、图5的放大器电路装置500或其组合而执行方法600。

[0071] 方法600包括在602处,放大在被调谐至第一频带的第一路径处的第一信号分量。例如,参照图3,电感器328的电感和可调谐电容器326的电容可以将第一路径调谐至第一频带(例如2.4GHz频带)。因此,第一路径(被调谐至第一频带)的晶体管304、312可以放大输入RF信号294pk的第一信号分量(例如2.4GHz信号分量)。

[0072] 在604处,可以放大在被调谐至第二频带的第二路径处的第二信号分量。例如,参照图3,电感器336的电感和可调谐电容器334的电容可以调谐第二路径至第二频带(例如5.6GHz频带)。因此,第二路径(被调谐至第二频带)的晶体管306、310可以放大输入RF信号294pk的第二信号分量(例如5.6GHz信号分量)。

[0073] 在606处,可以在交叉耦合电路装置处产生一个或多个抵消信号。例如,参照图3,交叉耦合电路390的晶体管318、322可以相移并放大在第二路径处2.4GHz信号分量。为了说明,晶体管318的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180度相移2.4GHz信号分量的相位。经相移的2.4GHz信号分量可以由晶体管318、322放大并提供至LC电路334、336,以基本上抵消在第二路径处2.4GHz分量(例如可以在LC电路334、336处产生2.4GHz缺口)。额外地,交叉耦合电路390的晶体管320、324可以相移并放大5.6GHz信号分量以基本上消除(例如破坏性干扰)在第一路径处第二信号分量(例如5.6GHz信号分量)。为了说明,晶体管320的拓扑结构(例如共源极晶体管拓扑结构)可以以大约180偏移5.6GHz信号分量的相位。相移的5.6GHz信号分量可以由晶体管320、324放大并提供至LC电路328、326以基本上消除在第一路径处5.6GHz分量(例如可以在LC电路328、326处产生5.6GHz缺口)。

[0074] 图6的方法600可以基本上消除在2.4GHz频率分量与5.6GHz频率分量之间的干扰以改进对于多频带信号(例如输入RF信号294pk)的放大器吞吐量。例如,交叉耦合电路390(例如晶体管318、322)可以基本上抵消在第二路径处的2.4GHz信号分量,以使能第二路径以“隔离”5.6GHz信号分量,并且交叉耦合电路390(例如晶体管320、324)可以基本上消除在第一路径处5.6GHz信号分量,以使能第一路径以“隔离”2.4GHz信号分量。抵消效果可以取决于两个路径的相移和幅度(例如取决于在晶体管318、320处相移以及取决于在第一路径、第二路径和交叉耦合电路处的信号放大)。

[0075] 因此,方法600可以减小在2.4GHz信号分量与5.6GHz信号分量之间的带间干扰。减小带间干扰可以增强对于遵照用于WLAN的WiFi标准的系统的吞吐量。例如,可以减小在2G WiFi信号(例如2.4GHz信号分量)和5G WiFi信号(例如5.6GHz信号分量)之间的干扰。

[0076] 结合所述实施例,一种设备包括用于放大第一信号分量的装置。可以将用于放大第一信号分量的装置调谐至第一频带。例如,用于放大第一信号分量的装置可以包括图3的第一路径、图4的第一路径、图5的第一路径、一个或多个其他装置、电路或其任意组合。

[0077] 设备也可以包括用于放大第二信号分量的装置。可以将用于放大第二信号分量的装置调谐至第二频带。例如,用于放大第二信号分量的装置可以包括图3的第二路径、图4的第二路径、图5的第二路径、一个或多个其他装置、电路或者其任意组合。

[0078] 设备也可以包括用于产生一个或多个消除信号的装置。用于产生一个或多个消除信号的装置具有耦合至用于放大第一信号分量的装置的第一输入端,以及耦合至用于放大第二信号分量的装置的第二输入端。用于产生一个或多个消除信号的装置也可以具有耦合至用于放大第二信号分量的第一输出端,以及耦合至用于放大第一信号分量的第二输出端。例如,用于产生一个或多个消除信号的装置可以包括图3的交叉耦合电路390、图4的交叉耦合电路390、图5的晶体管418、图5的晶体管520、图5的晶体管522、图5的晶体管524、一个或多个其他装置、电路、或者其任意组合。

[0079] 本领域技术人员将进一步知晓结合在此所公开实施例描述的各种示意性逻辑组块、配置、模块、电路和算法步骤可以实施作为电子硬件、由处理器执行的计算机软件、或者其组合。以上已经通常根据它们的功能而描述了各种示意性部件、组块、配置、模块、电路和步骤。该功能是否实施作为硬件或处理器可执行指令取决于特定的应用和对整体系统提出的设计约束。本领域技术人员可以对于每个特定应用以改变的方式实施所述功能,但是该实施方式决策不应解释为使得脱离本公开的范围。

[0080] 结合在此所公开实施例描述的方法或算法的步骤可以直接地具体化在硬件中、在由处理器执行的软件模块中、或者两者的组合。软件模块可以驻留在随机访问存储器 (RAM)、快闪存储器、只读存储器 (ROM)、可编程只读存储器 (PROM)、可擦除可编程只读存储器 (EPROM)、电可擦除可编程只读存储器 (EEPROM)、寄存器、硬盘、可移除盘、小型盘只读存储器 (CD-ROM)、或本领域已知的非临时存储媒介的任何其他形式中。示例性的存储媒介耦合至处理器以使得处理器可以从存储媒介读取信息并且向其写入信息。在备选例中,存储媒介可以集成至处理器。处理器和存储媒介可以驻留在专用集成电路 (ASIC) 中。ASIC可以驻留在计算装置或用户终端中。在备选例中,处理器和存储媒介可以作为分立部件驻留在计算装置或用户终端中。

[0081] 提供所公开实施例的之前说明以使得本领域技术人员制造或使用所公开实施例。对这些实施例的各种修改将对于本领域技术人员是显而易见的,并且在此所限定的原理可以适用于其他实施例而并未脱离本公开的范围。因此,本公开并非意在限定于在此所示的实施例而是应该符合与由以下权利要求所限定的原理和创新性特征一致的可能最宽的范围。

图1

图2

图3

图4

图5

图6