(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3914239号

(P3914239)

(45) 発行日 平成19年5月16日(2007.5.16)

(24) 登録日 平成19年2月9日(2007.2.9)

(51) Int.C1.

F 1

H05K 3/46 (2006.01)

H01L 23/12 (2006.01)H05K 3/46

H05K 3/46

H05K 3/46

H01L 23/12Q

B

N

N

請求項の数 11 (全 17 頁)

(21) 出願番号 特願2005-73946 (P2005-73946)

(22) 出願日 平成17年3月15日 (2005.3.15)

(65) 公開番号 特開2006-261246 (P2006-261246A)

(43) 公開日 平成18年9月28日 (2006.9.28)

審査請求日 平成18年8月21日 (2006.8.21)

早期審査対象出願

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 山野 孝治

長野県長野市小島田町80番地 新光電気

工業株式会社内

(72) 発明者 春原 昌宏

長野県長野市小島田町80番地 新光電気

工業株式会社内

(72) 発明者 飯塚 肇

長野県長野市小島田町80番地 新光電気

工業株式会社内

最終頁に続く

(54) 【発明の名称】配線基板および配線基板の製造方法

(57) 【特許請求の範囲】

【請求項1】

半導体チップが内蔵された配線基板であつて、

前記半導体チップが埋設される絶縁層と、

前記半導体チップの第1の側に形成され、該半導体チップに接続されるとともに第1の端子接続部に接続される第1のパターン配線と、

前記半導体チップの第2の側に形成され、該半導体チップに接続されるとともに第2の端子接続部に接続される第2のパターン配線と、

前記絶縁層に形成され、前記第1のパターン配線と前記第2のパターン配線を接続するビアプラグと、

前記絶縁層に形成される補強構造体と、を有し、

前記絶縁層は、前記第1のパターン配線および前記半導体チップを覆う絶縁層と、該絶縁層上に形成される別の絶縁層を含むように構成され、

前記補強構造体は、前記第1のパターン配線および前記半導体チップを覆う絶縁層上に設置されるとともに、前記別の絶縁層に埋設されていることを特徴とする配線基板。

【請求項2】

前記補強構造体は、前記半導体チップと同一平面上に形成されることを特徴とする請求項1記載の配線基板。

【請求項3】

前記補強構造体は、前記半導体チップを囲むように形成されることを特徴とする請求項

1または2記載の配線基板。

【請求項4】

前記第1の配線パターン、前記第2の配線パターン、および前記ビアプラグは、多層配線構造を構成することを特徴とする請求項1乃至3のうち、いずれか1項記載の配線基板。

【請求項5】

前記補強構造体は、有機コア材料または金属材料よりなることを特徴とする請求項1乃至4のうち、いずれか1項記載の配線基板。

【請求項6】

半導体チップが内蔵された配線基板の製造方法であって、

前記半導体チップに接続される第1のパターン配線と、該第1のパターン配線に接続される第1の端子接続部とを形成する工程と、

前記第1のパターン配線上に前記半導体チップを設置する工程と、

前記第1のパターン配線と前記半導体チップを覆う絶縁層を形成する工程と、

前記絶縁層上に補強構造体を設置する工程と、

前記絶縁層上に、前記補強構造体を埋設する別の絶縁層を形成する工程と、

前記絶縁層および前記別の絶縁層に、前記第1のパターン配線に接続されるビアプラグを形成する工程と、

前記ビアプラグに接続される第2のパターン配線と、該第2のパターン配線に接続される第2の端子接続部を形成する工程と、を有することを特徴とする配線基板の製造方法。

【請求項7】

前記補強構造体は、前記半導体チップと同一平面上に設置されることを特徴とする請求項6記載の配線基板の製造方法。

【請求項8】

前記第1のパターン配線は、コア基板上に形成され、当該コア基板を除去する工程をさらに有することを特徴とする請求項6または7記載の配線基板の製造方法。

【請求項9】

前記コア基板は導電性の材料よりなり、前記第1の端子接続部は当該コア基板を電極にした電解メッキにより形成される部分を含むことを特徴とする請求項8記載の配線基板の製造方法。

【請求項10】

前記半導体チップにはスタッドバンプが設置されており、当該スタッドバンプを介して当該半導体チップが前記第1のパターン配線に電気的に接続されることを特徴とする請求項6乃至9のうち、いずれか1項記載の配線基板の製造方法。

【請求項11】

前記スタッドバンプと前記第1のパターン配線の間には、半田よりなる接続部が形成されていることを特徴とする請求項10記載の配線基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は配線基板および配線基板の製造方法に係り、特には半導体チップを内蔵する配線基板およびその製造方法に関する。

【背景技術】

【0002】

現在、半導体チップなどの半導体装置を用いた電子機器の高性能化が進められており、基板へ半導体チップを実装する場合の高密度化や、また半導体チップを搭載した基板の小型化、省スペース化などが求められている。

【0003】

このため、半導体チップが埋め込まれた基板、いわゆるチップ内蔵型の配線基板が提案されており、半導体チップを基板に内蔵するための様々な構造が提案されている。このよ

10

20

30

40

50

うなチップ内蔵型の配線基板は、半導体チップに接続される配線構造を有し、さらに当該配線基板を他のデバイスや、マザーボードなどと接続可能にする端子接続部が形成されている。

【特許文献1】特開2001-196525号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし、チップ内蔵型の配線基板の薄型化、高密度化を実現しようとした場合、配線基板の反りが問題になる場合があった。このような反りに対応するためには、例えばコア基板などの所定の厚さの基板を、半導体チップが埋設された層と積層して反りを抑制する構造とする必要があり、このような積層構造とすると配線基板の薄型化や高密度化が困難となる問題があった。

【0005】

このように、配線基板の反りを抑制しながら、配線基板の薄型化を実現することは困難であった。

【0006】

そこで、本発明では上記の問題を解決した、新規で有用な配線基板および当該配線基板の製造方法を提供することを目的としている。

【0007】

本発明の具体的な課題は、半導体チップを内蔵した配線基板の薄型化を実現し、かつ当該配線基板の反りを抑制することである。

【課題を解決するための手段】

【0008】

本発明の第1の観点では、上記の課題を、半導体チップが内蔵された配線基板であって、前記半導体チップが埋設される絶縁層と、前記半導体チップの第1の側に形成され、該半導体チップに接続されるとともに第1の端子接続部に接続される第1のパターン配線と、前記半導体チップの第2の側に形成され、該半導体チップに接続されるとともに第2の端子接続部に接続される第2のパターン配線と、前記絶縁層に形成され、前記第1のパターン配線と前記第2のパターン配線を接続するビアプラグと、前記絶縁層に形成される補強構造体と、を有し、前記絶縁層は、前記第1のパターン配線および前記半導体チップを覆う絶縁層と、該絶縁層上に形成される別の絶縁層を含むように構成され、前記補強構造体は、前記第1のパターン配線および前記半導体チップを覆う絶縁層上に設置されるとともに、前記別の絶縁層に埋設されていることを特徴とする配線基板により、解決する。

【0009】

当該配線基板は、反りが抑制されると共に薄型化が可能な構造を有している。

【0010】

また、前記補強構造体は、前記半導体チップと同一平面上に形成されると、配線基板の薄型化を実現することが可能である。

【0011】

また、前記補強構造体は、前記半導体チップを囲むように形成されると、前記配線基板の反りを抑制する効果が良好となる。

【0012】

また、前記第1の配線パターン、前記第2の配線パターン、および前記ビアプラグは、多層配線構造を構成すると、当該配線構造の高密度化が可能となり、好適である。

【0016】

また、前記補強構造体は、有機コア材料または金属材料よりなると好適である。

【0017】

また、本発明の第2の観点では、上記の課題を、半導体チップが内蔵された配線基板の製造方法であって、前記半導体チップに接続される第1のパターン配線と、該第1のパターン配線に接続される第1の端子接続部とを形成する工程と、前記第1のパターン配線上

10

20

30

40

50

に前記半導体チップを設置する工程と、前記第1のパターン配線と前記半導体チップを覆う絶縁層を形成する工程と、前記絶縁層上に補強構造体を設置する工程と、前記絶縁層上に、前記補強構造体を埋設する別の絶縁層を形成する工程と、前記絶縁層および前記別の絶縁層に、前記第1のパターン配線に接続されるビアプラグを形成する工程と、前記ビアプラグに接続される第2のパターン配線と、該第2のパターン配線に接続される第2の端子接続部を形成する工程と、を有することを特徴とする配線基板の製造方法により、解決する。

【0018】

当該配線基板の製造方法によれば、半導体チップを内蔵した配線基板の薄型化を実現し、かつ当該配線基板の反りを抑制することが可能となる。

10

【0019】

また、前記補強構造体は、前記半導体チップと同一平面上に設置されると、当該配線基板の薄型化が可能となる。

【0021】

また、前記第1のパターン配線は、コア基板上に形成され、当該コア基板を除去する工程をさらに有すると、当該配線基板の薄型化を実現すると共に、安定に当該配線基板を形成することが可能となり、好適である。

【0022】

また、前記コア基板は導電性の材料よりなり、前記第1の端子接続部は当該コア基板を電極にした電解メッキにより形成される部分を含むと、当該電解メッキを行う場合の給電が容易になり、好適である。

20

【0023】

また、前記半導体チップにはスタッドバンプが設置されており、当該スタッドバンプを介して当該半導体チップが前記第1のパターン配線に電気的に接続されると、当該半導体チップと当該第1のパターン配線の電気的な接続の信頼性を向上させることができる。

【0024】

また、前記スタッドバンプと前記第1のパターン配線の間には、半田よりなる接続部が形成されていると、当該半導体チップと当該第1のパターン配線の電気的な接続の信頼性を向上させることができる。

【発明の効果】

30

【0025】

本発明によれば、半導体チップを内蔵した配線基板の薄型化を実現し、かつ当該配線基板の反りを抑制することが可能となる。

【発明を実施するための最良の形態】

【0026】

次に、本発明の実施の形態について図面に基づき、以下に説明する。

【実施例1】

【0027】

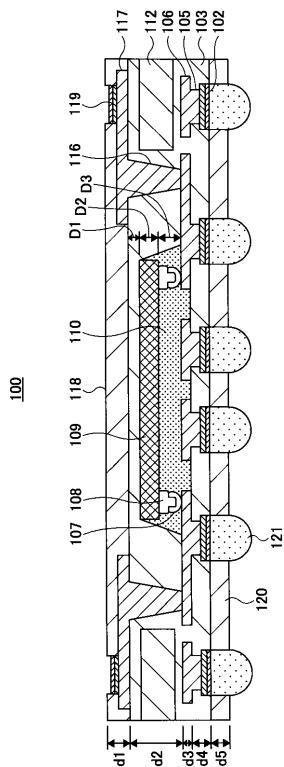

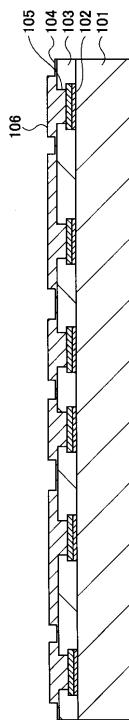

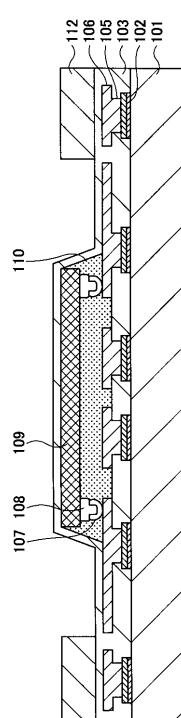

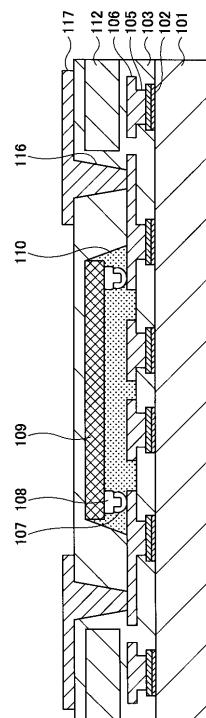

図1は、本発明の実施例1による配線基板100を、模式的に示した断面図である。

【0028】

40

図1を参照するに、本実施例による配線基板100の概要は、絶縁層103に埋設された半導体チップ109と、当該半導体チップ109に接続される配線構造とを有している。当該配線構造は、パターン配線106, 117, ビアプラグ105, 116を有している。

【0029】

さらに、前記配線基板100は、前記配線構造を介して前記半導体チップ100に接続された、当該配線基板100の第1の側に形成された端子接続部102、および第1の側の反対側の第2の側に形成された端子接続部119とを有している。

【0030】

従来、このような半導体チップ内蔵型の配線基板を薄型化しようとした場合、例えばコ

50

ア基板など、配線基板を支持して反りを抑制する構造体と積層される構造とされることがあり、薄型化と反りの抑制を実現することは困難であった。

【0031】

そこで、本実施例による配線基板100では、前記半導体チップ109が埋設された、前記絶縁層103に、当該絶縁層103を補強して、反りを防止する補強構造体112を埋設している。当該補強構造体112を用いることで、前記配線基板100の反りを抑制するところが可能となっている。また、上記の構造の場合には、前記配線基板100の厚さを実質的に増大させることなく、当該配線基板100の反りを効果的に抑制することが可能となっている。

【0032】

このため、例えば、前記絶縁層103と、当該絶縁層103を支持するためのコア基板とを積層させる構造を有する配線基板と比べて、薄型化が可能な構造になっている。

【0033】

次に、前記配線基板100の構造の詳細についてみると、例えば前記半導体チップ100に接続される前記配線構造は、例えば、Cuよりなる、パターン配線106, 117と、ビアプラグ105, 116とを有しており、これらの配線構造が前記半導体チップ109に接続される構造になっている。

【0034】

前記半導体チップ109の、例えば図示を省略する電極パッド上には、例えばAuよりなるスタッドバンプ108が形成され、当該スタッドバンプ108は、例えば半田よりなる接続構造107を介して、前記パターン配線106に電気的に接続されている。前記スタッドバンプ108を用いることで、前記半導体チップ100と前記パターン配線106の電気的な接続の信頼性が良好となり、さらに当該スタッドバンプ108と前記パターン配線106の間に前記接続部107が形成されることで、さらに接続の信頼性が良好となっている。

【0035】

前記パターン配線106は、前記ビアプラグ配線105と一体的に接続されて形成されており、当該ビアプラグ配線105の、前記パターン配線106と接続される側の反対側には、例えばAu/Niのメッキ層よりなる端子接続部102が形成されている。当該端子接続部102は、その一面が前記絶縁層103より露出するように形成されており、前記端子接続部102の周囲を覆うように、ソルダーレジスト層120が形成されている。また、必要に応じて前記端子接続部102上に、ハンダバンプ121が形成されていてよい。

【0036】

また、前記半導体チップ100の、前記パターン配線106が形成されている側の反対側には、例えば前記絶縁層103上に、パターン配線117が形成されており、当該パターン配線117と当該パターン配線106とは、ビアプラグ116により接続されている。また、当該ビアプラグ116と前記パターン配線117は、例えば一体的に形成されている。

【0037】

また、前記パターン配線117上には、例えばNi/Auのメッキ層よりなる端子接続部102が形成されており、前記端子接続部102の周囲を覆うように、前記絶縁層103および当該パターン配線117上に、ソルダーレジスト層118が形成されている。

【0038】

例えば、前記絶縁層103は、いわゆるビルドアップ基板で用いられるビルドアップ樹脂を用いることが可能であり、例えばエポキシ樹脂や、またはポリイミド樹脂などの、熱硬化性の樹脂材料を用いることが可能である。

【0039】

また、前記半導体チップ109と、前記パターン配線106または前記絶縁層103の間には、樹脂材料よりなるアンダーフィル層110が形成されていると好適である。

10

20

30

40

50

## 【0040】

また、上記配線基板100において、例えば、前記ソルダーレジスト層118, 120や、または前記半田バンプ121を省略した構造とすることも可能である。

## 【0041】

本実施例による配線基板100では、前記半導体チップ109と接続可能な端子接続部が両面に設けられているため、配線基板の両面において、例えば他のデバイスや他の半導体チップ、またはマザーボードなどの接続対象と接続が可能な構造になっている。

## 【0042】

また、前記補強構造体112は、例えば、前記絶縁層103より固い樹脂材料、例えばコア基板などに用いられる有機コア材（プリプレグ材とよばれる場合も有る）や、または、Cu、Ni、Feなどの金属材料、またはこれらの合金材料またはこれらの複合材料など、様々な材料を用いることが可能である。

10

## 【0043】

また、前記補強構造体112は、例えば前記半導体チップ109と実質的に同一平面上に形成されると、前記絶縁層103の厚さを増大させること無く当該補強構造体112を埋設することが可能となり、好適である。

## 【0044】

本実施例による配線基板100は、半導体チップの仕様や接続の仕様により、様々な形状、厚さで形成することが可能であるが、その構成の具体的な厚さの一例を以下に示す。

20

## 【0045】

例えば、前記半導体チップ109の厚さD2を80μmとすると、当該半導体チップ109の上端面から前記ソルダーレジスト層118までの距離D1は20μm、当該半導体チップ109の下端面から前記パターン配線106の上端面までの距離D3は45μmである。

## 【0046】

また、前記ソルダーレジスト層118, 120の厚さd1, d5は、それぞれ30μmであり、前記ソルダーレジスト層120の上端面から前記パターン配線106の下端面までの距離d4は25μm、前記パターン配線106の厚さd3は10μm、前記パターン配線106の上端面から前記ソルダーレジスト層118の下端面までの距離d2は、145μmである。

30

## 【0047】

この場合、前記ソルダーバンプ121を除くと、配線基板の厚さは、240μmとなる。

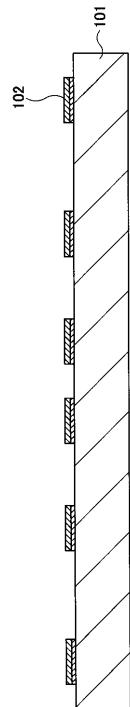

## 【0048】

また、図2Aには、図1に示した配線基板100の平面図を模式的に示す。但し、図2Aでは、前記半導体チップ109と、前記補強構造体112以外は、図示を省略している。図2に示すように、前記補強構造体112は、例えば前記半導体チップ109の周囲を囲むように、当該半導体チップ109の周囲に形成されており、このために反りを防止する効果が良好となっている。

## 【0049】

40

また、補強構造体は、上記の例に限定されず、例えば以下に示すように様々な形状を変更することも可能である。

## 【0050】

図2B～図2Cは、図2Aに示した補強構造体の変形例を示す図である。ただし図中、先に説明した部分には同一の参照符号を付し、説明を省略する。例えば、補強構造体は、図2Bに示す補強構造体112Aのように、配線基板の両端に、互いに対向するように配置したり、また、図2Cに示す補強構造体112Bのように、配線基板の角部付近に、互いに対向するように設置することも可能である。このように、補強構造体は、半導体チップの大きさや配線構造の取り回し、または配線基板の仕様に応じて、様々な変形・変更することが可能である。

50

**【0051】**

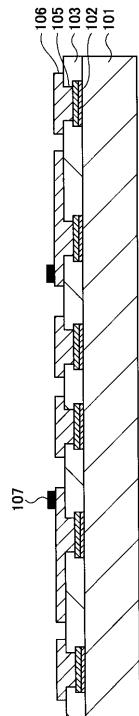

次に、本発明の一例である、図1に示した配線基板100を製造する方法の一例を、図3A～図3Oに基づき、手順を追って説明する。

**【0052】**

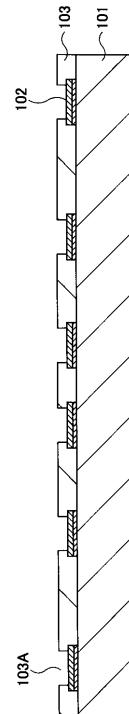

まず、図3Aに示すように、例えば厚さが200μmのCuよりなるコア基板101を用意する。

**【0053】**

次に、図3Bに示す工程において、前記コア基板101上に、リソグラフィ法によりパターニングされたレジストパターンをマスクにし、前記コア基板101を電極にして、電解メッキにより、例えばAu/Niよりなる端子接続部102を形成する。このように、コア基板101が導電性の材料で形成されていると、コア基板を電解メッキ時の電極として用いることができる。以降の工程でも電解メッキを行う場合には、必要に応じてコア基板を電極（または電解メッキ時の通電経路）として用いている。当該端子接続部102が形成された後、当該レジストパターンが剥離される。

**【0054】**

次に、図3Cに示す工程において、前記端子接続部102を覆うように、例えばエポキシ樹脂などの樹脂材料によるなる絶縁層103を、例えばラミネートにより、または塗布により形成し、さらに当該端子接続部が露出するように、たとえばレーザによるビアホール103Aの加工を行う。また、前記ビアホール103Aを形成した後は、必要に応じて、ビアホール103A内の残渣を排除し、かつ前記絶縁層103の表面の粗化をおこなう、いわゆるデスマニア処理を行うと好適である。

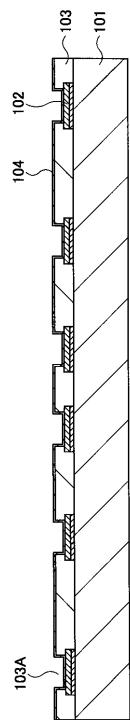

**【0055】**

次に、図3Dに示す工程において、前記絶縁層103および前記端子接続部102の表面に、例えば、Cuの無電解メッキにより、シード層102を形成する。

**【0056】**

次に、図3Eに示す工程において、リソグラフィ法によりパターニングされたレジストパターンをマスクにして、例えば、Cuの電解メッキにより、前記ビアホール103Aを埋設するようにビアプラグ105を形成するとともに、当該ビアプラグ105と接続されるパターン配線106を、当該ビアプラグ105と一体的に形成する。電解メッキを完了した後、レジストパターンを剥離する。

**【0057】**

次に、図3Fに示す工程において、前記絶縁層103上に形成された余剰な前記シード層104をエッティングして除去する。次に、前記前記絶縁層103上および前記パターン配線106上に形成された、リソグラフィ法によりパターニングされたレジストパターンをマスクにして、前記パターン配線106上に、電解メッキにより、例えば半田よりなる接続部107を形成する。

**【0058】**

この場合、前記接続部107と前記パターン配線106との間に、バリア層としてNi層を形成しておくと好適である。電解メッキが完了後、レジストパターンを剥離する。またこの場合、前記接続部107の形成方法は電解メッキに限定されず、例えば粘着性を有する粘着材を塗布した後、半田の微粉末を当該粘着材に吸着させるなどの方法をとってもよい。

**【0059】**

次に、図3Gに示す工程において、前記パターン配線106上に、半導体チップ109を設置（マウント）する。この場合、本図では図示を省略する半導体チップ109の電極パッド上には、例えばAuよりなるスタッドバンプ108が設置されており、当該スタッドバンプ108と前記接続部107が接触するように前記半導体チップ109をマウントする。ここで、半田のリフローのために加熱を行い、前記スタッドバンプ108と前記接続構造部107の電気的な接続の信頼性を向上させている。

**【0060】**

10

20

20

30

40

40

50

また、前記半導体チップ 109 と、前記配線パターン 106 または前記絶縁層 103 の間には、例えば樹脂材料を充填させて、アンダーフィル層 110 を形成すると好適である。

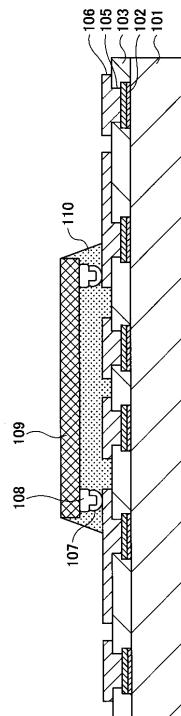

#### 【0061】

次に、図 3 H に示す工程において、例えば熱硬化性のエポキシ樹脂またはポリイミド樹脂よりなる絶縁層 111 を、前記絶縁層 103 、前記パターン配線 106 、および前記半導体チップ 109 を覆うように、ラミネートにより形成する。

#### 【0062】

前記絶縁層 111 は、例えばこの後の工程で設置される補強構造体が、前記パターン配線 106 に接触することで当該補強構造体または前記パターン配線 106 が損傷することを防止している。この場合、前記絶縁層 111 は、例えば 25  $\mu\text{m}$  程度の膜厚で形成される。

10

#### 【0063】

また、前記絶縁層 111 は、特に前記絶縁層 103 と同じ材料により形成された場合には、前記絶縁層 103 と渾然一体となるため、以降の図では前記絶縁層 111 と前記絶縁層 103 は一体の絶縁層であるものとし、当該絶縁層 111 を含めて絶縁層 103 として表示する。

#### 【0064】

次に、図 3 I に示す工程において、例えば、厚さが 100  $\mu\text{m}$  であって、有機コア材料（プリプレグ材料）よりなる補強構造体 112 を、前記絶縁層 103 を介して前記パターン配線 106 上に設置（マウント）する。この場合、前記補強構造体 112 は、例えば Cu や Ni などの金属材料よりなるものを用いることも可能であり、また、例えばメッキ法で形成することも可能である。

20

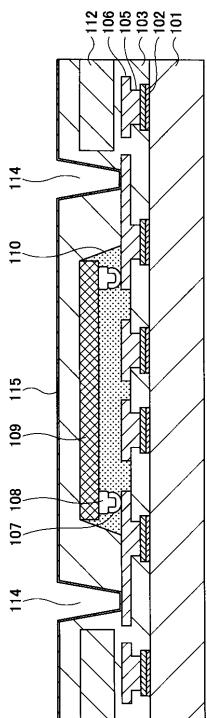

#### 【0065】

次に、図 3 J に示す工程において、前記補強構造体 112 と、前記半導体チップ 109 を覆うように、例えば熱硬化性の、エポキシ樹脂またはポリイミド樹脂よりなる絶縁層 113 を、ラミネートにより形成する。

#### 【0066】

また、前記絶縁層 113 は、特に前記絶縁層 103 と同じ材料により形成された場合には、前記絶縁層 103 と渾然一体となるため、以降の図では前記絶縁層 113 と前記絶縁層 103 は一体の絶縁層であるものとし、当該絶縁層 113 を含めて絶縁層 103 として表示する。

30

#### 【0067】

次に、図 3 K に示す工程において、前記絶縁層 103 のキュア工程、すなわち当該絶縁層 103 を加熱して熱硬化させる工程を行う。この場合、前記絶縁層 103 には前記補強構造体 112 が埋設されているため、温度変化による前記絶縁層 103 の反りの量が抑制され、良好な平面度を保持することができる。

#### 【0068】

次に、図 3 L に示す工程において、例えばレーザにより、前記絶縁層 103 に、前記パターン配線 106 にまで到達するビアホール 114 を形成し、さらに必要に応じてデスマニア処理を行う。次に、前記ビアホール 114 の内壁面を含む前記絶縁層 103 上、および露出した前記パターン配線 106 上に、例えば、Cu の無電解メッキにより、シード層 115 を形成する。

40

#### 【0069】

次に、図 3 M に示す工程において、リソグラフィ法によりパターンングされたレジストパターンをマスクにして、例えば、Cu の電解メッキにより、前記ビアホール 114 を埋設するようにビアプラグ 116 を形成するとともに、当該ビアプラグ 116 と接続されるパターン配線 117 を、当該ビアプラグ 116 と一体的に形成する。電解メッキを完了した後、レジストパターンを剥離し、さらに前記絶縁層 103 上に形成された余剰な前記シード層 115 を、エッティングして除去する。

50

## 【0070】

次に、図3Nに示す工程において、前記パターン配線117の一部が露出するように、当該パターン配線117および前記絶縁層103上にソルダーレジスト層118を形成し、前記パターン配線117が露出した部分に、例えばN<sub>i</sub> / A<sub>u</sub>よりなる端子接続部119を、無電解メッキにより、形成する。

## 【0071】

次に、図3Oに示す工程において、例えばC<sub>u</sub>よりなる前記コア基板101を、例えばエッティングにより除去する。次に、図1に示すように、ソルダーレジスト層120を形成し、必要に応じて半田バンプ121を形成し、配線基板100を形成することができる。

## 【0072】

本実施例による製造方法によれば、図3Iに示した工程において前記補強構造体112が設置され、さらに図3Jに示す工程において、前記補強構造体112が埋設された前記絶縁層103のキュアが実施されている。そのため、以降の工程において、前記絶縁層103または配線基板全体の反りの量が抑制される効果を奏する。特に、温度上層、温度降下によるストレスの変化やメッキ、デスマニア処理、ラミネート処理の場合などの応力の変化に対して、従来の方法に比べて反りの量が抑制され、平面度が高く、また信頼性にすぐれた配線基板を形成することが可能となる。

## 【0073】

さらに、本実施例の場合、所定の製造工程中において、例えばC<sub>u</sub>によるなりコア基板101上に前記配線基板100を形成しているため、製造工程における反りの量が抑制され、さらに当該コア基板101は所定の製造工程終了後に除去されるために、配線基板を薄型化することが可能となっている。

## 【0074】

また、本発明による配線基板は、上記の場合に限定されず、例えば配線構造、または補強構造体などを様々に変形・変更することも可能である。

## 【0075】

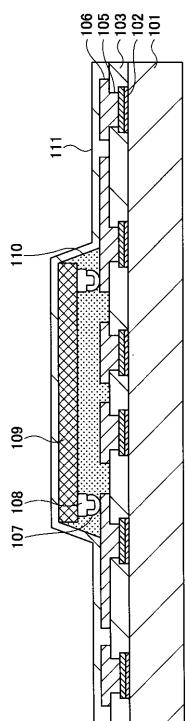

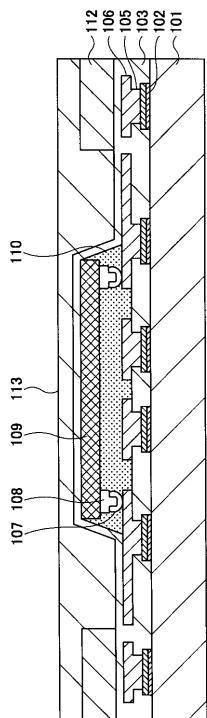

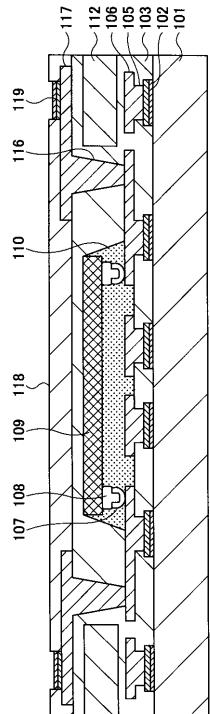

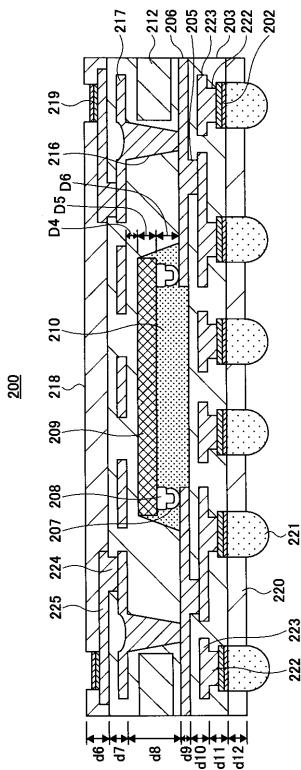

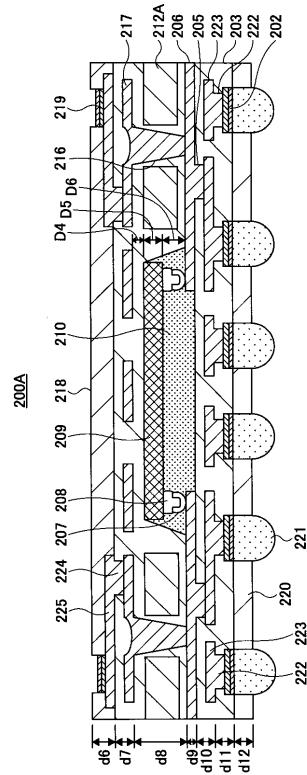

例えば図4に、上記配線基板100の変形例である、配線基板200を、模式的に示す。

## 【0076】

図4を参照するに、本図に示す配線基板200において、絶縁層203、端子接続部202、219、半導体チップ209、スタッドバンプ208、接続部207、アンダーフィル層210、ソルダーレジスト層218、220、および前記補強構造体212は、図1に示した前記配線基板100の、それぞれ、絶縁層103、端子接続部102、119、半導体チップ109、スタッドバンプ108、接続部107、アンダーフィル層110、ソルダーレジスト層118、120、および前記補強構造体112に対応し、同様の構造を有している。

## 【0077】

前記配線基板200の場合、前記半導体チップ209に接続される配線構造の層の数が前記配線基板100に比べて増えている。例えば、前記配線基板100の場合、前記半導体チップ109の下側で1層、上側で1層、あわせて2層配線であったものが、前記配線基板200の場合、前記半導体チップ209の下側で2層、上側で2層、あわせて4層配線となっている。

## 【0078】

前記配線基板200の場合、前記半導体チップが接続されるパターン配線206に対して、ビアプラグ205、216がそれぞれ接続されている。前記ビアプラグ205は、パターン配線223に、さらに当該パターン配線223は、前記端子接続部202が形成されたビアプラグ222に接続されている。一方、前記ビアプラグ216には、パターン配線217が接続され、当該パターン配線217は、ビアプラグ224を介して、前記端子接続部219が形成されたパターン配線225に接続されている。

## 【0079】

10

20

20

30

40

40

50

このように、配線の層の数は、必要に応じて変更することが可能である。

【0080】

前記配線基板200は、半導体チップの仕様や接続の仕様により、様々な形状、厚さで形成することが可能であるが、その構成の具体的な厚さの一例を以下に示す。

【0081】

例えば、前記半導体チップ209の厚さD5を80μmとすると、当該半導体チップ209の上端面から前記パターン配線217までの距離D4は20μm、当該半導体チップ209の下端面から前記パターン配線206の上端面までの距離D6は45μmである。

【0082】

また、前記ソルダーレジスト層218、220の厚さd6、d12は、それぞれ30μmであり、前記ソルダーレジスト層220の上端面から前記パターン配線223の下端面までの距離d11は25μm、前記パターン配線223の下端面から前記パターン配線206の下端面までの距離d10は25μm、前記パターン配線206の厚さd9は10μm、前記パターン配線206の上端面から前記パターン配線217の下端面までの距離d8は145μm、前記パターン配線217の下端面から前記ソルダーレジスト層218の下端面までの距離d7は、25μmである。

【0083】

この場合、前記配線基板200の厚さは、ソルダーバンプを除くと290μmである。

【0084】

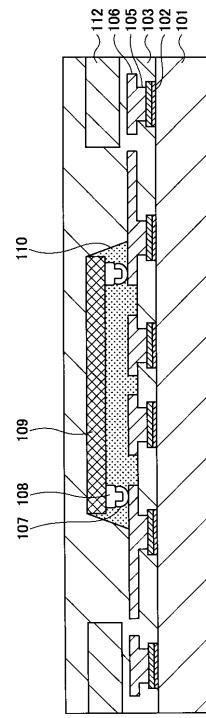

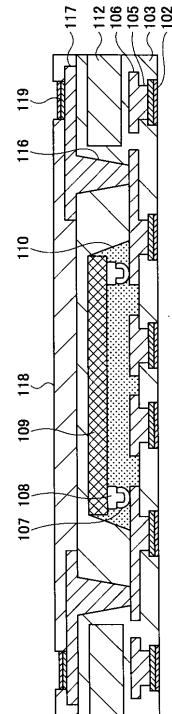

また、図5は、上記配線基板100の別の変形例である、配線基板200Aを、模式的に示した図面である。ただし図中、先に説明した部分には同一の参照符号を付し、説明を省略する。

【0085】

図5を参照するに、本図に示す配線基板200Aでは、前記補強構造体212に相当する補強構造体212Aの面積が、当該補強構造体212より大きく、前記半導体チップ209の近傍まで形成されている。

【0086】

この場合、例えば前記ビアプラグ216を形成するための穴部が、前記補強構造体212に形成されている。

【0087】

このように、補強構造体と配線構造は、必要に応じて様々な変形・変更が可能であることは明らかである。

【0088】

以上、本発明を好ましい実施例について説明したが、本発明は上記の特定の実施例に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【産業上の利用可能性】

【0089】

半導体チップを内蔵した配線基板の薄型化を実現し、かつ当該配線基板の反りを抑制することが可能となる。

【図面の簡単な説明】

【0090】

【図1】実施例1による配線基板を模式的に示した断面図である。

【図2A】実施例1による補強構造体の設置方法を示す図(その1)である。

【図2B】実施例1による補強構造体の設置方法を示す図(その2)である。

【図2C】実施例1による補強構造体の設置方法を示す図(その3)である。

【図3A】実施例1による配線基板の製造方法を示す図(その1)である。

【図3B】実施例1による配線基板の製造方法を示す図(その2)である。

【図3C】実施例1による配線基板の製造方法を示す図(その3)である。

【図3D】実施例1による配線基板の製造方法を示す図(その4)である。

10

20

30

40

50

【図3E】実施例1による配線基板の製造方法を示す図（その5）である。

【図3F】実施例1による配線基板の製造方法を示す図（その6）である。

【図3G】実施例1による配線基板の製造方法を示す図（その7）である。

【図3H】実施例1による配線基板の製造方法を示す図（その8）である。

【図3I】実施例1による配線基板の製造方法を示す図（その9）である。

【図3J】実施例1による配線基板の製造方法を示す図（その10）である。

【図3K】実施例1による配線基板の製造方法を示す図（その11）である。

【図3L】実施例1による配線基板の製造方法を示す図（その12）である。

【図3M】実施例1による配線基板の製造方法を示す図（その13）である。

【図3N】実施例1による配線基板の製造方法を示す図（その14）である。

【図3O】実施例1による配線基板の製造方法を示す図（その15）である。

10

【図4】図1に示した配線基板の変形例（その1）である。

【図5】図1に示した配線基板の変形例（その2）である。

【符号の説明】

【0091】

100, 200, 200A 配線基板

101 コア基板

102, 119, 202, 219 端子接続部

103, 111, 113, 203 絶縁層

104, 115 シード層

20

105, 116, 205, 216, 217, 222 ピアプラグ

106, 117, 206, 217, 223, 225 パターン配線

107, 207 接続部

108, 208 スタッドバンプ

109, 209 半導体チップ

110, 210 アンダーフィル

114 ピアホール

118, 120, 218, 220 ソルダーレジスト層

121, 221 ハンダバンプ

【図1】

実施例1による配線基板を模式的に示した断面図

【図3B】

実施例1による配線基板の製造方法を示す図(その2)

【図3C】

実施例1による配線基板の製造方法を示す図(その3)

【図3D】

実施例1による配線基板の製造方法を示す図(その4)

【図3E】

実施例1による配線基板の製造方法を示す図(その5)

【図3F】

実施例1による配線基板の製造方法を示す図(その6)

【図3G】

実施例1による配線基板の製造方法を示す図(その7)

【図3H】

実施例1による配線基板の製造方法を示す図(その8)

【図3I】

実施例1による配線基板の製造方法を示す図(その9)

【図3J】

実施例1による配線基板の製造方法を示す図(その10)

【図3K】

実施例1による配線基板の製造方法を示す図(その11)

【図3L】

実施例1による配線基板の製造方法を示す図(その12)

【図3M】

実施例1による配線基板の製造方法を示す図(その13)

### 【図3N】

## 実施例1による配線基板の製造方法を示す図(その14)

【図30】

### 実施例1による配線基板の製造方法を示す図(その15)

【 図 4 】

図1に示した配線基板の変形例(その1)

【 图 5 】

図1に示した配線基板の変形例(その2)

---

フロントページの続き

(72)発明者 小山 鉄也

長野県長野市小島田町80番地 新光電気工業株式会社内

審査官 黒石 孝志

(56)参考文献 特開2003-347741(JP,A)

特開2004-335641(JP,A)

特開2003-347459(JP,A)

実開平5-66973(JP,U)

(58)調査した分野(Int.Cl., DB名)

H05K 3/46

H01L 23/12

H05K 1/05

H05K 3/44