(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 698 35 100 T2 2007.02.01

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 031 074 B1

(21) Deutsches Aktenzeichen: 698 35 100.2

(86) PCT-Aktenzeichen: PCT/US98/22030

(96) Europäisches Aktenzeichen: 98 953 695.8

(87) PCT-Veröffentlichungs-Nr.: WO 1999/026132

(86) PCT-Anmeldetag: 19.10.1998

(87) Veröffentlichungstag

der PCT-Anmeldung: 27.05.1999

(97) Erstveröffentlichung durch das EPA: 30.08.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 28.06.2006

(47) Veröffentlichungstag im Patentblatt: 01.02.2007

(51) Int Cl.<sup>8</sup>: G06F 9/38 (2006.01)

G06F 7/50 (2006.01)

(30) Unionspriorität:

65878 P 17.11.1997 US

115123 14.07.1998 US

(74) Vertreter:

Grünecker, Kinkeldey, Stockmair &

Schwanhäusser, 80538 München

(73) Patentinhaber:

Advanced Micro Devices, Inc., Sunnyvale, Calif.,

US

(84) Benannte Vertragsstaaten:

DE, GB

(72) Erfinder:

WITT, B., David, Austin, TX 78759, US

(54) Bezeichnung: PROZESSOR KONFIGURIERT UM VORAUSSCHAUENDE RESULTATE VON ZUSAMMENGE-

FASSTEN ÜBERTRAGUNGS-, VERGLEICHS- UND EINFACHEN ARITHMETISCHEN BEFEHLEN ZU PRODUZIE-

REN

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

### Hintergrund der Erfindung

#### 1. Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung betrifft das Gebiet der Prozessoren und betrifft insbesondere die parallele Bearbeitung von Befehlen in Prozessoren.

#### 2. Beschreibung des Stands der Technik

**[0002]** In superskalaren Prozessoren wird versucht, ein hohes Leistungsvermögen zu erreichen, indem mehrere Befehle pro Taktzyklus ausgegeben und ausgeführt werden, und indem bei der kleinsten möglichen Taktzykluszeit, die mit dem Aufbau verträglich ist, gearbeitet wird. In dem Maße, wie es gelingt, in einem bestimmten Prozessor mehrere Befehle pro Taktzyklus auszugeben und/oder auszuführen, kann auch ein hohes Leistungsvermögen erreicht werden. Um die mittlere Anzahl der Befehle, die pro Taktzyklus ausgegeben werden, zu erhöhen, haben Entwurfsingenieure superskalare Prozessoren entworfen, die größere Ausgaberaten anwenden. Ein superskalarer Prozessor mit „breiterer Ausgabe“ ist in der Lage, eine größere maximale Anzahl an Befehlen pro Taktzyklus auszugeben (oder zu verteilen), als ein superskalarer Prozessor mit „schmaler Ausgabe“ dazu in der Lage ist. Während der Taktzyklen, in denen die Anzahl der ausgegebenen Befehle größer ist als von einem Prozessor mit schmaler Ausgabe verarbeitbar ist, kann der Prozessor mit breiterer Ausgabe mehr Befehle ausgeben, wodurch eine höhere mittlere Anzahl an ausgegebenen Befehlen pro Taktzyklus erreicht wird.

**[0003]** Jedoch erfordern höhere Ausgaberaten im Allgemeinen zur Ausführung einen größeren Anteil an Hardware in dem Prozessor. Wenn eine ausreichende Ausführungshardware nicht vorgesehen ist, kann der Befehlsdurchsatz des Prozessors darunter leiden, selbst wenn der Prozessor in der Lage ist, eine große Anzahl an Befehlen gleichzeitig auszugeben. Die Ausführungshardware kann einen wesentlichen Anteil der Halbleitersubstratfläche einnehmen, wodurch die Gesamtchipgröße des Prozessors und damit dessen Kosten ansteigen.

**[0004]** Ferner sind viele Befehle relativ einfache Befehle, die durch eine einfache Ausführungshardware gehandhabt werden könnten. Beispielsweise sind Verschiebungs- bzw. „Move“-Befehle, die lediglich Registeroperanden spezifizieren (d. h. eine Verschiebung von einem Quellenregister zu einem Zielregister) einfache Befehle, die im Wesentlichen keine Hardware zum Ausführen erfordern. Verschiebebefehle mit einem Speicheroperanden und einem Registeroperanden beinhalten eine Adressenerzeugung, erfordern jedoch relativ wenig zusätzliche Hardware. Des Weiteren sind Additionsbefehle (d. h. Addieren/Subtrahieren/inkrementieren/Dekrementieren) mit Registeroperanden relativ einfache Befehle. Die einfacheren Befehle können relativ häufig in üblichen Codierungssequenzen auftreten. Jedoch muss die Ausführungshardware in der Lage sein, auch die komplexeren Befehle auszuführen. Es wurden superskalare Prozessoren vorgeschlagen, die eine weniger kostenintensive Ausführungshardware besitzen, indem sowohl eine komplexe als auch eine einfache Einheit vorgesehen wird und indem die Ausgabe von Befehlen zu den Ausführungseinheiten so gesteuert wird, dass die einfachere Ausführungseinheit nur einfache Befehle erhält, während die komplexeren Einheiten einfachere Befehle oder komplexe Befehle erhalten. Obwohl eine derartige Strategie die von der Ausführungshardware eingenommene Fläche verringern kann, wird die Ausgabelogik komplexer. Die komplexe Logik kann eine größere Fläche einnehmen oder kann eine Beschränkung der Taktzykluszeit hervorrufen. Folglich sind effizientere Verfahren zum Handhaben der Mischung aus einfachen und komplexen Befehlen wünschenswert.

**[0005]** Um höhere Taktfrequenzen (d. h. kürzere Taktzykluszeiten) zu unterstützen, werden in superskalaren Prozessoren längere Pipelines (d. h. Pipelines mit mehr Stufen) sowie breitere Ausgaberaten eingesetzt. Während längere Pipelines das Erreichen höherer Taktfrequenzen zulassen, führen diese längeren Pipelines auch zu weiteren Entwurfsherausforderungen. Insbesondere wenn eine größere Anzahl an Befehlen abgeholt und in die Pipeline eingespeist wird, bevor vorhergehende Anweisungen in ihrer Ausführung abgeschlossen sind, ist eine zusätzliche Weiterleitungshardware erforderlich, um die parallele Ausführung zu unterstützen. Beispielsweise können mehrere Anweisungen über die Operandenabholstufe hinaus weiterschreiten, bevor die vorhergehenden Befehle ausgeführt sind. Wenn diese Befehle von den vorhergehenden Befehlen abhängig sind, sind die Operanden für diese Befehle unter Umständen nicht verfügbar, wenn die Befehle die Operandenabholstufe erreichen. Diesen Befehlen kann das Weiterschreiten zu nachfolgenden Pipeline-Stufen erlaubt werden, wenn eine Weiterleitungshardware vorgesehen ist, um die Operanden zu den Befehlen zu leiten, wenn diese während der Ausführung in der Pipeline weiterschreiten. Jedoch ist die Weiterleitungshardware im

Hinblick auf Chipfläche und Komplexität aufwendig. Eine effizientere Lösung zur Bereitstellung der Operanden für abhängige Befehle ist daher vorteilhaft.

**[0006]** Im hierin verwendeten Sinne bezeichnet der Begriff „Abhängigkeit“ die Beziehung zwischen einem ersten Befehl und einem nachfolgenden zweiten Befehl, wobei der zweite Befehl das Ausführen des ersten Befehls vor dem Ausführen des zweiten Befehls erfordert. Beispielsweise kann der zweite Befehl einen Quellenoperanden aufweisen, der durch Ausführen des ersten Befehls erzeugt wird. Im Allgemeinen ist ein Operand ein Wert, mit dem während des Ausführens eines Befehls operiert wird. Die Operanden für einen speziellen Befehl werden mittels Operandenspezifizierungen aufgefunden, die in den Befehl codiert sind. Beispielsweise können gewisse Operanden in Registern gespeichert sein, die in dem Prozessor verwendet sind. Eine Registeroperandenspezifizierung, die in dem Befehl codiert ist, wählt das spezielle Register aus, in dem der Operand gespeichert ist. Die Registeroperandenspezifizierung kann auch als eine Registeradresse oder eine Registernummer bezeichnet werden. Andererseits können andere Befehle einen Speicheroperanden spezifizieren, der in einer Speicherstelle innerhalb eines Hauptspeichers abgelegt ist, mit dem der Prozessor gekoppelt ist. Die Speicheradresse wird ebenfalls über Operandenspezifizierungen spezifiziert. Beispielsweise kann der Befehl eine Verschiebung beinhalten, die die Speicherstelle kennzeichnet, in der der Speicheroperand abgelegt ist. Andere Befehle können Adressenoperandenspezifizierungen enthalten, die Registeroperanden spezifizieren, die zur Bildung der Speicheradresse verwendet werden. Ein Operand kann ein Quellenoperand sein, wenn der Operand ein Eingabewert für den Befehl ist. Ein Operand kann ein Zieloperand sein, wenn der Operand das Ergebnis des Befehls ist. Die Zieloperandenspezifizierung spezifiziert die Speicherstelle, in der das Ergebnis des gerade ausgeführten Befehls abzulegen ist.

**[0007]** WO 93/20505 beschreibt eine Befehlsdisponierung bzw. eine Ablauforganisation in einem superskalaren RISC-Prozessor, der eine Ausführung außer der Reihenfolge ermöglicht. Es wird darin eine Registerumbenennungsschaltung offenbart, die ein Teil der Disponierlogik ist und die die parallele Abarbeitung von Befehlen beschleunigt, indem Datenabhängigkeiten in einer Abhängigkeitsprüfeinheit so aufgelöst werden, dass das Ergebnis eines Befehls in einem Temporärpufferbefehlsfenster gespeichert wird, ohne dass dieses in die Registerdatei übertragen wird. Das Weiterleiten des Ergebnisses zu einem zweiten Befehl unter Anwendung des Ergebnisses als einen Eingangsoperanden wird somit möglich. Jedoch tritt diese Bearbeitung in der Befehlausführungsstufe der Pipeline auf, nachdem Befehle ausgegeben wurden sind.

**[0008]** US-A-5,675,758 offenbart einen leistungsfähigen Prozessor, in welchem bestehende Ausführungseinheiten durch das Hinzufügen einer ergänzenden Ganzzahlausführungseinheit erweitert sind, die als Add/Move-Einheit (AMU) bezeichnet wird, die ausgewählte Additionen und Verschiebungen parallel und in Bezug auf die anderen Ausführungseinheiten außerhalb der Reihe ausführt. Die AMU entfernt Datenabhängigkeiten und vergrößert damit die verfügbare Befehlsebenenparallelität.

**[0009]** Die obigen dargestellten Probleme werden zum großen Teil durch einen Prozessor gemäß der vorliegenden Erfindung gelöst, wie er in Anspruch 1 der begleitenden Patentansprüche definiert ist. In einer Ausführungsform umfasst der Prozessor eine vorausschauende Adressen/Ergebnis-Berechnungseinheit, die ausgebildet ist, Operandeninformationen zu empfangen (entweder den Operanden oder eine Marke, die den Befehl kennzeichnet, der den Operandenwert erzeugen wird), die dem entsprechenden Quellenoperanden eines oder mehrerer Befehle entspricht. Wenn die Operanden verfügbar sind, erzeugt die vorausschauende Adressen/Ergebnis-Berechnungseinheit entweder eine Vorausschauadresse für einen Speicheroperanden des Befehls oder ein Vorausschauergebnis, das einer funktionellen Befehlsoperation des Befehls entspricht. Die Vorausschauadresse kann einer Lade/Schreib- bzw. Lade/Speichereinheit für eine frühe Initiierung eines Speichervorgangs gemäß dem Befehl zugeführt werden. Das vorausschauende Ergebnis kann einer spekulativen Operandenquelle (beispielsweise einer Zukunftsdatei) für die Aktualisierung zugeführt werden. Vorteilhafterweise wird ein vorausschauender Zustand für ein Register früh in der Pipeline vorgesehen. Nachfolgende Befehle erhalten den vorausschauenden Zustand und benutzen den vorausschauenden Zustand, um in einer frühen Phase einen zusätzlichen vorausschauenden Zustand zu erzeugen. Andererseits erhalten die nachfolgenden Befehle den vorausschauenden Zustand und sind somit für die Abarbeitung vorbereitet, wenn diese in ein Befehlsfenster ausgegeben werden (im Gegensatz zum Warten auf das Befehlsfenster zur Ausführung des vorhergehenden Befehls).

**[0010]** Der Prozessor kann eine effizientere Weiterleitung auf vielfältige Weisen erreichen. Beispielsweise können viele Befehle vorausschauende Ergebnisse beim Abholen von Operanden erhalten und müssen daher nicht auf die nachfolgende Weiterleitung von Operanden warten. Da ferner einige Befehlsoperanden in der vorausschauenden Adressen/Ergebnis-Berechnungseinheit abgeschlossen werden können, sind weniger Funktionseinheiten erforderlich, um eine breite Ausgaberate zu unterstützen. Folglich können weniger weiterleiten-

de Busse eingerichtet werden (entsprechend der geringeren Anzahl an Funktionseinheiten). Des weiteren kann das Leistungsvermögen gesteigert werden, indem vorausschauende Operanden für Befehle vor den Befehlen bereitgestellt werden, die die vorausschauenden Operanden erzeugen, die die Ausführungsstufe der Prozessорpipeline erreichen.

**[0011]** In einer Ausführungsform umfasst der Prozessor ferner eine Operandenzusammenfasseinheit, die ausgebildet ist, die vorausschauenden Ergebnisse in nachfolgende gleichzeitig decodierte Befehle (reiheninterne Abhängigkeiten) zusammenzufassen. Des weiteren ist die Operandenzusammenfasseinheit ausgebildet, einen Vergleichsbefehl in einen nachfolgenden Verzweigungsbefehl einzubinden, der von dem Ergebnis des Vergleichs abhängt. Vorteilhafterweise können die Vergleichs/Verzweigungskombinationen eine einzelne Funktionseinheit besitzen.

**[0012]** Allgemein gesagt, betrifft die vorliegende Erfindung einen Prozessor mit einer reiheninternen Abhängigkeitsprüfeinheit, einer Vorausschauberechnungseinheit, einer Operandenzusammenfass- bzw. zusammenführeinheit und einem oder mehreren Befehlsfenstern. Die reiheninterne Abhängigkeitsprüfeinheit, die angeschlossen ist, mehrere Operandenspezifizierungen entsprechend einer Linie bzw. Reihe aus Befehlen zu empfangen, ist ausgebildet, Abhängigkeiten zwischen Befehlen innerhalb der Reihe aus Befehlen zu bestimmen, indem die mehreren Operandenspezifizierungen verglichen werden. Die Vorausschauberechnungseinheit, die angeschlossen ist, einen oder mehrere Operanden, die durch die mehreren Operandenspezifizierungen gekennzeichnet sind, zu empfangen, ist ausgebildet, ein vorausschauendes Ergebnis entsprechend einem ersten Befehl innerhalb der Reihe aus Befehlen zu berechnen, wenn jeder Operand, der von dem ersten Befehl zur Erzeugung des vorausschauenden Ergebnisse verwendet wird, innerhalb des einen oder der mehreren Operanden enthalten ist. Die Operandenzusammenfasseinheit, die mit der Vorausschauberechnungseinheit und der reiheninternen Abhängigkeitsprüfeinheit verbunden ist, ist ausgebildet, das vorausschauende Ergebnis als einen Operanden eines zweiten Befehls aus der Reihe aus Befehlen bereitzustellen. Die Operandenzusammenführeinheit stellt das vorausschauende Ergebnis als den Operanden in Reaktion bereit auf: (i) eine Angabe aus der Vorausschauberechnungseinheit, dass das vorausschauende Ergebnis gültig ist, (ii) eine Angabe aus der reiheninternen Abhängigkeitsprüfeinheit, dass der zweite Befehl von dem ersten Befehl abhängig ist. Die Befehlsfenster, die mit der Operandenzusammenführeinheit gekoppelt sind, sind ausgebildet, Befehle zu speichern, bis entsprechende Operanden bereitgestellt werden und nachfolgend die Befehle zum Ausführen auszuwählen. Die Operandenzusammenführeinheit ist ausgebildet, den Befehlsfenstern anzuzeigen, die Ausführung mindestens einer ersten Befehlsoperation des ersten Befehls, der durch das vorausschauende Ergebnis repräsentiert ist, zu verhindern, wenn das vorausschauende Ergebnis gültig ist.

**[0013]** Die vorliegende Erfindung betrifft ferner einen Prozessor mit einer Operandenzusammenführeinheit und einem oder mehreren Befehlsfenstern. Die Operandenzusammenführeinheit ist angeschlossen, mehrere Operanden zu empfangen, die einer Reihe bzw. Linie aus Befehlen entsprechen. Die Operandenzusammenführeinheit ist ausgebildet, einen oder mehrere der mehreren Operanden entsprechend einem ersten Befehl in der Linie aus Befehlen als Operanden eines zweiten Befehls aus der Linie aus Befehlen bereitzustellen in Reaktion auf: (i) dass der erste Befehl ein Vergleichsbefehl ist, (ii) der zweite Befehl ein bedingter Verzweigungsbefehl ist, und (iii) der zweite Befehl auf den ersten Befehl folgt. Die Befehlsfenster, die mit der Operandenzusammenführeinheit verbunden sind, sind ausgebildet, Befehle zu speichern, bis entsprechende Operanden bereitgestellt werden und nachfolgend die Befehle für das Ausführen auszuwählen. Die Operandenzusammenführeinheit ist ausgebildet, den Befehlsfenstern anzuzeigen, den Empfang eines ersten Befehls zu verhindern, wenn: (i) der erste Befehl ein Vergleichsbefehl ist, (ii) der zweite Befehl ein bedingter Verzweigungsbefehl ist, und (iii) der zweite Befehl auf den ersten Befehl folgt.

**[0014]** Des weiteren betrifft die vorliegende Erfindung ein Verfahren zum Ausführen einer Reihe aus Befehlen in einem Prozessor. Die Reihe aus Befehlen ist decodiert, um mehrere Operandenspezifizierungen zu erkennen. Zieloperandenspezifizierungen jedes Befehls innerhalb der Reihe von Befehlen werden mit Quellenoperandenspezifizierungen jedes nachfolgenden Befehls aus der Reihe der Befehle verglichen, um reiheninterne Abhängigkeiten zu erkennen. Eine spekulative Operandenquelle wird ausgelesen, um QuellenOperanden zu erkennen, die durch Quellenoperandenspezifizierungen gekennzeichnet sind. Es wird ein vorausschauendes Ergebnis für einen ersten Befehl aus der Reihe berechnet, wenn die QuellenOperanden in der spekulativen Operandenquelle verfügbar sind. Einem Befehlsfenster, das ausgebildet ist, den ersten Befehl aufzunehmen, wird angezeigt, die Ausführung mindestens einer ersten Befehlsoperation des ersten Befehls zu verhindern, der das vorausschauende Ergebnis erzeugt, wenn das vorausschauende Ergebnis erfolgreich berechnet ist. Das vorausschauende Ergebnis wird einem zweiten Befehl aus der Reihe aus Befehlen bereitgestellt, wenn der Vergleich eine Abhängigkeit des zweiten Befehls von dem ersten Befehl angibt. Das Bereitstellen wird vor dem Speichern des zweiten Befehls in dem Befehlsfenster ausgeführt.

**[0015]** Die vorliegende Erfindung betrifft ferner ein Computersystem mit einem Prozessor und einer Eingabe/Ausgabe-(I/O) Einrichtung. Der Prozessor umfasst eine Ausrichteinheit, die ausgebildet ist, eine Linie bzw. Reihe aus Befehlen auf mehrere Ausgabepositionen auszurichten, eine spekulative Operandenquellen, die ausgebildet ist, spekulative Operanden zu speichern, ein Befehlsfenster, das ausgebildet ist, Befehle zu speichern, bis Operanden für diese Befehle bereitgestellt sind und eine Vorausschau/Zusammenführeinheit. Die Vorausschau/Zusammenführeinheit ist mit der spekulativen Operandenquelle, dem Befehlsfenster und der Ausrichteinheit verbunden und ist ausgebildet, Operanden von der spekulativen Operandenquelle in Reaktion darauf, dass die Reihe aus Befehlen von der Ausrichteinheit empfangen wird, auszulesen. Die Vorausschau/Zusammenführeinheit ist ausgebildet, ein vorausschauendes Ergebnis entsprechend einem ersten Befehl innerhalb der Befehlsreihe in Reaktion auf die Operanden zu erzeugen. Die Vorausschau/Zusammenführeinheit ist ferner ausgebildet, die spekulative Operandenquelle mit dem vorausschauenden Ergebnis zu aktualisieren und ist ferner ausgebildet, das vorausschauende Ergebnis an einen zweiten Befehl innerhalb der Befehlsreihe weiterzuleiten, der vom dem ersten Befehl abhängig ist. Die Vorausschau/Zusammenführeinheit ist ausgebildet, dem Befehlsfenster anzuzeigen, das Ausführen mindestens einer ersten Befehlsoperation des ersten Befehls zu unterdrücken, der das vorausschauende Ergebnis erzeugt. Die I/O-Einrichtung, die mit dem Prozessor verbunden ist, ist ausgebildet, eine Kommunikation zwischen dem Computersystem und einem weiteren Computersystem, mit welchem die I/O-Einrichtung verbunden ist, herzustellen.

#### Kurze Beschreibung der Zeichnungen

**[0016]** Weitere Aufgaben und Vorteile der Erfindung gehen aus dem Studium der folgenden detaillierten Beschreibung und durch Bezugnahme zu den begleitenden Zeichnungen hervor, in denen:

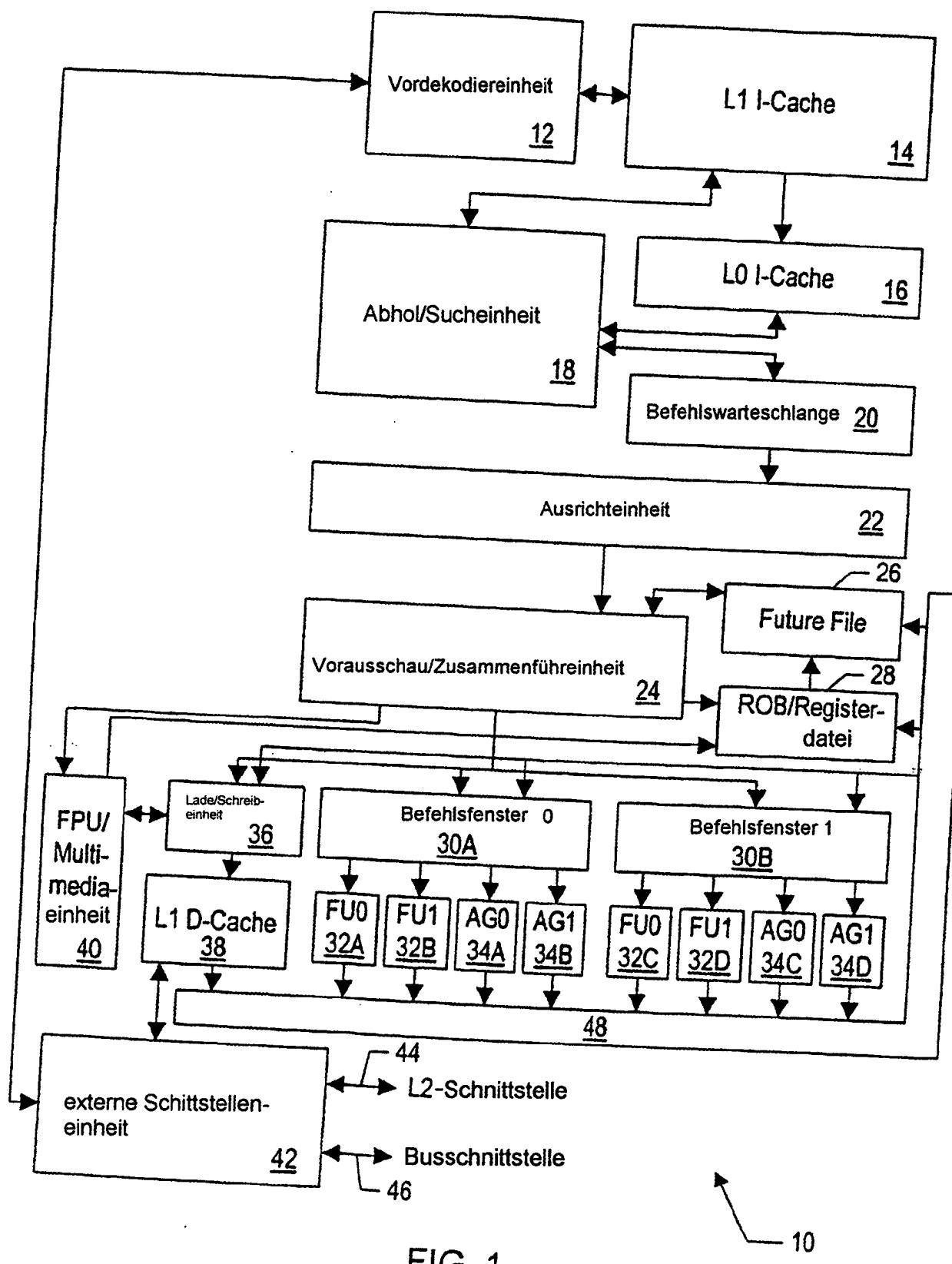

**[0017]** [Fig. 1](#) eine Blockansicht einer Ausführungsform eines Prozessors ist;

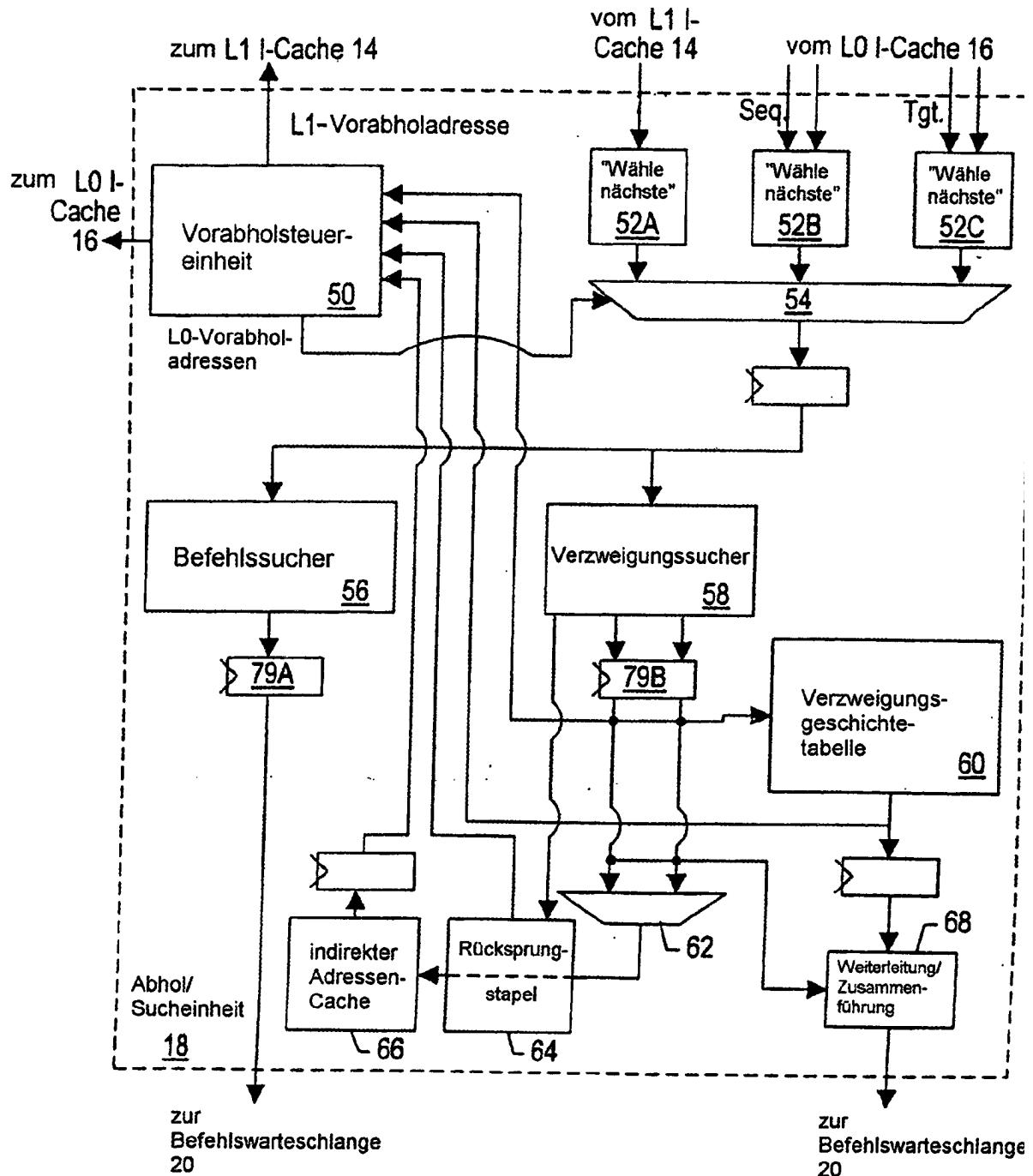

**[0018]** [Fig. 2](#) eine Blockansicht einer Ausführungsform einer Abhol/Such- bzw. Abtasteinheit ist, die in [Fig. 1](#) gezeigt ist;

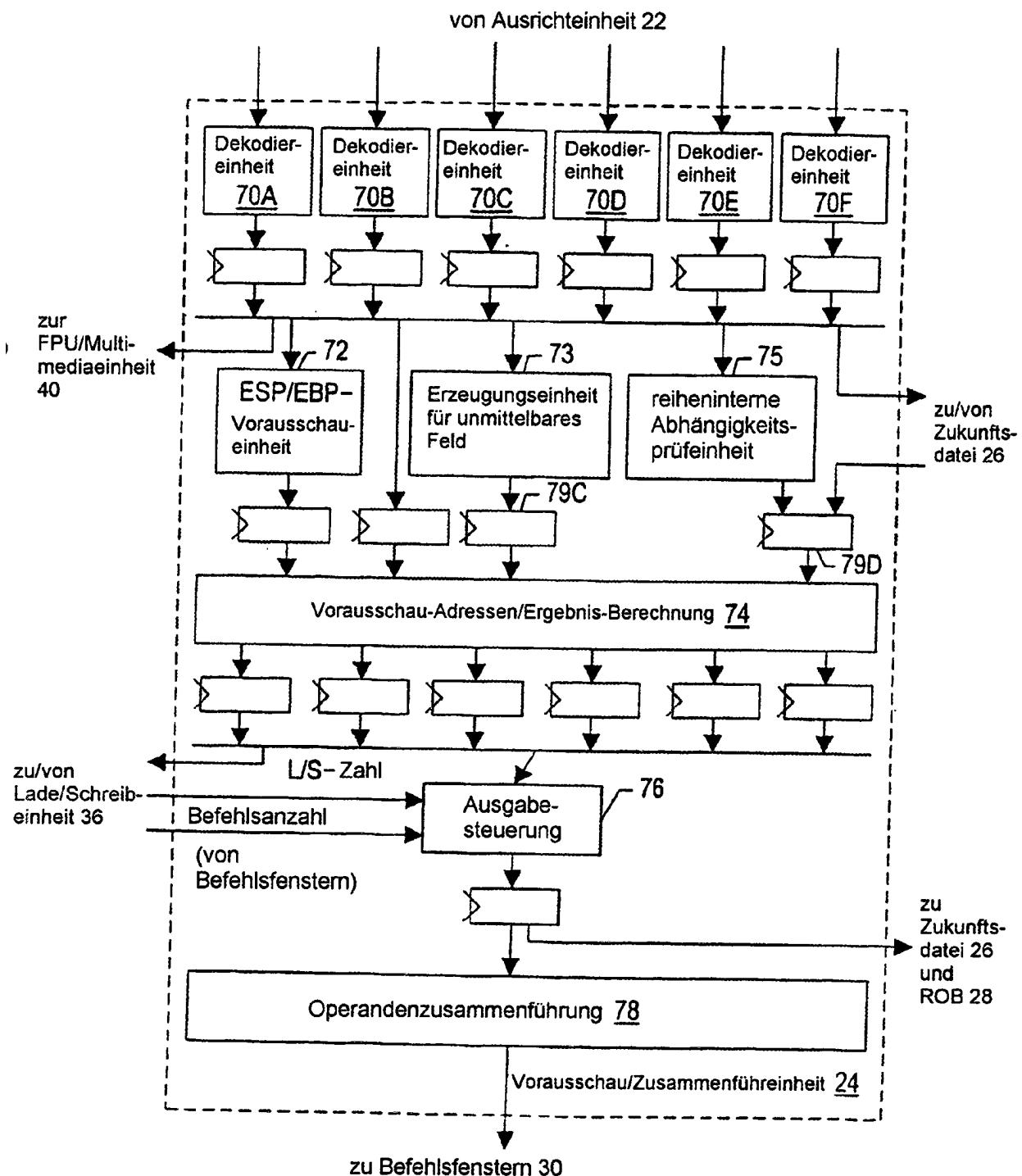

**[0019]** [Fig. 3](#) eine Blockansicht einer Ausführungsform einer Vorausschau/Zusammenführeinheit ist, die in [Fig. 1](#) gezeigt ist;

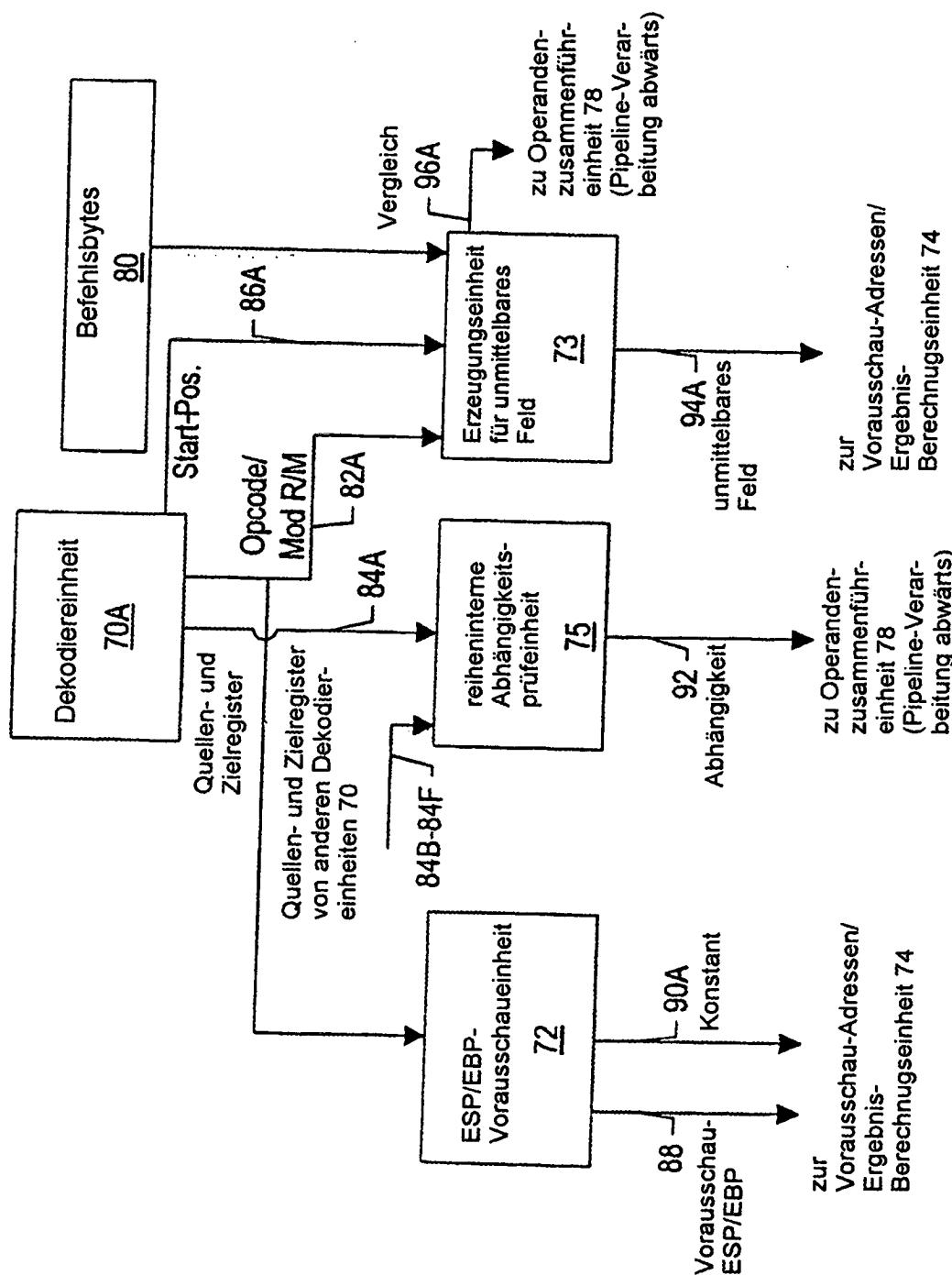

**[0020]** [Fig. 4](#) eine Blockansicht von Bereichen der in [Fig. 3](#) gezeigten Vorausschau/Zusammenführeinheit ist, wobei interne Verbindungen gezeigt sind;

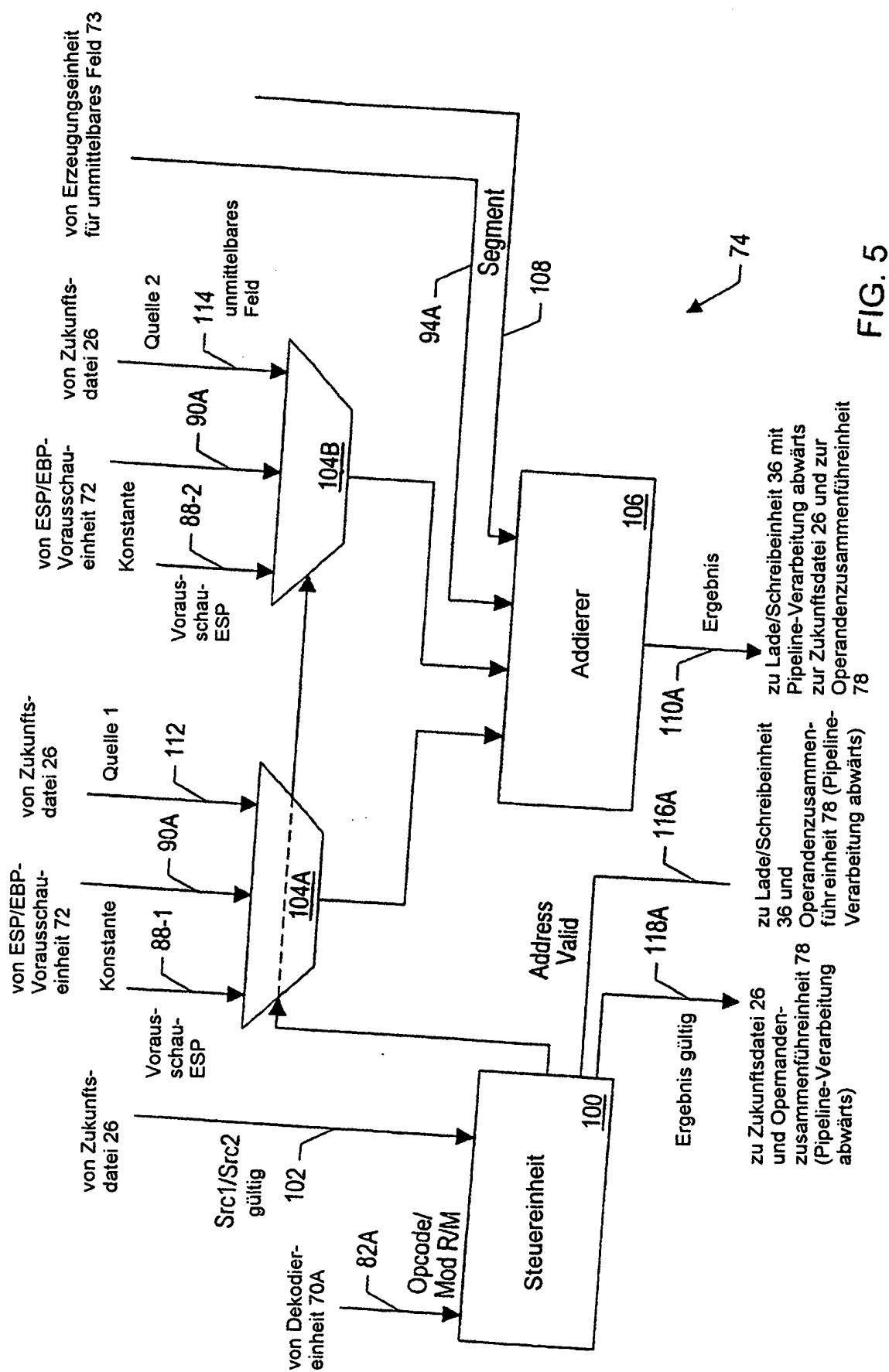

**[0021]** [Fig. 5](#) eine Ansicht ist, die einen Teil einer Ausführungsform einer vorausschauenden Adressen/Ergebnis-Erzeugungseinheit, die in den [Fig. 3](#) und [Fig. 4](#) gezeigt ist, darstellt;

**[0022]** [Fig. 6](#) eine Wahrheitstabelle gemäß einer Ausführungsform einer in [Fig. 5](#) gezeigten Steuereinheit für die vorausschauende Adressenerzeugung ist;

**[0023]** [Fig. 7](#) eine Wahrheitstabelle gemäß einer Ausführungsform einer in [Fig. 5](#) gezeigten Steuereinheit für die vorausschauende Adressenerzeugung ist;

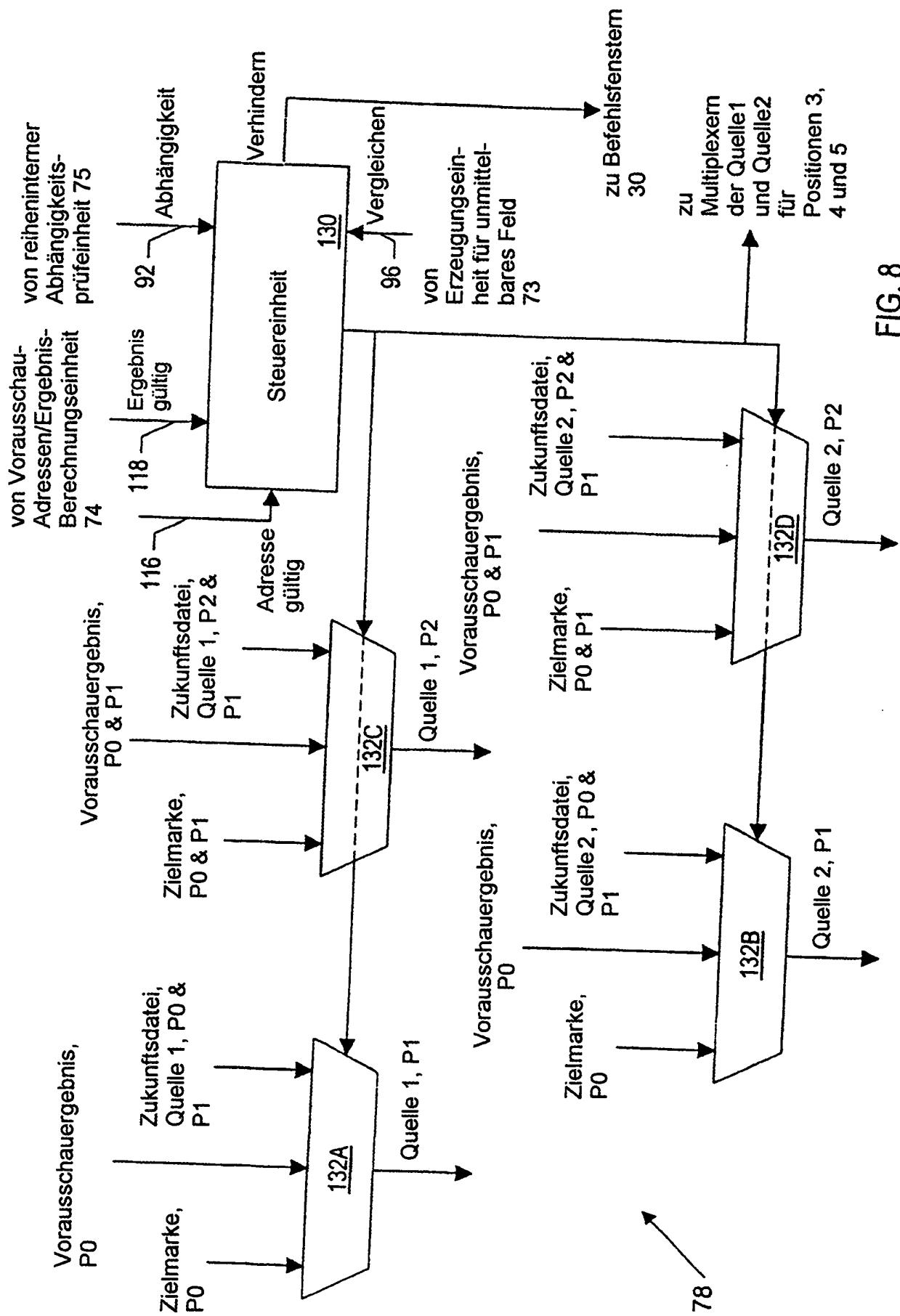

**[0024]** [Fig. 8](#) eine Blockansicht eines Teils einer Ausführungsform der Operandenzusammenführeinheit ist, die in [Fig. 3](#) dargestellt ist;

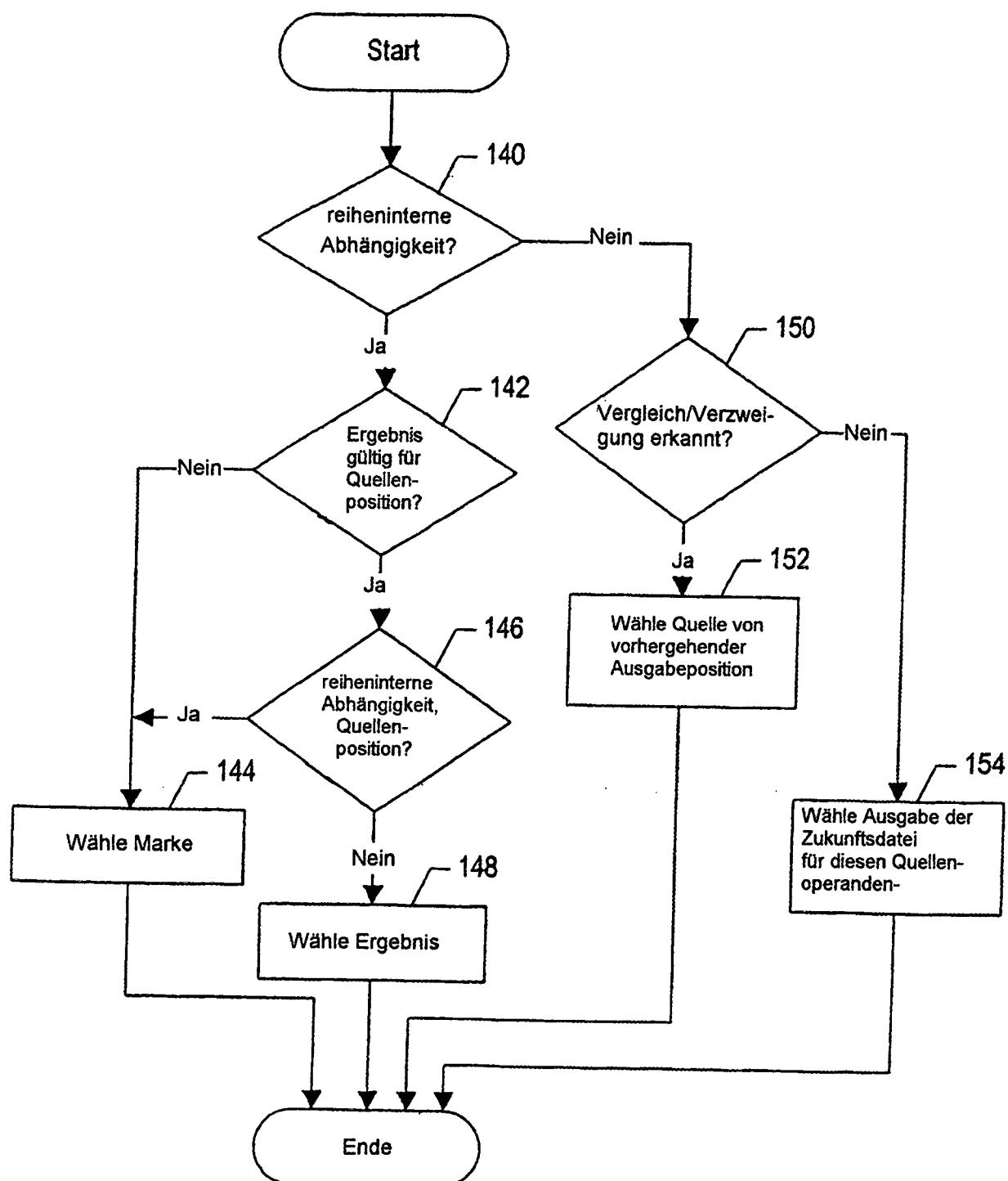

**[0025]** [Fig. 9](#) eine Blockansicht eines Flussdiagramms ist, das eine Ausführungsform einer in [Fig. 8](#) gezeigten Steuerungseinheit darstellt; und

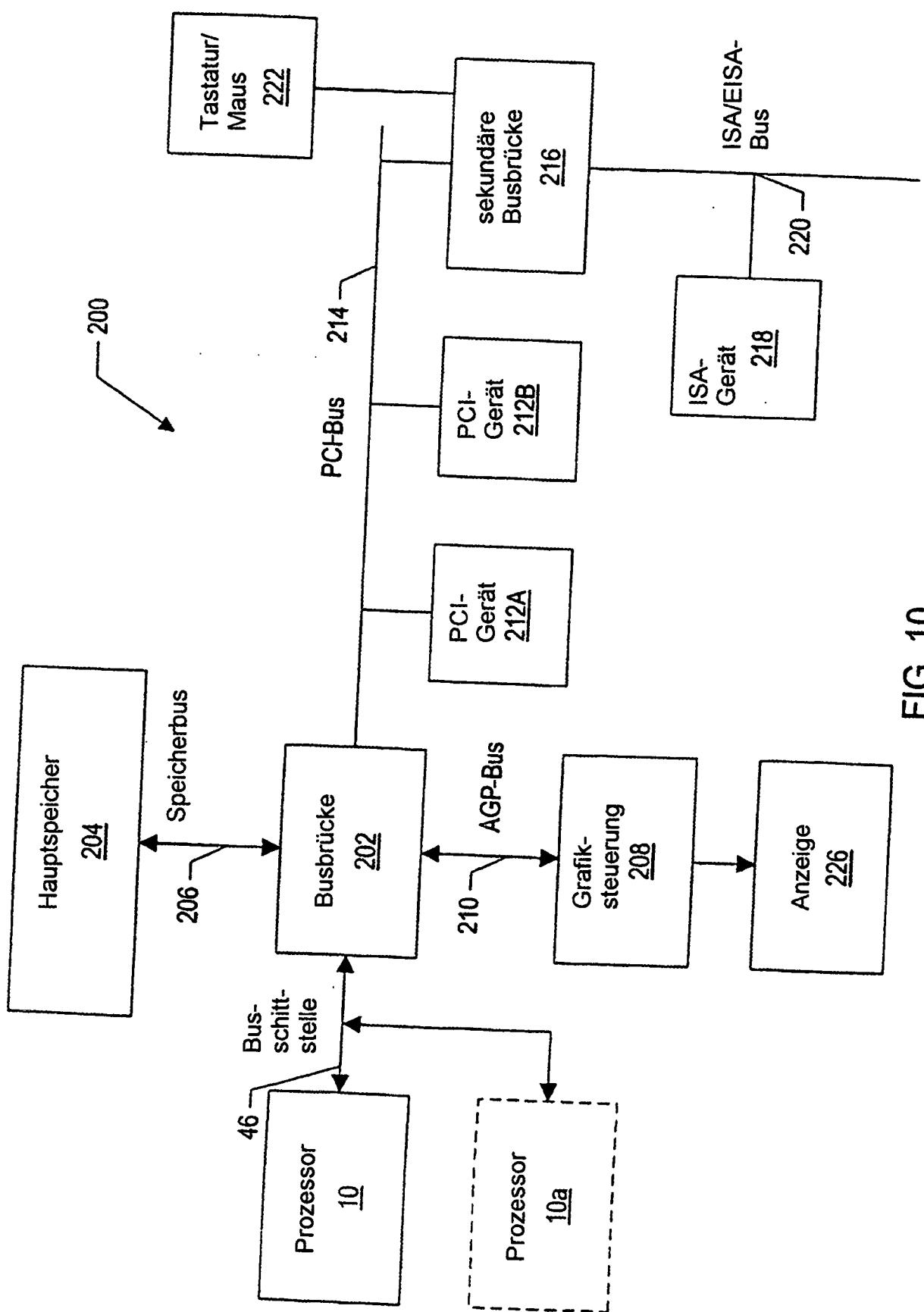

**[0026]** [Fig. 10](#) eine Blockansicht eines Computersystems ist, das den in [Fig. 1](#) gezeigten Prozessor aufweist.

**[0027]** Obwohl die Erfindung diversen Modifizierungen und alternativen Formen unterliegen kann, sind dennoch spezielle Ausführungsformen beispielhaft in den Zeichnungen gezeigt und werden hierin detailliert beschrieben. Es sollte jedoch beachtet werden, dass die Zeichnungen und die detaillierte Beschreibung nicht beabsichtigen, die vorliegende Erfindung auf die speziellen offenbarten Formen einzuschränken, sondern die Erfindung soll vielmehr alle Modifizierungen, Äquivalente und Alternativen abdecken, die innerhalb des Grundgedankens und Schutzbereichs der vorliegenden Erfindung, wie sie durch die angefügten Patentansprüche definiert ist, liegen.

## Detaillierte Beschreibung der Erfindung

**[0028]** [Fig. 1](#) zeigt eine Blockansicht einer Ausführungsform eines superskalaren Prozessors **10**. Andere Ausführungsformen sind möglich und hierin mit eingeschlossen. In der in [Fig. 1](#) gezeigten Ausführungsform umfasst der Prozessor **10** eine Vordecodierungseinheit **12**, einen L1 I-Cache-Speicher **14**, einen L0 I-Cache-Speicher **16**, eine Abhol/Such- bzw. Abtasteinheit **18**, eine Befehlswarteschlange **20**, eine Ausrichteinheit **22**, eine Vorausschau/Zusammenführeinheit **24**, eine Zukunftsdatei **26**, eine Umordnungspuffer/Registerdatei **28**, ein erstes Befehlsfenster **30a**, ein zweites Befehlsfenster **30b**, mehrere Funktionseinheiten **32a**, **32b**, **32c** und **32d**, mehrere Adressenerzeugungseinheiten **34a**, **34b**, **34c** und **34d**, eine Lade/Speicher- bzw. Schreibeinheit **36**, einen L1 D-Cache-Speicher **38**, eine FPU/Multimediaeinheit **40** und eine externe Schnittstelleneinheit **42**. Elemente, die hierin durch eine spezielle Bezugszahl gefolgt von einem bestimmten Buchstaben bezeichnet sind, werden gemeinsam auch unter Anwendung des Bezugszeichens alleine bezeichnet. Beispielsweise werden die Funktionseinheiten **32a**, **32b**, **32c** und **32d** gemeinsam auch als Funktionseinheiten **32** bezeichnet.

**[0029]** In der Ausführungsform aus [Fig. 1](#) ist die externe Schnittstelleneinheit **42** mit der Vordecodierungseinheit **12**, dem L1 D-Cache-Speicher **38**, einer L2-Schnittstelle **44** und einer Busschnittstelle **46** verbunden. Die Vordecodierungseinheit **12** ist ferner mit dem L1 I-Cache-Speicher **14** verbunden. Der L1 I-Cache-Speicher **14** ist mit dem L0 I-Cache-Speicher **16** und der Abhol/Scheinheit **18** verbunden. Die Abhol/Scheinheit **18** ist ferner mit dem L0 I-Cache-Speicher **16** und der Befehlswarteschlange **20** verbunden. Die Befehlswarteschlange **20** ist mit der Ausrichteinheit **22** verbunden, die wiederum mit der Vorausschau/Zusammenführeinheit **24** verbunden ist. Die Vorausschau/Zusammenführeinheit **24** ist ferner mit der Zukunftsdatei **26**, der Umordnungspuffer/Registerdatei **28**, der Lade/Schreibeinheit **36**, dem ersten Befehlsfenster **30a**, dem zweiten Befehlsfenster **30b** und der FPU-Multimediaeinheit **40** verbunden. Die FPU-Multimediaeinheit **40** ist mit der Lade/Schreibeinheit **36** und der Umordnungspuffer/Registerdatei **28** verbunden. Die Lade/Schreibeinheit **36** ist mit dem L1 D-Cache-Speicher **38** verbunden. Das erste Befehlsfenster **30a** ist mit den Funktionseinheiten **32a** bis **32b** und den Adressenerzeugungseinheiten **34a** bis **34b** verbunden. In ähnlicher Weise ist das zweite Befehlsfenster **30b** mit den Funktionseinheiten **32c** bis **32d** und den Adressenerzeugungseinheiten **34c** bis **34d** verbunden. Der L1 D-Cache-Speicher **38**, die Funktionseinheiten **32** und die Adressenerzeugungseinheiten **34** sind jeweils mit mehreren Ergebnissbussen **48** verbunden, die wiederum mit der Lade/Schreibeinheit **36**, dem ersten Befehlsfenster **30a**, dem zweiten Befehlsfenster **30b**, der Umordnungspuffer/Registerdatei **28** und der Zukunftsdatei **26** verbunden sind.

**[0030]** Allgemein gesagt, ist die Vorausschau/Zusammenführeinheit **24** ausgebildet, vorausschauende Ergebnisse für gewisse Befehle vor der Ausgabe dieser Befehle zur Ausführung zu erzeugen. Ein vorausschauendes bzw. ein Vorausschauergebnis wird für gewisse Befehle erzeugt, wenn die Operanden, die zum Erzeugen des Ergebnisses verwendet werden, innerhalb der Zukunftsdatei **26** beim Abholen von Operanden von dieser Datei verfügbar sind. Ein Operand ist verfügbar innerhalb der Zukunftsdatei **26**, wenn der Wert in der Zukunftsdatei **26** gültig ist (im Gegensatz dazu, dass dieser eine Ergebniswartenschlangenmarkierung ist, die den Befehl kennzeichnet, der den Operanden als Ergebnis beim Ausführen erzeugen soll). Wenn ein vorausschauendes Ergebnis erfolgreich erzeugt ist, wird das Ergebnis der Zukunftsdatei **26** zur Speicherung zugeführt und wird abhängigen Befehlen innerhalb der gleichen „Linie bzw. Reihe“ aus Befehlen zugeführt (d. h. gleichzeitig mit dem Befehl decodiert). Vorteilhafterweise werden spekulative Ergebnisse für nachfolgende Befehle früher in der Pipeline verfügbar. Somit sind die vorausschauenden Ergebnisse für die nachfolgenden Befehle berechenbar. Ferner kann das Weiterleiten effizienter sein, da das Weiterleiten häufiger über die Zukunftsdatei **26** möglich ist. Folglich kann die Weiterleitungshardware reduziert werden. Des weiteren kann der Aufwand an Ausführungshardware, die in dem Prozessor **10** eingesetzt wird, reduziert werden, wobei dennoch eine breite Ausgaberate unterstützt wird, da Ergebnisse außerhalb der Ausführungshardware für gewisse Befehle erzeugt wird.

**[0031]** In einer Ausführungsform ist die Vorausschau/Zusammenführeinheit **24** ausgebildet, eine vorausschauende Adresse für Befehle mit einem Speicheroperanden zu erzeugen. Für derartige Befehle wird die Adressenerzeugungsbefehlsoperation, die ansonsten von einer der Adressenerzeugungseinheiten **34** ausgeführt wird, von der Vorausschau/Zusammenführeinheit **24** ausgeführt. Folglich erhält die Lade/Schreibeinheit **36** die Adresse früher in der Pipeline als dies ansonsten möglich ist. Wenn der Befehl eine Additionsbefehlsoperation oder eine Register-Register-Verschiebung bzw. Übertragung spezifiziert und keinen Speicheroperanden enthält, kann die Vorausschau/Zusammenführeinheit **24** ein vorausschauendes Ergebnis erzeugen. Folglich wird die funktionale Befehlsoperation, die ansonsten durch eine der Funktionseinheiten **32** ausgeführt würde, von der Vorausschau/Zusammenführeinheit **24** früher in der Pipeline ausgeführt.

**[0032]** Die Vordecodierungseinheit **12** empfängt Befehlsbytes, die von der externen Schnittstelleneinheit **42** abgeholt werden, und vordecodiert die Befehlsbytes vor ihrer Speicherung innerhalb des L1 I-Cache-Speichers **14**. Die vordecodierte Information, die von der Vordecodierungseinheit **12** erzeugt wird, wird in dem L1 I-Cache-Speicher **14** ebenso abgelegt. Im Allgemeinen wird die vordecodierte Information vorgesehen, um die Erkennung von Befehlsmerkmalen zu unterstützen, was während des Abholens und der Ausgabe von Befehlen vorteilhaft sein kann, die jedoch während des Abhol- und Ausgabeoperationsvorgangs jedoch nur unter Schwierigkeiten rasch erzeugt werden kann. Der Begriff „Vordecodieren“, wie er hierin verwendet ist, bezeichnet das Decodieren von Befehlen, um die Vordecodierungsinformation zu erzeugen, die später mit den Befehlsbytes gespeichert wird, die in einem Befehlscache-Speicher (beispielsweise L1 I-Cache-Speicher **14** und/oder L0 I-Cache-Speicher **16**) decodiert werden.

**[0033]** In einer Ausführungsform verwendet der Prozessor 2 Bits an Vordecodierungsinformation pro Befehlsbyte. Eines der Bits, das als das „Startbit“ bezeichnet wird, gibt an, ob das Befehlsbyte das erste Byte eines Befehls ist. Wenn eine Gruppe aus Befehlsbytes abgeholt wird, kennzeichnet der entsprechende Satz aus Startbits die Grenzen zwischen den Befehlen innerhalb der Gruppe aus Befehlsbytes. Folglich können mehrere Befehle gleichzeitig aus der Gruppe aus Befehlsbytes ausgewählt werden, indem nach den entsprechenden Startbits gesucht wird. Während die Startbits verwendet werden, um Befehlgrenzen zu erkennen, indem das Anfangsbytes jedes Befehls ermittelt wird, können Endbits alternativ verwendet werden, um Befehlgrenzen zu erkennen, indem das letzte Byte jedes Befehls ermittelt wird.

**[0034]** Das zweite Vordecodierungsbit, das in dieser Ausführungsform verwendet wird, wird als das "Steuertransfer"-Bit bezeichnet und gibt an, welche Befehle Verzweigungsbefehle sind. Das Steuertransferbit entspricht dem Anfangsbyte eines Befehls, der angibt, ob der Befehl ein Verzweigungsbefehl ist oder nicht. Das Steuertransferbit, das nachfolgenden Bytes des Befehls entspricht, ist ein „beliebig“ mit Ausnahme für relative Verzweigungsbefehle mit einem kleinen Verschiebungsfeld. Gemäß einer speziellen Ausführungsform ist das kleine Verschiebungsfeld ein 8-Bit-Feld. Im Allgemeinen bezeichnet ein „kleines Verschiebungsfeld“ ein Verschiebungsfeld mit weniger Bits, als die Zieladresse, die von den Verzweigungsbefehlen erzeugt wird. Für relative Verzweigungsbefehle mit kleinen Verschiebungsfeldern wird das Steuertransferbit, das dem Verschiebungsbefehl entspricht, in der Weise verwendet, wie dies nachfolgend beschrieben ist.

**[0035]** Zusätzlich zu dem Erzeugen von Vordecodierungsinformationen, die den Befehlsbytes entsprechen, ist die Vordecodierungseinheit **12** ausgebildet, das Verschiebungsfeld relativer Verzweigungsbefehle umzucodieren, um tatsächlich die Zieladresse in der vorliegenden Ausführungsform zu speichern. Anders ausgedrückt, die Vordecodierungseinheit **12** addiert die Verschiebung des relativen Verzweigungsbefehles, die dem relativen Verzweigungsbefehl entspricht, wie er durch den Befehlssatz definiert ist, der von dem Prozessor **10** verwendet wird. Die sich ergebende Zieladresse wird in das Verschiebungsfeld als ein Ersatz für die Verschiebung codiert, und das aktualisierte Verschiebungsfeld wird in dem L1 I-Cache-Speicher **14** anstelle des ursprünglichen Verschiebungsfeldes gespeichert. Die Zieladressenerzeugung wird vereinfacht, indem relative Zieladressen im Voraus berechnet werden, und somit kann der Verzweigungsvorhersagemechanismus effizienter arbeiten.

**[0036]** In einer Ausführungsform des Prozessors **10**, in der der x86-Befehlssatz verwendet ist, ist die Vordecodierungseinheit **12** ausgebildet, 8 Bit- und 32-Bit-Verschiebungsfelder neu zu codieren. Die 32-Bit-Verschiebungsfelder können alle Zieladressen aufnehmen. Andererseits wird das 8-Bit-Verschiebungsfeld codiert. Insbesondere werden das 8-Bit-Verschiebungsfeld und entsprechende Steuertransfervordecodierungsbits in einen Cache-Zeilenoffsetbereich und in einen relativen Cache-Zeilenbereich unterteilt. Der Cache-Zeilenoffsetbereich ist der Cache-Zeilenoffsetbereich der Zieladresse. Der relative Cache-Zeilenbereich definiert die Cache-Zeile, die von der Zieladresse angegeben ist (die „Zielcache-Zeile“) in Bezug auf eine Anzahl an Cache-Zeilen über oder unter der Cache-Zeile, in der der relative Verzweigungsbefehl gespeichert ist. Eine erste Cache-Zeile ist über einer zweiten Cache-Zeile, wenn jedes Byte in der ersten Cache-Zeile an einer Adresse gespeichert ist, die numerisch größer ist als die Adressen, an denen die Bytes in der zweiten Cache-Zeile gespeichert sind. Andererseits ist eine erste Cache-Zeile unter der zweiten Cache-Zeile, wenn jedes Byte in der ersten Cache-Zeile an einer Adresse gespeichert ist, die numerisch kleiner ist als die Adressen, an denen die Bytes in der zweiten Cache-Zeile gespeichert sind. Eine 8-Bit-Verschiebung mit Vorzeichen spezifiziert eine Adresse, die innerhalb +/- 128 Bytes der Adresse liegt, die dem Verzweigungsbefehl entspricht. Folglich ist die Anzahl über und unter den Cache-Zeilen, die durch einen relativen Verzweigungsbefehl mit einer 8-Bit-Verschiebung erreicht werden kann, begrenzt. Der relative Cache-Zeilenbereich codiert diesen begrenzten Salz aus darüberliegenden und darunterliegenden Cache-Zeilen. Im Allgemeinen besitzen Verzweigungsbefehle, die ein kleines Verschiebungsfeld besitzen, Verschiebungen innerhalb eines vordefinierten Bereichs, wohin größere Verschiebungsfelder Werte außerhalb des vordefinierten Bereichs speichern können.

**[0037]** Die nachfolgenden Tabellen 1 und 2 zeigen eine beispielhafte Codierung der Vordecodierungsinformation, die einem Byte entspricht, gemäß einer Ausführungsform des Prozessors **10**.

Tabelle 1: Vordecodierungscodierung

| Startbit | Steuertransferbit | Bedeutung                                                                                                                                                                                                 |

|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | 0                 | Startbyte eines Befehls, der keine Verzweigung ist                                                                                                                                                        |

| 1        | 1                 | Startbyte eines Verzweigungsbefehls                                                                                                                                                                       |

| 0        | x                 | Keine Befehlgrenze. Steuertransferbit, das der Verschiebung entspricht, wird auf 8 Bit relative Verzweigungen angewendet, um die Zieladresse zu codieren, wie in der nachfolgenden Tabelle 2 gezeigt ist. |

Tabelle 2: Zieladressencodierung

| Steuer-transferbit | Verschiebungsbyte signifikanteste Bits (binär) | Bedeutung                       |

|--------------------|------------------------------------------------|---------------------------------|

| 0                  | 00                                             | innerhalb aktueller Cache-Zeile |

| 0                  | 01                                             | eine Cache-Zeile darüber        |

| 0                  | 10                                             | zwei Cache-Zeilen darüber       |

| 1                  | 01                                             | eine Cache-Zeile darunter       |

| 1                  | 10                                             | zwei Cache-Zeilen darunter      |

Beachte: Verbleibende Verschiebungsbytes-Bits sind der Offset innerhalb der Ziel-Cache-Zeile. Das Steuertransferbit ist tatsächlich eine Richtung und die signifikantesten Bits des Verschiebungsbytes sind die Anzahl der Cache-Zeilen.

**[0038]** Die Vordecodierungseinheit **12** überträgt die empfangenen Befehlsbytes und die entsprechende Vordecodierungsinformation zur Speicherung an den L1 I-Cache-Speicher **14**. Der L1 I-Cache-Speicher **14** ist ein Hochgeschwindigkeitscache-Speicher zur Speicherung von Befehlsbytes und Vordecodierungsinformationen. Der L1 I-Cache-Speicher **14** kann eine beliebige geeignete Konfiguration aufweisen, zur der eine direkt abgebildete und eine teilassoziative Konfiguration gehört. In einer speziellen Ausführungsform ist der L1 I-Cache-Speicher **14** ein 128 KB zweiwege-teilassoziativer Cache, in welchem 64 Byte-Cache-Zeilen verwendet werden. Der L1 I-Cache-Speicher **14** umfasst einen zusätzlichen Speicherplatz für die Vordecodierungsinformation, die den darin gespeicherten Befehlsbytes entspricht. Der zusätzliche Speicherplatz ist in ähnlicher Weise wie der Speicherplatz für die Befehlsbytes organisiert. Im hierin verwendeten Sinne bezeichnet der Begriff „Cache-Zeile“ die Einheit für die Reservierung von Speicherplatz in einem speziellen Cache-Speicher. Im Allgemeinen werden die Bytes innerhalb einer Cache-Zeile von dem Cache-Speicher als eine Einheit manipuliert (d. h. reserviert und freigegeben). In einer Ausführungsform wird der L1 I-Cache-Speicher **14** linear adressiert und physikalisch markiert. Ein Cache wird linear adressiert, wenn mindestens eines der Adressenbits, das zur Indizierung des Cache-Speichers verwendet wird, ein lineares Adressenbit ist, das nachfolgend in ein physikalisches Adressenbit übersetzt wird. Die Markierungen eines linear adressierten/physikalisch markierten Cache-Speichers enthalten jedes übersetzte Bit zusätzlich zu den Bits, die nicht zur Indizierung verwendet werden. Wie dies durch die x86-Architektur spezifiziert ist, werden Befehle definiert, um logische Adressen zu erzeugen, die über einen Segmentierungsübersetzungsmechanismus in eine lineare Adresse und ferner über einen Seitenübersetzungsmechanismus in eine physikalische Adresse übersetzt werden. Es ist zunehmend gebräuchlich, einen ausgeglichenen Adressierungsmodus einzusetzen, in welchem die logische Adresse und die entsprechende lineare Adresse gleich sind. Der Prozessor **10** kann so ausgebildet sein, dass dieser einen ausgeglichenen Adressierungsmodus ausübt. Folglich sind Abholadressen, Zieladressen, etc., wie sie beim Ausführen von Befehlen erzeugt werden, lineare Adressen. Um zu bestimmen, ob ein Treffer in L1 I-Cache-Speicher

cher **14** vorliegt, wird die durch die Abhol/Scheinheit **18** repräsentierte lineare Adresse unter Anwendung eines Übersetzungsnebenordnungspuffers (TLB) in eine entsprechende physikalische Adresse übersetzt, die mit den physikalischen Marken der indizierten Cache-Zeilen verglichen wird, um einen Treffer/Nichttreffer zu erkennen. Wenn der ausgeglichene Adressierungsmodus nicht verwendet wird, kann der Prozessor dennoch eine Codierung ausführen, wobei jedoch zusätzliche Taktzyklen verwendet werden, um lineare Adressen aus den logischen Adressen zu erzeugen.

**[0039]** Der L0 I-Cache-Speicher **16** ist ebenfalls ein Hochgeschwindigkeitscache-Speicher zur Speicherung von Befehlsbytes. Da der L1 I-Cache-Speicher **14** groß ist, kann auch die Zugriffszeit für den L1 I-Cache-Speicher **14** groß sein. In einer speziellen Ausführungsform verwendet der L1 I-Cache-Speicher **14** zwei Taktzyklen an Zugriffszeit. Um eine Abholzugriffszeit innerhalb eines einzelnen Taktzyklus zu ermöglichen, wird der L0 I-Cache-Speicher **16** verwendet. Der L0 I-Cache-Speicher **16** ist deutlich kleiner als der L1 I-Cache-Speicher **14** und bietet damit eine deutlich geringere Zugriffszeit. In einer speziellen Ausführungsform ist der L0 I-Cache-Speicher **16** ein 512 Byte vollassoziativer Cache-Speicher. Ähnlich zu dem L1 I-Cache-Speicher **14** ist der L0 I-Cache-Speicher **16** ausgebildet, Cache-Zeilen von Befehlsbytes und entsprechende Vordecodierungsinformationen (beispielsweise 512 Bytes speichern 864 Cache-Zeilen und entsprechende Vordecodierungsdaten werden zusätzlichen Speicherplatz abgelegt) zu speichern. In einer Ausführungsform wird der L0 I-Cache-Speicher **16** linear adressiert und linear markiert.

**[0040]** Die Abhol/Scheinheit **18** ist ausgebildet, Adressen für den L0 I-Cache-Speicher **16** zu erzeugen und Adressen für den L1 I-Cache-Speicher **14** abzuholen oder vorabzuholen. Von dem L0 I-Cache-Speicher **16** abgeholt Befehle werden von der Abhol/Scheinheit **18** durchsucht, um Befehle für die Ausgabe zu erkennen sowie Verzweigungsbefehle zu ermitteln und Verzweigungsvorhersagen entsprechend den erkannten Verzweigungsbefehlen zu erzeugen. Befehlssuchinformationen und entsprechende Befehlsbytes werden in der Befehlswarteschlange **20** durch die Abhol/Scheinheit **18** gespeichert. Zusätzlich werden die erkannten Verzweigungsbefehle und Verzweigungsvorhersagen verwendet, um nachfolgende Abholadressen für den L0 I-Cache-Speicher **16** zu erzeugen.

**[0041]** Die Abhol/Scheinheit **18** verwendet einen Vorabholalgorithmus, um zu versuchen, Cache-Zeilen von dem L1 I-Cache-Speicher **14** in den L0 I-Cache-Speicher **16** einzuladen, bevor die vorabgeholtten Cache-Zeilen von der Abhol/Scheinheit **18** zur Ausgabe in den Prozessor **10** abgeholt werden. Es kann ein beliebiger geeigneter Vorabholalgorithmus eingesetzt werden. Eine Ausführungsform des Vorabholalgorithmus ist nachfolgend detaillierter erläutert.

**[0042]** Die Abhol/Scheinheit **18** verwendet einen aggressiven Verzweigungsvorhersagemechanismus in dem Versuch, größere "Abschnitte" aus Befehlen während eines Taktzyklus abzuholen. Im hierin verwendeten Sinne bezeichnet "ein Abschnitt" aus Befehlen einen Satz aus einem oder mehreren Befehlen, von denen vorhergesagt wird, dass sie in der durch den Satz spezifizierten Reihenfolge ausgeführt werden. Beispielsweise kann die Abhol/Scheinheit **18** Abschnitte aus 24 Befehlsbytes aus dem L0 I-Cache-Speicher **16** abholen. Jeder Abschnitt wird in mehrere Teile unterteilt, die die Abhol/Scheinheit **18** parallel durchsucht, um Verzweigungsbefehle zu erkennen und um die Befehlssuchinformation für die Befehlswarteschlange **20** zu erzeugen. Gemäß einer Ausführungsform versucht die Abhol/Scheinheit **18** bis zu zwei Verzweigungsbefehle pro Taktzyklus vorherzusagen, um große Befehlsabschnitte zu unterstützen.

**[0043]** Die Befehlswarteschlange **20** ist ausgebildet, Befehlsbytes, die von der Abhol/Scheinheit **18** bereitgestellt werden, für das nachfolgende Ausgeben zu speichern. Die Befehlswarteschlange **20** kann als ein „zuerst herein, zuerst heraus“ (FIFO) Puffer arbeiten. In einer Ausführungsform ist die Befehlswarteschlange **20** ausgebildet, mehrere Einträge zu speichern, wobei jeder Eintrag umfasst: einen Abschnitt aus Befehlen, Suchdaten, die bis zu fünf Befehle innerhalb jedes Teils des Abschnitts kennzeichnen, und Adressen entsprechend jedem Teil des Abschnitts. Ferner kann die Befehlswarteschlange **20** ausgebildet sein, bis zu 6 Befehle innerhalb bis zu vier aufeinanderfolgender Abschnitte zur Zuführung zu der Ausrichteinheit **22** auszuwählen. Die Befehlswarteschlange **20** kann beispielsweise zwei bis drei Einträge verwenden.

**[0044]** Die Ausrichteinheit **22** ist ausgebildet, Befehle, die von der Befehlswarteschlange **20** gesendet sind, zu einem Satz aus Ausgabepositionen innerhalb der Vorausschau/Zusammenführeinheit **24** weiterzuleiten. Anders ausgedrückt, die Ausrichteinheit **22** wählt die Bytes, die jeden Befehl bilden, aus den Abschnitten aus, die von der Befehlswarteschlange **20** bereitgestellt werden, in Reaktion auf die Suchinformation, die von der Befehlswarteschlange **20** bereitgestellt wird. Die Befehle werden den Ausgabepositionen in der Programmreihenfolge zugeführt (d. h. der Befehl, der in der Programmreihenfolge zuerst erfolgt, wird der ersten Ausgabeposition zugeführt, der zweite Befehl in der Programmreihenfolge wird der zweiten Ausgabeposition zugeführt,

etc.).

**[0045]** Die Vorausschau/Zusammenföhreinheit **24** decodiert die Befehle, die von der Ausrichteinheit **22** bereitgestellt werden. FPU-Multimedia-Befehle, die von der Vorausschau/Zusammenföhreinheit **24** erkannt werden, werden der FPU-Multimediaeinheit **40** zugeführt. Andere Befehle werden dem ersten Befehlsfenster **30a**, dem zweiten Befehlsfenster **30b** und/oder der Lade/Schreibeinheit **36** zugeführt. In einer Ausführungsform wird ein spezieller Befehl dem ersten Befehlsfenster **30a** oder dem zweiten Befehlsfenster **30b** auf der Grundlage der Ausgabeposition zugeführt, die dem Befehl von der Ausrichteinheit **22** zugeordnet ist. Gemäß einer speziellen Ausführungsform werden Befehle von abwechselnden Ausgabepositionen abwechselnd den Befehlsfenster **30a** und **30b** zugeführt. Beispielsweise werden die Befehle aus den Ausgabepositionen 0, 2 und 4 dem ersten Befehlsfenster **30a** und Befehle von den Ausgabepositionen 1, 3 und 5 werden dem zweiten Befehlsfenster **30b** zugeführt. Befehle, die eine Speicheroperation beinhalten, werden ebenso zu der Lade/Schreibeinheit **36** für einen Zugriff auf den L1 D-Cache-Speicher **38** zugeführt.

**[0046]** Ferner versucht die Vorausschau/Zusammenföhreinheit **24**, vorrausschauende Adressen oder Ausführungsergebnisse für gewisse Arten von Befehlen zu erzeugen. Die vorausschauende Adressen/Ergebniserzeugung kann insbesondere vorteilhaft sein in Ausführungsformen, in denen der x86-Befehlssatz verwendet ist. Auf Grund der Natur des x86-Befehlssatzes sind viele der Befehle in einer typischen Codierungssequenz einfache Verschiebe- bzw. Übertragungsbefehle. Ein Grund für diese Eigenschaft besteht darin, dass die x86-Befehle zwei Operanden beinhalten, wovon beide Quellenoperanden sind und wovon einer ein Zieloperand ist. Daher wird einer der Quellenoperanden jedes Befehls mit einem Ausführungsergebnis überschrieben. Ferner spezifiziert der x86-Befehlssatz sehr wenige Register zur Speicherung von Registeroperanden. Folglich sind viele Befehle Übertragungen von Operanden zu und von einem Stapel, der in einem Speicher bewahrt wird. Des weiteren sind viele Befehlsabhängigkeiten Abhängigkeiten von ESP/EBP-Registern und somit sind viele der Aktualisierungen dieser Register Inkremente und Dekremente der zuvor gespeicherten Werte.

**[0047]** Um das Ausführen dieser Befehle zu beschleunigen, erzeugt die Vorausschau/Zusammenföhreinheit **24** vorausschauende Kopien der ESP und EBP-Register für jeden der Befehle, die während eines Taktzyklus decodiert werden. Ferner greift die Vorausschau/Zusammenföhreinheit **24** auf die Zukunftsdatei **26** für Registeroperanden, die durch den jeweiligen Befehl ausgewählt sind, zu. Für jeden Registeroperanden kann die Zukunftsdatei **26** ein Ausführungsergebnis oder eine Marke enthalten, die einen Umordnungspufferergebniswarteschlangeneintrag kennzeichnet, der dem jüngsten Befehl entspricht, der dieses Register als einen Zieloperanden aufweist.

**[0048]** In einer Ausführungsform versucht die Vorausschau/Zusammenföhreinheit **24**, eine Adressberechnung für jeden Befehl auszuführen, der: (i) einen Speicheroperanden enthält; und wenn (ii) Registeroperanden, die zur Erzeugung der Adresse des Speicheroperanden verwendet werden, aus der Zukunftsdatei **26** oder vorrausschauenden Kopien von ESP/EBP verfügbar sind. Des Weiteren versucht die Vorausschau/Zusammenföhreinheit **24** eine Ergebnisberechnung für jeden Befehl auszuführen, der: (i) keinen Speicheroperanden enthält; (ii) eine Addier/Subtrahieroperation einschließlich Inkrement oder Dekrement angibt; und wenn (iii) ein Registeroperand aus der Zukunftsdatei **26** oder Vorausschaukopien von ESP/EBP verfügbar sind. Auf diese Weise können viele einfache Operationen abgeschlossen werden, bevor Befehle zu den Befehlsfenster **30a** bis **30b** gesendet werden.

**[0049]** Die Vorausschau/Zusammenföhreinheit **24** erkennt Abhängigkeiten zwischen einer Gruppe aus Befehlen, die ausgegeben wurden, und führt Ausführungsergebnisse, die dann erzeugt werden, in Befehle zusammen, die von diesen Befehlsergebnissen abhängen. Ferner aktualisiert die Vorausschau/Zusammenföhreinheit **24** die Zukunftsdatei **26** mit den vorrausschauenden Ausführungsergebnissen. Befehlsoperationen, die von der Vorausschau/Zusammenföhreinheit **24** abgeschlossen werden (d. h. Adressenerzeugungen und/oder Befehlsergebnisse werden erzeugt und die Lade/Schreibeinheit **36** oder die Zukunftsdatei **26** und die Ergebniswarteschlange werden aktualisiert) werden nicht an die Befehlsfenster **30a** bis **30b** ausgegeben.

**[0050]** Die Vorausschau/Zusammenföhreinheit **24** reserviert einen Ergebniswarteschlangeneintrag in der Umordnungspuffer/Registerdatei **28** für jeden ausgegebenen Befehl. In einer speziellen Ausführungsform umfasst die Umordnungspuffer/Registerdatei **28** eine Ergebniswarteschlange, die in einer zeilenorientierten Weise organisiert ist, wobei die Speicherplätze für die Ausführungsergebnisse in Zeilen mit ausreichend Speicherplatz für Ausführungsergebnisse, die einer maximalen Zahl an gleichzeitig ausgebaren Befehlen entspricht, reserviert und freigegeben werden. Wenn weniger als die maximale Anzahl an Befehlen ausgegeben werden, dann bleiben gewisse Speicherplätze innerhalb der Zeile leer. Nachfolgend ausgegebene Befehle verwenden die nächste verfügbare Zeile, wobei gewisse Speicherplätze leer bleiben. In einer Ausführungsform umfasst

die Ergebniswarteschlange **40** Zeilen, wovon jede bis zu 6 Ausführungsergebnisse entsprechend den gleichzeitig ausgegebenen Befehlen speichern kann. Ausführungsergebnisse werden aus der Ergebniswarteschlange der Reihenfolge nach in die Registerdatei, die innerhalb der Umordnungspuffer/Registerdatei **28** enthalten ist, zurückgeführt. Des weiteren handelt der Umordnungspuffer Verzweigungsfehlvorhersagen und übermittelt die korrigierte Abholadresse, die von der Ausführung des Verzweigungsbefehls erzeugt wird, an die Abhol/Scheinheit **18**. In ähnlicher Weise werden Befehle, die andere Sonder- bzw. Ausnahmeeignisse erzeugen, innerhalb des Umordnungspuffers gehandhabt. Ergebnisse, die auf den das Ausnahmeeignis erzeugenden Befehl folgen, werden von dem Umordnungspuffer verworfen. Die Registerdatei umfasst einen Speicherplatz für jedes aufgebaute Register. Beispielsweise definiert der x86-Befehlssatz 8 speziell aufgebaute Register. Die Registerdatei für eine derartige Ausführungsform umfasst 8 Speicherplätze. Die Registerdatei kann ferner Speicherplätze enthalten, die als temporäre Register durch eine Mikrocodierungseinheit in Ausführungsformen verwendet werden, in denen Mikrocodierungseinheiten eingesetzt sind.

**[0051]** Die Zukunftsdatei **26** bewahrt den spekulativen Zustand jedes speziell gestalteten Registers, wenn Befehle von der Vorausschau/Zusammenföhreinheit **24** ausgegeben werden. Wenn ein Befehl mit einem Registerzieloperanden von der Vorausschau/Zusammenföhreinheit **24** decodiert wird, wird die Markierung, die den Speicherplatz innerhalb des Ergebniswarteschlangenbereichs der Umordnungspuffer/Registerdatei **28**, der dem Befehl zugeordnet ist, in dem Speicherplatz der Zukunftsdatei **26** abgelegt, der diesem Register entspricht. Wenn das entsprechende Ausführungsergebnis bereitgestellt wird, wird das Ausführungsergebnis in dem entsprechenden Speicherplatz abgelegt (wobei angenommen wird, dass ein nachfolgender Befehl, der das Register aktualisiert, nicht ausgegeben ist).

**[0052]** Es ist zu beachten, dass in einer Ausführungsform eine Gruppe bis zu 6 Befehlen aus der Befehlswarteschlange **20** ausgewählt wird und durch die Pipeline innerhalb der Vorausschau/Zusammenföhreinheit **24** als eine Einheit wandert. Wenn einer oder mehrere Befehle innerhalb der Gruppe eine Abbruchbedingung erzeugt, wird die ganze Gruppe beendet. Eine Ausnahme dieser Regel besteht darin, wenn die Vorausschau/Zusammenföhreinheit **24** eine Bedingung zur Aufteilung der Reihe auf Grund der Anzahl von ESP-Aktualisierungen innerhalb der Gruppe erzeugt. Eine derartige Gruppe aus Befehlen wird als eine „Reihe oder Linie“ aus Befehlen hierin bezeichnet.

**[0053]** Die Befehlsfenster **30** empfangen Befehle von der Vorausschau/Zusammenföhreinheit **24**. Die Befehlsfenster **30** speichern die Befehle bis die Operanden, die den Befehlen entsprechen, empfangen werden, und wählen dann die Befehle für die Ausführung aus. Sobald die Adressenoperanden eines Befehls, der eine Speicheroperation enthält, empfangen sind, wird der Befehl zu einer der Adressenerzeugungseinheiten **34** übermittelt. Die Adressenerzeugungseinheiten **34** erzeugen eine Adresse aus den Adressenoperanden und leiten die Adresse zu der Lade/Schreibeinheit **36** weiter. Wenn andererseits die Ausführungsoperanden eines Befehls empfangen werden, wird der Befehl zu einer der Funktionseinheiten **32** für die Ausführung weitergeleitet. In einer Ausführungsform enthält jedes Befehlsfenster **30a** bis **30b** 25 Speicherplätze für Befehle. Jedes Befehlsfenster **30a** bis **30b** ist ausgebildet, bis zu zwei Adressenerzeugungen und zwei Funktionseinheitenoperationen für die Ausführung in jedem Taktzyklus in den Adressenerzeugungseinheiten **34** und in den Funktionseinheiten **32**, die damit verbunden sind, auszuwählen. In einer Ausführungsform bleiben die Befehle, die aus dem L0 I-Cache-Speicher **16** abgeholt werden, in der gleichen Reihenfolge, wie sie abgeholt werden, bis sie in einem der Befehlsfenster **30** gespeichert werden, und ab diesem Zeitpunkt können die Befehle außer der Reihenfolge ausgeführt werden.

**[0054]** In einigen Ausführungsformen des Prozesses **10**, wobei der x86-Befehlssatz eingesetzt ist, kann ein Befehl implizierte Speicheroperationen für die Lade/Schreibeinheit **36** sowie explizite Funktionsoperationen für die Funktionseinheiten **32** enthalten. Befehle mit keinem Speicheroperanden beinhalten keine Speicheroperationen und werden von den Funktionseinheiten **32** behandelt. Befehle mit einem Quellspeicheroperanden und einem Registerzieloperanden enthalten eine implizite Ladespeicheroperation, die von der Lade/Schreibeinheit **36** behandelt wird, und eine explizite Funktionsoperation, die von den Funktionseinheiten **32** behandelt wird. Befehle mit einem Speicherquellen/Zieloperanden enthalten implizite Lade- und Schreibspeicheroperationen, die von der Lade/Schreibeinheit **36** behandelt werden, und besitzen explizite Funktionsoperationen, die von den Funktionseinheiten **32** behandelt werden. Schließlich werden Befehle, die keine explizite Funktionsoperation aufweisen, von der Lade/Schreibeinheit **36** behandelt. Jede Speicheroperation führt zu einer Adressenerzeugung, die von der Vorausschau/Zusammenföhreinheit **24** oder den Adressenerzeugungseinheiten **34** behandelt wird. Speicheroperationen und Befehle (d. h. Funktionsoperationen) werden hierin separat beschrieben, können jedoch von einem einzelnen Befehl stammen.

**[0055]** Die Adressenerzeugungseinheiten **34** sind ausgebildet, Adressenerzeugungsoperationen auszufüh-

ren, wodurch Adressen für Speicheroperationen in der Lade/Schreibeinheit **36** erzeugt werden. Die erzeugten Adressen werden zu der Lade/Schreibeinheit **36** über Ergebnisbusse **48** weitergeleitet. Die Funktionseinheiten **32** sind ausgebildet, arithmetische/logische Ganzzahloperationen und Verzweigungsbefehle auszuführen. Die Ausführungsergebnisse werden zu der Zukunftsdatei **26**, der Umordnungspuffer/Registerdatei **28** und dem Befehlsfenster **30a** bis **30b** über die Ergebnisbusse **48** weitergeleitet. Die Adressenerzeugungseinheiten **34** und die Funktionseinheiten **32** übermitteln die Ergebniswarteschlangenmarke, die dem Befehl zugeordnet ist, der ausgeführt wird, wenn die Ergebnisbusse **48** den gerade ausgeführten Befehl kennzeichnen. Auf diese Weise können die Zukunftsdatei **26**, die Umordnungspuffer/Registerdatei **28**, die Befehlsfenster **30a** bis **30b** und die Lade/Schreibeinheit **36** Ausführungsergebnisse des entsprechenden Befehls erkennen. Die FPU-Multimediaeinheit **40** ist ausgebildet, Fließkomma- und Multimediablebefehle auszuführen.

**[0056]** Die Lade/Schreibeinheit **36** ist ausgebildet, mit dem L1 D-Cache-Speicher **38** zu kommunizieren, um Speicheroperationen auszuführen. Eine Speicheroperation ist ein Datentransfer zwischen dem Prozessor **10** und einem externen Speicher. Die Speicheroperation kann ein expliziter Befehl sein oder kann ein impliziter Bereich eines Befehls sein, der auch Operationen enthält, die von den Funktionseinheiten **32** auszuführen sind. Die Ladespeicheroperationen geben einen Datentransfer von einem externen Speicher zu dem Prozessor **10** an, und Schreibspeicheroperationen spezifizieren einen Datentransfer von dem Prozessor **10** zu dem externen Speicher. Wenn ein Treffer für eine Speicheroperation in den L1 D-Cache-Speicher **38** erkannt wird, wird die Speicheroperation dann abgeschlossen, ohne dass auf den externen Speicher zugegriffen wird. Die Lade/Schreibeinheit **36** empfängt Adressen für Speicheroperationen von der Vorausschau/Zusammenführeinheit **24** (über eine vorrausschauende Adressberechnung) oder von den Adressenerzeugungseinheiten **34**. In einer Ausführungsform ist die Lade/Schreibeinheit **36** ausgebildet, bis zu drei Speicheroperationen pro Taktzyklus an dem L1 D-Cache-Speicher **38** auszuführen. Für diese Ausführungsform ist die Lade/Schreibeinheit **36** ausgebildet, bis zu 30 Lade/Schreibspeicheroperationen zu speichern, die noch nicht auf dem D-Cache-Speicher **38** zugegriffen haben. Die Ausführungsform kann ferner ausgebildet sein, um einen 96 Einträge-nichttrefferpuffer zur Speicherung von Ladespeicheroperationen zu speichern, die nicht den D-Cache-Speicher **38** treffen, und kann ferner einen 32 Einträgeschreibdatenpuffer aufweisen. Die Lade/Schreibeinheit **36** ist ausgebildet, eine Speicherabhängigkeitsprüfung zwischen den Lade- und Schreibspeicheroperationen auszuführen.

**[0057]** Der L1 D-Cache-Speicher **38** ist ein Hochgeschwindigkeitscachespeicher zur Datenspeicherung. Es kann eine beliebige Konfiguration für den L1 D-Cache-Speicher **38** verwendet werden, einschließlich einer teilassoziativen Konfiguration und einer direkt abgebildeten Konfiguration. In einer speziellen Ausführungsform ist der L1 D-Cache-Speicher **38** ein 128 KB Zweiwege-teilassoziativer Cache-Speicher mit 64 Bytezeilen. Der L1 D-Cache-Speicher **38** kann beispielsweise in 32 Bänken aus Cache-Speichern pro Weg eingeteilt sein. Zusätzlich kann der L1 D-Cache-Speicher **38** ein linear adressierter, physikalisch markierter Cache-Speicher sein, in welchem ein TLB ähnlich zu dem L1 I-Cache-Speicher **14** verwendet ist.

**[0058]** Die externe Schnittstelleneinheit **42** ist ausgebildet, Cache-Zeilen aus Befehlsbytes und Datenbytes in den Prozessor **10** in Reaktion auf Nichttreffer im Cache zu übertragen. Befehlscache-Zeilen werden zu der Vor-decodierungseinheit **12** geleitet, und Datencache-Zeilen werden zu dem L1 D-Cache-Speicher **38** geführt. Ferner ist die externe Schnittstelleneinheit **42** ausgebildet, Cache-Zeilen, die von dem L1 D-Cache-Speicher **38** in dem Speicher abgelegt werden, wenn die abgegebenen Cache-Zeilen modifiziert werden, an den Prozessor **10** zu übertragen. Wie in [Fig. 1](#) gezeigt ist, ist die externe Schnittstelleneinheit **42** ausgebildet, eine Verbindung mit einem externen L2 Cache-Speicher über die L2-Schnittstelle **44** sowie als Schnittstelle mit einem Computersystem über die Busschnittstelle **46** zu dienen. In einer Ausführungsform umfasst die Busschnittstelleneinheit **46** eine EV/6-Schnittstelle.

**[0059]** [Fig. 2](#) ist eine Blockansicht einer Ausführungsform einer Abhol/Sucheinheit **18**. Andere Ausführungsformen sind möglich und hierin mit eingeschlossen. Wie in [Fig. 2](#) gezeigt ist, umfasst die Abhol/Sucheinheit **18** eine Abholsteuereinheit **50**, mehrere "nächste Wahl"-Blöcke **52a** bis **52c**, einen Befehlauswahlmultiplexer (mux) **54**, einen Befehlsabtaster bzw. Sucher **56**, einen Verzweigungsabtaster bzw. Sucher **58**, eine Verzweigungshistorientabelle **60**, einen Verzweigungsauswahlmux **62**, einen Rücksprungstapel **64**, einen indirekten Adressencache-Speicher **66** und eine Vorwärtszusammenführenheit **68**. Die Abholsteuereinheit **50** ist mit dem L1 I-Cache-Speicher **14**, dem L0 I-Cache-Speicher **16**, dem indirekten Adressencachespeicher **66**, den Rücksprungstapel **64**, der Verzweigungshistorientabelle **60**, dem Verzweigungssucher **58** und dem Befehlauswahlmux **54** verbunden. Der „nächste Wahl“-Block **52a** ist mit dem L1 I-Cache-Speicher **14** verbunden, während die „nächste Wahl“-Blöcke **52b** bis **52c** mit dem L0 I-Cache-Speicher **16** verbunden sind. Jeder „nächste Wahl“-Block **52** ist mit einem Befehlauswahlmux **54** verbunden, der ferner mit dem Verzweigungssucher **58** und dem Befehlssucher **56** verbunden ist. Der Befehlssucher **56** ist mit der Befehlswarteschlange **20** verbun-

den. Der Verzweigungssucher **58** ist mit der Verzweigungshistorientabelle **60**, dem Rückkehrstapel **64** und dem Verzweigungsauwahlmux **68** verbunden. Der Verzweigungsauwahlmux **62** ist mit dem indirekten Adressencache-Speicher **66** verbunden. Die Verzweigungshistorientabelle **60** und der Verzweigungssucher **58** sind mit der Weiterleitungszusammenföhreinheit **68** verbunden, die mit der Befehlswartschlange **20** verbunden ist.

**[0060]** Die Abholsteuereinheit **50** empfängt eine Verzweigungsvorhersageinformation (einschließlich der Zieladressen und der Vorhersage über durchgeführt/nicht durchgeführt) von dem Verzweigungssucher **58**, der Verzweigungshistorientabelle **60**, dem Rücksprungstapel **64** und dem indirekten Cache-Speicher **66**. In Reaktion auf die Verzweigungsvorhersageinformation erzeugt die Abholsteuereinheit **50** Abholadressen für den L1 I-Cache-Speicher **16** und eine Abhol- oder Vorabholadresse für den L1 I-Cache-Speicher **14**. In einer Ausführungsform erzeugt die Abholsteuereinheit **50** zwei Abholadressen für den L0 I-Cache-Speicher **16**. Die erste Abholadresse wird als die Zieladresse entsprechend dem ersten Verzweigungsbefehl, der von dem Verzweigungssucher **58** erkannt wird (wenn es welche gibt), ausgewählt. Die zweite Abholadresse ist die sequenzielle Adresse zu der Abholadresse, die in dem vorhergehenden Taktzyklus ausgewählt wurde, d. h. die Abholadresse, die dem Abschnitt entspricht, der von dem Befehlauswahlmux **54** ausgewählt wurde.

**[0061]** Der L0 I-Cache-Speicher **14** liefert die Cache-Zeilen (und die Vordecodierungsinformation), die den beiden Abholadressen entspricht, sowie die Cache-Zeilen (und die Vordecodierungsinformation), die sequenziell zu jeder dieser Cache-Zeilen sind, um die „nächste Wahl“-Blöcke **52b** bis **52c** auszuwählen. Insbesondere empfängt der „nächste Wahl“-Block **52b** die sequenzielle Cache-Zeile, die der sequenziellen Adresse entspricht, und die nächste inkrementierte Cache-Zeile zu der sequenziellen Cache-Zeile. Der „nächste Wahl“-Block **52c** empfängt die Zielcache-Zeile entsprechend der Zieladresse sowie die Cache-Zeile, die der Zielcachezeile folgt. Zusätzlich empfangen die „nächste Wahl“-Blöcke **52b** bis **52c** den Offsetbereich der entsprechenden Abholadresse. Die „nächste Wahl“-Blöcke **52b** bis **52c** wählen jeweils einen Abschnitt aus Befehlsbytes (und entsprechende Vordecodierungsinformation) aus dem empfangenen Cache-Zeilen aus, wobei mit den Abschnittsteil begonnen wird, der den Offsetbereich der entsprechenden Abholadresse beinhaltet. Da der Offsetbereich jeder Abholadresse irgendwo innerhalb der Cache-Zeile beginnen kann, kann der ausgewählte Abschnitt Teile der abgeholt Cache-Zeile und der sequenziellen Cache-Zeile in Bezug auf die abgeholt Cache-Zeile enthalten. Somit werden sowohl die abgeholt Cache-Zeile als auch die nachfolgende Cache-Zeile von den „nächste Wahl“-Blöcken **52b** bis **52c** empfangen.

**[0062]** In ähnlicher Weise erhält der „nächste Wahl“-Block **52a** eine vorabgeholt Cache-Zeile (und entsprechende Vordecodierungsinformation) aus dem L1 I-Cache-Speicher **14** und wählt daraus einen Befehlsabschnitt aus. Da eine einzelne Cache-Zeile von dem L1 I-Cache-Speicher **14** vorabgeholt wird, kann der daraus ausgewählte Abschnitt mehr als einen vollständigen Abschnitt enthalten, wenn der Offsetbereich der Vorabholungssadresse in der Nähe des Endes der Cache-Zeile liegt. Zu beachten ist, dass die Abholcache-Zeilen aus dem L0 I-Cache-Speicher **16** in dem gleichen Taktzyklus mit der entsprechenden Adresse von der Abholsteuereinheit **50** erzeugt werden, jedoch kann die Vorabholungscachezeile um einen Taktzyklus auf Grund der größeren Größe und der geringeren Zugriffszeit des L1 I-Cache-Speichers **14** verzögert werden. Zusätzlich zu dem Bereistellen der vorabgeholt Cache-Zeile für den „nächste Wahl“-Block **52a** liefert der L1 I-Cache-Speicher **14** die vorabgeholt Cache-Zeile an den L0 I-Cache-Speicher **16**. Wenn die vorabgeholt Cache-Zeile bereits in dem L0 I-Cache-Speicher **16** gespeichert ist, kann der L0 I-Cache-Speicher **16** die vorabgeholt Cache-Zeile verwerfen. Wenn jedoch die vorabgeholt Cache-Zeile noch nicht in dem L0 I-Cache-Speicher **14** abgelegt ist, wird die vorabgeholt Cache-Zeile in dem L0 I-Cache-Speicher **16** gespeichert. Auf diese Weise werden Cache-Zeilen, auf die aktuell zugegriffen wird, in den L0 I-Cache-Speicher **16** gebracht, um darin einen schnellen Zugriff zu ermöglichen. Gemäß einer beispielhaften Ausführungsform umfasst der L0 I-Cache-Speicher **16** eine vollständig assoziative Cache-Struktur mit 8 Einträgen. Ein vollständig assoziative Struktur kann auf Grund der relativ geringen Anzahl an Cache-Zeilen, die in dem L0 I-Cache-Speicher **16** enthalten sind, eingesetzt werden. In anderen Ausführungsformen werden andere Organisationsformen (beispielsweise teilassoziativ oder direkt abgebildet) eingesetzt.

**[0063]** Die Abholsteuereinheit **50** wählt den Befehlsabschnitt, der von einem der „nächste Wahl“-Blöcke **52** ausgewählt wird, in Reaktion auf die Verzweigungsvorhersageinformation aus, indem der Befehlauswahlmux **54** angesteuert wird. Wie nachfolgend detaillierter beschrieben ist, empfängt die Abholsteuereinheit **50** (in der vorliegenden Ausführungsform) Zieladressen von dem Verzweigungssucher **58**, dem Rücksprungstapel **64** und dem indirekten Adressencache-Speicher **66** früh in dem Taktzyklus und zumindest einen Teil des Operationscodierungsbytes des ersten Verzweigungsbefehls, der von dem Verzweigungssucher **58** erkannt wird. Die Abholsteuereinheit **50** decodiert den Bereich des Operationscodierungsbytes, um die Zieladresse, die aus dem L0 I-Cache-Speicher **16** abzuholen ist, von den diversen Zieladressquellen auszuwählen, und liefert die ausgewählte Zieladresse zu dem L0 I-Cache-Speicher **16**. Parallel dazu wird die sequenzielle Adresse für die Ab-

holadresse, die in dem vorhergehenden Taktzyklus ausgewählt wurde (entweder die Zieladresse oder die nachfolgende Adresse aus dem vorhergehenden Taktzyklus, abhängig von der Verzweigungsvorhersage aus dem vorhergehenden Taktzyklus) berechnet und dem L0 I-Cache-Speicher **16** zugeführt. Die Verzweigungsvorhersageinformation (d. h. ausgeführt oder nicht ausgeführt) wird von der Verzweigungshistorientabelle **60** spät in dem Taktzyklus bereitgestellt. Wenn der Verzweigungsbefehl, der aus dem L0 I-Cache-Speicher **16** abgeholten Zieladresse entspricht, als durchgeführt vorhergesagt wird, dann wählt die Abholsteuereinheit **50** den Befehlsabschnitt aus, der von dem „nächste Wahl“-Block **52c** bereitgestellt wird. Wenn andererseits der Verzweigungsbefehl als nicht durchgeführt vorhergesagt wird, dann wird der Befehlsabschnitt, der von dem „nächste Wahl“-Block **52b** ausgewählt wurde, ausgewählt. Der Befehlsabschnitt, der von dem „nächste Wahl“-Block **52a** bereitgestellt wird, wird ausgewählt, wenn eine vorhergesagte Abholadresse nicht den L0 I-Cache-Speicher **16** in einem vorhergehenden Taktzyklus betraf und aus dem L1 I-Cache-Speicher **14** abgeholt wurde. Ferner wird der Befehlsabschnitt aus dem L1 I-Cache-Speicher **14** ausgewählt, wenn der Befehl in Reaktion auf einen Verzweigungsbefehl mit einer 32 Bit-Verschiebung oder einer indirekten Zieladressenerzeugung ausgeführt wurde oder ein L0 I-Cache-Speichernichttreffer abgeholt wurde.

**[0064]** Der ausgewählte Befehlsabschnitt wird dem Befehlssucher **56** und dem Verzweigungssucher **58** zugeführt. Der Befehlssucher **56** sondiert die Vordecodierungsinformation entsprechend den ausgewählten Befehlsabschnitt, um Befehle innerhalb des Befehlsabschnitts zu erkennen. Insbesondere sondiert in einer Ausführungsform der Befehlssucher **56** die Startbits, die jedem Abschnittsteil entsprechen, parallel ab und erkennt bis zu 5 Befehle innerhalb jedes Teilabschnitts. Es werden Zeiger zu den erkannten Befehlen (Offsetwerte innerhalb des Teilabschnitts) erzeugt. Die Zeiger, Befehlsbytes und Adressen (eine pro Teilabschnitt) werden von dem Befehlssucher **56** zu der Befehlswarteschlange **20** übermittelt. Wenn ein spezieller Teilabschnitt mehr als 5 Befehle enthält, wird die Information, die den Teilabschnitten entspricht, die auf den speziellen Teilabschnitt folgt, als unzulässig erklärt, und der spezielle Teilabschnitt und die nachfolgenden Teilabschnitte werden während des nächsten Taktzyklus erneut abgesucht.

**[0065]** Der Verzweigungssucher **58** sondiert den Befehlsabschnitt parallel mit dem Befehlssucher **56**. Der Verzweigungssucher **58** sucht die Startbits und die Steuertransferbits des Befehlsabschnitts, um die ersten beiden Verzweigungsbefehle innerhalb des Befehlsabschnitts zu erkennen. Wie zuvor beschrieben ist, wird ein Verzweigungsbefehl durch das gesetzte Steuertransferbit, das dem Startbyte eines Befehls entspricht (wie dies durch das Startbit gekennzeichnet ist) erkannt. Beim Auffinden des ersten der beiden Verzweigungsbefehle nimmt der Verzweigungsasucher **58** an, dass die Befehle relative Verzweigungsbefehle sind und wählt die entsprechenden codierten Zieladressen aus den Befehlsbytes aus, die auf das Startbyte des Verzweigungsbefehls folgen. Bei Ausführungsformen, in denen der x86-Befehlssatz verwendet ist, wird eine 9-Bit-Zieladresse (das Verschiebungsbyte sowie das entsprechende Steuertransferbit) ausgewählt, und es wird auch eine 32-Bit-Zieladresse ausgewählt. Ferner wird mindestens ein Teil des Operationscodierungsbytes, das von den Start- und Steuertransferbits gekennzeichnet ist, ausgewählt. Die Zieladressen und die Operationscodierungsbytes werden der Abholsteuereinheit **50** zugeführt, um beim Auswählen einer Zieladresse zum Abholen aus dem L0 I-Cache-Speicher **16** zu dienen. Die Abholadressen jedes Verzweigungsbefehls (die aus der Abholadresse des Teilabschnitts, der jeden Verzweigungsbefehl enthält und aus der Position des Verzweigungsbefehls innerhalb des Teilabschnitts bestimmt) werden zu der Verzweigungshistorientabelle **60** geleitet, um eine „durchgeführt/nicht durchgeführt“ Vorhersage entsprechend jedem Verzweigungsbefehl auszuwählen. Ferner werden die Abholadressen, die jedem Verzweigungsbefehl entsprechen, zu dem Verzweigungsauwahlmix **62** geführt, und dann weiter zu dem indirekten Adressencache-Speicher **66** geführt. Die Zieladresse jedes Verzweigungsbefehls wird zu der Weiterleitungszusammenführeinheit **68** geführt. Gemäß einer Ausführungsform ist der Verzweigungssucher **58** ausgebildet, jeden Teilabschnitt parallel nach den ersten beiden Verzweigungsbefehlen abzusuchen und dann das Suchergebnis zu kombinieren, um die ersten beiden Verzweigungsbefehle innerhalb des Abschnitts auszuwählen.

**[0066]** Der Verzweigungssucher **58** kann ferner ausgebildet sein, zu bestimmen, ob ein UnterROUTINENAUFRUF-Befehl während eines Taktzyklus erkannt wird. Der Verzweigungssucher **58** kann die Abholadresse des nächsten Befehls, der auf den erkannten UnterROUTINENAUFRUF-Befehl folgt, zum RÜCKSPRUNGSTAPEL **64** zur Speicherung weiterleiten.

**[0067]** Wenn in einer Ausführungsform mehr als zwei Verzweigungsbefehle innerhalb eines Abschnitts vorhanden sind, wird der Abschnitt während eines nachfolgenden Taktzyklus erneut abgesucht, um den nachfolgenden Verzweigungsbefehl zu ermitteln.

**[0068]** Die Abholadressen der erkannten Verzweigungsbefehle werden der Verzweigungshistorientabelle **60** zugeführt, um eine „durchgeführt/nicht durchgeführt“ Vorhersage für jeden Befehl zu bestimmen. Die Verzwei-

gungshistorientabelle **60** umfasst mehrere „durchgeführt/nicht durchgeführt“ Vorhersageelemente, die dem zuvor erkannten Verhalten der Verzweigungsbefehle entsprechen. Eines der Vorhersageelemente wird durch Beibehalten einer Historie der jüngsten Vorhersagen ausgewählt und diese jüngsten Vorhersagen werden mit einem Teil der Abholadressen, die dem Verzweigungsbefehlen entsprechen, durch eine exklusiv-Oder-Funktion verknüpft. Die am wenigsten aktuelle (älteste) Vorhersage wird mit dem signifikantesten Bit innerhalb des Bereichs der Abholadresse durch die exklusiv-Oder-Funktion verknüpft, usw., bis zu der aktuellsten Vorhersage, die mit dem wenigsten signifikanten Bit innerhalb des Bereichs der Abholadresse mittels der exklusiv-Oder-Funktion verknüpft wird. Da zwei Vorhersageelemente pro Taktzyklus ausgewählt werden, hängt das Vorhersageelement, das dem zweiten Verzweigungsbefehl entspricht, von der Vorhersage des ersten Verzweigungsbefehls ab (für die exklusiv-Oder-Verknüpfung mit dem am wenigsten signifikanten Bit der entsprechenden Abholadresse). Die Verzweigungshistorientabelle **60** liefert das zweite Verzweigungselement durch Auswählen sowohl der Verzweigungselemente, die ausgewählt werden könnten (d. h. das Vorhersageelement, das ausgewählt würde, wenn der erste Verzweigungsbefehl als nicht genommen vorhergesagt wird und das Verzweigungselement, das ausgewählt würde, wenn der erste Verzweigungsbefehl als durchgeführt vorhergesagt wird), und durch Auswählen eines der beiden Vorhersageelemente auf der Grundlage der tatsächlichen Vorhersage, die für den ersten Verzweigungsbefehl ausgewählt wurde.

**[0069]** Die Verzweigungshistorientabelle **60** empfängt die Information hinsichtlich des Ausführens der Verzweigungsbefehle von den Funktionseinheiten **32a** bis **32d**. Die Historie der jüngsten Vorhersagen, die dem ausgeführten Verzweigungsbefehl entsprechen, sowie die Abholadresse des ausgeführten Verzweigungsbefehls werden bereitgestellt, um ein Verzweigungselement für die Aktualisierung auszuwählen, und es wird das „durchgeführt/nicht durchgeführt“ Ergebnis des ausgeführten Verzweigungsbefehls bereitgestellt. Die Verzweigungshistorientabelle **60** wählt das entsprechende Vorhersageelement aus und aktualisiert das Vorhersageelement auf der Grundlage des „durchgeführt/nicht durchgeführt“ Ergebnisses. In einer Ausführungsform speichert die Verzweigungshistorientabelle einen bimodalen Zähler. Der bimodale Zähler ist ein Sättigungszähler, der bei einem minimalen und maximalen Wert die Sättigungsgrenze erreicht (d. h. nachfolgende Dekrementierung des minimalen Wertes oder Erhöhungen des maximalen Wertes verursachen keine Änderung in dem Zähler). Jedes mal, wenn ein Verzweigungsbefehl genommen wird, wird der entsprechende Zähler erhöht und jedes mal wenn ein Verzweigungsbefehl nicht genommen wird, wird der entsprechende Zähler erniedrigt. Das signifikanteste Bit des Zählers gibt die „durchgeführt/nicht durchgeführt“ Vorhersage an (beispielsweise ist es gesetzt, wenn die Vorhersage durchgeführt wurde, oder nicht gesetzt, wenn dieser nicht durchgeführt wurde). In einer Ausführungsform speichert die Verzweigungshistorientabelle **60** 64K an Vorhersageelementen und bewahrt eine Geschichte der 16 jüngsten Vorhersagen. Bei jedem Taktzyklus werden die während des Taktzyklus ausgewählten Vorhersagen in die Geschichtstabelle geschoben und die ältesten Vorhersagen werden aus der Geschichtstabelle herausgeschoben.

**[0070]** Der Rücksprungstapel **64** wird verwendet, um die Rücksprungadressen entsprechend den erkannten Unterrountinaufrufbefehlen zu speichern. Der Rücksprungstapel **64** empfängt die Abholadresse eines Unterrountinaufrufbefehls von dem Verzweigungssucher **58**. Die Adresse des Bytes, das auf dem Aufrufbefehl folgt (die aus der Abholadresse berechnet wird, die von dem Rücksprungstapel **64** geliefert wird) wird oben auf dem Rücksprungstapel **64** angeordnet. Der Rücksprungstapel **64** liefert die Adresse, die oben auf dem Rücksprungstapel abgelegt ist, an die Abholsteuereinheit **50** zur Auswahl als eine Zieladresse, wenn ein Rücksprungbefehl von dem Verzweigungssucher **58** und der Abholsteuereinheit **50** erkannt wird. Auf diese Weise erhält jeder Rücksprungbefehl die Adresse als Zieladresse, die dem jüngsten erkannten Aufrufbefehl entspricht. Im Allgemeinen ist in dem x86-Befehlssatz ein Aufrufbefehl ein Steuertransferbefehl, der angibt, dass die sequenzielle Adresse nach dem Aufrufbefehl auf dem Stapel anzuordnen ist, der durch die x86-Architektur definiert ist. Ein Rücksprungbefehl ist ein Befehl, der die Zieladresse an dem Stapel auswählt. Im Allgemeinen werden Aufruf- und Rücksprungbefehle verwendet, um innerhalb einer Codierungssequenz in eine Unterroutine zu springen und diese zu verlassen. Durch Anordnen der Adressen, die den Aufrufbefehlen entsprechen, in dem Rücksprungstapel **64** und durch Verwenden der Adresse an der Oberseite des Rücksprungstapels **64** als die Zieladresse von Rücksprungbefehlen kann die Zieladresse des Rücksprungbefehls in korrekter Weise vorhergesagt werden. In einer Ausführungsform umfasst der Rücksprungstapel **64** 16 Einträge.

**[0071]** Der indirekte Adressencachespeicher **66** speichert die Zieladressen, die den vorhergehenden Ausführungen indirekter Verzweigungsbefehle entsprechen. Die Abholadresse, die einem indirekten Verzweigungsbefehl entspricht, und die Zieladresse, die dem Ausführen des indirekten Verzweigungsbefehls entspricht, werden von den Funktionseinheiten **32a** bis **32d** an dem indirekten Adressencache-Speicher **66** geliefert. Der indirekte Adressencache-Speicher **66** speichert die Zieladressen, die von den entsprechenden Abholadressen angegeben werden. Der indirekte Adressencache-Speicher **66** empfängt die Abholadresse, die von dem Verzweigungsauwahlmux **62** ausgewählt wird (in Reaktion auf das Erkennen eines indirekten Verzweigungsbe-

fehls), und wenn die Abholadresse ein Treffer in dem indirekten Adressencache-Speicher **66** ist, liefert dieser die entsprechende Zieladresse an die Abholsteuereinheit **50**. In einer Ausführungsform umfasst der indirekte Adressencache-Speicher **66** 32 Einträge.