(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-217776

(P2008-217776A)

(43) 公開日 平成20年9月18日(2008.9.18)

| (51) Int.Cl.                  | F 1             | テーマコード (参考) |

|-------------------------------|-----------------|-------------|

| <b>G06K 19/077</b> (2006.01)  | G06K 19/00      | 2 C005      |

| <b>H01L 21/3205</b> (2006.01) | H01L 21/88      | 5 B035      |

| <b>H01L 23/52</b> (2006.01)   | H01L 27/04      | 5 F033      |

| <b>H01L 21/822</b> (2006.01)  | H01L 27/04      | 5 F038      |

| <b>H01L 27/04</b> (2006.01)   | H01L 29/78 613Z | 5 F110      |

審査請求 未請求 請求項の数 10 O L (全 29 頁) 最終頁に続く

|              |                            |            |                                                                                    |

|--------------|----------------------------|------------|------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2008-26598 (P2008-26598) | (71) 出願人   | 000153878                                                                          |

| (22) 出願日     | 平成20年2月6日 (2008.2.6)       |            | 株式会社半導体エネルギー研究所                                                                    |

| (31) 優先権主張番号 | 特願2007-30858 (P2007-30858) |            | 神奈川県厚木市長谷398番地                                                                     |

| (32) 優先日     | 平成19年2月9日 (2007.2.9)       | (72) 発明者   | 小山 潤                                                                               |

| (33) 優先権主張国  | 日本国 (JP)                   |            | 神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                |

|              |                            | (72) 発明者   | 山崎 舜平                                                                              |

|              |                            |            | 神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                                |

|              |                            | F ターム (参考) | 2C005 NA08 NA09 NB01 PA01 PA03<br>PA09 PA27 RA09<br>5B035 BA03 BB09 CA01 CA08 CA23 |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】アンテナを複数設ける場合であっても、アンテナの配置が制限されず集積回路部とアンテナの接続不良を低減し、且つ通信機との通信距離の低減を防止することが可能な半導体装置を提供することを目的とする。

【解決手段】絶縁性を有する基体の第1の面上に薄膜トランジスタを具備する集積回路部を設け、当該集積回路部上に第1のアンテナを設け、基体の第2の面上に第2のアンテナを設け、第1のアンテナを集積回路部と接続させ、第2のアンテナを基体に形成された貫通孔を介して集積回路部と接続させ、第1のアンテナ及び第2のアンテナを集積回路部と重疊させて設ける。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する集積回路部と、

前記集積回路部上に設けられた第1のアンテナと、

前記基体の第2の面上に設けられた第2のアンテナとを有し、

前記第1のアンテナは、前記集積回路部と接続され、

前記第2のアンテナは、前記基体に形成された貫通孔を介して前記集積回路部と接続され、

前記第1のアンテナ及び前記第2のアンテナが前記集積回路部と重畠していることを特徴とする半導体装置。 10

**【請求項 2】**

絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する集積回路部と、

前記集積回路部上に設けられた第1のアンテナと、

基板上に設けられた第2のアンテナとを有し、

前記第1のアンテナは、前記集積回路部と接続され、且つ前記集積回路部と重畠して設けられ、

前記第2のアンテナは、前記基体に形成された貫通孔を介して前記集積回路部と接続され、 20

前記集積回路部の面積と前記基板の面積が概略同一であることを特徴とする半導体装置。

**【請求項 3】**

請求項2において、

前記基板は、前記基体の第2の面と接着していることを特徴とする半導体装置。

**【請求項 4】**

絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する第1の集積回路部及び第2の集積回路部と、

前記第1の集積回路部上及び前記第2の集積回路部上に設けられた第1のアンテナと、 30

前記基体の第2の面上に設けられた第2のアンテナとを有し、

前記第1のアンテナは、前記第1の集積回路部と接続され、

前記第2のアンテナは、前記基体に形成された貫通孔を介して前記第2の集積回路部と接続され、

前記第1のアンテナ及び前記第2のアンテナが前記第1の集積回路部及び前記第2の集積回路部と重畠していることを特徴とする半導体装置。

**【請求項 5】**

請求項4において、

前記第1の集積回路部と前記第2の集積回路部は、それぞれ送受信回路部を有していることを特徴とする半導体装置。 40

**【請求項 6】**

請求項1乃至請求項5のいずれか一項において、

前記第1のアンテナと前記第2のアンテナは、異なる周波数を受信することを特徴とする半導体装置。

**【請求項 7】**

絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する集積回路部と、

前記集積回路部上に設けられた第1のアンテナと、

前記基体の第2の面上に設けられた第2のアンテナと、

前記第1のアンテナの上方に設けられた第3のアンテナとを有し、

前記第1のアンテナは、前記集積回路部と接続され、前記第3のアンテナを介して情報 50

の送受信を行い、

前記第2のアンテナは、前記基体に形成された貫通孔を介して前記集積回路部と接続され、

前記第3のアンテナは、前記集積回路部と絶縁されたブースターアンテナであり、

前記第1のアンテナ、前記第2のアンテナ及び前記第3のアンテナが前記集積回路部と重畳していることを特徴とする半導体装置。

【請求項8】

絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する集積回路部と、

前記集積回路部上に設けられた第1のアンテナと、

10

第1の基板上に設けられた第2のアンテナと、

第2の基板上に設けられた第3のアンテナとを有し、

前記第1の基板は前記基体の第2の面と接着し、

前記第2の基板は、前記第1のアンテナの上方に設けられた絶縁膜と接着し、

前記第1のアンテナは、前記集積回路部と接続され、前記第3のアンテナを介して情報の送受信を行い、

前記第2のアンテナは、前記基体に形成された貫通孔を介して前記集積回路部と接続され、

前記第3のアンテナは、前記集積回路部と絶縁されたブースターアンテナであり、

20

前記集積回路部の面積と、前記第1の基板の面積及び前記第2の基板の面積が概略同一であることを特徴とする半導体装置。

【請求項9】

請求項7又は請求項8において、

前記第2のアンテナと前記第3のアンテナは、異なる周波数を受信することを特徴とする半導体装置。

【請求項10】

請求項2又は請求項8において、

前記集積回路部の面積は、 $9\text{ mm}^2 \sim 400\text{ mm}^2$ であることを特徴とする半導体装置。

【発明の詳細な説明】

30

【技術分野】

【0001】

本発明は、半導体装置に関する。特に電磁波を利用して無線通信を行う半導体装置に関する。

【背景技術】

【0002】

近年、電磁波を無線通信に利用した個体識別技術が注目を集めている。特に、無線通信によりデータの交信を行う半導体装置として、RFID (Radio Frequency

Identification) を利用した半導体装置 (RFIDタグ、IC (Integrated Circuit) タグ、ICチップ、RFタグ、無線タグ、電子タグとも呼ばれる) による個体識別技術が注目を集めている。RFIDを利用した半導体装置による個体識別技術は、個々の対象物の生産、管理等に役立てられ始めており、個人認証への応用に向けて実用化も進んでいる。また、最近では、複数の周波数を用いて情報の書き込み及び読み出しを行うタグが提案されている (例えば、特許文献1)。

【0003】

このような半導体装置は、メモリ回路等を備えた信号処理回路を有する集積回路部とアンテナとによって構成される。一般的に、半導体装置を構成する集積回路部を有するチップは、一枚のシリコン基板から複数個作製され、チップを微細に形成することによって低コスト化を図っている。例えば、特許文献2では、シリコンウェハに複数のチップを $0.5\text{ mm}$ 以下で作製することにより、経済的にも歩留まり的にも有利であることが記載されて

40

50

いる。

【特許文献1】特開2005-252853号公報

【特許文献2】特開2004-78991号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、複数のアンテナを有する半導体装置において、同一面上に複数のアンテナを設ける場合、アンテナの配置（レイアウト）の制限により、それぞれのアンテナの大きさや形状が制限され通信距離が短くなるおそれがある。また、複数のアンテナをそれぞれ別の基板上に設け、集積回路部が設けられた微小なチップに貼り合わせて設ける場合、接続不良が問題となる。

【0005】

一方、微小なチップとアンテナとの接続不良を防止するためにアンテナをチップに作り込んで内蔵（オンチップ化）することが考えられるが、微小なチップへのアンテナのオンチップ化はアンテナサイズが小さくなり通信距離が短くなる問題がある。接続不良の防止や通信距離の低減を防止するためにシリコン基板からなるチップのサイズを大きくすることが考えられるが、コストの増大やシリコンチップの破損が問題となる。

【0006】

本発明は、上記問題を鑑み、アンテナを複数設ける場合であっても、アンテナの配置が制限されず集積回路部とアンテナの接続不良を低減し、且つ通信機との通信距離の低減を防止することを目的の一とする。

【課題を解決するための手段】

【0007】

本発明の半導体装置は、集積回路部と複数のアンテナを有し、集積回路部のサイズを所望のアンテナサイズに近づけ、集積回路部とアンテナとの接続を容易にし、通信機との信号の送受信を確実に行うことができることを特徴とする。以下に、具体的な構成を示す。

【0008】

本発明の半導体装置の一は、絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する集積回路部と、集積回路部上に設けられた第1のアンテナと、基体の第2の面上に設けられた第2のアンテナとを有し、第1のアンテナは、集積回路部と接続され、第2のアンテナは、基体に形成された貫通孔を介して集積回路部と接続され、第1のアンテナ及び第2のアンテナが集積回路部と重畳している。

【0009】

本発明の半導体装置の一は、絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する集積回路部と、集積回路部上に設けられた第1のアンテナと、基板上に設けられた第2のアンテナとを有し、第1のアンテナは、集積回路部と接続され、且つ集積回路部と重畳して設けられ、第2のアンテナは、基体に形成された貫通孔を介して集積回路部と接続され、集積回路部の面積と基板の面積が概略同一であることを特徴としている。例えば、集積回路部の面積は、 $9\text{ mm}^2 \sim 400\text{ mm}^2$ で設けることができる。また、基板を基体の第2の面と接着させた構造としてもよい。

【0010】

本発明の半導体装置の一は、絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する第1の集積回路部及び第2の集積回路部と、第1の集積回路部上及び第2の集積回路部上に設けられた第1のアンテナと、基体の第2の面上に設けられた第2のアンテナとを有し、第1のアンテナは、第1の集積回路部と接続され、第2のアンテナは、基体に形成された貫通孔を介して第2の集積回路部と接続され、第1のアンテナ及び第2のアンテナが第1の集積回路部及び第2の集積回路部と重畳している。

【0011】

本発明の半導体装置の一は、絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する集積回路部と、集積回路部上に設けられた第1のアンテナと、基体の第2

10

20

30

40

50

の面上に設けられた第2のアンテナと、第1のアンテナの上方に設けられた第3のアンテナとを有し、第1のアンテナは、集積回路部と接続され、第3のアンテナを介して情報の送受信を行い、第2のアンテナは、基体に形成された貫通孔を介して集積回路部と接続され、第3のアンテナは、集積回路部と絶縁されたブースターアンテナであり、第1のアンテナ、第2のアンテナ及び第3のアンテナが集積回路部と重畳している。

【0012】

本発明の半導体装置の一は、絶縁性を有する基体の第1の面上に設けられ、薄膜トランジスタを具備する集積回路部と、集積回路部上に設けられた第1のアンテナと、第1の基板上に設けられた第2のアンテナと、第2の基板上に設けられた第3のアンテナとを有し、第1の基板は基体の第2の面と接着し、第2の基板は、第1のアンテナの上方に設けられた絶縁膜と接着し、第1のアンテナは、集積回路部と接続され、第3のアンテナを介して情報の送受信を行い、第2のアンテナは、基体に形成された貫通孔を介して集積回路部と接続され、第3のアンテナは、集積回路部と絶縁されたブースターアンテナであり、集積回路部の面積と、第1の基板の面積及び第2の基板の面積が概略同一であることを特徴としている。例えば、集積回路部の面積は、 $9\text{ mm}^2 \sim 400\text{ mm}^2$ で設けることができる。

10

【0013】

上記構成において、基体は、ガラス基板、石英基板、金属基板やステンレス基板、又はプラスチック基板等の基板や、酸化珪素(SiO<sub>x</sub>)膜、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x > y)膜、窒化珪素(SiN<sub>x</sub>)膜、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x > y)膜等の絶縁膜で設けることができる。

20

【0014】

本明細書において、「通信機」とは半導体装置と無線通信により情報の送受信を行う手段を有していればよく、例えば、情報を読み取るリーダや、読み取り機能及び書き込み機能を備えたリーダ／ライタ等が挙げられる。また、読み取り機能と書き込み機能の一方又は両方を備える携帯電話やコンピュータ等も含まれる。

20

【0015】

なお、本発明において、トランジスタは、様々な形態のトランジスタを適用させることができる。よって、適用可能なトランジスタの種類に限定はない。したがって、例えば、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を有する薄膜トランジスタ(TFT)などを適用することが出来る。また、インクジェットや印刷法を用いて作成したトランジスタなどを適用することが出来る。これらにより、室温における製造、真空度の低い状態における製造、大型基板を用いて製造することができる。また、マスク(レチクル)を用いなくても製造することができるため、トランジスタのレイアウトを容易に変更することができる。また、有機半導体やカーボンナノチューブを有するトランジスタ、その他のトランジスタを適用することができる。これらにより、曲げることが可能な基板上にトランジスタを形成することができる。なお、非単結晶半導体膜には水素またはハロゲンが含まれていてもよい。また、トランジスタが配置されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。

30

【0016】

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート電極が2個以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすると、チャネル領域が直列に接続されるような構成となるため、複数のトランジスタが直列に接続されたような構成となる。マルチゲート構造にすることにより、オフ電流の低減や、トランジスタの耐圧を向上させることによる信頼性の向上や、飽和領域で動作する時に、ドレインとソース間電圧が変化しても、ドレインとソース間電流があまり変化せず、フラットな特性にすることなどができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値が大きくなったり、空乏層ができやすくなってS値を小さくすることができる。チャネルの上下にゲート電極が配置され

40

50

ると、複数のトランジスタが並列に接続されたような構成となる。

【0017】

また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよい。また、チャネル領域が複数の領域に分かれてもよいし、複数のチャネル領域が並列に接続されていてもよいし、直列に接続されていてもよい。また、チャネル（もしくはその一部）にソース電極やドレイン電極が重なっていてもよい。チャネル（もしくはその一部）にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域があってもよい。LDD領域を設けることにより、オフ電流の低減や、トランジスタの耐圧を向上させることによる信頼性の向上や、飽和領域で動作する時に、ドレインとソース間電圧が変化しても、ドレインとソース間電流があまり変化せず、フラットな特性にすることができる。

10

【0018】

なお、本発明において、半導体装置とは半導体素子（トランジスタやダイオードなど）を含む回路を有する装置をいう。また、半導体特性を利用して機能しうる装置全般でもよい。

【発明の効果】

【0019】

本発明によれば、アンテナを複数設ける場合であっても、アンテナの配置が制限されず、所望の形状で設けることができる。また、アンテナと集積回路部との接続不良を低減し、通信機との通信距離の低減を防止することができる。

20

【発明を実施するための最良の形態】

【0020】

以下、本発明の実施の形態について図面を参照しながら説明する。ただし、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本実施の形態の記載内容に限定して解釈されるものではない。なお、本明細書中の図面において、同一部分または同様な機能を有する部分には同一の符号を付し、その説明は省略する場合がある。

30

【0021】

（実施の形態1）

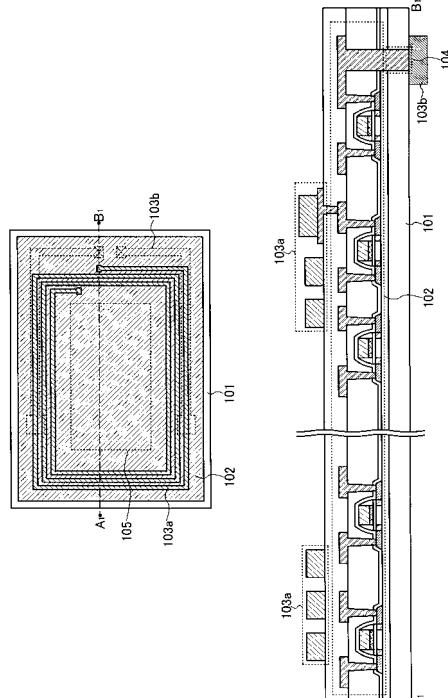

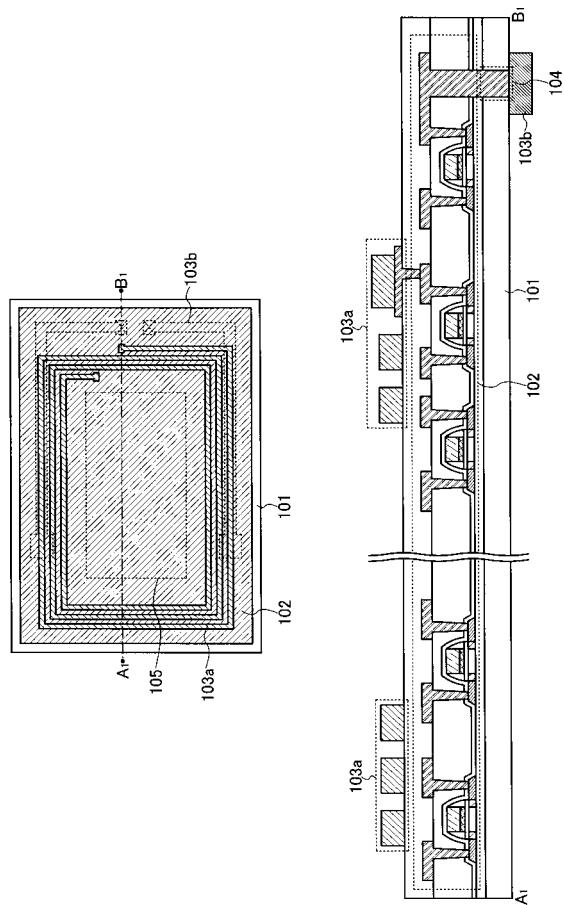

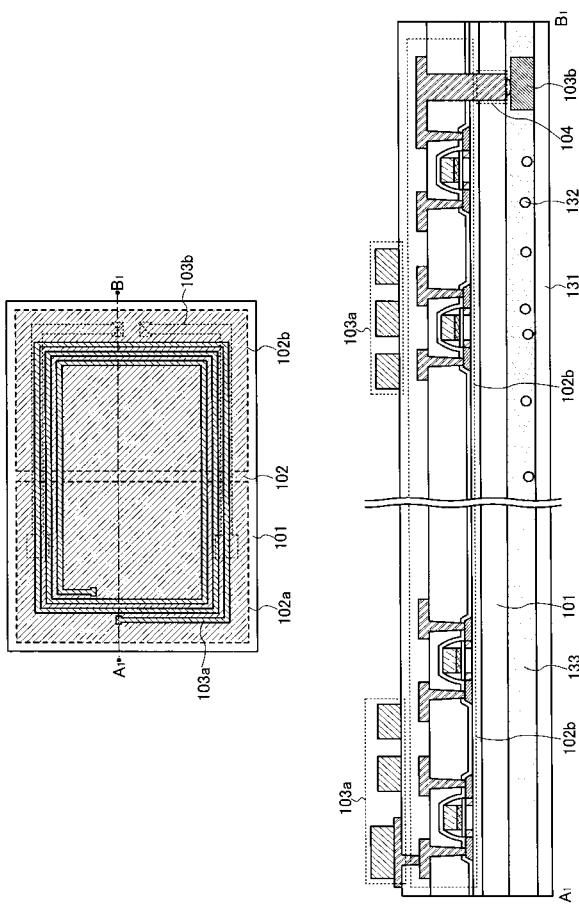

本発明の半導体装置は、異なる面に設けられた複数のアンテナを有し、少なくとも一つの面に設けられたアンテナは集積回路部上に作り込まれたオンチップアンテナであることを特徴とする。以下に、異なる2つの面に設けられた複数のアンテナを有し、一方の面に設けられたアンテナが集積回路と同一の工程で形成したオンチップアンテナである構成に関して図1を参照して説明する。なお、図1（A）は半導体装置の上面の模式図であり、図1（B）は図1（A）におけるA1-B1間の断面の模式図である。

【0022】

本実施の形態で示す半導体装置は、絶縁性を有する基体（ここでは、基板101）の第1の面（以下、「一方の面」とも記す）側に設けられた集積回路部102と、当該集積回路部102の上方に設けられた第1のアンテナ103aと、絶縁性を有する基体（基板101）の第2の面（以下、「他方の面」とも記す）側に設けられた第2のアンテナ103bを有している。第1のアンテナ103aは、集積回路部102の上方に作り込まれたオンチップアンテナであり、集積回路部102と重畳するように電気的に接続されている。第2のアンテナ103bは、絶縁性を有する基体（基板101）に設けられた貫通孔104を介して集積回路部102と電気的に接続するように設けられたアンテナである。

40

【0023】

また、図1に示す半導体装置は、第1のアンテナ103aと第2のアンテナ103bが異なる周波数を受信する構成とすることができます。例えば、第1のアンテナ103aをコイ

50

ル状に設け、第2のアンテナ103bを線状( L字型 )に設けることにより、半導体装置が異なる周波数を受信することができる。なお、半導体装置にコイル状のアンテナを設ける場合には、コイル状のアンテナの内側に位置する集積回路部102にトランジスタ等の素子を設けない領域105を設けた構成とすることが望ましい。領域105を設けることにより、コイル状に設けられた第1のアンテナ103aが電磁誘導により通信機と通信を行う際の磁界を通しやすくすることができる。

【0024】

基板101は、ガラス基板、石英基板、金属基板やステンレス基板、又はプラスチック基板等を用いる。このような基板であれば、シリコン(Si)基板と比較してその面積や形状に大きな制限はないため、例えば、1辺が1メートル以上あって、矩形状のものを用いれば、生産性を格段に向上させることができる。このような利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。従って、集積回路部102を大きく形成した場合( 例えば、面積が  $9\text{ mm}^2 \sim 400\text{ mm}^2$  )であってもシリコン基板と比較して、低コスト化が実現でき且つアンテナ103a、103bを大きく形成することが可能となり通信距離の拡大を図ることができる。また、基板101を可撓性を有する材料で設けることにより、商品の湾曲した面等に半導体装置を設けることができる。

10

【0025】

集積回路部102は、トランジスタ等の素子やこれらの素子を接続する配線等を有しており、大型の基板に複数形成され当該大型の基板を切り分けることにより得られるチップに設けられる。集積回路部102に設けられる素子は、例えば、非晶質シリコン、多結晶シリコン等に代表される非単結晶半導体膜を有する薄膜トランジスタで構成することができる。薄膜トランジスタを用いる場合、様々なメリットがある。例えば、シリコンウエハより切り出された単結晶シリコンを用いた半導体装置よりも低い温度で製造できるため、製造コストの削減、又は製造装置の大型化を図ることができる。また、製造装置を大きくできるため、大型基板上に製造できる。そのため、同時に多くの個数の半導体装置を製造できるため、低コストで製造できる。さらに、製造温度が低いため、耐熱性の弱い基板を用いることができる。そのため、安価なガラス基板上にトランジスタを製造できる。そして、ガラス基板は透明であるため、基板上のトランジスタを用いた半導体装置での光の透過を制御することが出来る。あるいは、トランジスタの膜厚が薄いため、トランジスタを構成する膜の一部は、光を透過させることができる。そのため、デザイン性の向上を図ることもできる。

20

【0026】

アンテナ103aは、スパッタリング法や、CVD法、スピンドルティング法などにより導電膜を形成した後、当該導電膜をパターニングして形成してもよいし、インクジェット法に代表される液滴吐出法又はスクリーン印刷法などにより形成してもよいし、アディティブ法またはセミアディティブ法等のめっき技術などを用いて形成してもよい。アンテナ103bは、アンテナ103aが形成された面と異なる面に基板101を介して集積回路部102と電気的に接続して設ければよい。

30

【0027】

図1では、基板101の他方の面にアンテナ103bを設けた例を示している。この場合、基板101の他方の面に液滴吐出法、スクリーン印刷法等により形成することができる。また、他にも、あらかじめアンテナ103bが設けられた基板と、絶縁性を有する基体( ここでは、基板101 )の他方の面とを接着性を有する樹脂により貼り合わせて( 接着させて )設けてもよい。貼り合わせて設ける場合には、アンテナ103bと集積回路部102bとの電気的な接続は、導電性粒子等を用いることができる。

40

【0028】

貫通孔104は、どのような形状( 矩形状、円状、橢円状等 )で設けてもよい。

【0029】

領域105は、集積回路部102において、トランジスタ等の素子や配線等が設けられていない領域であるが、必ずしも設ける必要はない。アンテナ103a又はアンテナ103

50

b の一方をコイル状とする場合等に磁界を通しやすくするために設けることが好ましい。

【0030】

図1に示したように、複数のアンテナを異なる面に設けることによって、個々のアンテナの形状を大きくすることができる。その結果、波長が長い電磁波の受信や通信距離の拡大が可能となる。また、個々のアンテナのレイアウトを自由に設計できるため、受信する電磁波の波長に応じて、様々な形状のアンテナの形成が可能となる。また、一方の面に設けられたアンテナをオンチップアンテナとすることによって、別々の基板上に形成されたアンテナをそれぞれ集積回路部に貼り合わせて設ける必要がないため、集積回路部とアンテナとの接続不良を防止することができる。

【0031】

また、貼り合わせ等により設けるアンテナ103bをアンテナ103aの上方に設けた構成としてもよいが、集積回路部102及びアンテナ103aが設けられた基板101の面と反対側の面に設けることによって、集積回路部102とアンテナ103bとの接続に用いられる配線がアンテナ103aの配置場所を制限することができないため好ましい。

【0032】

本実施の形態で示す半導体装置は、集積回路部102の面積Sを基板101の面積S'に近づけるように設ける。好ましくは、概略同じ面積( $S = S'$ )とする。このように設けることによって、集積回路部102と同一の工程で作り込まれるアンテナ103aを大きく形成することができるため、通信距離の拡大が可能となる。本実施の形態では、上述したように一枚の大型基板から集積回路部102が設けられたチップを複数個作製が可能であるため、集積回路部102を大きく設けた場合であってもS i 基板を用いた場合と比較して低コスト化を図ることができる。

【0033】

また、アンテナ103bの大部分(好ましくは全部)が集積回路部102と重なる構成としてもよい。このように設けることにより、大型基板に形成された複数の集積回路部102を切り分ける際に集積回路部102のサイズに応じて切り分けることができるため、1枚の大型基板から複数の半導体装置を得ることができる。また、大型基板に形成された複数の集積回路部102を切り分ける前にそれぞれの集積回路部102にアンテナ103bを貼り合わせることができると、工程を簡略化することができる。この場合、集積回路部102が、アンテナ103a及びアンテナ103bと重畠した構成となる。なお、アンテナ103bと集積回路部102を重ねて設ける場合であっても、集積回路部102の面積を大きく設けることにより、通信距離の低下を抑制することができる。

【0034】

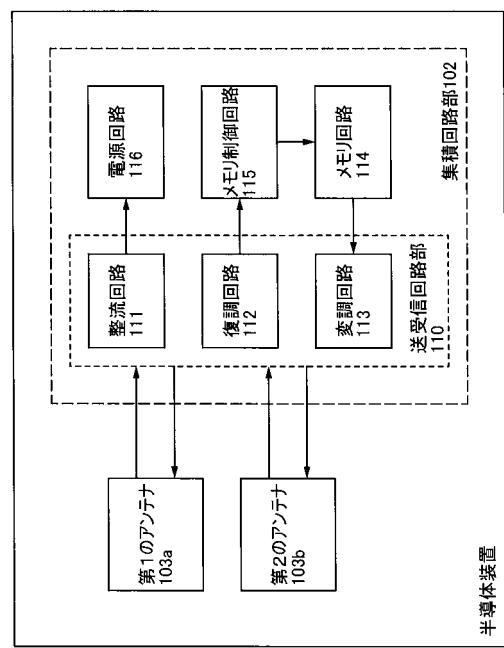

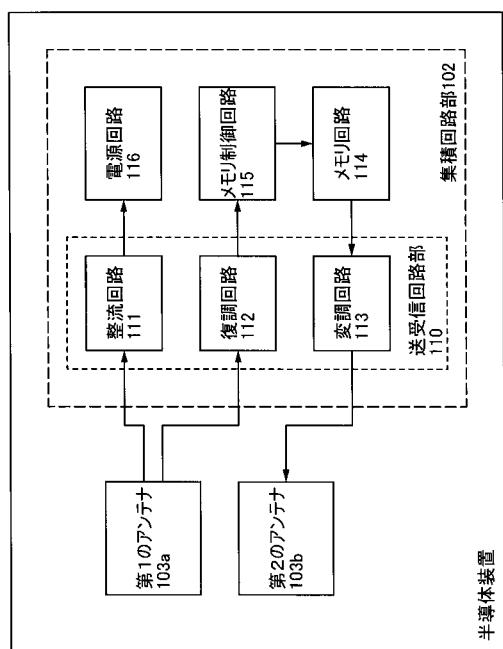

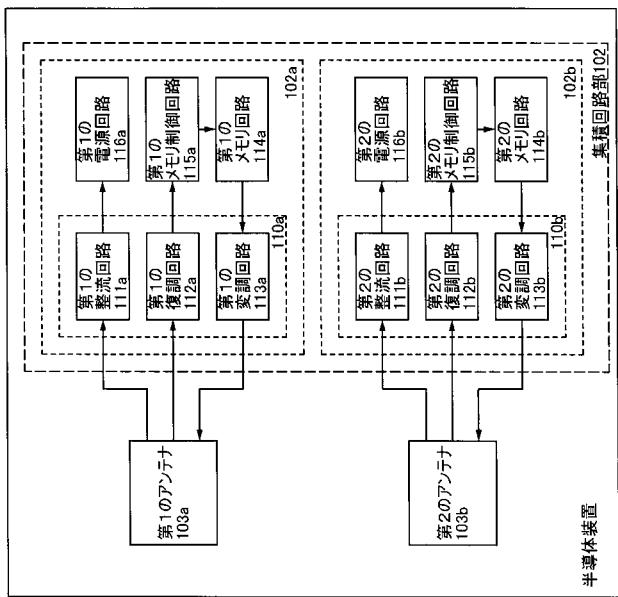

次に、本実施の形態で示す半導体装置についてブロック図を参照して説明する。

【0035】

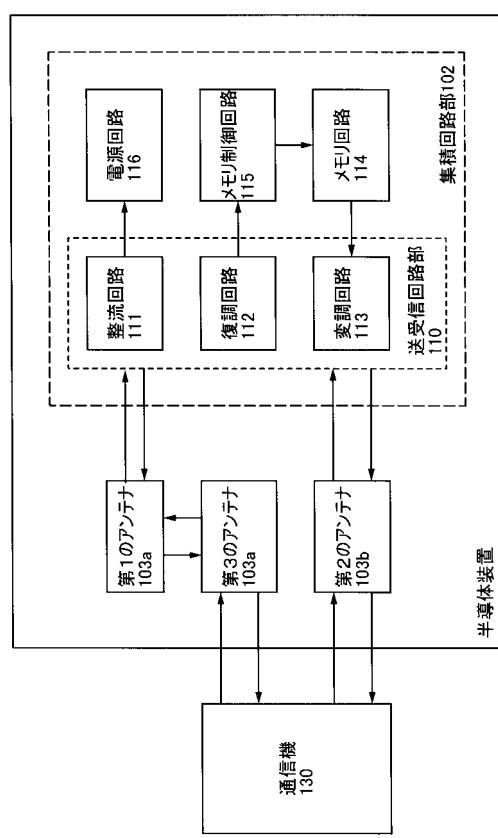

図2に示す半導体装置は、第1のアンテナ103a及び第2のアンテナ103bと、送受信回路部110と、メモリ回路114と、メモリ制御回路115と、電源回路116とを有している。また、送受信回路部110は、第1のアンテナ103a又は第2のアンテナ103bで受信した無線信号の電力を電源電位に変換する整流回路111、無線信号からデータを取り出す復調回路112、送受信回路部110よりデータを送信する変調回路113により構成されている。

【0036】

整流回路111は、一例として、第1のアンテナ103a又は第2のアンテナ103bで受信した交流信号を整流化及び平滑化して電源回路116に直流信号を供給する回路である。復調回路112は、一例として、第1のアンテナ103a又は第2のアンテナ103bで受信した交流信号をダイオード等により復調した信号に変換し、メモリ制御回路115に出力する回路である。変調回路113は、一例として、メモリ制御回路115により読み出されたデータをもとに、半導体装置の入力インピーダンスの変化に応じて、通信機から出力された搬送波を反射する強度を変化させてASK(振幅偏移; Amplitude shift keying)変調を行い、通信機にデータを送信すること

10

20

30

40

50

ができる。

【0037】

メモリ回路114は、集積回路部102のデータを保持する回路であり、一例として、不揮発性メモリに分類されるマスクROM、EEPROM、EEEPROM、フラッシュメモリ、強誘電体メモリなどを用いることができる。なお、半導体装置にバッテリーを設け、メモリ回路114に電力が定常に供給される構成であれば、揮発性メモリに分類されるDRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)を用いることもできる。

【0038】

メモリ制御回路115は、送受信回路部110より出力された復調信号に基づいてメモリ回路114からのデータの読み出しを制御する回路であり、一例として、薄膜トランジスタで構成される複数の論理回路を組み合わせてメモリ回路114からのデータの読み出しを制御する回路とすることができる。

【0039】

電源回路116は、一例として、薄膜トランジスタを用いて構成されるレギュレータにより、入力される信号を定電圧化する回路とすることができる。

【0040】

なお、半導体装置において、無線通信の信号の伝送方式は、電磁結合方式、電磁誘導方式(例えば、13.56MHz帯)、電界方式(例えば、UHF帯(860~960MHz帯)、2.45GHz帯等)を適用することができる。電磁結合方式を用いる場合には、第1のアンテナ103a、第2のアンテナ103bをコイル状に設け、電解方式を用いる場合には、第1のアンテナ103a、第2のアンテナ103bをモノポールアンテナ、ダイポールアンテナ、パッチアンテナ等にすればよい。もちろん、半導体装置において、電磁誘導方式と電界方式の双方により通信する構成としても良いし、電磁誘導方式又は電界方式の一方のみによって通信を行う構成としても良い。

【0041】

また、図2に示した半導体装置において、第1のアンテナ103aと第2のアンテナ103bの一方を受信専用のアンテナとし、他方を送信専用のアンテナとして設けた構成としてもよい(図3参照)。この場合、半導体装置は、情報の受信と送信を異なる波長の電磁波を利用して行うことができる。

【0042】

なお、本実施の形態では、半導体装置に2つのアンテナを設けた場合を示したが、これに限られず3つ以上のアンテナを設けた構成としてもよい。より複数のアンテナを設けた場合であっても、異なる2つの面に複数のアンテナを設けることによって、アンテナのレイアウトの制限を緩和することができる。

【0043】

本実施の形態は、本明細書の他の実施の形態で示した半導体装置の構成と組み合わせて実施することができる。

【0044】

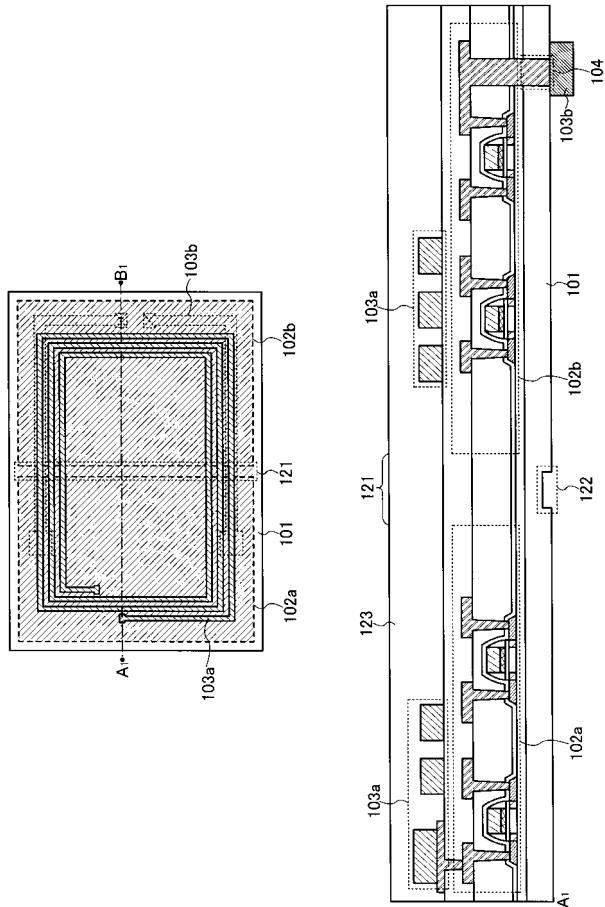

(実施の形態2)

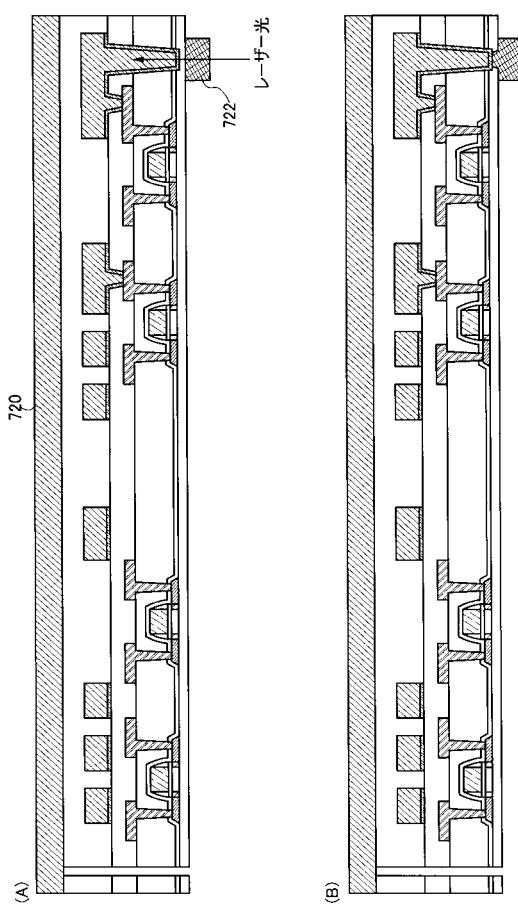

本実施の形態では、上記実施の形態と異なる半導体装置の構成に関して図面を参照して説明する。なお、図4(A)は半導体装置の上面の模式図であり、図4(B)は図4(A)におけるA1-B1間の断面の模式図である。

【0045】

本実施の形態で示す半導体装置は、基板101の第1の面(一方の面)側に設けられた集積回路部102と、当該集積回路部102の上方に設けられた第1のアンテナ103aと、基板101の第2の面(他方の面)側に設けられた第2のアンテナ103bを有している(図4参照)。集積回路部102は、第1の集積回路部102aと第2の集積回路部102bとを有し、それぞれ第1のアンテナ103a、第2のアンテナ103bと電気的に接続されている。

10

20

30

40

50

## 【0046】

第1のアンテナ103aは、第1の集積回路部102aと電気的に接続するように作り込まれたオンチップアンテナである。第2のアンテナ103bは、基板101に設けられた貫通孔104を介して第2の集積回路部102bと電気的に接続するように設けられたアンテナである。

## 【0047】

なお、図4では、アンテナ103bが設けられた基板131と絶縁性を有する基体(ここでは、基板101)の他方の面を、接着性を有する樹脂133を用いて貼り合わせた例を示している。また、アンテナ103bと第2の集積回路部102bは導電性粒子132により電気的に接続されている。もちろん、図1に示したように、基板101の他方の面にアンテナ103bを直接設けた構造としてもよい。

10

## 【0048】

また、第1の集積回路部102aは、第1の送受信回路部110aと、第1のメモリ回路114aと、第1のメモリ制御回路115aと、第1の電源回路116aとを有している。第1の送受信回路部110aは、第1のアンテナ103aで受信した無線信号の電力を電源電位に変換する第1の整流回路111a、無線信号からデータを取り出す第1の復調回路112a、第1の送受信回路部110aよりデータを送信する第1の変調回路113aにより構成されている(図5参照)。

## 【0049】

また、第2の集積回路部102bは、第2の送受信回路部110bと、第2のメモリ回路114bと、第2のメモリ制御回路115bと、第2の電源回路116bとを有している。第2の送受信回路部110bは、第2のアンテナ103bで受信した無線信号の電力を電源電位に変換する第2の整流回路111b、無線信号からデータを取り出す第2の復調回路112b、第2の送受信回路部110bよりデータを送信する第2の変調回路113bにより構成されている。

20

## 【0050】

本実施の形態で示す半導体装置は、上記実施の形態1で示した半導体装置と比較して複数のアンテナ毎に集積回路部を設ける点が異なっており、それぞれのアンテナの送受信を独立して制御することができる。従って、異なる周波数の無線信号をそれぞれのアンテナで同時に送受信することが可能となる。

30

## 【0051】

また、半導体装置にコイル状のアンテナを設ける場合には、コイル状のアンテナの内部に位置する第1の集積回路部102aと第2の集積回路部102bの一方又は両方にトランジスタ等の素子を設けない領域を設けてもよい。当該領域を設けることにより、コイル状に設けられたアンテナが電磁誘導により通信機と通信を行う際の磁界を通しやすくすることができる。

## 【0052】

また、基板101として可撓性を有する材料を用いた場合には、商品の湾曲した面等に半導体装置を設けることができる。この場合、第1の集積回路部102aと第2の集積回路部102bとの間に薄膜トランジスタ等の素子を設けない領域121を形成し、当該領域に選択的に応力を集中させる構造とすることによって、半導体装置を曲げた場合であっても素子の破損を防ぐことができる。例えば、領域121における半導体装置の表面の絶縁膜123と基板101(アンテナ103bを貼り合わせた場合には基板131)の一方又は両方(ここでは、基板101)に凹部122を設ける構成とすることができます(図6参照)。その結果、半導体装置が湾曲させた場合に選択的に領域121に応力を集中させることができ、曲面に沿って半導体装置を設けた場合であっても薄膜トランジスタ等の素子の破損を防ぐことができる。

40

## 【0053】

本実施の形態は、本明細書の他の実施の形態で示した半導体装置の構成と組み合わせて実施することができる。

50

## 【0054】

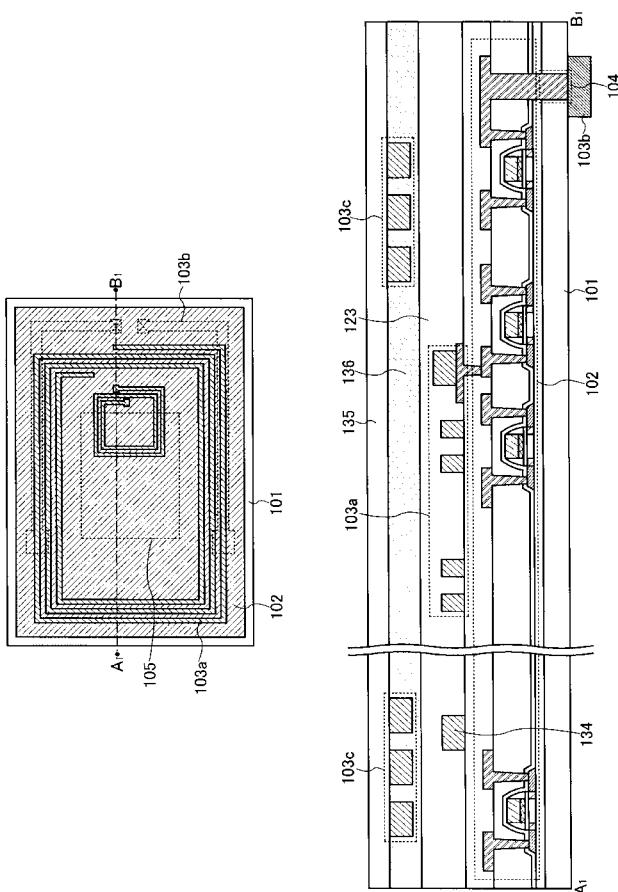

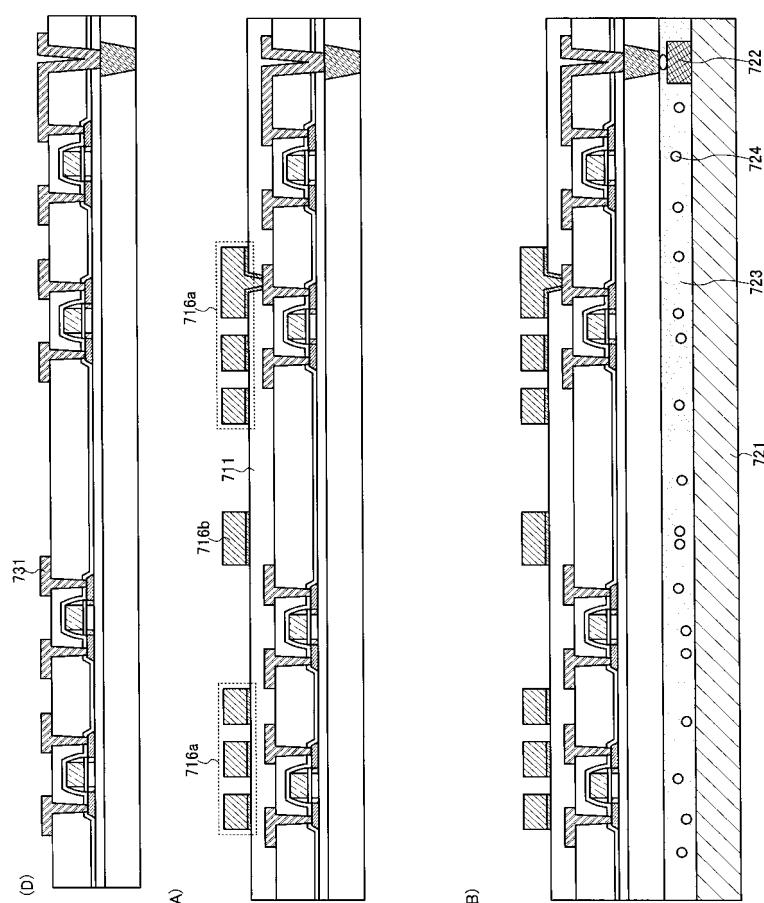

(実施の形態3)

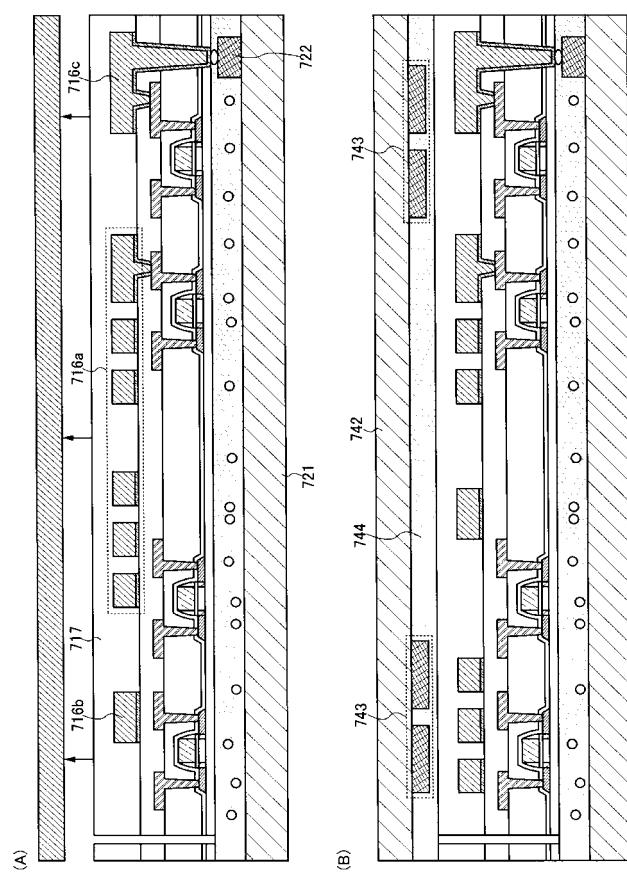

本実施の形態では、上記実施の形態と異なる半導体装置の構成に関して図面を参照して説明する。なお、図7(A)は半導体装置の上面の模式図であり、図7(B)は図7(A)におけるA1-B1間の断面の模式図である。

## 【0055】

本実施の形態で示す半導体装置は、基板101の第1の面(一方の面)側に設けられた集積回路部102と、当該集積回路部102の上方に設けられた第1のアンテナ103aと、当該第1のアンテナ103aの上方に設けられた第3のアンテナ103cと、基板の第2の面(他方の面)側に設けられた第2のアンテナ103bを有している(図7参照)。また、ここでは、第1のアンテナ103aと、集積回路部102を構成する薄膜トランジスタと電気的に接続される配線134を同一の面上に設けた場合を示している。

10

## 【0056】

第1のアンテナ103aは、集積回路部102と電気的に接続するように作り込まれたオンチップアンテナである。第2のアンテナ103bは、基板101に設けられた貫通孔104を介して集積回路部102と電気的に接続して設けられたアンテナである。第3のアンテナ103cは、第1のアンテナ103aの通信距離を拡大するために設けられたブースターアンテナである。

## 【0057】

図7では、アンテナ103cが設けられた基板135と絶縁膜123とを、接着性を有する樹脂136を用いて貼り合わせて設けた例を示している。ブースターアンテナとして機能する第3のアンテナ103cは、集積回路部102、第1のアンテナ103aと電気的に接続する必要がないため、絶縁状態となっている。従って、第3のアンテナ103cを貼り合わせて設ける場合であっても集積回路部102等と電気的な接続をとる必要がないため、接続不良が生じるおそれがない。

20

## 【0058】

なお、図7において、第2のアンテナ103bは基板101の他方の面に設けられた例を示しているが、図4に示すように第2のアンテナ103bが設けられた基板131と基板101の他方の面を貼り合わせて設けてもよい。

## 【0059】

本実施の形態で示す半導体装置は、第2のアンテナ103b又は第3のアンテナ103cを利用して通信機130との無線通信を行い、第3のアンテナ103cで受信した信号は第1のアンテナ103aとの電磁誘導により集積回路部102に供給される(図8参照)。なお、上記図5に示したように、第1のアンテナ103aと接続する第1の集積回路部と第2のアンテナ103bと接続する第2の集積回路部を設けた構成としてもよい。

30

## 【0060】

このように、第3のアンテナ103cを設けることによって、第1のアンテナ103aと集積回路部102を構成する配線134とを同一面上に設ける場合や、同一面上に複数のオンチップアンテナを設ける場合等の、第1のアンテナ103aのレイアウトが制限される場合であっても、通信距離の低下を抑制することができる。

40

## 【0061】

本実施の形態は、本明細書の他の実施の形態で示した半導体装置の構成と組み合わせて実施することができる。

## 【0062】

(実施の形態4)

本実施の形態では、上記実施の形態で示した半導体装置の作製方法の一例に関して、図面を参照して説明する。本実施の形態においては、半導体装置の集積回路部を薄膜トランジスタ等の素子で設ける場合について説明する。なお、本実施の形態では、薄膜トランジスタ等の素子を一度支持基板に設けた後、可撓性を有する基板に転置して半導体装置を作製する場合について説明する。また、本実施の形態では、一つの基板に集積回路部が設けら

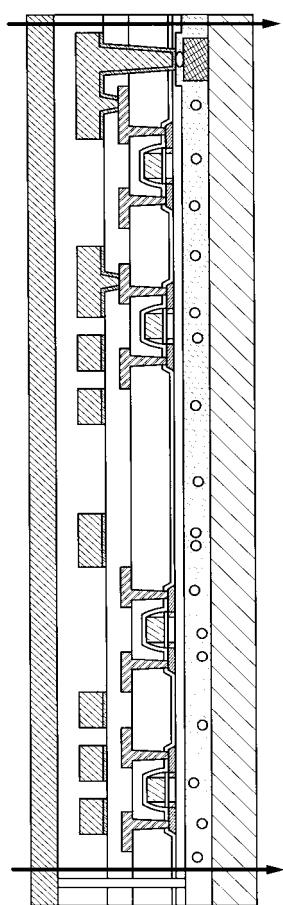

50

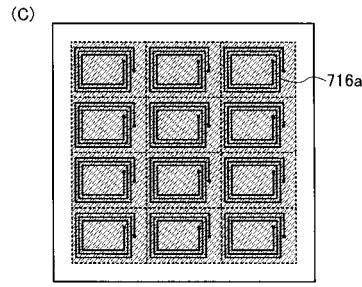

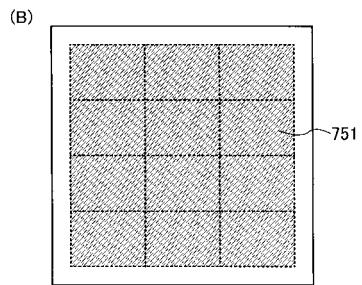

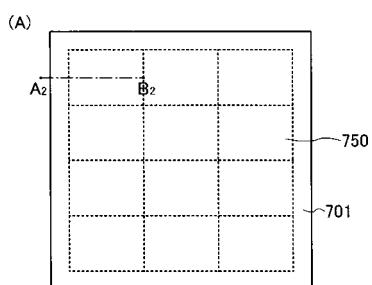

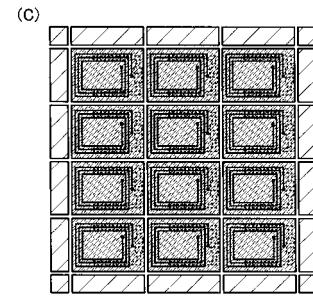

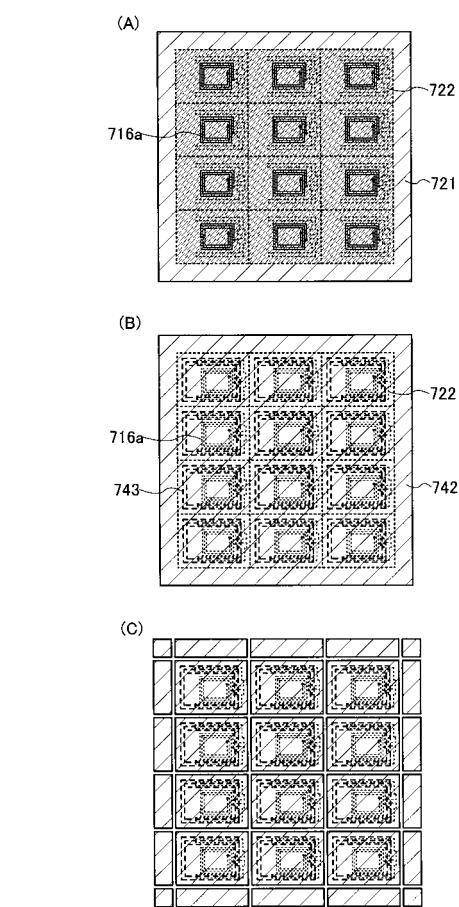

れた複数のチップ及びアンテナを形成し(ここでは、縦4×横3)、複数の半導体装置を作製する場合について説明する。以下の説明において、図9、図10は上面図の模式図であり、図11～図15は図9、図10におけるA-B間の断面図の模式図である。

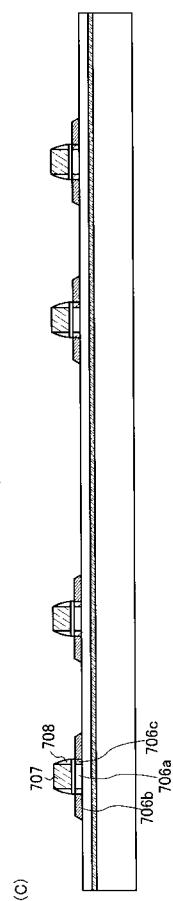

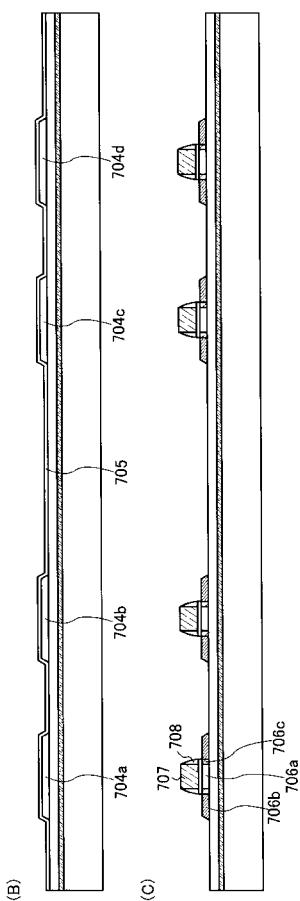

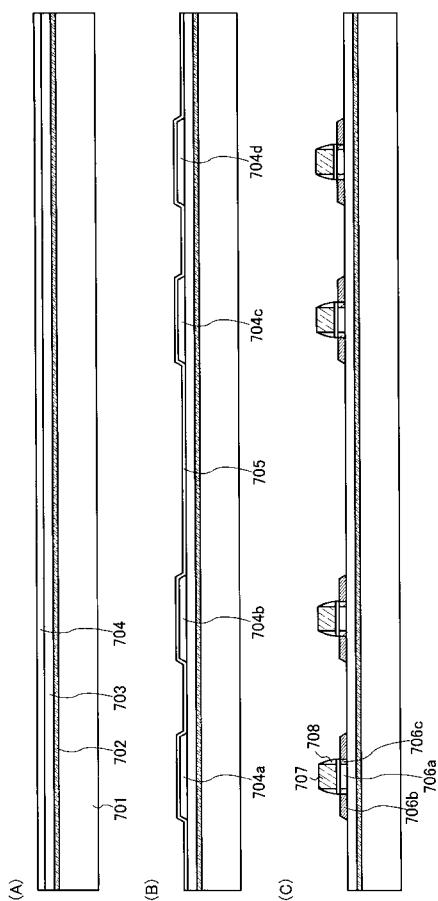

#### 【0063】

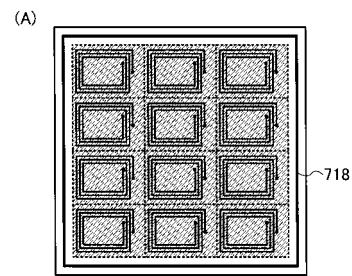

まず、基板701の一表面に剥離層702を形成し、続けて下地となる絶縁膜703および非晶質半導体膜704(例えば非晶質珪素を含む膜)を形成する(図9(A)、図11(A)参照)。剥離層702、絶縁膜703および非晶質半導体膜704は、連続して形成することができる。連続して形成することにより、大気に曝されないため不純物の混入を防ぐことができる。なお、以下の工程において、図9(A)に示された複数の領域750にそれぞれ半導体装置を構成する集積回路部及びアンテナが形成される。

10

#### 【0064】

基板701は、ガラス基板、石英基板、金属基板やステンレス基板、本工程の処理温度に耐えうる耐熱性があるプラスチック基板等を用いるとよい。このような基板であれば、その面積や形状に大きな制限はないため、例えば、1辺が1メートル以上あって、矩形状のものを用いれば、生産性を格段に向上させることができる。このような利点は、円形のシリコン基板を用いる場合と比較すると、大きな優位点である。従って、集積回路部を大きく形成した場合であっても、シリコン基板を用いる場合と比較して低コスト化を実現することができる。

#### 【0065】

なお、本工程では、剥離層702を基板701の全面に設けているが、必要に応じて、基板701の全面に剥離層を設けた後に、フォトリソグラフィ法により剥離層702を選択的に設けてもよい。また、基板701に接するように剥離層702を形成しているが、必要に応じて、基板701に接するように酸化珪素(SiO<sub>x</sub>)膜、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)膜、窒化珪素(SiN<sub>x</sub>)膜、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)膜等の絶縁膜を形成し、当該絶縁膜に接するように剥離層702を形成してもよい。

20

#### 【0066】

剥離層702は、金属膜や金属膜と金属酸化膜の積層構造等を用いることができる。金属膜としては、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)から選択された元素または前記元素を主成分とする合金材料若しくは化合物材料からなる膜を単層又は積層して形成する。また、これらの材料は、スパッタ法やプラズマCVD法等の各種CVD法等を用いて形成することができる。金属膜と金属酸化膜の積層構造としては、上述した金属膜を形成した後に、酸素雰囲気化またはN<sub>2</sub>O雰囲気下におけるプラズマ処理、酸素雰囲気化またはN<sub>2</sub>O雰囲気下における加熱処理を行うことによって、金属膜表面に当該金属膜の酸化物または酸化窒化物を設けることができる。また、金属膜を形成した後に、オゾン水等の酸化力の強い溶液で表面を処理することにより、金属膜表面に当該金属膜の酸化物又は酸化窒化物を設けることができる。

30

#### 【0067】

絶縁膜703は、スパッタ法やプラズマCVD法等により、珪素の酸化物または珪素の窒化物を含む膜を、単層又は積層で形成する。下地となる絶縁膜が2層構造の場合、例えば、1層目として窒化酸化珪素膜を形成し、2層目として酸化窒化珪素膜を形成するとよい。下地となる絶縁膜が3層構造の場合、1層目の絶縁膜として酸化珪素膜を形成し、2層目の絶縁膜として窒化酸化珪素膜を形成し、3層目の絶縁膜として酸化窒化珪素膜を形成するとよい。または、1層目の絶縁膜として酸化窒化珪素膜を形成し、2層目の絶縁膜として窒化酸化珪素膜を形成し、3層目の絶縁膜として酸化窒化珪素膜を形成するとよい。下地となる絶縁膜は、基板701からの不純物の侵入を防止するプロッキング膜として機能する。

40

#### 【0068】

50

半導体膜704は、スパッタ法、LPCVD法、プラズマCVD法等により、25～200nm（好ましくは30～150nm）の厚さで形成する。半導体膜704としては、例えば、非晶質珪素膜を形成すればよい。

#### 【0069】

次に、半導体膜704にレーザー光を照射して結晶化を行う。なお、レーザー光の照射と、RTA又はファーネスアーナー炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とを組み合わせた方法等により半導体膜704の結晶化を行ってもよい。その後、得られた結晶質半導体膜を所望の形状にエッティングして、結晶質半導体膜704a～704dを形成し、当該半導体膜704a～704dを覆うようにゲート絶縁膜705を形成する（図11（B）参照）。

10

#### 【0070】

結晶質半導体膜704a～704dの作製工程の一例を以下に簡単に説明すると、まず、プラズマCVD法を用いて、膜厚50～60nmの非晶質半導体膜（例えば、非晶質珪素膜）を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体膜上に保持させた後、非晶質半導体膜に脱水素化の処理（500、1時間）と、熱結晶化の処理（550、4時間）を行って結晶質半導体膜を形成する。その後、レーザー発振器からレーザー光を照射し、フォトリソグラフィ法を用いることによって結晶質半導体膜704a～704dを形成する。なお、結晶化を助長する金属元素を用いる熱結晶化を行わずに、レーザー光の照射だけで非晶質半導体膜の結晶化を行ってもよい。

#### 【0071】

レーザー発振器としては、連続発振型のレーザービーム（CWレーザービーム）やパルス発振型のレーザービーム（パルスレーザービーム）を用いることができる。ここで用いることができるレーザービームは、Arレーザー、Krレーザー、エキシマレーザーなどの気体レーザー、単結晶のYAG、YVO<sub>4</sub>、フォルステライト（Mg<sub>2</sub>SiO<sub>4</sub>）、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶（セラミック）のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザー、ガラスレーザー、ルビーレーザー、アレキサンドライトレーザー、Ti：サファイアレーザー、銅蒸気レーザーまたは金蒸気レーザーのうち1種または複数種から発振されるものを用いることができる。このようなレーザービームの基本波、及びこれらの基本波の第2高調波から第4高調波のレーザービームを照射することで、大粒径の結晶を得ることができる。例えば、Nd：YVO<sub>4</sub>レーザー（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を用いることができる。このときレーザーのパワー密度は0.01～100MW/cm<sup>2</sup>程度（好ましくは0.1～10MW/cm<sup>2</sup>）が必要である。そして、走査速度を10～2000cm/sec程度として照射する。なお、単結晶のYAG、YVO<sub>4</sub>、フォルステライト（Mg<sub>2</sub>SiO<sub>4</sub>）、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶（セラミック）のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザー、Arイオンレーザー、またはTi：サファイアレーザーは、連続発振をさせることができ、Qスイッチ動作やモード同期などを行うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。10MHz以上の発振周波数でレーザービームを発振させると、半導体膜がレーザーによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザーを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができるために、走査方向に向かって連続的に成長した結晶粒を得ることができる。

20

#### 【0072】

次に、結晶質半導体膜704a～704dを覆うゲート絶縁膜705を形成する。ゲート絶縁膜705は、CVD法やスパッタ法等により、珪素の酸化物又は珪素の窒化物を含む膜を、単層又は積層して形成する。具体的には、酸化珪素膜、酸化窒化珪素膜、窒化酸化

30

40

50

珪素膜を、単層又は積層して形成する。

【0073】

また、ゲート絶縁膜705は、半導体膜704a～704dに対し高密度プラズマ処理を行い、表面を酸化又は窒化することで形成しても良い。例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素(NO<sub>2</sub>)、アンモニア、窒素、水素などの混合ガスを導入したプラズマ処理で形成する。この場合のプラズマの励起は、マイクロ波の導入により行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)や窒素ラジカル(NHラジカルを含む場合もある)によって、半導体膜の表面を酸化又は窒化することができる。

10

【0074】

このような高密度プラズマを用いた処理により、1～20nm、代表的には5～10nmの絶縁膜が半導体膜に形成される。この場合の反応は、固相反応であるため、当該絶縁膜と半導体膜との界面準位密度はきわめて低くすることができる。このような、高密度プラズマ処理は、半導体膜(結晶性シリコン、或いは多結晶シリコン)を直接酸化(若しくは窒化)するため、形成される絶縁膜の厚さは理想的には、ばらつきをきわめて小さくすることができる。加えて、結晶性シリコンの結晶粒界でも酸化が強くされることはないと、非常に好ましい状態となる。すなわち、ここで示す高密度プラズマ処理で半導体膜の表面を固相酸化することにより、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜を形成することができる。

20

【0075】

ゲート絶縁膜705は、高密度プラズマ処理によって形成される絶縁膜のみを用いても良いし、それに加えてプラズマや熱反応を利用したCVD法で酸化シリコン、酸窒化シリコン、窒化シリコンなどの絶縁膜を堆積し、積層させても良い。いずれにしても、高密度プラズマで形成した絶縁膜をゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを小さくすることができる。

30

【0076】

また、半導体膜に対し、連続発振レーザー光若しくは10MHz以上の周波数で発振するレーザー光を照射しながら一方向に走査して結晶化させて得られた半導体膜704a～704dは、そのレーザー光の走査方向に結晶が成長する特性がある。その走査方向をチャネル長方向(チャネル形成領域が形成されたときにキャリアが流れる方向)に合わせてトランジスタを配置し、上記ゲート絶縁層を組み合わせることで、特性ばらつきが小さく、しかも電界効果移動度が高い薄膜トランジスタ(TFT)を得ることができる。

30

【0077】

次に、ゲート絶縁膜705上に、第1の導電膜と第2の導電膜とを積層して形成する。ここでは、第1の導電膜は、プラズマCVD法やスパッタ法等により、20～100nmの厚さで形成する。第2の導電膜は、100～400nmの厚さで形成する。第1の導電膜と第2の導電膜は、タンタル(Ta)、タンクステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素又はこれらの元素を主成分とする合金材料若しくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成する。第1の導電膜と第2の導電膜の組み合わせの例を挙げると、窒化タンタル膜とタンクステン膜、窒化タンクステン膜とタンクステン膜、窒化モリブデン膜とモリブデン膜等が挙げられる。タンクステンや窒化タンタルは、耐熱性が高いため、第1の導電膜と第2の導電膜を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2層構造ではなく、3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

40

【0078】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極とゲート配線を形成するためのエッチング処理を行って、半導体膜704a～704dの上方にゲート電極707を形成する。

50

## 【0079】

次に、フォトリソグラフィ法により、レジストからなるマスクを形成して、結晶質半導体膜704a～704dに、イオンドープ法またはイオン注入法により、n型を付与する不純物元素を低濃度に添加する。n型を付与する不純物元素は、15族に属する元素を用いれば良く、例えばリン(P)、砒素(As)を用いる。

## 【0080】

次に、ゲート絶縁膜705とゲート電極707を覆うように、絶縁膜を形成する。絶縁膜は、プラズマCVD法やスパッタ法等により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む膜や、有機樹脂などの有機材料を含む膜を、単層又は積層して形成する。次に、絶縁膜を、垂直方向を主体とした異方性エッティングにより選択的にエッティングして、ゲート電極707の側面に接する絶縁膜708(サイドウォールともよばれる)を形成する。絶縁膜708は、後にLDD(Lightly Doped drain)領域を形成する際のドーピング用のマスクとして用いる。

10

## 【0081】

次に、フォトリソグラフィ法により形成したレジストからなるマスクと、ゲート電極707および絶縁膜708をマスクとして用いて、結晶質半導体膜704a～704dにn型を付与する不純物元素を添加して、チャネル形成領域706aと、第1の不純物領域706bと、第2の不純物領域706cを形成する(図11(C)参照)。第1の不純物領域706bは薄膜トランジスタのソース領域又はドレイン領域として機能し、第2の不純物領域706cはLDD領域として機能する。第2の不純物領域706cが含む不純物元素の濃度は、第1の不純物領域706bが含む不純物元素の濃度よりも低い。

20

## 【0082】

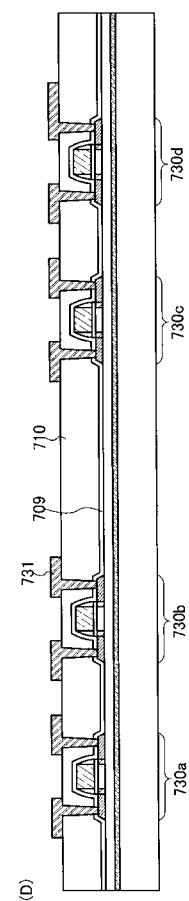

続いて、ゲート電極707、絶縁膜708等を覆うように、絶縁膜を単層または積層して形成し、当該絶縁膜上に薄膜トランジスタのソース電極又はドレイン電極として機能する導電膜731を形成する。その結果、薄膜トランジスタ730a～730dを含む素子層751が得られる(図11(D)、図9(B)参照)。なお、薄膜トランジスタ等の素子は、領域750の全面に設けた構成としても良いし、上記実施の形態で示したように、領域750の一部(例えば、中心部)を除いた部分に設けた構成としても良い。

30

## 【0083】

絶縁膜は、CVD法、スパッタ法、SOG法、液滴吐出法、スクリーン印刷法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ等の有機材料やシリコサン材料等により、単層または積層で形成する。ここでは、絶縁膜を2層で設けた例を示しており、1層目の絶縁膜709として窒化酸化珪素膜で形成し、2層目の絶縁膜710として酸化窒化珪素膜で形成することができる。

40

## 【0084】

なお、絶縁膜709、710を形成する前、または絶縁膜709、710のうちの一方又は両方を形成した後に、半導体膜704の結晶性の回復や半導体膜に添加された不純物元素の活性化、半導体膜の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザーアニール法またはRTA法などを適用するとよい。

## 【0085】

導電膜731は、フォトリソグラフィ法により絶縁膜709、710等をエッティングして、第1の不純物領域706bを露出させるコンタクトホールを形成した後、コンタクトホールを充填するように導電膜を形成し、当該導電膜を選択的にエッティングして形成する。なお、導電膜を形成する前に、コンタクトホールにおいて露出した半導体膜704a～704dの表面にシリサイドを形成してもよい。

## 【0086】

また、導電膜731は、CVD法やスパッタリング法等により、アルミニウム(Al)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、

50

ネオジム (Nd)、炭素 (C)、シリコン (Si) から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。導電膜 731 は、例えば、バリア膜とアルミニウムシリコン (Al-Si) 膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン (Al-Si) 膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜 731 を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができる。

10

## 【0087】

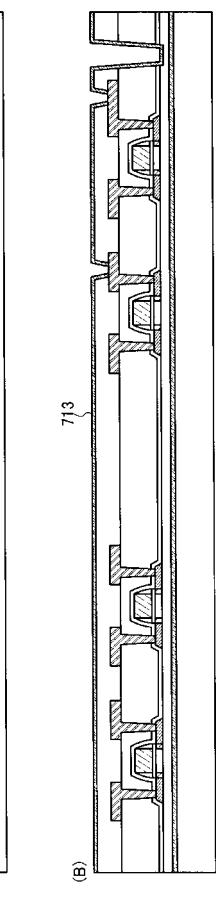

次に、導電膜 731 を覆うように、絶縁膜 711 を形成し、当該絶縁膜 711 上に開口部 712a、712b を形成する (図 12 (A) 参照)。ここでは、薄膜トランジスタ 730c、730d のソース電極又はドレイン電極として機能する導電膜 731 が露出するように開口部 712a を形成する。また、絶縁膜 703 が露出するように開口部 712b を形成する。絶縁膜 711 は、CVD 法、スパッタ法、SOG 法、液滴吐出法またはスクリーン印刷法等を用いて、無機材料又は有機材料により、単層又は積層で形成する。また、絶縁膜 711 は、好適には、0.75 μm ~ 3 μm の厚さで形成する。なお、剥離層 702 が露出するように開口部 712b を形成してもよいし、基板 701 が露出又は基板 701 に凹部が形成されるように開口部 712b を形成してもよい。

20

## 【0088】

次に、絶縁膜 711 の表面及び露出した絶縁膜 703、709、710 に薄膜の金属膜 713 を形成する (図 12 (B) 参照)。金属膜 713 は、絶縁膜 711 及び露出した絶縁膜 703、709、710 の表面に粗化処理を施した後にめっき処理を行うことによって形成することができる。例えば、絶縁膜 711 及び露出した絶縁膜 703、709、710 を化学的に粗化して表面に凹凸を形成した後に、無電解で銅 (Cu) めっき処理を行えばよい。また、めっき処理は銅に限らず、ニッケル (Ni)、金 (Au)、白金 (Pt)、銀 (Ag) 等を用いてもよい。

30

## 【0089】

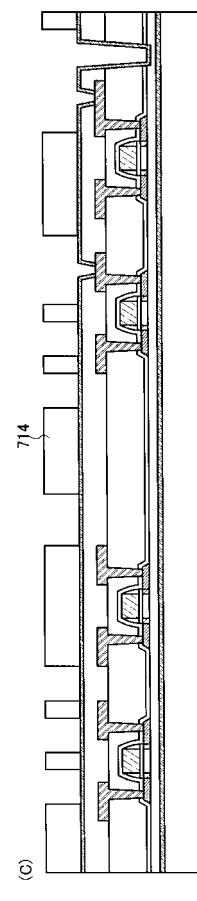

次に、金属膜 713 上にレジスト 714 を選択的に形成する (図 12 (C) 参照)。レジスト 714 は、導電膜を設けたい部分を除いた領域に形成する。

## 【0090】

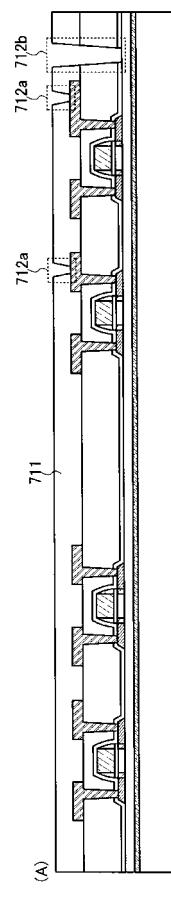

次に、レジスト 714 に覆われていない金属膜 713 上に導電膜 715 を形成する (図 13 (A) 参照)。導電膜 715 は、めっき処理を行うことによって形成することができる。例えば、銅 (Cu) を用いた電解めっき処理により形成することができる。めっき処理は銅に限らず、ニッケル (Ni)、金 (Au)、白金 (Pt)、銀 (Ag) 等を用いてもよい。

40

## 【0091】

次に、レジスト 714 及び導電膜 715 に覆われていない金属膜 713 を選択的に除去することによって、導電膜 716a ~ 716c を形成する (図 13 (B)、図 9 (C) 参照)。なお、導電膜 716a はオンチップのアンテナとして機能し、導電膜 716b、716c は薄膜トランジスタ等の素子における配線として機能する。導電膜 716c は、後に形成されるアンテナと電気的に接続するための配線である。

## 【0092】

本実施の形態では、アンテナとして機能する導電膜 (導電膜 716a) と配線として機能する導電膜 (導電膜 716b、716c) を同時に形成する。この場合、作製工程を省略

50

できるため低コスト化を図ることができる。もちろん、アンテナとして機能する導電膜 716a と配線として機能する導電膜 716b、716c を別途形成してもよい。

【0093】

なお、導電膜 716a～716c の作製は、図 12 (B)～図 13 (B) に示した方法に限られず、導電膜 731 の作製方法と同様に CVD 法やスパッタリング法等により形成した後、フォトリソグラフィ法を用いて形成しても良い。また、液滴吐出法やスクリーン印刷法等により直接パターンを形成しても良い。スクリーン印刷法により導電膜 716a、716b を形成する場合には、例えば、図 12 (A) の状態まで形成した後、銀等の導電性のペーストを絶縁膜 711 上に選択的に形成し、その後、50～350 度の加熱処理を行って導電膜 716a～716c とすればよい。また、導電膜 716c は、導電膜 731 10 と同時に形成することもできる。

【0094】

次に、薄膜トランジスタ 730a～730d やアンテナとして機能する導電膜 716a 等を含む素子形成層を基板 701 から剥離する。

【0095】

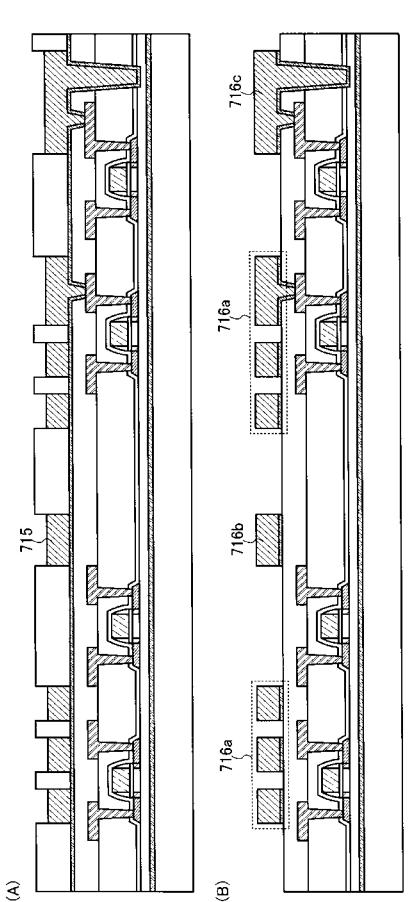

まず、導電膜 716a、716b を覆うように絶縁膜 717 を形成した後、レーザー光を照射することにより開口部 718 を形成する (図 13 (C)、図 10 (A) 参照)。続いて、素子形成層 719 の一方の面 (ここでは、絶縁膜 717 の表面) をシート材料 720 に貼り合わせた後、基板 701 から素子形成層 719 を剥離する (図 14 (A) 参照)。シート材料 720 としては、ホットメルトフィルム等のプラスチックフィルムを用いることができる。また、後にシート材料 720 を剥離する場合には、熱を加えることにより粘着力が弱まる熱剥離テープを用いることができる。20

【0096】

なお、剥離する際に水やオゾン水等の水溶液で剥離する面を濡らしながら行うことによって、薄膜トランジスタ 730a～薄膜トランジスタ 730d 等の素子が静電気等によって破壊されることを防止できる。また、素子形成層 719 が剥離された基板 701 を再利用することによって、低コスト化を実現することができる。

【0097】

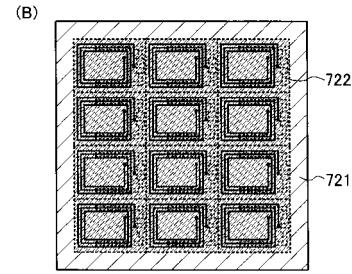

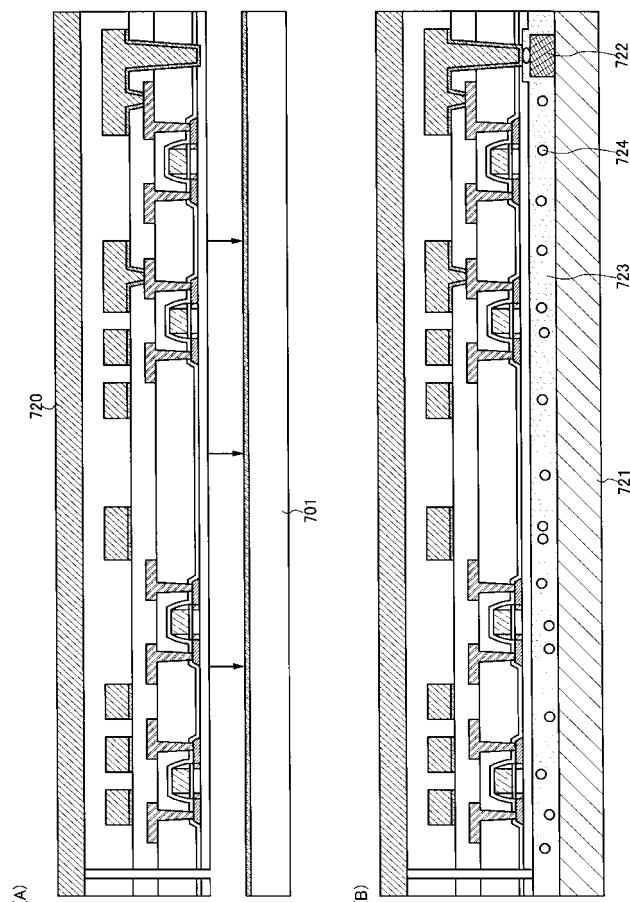

次に、素子形成層 719 の他方の面 (基板 701 から剥離により露出した面) において、導電膜 716c を露出させた後 (図 14 (B)、図 10 (B) 参照)、アンテナとして機能する導電膜 722 と電気的に接続する。ここでは、接着性を有する樹脂 723 を用いて、素子形成層 719 と導電膜 722 が設けられた基板 721 とを接着する。また、樹脂 723 に含まれる導電性粒子 724 により導電膜 716c と導電膜 722 とを電気的に接続する。このように、複数の素子形成層 719 のそれぞれに導電膜 722 を一度に設けることによって、工程の簡略化を図ることができる。30

【0098】

従って、導電膜 722 は絶縁性を有する基体 (ここでは、絶縁膜 703) を介して、集積回路部を構成する薄膜トランジスタ 703d と電気的に接続された構成となる。なお、基板 701 から素子形成層 719 を剥離した後、導電膜 716c が露出していない場合は絶縁膜 703 等に研削処理、研磨処理を行うことにより露出させることができる。また、導電膜 716c が露出していない場合であっても、絶縁膜 703 等を介して導電膜 716c と重なるように導電膜 722 を設けた後、レーザー光の照射を行うことにより導電膜 716c と導電膜 722 とを電気的に接続することも可能である (図 16 (A)、(B) 参照)。40

【0099】

基板 721 は、プラスチック基板等を用いることができる。プラスチック基板を用いることによって、安価で可撓性を有する半導体装置を得ることができる。また、ここでは、基板 721 上に設けられた導電膜 722 を素子形成層 719 に貼り合わせて設けているが、アンテナとして機能する導電膜 722 は素子形成層 719 の他方の面に液滴吐出法又はスクリーン印刷法等により形成してもよい。

## 【0100】

次に、導電膜722が設けられた素子形成層719をダイシング、スクライビング又はレーザーカット法等により選択的に分断することによって、複数の半導体装置を得ることができる(図15、図10(C)参照)。なお、本実施の形態では、半導体装置を3mm×3mm～20mm×20mmのサイズで設けることが望ましい。

## 【0101】

なお、本実施の形態では、素子形成層719にアンテナとして機能する導電膜722が設けられた基板721を貼り合わせた後に、分断することによって複数の半導体装置を作製する場合を示したが、素子形成層719を複数に分断した後にアンテナとして機能する導電膜722が設けられた基板721を貼り合わせてもよい。この場合、素子形成層719を含む集積回路部と基板721を異なった大きさで設けることができる。一方、上述した工程(図14(B)～図15)においては、素子形成層719を含む集積回路部と基板721の面積が概略同一となる。

10

## 【0102】

また、本実施の形態では、基板701上に薄膜トランジスタやアンテナ等の素子を形成した後、当該基板701から剥離することによって可撓性を有する半導体装置を作製する場合について示したが、これに限られない。

## 【0103】

例えば、基板701上に剥離層702を設けずに図11(A)～図13(B)までの工程を経た後、基板701を研削処理、研磨処理して導電膜716cを露出させた後アンテナとして機能する導電膜722を貼り合わせて設けることにより半導体装置が得られる。また、この際、図12(A)において基板701に凹部が形成されるように、開口部712bを設け、当該開口部712bに導電膜722を形成することにより、薄膜化した基板701上に薄膜トランジスタやアンテナ等の素子が設けられた半導体装置を作製することができる。この場合、アンテナとして機能する導電膜722は、基板701を介して薄膜トランジスタと電気的に接続された構造となる。

20

## 【0104】

本実施の形態で示した半導体装置の作製方法は、本明細書の他の実施の形態で示した半導体装置の作製に適用することができる。

30

## 【0105】

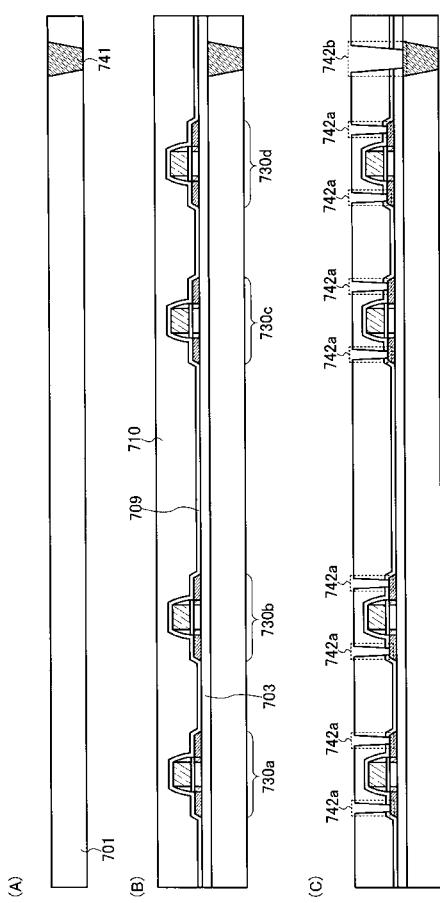

## (実施の形態5)

本実施の形態では、上記実施の形態と異なる半導体装置の作製方法について、図面を参照して説明する。

## 【0106】

まず、導電膜741が埋め込まれた基板701を準備する(図17(A)参照)。導電膜741は、基板を貫通して埋め込まれていてもよいし、基板701に設けられた凹部に埋め込まれていてもよい。

## 【0107】

次に、基板701上に絶縁膜703を介して薄膜トランジスタ730a～730dを設ける(図17(B)参照)。上記実施の形態で示した作製方法を用いることができる。

40

## 【0108】

次に、薄膜トランジスタ730a～730dのソース領域及びドレイン領域に達する開口部742a及び基板701に設けられた導電膜741に達する開口部742bを設ける(図17(C)参照)。

## 【0109】

次に、絶縁膜710上及び開口部742a、742bに導電膜731を選択的に形成する(図17(D)参照)。

## 【0110】

次に、絶縁膜711を介して、アンテナとして機能する導電膜716aと配線として機能する導電膜716bを形成する(図18(A)参照)。

50

## 【0111】

次に、導電膜741と電気的に接続するようにアンテナとして機能する導電膜722を設ける(図18(B)参照)。ここでは、接着性を有する樹脂723を用いて、基板701と導電膜722が設けられた基板721とを接着する。また、樹脂723に含まれる導電性粒子724により導電膜741と導電膜722とを電気的に接続する。なお、基板701の凹部に導電膜741を設けた場合には、基板701を研削処理、研磨処理により薄膜化させて導電膜741を露出させた後に導電膜722と接続する。

## 【0112】

このように、導電膜が埋め込まれた基板を用いることによって、作製工程において基板をエッチングする工程を省略し簡略化することができる。また、基板のエッチングに伴い発生するゴミ等の不純物をなくすことができる。

10

## 【0113】

本実施の形態で示した半導体装置の作製方法は、本明細書の他の実施の形態で示した半導体装置の作製に適用することができる。

## 【0114】

## (実施の形態6)

本実施の形態では、上記実施の形態と異なる半導体装置の作製方法について、図面を参照して説明する。具体的には、ブースターアンテナを有する半導体装置の作製方法について説明する。

## 【0115】

まず、上述した図11(A)～図14(B)まで同様に形成する。次に、シート材料720を剥離する(図19(A)、図20(A)参照)。

20

## 【0116】

次に、ブースターアンテナとして機能する導電膜743が設けられた基板742を素子形成層719の一方の面(ここでは、絶縁膜717の表面)に貼り合わせて設ける(図19(B)、図20(B)参照)。ここでは、接着性を有する樹脂744を用いて、導電膜743が設けられた基板742を素子形成層719の一方の面に貼り合わせて設ける。その後、上記図15で示したようにダイシング、スクライビング又はレーザーカット法等により選択的に分断することによって、複数の半導体装置を得ることができる(図19(C)参照)。

30

## 【0117】

なお、基板742に設けられた導電膜743と、素子形成層719に設けられた薄膜トランジスタ等の素子とは電気的に接続せずに設ける。つまり、本実施の形態で示す半導体装置において、導電膜716aはオンチップアンテナであり、導電膜743は外部アンテナ(ブースターアンテナ)となる。従って、外部(通信機)との情報の送受信は、導電膜743から構成されるアンテナを利用して行い、当該導電膜743から構成されるアンテナと導電膜716bから構成されるアンテナが情報の授受を行うことによって、半導体装置と外部との通信が行われる。

## 【0118】

以上のように、本実施の形態で示す半導体装置は、当該半導体装置を構成する集積回路部と、ブースターアンテナが基板721と概略同じ面積で設ける。このような構成とすることにより、オンチップアンテナとして機能する導電膜716aが薄膜トランジスタ等の配線により位置(レイアウト)が制限される場合(例えば、導電膜716aと導電膜716bが同一の膜上に設けられる場合)であっても、通信距離を確保することが可能となる。

40

## 【0119】

本実施の形態で示した半導体装置の作製方法は、本明細書の他の実施の形態で示した半導体装置の作製に適用することができる。

## 【0120】

## (実施の形態7)

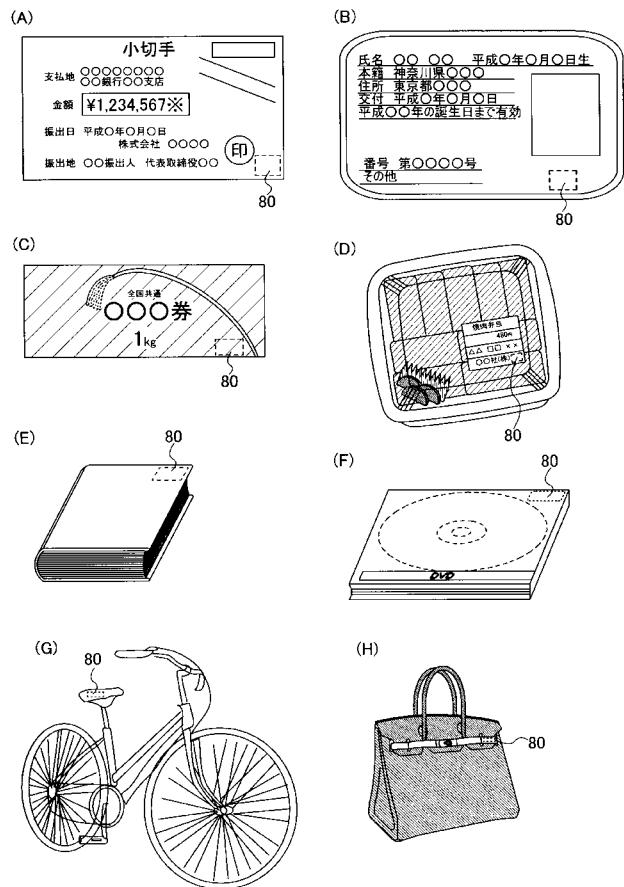

本実施の形態では、本発明の半導体装置の利用形態の一例について説明する。本発明の半

50

導体装置の用途は広範にわたり、非接触で対象物の履歴等の情報を明確にし、生産・管理等に役立てる商品であればどのようなものにも適用することができる。例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。これらの例に関して図21を用いて説明する。

#### 【0121】

紙幣、硬貨とは、市場に流通する金銭であり、特定の地域で貨幣と同じように通用するもの（金券）、記念コイン等を含む。有価証券類とは、小切手、証券、約束手形等を指す（図21（A））。証書類とは、運転免許証、住民票等を指す（図21（B））。無記名債券類とは、切手、おこめ券、各種ギフト券等を指す（図21（C））。包装用容器類とは、お弁当等の包装紙、ペットボトル等を指す（図21（D））。書籍類とは、書物、本等を指す（図21（E））。記録媒体とは、DVDソフト、ビデオテープ等を指す（図21（F））。乗物類とは、自転車等の車両、船舶等を指す（図21（G））。身の回り品とは、鞄、眼鏡等を指す（図21（H））。食品類とは、食料品、飲料等を指す。衣類とは、衣服、履物等を指す。保健用品類とは、医療器具、健康器具等を指す。生活用品類とは、家具、照明器具等を指す。薬品類とは、医薬品、農薬等を指す。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置（テレビ受像機、薄型テレビ受像機）、携帯電話機等を指す。

10

#### 【0122】

紙幣、硬貨、有価証券類、証書類、無記名債券類等に半導体装置80を設けることにより、偽造を防止することができる。また、包装用容器類、書籍類、記録媒体等、身の回り品、食品類、生活用品類、電子機器等に半導体装置80を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。乗物類、保健用品類、薬品類等に半導体装置80を設けることにより、偽造や盗難の防止、薬品類ならば、薬の服用の間違いを防止することができる。半導体装置80の設け方としては、物品の表面に貼ったり、物品に埋め込んだりして設ける。例えば、本ならば紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりするとよい。

20

#### 【0123】

このように、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に半導体装置を設けることにより、検品システムやレンタル店のシステムなどの効率化を図ることができる。また乗物類に半導体装置を設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物にセンサーを備えた半導体装置を埋め込むことによって、生まれた年や性別または種類等はもちろん体温等の健康状態を容易に管理することができる。特に、上記実施の形態で示した半導体装置を用いることによって、湾曲した面に設ける場合や物品を曲げた場合であってもアンテナとICチップの接続不良に伴う半導体装置の不良を防止し、且つ通信距離を確保することができる。

30

#### 【0124】

本実施の形態で示した半導体装置の作製方法は、本明細書に記載した他の実施の形態の半導体装置に適用することができる。

40

#### 【図面の簡単な説明】

#### 【0125】

【図1】本発明の半導体装置の一構成例を示す図。

【図2】本発明の半導体装置のブロック図の一例を示す図。

【図3】本発明の半導体装置のブロック図の一例を示す図。

【図4】本発明の半導体装置の一構成例を示す図。

【図5】本発明の半導体装置のブロック図の一例を示す図。

【図6】本発明の半導体装置の一構成例を示す図。

【図7】本発明の半導体装置の一構成例を示す図。

【図8】本発明の半導体装置のブロック図の一例を示す図。

50

【図9】本発明の半導体装置の作製方法の一例を示す図。

【図10】本発明の半導体装置の作製方法の一例を示す図。

【図11】本発明の半導体装置の作製方法の一例を示す図。

【図12】本発明の半導体装置の作製方法の一例を示す図。

【図13】本発明の半導体装置の作製方法の一例を示す図。

【図14】本発明の半導体装置の作製方法の一例を示す図。

【図15】本発明の半導体装置の作製方法の一例を示す図。

【図16】本発明の半導体装置の作製方法の一例を示す図。

【図17】本発明の半導体装置の作製方法の一例を示す図。

【図18】本発明の半導体装置の作製方法の一例を示す図。

【図19】本発明の半導体装置の作製方法の一例を示す図。

【図20】本発明の半導体装置の作製方法の一例を示す図。

【図21】本発明の半導体装置の作製方法の使用形態の一例を示す図。

## 【符号の説明】

## 【0126】

80 半導体装置

101 基板

102 集積回路部

104 貫通孔

105 領域

106 電源回路

110 送受信回路部

111 整流回路

112 復調回路

113 変調回路

114 メモリ回路

115 メモリ制御回路

116 電源回路

121 領域

122 凹部

123 絶縁膜

130 通信機

131 基板

132 導電性粒子

133 樹脂

135 基板

136 樹脂

701 基板

702 剥離層

703 絶縁膜

704 半導体膜

705 ゲート絶縁膜

707 ゲート電極

708 絶縁膜

709 絶縁膜

710 絶縁膜

711 絶縁膜

713 金属膜

714 レジスト

715 導電膜

10

20

30

40

50

|         |          |    |

|---------|----------|----|

| 7 1 7   | 絶縁膜      |    |

| 7 1 8   | 開口部      |    |

| 7 1 9   | 素子形成層    |    |

| 7 2 0   | シート材料    |    |

| 7 2 1   | 基板       |    |

| 7 2 2   | 導電膜      |    |

| 7 2 3   | 樹脂       |    |

| 7 2 4   | 導電性粒子    |    |

| 7 3 1   | 導電膜      | 10 |

| 7 4 1   | 導電膜      |    |

| 7 4 2   | 基板       |    |

| 7 4 3   | 導電膜      |    |

| 7 4 4   | 樹脂       |    |

| 7 5 0   | 領域       |    |

| 7 5 1   | 素子層      |    |

| 1 0 2 a | 集積回路部    |    |

| 1 0 2 b | 集積回路部    |    |

| 1 0 3 a | アンテナ     |    |

| 1 0 3 b | アンテナ     |    |

| 1 0 3 c | アンテナ     | 20 |

| 1 1 0 a | 送受信回路部   |    |

| 1 1 0 b | 送受信回路部   |    |

| 1 1 1 a | 整流回路     |    |

| 1 1 1 b | 整流回路     |    |

| 1 1 2 a | 復調回路     |    |

| 1 1 2 b | 復調回路     |    |

| 1 1 3 a | 変調回路     |    |

| 1 1 3 b | 変調回路     |    |

| 1 1 4 a | メモリ回路    |    |

| 1 1 4 b | メモリ回路    | 30 |

| 1 1 5 a | メモリ制御回路  |    |

| 1 1 5 b | メモリ制御回路  |    |

| 1 1 6 a | 電源回路     |    |

| 1 1 6 b | 電源回路     |    |

| 7 0 3 d | 薄膜トランジスタ |    |

| 7 0 4 a | 半導体膜     |    |

| 7 0 6 a | チャネル形成領域 |    |

| 7 0 6 b | 不純物領域    |    |

| 7 0 6 c | 不純物領域    |    |

| 7 1 2 a | 開口部      | 40 |

| 7 1 2 b | 開口部      |    |

| 7 1 6 a | 導電膜      |    |

| 7 1 6 b | 導電膜      |    |

| 7 1 6 c | 導電膜      |    |

| 7 3 0 a | 薄膜トランジスタ |    |

| 7 3 0 c | 薄膜トランジスタ |    |

| 7 3 0 d | 薄膜トランジスタ |    |

| 7 4 2 a | 開口部      |    |

| 7 4 2 b | 開口部      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

【図 15】

【図 16】

【図17】

【図18】

【図19】

【図20】

## 【図 2 1】

## フロントページの続き

|                        |             |            |

|------------------------|-------------|------------|

| (51) Int.Cl.           | F I         | テーマコード(参考) |

| H 01L 29/786 (2006.01) | H 01L 29/78 | 627D       |

| H 01L 21/336 (2006.01) | G 06K 19/00 | H          |

| G 06K 19/07 (2006.01)  | B 42D 15/10 | 521        |

| B 42D 15/10 (2006.01)  |             |            |