(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4458807号

(P4458807)

(45) 発行日 平成22年4月28日(2010.4.28)

(24) 登録日 平成22年2月19日(2010.2.19)

(51) Int.Cl.

G06F 13/12 (2006.01)

F 1

G06F 13/12 340 G

請求項の数 18 (全 39 頁)

(21) 出願番号 特願2003-366476 (P2003-366476)

(22) 出願日 平成15年10月27日 (2003.10.27)

(65) 公開番号 特開2004-199658 (P2004-199658A)

(43) 公開日 平成16年7月15日 (2004.7.15)

審査請求日 平成18年10月24日 (2006.10.24)

(31) 優先権主張番号 特願2002-355417 (P2002-355417)

(32) 優先日 平成14年12月6日 (2002.12.6)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000237592

富士通テン株式会社

兵庫県神戸市兵庫区御所通1丁目2番28

号

(74) 代理人 100077517

弁理士 石田 敬

(74) 代理人 100092624

弁理士 鶴田 準一

(74) 代理人 100100871

弁理士 土屋 繁

(74) 代理人 100082898

弁理士 西山 雅也

(74) 代理人 100081330

弁理士 樋口 外治

最終頁に続く

(54) 【発明の名称】デジタル信号処理装置、システム、方法およびホスト装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のチャンネルからの各入力信号を受信する入力部と、

各々が前記入力部からの信号を共通に受信可能であって、かつ、各々が所定の順序で受信した該信号に対し、各々に固有の機能によって信号処理を行う複数の機能モジュールと、

前記複数のチャンネルの各々に対応する1または複数の前記機能モジュールを順次選択し、選択された該機能モジュールに対して当該入力信号の信号処理を行わせるモジュール選択／制御手段と、

を備えることを特徴とするデジタル信号処理装置。

10

## 【請求項 2】

メモリ手段をさらに含み、該メモリ手段は、各前記チャンネル対応に選択すべき前記1または複数の前記機能モジュールを指定するための処理シーケンス情報を書き換え可能に保持するシーケンスマモリを有することを特徴とする請求項1に記載のデジタル信号処理装置。

## 【請求項 3】

メモリ手段をさらに含み、該メモリ手段は、各前記機能モジュールにおける前記信号処理の内容を修飾するためのパラメータ情報を書き換え可能に保持するパラメータメモリを有することを特徴とする請求項1に記載のデジタル信号処理装置。

## 【請求項 4】

20

前記の信号処理をすべき各信号の処理順序情報を保持するチャンネル順序メモリをさらに有することを特徴とする請求項 1 に記載のデジタル信号処理装置。

【請求項 5】

前記モジュール選択 / 制御手段は、各前記チャンネル対応に選択すべき前記機能モジュールを、指定された一連の処理シーケンスに従って選択すると共に、前記入力信号として新たな割込み入力信号が発生したときには、その指定された一連の処理シーケンスの中に割込み処理シーケンスを挿入することを特徴とする請求項 1 に記載のデジタル信号処理装置。

【請求項 6】

少なくとも前記入力部と、前記機能モジュールと、前記モジュール選択 / 制御手段との間を接続する共有バスを備え、かつ、該共有バスは、前記信号処理において扱うデータ種別毎に分離した複数の個別バスからなることを特徴とする請求項 1 に記載のデジタル信号処理装置。 10

【請求項 7】

少なくとも前記入力部と、前記機能モジュールと、前記モジュール選択 / 制御手段との間を接続する共有バスを備え、かつ、該共有バスは、前記信号処理において扱う複数種のデータを時分割にて転送する単一バスからなることを特徴とする請求項 1 に記載のデジタル信号処理装置。

【請求項 8】

前記信号処理による処理結果を外部に送信する出力部をさらに備え、該出力部は、前記複数のチャンネルのうちのいずれのチャンネルからの前記入力信号についての処理結果であるかを示す ID を、当該処理結果のデータにさらに付加して送信することを特徴とする請求項 1 に記載のデジタル信号処理装置。 20

【請求項 9】

前記信号処理による処理結果を外部に送信する出力部をさらに備え、該出力部は、前記複数のチャンネルの各前記入力信号についての処理結果を、各該チャンネルに割り当てた送信順番に従って順次送信することを特徴とする請求項 1 に記載のデジタル信号処理装置。

【請求項 10】

少なくとも前記複数の機能モジュールの間を接続する共有バスを備えると共に、これら複数の機能モジュールを現用機能モジュール群とすると、該現用機能モジュール群とミラーをなす予備機能モジュール群を、前記共有バスを介して接続し、該現用機能モジュール群内のいずれかの機能モジュールに故障ありと判定されたとき、該予備機能モジュール群内の対応する機能モジュールを選択して使用することを特徴とする請求項 1 に記載のデジタル信号処理装置。 30

【請求項 11】

少なくとも前記複数の機能モジュールの間を接続する共有バスを備えると共に、これら複数の機能モジュールを現用機能モジュール群とすると、該現用機能モジュール群とミラーをなす予備機能モジュール群を、前記共有バスを介して接続し、該現用機能モジュール群内のいずれかの機能モジュールに故障ありと判定されたとき、該予備機能モジュール群に切り替えて使用することを特徴とする請求項 1 に記載のデジタル信号処理装置。 40

【請求項 12】

請求項 1 に記載のデジタル信号処理装置に対して、前記信号処理の処理結果を送受信可能な通信インターフェースを設けると共に、係るデジタル信号処理装置と同様のデジタル信号処理装置を複数設け、それぞれの該通信インターフェースを介してこれらをカスケード接続してなることを特徴とするデジタル信号処理システム。

【請求項 13】

請求項 1 に記載のデジタル信号処理装置に対して、前記信号処理の処理結果を送受信可能な通信インターフェースを設けると共に、係るデジタル信号処理装置と同様のデジタル信号処理装置を複数設けてそのうちの 1 つをマスター・デジタル信号処理装置なし、その

他をスレーブ・デジタル信号処理装置となして、それぞれの前記通信インターフェースを介してこれらを、前記マスター・デジタル信号処理装置を中心としてスター接続することを特徴とするデジタル信号処理システム。

**【請求項 1 4】**

少なくとも入力部と複数の機能モジュールとを備えるデジタル信号処理装置において、前記複数の機能モジュールの各々に、それぞれ固有の信号処理機能を持たせ、前記入力部に入力される、複数のチャンネル毎の入力信号を、各該チャンネル対応に選択される1または複数の該機能モジュールに与えて信号処理することを特徴とするデジタル信号処理方法。

**【請求項 1 5】**

10

請求項1に記載のデジタル信号処理装置に対し、該デジタル信号処理装置から送信される前記信号処理による処理結果のデータを受信するホスト装置をさらに付加し、

前記ホスト装置は、その処理結果のデータに異常があるとき、該データを破棄しこれに代えて予め保持していたデフォルト値を使用することを特徴とするデジタル信号処理装置。

**【請求項 1 6】**

請求項1に記載のデジタル信号処理装置に対し、該デジタル信号処理装置から送信される前記信号処理による処理結果のデータを受信するホスト装置をさらに付加し、

前記ホスト装置は、その処理結果のデータに異常があると判定したとき、その異常データを生じさせた前記信号処理を特定し、この特定情報を前記デジタル信号処理装置に返送して、その特定された信号処理に対応する予め保持していたデフォルト値を使用することを特徴とするデジタル信号処理装置。

20

**【請求項 1 7】**

請求項1に記載のデジタル信号処理装置に対し、該デジタル信号処理装置から送信される前記信号処理による処理結果のデータを受信するホスト装置をさらに付加し、

前記ホスト装置は、各前記処理結果のデータに付加して前記デジタル信号処理装置から送信された、各該処理結果を生成した前記機能モジュールを示すIDを受信し、該機能モジュールに故障があると判定したとき、当該機能モジュールのIDを前記デジタル信号処理装置に送信してその故障箇所を特定させることを特徴とするデジタル信号処理装置。

30

**【請求項 1 8】**

請求項1に記載のデジタル信号処理装置に対し、該デジタル信号処理装置から送信される前記信号処理による処理結果のデータを受信するホスト装置をさらに付加し、

前記ホスト装置は、各前記チャンネル対応に選択すべき前記1または複数の前記機能モジュールを指定するための処理シーケンス情報を前記デジタル信号処理装置に送信して読みませ、さらに所定のデータを送信してその処理シーケンスを走らせ、その処理結果のデータを該デジタル信号処理装置から受信して所定の期待値と比較することにより、前記の読みませた処理シーケンス情報の正常性を判定することを特徴とするデジタル信号処理装置。

**【発明の詳細な説明】**

**【技術分野】**

40

**【0001】**

本発明は、デジタル信号処理装置、システムおよび方法とホスト装置に関する。

**【背景技術】**

**【0002】**

複数のチャンネルからそれぞれ入力された各入力信号に対して所定の信号処理を施し、それをホスト装置に印加するといった形式のデジタル信号処理システムが、種々の電子機器で広く用いられている。これに相当する電子機器の一例としては、テスト用機器やオーディオ機器や車載用コンピュータ制御機器などが挙げられる。

**【0003】**

本発明の理解を容易にするために後者の車載用コンピュータ制御機器を例にとって説明

50

すると、この機器においては、車両の各部に設けられたセンサ類（スロットル開度センサ、車速センサ、水温センサ、モード切替えスイッチ状態センサ、ステアリングセンサ等々）からのアナログ信号は、個々にすなわちチャンネル毎に、1つのホスト装置すなわちマイクロコンピュータ（マイコン）に入力され、ここで車両の最適制御のためのデジタル演算処理が施される。

#### 【0004】

この場合、ホスト装置（マイコン）は各チャンネルからの入力信号を未加工のまま直接受信することはできないので、該ホスト装置に入力される前の各該入力信号に対して、各該入力信号の性質に応じた既述の所定の信号処理を施さなければならない。この所定の信号処理を行うのが既述の「デジタル信号処理装置」である。ここに、上記のホスト装置と、デジタル信号処理装置と、該デジタル信号処理装置前段の入力端子群とによって、E C U (Electronic Control Unit) すなわち既述の「デジタル信号処理システム」が構築される。10

#### 【0005】

なお本発明に関連する公知技術としては、下記の特許文献1～4がある。しかしいずれの公知技術も、後述する説明から明らかになるとおり、「所定の順序で選択される複数のチャンネルの各々に対して、1つまたは複数の機能モジュールを順次選択して、コンフィギュラブル（configurable）にデジタル信号処理装置を形成する」という考え方に基づく本発明とは明確に区別される。

#### 【0006】

【特許文献1】特許第3015722号明細書

【特許文献2】特開平3-203422号公報

【特許文献3】特開平1-232458号公報

【特許文献4】特許第3335482号明細書

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

本出願人が実施した従来のデジタル信号処理装置の形態には2つある。

#### 【0008】

第1の形態においては、そのデジタル信号処理装置を、上述したチャンネルの構成に応じて、専用のハードウェア回路により構成する。30

#### 【0009】

また第2の形態においては、そのデジタル信号処理装置を、マイコンあるいはD S P (Digital Signal Processor)などの固定のハードウェア回路と、上述したチャンネルの構成に応じて該ハードウェア回路を動作させるためのソフトウェア処理部とによって構成する。

#### 【0010】

しかしながら、上記第2の形態によるデジタル信号処理装置においては、上記デジタル信号処理システムの変更があったときあるいは上記のチャンネルの構成に変更（例えば上記入力端子の増設など）があったときに柔軟に対応することができるといった利便性がある反面、ソフトウェア処理による処理速度に限界がある、といった問題がある。40

#### 【0011】

また、上記第1の形態によるデジタル信号処理装置においては、上記の処理速度は十分満足するものの、各チャンネル対応に1つずつデジタル信号処理回路が必要となることから、回路規模が大きくなってしまう、という問題、したがってコスト高になる、という問題がある。さらに上記のチャンネルの構成が変わった場合には、それに対応させたデジタル信号処理回路を新たに作り直さなければならない、という問題もある。

#### 【0012】

したがって本発明は、上記の諸問題点に鑑み、デジタル信号処理システムあるいはチャンネルの構成に変更があっても、ハードウェアに変更を加えることなく、これに柔軟に対50

応し得ると共に、小さい回路規模のままで高速処理が可能な、デジタル信号処理装置、システムおよび方法ならびにホスト装置を提供することを目的とするものである。

【課題を解決するための手段】

【0013】

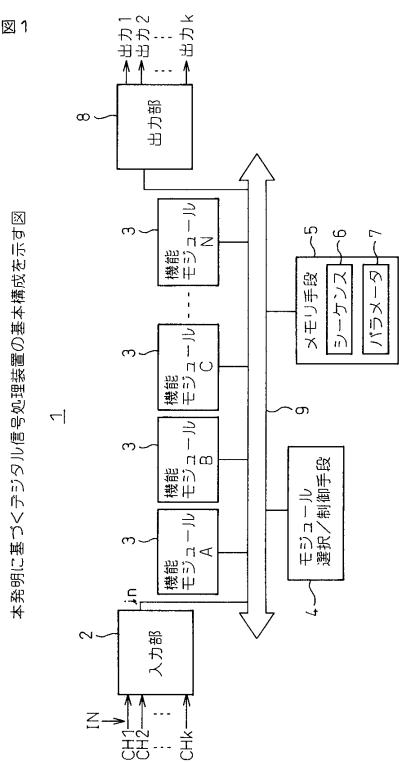

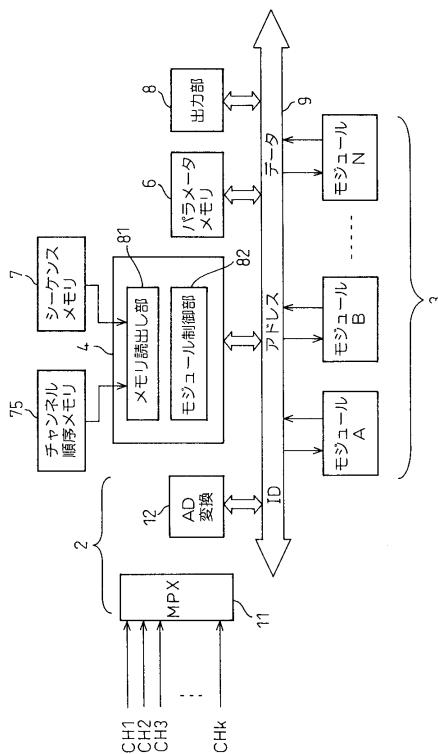

図1は本発明に基づくデジタル信号処理装置の基本構成を示す図である。

【0014】

本発明によるデジタル信号処理装置1の基本構成は、入力部2と、複数の機能モジュール3(A,B,C...N)と、モジュール選択/制御手段4とを備えてなる。具体的には、入力部2は、複数のチャンネルCH1,CH2...からの各入力信号INを受信し、複数の機能モジュール3は、各々が入力部2からの信号inを共通に受信可能であって、かつ、各々が所定の順序で受信した信号inに対し、各々に固有の機能によって信号処理を行い、

10

モジュール選択/制御手段4は、複数のチャンネルCH1,CH2...の各々に対応する1または複数の機能モジュール3を順次選択し、選択された機能モジュールに対して当該入力信号inの信号処理を行わせる。

【0015】

さらに好適には、メモリ手段5を備える。

【0016】

このメモリ手段5は、各チャンネル(CH1,CH2...)に対応に選択すべき1または複数の機能モジュール3を指定するための処理シーケンス情報を、書き換え可能に保持するシーケンスマモリ6を有する。

20

【0017】

さらにまた好ましくは、メモリ手段5は、各機能モジュール3における信号処理の内容を修飾するためのパラメータ情報を、書き換え可能に保持するパラメタメモリ7を有する。

【0018】

なお本図中の参照番号8は出力部、9は共有バスである。

【発明の効果】

【0019】

このようにして、各チャンネル毎に1つまたは複数の機能モジュール3を順次選択して、コンフィギュラブル(configurable)にデジタル信号処理装置1を形成することが可能になる。

30

【0020】

このため、システム構成やチャンネル構成に変更があってもこれに柔軟に対応できると共に、小さい回路規模のままで高速信号処理を実現することができる。

【発明を実施するための最良の形態】

【0021】

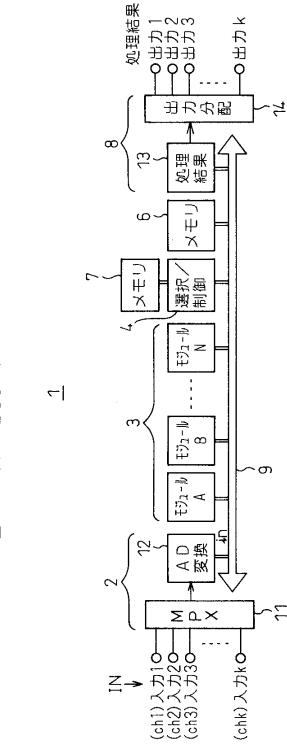

図2は図1の基本構成をさらに具体的に示す図である。なお全図を通じて同様の構成要素には同一の参照番号または記号を付して示す。

【0022】

入力部2は、各チャンネル(CH)対応の入力信号INを受信し時分割処理する分離部(MPX:multiplexer)11およびそのアナログ(A)入力信号INをデジタル(D)データ(in)に変換するAD変換部12からなり、そのデジタルデータを共有バス9に転送する。

40

【0023】

選択/制御手段4は、その共有バス9を介し、メモリ6および7の内容を参照しながら、機能モジュール(3A,3B...)に対して、チャンネル対応の信号処理を行わせる。その処理結果は、処理結果バッファ13に一旦格納された後、出力分配部14から外部に送信される。この外部をなす一例は既述したホスト装置である。ここに共有バス9は、アドレス信号、データ信号、制御信号等を転送する。次に処理動作を説明する。

50

## 【0024】

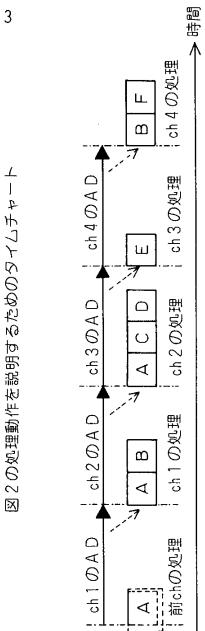

図3は図2の処理動作を説明するためのタイムチャートである。

## 【0025】

本図において、横軸は時間をとて示す。垂直の各一点鎖線は、A/D変換部12におけるサンプリング間隔を表しており、各サンプリング間隔で順次、チャンネルCH1, CH2...上の各入力信号in(これらをch1, ch2...で表す)をA/D変換する(図中の「ch1のA/D」、「ch2のA/D」...参照)。

## 【0026】

また本図中の“A”, “B”, “C”...は、図2における機能モジュール3A, 3B, 3C...をそれぞれ示しており、ch1のA/Dを経たデータ(in)は、例えば機能モジュール3Aおよび3Bにて順次信号処理される(図3中の「ch1の処理」参照)。すなわち、ch1のA/Dを経たデータ(in)は機能モジュール3Aにより信号処理された後、その信号処理されたデータが機能モジュール3Bによって信号処理される。このとき同時に並行してチャンネルCH2上の入力信号(IN)のA/D変換(図3中の「ch2のA/D」参照)が行われており、このA/D変換後のch2のデータ(in)は、例えば機能モジュール3A, 3Cおよび3Dにて順次信号処理される(図3中の「ch2の処理」参照)。以下、同様である。

## 【0027】

以上を要約すると、本発明においては、複数のデジタル入力信号の処理システムにおいて、複数の演算モジュール(3)を有し、そのデジタル入力信号をどのように処理するかを定義したデータ(メモリ6および7)に基づき、1つまたは複数個の演算モジュール(3)を選択して処理を行うものである。ここにコンフィギュラブルな処理システムが実現される。

## 【0028】

ここで「コンフィギュラブル」とは、その処理システムにおいて、機能レベルで処理を書き換え可能なことを意味する。このために、予め用意している処理モジュール(機能ブロック)を、処理内容を記述したデータ(コンフィギュレーションデータ)に基づき、入力信号毎に処理モジュールを切り替えて動作させる。

## 【0029】

以下、本発明による各実施例について詳しく述べるが、本発明の理解を容易にするために、上述した「複数のデジタル入力信号の処理システム」の一具体例を説明する。これは単なる一例に過ぎないが、既述した「車載用コンピュータ制御システム」である。一般的なデジタルデータ処理システムにももちろん適用することができる。

## 【0030】

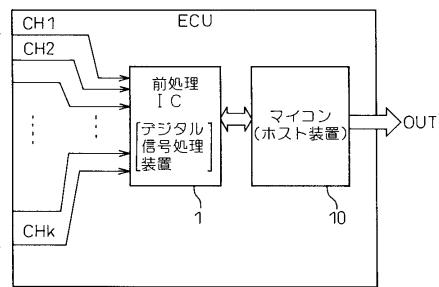

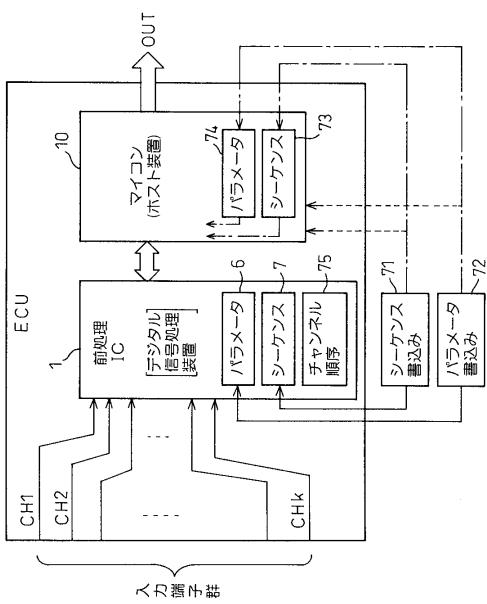

図4は本発明が適用される1システム例を示す図である。

## 【0031】

本図において、全体ブロックはECU(Electronic Control Unit)であり、各種センサ類(スロットル開度センサ等)からのアナログ信号は、ECUの入力端子群に各チャンネル信号として印加される。

## 【0032】

これらのチャンネル信号には、マイコン10での演算処理に必要な前処理が加えられる。これが前処理ICであり、本発明のデジタル信号処理装置1に相当する。上記マイコンは後にさらに詳述するホスト装置に相当する。

## 【0033】

この場合、前処理IC(1)内の複数の機能モジュール(3)は、例えばLPF(low-pass filter)、BPF(band-pass filter)、ピークホールド回路、コンパレータ等である。

## 【0034】

つまりシーケンスマモリ6には、各入力信号inを、どの機能(演算)モジュール3を用いて処理するかを定義したシーケンスマップが格納されている。

10

20

30

40

50

**【0035】**

このシーケンスマップに従う各機能モジュール3での信号処理動作は図7に示すとおりである。ただしこの図7の見方は、前述した図3と全く同じである。

**【0036】**

図5は図4に対し付加すべき本発明に係る書き込み手段を示す図である。

**【0037】**

本図にて新たに付加された構成要素は、シーケンス書き込み手段71およびパラメータ書き込み手段72と、ホスト装置10内のシーケンスマモリ(フラッシュメモリ等)73およびパラメタメモリ(フラッシュメモリ等)74である。

**【0038】**

シーケンス書き込み手段71は、図2のシーケンスマモリ7に保持すべき処理シーケンス情報を、装置(ECU)外部から書き換えるものであり、

パラメータ書き込み手段72は、図2のパラメタメモリ6に保持すべきパラメータ情報を、装置(ECU)外部から書き換えるものである(図5において、実線矢印のルート参照)。

**【0039】**

また図5に示すとおり、入力信号に対する信号処理を行った処理結果のデータを受信するホスト装置10と連携する場合、図2のシーケンスマモリ7への処理シーケンス情報の書き込みを、このホスト装置10を経由して行い、

また、図2のパラメタメモリ6へのパラメータ情報の書き込みを、このホスト装置10を経由して行う(図5において、点線矢印のルート参照)。

**【0040】**

あるいは、予め定めた複数種の処理シーケンス情報をホスト装置10内のシーケンスマモリ73に保持しておき、シーケンス書き込み手段71は所望の処理シーケンス情報をこのメモリ73に対して指定してこれをシーケンスマモリ7へ転送して書き込むようにし、

同様に、予め定めた複数種のパラメータ情報をホスト装置10内のパラメタメモリ74に保持しておき、パラメータ書き込み手段72は所望のパラメータ情報をこのメモリ74に対して指定してこれをパラメタメモリ6へ転送して書き込むようとする(図5において一点鎖線のルート参照)。

**【0041】**

なお、上記の書き込み手段71, 72は、ホスト装置(マイコン)10にインストールすべき本来の制御プログラムを入力するための手段と兼用することもできる。

**【0042】**

この図5においてさらに注目すべきメモリは、チャンネル順序メモリ75である。

**【0043】**

前述したチャンネルCH1, CH2...CHkからの各入力信号は、CH1 CH2 CH3 ...といったように、順番に信号処理されてもよいし、あるいは予め定めた任意の順序(例えば、CH1 CH3 CH2 ...)に従って信号処理されてもよい。このために、信号処理をすべき各信号の処理順序情報を保持するのがチャンネル順序メモリ75である。なお、このチャンネルの処理順序の詳しい具体例については後述する。

**【0044】**

図6は図2に示す選択/制御手段4とその周辺をより具体的に示す図である。なお、説明の都合上、機能モジュール3の配置が図2とは異なっている。また、上述したチャンネル順序メモリ75が、一例として、図示する位置に置かれている。

**【0045】**

図6に示すモジュール選択/制御手段4は、メモリ読出し部81と、このメモリ読出し部81からの読出し情報に従って各機能モジュール3(A, B...N)の制御を行うモジュール制御部82と、を含んでなる。ここにメモリ読出し部81は、シーケンスマモリ7の情報を読み出す。

**【0046】**

10

20

30

40

50

一方モジュール制御部 8 2 は、パラメータメモリ 6 からのパラメータ情報に従って各機能モジュール 3 ( A , B ... N ) の制御を行う。

【 0 0 4 7 】

また、メモリ読出し部 8 1 は、チャンネル順序メモリ 7 5 の情報を読み出す。

【 0 0 4 8 】

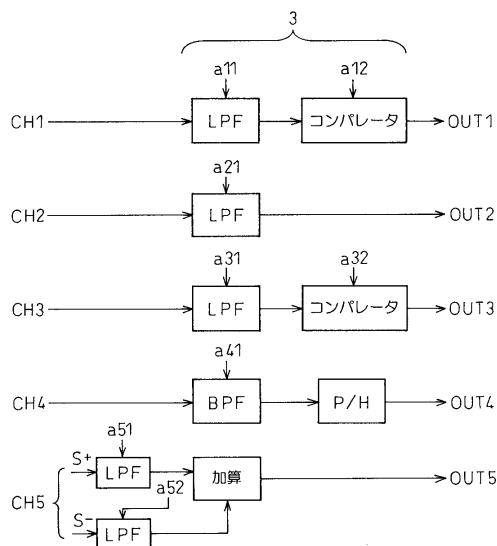

上記図 6 に示すモジュール選択 / 制御手段 4 について、フローチャートやタイムチャートを参照しながらもう少し具体的に以下に説明するが、その前に理解を早めるための、車載用装置の場合を例にとって、チャンネル C H 1 , C H 2 ... の各入力信号の具体例と、各該入力信号を処理する 1 または複数の機能モジュール 3 の具体例を説明する。

【 0 0 4 9 】

10

図 7 は各チャンネルの入力信号の例とそれを処理する機能モジュールの例を示す図である。

【 0 0 5 0 】

本図において、左端は前述の入力部 2 に相当しており、複数のチャンネル C H 1 , C H 2 , C H 3 ... からの各入力信号がここから与えられる。

【 0 0 5 1 】

一方本図の上端 3 は前述の複数の機能モジュールを表す。

【 0 0 5 2 】

各該チャンネルの処理対象は、一例として、次のとおりである。

【 0 0 5 3 】

20

C H 1 : エンジン回転数

C H 2 : 水温

C H 3 : ストップ ( ブレーキ ) ランプ

C H 4 : ノック

C H 5 : 差動型センサ

チャンネル C H 1 からのエンジン回転数信号は、まず初段機能モジュールのローパスフィルタ ( L P F ) に入力され、そのフィルタ出力は次段の機能モジュールであるコンパレータに入力されて、処理結果 O U T 1 を得る。ただし、上記ローパスフィルタ ( L P F ) から上記コンパレータへ進むとき、そのローパスフィルタ ( L P F ) からのフィルタ出力が一旦バッファされ、次に上記コンパレータがモジュール制御部 ( 図 6 の 8 2 ) により選択されたときにそのバッファから該フィルタ出力を読み出し、該コンパレータに印加する。なお、ここに言うバッファは、選択 / 制御手段 ( 図 6 の 4 ) 内にあってもよいし、出力部 ( 図 6 の 8 ) 内にあってもよいし、図 6 の共有バスに接続して独立に設けてもよい。

30

【 0 0 5 4 】

そして上記ローパスフィルタ ( L P F ) には独自のパラメータ a 1 1 がパラメータメモリ 6 側からモジュール制御部 8 2 を介して供給され、上記コンパレータにも独自のパラメータ a 1 2 がそのパラメータメモリ 6 側からモジュール制御部 8 2 を介して供給される。これらパラメータ a 1 1 , a 1 2 等については後に図 2 2 等においても、もう一度説明するが、図 7 の a 1 1 , a 1 2 や図 2 2 の a 1 1 , a 1 2 は単なる区別のための記号であつて、 a 1 1 や a 1 2 が両図で相互に同じ意味をもつものではない。

40

【 0 0 5 5 】

図 7 において上記パラメータ a 1 1 は、ローパスフィルタ ( L P F ) においてノイズを除去するのに適したフィルタ定数を設定する。また上記パラメータ a 1 2 は、コンパレータの比較基準値を設定する。

【 0 0 5 6 】

チャンネル C H 2 からの水温信号についても、ノイズをとるための機能モジュールである L P F により信号処理される。

【 0 0 5 7 】

チャンネル C H 3 からのストップ ( ブレーキ ) ランプ信号は、ノイズ除去の後 ( L P F ) 、コンパレータにて点灯 / 非点灯が判別 ( O U T 3 ) される。

50

**【0058】**

C H 4 からのノック信号、すなわちノックセンサからの出力信号は、まず所要の周波数帯域にある信号を抽出する必要があることから、他の機能モジュールであるバンドパスフィルタ（B P F）に入力され、その出力をなす多数のサンプル値の中からピーク値を保持するために、機能モジュールであるピークホールド（P / H）回路にさらに入力され、O U T 4 となる。

**【0059】**

チャンネル C H 5 は、ある特定のセンサからの出力信号である差動信号 S + および S - であって、これらの差分が加算回路より出力され、O U T 5 となる。

**【0060】**

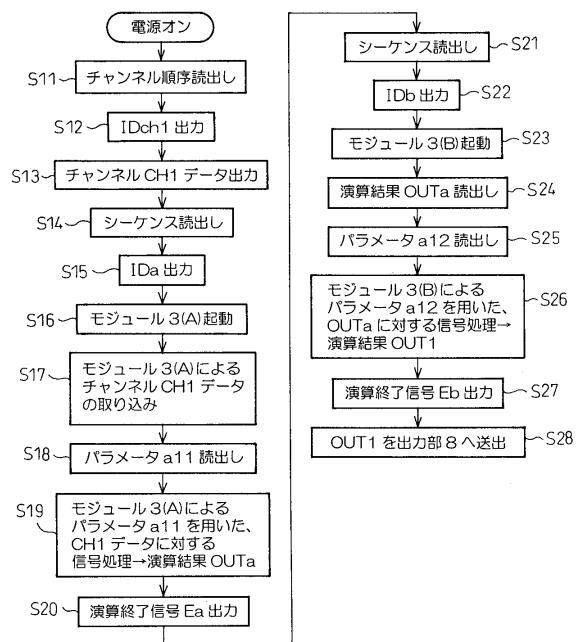

上記図 7 において各チャンネル（C H 1, C H 2, C H 3 …）の入力信号と各機能モジュールの具体例とを示したので、次にこれを踏まえて、図 6 の選択 / 制御手段 4 の動作例を、図 8 および図 9 も参照しながら説明する。

**【0061】**

図 8 は図 6 に示す選択 / 制御手段 4 の動作例を示すフローチャートであり、

図 9 は図 8 のフローチャートに対応するタイムチャートである。

なお図 7 のうち、チャンネル C H 1 と、それに対応する機能モジュール「L P F」（3 A）および機能モジュール「コンパレータ」（3 B）の場合を一例として想定して説明する（以下同様）。

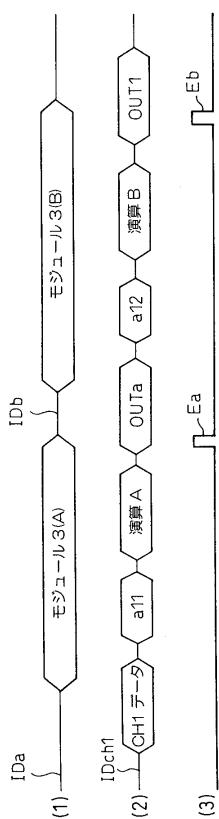

**【0062】**

図 6 ~ 図 9 を参照すると、

ステップ S 1 1（図 8）：モジュール選択 / 制御手段 4 は、メモリ読出し部 8 1 により、チャンネル順序メモリ 7 5 のチャンネル順序情報を読み出す。

**【0063】**

ステップ S 1 2：この例ではチャンネル C H 1 が指定されており、I D c h 1 が出力される（図 9 の（2）参照）。

**【0064】**

ステップ S 1 3：選択 / 制御手段 4 はその I D c h 1 を入力部 2 に出力し、チャンネル C H 1 の入力データ「C H 1 データ」が共有バス 9 上に転送される。

**【0065】**

ステップ S 1 4：選択 / 制御手段 4 は、メモリ読出し部 8 1 により、シーケンスメモリ 7 のシーケンス情報を読み出す。

**【0066】**

ステップ S 1 5：この想定している例においては、ステップ S 1 1 で読み出した第 1 のシーケンスは機能モジュール 3（A）であり、これを I D a と表す（図 9 の（1）参照）。

**【0067】**

ステップ S 1 6：共有バス 9 を介して上記 I D a を受信したモジュール 3（A）が起動される（図 9 の（1）参照）。

**【0068】**

ステップ S 1 7：機能モジュール 3（A）は、その共有バス 9 上の上記「C H 1 データ」を自内に取り込む。

**【0069】**

ステップ S 1 8：上記手段 4 は、パラメータメモリ 6 から、対応するパラメータを読み出して共有バス 9 上に転送する（図 9 の（2）参照）。上記の例であると、このパラメータは a 1 1（図 7）である。

**【0070】**

ステップ S 1 9：ここで目的とする信号処理が、C H 1 データと a 1 1 とを用いて、機能モジュール 3（A）にて実行される（図 9 の（2）の「演算 A」参照）。そしてその演算結果が出力される（図 9 の（2）の“O U T a” 参照）。

10

20

30

40

50

**【0071】**

ステップS20：このとき、機能モジュール3（A）は、上記演算の終了を示す演算終了信号を共有バス9上に出力する（図9の（3）のEa参照）。ここで図7のLPFによる演算が終了し、次段のコンパレータに演算が移行する。

**【0072】**

ステップS21：選択／制御手段4は、メモリ読出し部81により、シーケンスメモリ7のシーケンス情報を読み出す。

**【0073】**

ステップS22：この想定している例においては、ステップS21で読み出した第2のシーケンスは機能モジュール3（B）であり、これをIDbと表す（図9の（1）参照）。

10

**【0074】**

ステップS23：共有バス9を介して上記 IDb を受信したモジュール3（B）が起動される（図9の（1）参照）。

**【0075】**

ステップS24：機能モジュール3（B）は、既述したバッファから、上記演算結果OUTaを読み出して取り込む。

**【0076】**

ステップS25：上記手段4は、パラメータメモリ6から、対応するパラメータを読み出して共有バス9上に転送する（図9の（2）参照）。上記の例であると、このパラメータはa12（図7）である。

20

**【0077】**

ステップS26：ここで目的とする信号処理が、OUTaとa12とを用いて、機能モジュール3（B）にて実行される（図9の（2）の「演算B」参照）。そしてその演算結果が出力される（図9の（2）と図7の“OUT1”参照）。

**【0078】**

ステップS27：このとき、機能モジュール3（B）は、上記演算の終了を示す演算終了信号を共有バス9上に出力する（図9の（3）のEb参照）。

**【0079】**

ここで図8のステップS14について補足説明する。このチャンネル順序読出しが、信号処理すべきチャンネルの順序を設定するためのものである。既述のとおり、チャンネルCH1, CH2...CHkからの各入力信号は、CH1 CH2 CH3 ...といったように、順番に信号処理されてもよいし、あるいは予め定めた任意の順序に従って信号処理されてもよい。

30

**【0080】**

この後者の具体例を図7を参照しながら説明する。

**【0081】**

チャンネルCH1はエンジン回転数に係る入力信号であり、2サンプル毎といった頻繁な信号処理を必要とし、一方、チャンネルCH3はストップ（ブレーキ）ランプ信号、CH4はノックセンサ信号であって、12サンプル毎といった比較的ゆっくりしたタイミングで信号処理をすればよい。その中間のチャンネルCH2は水温信号であり、上記の中間の6サンプル毎といったタイミングで信号処理をすればよい。これを図で表すと図10のようになる。

40

**【0082】**

図10はチャンネル処理順序の一例を表す図である。上述した2サンプル毎、6サンプル毎および12サンプル毎等のチャンネル処理順序の指定が分かりやすく表されている。なお図10のサンプリングを1サイクルとして、これが毎サイクル繰り返される。

**【0083】**

このようなチャンネル処理順序の設定や、また機能モジュール3の順次設定（図7）においては、車の場合であると、多様の車種毎に適宜最適なものが設定される。本発明によ

50

れば、どのような車種であっても、パラメータメモリ 6、シーケンスメモリ 7 およびチャンネル順序メモリ 7 5 の内容を外部から書き換えるだけで簡単に対応することができる。つまり図 4 および図 5 に示す「前処理 I C」を多様な車種毎にそれぞれ作り変える必要がない。

**【実施例】**

**【0084】**

**〔実施例1〕**

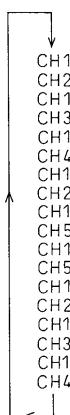

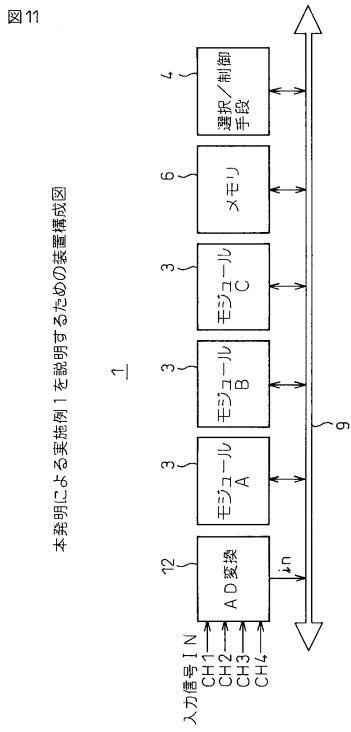

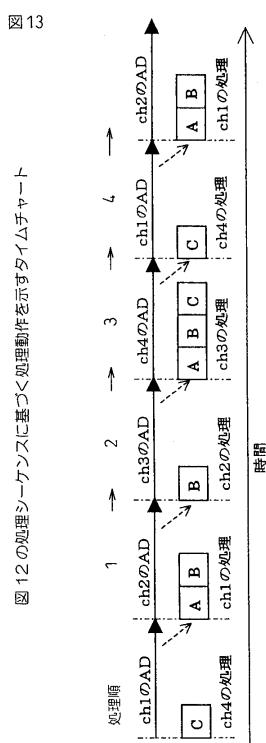

図 1 1 は本発明による実施例 1 を説明するための装置構成図であり、

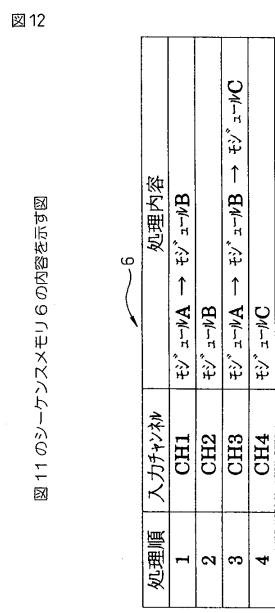

図 1 2 は図 1 1 のシーケンスメモリ 6 の内容を示す図であり、

図 1 3 は図 1 2 の処理シーケンスに基づく処理動作を示すタイムチャートである。 10

**【0085】**

図 1 1 のシーケンスメモリ 6 内には、図 1 2 に示す処理シーケンスマップの一例が示されている。処理順 1 では、入力チャンネル C H 1 に対して、機能モジュール 3 A での信号処理を行い、さらに機能モジュール 3 B での信号処理を行う、ということが指示されている。処理順 2 以降についても同様である。

**【0086】**

すなわち実施例 1 において、各チャンネルの入力信号 i n に対する処理内容は、予めシーケンスメモリ 6 に記述され、このデータを読み出しつつ、処理を行う。そのデータは動作サイクル（処理順）毎の処理内容を記述したマップになっている。かくしてメモリ 6 への記述内容を変更することにより、柔軟に外部システム（E C U）に対応できる。 20

**〔実施例2〕**

図 1 4 は本発明による実施例 2 を説明するためのシーケンスメモリ 6 の内容を示す図であり、

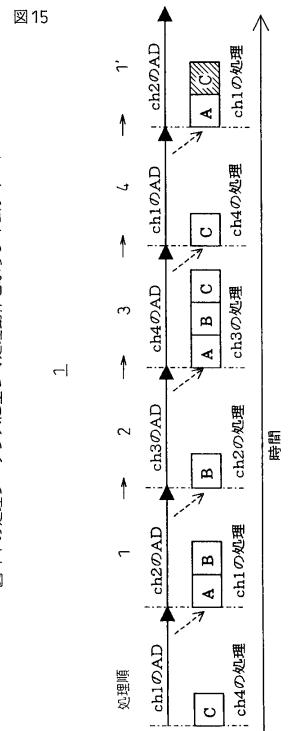

図 1 5 は図 1 4 の処理シーケンスに基づく処理動作を示すタイムチャートである。 25

**【0087】**

実施例 2 において、モジュール選択 / 制御手段 4 は、当該デジタル信号処理装置 1 の動作途中であっても、シーケンスメモリ 6 およびパラメータメモリ 7 の一方または双方の内容を書き換えることを特徴とするものである。ただし図 8 および図 9 においては、シーケンスメモリ 6 の内容変更のみについて示している。 30

**【0088】**

この例では、入力チャンネル C H 1 について、モジュール A → B となっていたのを、途中から、モジュール A → C に変更されている。図 1 5 の処理順 1 がこの変更による動作を表している。 35

**【0089】**

すなわち実施例 2 によると、図 1 1 のシステムにおいて、システム動作中にシーケンスメモリ 6 の内容を書き換えることにより、処理内容を変更する。例えば各機能（演算）モジュール 3 が共有バス 9 を使用していない間に、選択 / 制御手段 4 からメモリ 6 の内容を直接書き換える。 40

**〔実施例3〕**

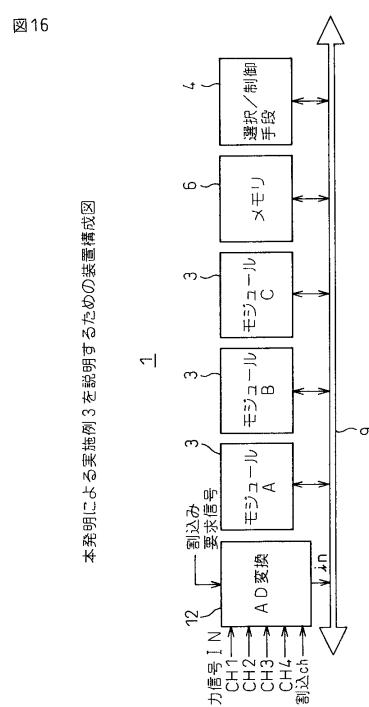

図 1 6 は本発明による実施例 3 を説明するための装置構成図であり、

図 1 7 は図 1 6 のシーケンスメモリ 6 の内容を示す図であり、

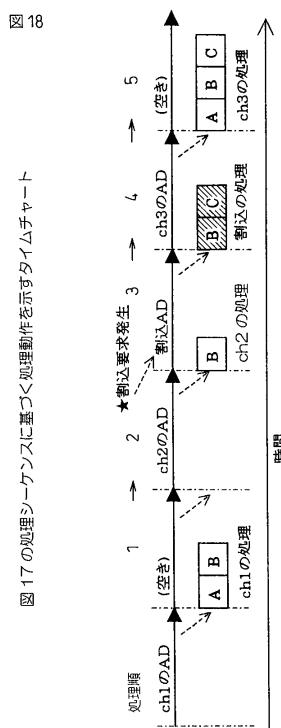

図 1 8 は図 1 7 の処理シーケンスに基づく処理動作を示すタイムチャートである。 45

**【0090】**

実施例 3 において、モジュール選択 / 制御手段 4 は、各チャンネル（C H 1, C H 2 ...）に対応に選択すべき機能モジュール 3 を、指定された一連の処理シーケンスに従って選択すると共に、入力信号 I N として新たな割込み入力信号が発生したときには、その指定された一連の処理シーケンスの中に割込み処理シーケンスを挿入することを特徴とするものである。図 1 7 の下端に示す 1 5 がその割込み処理シーケンスである。 50

**【0091】**

この場合、シーケンスメモリ 6 内には予め空きの処理内容 1 6 を適宜挿入しておいて、

割り込みが発生したときは、その割込みに最も近い空きを利用して当該割込みシーケンスを実行する。図18を参照すると、処理順4の空きの部分で、その割込み処理シーケンスが実行されている。

#### 【0092】

すなわち実施例3によると、図11のシステムにおいては、シーケンスマップで定義できないタイミングで処理を行いたい入力信号INがある場合に対応できない。このためこのような入力信号は、予め定めた入力で受け、割込み用として処理を行う。

#### 【0093】

なお、割込み入力は、他の入力と別系統にしても良いし、他の入力を割込み兼用として使用しても良い。

10

#### 【実施例4】

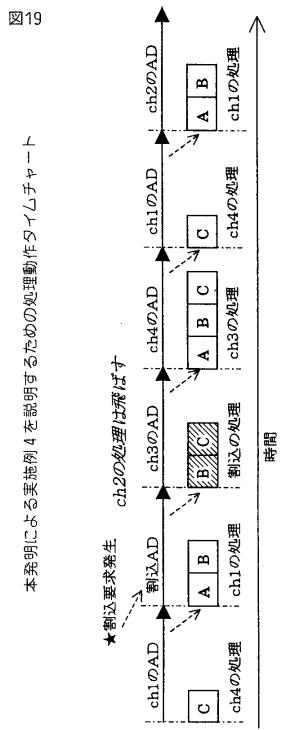

図19は本発明による実施例4を説明するための処理動作タイムチャートである。

#### 【0094】

実施例4においては、前述した割込み処理シーケンス15(図17)の挿入と重なった1つの処理シーケンスにて処理すべきであったチャンネルの入力信号に対する処理については、これを中止することを特徴とするものである。

#### 【0095】

図19においてはch2の処理が上記の中止により飛ばされている。

#### 【0096】

ただしこの場合は、処理結果に重大な影響を与えない処理についてのみ、その飛ばしを行う。

20

#### 【実施例5】

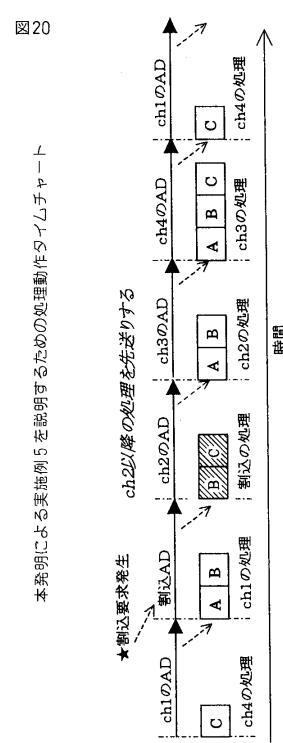

図20は本発明による実施例5を説明するための処理動作タイムチャートである。

#### 【0097】

実施例5においては、上述した割込み処理シーケンス15の挿入と重なった1つの処理シーケンスにて処理すべきであったチャンネルの入力信号に対する処理については一旦保留し、その割込み処理シーケンスが終了し次第、その処理を開始することを特徴とするものである。

#### 【0098】

図20を参照すると、ハッチングを付した「BC」が割込みによる信号処理を表しており、これによりch2以降の信号処理は先送りされる。処理時間の若干の遅れは伴うが、割込みを受け入れることができる。

30

#### 【実施例6】

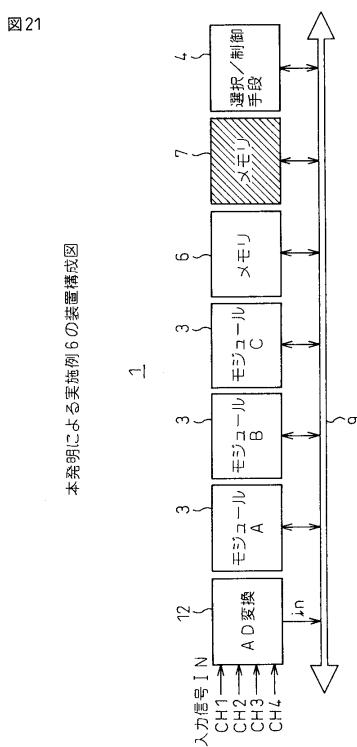

図21は本発明による実施例6の装置構成図であり、

図22は図21のパラメータメモリ7の内容を示す図である。

#### 【0099】

実施例6においてパラメータメモリ7は、チャンネル(CH1, CH2...)毎に設定されたパラメータ情報を予め保持し、かつ、このパラメータメモリ7は全ての機能モジュール3から参照される共有メモリであることを特徴とするものである。

#### 【0100】

40

図22に示す例によれば、パラメータ情報をなすパラメータの数は3であって、これらのパラメータを使用するのは入力チャンネルCH1およびCH3からの入力信号に対してである。

#### 【0101】

すなわち本発明によれば、機能(演算)モジュール3での処理には、例えばフィルタであれば、フィルタ定数をパラメータとして外部から設定するようにしておけば、同じフィルタ演算モジュールを使用しても入力チャンネルによって、異なる遮断周波数で動作させることができる。

#### 【0102】

上記実施例6によると、各チャンネルの入力信号INに定義された機能(演算)モジュ

50

ール 3 での処理実行に必要なパラメータ（定数データ）は、入力信号 IN 毎に予めパラメータメモリ 7 に記述され、これを読み出して、処理を行う。このメモリ 7 は、各モジュール 3 から参照できる共有メモリである。全ての機能（演算）モジュール 3 のパラメータ情報を共有メモリに置くことにより、パラメータの設定を一括して行うことができる。

【実施例 7】

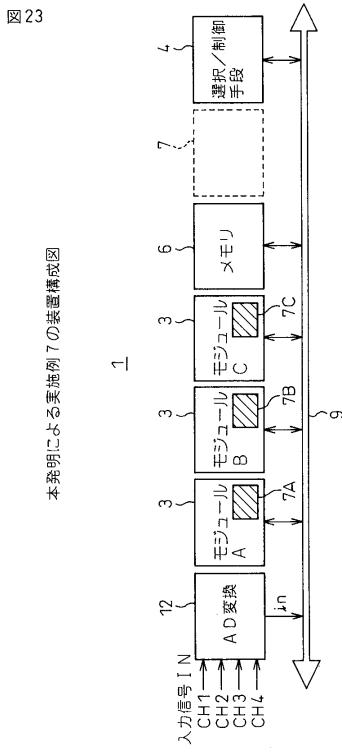

図 2 3 は本発明による実施例 7 の装置構成図である。

【0103】

実施例 7 においてパラメータメモリ 7（図 2 1）は、機能モジュール 3 每に内蔵される個別メモリ 7A, 7B, 7C であって、かつ、これら個別メモリはチャンネル毎に設定されたパラメータ情報を予め保持することを特徴とするものである。

10

【0104】

この実施例 7 によると、各入力のパラメータを格納する領域（パラメータメモリ 7 の内容）を、各モジュール 3 内に持つことになるから、共有バス 9 を通して共有メモリ（図 2 1）をアクセスする場合よりも時間短縮が図れる。

【実施例 8】

実施例 8 においては、前述した信号処理内容の修飾により、その信号処理における動作特性を変更することを特徴とするものである。

【0105】

すなわち入力信号毎のパラメータの動的変更であり、上記実施例 6 および 7 のシステムにおいて、システム動作中に、メモリ 7（7A, 7B …）の内容（パラメータ）を書き換えることにより、処理の動作特性（例えばフィルタの遮断周波数）を変更することができる。

20

【実施例 9】

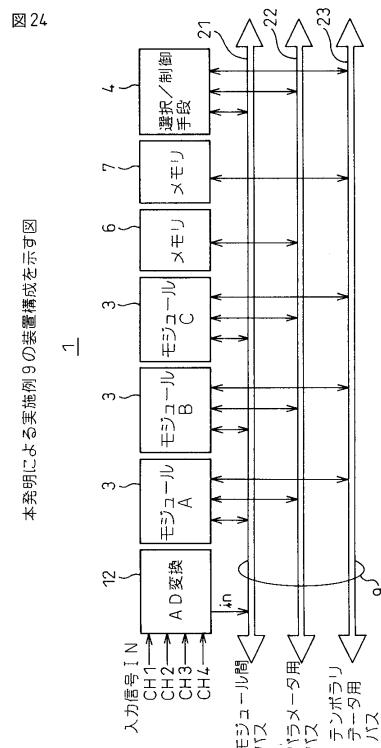

図 2 4 は本発明による実施例 9 の装置構成を示す図である。

【0106】

実施例 9 は、少なくとも入力部 2 と、機能モジュール 3 と、モジュール選択 / 制御手段 4 との間を接続する共有バス 9 を備え、かつ、この共有バス 9 は、信号処理において扱うデータ種別毎に分離した複数の個別バス 2 1 ~ 2 3 からなることを特徴とするものである。

【0107】

30

具体的には、モジュール間バス 2 1、パラメータ用バス 2 2 およびテンポラリデータ用 2 3 である。

【0108】

本発明のシステムは、複数の機能（演算）モジュール、メモリ、全体の動作制御部などで構成するが、それらのデータ受渡しに必要なバスの構成は、その一例として実施例 9 のようにすることができる。すなわち、データの受渡しを複数のバスで行うことができ、各機能（演算）モジュールに必要なデータを受渡しする時間を短縮することができる。つまりモジュール間のデータ授受用（2 1）、パラメータの読み書き用（2 2）、テンポラリデータ（内部の演算における前回値など）の読み書き用（2 3）などのように、データの種類毎に受け渡し用のバスを持つ。

40

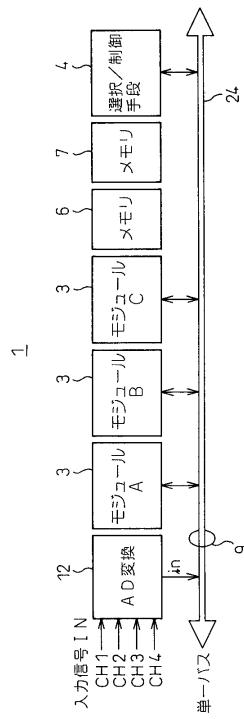

【実施例 10】

図 2 5 は本発明による実施例 10 の装置構成を示す図である。

【0109】

実施例 10 は、少なくとも入力部 2 と、機能モジュール 3 と、モジュール選択 / 制御手段 4 との間を接続する共有バス 9 を備え、かつ、この共有バス 9 は、信号処理において扱う複数種のデータを時分割にて転送する単一バス 2 4 からなることを特徴とするものである。

【0110】

すなわちデータの受渡しは单一のバスによって行う。つまり各機能（演算）モジュールに必要なデータを受渡しするためのバスの回路規模を小さくするために、1 つのバスで構

50

成し、時分割で使用して全ての種類のデータの受渡しを行うようとする。

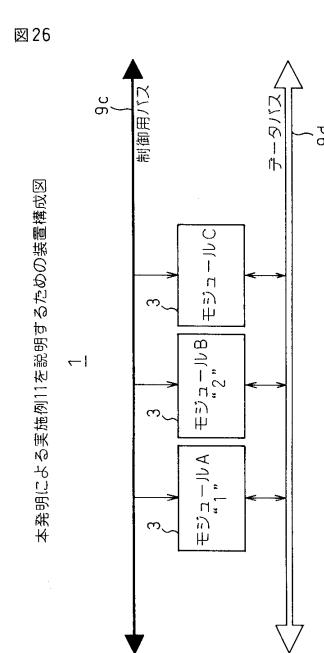

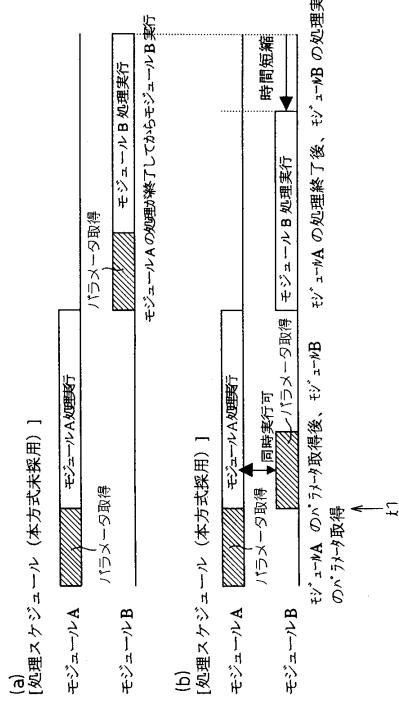

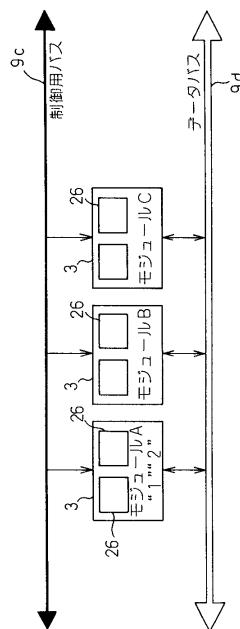

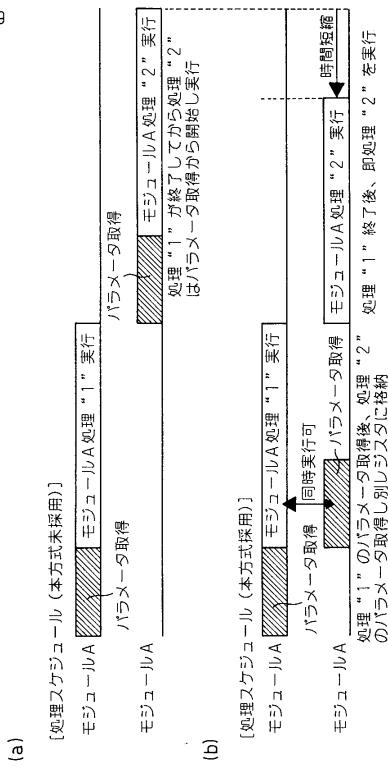

【実施例 1 1】

図 2 6 は本発明による実施例 1 1 を説明するための装置構成図であり、

図 2 7 の ( a ) は実施例 1 1 によらない処理動作、( b ) は実施例 1 1 による処理動作をそれぞれ示すタイムチャートである。

【0 1 1 1】

実施例 1 1 においては、少なくとも 2 つの機能モジュール 3 A , 3 B が順次 (“ 1 ” “ 2 ”) 選択されてそれぞれの信号処理を実行するとき、先行の機能モジュール 3 A での信号処理中に、後行の機能モジュール 3 B にて使用すべきパラメータ情報を取得しておき、その先行の機能モジュール 3 A での信号処理が終了した直後に、その取得したパラメータ情報を用いて後行の該機能モジュール 3 B での信号処理を開始することを特徴とするものである。10

【0 1 1 2】

本発明の機能モジュールにおけるデータ入出力方法について考察すると、入力信号 IN 毎に動作を切り換えるために、コンフィギュレーション・データをその都度読み込む必要がある。しかしこの動作のために時間がかかると、システム全体の動作速度が低下してしまうことになる。これを少ないクロック数で実現する第 1 の方法が実施例 1 1 である。これは同じモジュールを続けて利用しない場合についての方法である。

【0 1 1 3】

図 2 7 特に ( b ) を参照すると、モジュールの設定に際し現在処理を行うモジュール A と次に処理を行うモジュール B とを対にして指定する。そして現在のモジュール A のパラメータ設定が終了した後、次のモジュール B のパラメータ設定をただちに開始 ( 時刻 t 1 ) することにより、現在のモジュール A の処理終了後、次のモジュール B についてのパラメータ設定を省いて時間短縮を図ることができる。すなわち、今回の処理を行う際にモジュール A を使用し、次にモジュール B を使用するという場合、制御用バス 9 c ( 図 2 6 ) により、モジュール A に必要なパラメータなどを送信する。その後、データバス 9 d ( 図 2 6 ) からデータを読み取って演算処理を行う。この場合モジュール A の演算中には、制御用バス 9 c は使用されていないので、モジュール A の演算中に、モジュール B 用のパラメータを設定しておくことができる。これにより、モジュール A から演算結果が出力された際に、モジュール B はただちに動作を開始できる。2030

【実施例 1 2】

図 2 8 は本発明による実施例 1 2 を説明するための装置構成図であり、

図 2 9 の ( a ) は実施例 1 2 によらない処理動作、( b ) は実施例 1 2 による処理動作をそれぞれ示すタイムチャートである。

【0 1 1 4】

実施例 1 2 では、同一の機能モジュール ( 例えば図 1 8 の A ) において、第 1 の信号処理 “ 1 ” と第 2 の信号処理 “ 2 ” とを続けて順次実行するとき、第 1 の信号処理 “ 1 ” の実行中に、第 2 の信号処理 “ 2 ” において使用すべきパラメータ情報を取得しておき、その第 1 の信号処理 “ 1 ” が終了した直後に、その取得したパラメータ情報を用いて第 2 の信号処理 “ 2 ” を開始することを特徴とするものである。40

【0 1 1 5】

これは同じモジュールを続けて利用する場合であり、各モジュール 3 の内部にパラメータ保存用レジスタ 2 6 を複数持ち、現在のモジュール A のパラメータ設定値を取り込んだ後、次のパラメータ設定を引き続いて行うものである。このモジュール A で次の処理を行う時には、レジスタ 2 6 を切り替えることでただちに設定が終了するので、設定時間の短縮が図れる。

【0 1 1 6】

処理によっては、同一のモジュールを複数回使用することがあるが、設定のパラメータが異なる場合、前回使用したパラメータを破棄して新たなパラメータを設定する必要がある。そこで、まず 1 回目のモジュール A のパラメータを送信し、演算処理を行っている間50

に、空いている制御用バス 9 c から 2 回目のパラメータを送信し、保存用として複数用意したレジスタ 2 6 にそのパラメータ値を保存する。モジュール A の 2 回目の演算を行うときには、パラメータ値を取り込むためのバスアクセスをする必要がなくなるので、少ないクロック数で動作することができる。モジュール A の 2 回目の演算中は、別のレジスタ 2 6 は書き込み可能であるので、空いている制御用バス 9 c が使える。このため、3 度以上同一モジュールを使う場合にも同様に少ないクロック数で動作できる。

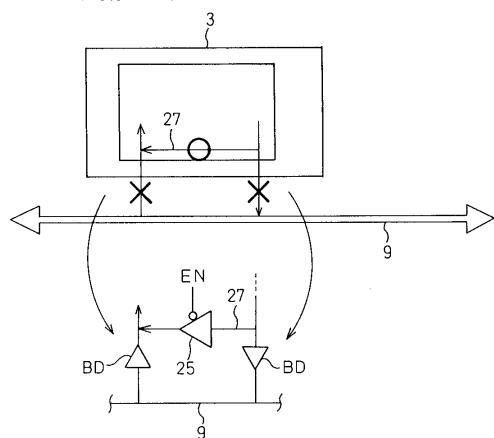

**[実施例 1 3]**

図 3 0 は本発明による実施例 1 3 を説明するための装置構成図である。

**[0 1 1 7]**

実施例 1 3 では、上述した第 1 の信号処理において得られた出力データを当該機能モジュール 3 に戻して上述した第 2 の信号処理に供するとき、その出力データを当該機能モジュール外に送出することなく、例えばゲート 2 5 をイネーブル信号 E N により開いて、当該機能モジュール内の信号経路 2 7 により戻すことを特徴とするものである。なお B D はバスドライバである。

**[0 1 1 8]**

実施例 1 3 も実施例 1 2 のように同じモジュールを続けて利用する場合であり、出力値を一旦バス 9 に出力すると、1 データバス 9 d に出力、2 データバス 9 d から入力、というようにわざわざデータバスにアクセスする必要がある。そこで、同一モジュール 3 を複数回利用する場合には、内部で結合する配線(2 7)を持ち、データの入出力にバス 9 をいちいち利用しない構成とする。当然処理速度は向上する。

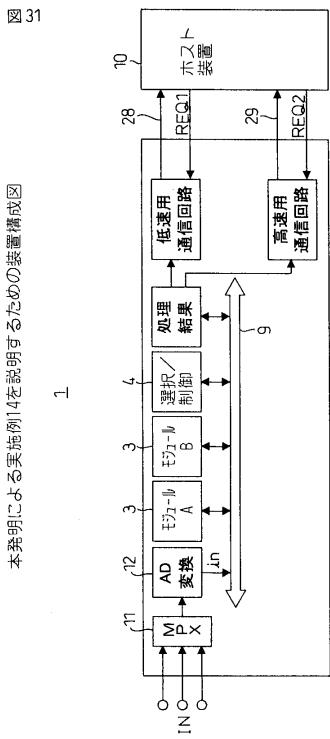

**[実施例 1 4]**

図 3 1 は本発明による実施例 1 4 を説明するための装置構成図である。

**[0 1 1 9]**

本実施例 1 4 ならびに後述する実施例 1 5 および 1 6 は、信号処理による処理結果を外部のホスト装置 1 0 に送信するための通信ラインとして、低速用通信ライン 2 8 と高速用通信ライン 2 9 とを具備することを特徴とするものである。

**[0 1 2 0]**

さらに具体的には、低速用通信ライン 2 8 はホスト装置 1 0 から送信要求 R E Q 1 があったときに一定周期で上記の送信を行う通信ラインであり、一方、高速用通信ライン 2 9 はホスト装置 1 0 からの送信要求 R E Q 2 に応じてその都度上記の送信を行う通信ラインである。

**[0 1 2 1]**

このようにすると、一定周期で送信するデータと、外部(1 0)から要求のあったときに送信するデータとが重なることがなく、通信速度や通信データ量などを抑えることができる。

**[実施例 1 5]**

実施例 1 5 によれば、低速用通信ライン 2 8 および高速用通信ライン 2 9 は、それぞれパラレルラインで構成する。

**[0 1 2 2]**

この実施例 1 5 は、パラレルポート出力インタフェース(I/F)を有する場合であり、外部(1 0)にシステム(1)の処理結果を出力する I/F が、パラレルポートで構成され、外部(1 0)からは取り出したいデータを識別できる信号(アドレスや I/D コードなど)を指定することにより、任意のデータを取り出すことができる。

**[0 1 2 3]**

この実施例の場合、高速で通信を行うことができると共に、通信ラインのクロック速度を抑えることもできる。

**[実施例 1 6]**

実施例 1 6 によれば、低速用通信ライン 2 8 および高速用通信ライン 2 9 は、それぞれシリアルラインで構成する。

**[0 1 2 4]**

10

20

30

40

50

この実施例 16 は、シリアルポート出力インターフェース I / F を有する場合であり、外部(10)にシステム(1)の処理結果を出力する I / F が、シリアルポートで構成されているので、外部(10)からは取り出したいデータを識別できる信号を受けそれに対応するデータを出力するか、あるいは所定の順番でデータ出力を行う。

**【0125】**

この実施例の場合、通信ラインの本数を抑えることができる。

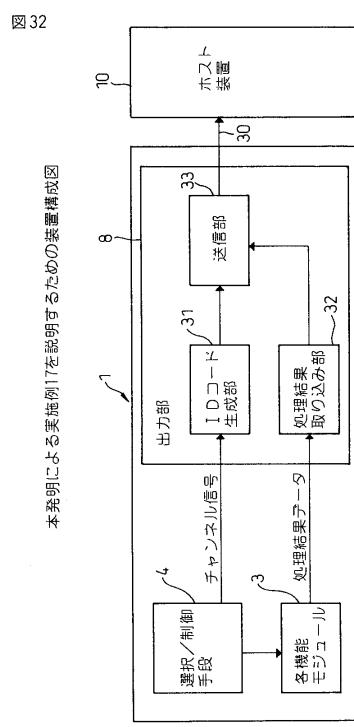

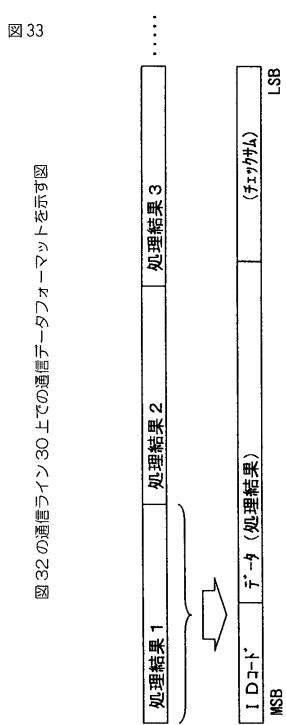

**[実施例 17]**

図 32 は本発明による実施例 17 を説明するための装置構成図であり、

図 33 は図 32 の通信ライン 30 上での通信データフォーマットを示す図である。

**【0126】**

10

実施例 17 に係る出力部 8 (図 1 参照) は、複数のチャンネル (CH1, CH2...) のうちのいずれのチャンネルからの入力信号 IN についての処理結果であるかを示す ID を、当該処理結果のデータにさらに付加して送信することを特徴とするものである。

**【0127】**

上記 ID は、図 33 の下欄の左端に「ID コード」として示される。

**【0128】**

本実施例 17 によれば、どの入力信号を処理した結果なのか見分けられるので、送信順番などを決めておかなくてもよい。

**【0129】**

また、必要なデータだけをホスト装置 10 に出力できる。

20

**【0130】**

図 32 を参照すると、各機能モジュール 3 からの処理結果データは一旦、処理結果取り込み部 32 に取り込まれる。このとき選択 / 制御手段 4 は今取り込まれた処理結果がどのチャンネルの入力信号に対するものか知っているので、そのチャンネル信号を ID コード生成部 31 に送信する。この ID コードは、当該チャンネルを示すものであり、これを送信部 33 において上記の取り込まれた処理結果のデータに付加しさらに通信ライン 30 へ送出する。

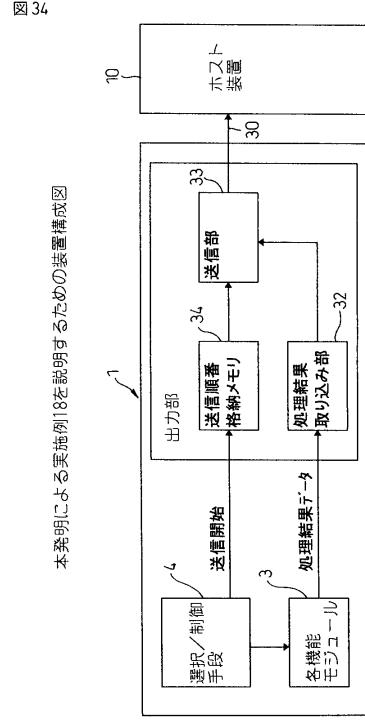

**[実施例 18]**

図 34 は本発明による実施例 18 を説明するための装置構成図である。

**【0131】**

30

実施例 18 は前述の実施例 17 と同様の効果をもたらすものであるが、この実施例 18 において出力部 8 (図 1 参照) は、複数のチャンネルの各入力信号についての処理結果を、各該チャンネルに割り当てた送信順番に従って順次送信することを特徴とするものである。

**【0132】**

本実施例 18 によれば、どの入力信号 IN を処理した結果なのか識別するためのデータを付ける必要がなく、純粋に処理結果のみ送信すればよい。また、ID コードが不要となつた分、送信データ量を少なく抑えられる。

**【0133】**

図 34 を参照すると、図 32 と相違するのは、送信順番格納メモリ 34 が導入されたことであり、手段 4 が送信開始を指示すると、該メモリ 34 内の所定の送信順番で取り込み部 32 内のデータが通信ライン 30 に送出される。

40

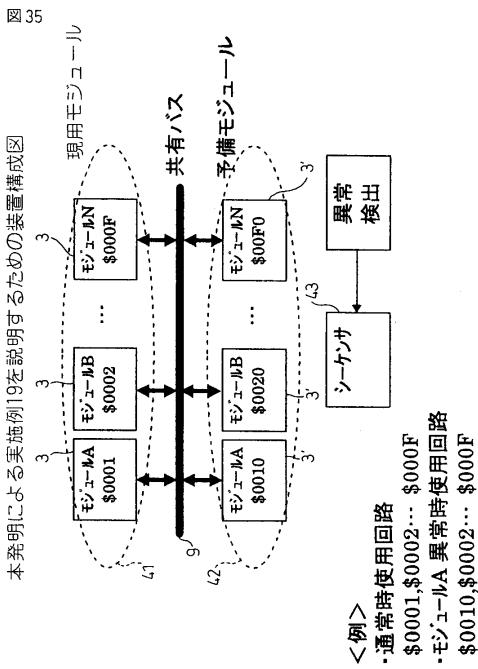

**[実施例 19]**

図 35 は本発明による実施例 19 を説明するための装置構成図である。

**【0134】**

本実施例 19 ならびに後述の実施例 20 ~ 23 は、システムに故障が発生した場合でも常に正確なデータで処理することが求められる場合に対処するものであり、これによりシステムを高信頼度で正常な状態に保つことができる。

**【0135】**

まず本実施例 19 においては、少なくとも複数の機能モジュール 3 の間を接続する共有

50

バス 9 を備えると共に、これら複数の機能モジュール 3 を現用機能モジュール群 4 1 とすると、この現用機能モジュール群 4 1 とミラーをなす予備機能モジュール群 4 2 を、その共有バス 9 を介して接続し、現用機能モジュール群 4 1 内のいずれかの機能モジュール 3 ( 例えは A ) に故障ありと判定されたとき、予備機能モジュール群 4 2 内の対応する機能モジュール 3 ( A ) を選択して使用することを特徴とするものである。

#### 【 0 1 3 6 】

すなわち、共有バス 9 には各モジュールについて同じモジュールを 2 個以上予備として接続しておき、受け手側 ( 例えはホスト装置 1 0 ) もしくは自身 ( 1 ) が本システムの故障を検出した場合には、直ちに故障と判定されたモジュール ( A ) の使用を中止し、予備のモジュールを使用する。

10

#### 【 0 1 3 7 】

図 3 5 を参照すると、「異常検出」があったとき、シーケンサ 4 3 はどのモジュールを使用して信号処理すべきかを指示するためのコマンドを発行する。本図の例では現用のモジュール 3 A に異常を検出したので、これ ( 3 A ) のみを予備のモジュール 3 ( A ) に置き換える。

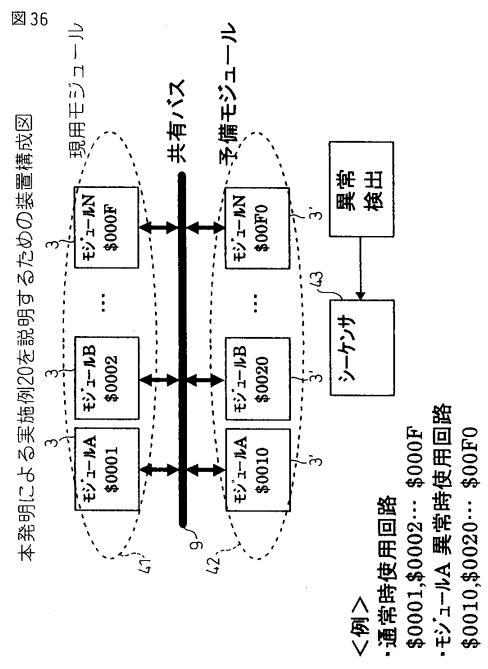

#### 〔 実施例 2 0 〕

図 3 6 は本発明による実施例 2 0 を説明するための装置構成図である。

#### 【 0 1 3 8 】

実施例 2 0 においては、少なくとも複数の機能モジュール 3 の間を接続する共有バス 9 を備えると共に、これら複数の機能モジュール 3 を現用機能モジュール群 4 1 とすると、この現用機能モジュール群 4 1 とミラーをなす予備機能モジュール群 4 2 を、その共有バス 9 を介して接続し、現用機能モジュール群 4 1 内のいずれかの機能モジュール 3 ( 例えは A ) に故障ありと判定されたとき、予備機能モジュール群 4 2 に切り替えて使用することを特徴とするものである。すなわち、現在使用中の現用モジュール 3 を全て一括して予備モジュール 3 に置き換える。

20

#### 〔 実施例 2 1 〕

実施例 2 1 においては、当該デジタル信号処理装置 1 における信号処理を終了したときに、故障を有する機能モジュールについての記録を保持しておき、当該デジタル信号処理装置 1 の再起動時に、その記録をもとに正常な機能モジュールを選択して使用することを特徴とするものである。

30

#### 【 0 1 3 9 】

すなわち、故障を検出した後、一度電源を落とす等システムを再起動させた場合でも故障情報を記憶しておき、故障のないモジュールを使用して動作させることができる。

#### 〔 実施例 2 2 〕

実施例 2 2 においては、信号処理による処理結果を送信すべき外部のホスト装置 1 0 があるとき、各処理結果を生成したモジュールを示す ID を各処理結果のデータに付加してホスト装置 1 0 に送信し、このホスト装置 1 0 において故障の有無を判定し故障を有する機能モジュールを特定した特定情報をホスト装置 1 0 から受信することを特徴とするものである。

#### 【 0 1 4 0 】

40

すなわち、受け手側 ( 1 0 ) への出力データに、その処理に使用したモジュールが識別できる情報 ( ID コード等 ) を付加しておき、その受け手側 ( 1 0 ) で故障モジュールの特定をし、予備のモジュールへ切り替えるための情報を、受け手側 ( 1 0 ) から本装置 1 に送信するというものである。

#### 〔 実施例 2 3 〕

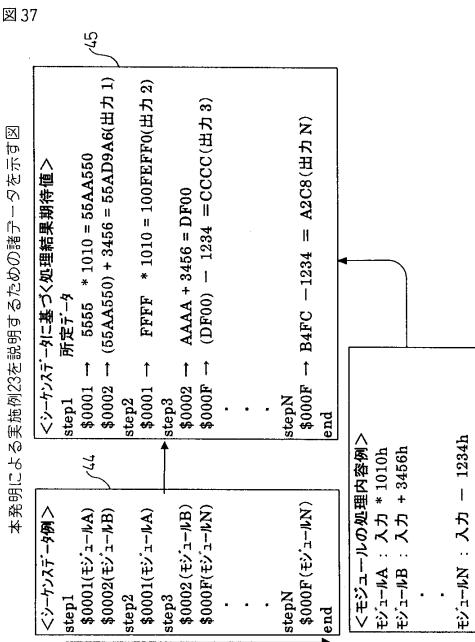

図 3 7 は本発明による実施例 2 3 を説明するための諸データを示す図である。

#### 【 0 1 4 1 】

実施例 2 3 においては、前述した信号処理による処理結果を送信すべき外部のホスト装置 1 0 があるとき、シーケンスメモリ 6 に保持すべき処理シーケンス情報をこのホスト装置 1 0 から読み込むと共に、その読み込み完了時に、このホスト装置 1 0 から当該デジタル

50

信号処理装置 1 に所定のデータを与えてその読み込み処理シーケンスを走らせ、その処理結果をそのホスト装置 10 にて受信し所定の期待値と比較して両者の一致がとれたときに、その読み込み処理シーケンスが正常であることを確認することを特徴とするものである。

#### 【 0 1 4 2 】

本実施例 2 3 ならびに後述する実施例 2 4 ~ 2 6 は、故障診断に関するものである。

#### 【 0 1 4 3 】

シーケンスデータを本システム(1)の外部(10)から読み込む方式を取る場合、シーケンスデータが正確に受信できたかどうかを確認する必要があり、これが実施例 2 3 のチェック方法である。すなわちシーケンスデータが正しくダウンロードできたかどうかを確認するため、所定のデータを使用し、シーケンスを 1 周以上動作させ、受け手側(10)で受信したデータを、予め記憶された期待値と比較する方法をとる。10

#### 【 0 1 4 4 】

図 3 7 を参照すると、4 4 はホスト装置(受け手側)10 から送信されるシーケンスデータであり、このシーケンスをデジタル信号処理装置(システム)1において走らせ、その結果をホスト装置 10 に送り返して、ホスト装置 10 で予め用意していた処理結果期待値データと比較する。すなわち、所定データを入力した場合の出力結果は予め算出できるので、それを期待値として受け手側に記憶させておき、実際の出力結果と合っているかをチェックする。

#### 【 0 1 4 5 】

なお図 3 7 の左下には、機能モジュール 3 における信号処理の内容を示す。ただし一例である。20

#### 〔実施例 2 4 〕

実施例 2 4 は、上記実施例 2 3 において、前述した比較が不一致のとき、ホスト装置 10 から上記の処理シーケンス情報を再送して同様の確認を再度行うことを特徴とするものである。これによって検出精度を向上させることができる。

#### 〔実施例 2 5 〕

実施例 2 5 は、上記実施例 2 4 において、上記の不一致が解消しないとき、外部のユーザにアラームを送出することを特徴とするものである。ここで言うユーザとは、例えば上記 ECU 搭載の車の運転者であり、あるいは、その ECU の生産工場における製品検査員もしくはその ECU を搭載した車の生産工場における製品検査員である。30

#### 〔実施例 2 6 〕

実施例 2 6 は、上記実施例 2 3 において、ホスト装置 10 から読み込んだ上記の処理シーケンス情報をそのまま、ホスト装置 10 内のチェック手段(チェックプログラム)またはこのチェック手段の機能と同等の機能を備えた外部装置に返送し、その返送された処理シーケンス情報と、送信した処理シーケンス情報との一致がとれたときに、前述した読み込み処理シーケンスが正常であることを確認することを特徴とするものである。

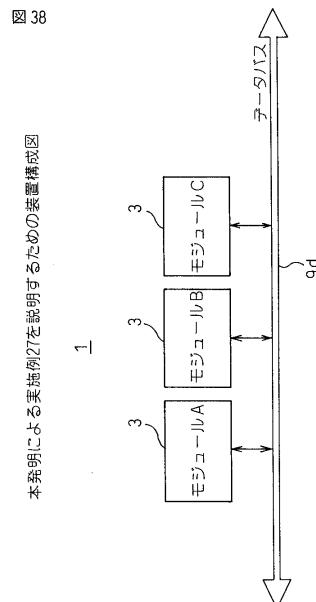

#### 〔実施例 2 7 〕

図 3 8 は本発明による実施例 2 7 を説明するための装置構成図であり、

図 3 9 は図 3 8 において用いるデータのデータ構造の一例を示す図である。40

#### 【 0 1 4 6 】

本実施例 2 7 ならびに後述する実施例 2 8 ~ 3 0 は、機能モジュール 3 を正しく使用したか否か判定するための故障診断に関するものである。

#### 【 0 1 4 7 】

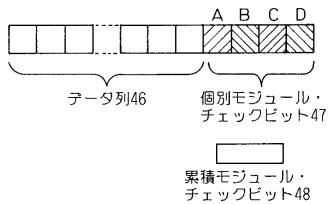

まず実施例 2 7 においては、選択された各機能モジュール 3 での信号処理の終了時に、その信号処理の正常終了を示す個別モジュール・チェックビット 4 7 (図 3 9) を各機能モジュール(A, B, C, D)毎に生成し、そのビット列が、期待されたビット列と一致するか否か判定することにより、これら機能モジュール 3 の故障判定を行うことを特徴とするものである。

#### 【 0 1 4 8 】

10

20

30

40

50

すなわち、データ列46に通過モジュールチェック用ビットを設けておき、機能モジュール3を正しく使用したかを判定する故障診断方式である。

**【0149】**

本発明のようにモジュール3を任意に組み合わせて動作させる場合、使用すべきモジュール3が正しく使われているか把握しておく必要がある。しかし実際の動作中に確認するのは困難である。

**【0150】**

そこで本発明では、故障判定用の専用ビットを持つようにし、モジュール通過時にチェックすることによって、モジュールの故障や不通過を検出できるようにした。

**【0151】**

図38を参照すると、各モジュール3での演算終了後に、その結果のデータをデータバス9dに送出する際、それぞれのチェックビット47を立てるようとする。

**【実施例28】**

実施例28は、実施例27における個別モジュール・チェックビット47を、累積モジュール・チェックビット48に置き換えたものである。

**【0152】**

すなわち、選択された各機能モジュール3での信号処理の終了時に、その信号処理が各機能モジュール3で正常終了する毎に順次加算または減算した累積値を示す累積モジュール・チェックビット48(図39)を生成し、その累積値が、期待された累積値と一致するか否か判定することにより、機能モジュール3の故障判定を行うことを特徴とするものである。

**【実施例29】**

実施例29は、上記実施例27または28において、前述の信号処理による処理結果を送信すべき外部のホスト装置10があるとき、前述した故障判定の期待値を、このホスト装置10から送信された処理シーケンスに基づいて得ることを特徴とするものである。

**【0153】**

すなわち、ホスト装置10はどのチャンネル(CH1, CH2...)についてはどのモジュール3を使用するか、ということを指示するので、それを与えた結果を見て指示どおりに当該モジュールが使用されたかどうかをチェックできる。

**【実施例30】**

実施例30は、上記実施例27または28において、前述した故障判定の期待値を、当該デジタル信号処理装置1がもともと保有する処理シーケンスに基づいて得ることを特徴とするものである。

**【実施例31】**

図40は本発明による実施例31を説明するためのシーケンス図である。

**【0154】**

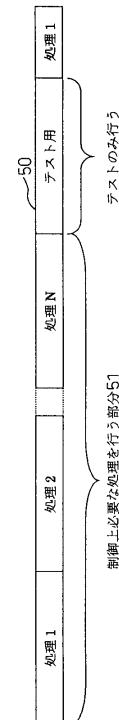

本実施例31ならびに後述する実施例32~35は、デジタル信号処理装置1における故障検出に関するものであり、いわゆるテストパターンを組み込んで故障の検出を行うものである。

**【0155】**

本実施例31においては、前述した処理シーケンス情報の中に、テスト用処理シーケンス50(図40)を組み込んでおき、このテスト用処理シーケンス50を所定の周期で走らせて、複数の機能モジュール3の動作確認を行うことを特徴とするものである。すなわち、各処理を時間を区切って実行しているので、予めテストを行うシーケンスを組み込んでおき、一定周期毎にテストが実行されるようにする。テストが行われる周期は制御上必要な処理51の1周期に限定される必要はなく、処理のどこで実行しても構わない。また複数回実行してもよい。

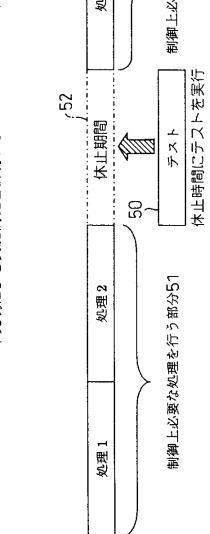

**【実施例32】**

図41は本発明による実施例32を説明するためのシーケンス図である。

**【0156】**

10

20

30

40

50

実施例32においては、前述の処理シーケンス情報の中に、テスト用処理シーケンス50を組み込んでおき、隣接する2つの信号処理（「処理2」と「処理3」）の間に信号処理の休止期間52が存在するとき、そのテスト用処理シーケンス50を休止期間52に走らせて、複数の機能モジュール3の動作確認を行うことを特徴とするものである。

#### 【0157】

すなわち、処理に余裕があるときに、テスト用のシーケンス動作を行うものである。処理に余裕があれば、処理と処理との間に時間的な空きがある場合に、その余裕時間を利用してテストシーケンスを動作させることができる。

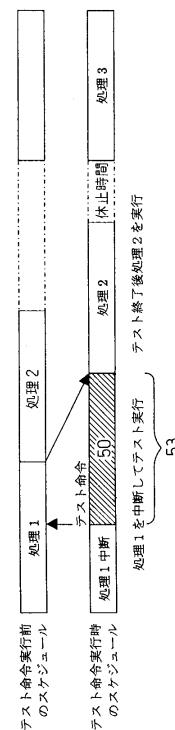

#### 【実施例33】

図42は本発明による実施例33を説明するためのシーケンス図である。

10

#### 【0158】

実施例33においては、前述した処理シーケンス情報の中に、テスト用処理シーケンス50を組み込んでおき、外部（例えばホスト装置10）からテストコマンド（命令）が印加されたとき、その印加タイミングに一致する信号処理についてはこれを中止（中止期間53）してそのテスト用処理シーケンスを強制実行し、複数の機能モジュール3の動作確認を行うことを特徴とするものである。

#### 【0159】

すなわち、外部から任意のタイミングでコマンド（命令）を受けて動作確認を行うものであり、動作中に外部からの命令により強制的にテストを実行させ、他の処理を取り止める。

20

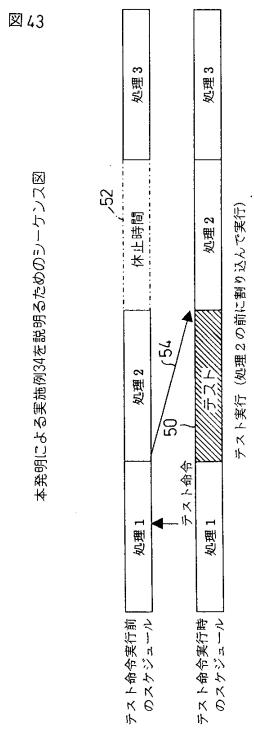

#### 【実施例34】

図43は本発明による実施例34を説明するためのシーケンス図である。

#### 【0160】

実施例34においては、前述した処理シーケンス情報の中に、テスト用処理シーケンス50を組み込んでおき、外部からテストコマンド（命令）が印加されたとき、その印加タイミングに一致する信号処理についてはこれを先送りして（図43の矢印54）、テスト用処理シーケンス50を強制実行し、複数の機能モジュール3の動作確認を行うことを特徴とするものである。

#### 【0161】

すなわち、外部から任意のタイミングでコマンド（命令）を受けて動作確認を行うものであり、動作中に外部から、例えばホスト装置10からの命令により強制的にテストを実行させ、他の処理を遅らせるものである。

30

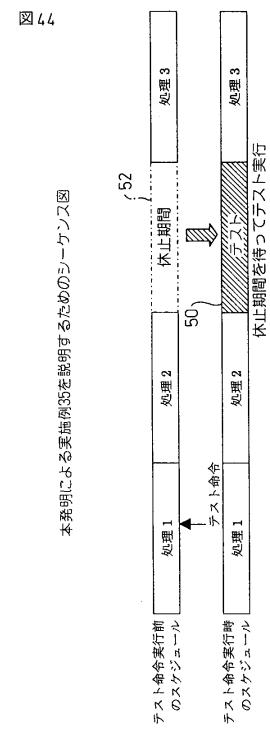

#### 【実施例35】

図44は本発明による実施例35を説明するためのシーケンス図である。

#### 【0162】

実施例35においては、前述した処理シーケンス情報の中に、テスト用処理シーケンス50を組み込んでおき、外部からテストコマンドが印加されたとき、信号処理を休止する休止期間52の到来を待ってそのテスト用処理シーケンス50を実行し、複数の機能モジュール3の動作確認を行うことを特徴とするものである。

#### 【0163】

40

すなわち、外部から任意のタイミングでコマンド（命令）を受けて動作確認を行うものであり、動作中に外部から、例えばホスト装置10からの命令により強制的にテストを実行させ、次の休止期間（空き時間）を待ってテストを実行させるものである。

#### 【実施例36】

以上、実施例1～実施例35を通して本発明に基づくデジタル信号処理装置1の種々の態様について詳しく説明したので、ここで、別の観点から本発明を捉えてみる。

#### 【0164】

本発明の技術思想は、装置構成のみでなく、信号処理の手法としても捉えることができる。その第1のポイントは、下記の点、すなわち、少なくとも入力部2と複数の機能モジュール3とを備えるデジタル信号処理装置1において、

50

( i ) 複数の機能モジュール 3 の各々に、それぞれ固有の信号処理機能を持たせること、

( ii ) その入力部 2 に入力される、複数のチャンネル ( C H 1 , C H 2 ... ) 每の入力信号 I N を、各チャンネル対応に選択される 1 または複数の機能モジュール 3 に与えて信号処理すること、にある。

**【 0 1 6 5 】**

さらに、

上記の各チャンネル対応に使用すべき 1 または複数の機能モジュール 3 を指定するための一連の処理シーケンスを予め保持しておき ( シーケンスマモリ 6 ) 、その一連の処理シーケンスを順次読み出して信号処理を実行すること、にある。 10

**【 0 1 6 6 】**

さらにまた、上記の各機能モジュール 3 における信号処理の内容を修飾するためのパラメータ情報を予め保持しておき ( パラメータメモリ 7 ) 、上記のチャンネル毎の入力信号 I N の性質に応じて対応するパラメータ情報を読み出し、信号処理を実行すること、にある。

**【 実施例 3 7 】**

上記実施例 3 6 に示した本発明の技術思想をさらに発展させると、さらにデジタル信号処理システムを構築することができる。

**【 0 1 6 7 】**

本実施例 3 7 および次に述べる実施例 3 8 は、そのようなデジタル信号処理システムに関するものである。 20

**【 0 1 6 8 】**

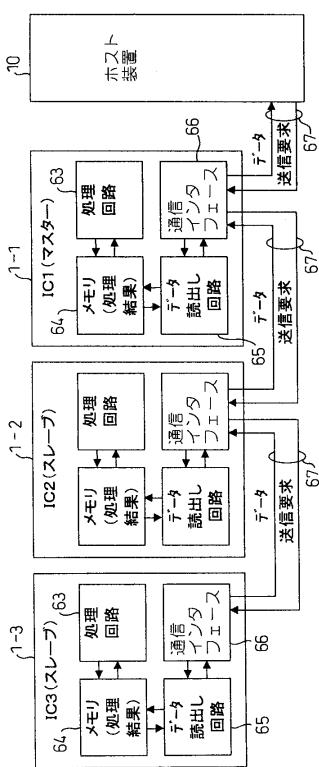

図 4 5 は本発明の実施例 3 7 による第 1 のデジタル信号処理システムを示す図である。

**【 0 1 6 9 】**

本実施例 3 7 に基づく第 1 のデジタル信号処理システム 6 1 は、前述したデジタル信号処理装置 1 に対して、信号処理の処理結果を送受信可能な通信インターフェース 6 6 を設けると共に、係るデジタル信号処理装置と同様のデジタル信号処理装置 1 を複数設け ( 図 4 5 の 1 - 1 , 1 - 2 , 1 - 3 ... ) 、それぞれの通信インターフェース 6 6 を介してこれらをカスケード接続したデジタル信号処理システムである。

**【 0 1 7 0 】**

図 4 5 を参照すると、本処理装置 1 が複数存在するときには、1 つをマスター装置 1 - 1 とし、それ以外をスレーブ装置 1 - 2 , 1 - 3 ... として、カスケード接続ライン 6 7 を用いて各々の装置間を接続し、マスター装置 1 - 1 に全てのスレーブ装置 1 - 2 , 1 - 3 ... の各処理結果を集約する。したがって外部 ( 1 0 ) とはマスター装置 1 - 1 のみを接続するだけで、全ての装置 1 - 2 , 1 - 3 ... からの各処理結果を取り出すことができる。 30

**【 0 1 7 1 】**

各処理装置 1 を I C とした場合、図 4 5 に示すように各 I C ともに、処理回路 6 3 ( モジュール 3 相当 ) と、メモリ 6 4 ( 例えば図 2 の 1 3 相当 ) と、データ読出し回路 6 5 ( 例えば図 2 の 1 4 相当 ) と、先の通信インターフェース 6 6 とを有しており、マスターとなる I C ( 1 - 1 ) から、スレーブとなる I C ( 1 - 2 , 1 - 3 ... ) の処理結果に、送信要求信号を送ることによって、処理結果のデータを読み出すことができる。 40

**【 0 1 7 2 】**

このように、I C を複数 ( 1 - 1 , 1 - 2 , 1 - 3 ... ) 使用することになっても、外部 ( 1 0 ) との通信ライン 3 0 の数は、これらの I C の数分は必要とせず、1 系統のみで良い。なお、スレーブ I C の数は、信号ライン 6 7 上の伝搬遅延が許す限り、制限はない。

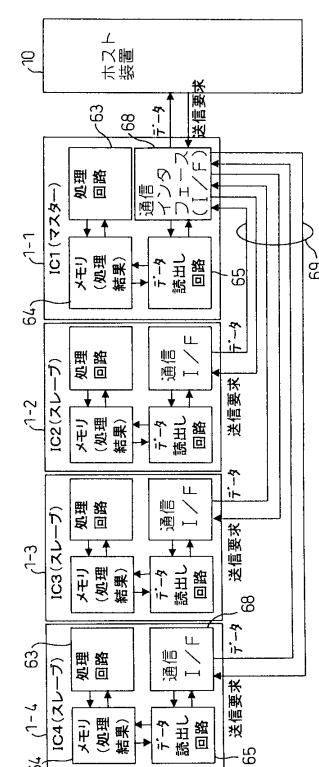

**【 実施例 3 8 】**

図 4 6 は本発明の実施例 3 8 による第 2 のデジタル信号処理システムを示す図である。

**【 0 1 7 3 】**

本実施例 3 8 に基づく第 2 のデジタル信号処理システム 6 2 は、前述したデジタル信号処理装置 1 に対して、信号処理の処理結果を送受信可能な通信インターフェース 6 8 を設け 50

ると共に、係るデジタル信号処理装置1と同様のデジタル信号処理装置1を複数設け(図40の1-1, 1-2, 1-3...)、そのうちの1つをマスター・デジタル信号処理装置1-1となし、その他をスレーブ・デジタル信号処理装置(1-2, 1-3...)となして、それぞれの通信インターフェース68を介してこれらを、マスター・デジタル信号処理装置1-1を中心としてスター接続することを特徴とするものである。

#### 【0174】

図46を参照すると、本処理装置1が複数存在するときには、1つをマスター装置1-1とし、それ以外をスレーブ装置1-2, 1-3...とし、スター接続ライン69を用いて各装置(1-1, 1-2, 1-3...)を接続し、マスター装置1-1に全てのスレーブ装置1-2, 1-3...の各処理結果を集約する。したがって外部(10)とはマスター装置1-1のみを接続するだけで、全ての装置1-2, 1-3...からの処理結果を取り出すことができる。

10

#### 【0175】

ここで、

各処理装置1をICとした場合、図46に示すように各ICとともに、前述の回路63, 64, 65および先の通信インターフェース68を有しており、マスターとなるIC(1-1)から、直接それぞれのスレーブICの処理結果に対する送信要求信号を送ることによって、処理結果のデータを読み出すことができる。

#### 【0176】

このように、ICを複数(1-1, 1-2, 1-3...)使用することになっても、外部(10)との通信ライン30の数は、これらのICの数分は必要とせず、1系統のみで良い。また、上記のシステム61(図45)に比べ、どのICの結果も同じ応答速度で取得可能である。

20

#### 【実施例39】

これまでの実施例1~38は、例えば図4を参照すると、前処理IC(デジタル信号処理装置1)に主として向けられてきた。

#### 【0177】

本実施例39ならびに後述する実施例40~42は、今度は、その図4を参照すると、マイコン(ホスト装置10)そのものに向けたものである。

#### 【0178】

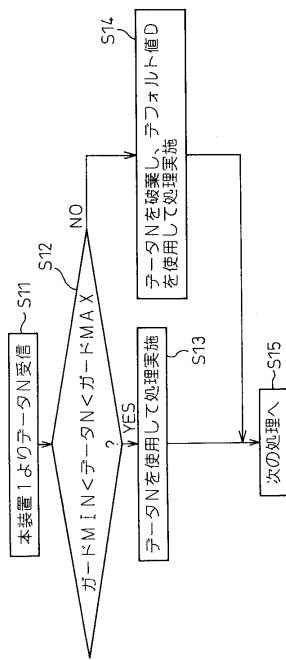

図47は本発明の実施例39におけるホスト装置10の動作を表すフローチャートである。

30

#### 【0179】

なお、本実施例39と次に述べる実施例40は、主としてフェイルセーフの実現に向けたものである。

#### 【0180】

システム例えば図4のECUが故障した場合でも、必要最低限の動作をさせる必要がある。例えばそのECUによる自動車のエンジン制御での使用においては、ECUが故障した場合に最適な燃料噴射制御等はできないにしても、何とか修理工場まで辿り着けるだけの動作ができれば十分である。このような場合、処理におけるデータは必ずしも正確な値でなくても良い場合がある。

40

#### 【0181】

本装置1から出力された値が正常であるかどうかを受け手側のホスト装置10で判断し、異常ありと判断した場合には、この受け手側(10)から本装置1にその異常を知らせることで、その後、本装置1を搭載する製品(自動車)が必要最小限の動作を確保できるようにする。

#### 【0182】

図47は、異常と判定されたデータについては本装置1からの出力値を破棄し、受け手側の装置10で予め用意したデフォルト値を使用することを表している。

#### 【0183】

10

20

30

40

50

すなわち実施例 3 9 のホスト装置 1 0 は、前述のデジタル信号処理装置 1 から送信される信号処理による処理結果のデータを受信するホスト装置であって、その処理結果のデータに異常があるとき、このデータを破棄しこれに代えて予め保持していたデフォルト値を使用することを特徴とするものである。

**【 0 1 8 4 】**

図 4 7 を参照すると、

ステップ S 1 1 : ホスト装置 1 0 は、本装置 1 から送信されたデータ N を受信する。データ N は、前述した信号処理 N ( N = 1 , 2 , 3 , 4 ... ) によってそれぞれ演算されるデータである。

**【 0 1 8 5 】**

ステップ S 1 2 : そのデータ N が正常な範囲に入っているとホスト装置 1 0 が判断すれば ( Y E S ) 、

ステップ S 1 3 : ホスト装置 1 0 は、そのデータ N を使用して、所定の演算処理を実施する。

**【 0 1 8 6 】**

ステップ S 1 4 : もし上記ステップ S 1 2 の結果が N O であれば、その受信したデータ N は破棄し、これに代えてデフォルト値 D を使用して、上記の所定の演算処理を実施する。実施例 3 9 のポイントはこのステップ S 1 4 にある。

**【 0 1 8 7 】**

ステップ S 1 5 : さらにデータ ( N + 1 ) を受信して次の演算処理に入る。

**[ 実施例 4 0 ]**

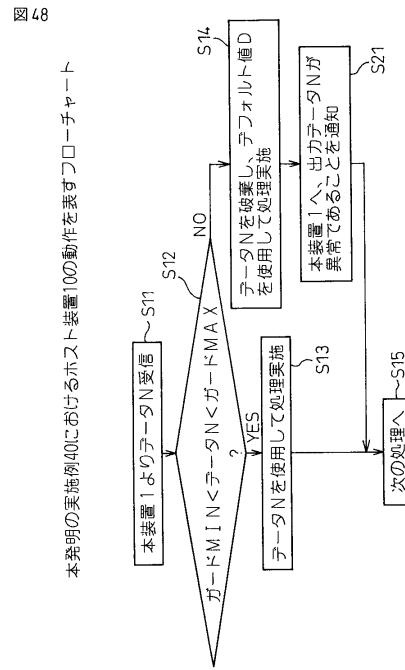

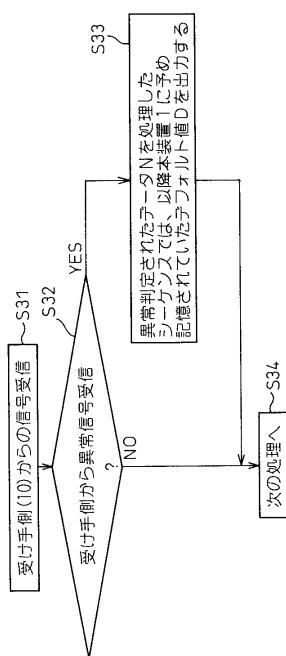

図 4 8 は本発明の実施例 4 0 におけるホスト装置 1 0 の動作を表すフローチャートであり、

図 4 9 は図 4 8 の動作と連携する信号処理装置 1 の動作を表すフローチャートである。

**【 0 1 8 8 】**

これら図 4 8 および図 4 9 は、異常と判定された出力値がどれであったかを、受け手側 ( 1 0 ) から本装置側 ( 1 ) に知らせることにより、本装置 1 からその出力値のデフォルト値を出力することを表す。

**【 0 1 8 9 】**

すなわち実施例 4 0 のホスト装置 1 0 は、前述のデジタル信号処理装置 1 から送信される信号処理による処理結果のデータを受信するホスト装置であって、その処理結果のデータに異常があると判定したとき、その異常データを生じさせた信号処理を特定し、この特定情報をその信号処理装置 1 に返送して、その特定された信号処理に対応する、該装置 1 に予め保持していたデフォルト値 D を使用させる。

**【 0 1 9 0 】**

図 4 8 を参照すると、ステップ S 2 1 が本実施例 4 0 の特徴をなすものであり、この S 2 1 での「通知」により、図 4 9 のフローチャートが装置 1 にて起動される。

**【 0 1 9 1 】**

図 4 9 を参照すると、

ステップ S 3 1 : 本装置 1 は、処理結果の受け手側であるホスト装置 1 0 から送信される信号を受信する。

**【 0 1 9 2 】**

ステップ S 3 2 : その受信した信号は、図 4 8 のステップ S 2 1 に起因する異常信号か判断し、 Y E S であると、

ステップ S 3 3 : 異常であるとホスト装置 1 0 で判定されたデータ N を処理した既述の処理シーケンス ( 例えば図 1 4 の処理順 1 , 2 , 3 ... 等参照 ) についてには、それ以降の同処理シーケンスによる処理結果としては、本装置 1 内で予め用意していたデフォルト値を出力するようとする。

**【 0 1 9 3 】**

ステップ S 3 4 : 本装置 1 はさらに続く処理シーケンスに入る。

10

20

30

40

50

## 【実施例 4 1】

実施例 4 1 は、既述した実施例 2 2 に対応するものであるが、本実施例 4 1 におけるホスト装置 1 0 は、前述のデジタル信号処理装置 1 から送信される信号処理による処理結果のデータを受信するホスト装置であって、各処理結果のデータに付加して装置 1 から送信された、各処理結果を生成した機能モジュール 3 を示す ID を受信する。そしてある機能モジュール 3 ( 例えば B ) に故障があると判定したときには、当該機能モジュール ( B ) の ID を装置 1 に送信してその故障箇所を特定させることを特徴とするものである。

## 【実施例 4 2】

最後の実施例 4 2 は、既述した実施例 2 3 に対応するものであるが、本実施例 4 2 におけるホスト装置 1 0 は、前述のデジタル信号処理装置 1 から送信される信号処理による処理結果のデータを受信するホスト装置であって、各チャンネル ( C H 1 , C H 2 ... ) 対応に選択すべき 1 または複数の機能モジュール 3 を指定するための前述した処理シーケンス情報を装置 1 に送信して読み込ませる。さらに所定のデータを送信してその処理シーケンスを走らせる。装置 1 0 はその処理結果のデータを装置 1 から受信して所定の期待値と比較する。そしてその比較結果によって、前述の読み込ませた処理シーケンス情報の正常性を判定することを特徴とするものである。

10

## 【産業上の利用可能性】

## 【0 1 9 4】

本発明に係るデジタル信号処理回路は、複数種類の入力信号に対し、複数種類の機能モジュールによって所望の信号処理を行う必要があるシステムに利用できる。この場合、単一の I C で、入力信号と機能モジュールとの任意の組合せに柔軟に対応することができる。

20

## 【図面の簡単な説明】

## 【0 1 9 5】

【図 1】本発明に基づくデジタル信号処理装置の基本構成を示す図である。

【図 2】図 1 の基本構成をさらに具体的に示す図である。

【図 3】図 2 の処理動作を説明するためのタイムチャートである。

【図 4】本発明が適用される 1 システム例を示す図である。

【図 5】図 4 に対して付加すべき本発明に係る書き込み手段を示す図である。

【図 6】図 2 に示す選択 / 制御手段 4 とその周辺をより具体的に示す図である。

30

【図 7】各チャンネルの入力信号の例とそれを処理する機能モジュールの例を示す図である。

【図 8】図 6 に示す選択 / 制御手段 4 の動作例を示すフローチャートである。

【図 9】図 8 のフローチャートに対応するタイムチャートである。

【図 1 0】チャンネル処理順序の一例を表す図である。

【図 1 1】本発明による実施例 1 を説明するための装置構成図である。

【図 1 2】図 1 1 のシーケンスマモリ 6 の内容を示す図である。

【図 1 3】図 1 2 の処理シーケンスに基づく処理動作を示すタイムチャートである。

【図 1 4】本発明による実施例 2 を説明するためのシーケンスマモリ 6 の内容を示す図である。

40

【図 1 5】図 1 4 の処理シーケンスに基づく処理動作を示すタイムチャートである。

【図 1 6】本発明による実施例 3 を説明するための装置構成図である。

【図 1 7】図 1 6 のシーケンスマモリ 6 の内容を示す図である。

【図 1 8】図 1 7 の処理シーケンスに基づく処理動作を示すタイムチャートである。

【図 1 9】本発明による実施例 4 を説明するための処理動作タイムチャートである。

【図 2 0】本発明による実施例 5 を説明するための処理動作タイムチャートである。

【図 2 1】本発明による実施例 6 の装置構成図である。

【図 2 2】図 2 1 のパラメータメモリ 7 の内容を示す図である。

【図 2 3】本発明による実施例 7 の装置構成図である。

【図 2 4】本発明による実施例 9 の装置構成を示す図である。

50

【図25】本発明による実施例10の装置構成を示す図である。

【図26】本発明による実施例11を説明するための装置構成図である。

【図27】(a)は実施例11によらない処理動作、(b)は実施例11による処理動作をそれぞれ示すタイムチャートである。

【図28】本発明による実施例12を説明するための装置構成図である。

【図29】(a)は実施例12によらない処理動作、(b)は実施例12による処理動作をそれぞれ示すタイムチャートである。

【図30】本発明による実施例13を説明するための装置構成図である。

【図31】本発明による実施例14を説明するための装置構成図である。

【図32】本発明による実施例17を説明するための装置構成図である。

【図33】図32の通信ライン30上での通信データフォーマットを示す図である。

【図34】本発明による実施例18を説明するための装置構成図である。

【図35】本発明による実施例19を説明するための装置構成図である。

【図36】本発明による実施例20を説明するための装置構成図である。

【図37】本発明による実施例23を説明するための諸データを示す図である。

【図38】本発明による実施例27を説明するための装置構成図である。

【図39】図38において用いるデータのデータ構造の一例を示す図である。

【図40】本発明による実施例31を説明するためのシーケンス図である。

【図41】本発明による実施例32を説明するためのシーケンス図である。

【図42】本発明による実施例33を説明するためのシーケンス図である。

【図43】本発明による実施例34を説明するためのシーケンス図である。

【図44】本発明による実施例35を説明するためのシーケンス図である。

【図45】本発明の実施例37による第1のデジタル信号処理システムを示す図である。

【図46】本発明の実施例38による第2のデジタル信号処理システムを示す図である。

【図47】本発明の実施例39におけるホスト装置10の動作を表すフローチャートである。

【図48】本発明の実施例40におけるホスト装置10の動作を表すフローチャートである。

【図49】図48の動作と連携する信号処理装置1の動作を表すフローチャートである。

#### 【符号の説明】

【0196】

1 ... デジタル信号処理装置

2 ... 入力部

3 ... 機能モジュール

4 ... 選択 / 制御手段

5 ... メモリ手段

6 ... シーケンスメモリ

7 , 7A , 7B , 7C ... パラメータメモリ

8 ... 出力部

9 ... 共有バス

10 ... ホスト装置(マイコン)

11 ... 分離部(MPX)

12 ... A/D変換部

13 ... 処理結果バッファ

14 ... 出力分配部

15 ... 割込み処理シーケンス

21 , 22 , 23 ... 個別バス

24 ... 単一バス

26 ... パラメータ保存用レジスタ

27 ... 信号経路

10

20

30

40

50

- 2 8 ... 低速用通信ライン

2 9 ... 高速用通信ライン

3 0 ... 通信ライン

4 1 ... 現用モジュール群

4 2 ... 予備モジュール群

4 7 ... 個別モジュール・チェックビット

5 0 ... テスト処理シーケンス

5 2 ... 休止期間

5 3 ... 中止期間

6 1 ... 第1のデジタル信号処理システム

6 2 ... 第2のデジタル信号処理システム

6 6 ... 通信インターフェース

6 7 ... カスケード接続ライン

6 8 ... 通信インターフェース

6 9 ... スター接続ライン

7 1 ... シーケンス書込み手段

7 2 ... パラメータ書込み手段

7 3 ... シーケンスマモリ

7 4 ... パラメタメモリ

7 5 ... チャンネル順序メモリ

8 1 ... メモリ読出し部

8 2 ... モジュール制御部

10

20

【図1】

本発明に基づくデジタル信号処理装置の基本構成を示す図

【図2】

図1の基本構成をさらに具体的に示す図

【図3】

図3

図2の処理動作を説明するためのタイムチャート

【図4】

図4

本発明が適用される1システム例を示す図

【図5】

図5

図4に対して付加すべき本発明に係る書き込み手段を示す図

【図6】

図6

図2に示す選択/制御手段4とその周辺をより具体的に示す図

【図7】

図7

各チャンネルの入力信号の例とそれを処理する機能モジュールの例を示す図

【図8】

図8 図6に示す選択/制御手段4の動作例を示すフローチャート

【図9】

図9

図8のフローチャートに対応するタイムチャート

【図10】

図10 チャンネル処理順序の一例を表す図

【図 1 1】

本発明による実施例1を説明するための装置構成図

【図 1 3】

本発明による実施例2に基づく処理動作を示すタイムチャート

【図 1 2】

図11のシーケンスメモリ6の内容を示す図

【図 1 4】

| 6    |         |                |

|------|---------|----------------|

| 処理順  | 入力チャンネル | 処理内容(変更前)      |

| 1 1' | CH1     | モジュールA → B     |

| 2    | CH2     | モジュールB         |

| 3    | CH3     | モジュールA → B → C |

| 4    | CH4     | モジュールC         |

本発明による実施例2を説明するためのシーケンスメモリ6の内容を示す図

【図 15】

図 14 の処理シーケンスに基づく処理動作を示すタイムチャート

【図 16】

本発明による実施例 3 を説明するための装置構成図

【図 17】

| 処理順 | 入力チャンネル | 処理内容                  |       |

|-----|---------|-----------------------|-------|

|     |         | モジューA                 | モジューB |

| 1   | CH1     | モジューA → モジューB         |       |

| 2   | —       | (空き)                  |       |

| 3   | CH2     | モジューB                 |       |

| 4   | —       | (空き)                  |       |

| 5   | CH3     | モジューA → モジューB → モジューC |       |

| 6   | —       | (空き)                  |       |

| 7   | CH4     | モジューC                 |       |

| 8   | —       | (空き)                  |       |

| 割込  | 割込 chn  | モジューB → モジューC         |       |

|     |         |                       | 15    |

図 16 のシーケンスマップの例

【図 18】

図 17 の処理シーケンスに基づく処理動作を示すタイムチャート

【図19】

【図20】

【図21】

【 図 2 2 】

図22 図21のパラメータモリナの内容を示す図

| 入力チャンネル | パラメータ1 | パラメータ2 | パラメータ3 |

|---------|--------|--------|--------|

| C H 1   | a11    | a12    | a13    |

| C H 2   | —      | —      | —      |

| C H 3   | a31    | a32    | a33    |

| C H 4   | —      | —      | —      |

【図23】

図23

【図24】

図24

【図25】

図25

【図26】

図26

【図 27】

図27

(a) は実施例12にようない処理動作、(b) は実施例12による処理動作を

それぞれ示すタイムチャート

【図 28】

図28

本発明による実施例12を説明するための装置構成図

【図 29】

図29

(a) は実施例12にようない処理動作、(b) は実施例12による処理動作を

それぞれ示すタイムチャート

【図 30】

図30

本発明による実施例13を説明するための装置構成図

【図 3 1】

本発明による実施例4を説明するための装置構成図

【図 3 2】

本発明による実施例17を説明するための装置構成図

【図 3 3】

図32の通信ライン30上で通信データフォーマットを示す図

【図 3 4】

本発明による実施例18を説明するための装置構成図

【図35】

【図37】

【 図 3 6 】

【図38】

大學生の上級書類27卷説明するための参考書

【図 39】

図39

図38において用いるデータのデータ構造の一例を示す図

【図 40】

図40

本発明による実施例3を説明するためのシーケンス図

【図 41】

図41

【図 42】

図42

本発明による実施例3を説明するためのシーケンス図

【図43】

【 図 4 5 】

本発明の実施例37による第1のデジタル信号処理システムを示す図

61

【図4-4】

卷之三

【図46】

本聲明の実施例3817による第20章の信号処理

【図47】

本発明の実施例39におけるホスト装置10の動作を表すフローチャート

【 図 4 8 】

【 図 4 9 】

図 4-8 の動作と連携する信号処理装置 1 の動作を表すフローチャート

---

フロントページの続き

(72)発明者 橋本 欣和

兵庫県神戸市兵庫区御所通1丁目2番28号 富士通テン株式会社内

(72)発明者 笠目 知秀

兵庫県神戸市兵庫区御所通1丁目2番28号 富士通テン株式会社内

(72)発明者 朝山 信徳

兵庫県神戸市兵庫区御所通1丁目2番28号 富士通テン株式会社内

(72)発明者 清水 雄一郎

兵庫県神戸市兵庫区御所通1丁目2番28号 富士通テン株式会社内

審査官 高瀬 勤

(56)参考文献 特開2001-281016(JP,A)

特開平09-269870(JP,A)

特開平02-010454(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 13 / 12