(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4651359号

(P4651359)

(45) 発行日 平成23年3月16日(2011.3.16)

(24) 登録日 平成22年12月24日(2010.12.24)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12 501W

請求項の数 11 (全 39 頁)

(21) 出願番号 特願2004-315998 (P2004-315998)

(22) 出願日 平成16年10月29日 (2004.10.29)

(65) 公開番号 特開2006-128455 (P2006-128455A)

(43) 公開日 平成18年5月18日 (2006.5.18)

審査請求日 平成19年10月25日 (2007.10.25)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 嶋貫 好彦

北海道千歳市泉沢1007番地39 株式

会社ルネサス北日本セミコンダクタ内

審査官 大塚 徹

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

平面形状が四角形から成る基材層と、前記基材層の主面に設けられた複数の配線と、前記基材層の各辺に沿って配置され、前記複数の配線のそれぞれと一体に形成された複数の接続端子と、前記基材層の周縁部及び前記複数の接続端子が露出するように前記複数の配線を覆う絶縁膜と、前記絶縁膜において前記複数の接続端子よりも内側の領域に形成され、前記複数の配線のそれぞれの一部及び前記基材層の一部を露出する開口部とを有する配線基板を準備する工程、

複数の電極が形成された主面と、前記主面と対向する裏面とを有する半導体チップを準備する工程、

前記絶縁膜において前記開口部よりも内側の領域に供給されたペースト状の接着材を介して、前記半導体チップの裏面が前記配線基板の主面と対向するように、前記半導体チップを前記配線基板の主面上に搭載する工程、

前記半導体チップの前記複数の電極と前記配線基板の前記複数の接続端子とを複数のボンディングワイヤを介してそれぞれ電気的に接続する工程、

前記半導体チップ、前記複数のボンディングワイヤ、及び前記配線基板の主面を樹脂で封止する工程、

を含み、

前記半導体チップは、前記半導体チップの端部が前記絶縁膜の前記開口部と平面的に重なるように、前記配線基板の主面上に搭載され、

10

20

前記半導体チップ正面、前記半導体チップの側面、及び前記半導体チップの裏面の一部を前記樹脂で覆うように封止することを特徴とする半導体装置の製造方法。

**【請求項 2】**

請求項 1 記載の半導体装置の製造方法において、

前記複数のポンディングワイヤの接続は、キャピラリを用いて行われることを特徴とする半導体装置の製造方法。

**【請求項 3】**

請求項 1 記載の半導体装置の製造方法において、

前記開口部は、前記半導体チップの端部に沿って形成されていることを特徴とする半導体装置の製造方法。 10

**【請求項 4】**

請求項 1 記載の半導体装置の製造方法において、

前記開口部の平面形状は、リング状に形成されていることを特徴とする半導体装置の製造方法。 10

**【請求項 5】**

請求項 1 記載の半導体装置の製造方法において、

前記半導体チップの平面形状は四角形から成り、

前記半導体チップは、前記半導体チップの各辺が前記配線基板の各辺と並ぶように前記配線基板の主面上に搭載され、 20

前記開口部は、前記半導体チップの各辺に沿って形成され、

前記開口部の角部は、前記配線基板の角部に向かって後退していることを特徴とする半導体装置の製造方法。 20

**【請求項 6】**

請求項 5 記載の半導体装置の製造方法において、

前記開口部の各辺のそれぞれの一部は、前記配線基板の各辺に向かって後退していることを特徴とする半導体装置の製造方法。 20

**【請求項 7】**

平面形状が四角形から成る基材層と、前記基材層の正面に設けられた複数の配線と、前記基材層の各辺に沿って配置され、前記複数の配線のそれぞれと一体に形成された複数の接続端子と、前記基材層の周縁部及び前記複数の接続端子が露出するように前記複数の配線を覆う絶縁膜と、前記絶縁膜において前記複数の接続端子よりも内側の領域に形成され、前記複数の配線のそれぞれの一部及び前記基材層の一部を露出する開口部とを有する配線基板と、 30

前記絶縁膜において前記開口部よりも内側の領域に供給されたペースト状の接着材と、

複数の電極が形成された正面と、前記正面と対向する裏面とを有し、前記裏面が前記配線基板の正面と対向するように、前記接着材を介して前記配線基板の正面に搭載された半導体チップと、

前記半導体チップの前記複数の電極と前記配線基板の前記複数の接続端子とをそれぞれ電気的に接続する複数のポンディングワイヤと、 40

前記半導体チップ、前記複数のポンディングワイヤ、及び前記配線基板の正面を封止する封止樹脂と、

を含み、

前記開口部は、前記絶縁膜において前記半導体チップの端部と平面的に重なる領域に形成されており、

前記封止樹脂は、前記半導体チップ正面、前記半導体チップの側面、及び前記半導体チップの裏面の一部を覆うように形成されていることを特徴とする半導体装置。 40

**【請求項 8】**

請求項 7 記載の半導体装置において、

前記開口部は、前記半導体チップの端部に沿って形成されていることを特徴とする半導体装置。 50

**【請求項 9】**

請求項7記載の半導体装置において、

前記開口部の平面形状は、リング状に形成されていることを特徴とする半導体装置。

**【請求項 10】**

請求項7記載の半導体装置において、

前記半導体チップの平面形状は四角形から成り、

前記半導体チップは、前記半導体チップの各辺が前記配線基板の各辺と並ぶように前記配線基板の主面上に搭載され、

前記開口部は、前記半導体チップの各辺に沿って形成され、

前記開口部の角部は、前記配線基板の角部に向かって後退していることを特徴とする半導体装置。 10

**【請求項 11】**

請求項10記載の半導体装置において、

前記開口部の各辺のそれぞれの一部は、前記配線基板の各辺に向かって後退していることを特徴とする半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置およびその製造技術に関し、特に、配線基板上に半導体チップが搭載された半導体装置およびその製造技術に適用して有効な技術に関する。 20

**【背景技術】****【0002】**

配線基板上に半導体チップを搭載し、半導体チップの電極と配線基板の接続端子をボンディングワイヤで電気的に接続し、半導体チップおよびボンディングワイヤを樹脂封止し、配線基板の裏面に半田ボールを接続することで、半導体パッケージ形態の半導体装置が製造される。このような半導体装置には、例えば、CSP (Chip Size Package) と呼ばれるチップサイズもしくは半導体チップより僅かに大きい程度の小形の半導体パッケージがある。

**【0003】**

特開2003-92374号公報（特許文献1）には、主面と主面上に形成される絶縁膜とその絶縁膜から露出し前記主面上に形成される電極とを有する配線基板と、配線基板の主面上の絶縁膜上に接着材を介して固定される半導体チップと、配線基板主面の電極と半導体チップの電極とを接続する導電性のワイヤと、半導体チップ、配線基板の主面および電極を覆う封止体とを有する半導体装置において、半導体チップと電極との間に絶縁膜をその深さ全域に亘って除去することで溝を形成し、接着材（絶縁性樹脂）の流出部分が溝内に溜まり溝を乗り越えず、電極には到達しないようにする技術が記載されている。 30

**【特許文献1】特開2003-92374号公報****【発明の開示】****【発明が解決しようとする課題】****【0004】**

本発明者の検討によれば、新たに次のことが分かった。 40

**【0005】**

CSP形態の半導体装置のように、半導体パッケージが小型化すると、半導体チップの端部と配線基板の電極との距離が接近するようになる。配線基板に半導体チップを接着材で固定する場合、この接着材が配線基板の電極上に流出すると、その電極へのボンディングワイヤの接続不良が発生しやすくなり、配線基板の電極とボンディングワイヤとの間の電気的接続の信頼性が低下する可能性がある。

**【0006】**

配線基板の主面上に形成される絶縁膜をその深さ全域に亘って除去することで半導体チップと電極との間に溝を形成する技術では、接着材（絶縁性樹脂）の流出部分が溝内に溜 50

まり溝を乗り越えず、電極には到達しないようにすることができる。これにより、接着材流出に伴う不良発生を抑止することができる。

#### 【0007】

しかしながら、配線基板の主面上の絶縁膜上に接着材を介して半導体チップを固定する技術では、半導体チップの裏面における全面が配線基板の主面上の絶縁膜上に接着材を介して接合される。接着材と封止樹脂との密着性は、半導体チップと封止樹脂との密着性に比べて低い。そのため、塗布された接着材が半導体チップの外周部からはみ出す、あるいはチップの側面に濡れあがると、接着材と封止樹脂との接合面積が増加することから、封止樹脂の密着性が低下する。封止樹脂の密着性が低いと、半導体装置（半導体パッケージ）の信頼性や製造歩留りが低下する可能性がある。

10

#### 【0008】

また、半導体チップを固定するために使用される接着材が半導体チップの外周部よりもはみ出した位置まで到達していると、配線基板の電極を半導体チップの外周部により接近して配置することが困難であるため、更なる半導体装置の小型化が実現できない。

#### 【0009】

本発明の目的は、半導体装置の信頼性を向上させることができる技術を提供することにある。

#### 【0010】

本発明の他の目的は、半導体パッケージの小型化を実現できる技術を提供することにある。

20

#### 【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

#### 【課題を解決するための手段】

#### 【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

#### 【0013】

本発明は、平面形状が四角形から成る基材層と、前記基材層の主面に設けられた複数の配線と、前記基材層の各辺に沿って配置され、前記複数の配線のそれぞれと一体に形成された複数の接続端子と、前記基材層の周縁部及び前記複数の接続端子が露出するように前記複数の配線を覆う絶縁膜と、前記絶縁膜において前記複数の接続端子よりも内側の領域に形成され、前記複数の配線のそれぞれの一部及び前記基材層の一部を露出する開口部とを有する配線基板を準備する工程、

30

複数の電極が形成された主面と、前記主面と対向する裏面とを有する半導体チップを準備する工程、

前記絶縁膜において前記開口部よりも内側の領域に供給されたペースト状の接着材を介して、前記半導体チップの裏面が前記配線基板の主面と対向するように、前記半導体チップを前記配線基板の主面上に搭載する工程、

前記半導体チップの前記複数の電極と前記配線基板の前記複数の接続端子とを複数のボンディングワイヤを介してそれぞれ電気的に接続する工程、

40

前記半導体チップ、前記複数のボンディングワイヤ、及び前記配線基板の主面を樹脂で封止する工程、

を含み、

前記半導体チップは、前記半導体チップの端部が前記絶縁膜の前記開口部と平面的に重なるように、前記配線基板の主面上に搭載され、

前記半導体チップ主面、前記半導体チップの側面、及び前記半導体チップの裏面の一部を前記樹脂で覆うように封止するものである。

#### 【0014】

また、本発明は、平面形状が四角形から成る基材層と、前記基材層の主面に設けられた

50

複数の配線と、前記基材層の各辺に沿って配置され、前記複数の配線のそれぞれと一体に形成された複数の接続端子と、前記基材層の周縁部及び前記複数の接続端子が露出するよう前記複数の配線を覆う絶縁膜と、前記絶縁膜において前記複数の接続端子よりも内側の領域に形成され、前記複数の配線のそれぞれの一部及び前記基材層の一部を露出する開口部とを有する配線基板と、

前記絶縁膜において前記開口部よりも内側の領域に供給されたペースト状の接着材と、

複数の電極が形成された正面と、前記正面と対向する裏面とを有し、前記裏面が前記配線基板の正面と対向するように、前記接着材を介して前記配線基板の正面に搭載された半導体チップと、

前記半導体チップの前記複数の電極と前記配線基板の前記複数の接続端子とをそれぞれ電気的に接続する複数のボンディングワイヤと、10

前記半導体チップ、前記複数のボンディングワイヤ、及び前記配線基板の正面を封止する封止樹脂と、

を含み、

前記開口部は、前記絶縁膜において前記半導体チップの端部と平面的に重なる領域に形成されており、

前記封止樹脂は、前記半導体チップ正面、前記半導体チップの側面、及び前記半導体チップの裏面の一部を覆うように形成されているものである。

#### 【発明の効果】

#### 【0015】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。20

#### 【0016】

半導体チップの裏面の外周部の下方にも封止樹脂が充填されるため、半導体装置の信頼性を向上することができる。

#### 【0017】

また、半導体チップと封止樹脂との接合面積が増加するため、封止樹脂の密着性が向上し、半導体装置の製造歩留りを向上することができる。

#### 【発明を実施するための最良の形態】

#### 【0018】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションに分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。3040

#### 【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

#### 【0020】

また、実施の形態で用いる図面においては、断面図であっても図面を見易くするためにハッティングを省略する場合もある。また、平面図であっても図面を見易くするためにハッ50

チングを付す場合もある。

**【0021】**

(実施の形態1)

本実施の形態の半導体装置およびその製造工程を図面を参照して説明する。

**【0022】**

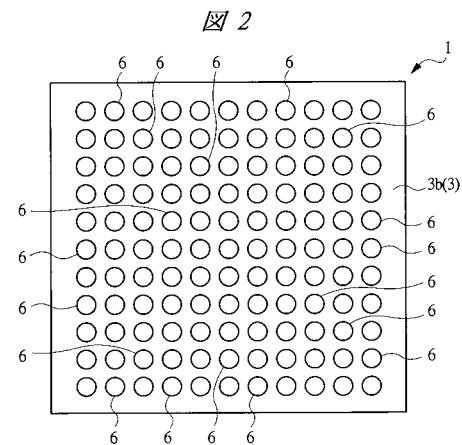

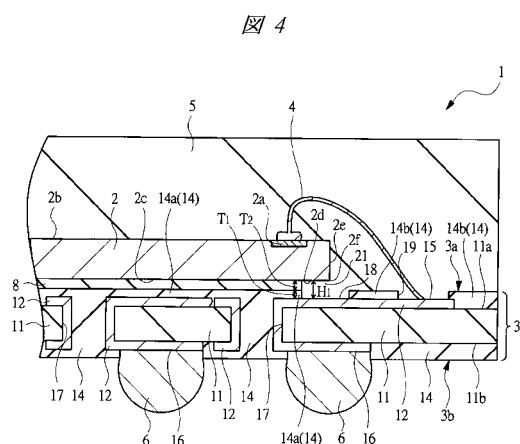

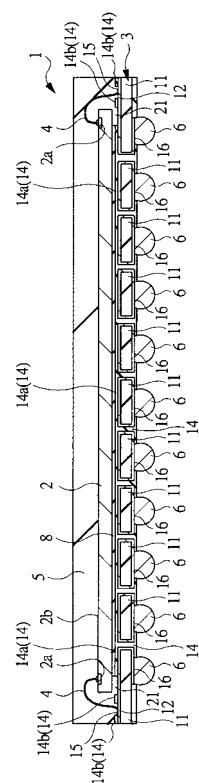

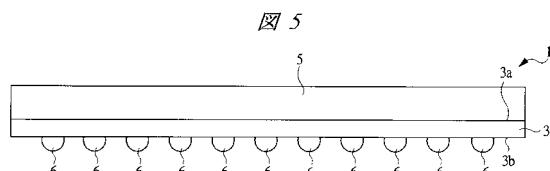

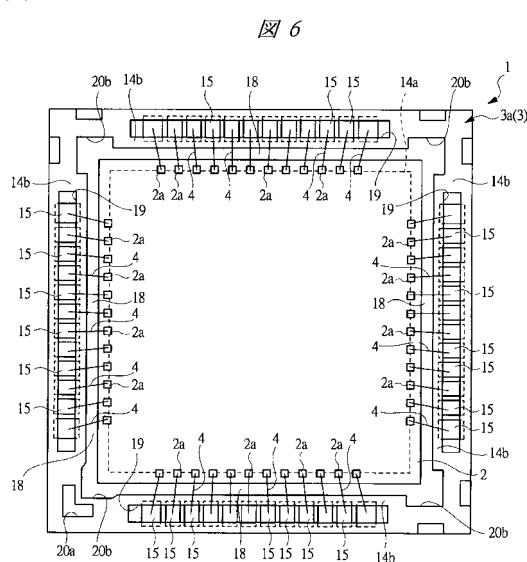

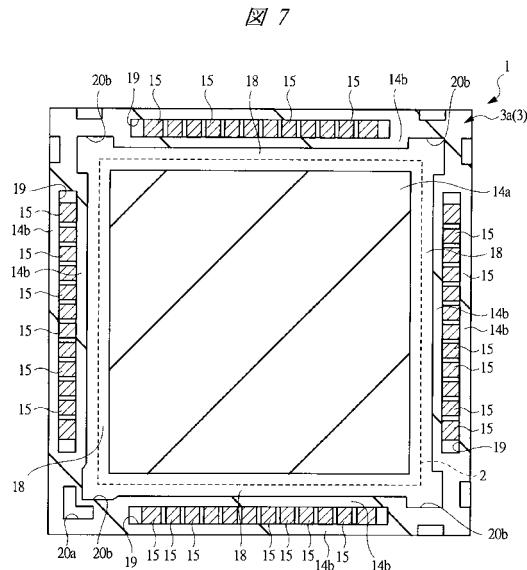

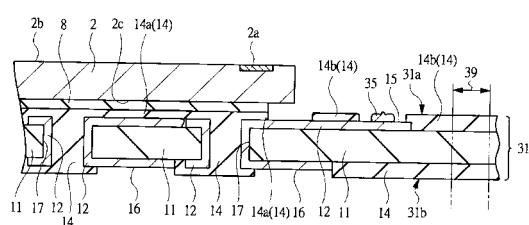

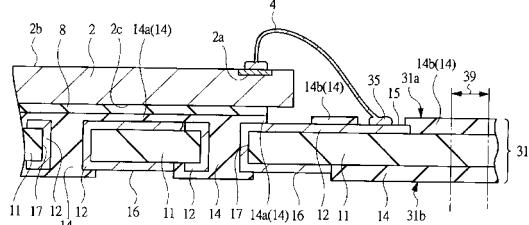

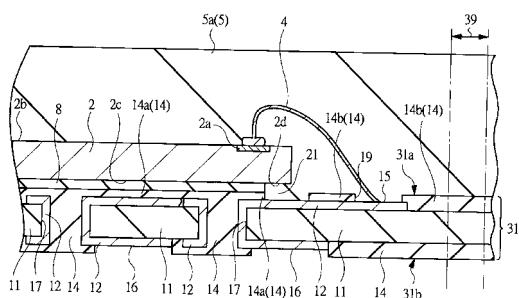

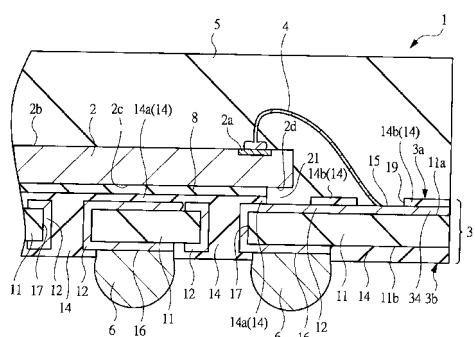

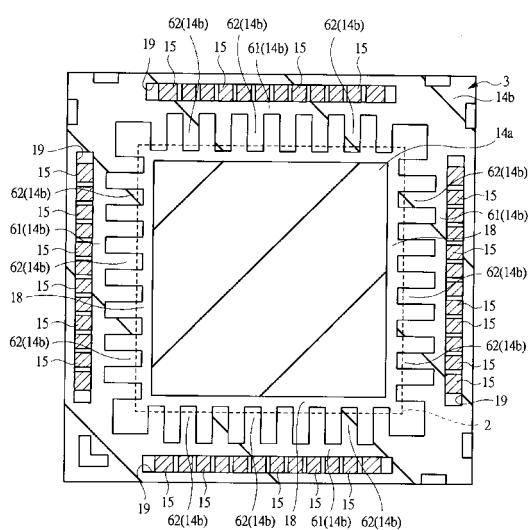

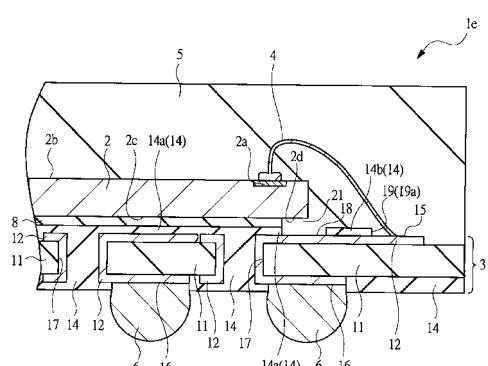

図1は、本発明の一実施の形態である半導体装置1の上面図、図2はその下面図、図3はその断面図(全体断面図)、図4はその要部断面図(部分拡大断面図)、図5はその側面図である。図1のA-A線の断面が図3にほぼ対応し、図3の端部近傍領域の拡大図が図4にほぼ対応する。また、図6は、封止樹脂5を透視したときの半導体装置1の平面透視図(上面図)であり、図7は、封止樹脂5、半導体チップ2およびボンディングワイヤ4を透視したときの半導体装置1の平面透視図(上面図)、すなわち半導体装置1に用いられている配線基板3の上面図である。なお、図7では、半導体チップ2の外形を点線で示してある。また、図7は平面図であるが、理解を簡単にするために、第1ソルダレジスト部14a、第2ソルダレジスト部14b、および第2ソルダレジスト部14bの開口部19から露出する接続端子15にハッチングを付してある。

10

**【0023】**

図1～図7に示される本実施の形態の半導体装置1は、半導体チップ2が配線基板3に搭載(接合、接続、実装)された半導体装置(半導体パッケージ)であり、例えば、チップサイズもしくは半導体チップ2より僅かに大きい程度の小形の半導体パッケージであるCSP(Chip Size Package)形態の半導体装置である。

20

**【0024】**

本実施の形態の半導体装置1は、半導体チップ2と、半導体チップ2を支持または搭載する配線基板3と、半導体チップ2の表面の複数の電極(第2電極、ボンディングパッド、パッド電極)2aとこれに対応する配線基板3の複数の接続端子(第1電極、ボンディングパッド、パッド電極)15とを電気的に接続する複数のボンディングワイヤ4と、半導体チップ2およびボンディングワイヤ4を含む配線基板3の上面3aを覆う封止樹脂(封止樹脂部、封止部、封止体)5と、配線基板3の下面3bに外部端子としてエリアアレイ配置で設けられた複数の半田ボール(ボール電極、突起電極、電極、外部端子)6とを有している。

**【0025】**

半導体チップ2は、その厚さと交差する平面形状が正方形であり、例えば、単結晶シリコンなどからなる半導体基板(半導体ウエハ)の主面に種々の半導体素子または半導体集積回路を形成した後、必要に応じて半導体基板の裏面研削を行ってから、ダイシングなどにより半導体基板を各半導体チップ2に分離したものである。半導体チップ2は、互いに対向する表面(半導体素子形成側の主面、上面)2bおよび裏面(半導体素子形成側の主面とは逆側の主面、下面)2cを有し、その表面2bが上方を向くように配線基板3上面(チップ支持面)3a上に配置され、半導体チップ2の裏面2cが配線基板3の上面3aに接着材(ダイボンド材、接合材、接着剤)8を介して接着され固定されている。接着材8は、例えば絶縁性または導電性のペースト材などを用いることができる。接着材8の厚みは、例えば20～30μm程度とすることができる。半導体チップ2の表面2bには、複数の電極2aが形成されており、電極2aは、半導体チップ2内部または表層部分に形成された半導体素子または半導体集積回路に電気的に接続されている。

40

**【0026】**

配線基板3は、絶縁性の基材層(絶縁基板、コア材)11と、基材層11の上面11aおよび下面11bに形成された導体層(導体パターン、導体膜パターン、配線層)12と、基材層11の上面11aおよび下面11b上に導体層12を覆うように形成された絶縁層(絶縁体層、絶縁膜)としてのソルダレジスト層(絶縁膜、半田レジスト層)14とを有している。他の形態として、配線基板3を、複数の絶縁層と複数の配線層とを積層した多層配線基板により形成することもできる。

**【0027】**

50

導体層 1 2 はパターン化されており、配線基板 3 の配線または配線層となる導体パターンである。導体層 1 2 は、導電性材料からなり、例えばめっき法で形成された銅薄膜などにより形成することができる。基材層 1 1 の上面 1 1 a の導体層 1 2 により、ポンディングワイヤ 4 を接続するための接続端子（電極、ポンディングパッド、パッド電極）1 5 が複数形成され、基材層 1 1 の下面 1 1 b の導体層 1 2 により、半田ボール 6 を接続するための導電性のランド（電極、パッド、端子）1 6 が複数形成されている。また、基材層 1 1 には複数の開口部（スルーホール、ビア、貫通孔）1 7 が形成されており、各開口部 1 7 の側壁上にも導体層 1 2 が形成されている。基材層 1 1 の上面 1 1 a の接続端子 1 5 は、基材層 1 1 の上面 1 1 a の導体層 1 2（導体層 1 2 からなる引き出し配線）、開口部 1 7 の側壁上の導体層 1 2、および基材層 1 1 の下面 1 1 b の導体層 1 2 を介して、基材層 1 1 の下面 1 1 b のランド 1 6 に電気的に接続されている。従って、半導体チップ 2 の複数の電極 2 a は、複数のポンディングワイヤ 4 を介して配線基板 3 の複数の接続端子 1 5 に電気的に接続され、更に配線基板 3 の導体層 1 2 を介して配線基板 3 の複数のランド 1 6 に電気的に接続されている。ポンディングワイヤ 4 は、例えば金線などの金属細線からなる。

#### 【 0 0 2 8 】

ソルダレジスト層 1 4 は、導体層 1 2 を保護する絶縁層（絶縁膜）としての機能を有しており、例えば有機系樹脂材料などの絶縁体材料からなる。また、ソルダレジスト層 1 4 は、基材層 1 1 の上面 1 1 a および下面 1 1 b 上に導体層 1 2 を覆うように形成されており、ソルダレジスト層 1 4 が基材層 1 1 の開口部 1 7 の内部を埋めている。ソルダレジスト層 1 4 が基材層 1 1 の開口部 1 7 を埋めているので、半導体チップ 2 を配線基板 3 に接合するための接着材 8 が開口部 1 7 から配線基板 3 の下面 3 b 側に漏れてしまうのを防止することができ、また、開口部 1 7 から半導体チップ 2 の裏面 2 c が露出してしまうのを防止することができる。また、配線基板 3 の導体層 1 2 のうち、接続端子 1 5 とランド 1 6 とは、ソルダレジスト層 1 4（の開口部）から露出されている。また、基材層 1 1 の上面 1 1 a および下面 1 1 b 上のソルダレジスト層 1 4 の厚みは、例えば 2 0 ~ 3 0 μm 程度とすることができます。

#### 【 0 0 2 9 】

複数のランド 1 6 は、配線基板 3 の下面 3 b にアレイ状に配置されている。各ランド 1 6 の隣に開口部 1 7 が形成されている。また、各ランド 1 6 には半田ボール 6 が接続されている。このため、配線基板 3 の下面 3 b に複数の半田ボール 6 がアレイ状に配置されている。半田ボール 6 は、半導体装置 1 の外部端子として機能することができる。従って、半導体チップ 2 の複数の電極 2 a は、複数のポンディングワイヤ 4 を介して配線基板 3 の複数の接続端子 1 5 に電気的に接続され、更に配線基板 3 の導体層 1 2 を介して配線基板 3 の複数のランド 1 6 および複数のランド 1 6 に接続された複数の半田ボール 6 に電気的に接続されている。なお、図 2 の半田ボール 6 の数と図 6、図 7 の接続端子 1 5 の数とは一致していないが、図 1 ~ 図 7 は半導体装置 1 の構造を模式的に示したものであり、半導体装置 1 における半田ボール 6 の数や接続端子 1 5 の数は必要に応じて種々変更可能であり、半導体装置 1 における半田ボール 6 の数と接続端子 1 5 の数とと同じにすることもでき、また異なることもできる。また、半導体チップ 2 の電極 2 a と電気的に接続していない半田ボール 6 は、放熱用に用いることもできる。

#### 【 0 0 3 0 】

本実施の形態では、配線基板 3 の上面 3 a にソルダレジスト層 1 4 が形成されているが、配線基板 3 の上面 3 a のソルダレジスト層 1 4 は、半導体チップ 2 の下方（すなわち配線基板 3 の上面 3 a の中央部）に位置する第 1 ソルダレジスト部（第 1 の絶縁膜部）1 4 a と、第 1 ソルダレジスト部 1 4 a の外周（周囲）に位置する（すなわち配線基板 3 の上面 3 a の外周部に位置する）第 2 ソルダレジスト部（第 2 の絶縁膜部）1 4 b とを有している。第 1 ソルダレジスト部 1 4 a と第 2 ソルダレジスト部 1 4 bとの間には、ソルダレジスト層 1 4 が形成されずに基材層 1 1 が露出された領域（ダム領域）1 8 が存在している。従って、第 1 ソルダレジスト部 1 4 a と第 2 ソルダレジスト部 1 4 b とは、領域 1 8

を挟んで離間している。領域 18 では、接続端子 15 と開口部 17 の側壁上の導体層 12 との間を接続するための引き出し配線（この引き出し配線も導体層 12 からなるが、図 6, 図 7 の平面図では図示を省略している）も露出している。

#### 【 0 0 3 1 】

半導体チップ 2 は、第 1 ソルダレジスト部 14 a 上に接着材 8 を介して接合（搭載、接続、固定、配置）されている。第 2 ソルダレジスト部 14 b は、接続端子 15 を露出するための開口部 19 を有している。図 6 に示されるように、接続端子 15 は略長方形形状のパターン（導体パターン）を有しており、第 2 ソルダレジスト部 14 b の開口部 19 は、接続端子 15 用の導体パターンにオーバラップするように形成されている。このため、接続端子 15 の一部（両端部）上に第 2 ソルダレジスト部 14 b が重なっている。これにより 10、接続端子 15 が剥離するのをより確実に防止し、半導体装置の信頼性をより向上させることができる。

#### 【 0 0 3 2 】

第 2 ソルダレジスト部 14 b の開口部 19 から露出する接続端子 15 に、ボンディングワイヤ 4 が接続されている。接続端子 15 へのボンディングワイヤ 4 の接続を容易または確実にするために、第 2 ソルダレジスト部 14 b の開口部 19 から露出する接続端子 15 の上面（ボンディングワイヤ 4 の接続面）には金めっき層（またはニッケルめっき層（下層側）と金めっき層（上層側）の積層膜）などが形成されている。また、第 2 ソルダレジスト部 14 b には、パッケージインデックスとしての開口部 20 a が形成されている。第 2 ソルダレジスト部 14 b に形成されたパッケージインデックスとしての開口部 20 a は 20、半導体装置 1 の製造工程中の位置決めや向きの認識などに用いることができる。

#### 【 0 0 3 3 】

半導体チップ 2 は、配線基板 3 の上面 3 a の第 1 ソルダレジスト部 14 a 上に接着材 8 を介して接合（搭載、接続、固定、配置）されているが、この第 1 ソルダレジスト部 14 a の平面寸法（面積）は、半導体チップ 2 の平面寸法（面積）よりも小さい。このため、半導体チップ 2 を搭載したとき、半導体チップ 2 の裏面 2 c の外周部（周辺部、端部近傍領域）2 d の下方には、第 1 ソルダレジスト部 14 a が延在（存在）していない。従って、半導体チップ 2 の裏面 2 c の外周部 2 d および裏面 2 c の端部 2 f は、ソルダレジスト層 14 が形成されていない領域 18 上に位置することになる。また、半導体チップ 2 を配線基板 3 上にダイボンディング（接合）する際には、半導体チップ 2 よりも小さな寸法の第 1 ソルダレジスト部 14 a 上に接着材 8 を配置してそこに半導体チップ 2 が接合されるので、半導体チップ 2 の裏面 2 c の外周部 2 d 上には接着材 8 が延在（存在）しない。従って、半導体チップ 2 を配線基板 3 上にダイボンディングしたとき、半導体チップ 2 の裏面 2 c の外周部 2 d の下方には接着材 8 およびソルダレジスト層 14 が存在しない。すなわち、接着材 8 およびソルダレジスト層 14（第 1 ソルダレジスト部 14 a）は半導体チップ 2 の側面 2 e（端部 2 f）よりも内側に存在するため、半導体チップ 2 の裏面 2 c の外周部 2 d は露出された状態となる。このため、半導体チップ 2 の裏面 2 c の外周部 2 d と配線基板 3 の上面 3 a との間には空間（隙間）21 が形成される。空間 21 の高さ方向の寸法（半導体チップ 2 の裏面 2 c の外周部 2 d と配線基板 3 の上面 3 a との間の距離）H<sub>1</sub> は、第 1 ソルダレジスト部 14 a の厚み T<sub>1</sub> と、接着材 8 の厚み T<sub>2</sub> との合計にほぼ 30 相当する（H<sub>1</sub> = T<sub>1</sub> + T<sub>2</sub>）。封止樹脂 5 を形成するとき（モールド工程）には、封止樹脂 5 を形成するための材料が半導体チップ 2 の裏面 2 c の外周部 2 d の下方の空間 21 にも充填され、硬化（固化）した封止樹脂 5 が半導体チップ 2 の裏面 2 c の外周部 2 d の下方を充填することとなり、硬化した封止樹脂 5 が半導体チップ 2 の表面 2 b と、半導体チップ 2 の側面 2 e と、半導体チップ 2 の裏面 2 c の外周部 2 d とを覆うので、半導体チップ 2 と封止樹脂 5 との密着性（接着強度）を高めることができ、半導体装置 1 の信頼性を向上させることができる。

#### 【 0 0 3 4 】

封止樹脂 5 は、例えば熱硬化性樹脂材料などの樹脂材料などからなり、フィラーなどを含むこともできる。例えば、フィラーを含むエポキシ樹脂などを用いて封止樹脂 5 を形成 40

10

20

30

40

50

することもできる。封止樹脂5は、配線基板3の上面3a上に半導体チップ2およびボンディングワイヤ4を覆うように形成されており、封止樹脂5により、半導体チップ2およびボンディングワイヤ4が封止され、保護される。

#### 【0035】

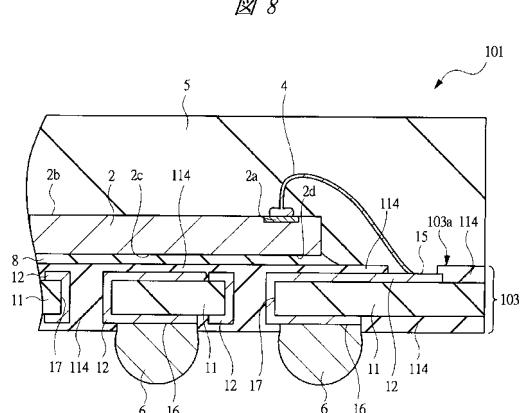

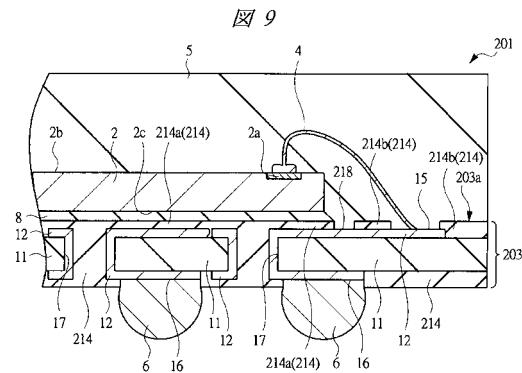

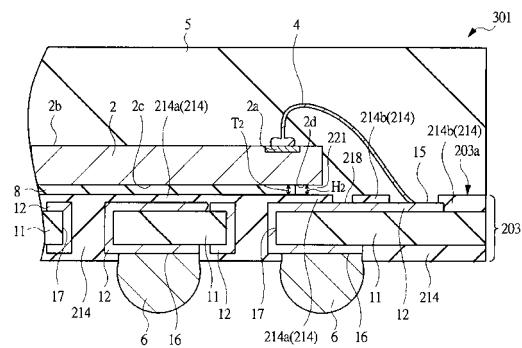

図8は、第1の比較例の半導体装置101の要部断面図（部分拡大断面図）であり、図9は、第2の比較例の半導体装置201の要部断面図（部分拡大断面図）であり、図10は、第3の比較例の半導体装置301の要部断面図（部分拡大断面図）であり、それぞれ本実施の形態の図4に対応する領域が示されている。

#### 【0036】

図8に示される第1の比較例の半導体装置101では、本実施の形態とは異なり、接続端子15上を除く配線基板103の上面103aの全面にソルダレジスト層114が形成されており、半導体チップ2の裏面2cの外周部2dの下方にも、ソルダレジスト層114が延在している。このため、第1の比較例の半導体装置101では、半導体チップ2を配線基板103上にダイボンディングしたときに、ペースト材などからなる接着材8が半導体チップ2の裏面2cの端部を越えて広がり、更にソルダレジスト層114の上面上を流れて接続端子15上にまで接着材8が広がってしまう可能性がある。接続端子15上にまで接着材8が広がってしまう（流出する）と、その接続端子15へのボンディングワイヤ4の接続不良が発生しやすくなり、ボンディングワイヤ4と接続端子15との間の電気的接続の信頼性が低下する可能性がある。また、接続端子15への接着材8の流出を防止するために半導体チップ2の端部と配線基板3の接続端子15との距離を長くすることも考えられるが、これは、半導体装置の大型化（大面積化）を招いてしまう。

#### 【0037】

図9に示される第2の比較例の半導体装置201では、配線基板203の上面203aに第1ソルダレジスト部214aと第2ソルダレジスト部214bとからなるソルダレジスト層214が形成されており、第1ソルダレジスト部214aと第2ソルダレジスト部214bとの間には、ソルダレジスト層214が形成されずに配線基板203の基材層11が露出した領域（ダム領域）218が存在しているが、本実施の形態とは異なり、第1ソルダレジスト部214aの平面寸法（面積）は、半導体チップ2の平面寸法（面積）よりも大きく、半導体チップ2の裏面2c全面の下方に第1ソルダレジスト部214aが延在（存在）している。第2の比較例の半導体装置201では、半導体チップ2を配線基板203上にダイボンディングしたときには、第1ソルダレジスト部214aと第2ソルダレジスト部214bとの間にソルダレジスト層214がなく基材層11が露出した領域（ダム領域）218を設けたことにより、ペースト材などからなる接着材8が領域218を越えて第2ソルダレジスト部214b上にまで広がってしまうのを防止することができる。これにより、接着材8が接続端子15上にまで広がってしまうのを防止でき、ボンディングワイヤ4と接続端子15との間の電気的接続の信頼性を向上することができる。

#### 【0038】

しかしながら、図9に示される第2の比較例の半導体装置201では、第1ソルダレジスト部214aの平面寸法（面積）が半導体チップ2の平面寸法（面積）よりも大きく、半導体チップ2の裏面2c全面が接着材8を介して第1ソルダレジスト部214aに接着されている。封止樹脂5と接着材8との密着性（接着強度）は、半導体チップ2と封止樹脂5との密着性（接着強度）に比較して低い。このため、第2の比較例の半導体装置201では、封止樹脂5が半導体チップ2の表面2bおよび側面2eを覆うが、封止樹脂5は半導体チップ2の裏面2cは覆わず、半導体チップ2と封止樹脂5の接合面積が本実施の形態1（の半導体装置1）よりも小さいため、半導体チップ2と封止樹脂5との密着性（接着強度）が本実施の形態1（の半導体装置1）よりも比較的低くなる可能性がある。更には、半導体チップ2を固定するために使用される接着材8が半導体チップ2の外周部よりもはみ出した位置まで到達していると、配線基板203上の接続端子15を半導体チップ2の外周部により接近して配置することが困難であるため、本実施の形態1（の半導体装置1）に比較して半導体装置201の小型化が実現できない。

10

20

30

40

50

## 【0039】

図10に示される第3の比較例の半導体装置301では、第2の比較例の半導体装置201よりも接着材8の塗布領域や塗布量を少なくしている。これにより、半導体チップ2を配線基板203の上面203aの第1ソルダレジスト部14a上に接着材8を介して接合したときに、半導体チップ2の裏面2cの外周部2dの下方に接着材8が延在(存在)せず、半導体チップ2の裏面2cの外周部2dと配線基板203の上面203aとの間に空間(隙間)221を形成することができる。これにより、封止樹脂5を形成するときは、封止樹脂5を形成するための材料を空間221にも充填可能となり、硬化した封止樹脂5が半導体チップ2の表面2bと、半導体チップ2の側面2eと、半導体チップ2の裏面2cの外周部2dとを覆い、半導体チップ2と封止樹脂5との密着性(接着強度)を高めることができる。10

## 【0040】

しかしながら、図10に示される第3の比較例の半導体装置301では、接着材8の塗布領域や塗布量を調節することにより半導体チップ2の裏面2cの外周部2dと配線基板203の上面203aとの間に空間221を形成しているので、接着材8の塗布量が少な過ぎて半導体チップ2と配線基板203の接合強度が低下したり、あるいは接着材8の塗布量が多過ぎて半導体チップ2の裏面2cの外周部2dと配線基板203の上面203aとの間に空間221を形成できない可能性がある。このため、ダイボンディング工程の管理が容易ではなく、製品ごとのばらつきが大きくなる。また、半導体チップ2よりも平面寸法(面積)が小さなダイボンドフィルムを接着材8として用いることで、半導体チップ2の裏面2cの外周部2dと配線基板203の上面203aとの間に空間221を形成することも考えられるが、ダイボンドフィルムはペースト型の接着材よりも高価であり、半導体装置の製造コストの増大を招く可能性がある。20

## 【0041】

また、図10に示される第3の比較例の半導体装置301では、本実施の形態とは異なり、半導体チップ2の裏面2cの外周部2dの下方に第1ソルダレジスト部214aが延在しているので、半導体チップ2を配線基板203上にダイボンディングしたときに、半導体チップ2の裏面2cの外周部2dと配線基板203の上面203aとの間に形成される空間221の高さ方向の寸法H<sub>2</sub>が低く(小さく)なる。空間221の高さ方向の寸法H<sub>2</sub>は、接着材8の厚みT<sub>2</sub>にほぼ相当する(H<sub>2</sub>=T<sub>2</sub>)。接着材8の厚みが例えば20~30μm程度であれば、空間221の高さ方向の寸法H<sub>2</sub>も20~30μm程度となる。半導体チップ2の裏面2cの外周部2dの下方の空間221の高さ方向の寸法H<sub>2</sub>が小さいので、封止樹脂5を形成するときに、封止樹脂5を形成するための材料に含まれるフィラーなどが、半導体チップ2の裏面2cの外周部2dの下方の空間221に侵入しにくくなり、空間221を充填した封止樹脂5の成分比と、他の領域の封止樹脂5の成分比とが不均一化するなどして、硬化した封止樹脂5と半導体チップ2との密着性(接着強度)が低下する可能性がある。30

## 【0042】

それに対して、本実施の形態では、配線基板3の上面3aには、その上に接着材8を介して半導体チップ2を接合する第1ソルダレジスト部(第1の絶縁膜部)14aと、第1ソルダレジスト部14aの周囲(外周)に設けられ、その開口部19から接続端子15を露出する第2ソルダレジスト部(第2の絶縁膜部)14bとが形成されている。第1ソルダレジスト部14aと第2ソルダレジスト部14bとの間には、ソルダレジスト層14が形成されずに基材層11が露出する領域(ダム領域)18が存在している。このため、半導体チップ2を配線基板3上にダイボンディングしたときには、第1ソルダレジスト部14aと第2ソルダレジスト部14bとの間にソルダレジスト層14がなく基材層11が露出した領域(ダム領域)18を設けたことにより、接着材8が領域18を越えて第2ソルダレジスト部14b上にまで広がってしまうのを防止することができる。これにより、接着材8が接続端子15上にまで広がってしまうのを防止でき、ボンディングワイヤ4と接続端子15との間の電気的接続の信頼性を向上することができる。また、たとえ流動性が4050

比較的高いペースト型の接着材（接合材）を接着材8として用いたとしても、第1ソルダレジスト部14aと第2ソルダレジスト部14bとの間にソルダレジスト層14がない領域（ダム領域）18を設けたことにより、ペースト材からなる接着材8が接続端子15上にまで広がってしまうのを防止することができるので、ダイボンドフィルムよりも相対的に廉価なペースト型の接着材を接着材8として用いることが可能になり、半導体装置の製造コストの低減に有利である。また、配線基板3の接続端子15を半導体チップ2の外周部により接近して配置することが可能になるので、半導体装置の更なる小型化が可能になる。

#### 【0043】

更に、本実施の形態では、第1ソルダレジスト部14a上に接着材8を介して半導体チップ2が搭載され固定されているが、この第1ソルダレジスト部14aの平面寸法（面積）は、半導体チップ2の平面寸法（面積）よりも小さい。このため、半導体チップ2を配線基板3の上面3aの第1ソルダレジスト部14a上に接着材8を介して接合したときに、半導体チップ2の裏面2cの外周部2dの下方には第1ソルダレジスト部14aおよび接着材8が延在（存在）せず、半導体チップ2の裏面2cの外周部2dと配線基板3の上面3aとの間に空間21が形成される。このため、封止樹脂5を形成するときには、封止樹脂5を形成するための材料がこの空間21にも充填され、硬化した封止樹脂5が半導体チップ2の表面2bと、半導体チップ2の側面2eと、半導体チップ2の裏面2cの外周部2dとを覆うので、半導体チップ2と封止樹脂5との接合面積が増加するため、半導体チップ2と封止樹脂5との密着性（接着強度）を高めることができ、半導体装置1の信頼性を向上させることができる。本実施の形態のように、半導体チップ2の裏面2c側にも封止樹脂5を回り込ませ、半導体チップ2の裏面2cの外周部2dと配線基板3の上面3aとの間を封止樹脂5で満たす（充填する）ことにより、半導体チップ2の表面2bおよび裏面2cの両面（と側面2eと）で封止樹脂5により半導体チップ2をしっかりと封止することができ、半導体チップ2と封止樹脂5との密着性を高め、半導体チップ2と封止樹脂5との間に剥離などが生じるのをより的確に防止することができる。

#### 【0044】

更に、本実施の形態では、半導体チップ2の裏面2cの外周部2dと配線基板3の上面3aとの間に形成される空間21の高さ方向の寸法H<sub>1</sub>は、第3の比較例の半導体装置301の空間221の高さ方向の寸法H<sub>2</sub>よりも、第1ソルダレジスト部14aの厚みT<sub>1</sub>の分だけ大きくすることができる（H<sub>1</sub> > H<sub>2</sub>）。例えば、接着材8の厚みT<sub>2</sub>が20～30μm程度で、第1ソルダレジスト部14aの厚みT<sub>1</sub>が20～30μm程度であれば、空間21の高さ方向の寸法H<sub>1</sub>は40～60μm程度にすることができる。このように、本実施の形態では、半導体チップ2の裏面2cの外周部2dの下方の空間21の高さ方向の寸法H<sub>1</sub>を比較的大きくすることができるので、封止樹脂5を形成するとき（モールド工程）に、封止樹脂5を形成するための材料に含まれるフィラーなどが、半導体チップ2の裏面2cの外周部2dの下方の空間21に侵入しやすく、空間21を充填した封止樹脂5の成分比と、他の領域の封止樹脂5の成分比とが均一化される。これにより、硬化した封止樹脂5と半導体チップ2との密着性（接着強度）をより向上させ、半導体装置1の信頼性をより向上することができる。

#### 【0045】

また、本実施の形態では、第2ソルダレジスト部14bの内周部（第1ソルダレジスト部14aに対向する第2ソルダレジスト部14bの内周部、半導体チップ2の四辺に対向する第2ソルダレジスト部14bの内周部）の角部（四隅、コーナー部）では、第2ソルダレジスト部14bのパターンを半導体装置1の外周方向に（すなわち半導体チップ2から遠ざかる方向に）後退させている。すなわち、第2ソルダレジスト部14bの内周部の角部（四隅）に、ソルダレジストが形成されずに基材層11が露出したソルダレジスト後退部20bを設けている。

#### 【0046】

第2ソルダレジスト部14bの内周部の角部（四隅）で第2ソルダレジスト部14bの

10

20

30

40

50

パターンを後退させる（すなわちソルダレジスト後退部 20 b を設ける）ことで、封止樹脂 5 をトランスファモールド工程などによって形成する際に、半導体チップ 2 の裏面 2 c の外周部 2 d と配線基板 3 の上面 3 a との間の空間 21 から空気が抜けやすくなり、封止樹脂 5 を形成するための材料の流動性が向上し、上記空間 21 への封止樹脂の充填性をより向上させることができ。このため、半導体チップ 2 と封止樹脂 5 との密着性（接着強度）をより向上させることができ、半導体装置 1 の信頼性をより向上させることができる。

#### 【 0 0 4 7 】

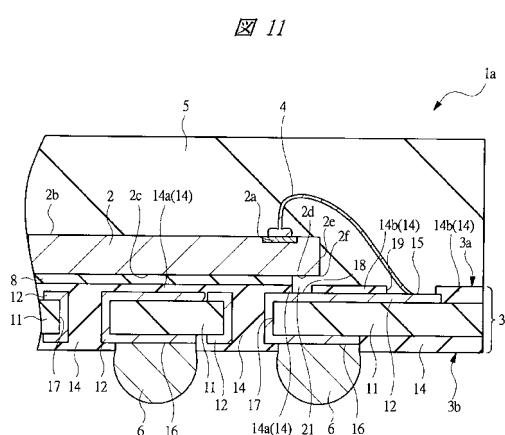

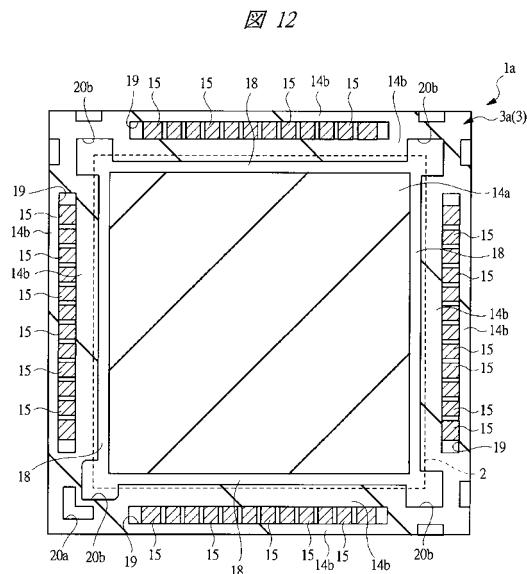

図 1 1 は、他の形態の半導体装置 1 a の要部断面図であり、図 1 2 は、その平面透視図（上面図）である。図 1 1 は、上記図 4 に対応する。また、図 1 2 は、上記図 7 に対応し、封止樹脂 5 、半導体チップ 2 およびボンディングワイヤ 4 を透視したときの半導体装置 1 a の平面透視図（上面図）、すなわち半導体装置 1 a に用いられている配線基板 3 の上面図が示されている。なお、図 1 2 では、半導体チップ 2 の外形を点線で示してある。また、図 1 2 は平面図であるが、理解を簡単にするために、第 1 ソルダレジスト部 14 a 、第 2 ソルダレジスト部 14 b 、および第 2 ソルダレジスト部 14 b の開口部 19 から露出する接続端子 15 にハッチングを付してある。

#### 【 0 0 4 8 】

上記半導体装置 1 では、半導体チップ 2 の裏面 2 c の端部 2 f （半導体チップ 2 の側面 2 e ）は、ソルダレジスト層 14 が形成されずに基材層 11 が露出する領域（ダム領域） 18 上に位置していたが、図 1 1 および図 1 2 に示される半導体装置 1 a では、半導体チップ 2 の裏面 2 c の端部 2 f （半導体チップ 2 の側面 2 e ）は、第 2 ソルダレジスト部 14 b 上に位置している。半導体装置 1 a の他の構成は上記半導体装置 1 とほぼ同様である。

#### 【 0 0 4 9 】

半導体装置 1 a も半導体装置 1 とほぼ同様の効果を得ることができ、本発明の半導体装置に含むものとする。ただし、半導体装置 1 のように半導体チップ 2 の裏面 2 c の端部 2 f （半導体チップ 2 の側面 2 e ）が領域（ダム領域） 18 上に位置している場合の方が、半導体装置 1 a のように半導体チップ 2 の裏面 2 c の端部 2 f （半導体チップ 2 の側面 2 e ）が第 2 ソルダレジスト部 14 b 上に位置している場合よりも、半導体チップ 2 を配線基板 3 の上面 3 a にダイボンディングしたときに半導体チップ 2 の裏面 2 c の外周部 2 d と配線基板 3 の上面 3 a との間に形成される空間 21 をより広くすることができ、封止樹脂 5 を形成するときにフィラーなどが半導体チップ 2 の裏面 2 c の外周部 2 d の下方の空間 21 に侵入しやすくなるので、空間 21 を満たす封止樹脂 5 の成分比と、他の領域の封止樹脂 5 の成分比とをより均一にすることができます。このため、半導体装置 1 は、封止樹脂 5 と半導体チップ 2 との密着性（接着強度）向上や信頼性の向上により有利である。一方、半導体装置 1 a のように半導体チップ 2 の裏面 2 c の端部 2 f （半導体チップ 2 の側面 2 e ）の下方に第 2 ソルダレジスト部 14 b を延在させることで、接続端子 15 を半導体チップ 2 側により近づけることが可能になる。このため、半導体装置 1 a は、小型化（小面積化）により有利である。

#### 【 0 0 5 0 】

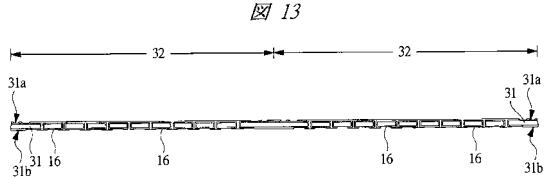

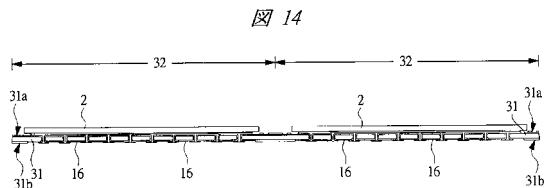

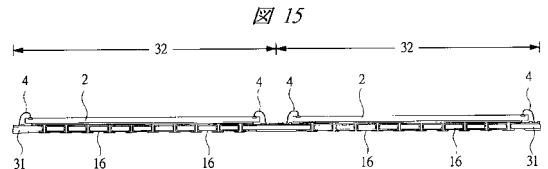

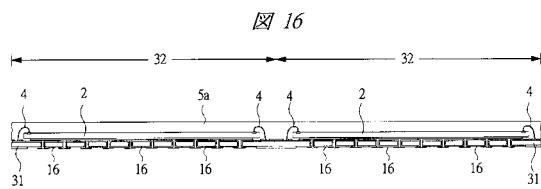

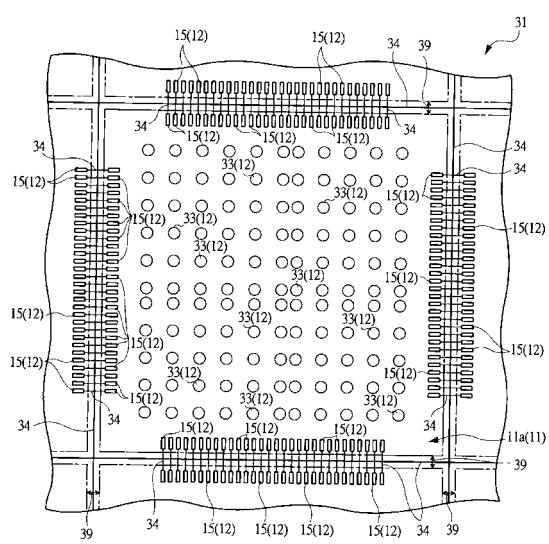

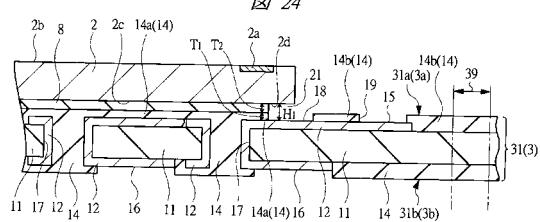

次に、本実施の形態の半導体装置の製造方法を、図面を参照して説明する。図 1 3 ~ 図 2 0 は、本実施の形態の半導体装置の製造工程中の断面図である。図 2 1 ~ 図 2 3 は、本実施の形態の半導体装置 1 の製造に用いられる配線基板 31 の製造工程の一例を模式的に示す平面図（上面図）である。図 2 4 は、本実施の形態の半導体装置の製造工程中の要部断面図であり、図 1 4 と同じ工程段階（ダイボンディング工程）に対応する。図 2 5 は、本実施の形態の半導体装置の製造工程中の平面図（上面図）であり、図 1 5 と同じ工程段階に対応する。図 2 6 , 図 2 7 は、ワイヤボンディング工程の説明図（要部断面図）である。図 2 8 は、本実施の形態の半導体装置の製造工程中の要部断面図であり、図 1 6 と同じ工程段階（モールド工程）に対応する。また、図 2 1 ~ 図 2 8 には、後述する切断工程で配線基板 31 を切断するダイシング領域（ダイシングライン） 39 も示してある。

10

20

30

40

50

**【0051】**

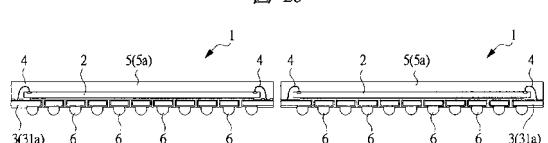

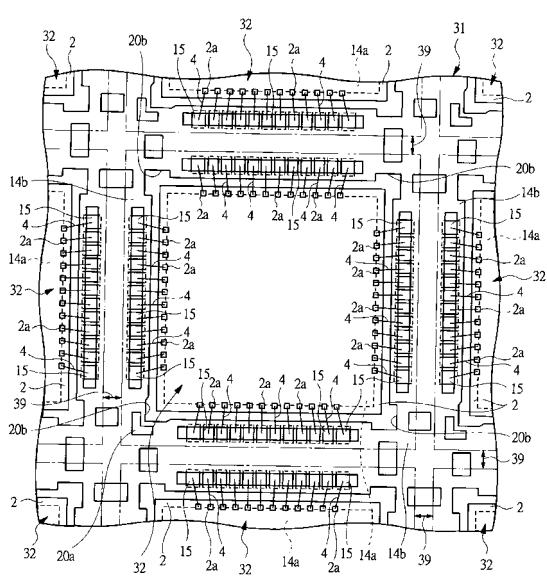

なお、本実施の形態では、複数の配線基板3がアレイ状に繋がって形成された多数個取りの配線基板(配線基板母体)31を用いて個々の半導体装置1を製造する場合について説明する。この配線基板31は、上記配線基板3の母体であり、配線基板31を後述する切断工程で切断し、各半導体装置領域(基板領域、単位基板領域)32に分離したものが半導体装置1の配線基板3に対応する。配線基板31は、そこから1つの半導体装置1が形成される領域である半導体装置領域(基板領域、単位基板領域)32がマトリクス状に複数配列した構成を有している。

**【0052】**

まず、配線基板31を準備する。配線基板31は例えば次のようにして製造することができる。10

**【0053】**

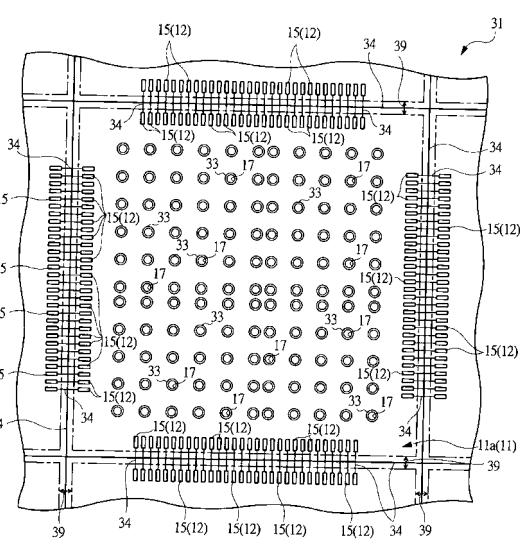

コア材としての絶縁性の基材層11の上面11aおよび下面上に無電解めっき(無電界めっき)法により無電解銅めっき層を形成し、この無電解銅めっき層をエッチングなどによりパターニングする。それから、無電解銅めっき層上に電解めっき(電界めっき)法により電解銅めっき層を形成し、銅層の厚みを厚くする。この無電解銅めっき層および電解銅めっき層の積層膜(銅層)によって、上記導体層12を形成することができる。図21には、スルーホール用の導体パターン33と接続端子15(用の導体パターン)とが、基材層11の上面に、無電解銅めっき層および電解銅めっき層の積層膜(導体層12)によつて形成された状態が示されている。接続端子15と導体パターン33とは、基材層11の上面11aに形成された無電解銅めっき層および電解銅めっき層の積層膜(導体層12)からなる引き出し配線(図示省略)によって電気的に接続されている。また、図示はしないけれども、基材層11の下面には、ランド16も、無電解銅めっき層および電解銅めっき層の積層膜によって形成されている。また、電解めっき法を用いるので、基材層11の上面11aには、めっき配線(給電線)34も形成されており、このめっき配線34を介して所定の電位(電力)を供給して、無電解銅めっき層上に電解銅めっき層を形成することができる。20

**【0054】**

次に、図22に示されるように、基材層11に開口部(スルーホール、ビア、貫通孔)17を形成する。開口部17は、スルーホール用の導体パターン33の内側に形成される。30

**【0055】**

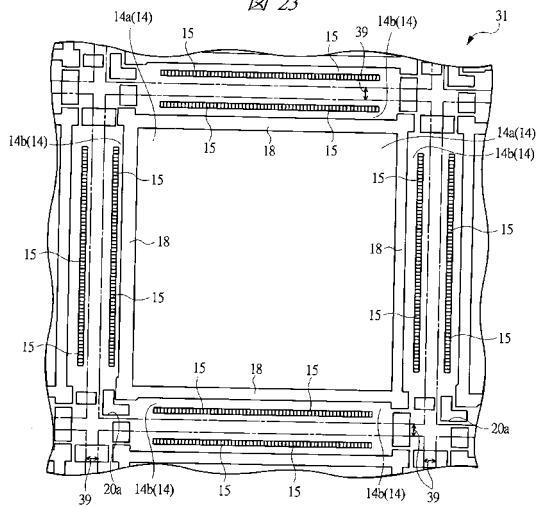

次に、無電解めっき法により開口部17の側壁上に無電解銅めっき層を形成する。この基材層11の開口部17の側壁上に形成された無電解銅めっき層が、開口部17の側壁上に形成された上記導体層12となる。それから、図23に示されるように、印刷法などを用いてソルダレジスト層14を基材層11の上面11aおよび下面上に開口部17内を埋めるように形成する。これにより、基材層11の上面11aには、第1ソルダレジスト部14aと第2ソルダレジスト部14bが形成される。基材層11の上面11aでは、接続端子15がソルダレジスト層14(第2ソルダレジスト部14b)の開口部から露出し、基材層11の下面では、ランド16がソルダレジスト層14の開口部から露出する。次に、基材層11の上面11aおよび下面上の銅めっき層の露出部(すなわち接続端子15およびランド16)上に、ニッケルめっき層および金めっき層を電解めっき法により順に形成する。その後、必要に応じて基材層11を外形加工(切断)して配線基板31を形成することができる。このようにして準備された配線基板31は、後述する配線基板31の切断工程で分割されて配線基板3となる半導体装置領域(基板領域、単位基板領域)32を複数有しており、配線基板31の上面31aの各半導体装置領域32に形成された第1ソルダレジスト部14aと、この第1ソルダレジスト部14aの外周に形成された第2ソルダレジスト部14bとを有している。40

**【0056】**

上記のようにして準備(製造)された配線基板31の上面31aの各半導体装置領域350

2上に、図14および図24に示されるように、半導体チップ2を接着材8を介して接合(ダイボンディング、チップマウント)する。このダイボンディング工程では、例えば、配線基板31の上面31aの各半導体装置領域32の第1ソルダレジスト部14a上に熱硬化性の接着材8を塗布してチップ固定用の接着層を第1ソルダレジスト部14a上に形成し、接着材8上に半導体チップ2を載置し、加熱などにより接着材8を硬化して、半導体チップ2の裏面2cと第1ソルダレジスト部14aとを接着材8を介して接合する。半導体チップ2のダイボンディング工程では、上記のように、半導体チップ2よりも平面寸法(面積)が小さな第1ソルダレジスト部14a上に接着材8を介して半導体チップ2を接合しているので、半導体チップ2の裏面2cの外周部2dの下方にはソルダレジスト層14(第1ソルダレジスト部14aおよび第2ソルダレジスト部14b)や接着材8が延在(存在)しない。このため、半導体チップ2を配線基板31の各半導体装置領域32上に接合したときに、半導体チップ2の裏面2cの外周部2dと配線基板31の上面31aとの間に空間21が形成され、この空間21の高さ方向の寸法H<sub>1</sub>は、第1ソルダレジスト部14aの厚みT<sub>1</sub>と、接着材8の厚みT<sub>2</sub>との合計にほぼ相当する(H<sub>1</sub>=T<sub>1</sub>+T<sub>2</sub>)ものになり、空間21の高さ方向の寸法H<sub>1</sub>を比較的大きくすることができる。例えば、接着材8の厚みT<sub>2</sub>が20~30μm程度で、第1ソルダレジスト部14aの厚みT<sub>1</sub>が20~30μm程度であれば、空間21の高さ方向の寸法H<sub>1</sub>は40~60μm程度にすることができる。10

#### 【0057】

次に、図15および図25に示されるように、ワイヤボンディング工程を行って、半導体チップ2の各電極2aと、これに対応する配線基板31に形成された接続端子15とをボンディングワイヤ4を介して電気的に接続する。すなわち、配線基板31の上面31aの各半導体装置領域32上の複数の接続端子15とその半導体装置領域32上に接合された半導体チップ2の複数の電極2aとを複数のボンディングワイヤ4を介して電気的に接続する。例えば、ワイヤボンディング装置を用い、半導体チップ2の電極2aにボンディングワイヤ4の一端を接続(ファーストボンディング)してから、配線基板31の接続端子15にボンディングワイヤ4の他端を接続(セカンドボンディング)する。20

#### 【0058】

このワイヤボンディング工程においては、他の形態として、図26の要部断面図に示されるように、まず配線基板31の接続端子15に金(Au)などからなるスタッドバンプ(バンプ電極、バンプ)35を形成した後、図27に示されるように、半導体チップ2の電極2aにボンディングワイヤ4の一端を接続してから、配線基板31の接続端子15上に形成したスタッドバンプ35にボンディングワイヤ4の他端を接続することもできる。接続端子15を半導体チップ2に比較的近い位置に形成し、あるいは比較的厚い半導体チップ2を用いるなどして、ボンディングワイヤ4と接続端子15とが為す角度が急に(例えば垂直に近く)なり、ボンディングワイヤ4に対する折り曲げストレスが大きくなつたとしても、接続端子15上にスタッドバンプ35を形成し、このスタッドバンプ35にボンディングワイヤ4を接続したことによりボンディングワイヤ4と接続端子15(スタッドバンプ35)との間の接続強度を向上でき、ボンディングワイヤ4の接続端子15(スタッドバンプ35)からの剥がれを抑制または防止することができる。このため、接続端子15から半導体チップ2までの距離を小さくすることができ、半導体装置1の平面寸法を低減することができる。また、厚みが比較的厚い半導体チップ2の使用も可能になり、半導体チップ2に対する選択の幅を広くすることができる。3040

#### 【0059】

ワイヤボンディング工程の後、図16および図28に示されるように、モールド工程(例えばトランスファモールド工程)による樹脂封止を行って封止樹脂5a(封止部)を形成し、半導体チップ2およびボンディングワイヤ4を封止樹脂5aによって封止する。このモールド工程では、配線基板31の上面31aの複数の半導体装置領域32を封止樹脂5aで一括して封止する一括封止を行う。すなわち、配線基板31の上面31aの複数の半導体装置領域32上に半導体チップ2およびボンディングワイヤ4を覆うように封止樹50

脂 5 a を形成する。このため、封止樹脂 5 a は、配線基板 3 1 の上面 3 1 a の複数の半導体装置領域 3 2 を覆うように形成される。封止樹脂 5 a は、例えば熱硬化性樹脂材料などの樹脂材料などからなり、フィラーなどを含むこともできる。例えば、フィラーを含むエポキシ樹脂などを用いて封止樹脂 5 a を形成することができる。

#### 【 0 0 6 0 】

このモールド工程では、封止樹脂 5 a を形成するための材料は、半導体チップ 2 の裏面 2 c の外周部 2 d の下方の空間 2 1 にも充填される。本実施の形態では、半導体チップ 2 の裏面 2 c の外周部 2 d の下方の空間 2 1 の高さ方向の寸法 H<sub>1</sub> が比較的大きいので、モールド工程で、封止樹脂 5 a を形成するための材料に含まれるフィラーなどが、半導体チップ 2 の裏面 2 c の外周部 2 d の下方の空間 2 1 に侵入しやすく、空間 2 1 を満たした（充填した）封止樹脂 5 a の成分比と、他の領域の封止樹脂 5 a の成分比とが均一化されるので、硬化した封止樹脂 5 a と半導体チップ 2 との密着性（接着強度）をより向上させることができる。10

#### 【 0 0 6 1 】

次に、図 1 7 に示されるように、配線基板 3 1 の下面 3 1 b のランド 1 6 に半田ボール 6 を接続（接合）する。例えば、配線基板 3 1 の下面 3 1 b を上方に向け、配線基板 3 1 の下面 3 1 b の複数のランド 1 6 上に複数の半田ボール 6 を配置してフラックスなどで仮固定し、リフロー処理（半田リフロー処理、熱処理）を行って半田を溶融し、半田ボール 6 と配線基板 3 1 の下面 3 1 b のランド 1 6 とを接合することができる。その後、必要に応じて洗浄工程を行い、半田ボール 6 の表面に付着したフラックスなどを取り除くことができる。このようにして、半導体装置 1 の外部端子としての半田ボール 6 が接合される。なお、本実施の形態では、半導体装置 1 の外部端子として半田ボール 6 を接合する場合について説明したが、これに限定されるものではなく、例えば半田ボール 6 の代わりに印刷法などによりランド 1 6 上に半田を供給して半導体装置 1 の外部端子（バンプ電極）を形成することもできる。また、半導体装置 1 は B G A (Ball Grid Array) 形態の半導体装置として説明したが、これに限定されるものではなく、半田ボール 6 の形成を省略し、半導体装置 1 を L G A (Land Grid Array) 形態の半導体装置とすることもできる。また、半導体装置 1 の外部端子（ここでは半田ボール 6 ）の材質は、鉛含有半田や鉛を含有しない鉛フリー半田を用いることができ、また、めっき（例えば金めっきや P d めっきなど）により半導体装置 1 の外部端子（バンプ電極）を形成することもできる。20

#### 【 0 0 6 2 】

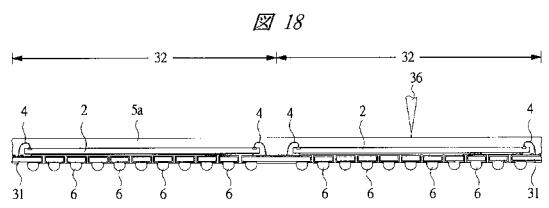

次に、図 1 8 に示されるように、マーキングを行って、封止樹脂 5 a の表面に製品番号などのマークを付す。例えば、レーザ 3 6 によりマーキングを行うレーザマークを行うことができるが、インクによりマーキングを行うインクマークを行うこともできる。また、図 1 7 の半田ボール 6 の接続工程と図 1 8 のマーキング工程の順番を入れ換え、図 1 8 のマーキング工程を行った後に、図 1 7 の半田ボール 6 の接続工程を行うこともできる。30

#### 【 0 0 6 3 】

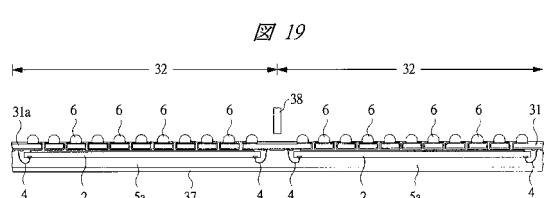

次に、図 1 9 に示されるように、封止樹脂 5 a の上面をパッケージ固定テープ 3 7 に貼り付け、配線基板 3 1 およびその上に形成された封止樹脂 5 a をダイシング領域（ダイシングライン）3 9 に沿ってダイシングブレード 3 8 などにより切断（ダイシング）して、それぞれの半導体装置領域（C S P 領域）を個々の（個片化された）半導体装置 1 （C S P ）に切断分離する。すなわち、配線基板 3 1 および封止樹脂 5 a を各半導体装置領域 3 2 に切断して分割する。このように、切断・個片化を行って、図 1 ~ 図 7 に示されるような半導体装置 1 を製造することができる。各半導体装置領域 3 2 に切断され分離（分割）された配線基板 3 1 が配線基板 3 に対応し、各半導体装置領域 3 2 に切断され分離（分割）された封止樹脂 5 a が封止樹脂 5 に対応する。40

#### 【 0 0 6 4 】

図 2 9 は、上記のようにして製造された半導体装置 1 の端部近傍領域の他の要部断面図（部分拡大断面図）であり、図 4 とは異なる領域の断面が示されている。上記のように、配線基板 3 （配線基板 3 1 ）の導体層 1 2 を電解めっき法を用いて形成しているので、配50

線基板 3 を構成する基材層 1 1 の上面 1 1 a 周辺部（基材層 1 1 の上面 1 1 a の端部と接続端子 1 5との間）には、めっき配線 3 4 が存在している。本実施の形態では、このめっき配線 3 4 上はソルダレジスト層 1 4（第 2 ソルダレジスト部 1 4 b）で覆われており、めっき配線 3 4 と封止樹脂 5 とは接触しないようになっている。

#### 【 0 0 6 5 】

本実施の形態とは異なり、めっき配線 3 4 上にソルダレジスト層 1 4 が形成されていない場合、接続端子 1 5 上に金めっき層を形成した際に、めっき配線 3 4 上にも金めっき層が形成され、封止樹脂 5（封止樹脂 5 a）を形成した際には、上面に金めっき層が形成されためっき配線 3 4 と封止樹脂 5 とが直接接触してしまう。この場合、封止樹脂 5 と電解金めっき層の密着性はソルダレジスト層 1 4 と封止樹脂 5 との密着性よりも低いため、めっき配線 3 4 と封止樹脂 5 における密着性が低下する。この密着性が低い界面（めっき配線 3 4 と封止樹脂 5 との界面）は個片化後に半導体装置の側面で露出するので、その界面から湿気（水分）が進入する吸湿不良を引き起こす。この吸湿不良により封止樹脂 5 の密着性の低下による剥離や、湿気によるボンディングワイヤ 4 の錆や酸化が生じ、半導体装置の信頼性が低下する可能性がある。10

#### 【 0 0 6 6 】

本実施の形態では、配線基板 3（配線基板 3 1）の導体層 1 2 を電解めっき法を用いて形成した場合には、めっき配線 3 4 上をソルダレジスト層 1 4（第 2 ソルダレジスト部 1 4 b）で覆うことで、めっき配線 3 4 と封止樹脂 5 とが接触しないようにし、密着性が低い界面が半導体装置の側面に形成されないようにするので、半導体装置の側面からの吸湿不良を抑制し、半導体装置の信頼性を向上させることができる。20

#### 【 0 0 6 7 】

##### （実施の形態 2 ）

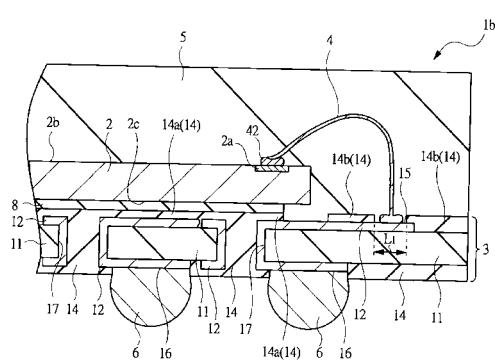

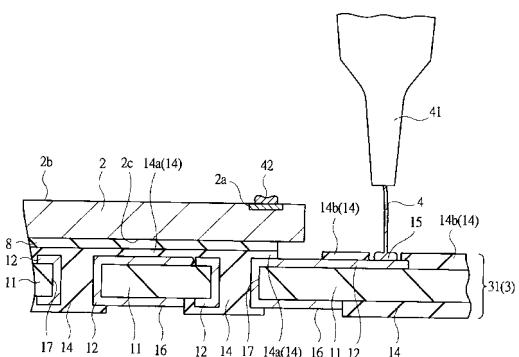

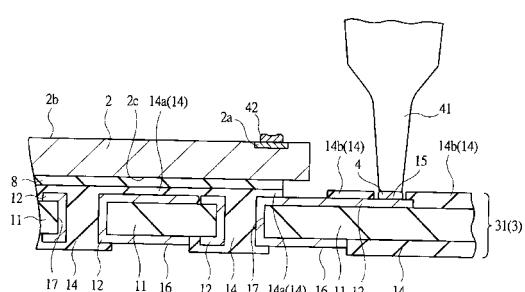

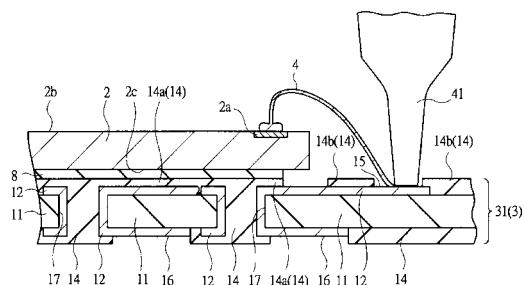

図 3 0 は、本発明の他の実施の形態である半導体装置 1 b の製造工程中の要部断面図であり、上記実施の形態 1 の図 4 にほぼ対応する領域が示されている。図 3 1 および図 3 2 は、本実施の形態のワイヤボンディング工程の説明図（要部断面図）である。

#### 【 0 0 6 8 】

本実施の形態の半導体装置 1 b の製造工程は、ワイヤボンディング工程以外は上記実施の形態 1 とほぼ同様であるのでここではその説明は省略し、本実施の形態の半導体装置 1 b の製造工程におけるワイヤボンディング工程について説明する。30

#### 【 0 0 6 9 】

上記実施の形態 1 では、先に半導体チップ 2 の電極 2 a にボンディングワイヤ 4 の一端を接続（ファーストボンディング）してから、配線基板 3 1 の接続端子 1 5 にボンディングワイヤ 4 の他端を接続（セカンドボンディング）しているが、本実施の形態では、先に配線基板 3 1 の接続端子 1 5 にボンディングワイヤ 4 の一端を接続（ファーストボンディング）してから、半導体チップ 2 の電極 2 a にボンディングワイヤ 4 の他端を接続（セカンドボンディング）している。

#### 【 0 0 7 0 】

すなわち、まず、図 3 1 に示されるように、ボンディングワイヤ 4 形成用のワイヤボンディング装置のキャピラリ 4 1 に保持された金（Au）などからなるボンディングワイヤ 4 の先端を超音波を印加しながら配線基板 3 1 の接続端子 1 5 表面に押し付けて接続する。それから、図 3 2 に示されるように、キャピラリ 4 1 を上方に引き上げてから横方向に移動させ、ボンディングワイヤ 4 を半導体チップ 2 の電極 2 a の表面に超音波を印加しながらこすりつけて接続してからボンディングワイヤ 4 を切断する。これにより、配線基板 3 1 の接続端子 1 5 と半導体チップ 2 の電極 2 a とをボンディングワイヤ 4 を介して電気的に接続することができる。このようにしてワイヤボンディングを行うことで、図 3 0 に示される半導体装置 1 b を製造することができる。40

#### 【 0 0 7 1 】

図 3 3 は、本実施の形態とは異なり、先に半導体チップ 2 の電極 2 a にボンディングワイヤ 4 の一端を接続（ファーストボンディング）してから、配線基板 3 1 の接続端子 1 5

10

20

30

40

50

にボンディングワイヤ4の他端を接続(セカンドボンディング)する様子を示す要部断面図である。図33に示されるように、先に半導体チップ2の電極2aにボンディングワイヤ4の一端を接続する場合は、セカンドボンディングを行うためにキャピラリ41を接続端子15上に移動するときにキャピラリ41と半導体チップ2との間にボンディングワイヤ4が位置することになる。このため、配線基板31の接続端子15を半導体チップ2に近づけ過ぎると、ボンディングワイヤ4が半導体チップ2と接触してしまう可能性がある。

#### 【0072】

それに対して、本実施の形態では、図31および図32に示されるように、先に配線基板31の接続端子15にボンディングワイヤ4の一端を接続(ファーストボンディング)してから、半導体チップ2の電極2aにボンディングワイヤ4の他端を接続(セカンドボンディング)している。すなわち、配線基板31の接続端子15へのファーストボンディングを行った後、キャピラリ41を上方に引き上げてから横方向に移動させ、半導体チップ2の電極2aへのセカンドボンディングを行うことができる。このため、セカンドボンディングを行うためにキャピラリ41を半導体チップ2の電極2a上に移動するときに、キャピラリ41と半導体チップ2との間にボンディングワイヤ4が位置しない。従って、配線基板31の接続端子15を半導体チップ2に近づけても、ボンディングワイヤ4が半導体チップ2と接触してしまうのを防止することができる。これにより、半導体装置の信頼性を高めることができる。また、配線基板31の接続端子15を半導体チップ2により近づけることが可能になるので、半導体装置を小型化(小面積化)することができる。

#### 【0073】

また、ワイヤボンディング工程では、セカンドボンディングに比較してファーストボンディングの方が、接続に要する電極面積を小さくすることができる。本実施の形態では、先に配線基板31の接続端子15にボンディングワイヤ4の一端を接続(ファーストボンディング)することにより、接続端子15の面積を小さくすることができる。第2ソルダレジスト部14bの接続端子15露出用の開口部19を小さくすることができる。すなわち、キャピラリ41に保持されたボンディングワイヤ4の先端を超音波を印加しながら配線基板31の接続端子15表面に押し付けて接続(ファーストボンディング)してから、キャピラリ41を上方に引き上げるので、接続端子15を小さくすることができ、第2ソルダレジスト部14bの接続端子15露出用の開口部19を小さくすることができる。例えば、接続端子15の長さ(接続端子15の延在方向の長さ) $L_1$ 、すなわち第2ソルダレジスト部14bの接続端子15露出用の開口部19の長さ $L_1$ を、好ましくは120μm以下( $L_1 = 120 \mu m$ )、より好ましくは100μm以下( $L_1 = 100 \mu m$ )にすることができる。これにより、半導体装置の小型化(小面積化)が可能になる。

#### 【0074】

また、図31および図32の要部断面図に示されるように、半導体チップ2の電極2aに金(Au)などからなるスタッドバンプ(バンプ電極、バンプ)42を形成しておき、セカンドボンディングの際には、半導体チップ2の電極2a上のスタッドバンプ42にボンディングワイヤ4を接続すれば、より好ましい。これにより、ボンディングワイヤ4と半導体チップ2の電極2aとの接続強度を向上することができる。また、半導体チップ2の電極2aへのセカンドボンディングの際に半導体チップ2に与えられるストレスを低減することができる。

#### 【0075】

さらには、ボンディングワイヤ4と半導体チップ2(半導体チップの表面側における端部2f)との距離が大きく取れるので、半導体チップ2の裏面2c側への封止樹脂5の流动性が、図33に示すようにワイヤボンディングする場合よりも向上できる。

#### 【0076】

##### (実施の形態3)

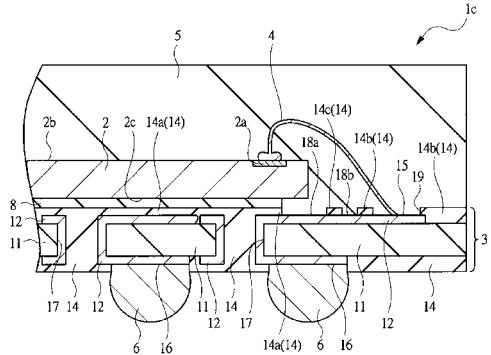

図34は、本発明の他の実施の形態である半導体装置1cの要部断面図であり、図35は、その平面透視図(上面図)である。図34は、上記実施の形態1の図4に対応する。

10

20

30

40

50

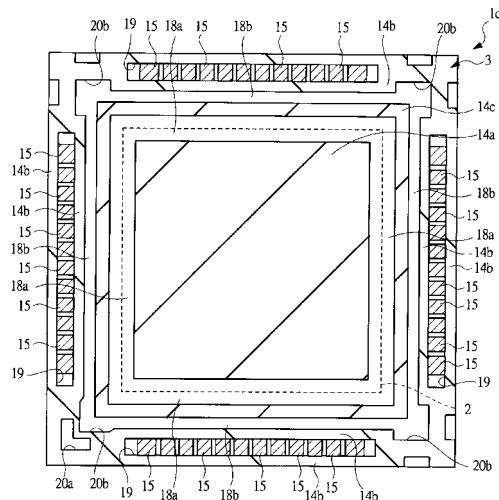

また、図35は、上記実施の形態1の図7に対応し、封止樹脂5、半導体チップ2およびボンディングワイヤ4を透視したときの半導体装置1cの平面透視図（上面図）、すなわち半導体装置1cに用いられている配線基板3の上面図が示されている。なお、図35では、半導体チップ2の外形を点線で示してある。また、図35は平面図であるが、理解を簡単にするために、第1ソルダレジスト部14a、第2ソルダレジスト部14b、第3ソルダレジスト部14c、および第2ソルダレジスト部14bの開口部19から露出する接続端子15にハッチングを付してある。

#### 【0077】

本実施の形態の半導体装置1cは、配線基板3の上面3aに形成されたソルダレジスト層14以外の構成は、上記実施の形態1の半導体装置1とほぼ同様であるのでここではその説明は省略し、半導体装置1cにおける配線基板3の上面3aに形成されたソルダレジスト層14について説明する。10

#### 【0078】

上記実施の形態1では、配線基板3の上面3aのソルダレジスト層14は、半導体チップ2の下方に位置する第1ソルダレジスト部14aと、配線基板3の上面3aの外周部上に位置する第2ソルダレジスト部14bとによって構成されていたが、本実施の形態の半導体装置1cでは、配線基板3の上面3aのソルダレジスト層14は、図34および図35に示されるように、半導体チップ2の下方に位置する第1ソルダレジスト部14aと、配線基板3の上面3aの外周部上に位置する第2ソルダレジスト部14bと、更に、第1ソルダレジスト部14aと第2ソルダレジスト部14bとの間に第3ソルダレジスト部14cを有している。第1ソルダレジスト部14aと第3ソルダレジスト部14cとの間には、ソルダレジスト層14が形成されずに基材層11（および導体層12からなる引き出し配線）が露出された領域（ダム領域）18aが存在し、第3ソルダレジスト部14cと第2ソルダレジスト部14bとの間には、ソルダレジスト層14が形成されずに基材層11（および導体層12からなる引き出し配線）が露出された領域（ダム領域）18bが存在している。第1ソルダレジスト部14a上に接着材8を介して半導体チップ2が接合（搭載、接続、固定、配置）されている。第2ソルダレジスト部14bは、接続端子15を露出するための開口部19を有している。上記実施の形態1と同様に、第1ソルダレジスト部14aの平面寸法（面積）は、半導体チップ2の平面寸法（面積）よりも小さい。このため、半導体チップ2を搭載したとき、半導体チップ2の裏面2cの外周部2dの下方には、第1ソルダレジスト部14aが延在（存在）しない。20

#### 【0079】

このように、本実施の形態では、配線基板3の上面3aには、その上に接着材8を介して半導体チップ2を接合する第1ソルダレジスト部14aと、第1ソルダレジスト部14aの周囲（外周）に設けられた第3ソルダレジスト部14cと、第3ソルダレジスト部14cの周囲（外周）に設けられてその開口部19から接続端子15を露出する第2ソルダレジスト部14bとが形成されている。第1ソルダレジスト部14aと第3ソルダレジスト部14cとの間および第3ソルダレジスト部14cと第2ソルダレジスト部14bとの間には、ソルダレジスト層14が形成されずに基材層11が露出する領域（ダム領域）18a, 18bが存在している。このため、半導体チップ2を配線基板3上にダイボンディングしたときには、第1ソルダレジスト部14aと第3ソルダレジスト部14cとの間にソルダレジスト層14がなく基材層11が露出した領域（ダム領域）18aを設けたことにより、ペースト材などからなる接着材8が領域18aを越えて第3ソルダレジスト部14c上にまで広がったとしても、第3ソルダレジスト部14cと第2ソルダレジスト部14bとの間にソルダレジスト層14がなく基材層11が露出した領域（ダム領域）18bを設けたことにより、ペースト材などからなる接着材8が領域18bを越えて第2ソルダレジスト部14b上にまで広がってしまうのを防止することができる。これにより、接着材8が接続端子15上にまで広がってしまうのを防止することができる。30

うのをより確実に防止でき、ボンディングワイヤ4と接続端子15との間の電気的接続の信頼性をより的確に向上することができる。また、たとえ流動性が比較的高いペースト型の接着材(接合材)を接着材8として用いたとしても、ペースト材からなる接着材8が接合端子15上にまで広がってしまうのを防止することができるので、ダイボンドフィルムよりも相対的に廉価なペースト型の接着材を接着材8として用いることが可能になり、半導体装置の製造コストの低減に有利である。

#### 【0080】

##### (実施の形態4)

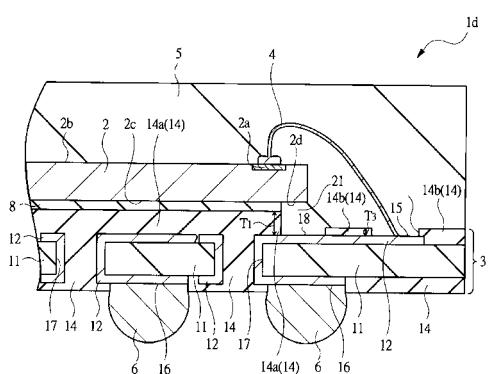

図36は、本発明の他の実施の形態である半導体装置1dの要部断面図であり、上記実施の形態1の図4に対応する。

10

#### 【0081】

上記実施の形態1では、半導体装置1の配線基板3の上面3aの第1ソルダレジスト部14aの厚みと第2ソルダレジスト部14bとの厚みとは、ほぼ同じ厚みであったが、本実施の形態の半導体装置1dでは、配線基板3の上面3aの第1ソルダレジスト部14aの厚みT<sub>1</sub>が第2ソルダレジスト部14bの厚みT<sub>3</sub>よりも厚く(T<sub>1</sub>>T<sub>3</sub>)なっている。他の構成は上記実施の形態1とほぼ同様であるので、ここではその説明は省略する。

#### 【0082】

本実施の形態では、図36に示されるように、半導体チップ2よりも平面寸法が小さく、その上に接着材8を介して半導体チップ2を接合する第1ソルダレジスト部14aの厚みをT<sub>1</sub>を、第1ソルダレジスト部14aの周囲(外周)に設けられた第2ソルダレジスト部14bの厚みT<sub>3</sub>よりも厚く(T<sub>1</sub>>T<sub>3</sub>)している。このような配線基板3は、例えば、基材層11の上面11aにソルダレジスト層14を形成する際に、ソルダレジスト層を2度塗り(複数塗り、複数印刷)し、第2ソルダレジスト部14bは1層目のソルダレジスト層によって形成することで相対的に薄くし、第1ソルダレジスト部14aは1層目および2層目のソルダレジスト層(の積層膜)によって形成することで相対的に厚くすることで、準備(製造)することができる。

20

#### 【0083】

本実施の形態では、第1ソルダレジスト部14aの厚みT<sub>1</sub>を第2ソルダレジスト部14bの厚みT<sub>3</sub>よりも厚く(T<sub>1</sub>>T<sub>3</sub>)しているので、第1ソルダレジスト部14aの厚みT<sub>1</sub>と第2ソルダレジスト部14bの厚みT<sub>3</sub>とが同じ(T<sub>1</sub>=T<sub>3</sub>)場合に比較して、配線基板3上に半導体チップ2をダイボンディングしたときに半導体チップ2の裏面2cの外周部2dと配線基板3の上面3aとの間に形成される空間21の高さ方向の寸法H<sub>1</sub>をより大きくすることができる。このため、封止樹脂5を形成するときに、封止樹脂5を形成するための材料に含まれるフィラーなどが、半導体チップ2の裏面2cの外周部2dの下方の空間21により侵入しやすくなり、空間21を充填した封止樹脂5の成分比と、他の領域の封止樹脂5の成分比とをより均一化することができる。これにより、硬化した封止樹脂5と半導体チップ2との密着性(接着強度)をより向上させ、半導体装置1dの信頼性をより向上することができる。

30

#### 【0084】

##### (実施の形態5)

40

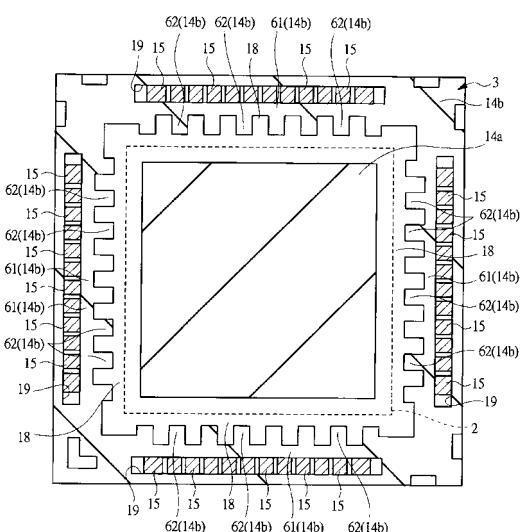

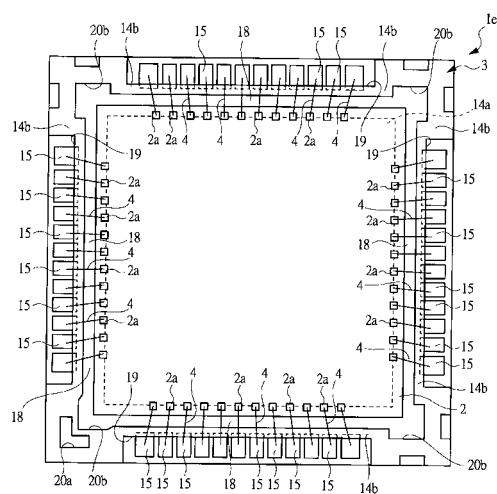

図37は、本発明の他の実施の形態である半導体装置の平面透視図(上面図)であり、図38は、本発明の更に他の実施の形態である半導体装置の平面透視図(上面図)であり、それぞれ上記実施の形態1の図7に対応する。従って図37および図38には、封止樹脂5、半導体チップ2およびボンディングワイヤ4を透視したときの半導体装置の平面透視図(上面図)、すなわち、本実施の形態の半導体装置に用いられている配線基板3の上面図が示されている。また、図37および図38では、半導体チップ2の外形を点線で示してある。また、図37および図38は平面図であるが、理解を簡単にするために、第1ソルダレジスト部14a、第2ソルダレジスト部14b、および第2ソルダレジスト部14bの開口部19から露出する接続端子15にハッチングを付してある。

#### 【0085】

50

本実施の形態の半導体装置は、配線基板3の上面3aに形成された第2ソルダレジスト部14bのパターン形状以外の構成は、上記実施の形態1の半導体装置1とほぼ同様であるのでここではその説明は省略し、本実施の形態の半導体装置における配線基板3の上面3aに形成された第2ソルダレジスト部14bのパターン形状について説明する。

#### 【0086】

本実施の形態では、第2ソルダレジスト部14bの内周部（第1ソルダレジスト部14aに対向する第2ソルダレジスト部14bの四辺、半導体チップ2の四辺に対向する第2ソルダレジスト部14bの四辺）には、櫛歯状（凹凸状）のパターンが形成されている。すなわち、第2ソルダレジスト部14bは、配線基板3の上面3aの外周部上に形成され、接続端子15を露出するための開口部19を有する第1の部分61と、第1の部分61に接続し、第1の部分61から第1ソルダレジスト部14a（半導体チップ2）に近づく方向に延在する複数の第2の部分62とを有している。櫛歯状のパターンを含む第2ソルダレジスト部14b全体の膜厚はほぼ均一である。

10

#### 【0087】

第2ソルダレジスト部14bを第1の部分61と複数の第2の部分62とにより形成し、第2ソルダレジスト部14bの内周の四辺に櫛歯状のパターン（ソルダレジストパターン）を設けることで、封止樹脂5をトランスファモールド工程などによって形成する際に、半導体チップ2の裏面2cの外周部2dと配線基板3の上面3aとの間の空間21から空気が抜けやすくなり、封止樹脂5を形成するための材料の流動性が向上し、上記空間21への封止樹脂の充填性をより向上させることができる。このため、半導体チップ2と封止樹脂5との密着性（接着強度）をより向上させることができ、半導体装置の信頼性をより向上させることができる。

20

#### 【0088】

また、図37のように、第2ソルダレジスト部14bの第2の部分62が半導体チップ2の下方まで延在していなければ、半導体チップ2を配線基板3の上面3aにダイボンディングしたときに半導体チップ2の裏面2cの外周部2dと配線基板3の上面3aとの間に形成される空間21をより広くすることができ、封止樹脂5を形成するときにフィラーなどが半導体チップ2の裏面2cの外周部2dの下方の空間21に侵入しやすくすることができる。これにより、空間21を満たす封止樹脂5の成分比と、他の領域の封止樹脂5の成分比とをより均一にすることができる。また、図38のように第2ソルダレジスト部14bの第2の部分62を半導体チップ2の下方まで延在させることもでき、この場合、接続端子15を半導体チップ2側により近づけることが可能になり、半導体装置の小型化（小面積化）により有利である。

30

#### 【0089】

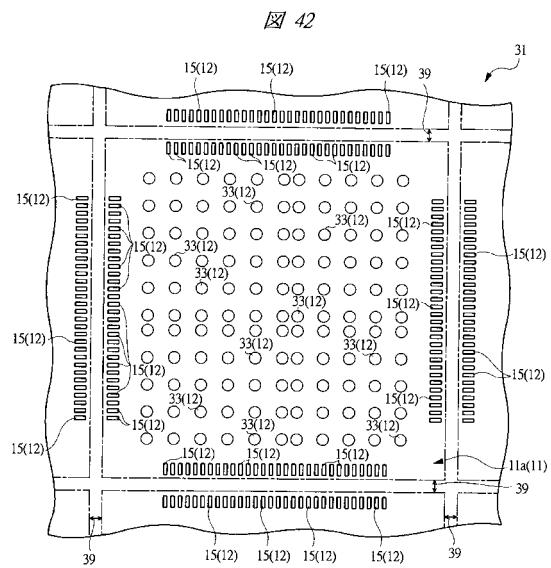

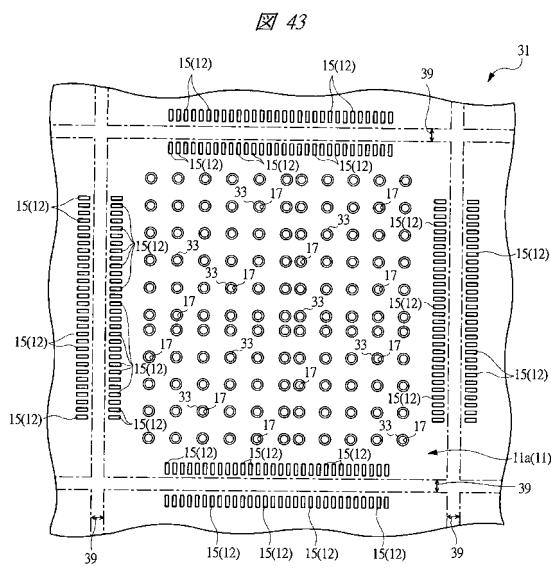

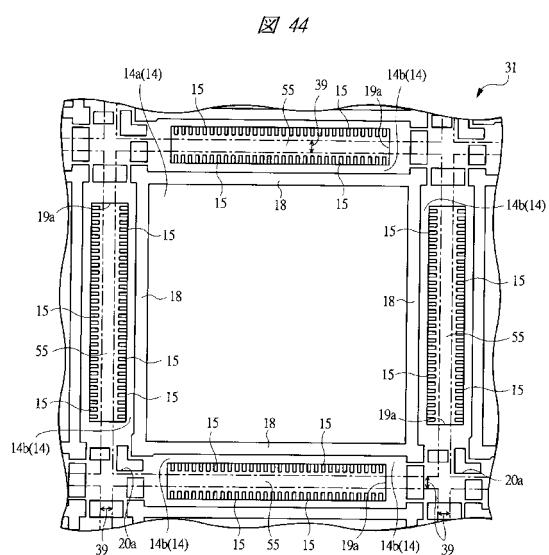

##### （実施の形態6）

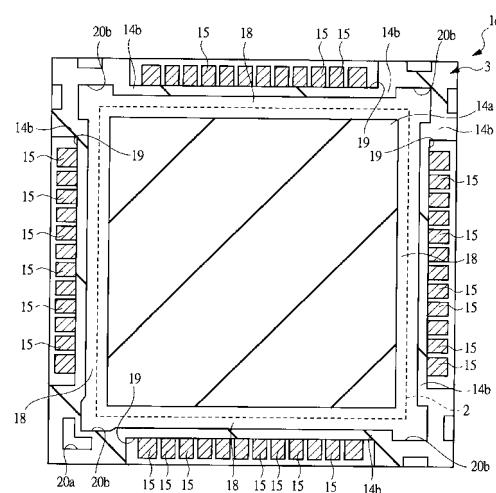

図39は、本発明の他の実施の形態である半導体装置1eの端部近傍領域の要部断面図（部分拡大断面図）であり、上記実施の形態1の図4に対応する。図40は、封止樹脂5を透視したときの半導体装置1eの平面透視図（上面図）であり、上記実施の形態1の図6に対応する。図41は、封止樹脂5、半導体チップ2およびボンディングワイヤ4を透視したときの半導体装置1eの平面透視図（上面図）、すなわち半導体装置1eに用いられている配線基板3の上面図であり、上記実施の形態1の図7に対応する。図42～図44は、本実施の形態の半導体装置1eの製造に用いられる配線基板31の製造工程の一例を模式的に示す平面図（上面図）であり、上記実施の形態1の図21～図23に対応する。なお、図41では、半導体チップ2の外形を点線で示してある。また、図41は平面図であるが、理解を簡単にするために、第1ソルダレジスト部14a、第2ソルダレジスト部14b、および第2ソルダレジスト部14bから露出する接続端子15にハッチングを付してある。

40

#### 【0090】

上記実施の形態1では、半導体装置1の配線基板3の上面3aおよび下面3bの導体層12は、主として電解めっき法を用いて形成されていたが、本実施の形態では、半導体装

50

置 1 e の配線基板 3 の上面 3 a および下面 3 b の導体層 1 2 は、電解めっき法を用いずに、無電解めっき法を用いて形成されている。また、上記実施の形態 1 では、半導体装置 1 の配線基板 3 の上面 3 a の外周端部上には第 2 ソルダレジスト部 1 4 b が形成されていたが、本実施の形態の半導体装置 1 e では、図 3 9 ~ 図 4 1 に示されるように、配線基板 3 の上面 3 a の接続端子 1 5 よりも外周側の領域には第 2 ソルダレジスト部 1 4 b ( ソルダレジスト層 1 4 ) が形成されておらず、配線基板 3 の上面 3 a の外周端部では配線基板 3 の基材層 1 1 が封止樹脂 5 と密着 ( 接触 ) している。他の構成は上記実施の形態 1 とほぼ同様であるので、ここではその説明は省略する。

#### 【 0 0 9 1 】

まず、本実施の形態の半導体装置 1 e の製造に用いられる配線基板 3 1 の製造工程について説明する。配線基板 3 1 は例えば次のようにして製造することができる。 10

#### 【 0 0 9 2 】

コア材としての絶縁性の基材層 1 1 の上面 1 1 a および下面に無電解めっき ( 無電界めっき ) 法により無電解銅めっき層を形成し、この無電解銅めっき層をエッチングなどによりパターニングする。上記実施の形態 1 では無電解銅めっき層上に、電解銅めっき層を形成したが、本実施の形態では、無電解銅めっき層を厚く形成しておき、電解銅めっき層は形成しない。この無電解銅めっき層 ( 銅層 ) によって、配線基板 3 1 ( 配線基板 3 ) の導体層 1 2 を形成することができる。図 4 2 には、スルーホール用の導体パターン 3 3 と接続端子 1 5 ( 用の導体パターン ) とが、基材層 1 1 の上面に、無電解銅めっき層 ( 導体層 1 2 ) によって形成された状態が示されている。接続端子 1 5 と導体パターン 3 3 とは、基材層 1 1 の上面 1 1 a に形成された無電解銅めっき層 ( 導体層 1 2 ) からなる引き出し配線 ( 図示省略 ) によって電気的に接続されている。また、図示はしないけれども、基材層 1 1 の下面には、ランド 1 6 も、無電解銅めっき層 ( 導体層 1 2 ) によって形成されている。また、本実施の形態では、電解めっき法を用いないので、基材層 1 1 の上面 1 1 a には、上記実施の形態 1 のようなめっき配線 ( 給電線 ) 3 4 は形成されていない。 20

#### 【 0 0 9 3 】

次に、図 4 3 に示されるように、基材層 1 1 に開口部 ( スルーホール、ビア、貫通孔 ) 1 7 を形成する。開口部 1 7 は、スルーホール用の導体パターン 3 3 の内側に形成される。 30

#### 【 0 0 9 4 】

次に、無電解めっき法により開口部 1 7 の側壁上に無電解銅めっき層を形成する。この基材層 1 1 の側壁上に形成された無電解銅めっき層によって、開口部 1 7 の側壁上の上記導体層 1 2 が形成される。それから、図 4 4 に示されるように、印刷法などを用いてソルダレジスト層 1 4 を基材層 1 1 の上面 1 1 a および下面に開口部 1 7 内を埋めるように形成する。これにより、基材層 1 1 の上面 1 1 a には、第 1 ソルダレジスト部 1 4 a と第 2 ソルダレジスト部 1 4 b が形成される。基材層 1 1 の上面 1 1 a では、接続端子 1 5 がソルダレジスト層 1 4 の開口部 1 9 a から露出し、基材層 1 1 の下面では、ランド 1 6 がソルダレジスト層 1 4 の開口部から露出する。接続端子 1 5 を露出するための開口部 1 9 a は、第 2 ソルダレジスト部 1 4 b に形成されており、第 2 ソルダレジスト部 1 4 b の開口部 1 9 a の中央をダイシング領域 3 9 が横切るように形成されている。次に、基材層 1 1 の上面 1 1 a および下面の無電解銅めっき層の露出部 ( すなわち接続端子 1 5 およびランド 1 6 ) 上に、無電解ニッケルめっき層、無電解パラジウムめっき層および金めっき層を無電解めっき法により順に形成する。その後、必要に応じて基材層 1 1 を外形加工 ( 切断 ) して配線基板 3 1 を形成することができる。 40

#### 【 0 0 9 5 】

このようにして製造された配線基板 3 1 を用いて本実施の形態の半導体装置 1 e を製造することができるが、その製造工程は上記実施の形態 1 とほぼ同様であるので、ここではその説明は省略する。

#### 【 0 0 9 6 】

本実施の形態では、上記のように、配線基板 3 ( 配線基板 3 1 ) の導体層 1 2 を電解め 50

つき法を用いずに、無電解めっき法を用いて形成している。すなわち、配線基板3の接続端子15やランド16を電解めっき法を用いずに、無電解めっき法を用いて形成している。導体層12の形成のために電解めっき法を用いていないので、配線基板3の上面3a(配線基板31上面31a)には、上記実施の形態1のようなめっき配線(給電線)34は形成されていない。また、本実施の形態では、上記のように、接続端子15を露出するための開口部19aの中央をダイシング領域39が横切るようにすることで、配線基板3の上面3aの接続端子15よりも外周側の領域には第2ソルダレジスト部14bが形成されない。すなわち、配線基板3の上面3aでは、接続端子15から配線基板3の端部にかけて第2ソルダレジスト部14b(ソルダレジスト層14)が延在していない。このため、配線基板3の上面3aの外周端部では配線基板3の基材層11が露出し、露出した基材層11が封止樹脂5と密着することができる。本実施の形態では、配線基板3の上面3aの外周端部では、めっき配線が存在せず、基材層11と封止樹脂5とが密着するので、密着性が低い界面が半導体装置の側面に形成されず、半導体装置の信頼性を向上させることができる。10

#### 【0097】

また、配線基板3の上面3aの接続端子15よりも外周側の領域には第2ソルダレジスト部14bが形成されていないので、接続端子15へのワイヤボンディングを行う際に、キャピラリ(上記キャピラリ41に対応)が第2ソルダレジスト部14bに接触するのを防止することができる。このため、接続端子15へのワイヤボンディングが安定し、接続端子15とボンディングワイヤ4との電気的接続の信頼性をより向上させることができる。20また、接続端子15の面積を小さくすることも可能になり、半導体装置の小型化(小面積化)に有利である。また、一つの接続端子15に複数のボンディングワイヤ4を接続する複数ボンディング(例えばダブルボンディングやトリプルボンディング)も容易になる。

#### 【0098】

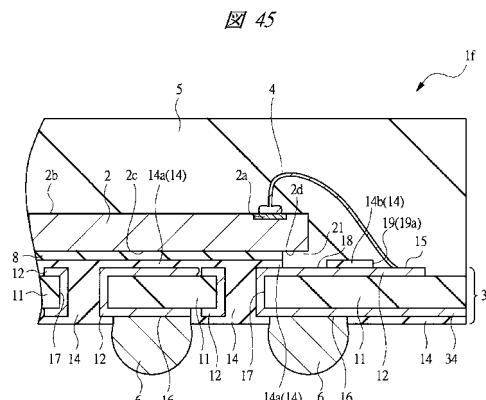

##### (実施の形態7)

図45は、本発明の他の実施の形態である半導体装置1fの要部断面図であり、上記実施の形態6の図39に対応する。

#### 【0099】

上記実施の形態6の半導体装置1eでは、半導体装置1eの配線基板3の上面3aおよび下面3bの導体層12は、電解めっき法を用いずに無電解めっき法を用いて形成していたが、本実施の形態の半導体装置1fでは、上記実施の形態1の半導体装置1と同様に、半導体装置1の配線基板3の上面3aおよび下面3bの導体層12を主として電解めっき法(または電解めっき法および無電界めっき法の組み合わせ)を用いて形成している。しかしながら、上記実施の形態1の半導体装置1とは異なり、本実施の形態の半導体装置1fでは、めっき配線(給電線)34を基材層11の上面11a上は形成せずに、基材層11の下面11b上に形成している。本実施の形態の半導体装置1fの他の構成および製造工程は上記半導体装置1eとほぼ同様である。従って、封止樹脂5を透視したときの半導体装置1fの平面透視図(上面図)は、上記実施の形態6の図40と同様であり、封止樹脂5、半導体チップ2およびボンディングワイヤ4を透視したときの半導体装置1fの平面透視図(上面図)、すなわち半導体装置1fに用いられている配線基板3の上面図は、上記実施の形態6の図41と同様である。すなわち、本実施の形態の半導体装置1fにおいても、上記実施の形態6の半導体装置1eと同様のソルダレジスト層14(第1ソルダレジスト部14aおよび第2ソルダレジスト部14b)のパターン形状を有している。このため、上記実施の形態6の半導体装置1eと同様に、本実施の形態の半導体装置1fにおいても、配線基板3の上面3aの接続端子15よりも外周側の領域には第2ソルダレジスト部14b(ソルダレジスト層14)が形成されておらず、配線基板3の上面3aの外周端部では配線基板3の基材層11が封止樹脂5と密着(接触)している。3040

#### 【0100】

本実施の形態においても、上記実施の形態6と同様に、配線基板3の上面3aの接続端

50

子 15 よりも外周側の領域には第 2 ソルダレジスト部 14 b が形成されていないので、接続端子 15 へのワイヤボンディングを行う際に、キャピラリ（上記キャピラリ 41 に対応）が第 2 ソルダレジスト部 14 b に接触するのを防止することができる。このため、接続端子 15 へのワイヤボンディングが安定し、接続端子 15 とボンディングワイヤ 4 との電気的接続の信頼性をより向上させることができる。また、接続端子 15 の面積を小さくすることも可能になり、半導体装置の小型化（小面積化）に有利である。また、一つの接続端子 15 に複数のボンディングワイヤ 4 を接続する複数ボンディング（例えばダブルボンディングやトリプルボンディング）も容易になる。

#### 【 0101 】

また、本実施の形態では、配線基板 3 の上面 3 a および下面 3 b の導体層 12 を主として電解めっき法を用いて形成しているが、電解めっきの際に用いるめっき配線（給電線）34 を基材層 11 の上面 11 a 上は形成せずに、基材層 11 の下面 11 b 上に形成している。このため、配線基板 3 の上面 3 a（配線基板 31 上面 31 a）には、めっき配線（給電線）34 は形成されていない。また、本実施の形態でも、上記実施の形態 6 のように、接続端子 15 を露出するための開口部 19 a の中央をダイシング領域 39 が横切るようにすることで、配線基板 3 の上面 3 a の接続端子 15 よりも外周側の領域には第 2 ソルダレジスト部 14 b が形成されない。すなわち、半導体装置 1f の配線基板 3 の上面 3 a では、接続端子 15 から配線基板 3 の端部にかけて第 2 ソルダレジスト部 14 b（ソルダレジスト層 14）が延在していない。このため、配線基板 3 の上面 3 a の外周端部では配線基板 3 の基材層 11 が露出し、露出した基材層 11 が封止樹脂 5 と密着することができる。本実施の形態では、配線基板 3 の上面 3 a の外周端部では、めっき配線が存在せず、基材層 11 と封止樹脂 5 とが密着するので、密着性が低い界面が半導体装置の側面に形成されず、半導体装置の信頼性を向上させることができる。

#### 【 0102 】

##### （実施の形態 8 ）

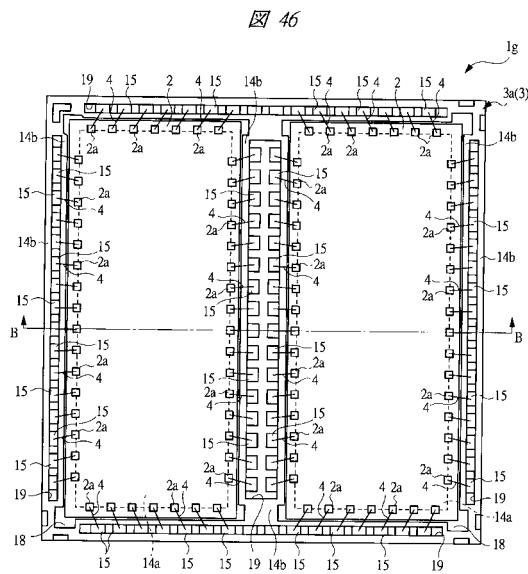

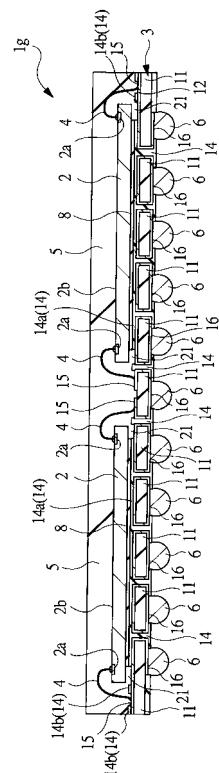

図 46 は、本発明の他の実施の形態である半導体装置 1g の平面透視図（上面図）であり、図 47 は、その断面図である。図 46 は、上記実施の形態 1 の図 6 に対応し、封止樹脂 5 を透視したときの半導体装置 1g の平面透視図（上面図）が示されている。図 47 は、上記実施の形態 1 の図 3 に対応し、図 46 の B - B 線の断面が図 47 にほぼ対応する。

#### 【 0103 】

上記実施の形態 1 の半導体装置 1 では、配線基板 3 上に一つの半導体チップ 2 が搭載されていたが、本実施の形態の半導体装置 1g では、配線基板 3 上に複数の半導体チップ 2 が搭載されている。ここでは 2 つの半導体チップ 2 が搭載されている例について説明するが、これに限定されるものではなく、配線基板 3 上に 2 つ以上の半導体チップ 2 を搭載して半導体装置 1g を製造することができる。

#### 【 0104 】

本実施の形態では、配線基板 3 の上面 3 a には、その上に接着材 8 を介して半導体チップ 2 を接合する第 1 ソルダレジスト部 14 a と、第 1 ソルダレジスト部 14 a の周囲（外周）に設けられ、その開口部 19 から接続端子 15 を露出する第 2 ソルダレジスト部 14 b とが形成されているが、配線基板 3 上に搭載する半導体チップ 2 の数と同数の第 1 ソルダレジスト部 14 a が配線基板 3 の上面 3 a に形成されている。例えば、図 46 および図 47 のように 2 つの半導体チップ 2 を配線基板 3 上に搭載する場合は、2 つの第 1 ソルダレジスト部 14 a が配線基板 3 の上面 3 a に形成され、各第 1 ソルダレジスト部 14 a 上に接着材 8 を介して半導体チップ 2 が接合されている。複数の半導体チップ 2 の複数の電極 2 a は、配線基板 3 の複数の接続端子 15 に複数のボンディングワイヤ 4 を介して電気的に接続されている。他の構成は上記実施の形態 1 とほぼ同様である。

#### 【 0105 】

本実施の形態においても、半導体チップ 2 を接合する第 1 ソルダレジスト部 14 a のそれぞれと第 2 ソルダレジスト部 14 b との間には、ソルダレジスト層 14 が形成されずに基材層 11 が露出する領域（ダム領域）18 が存在しているので、半導体チップ 2 を配線

10

20

30

40

50

基板 3 上にダイボンディングしたときに、ペースト材などからなる接着材 8 が領域 1 8 を越えて第 2 ソルダレジスト部 1 4 b 上にまで広がってしまうのを防止することができる。これにより、接着材 8 が接続端子 1 5 上にまで広がってしまうのを防止でき、ボンディングワイヤ 4 と接続端子 1 5 との間の電気的接続の信頼性を向上することができる。

#### 【 0 1 0 6 】

また、本実施の形態においても、各半導体チップ 2 は、その半導体チップよりも平面寸法（面積）が小さな第 1 ソルダレジスト部 1 4 a 上に接着材 8 を介して接合されている。このため、各半導体チップ 2 を配線基板 3 の上面 3 a にダイボンディングしたときに、各半導体チップ 2 の裏面 2 c の外周部 2 d の下方には第 1 ソルダレジスト部 1 4 a および接着材 8 が延在（存在）せず、各半導体チップ 2 の裏面 2 c の外周部 2 d と配線基板 3 の上面 3 a との間に空間 2 1 が形成される。このため、封止樹脂 5 を形成するときには、封止樹脂 5 を形成するための材料が各半導体チップ 2 の裏面 2 c の外周部 2 d と配線基板 3 の上面 3 a との間の空間 2 1 にも充填され、硬化した封止樹脂 5 が各半導体チップ 2 の表面 2 b、側面 2 e、および裏面 2 c の外周部 2 d を覆うので、各半導体チップ 2 と封止樹脂 5 との密着性（接着強度）を高めることができ、半導体装置 1 g の信頼性を向上させることができる。また、封止樹脂 5 を形成するときに、封止樹脂 5 を形成するための材料に含まれるフィラーなどが、各半導体チップ 2 の裏面 2 c の外周部 2 d の下方の空間 2 1 に侵入しやすく、空間 2 1 を充填した封止樹脂 5 の成分比と、他の領域の封止樹脂 5 の成分比とが均一化される。これにより、硬化した封止樹脂 5 と各半導体チップ 2 との密着性（接着強度）をより向上させ、半導体装置 1 g の信頼性をより向上させることができる。10

#### 【 0 1 0 7 】

##### （実施の形態 9 ）

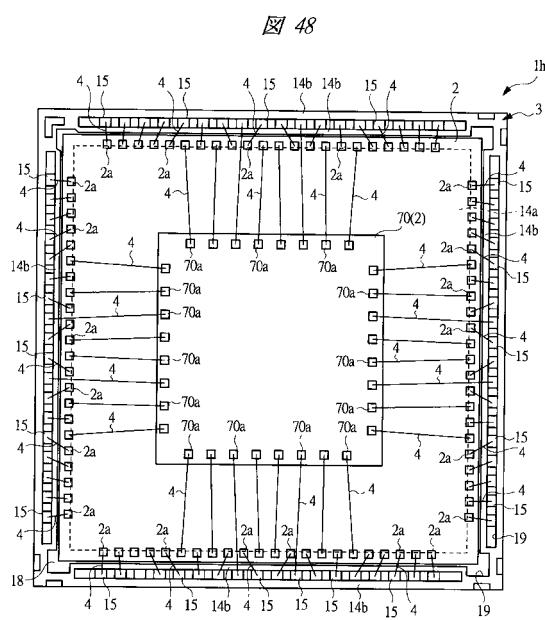

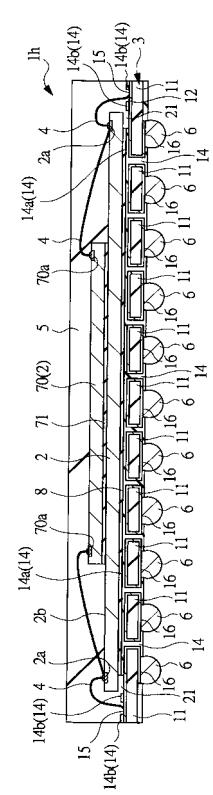

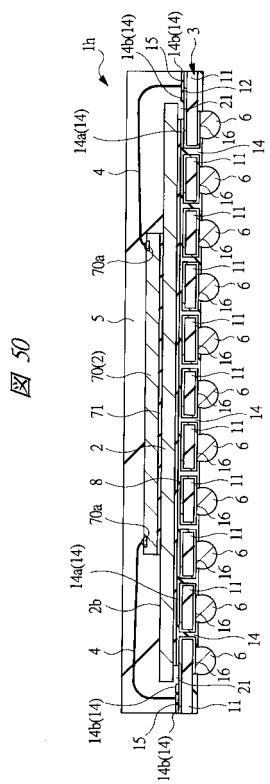

図 4 8 は、本発明の他の実施の形態である半導体装置 1 h の平面透視図（上面図）であり、図 4 9 および図 5 0 は、その断面図である。図 4 8 は、上記実施の形態 1 の図 6 に対応し、封止樹脂 5 を透視したときの半導体装置 1 h の平面透視図（上面図）が示されている。また、図 4 9 と図 5 0 とは異なる断面である。

#### 【 0 1 0 8 】

上記実施の形態 1 の半導体装置 1 では、配線基板 3 上に一つの半導体チップ 2 が搭載されていたが、本実施の形態の半導体装置 1 h では、配線基板 3 上に複数の半導体チップ 2 を積層して搭載している。ここでは 2 つの半導体チップ 2 が積層されて配線基板 3 上に搭載されている例について説明するが、これに限定されるものではなく、2 つ以上の半導体チップ 2 を積層して配線基板 3 上に搭載して半導体装置 1 h を製造することができる。30

#### 【 0 1 0 9 】

本実施の形態では、図 4 8 ~ 図 5 0 に示されるように、配線基板 3 の上面 3 a の第 1 ソルダレジスト部 1 4 a 上に接着材 8 を介して半導体チップ 2 を搭載（接合）し、更に半導体チップ 2 の表面 2 b 上に他の半導体チップ 2、すなわち半導体チップ 7 0 を接着材 7 1 を介して搭載（接合）している。すなわち、配線基板 3 の上面 3 a 上に半導体チップ 2 および半導体チップ 7 0 が積層されている。上層側の半導体チップ 7 0 の平面寸法（面積）は下層側の半導体チップ 2 の平面寸法（面積）よりも小さい。下層側の半導体チップ 2 の複数の電極 2 a は、配線基板 3 の複数の接続端子 1 5 に複数のボンディングワイヤ 4 を介して電気的に接続されている。上層側の半導体チップ 7 0 の複数の電極 7 0 a は、半導体チップ 2 の複数の電極 2 a および / または配線基板 3 の複数の接続端子 1 5 に複数のボンディングワイヤ 4 を介して電気的に接続されている。他の構成は上記実施の形態 1 とほぼ同様である。40

#### 【 0 1 1 0 】

本実施の形態においても、下層側の半導体チップ 2 を接合する第 1 ソルダレジスト部 1 4 a と第 2 ソルダレジスト部 1 4 b との間には、ソルダレジスト層 1 4 が形成されずに基材層 1 1 が露出する領域（ダム領域）1 8 が存在しているので、半導体チップ 2 を配線基板 3 上にダイボンディングしたときに、ペースト材などからなる接着材 8 が領域 1 8 を越えて第 2 ソルダレジスト部 1 4 b 上にまで広がってしまうのを防止することができる。こ50

れにより、接着材 8 が接続端子 15 上にまで広がってしまうのを防止でき、ボンディングワイヤ 4 と接続端子 15 との間の電気的接続の信頼性を向上することができる。

#### 【0111】

また、本実施の形態においても、下層側の半導体チップ 2 は、その半導体チップ 2 よりも平面寸法（面積）が小さな第 1 ソルダレジスト部 14a 上に接着材 8 を介して接合されている。このため、下層側の半導体チップ 2 を配線基板 3 の上面 3a にダイボンディングしたときに、下層側の半導体チップ 2 の裏面 2c の外周部 2d の下方には第 1 ソルダレジスト部 14a および接着材 8 が延在（存在）せず、下層側の半導体チップ 2 の裏面 2c の外周部 2d と配線基板 3 の上面 3a との間に空間 21 が形成される。このため、封止樹脂 5 を形成するときには、封止樹脂 5 を形成するための材料が下層側の半導体チップ 2 の裏面 2c の外周部 2d と配線基板 3 の上面 3a との間の空間 21 にも充填され、硬化した封止樹脂 5 が下層側の半導体チップ 2 の表面 2b、側面 2e、および裏面 2c の外周部 2d と上層側の半導体チップ 70 の表面および側面を覆うので、半導体チップ 2, 70 と封止樹脂 5 との密着性（接着強度）を高めることができ、半導体装置 1h の信頼性を向上させることができる。また、封止樹脂 5 を形成するときに、封止樹脂 5 を形成するための材料に含まれるフィラーなどが、下層側の半導体チップ 2 の裏面 2c の外周部 2d の下方の空間 21 に侵入しやすく、空間 21 を充填した封止樹脂 5 の成分比と、他の領域の封止樹脂 5 の成分比とが均一化される。これにより、硬化した封止樹脂 5 と各半導体チップ 2 との密着性（接着強度）をより向上させ、半導体装置 1h の信頼性をより向上させることができる。10 20

#### 【0112】

また、本実施の形態では、複数の半導体チップ 2 を積層したことにより、ここでは半導体チップ 2 上に他の半導体チップ 70 を積層したことにより、半導体装置の小型化（低面積化）が可能になる。

#### 【0113】

以上、本発明者によってなされた発明をその実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

#### 【0114】

また、本発明は、配線基板上に半導体チップが搭載された種々の半導体パッケージ形態の半導体装置に適用できるが、CSP（Chip Size Package）のような小形の半導体パッケージ形態の半導体装置に適用すれば、より効果が大きい。30

#### 【0115】

また、上記実施の形態 1～9 では、配線基板 3 の上面 3a のソルダレジスト層 14 の第 1 ソルダレジスト部 14a と第 2 ソルダレジスト部 14b との間に、ソルダレジスト層 14 が形成されずに基材層 11 が露出された領域（ダム領域）18 を設けていたが、この基材層 11 が露出された領域 18 の代わりにソルダレジスト層 14 の凹部（溝部）を設けることもできる。すなわち、領域 18 にもソルダレジスト層 14 を第 1 および第 2 ソルダレジスト部 14a, 14b よりも薄く残存（存在）させることもでき、このような場合も本発明に含むものとする。このように、領域 18 にもソルダレジスト層 14 を薄く残存させ、配線基板 3 の上面 3a のソルダレジスト層 14 に凹凸により第 1 ソルダレジスト部 14a（凸部）と第 2 ソルダレジスト部 14b（凸部）と、それらの間の凹部（上記領域 18 に対応する位置の凹部）とを設けた場合も、上記実施の形態 1～9 とほぼ同様の効果を得ることができる。但し、上記実施の形態 1～9 のように、第 1 ソルダレジスト部 14a と第 2 ソルダレジスト部 14b との間の領域 18 で基材層 11 を露出させた場合の方が、領域 18 にソルダレジスト層 14 を薄く残存させた場合よりも、第 1 ソルダレジスト部 14a と第 2 ソルダレジスト部 14b との間に形成される凹部（溝部）の深さをより深くすることができるので、半導体チップ 2 を配線基板 3 上にダイボンディングしたときに接着材 8 が第 2 ソルダレジスト部 14b 上や接続端子 15 上にまで広がってしまうのをより確実に防止でき、ボンディングワイヤ 4 と接続端子 15 との間の電気的接続の信頼性向上の効40 50

果は大きい。

【産業上の利用可能性】

【0116】

本発明は、配線基板上に半導体チップが搭載された半導体装置およびその製造技術に適用できる。

【図面の簡単な説明】

【0117】

【図1】本発明の一実施の形態である半導体装置の上面図である。

【図2】図1の半導体装置の下面図である。

【図3】図1の半導体装置の断面図である。

10

【図4】図1の半導体装置の要部断面図である。

【図5】図1の半導体装置の側面図である。

【図6】封止樹脂を透視したときの図1の半導体装置の平面透視図である。

【図7】封止樹脂、半導体チップおよびボンディングワイヤを透視したときの図1の半導体装置の平面透視図である。

【図8】第1の比較例の半導体装置の要部断面図である。

【図9】第2の比較例の半導体装置の要部断面図である。

【図10】第3の比較例の半導体装置の要部断面図である。

【図11】本発明の他の実施の形態の半導体装置の要部断面図である。

【図12】図11の半導体装置の平面透視図である。

20

【図13】本発明の一実施の形態である半導体装置の製造工程中の断面図である。

【図14】図13に続く半導体装置の製造工程中における断面図である。

【図15】図14に続く半導体装置の製造工程中における断面図である。

【図16】図15に続く半導体装置の製造工程中における断面図である。

【図17】図16に続く半導体装置の製造工程中における断面図である。

【図18】図17に続く半導体装置の製造工程中における断面図である。

【図19】図18に続く半導体装置の製造工程中における断面図である。

【図20】図19に続く半導体装置の製造工程中における断面図である。

【図21】配線基板の製造工程を示す平面図である。

【図22】図21に続く配線基板の製造工程中における平面図である。

30

【図23】図22に続く配線基板の製造工程中における平面図である。

【図24】本発明の一実施の形態である半導体装置の製造工程中の要部断面図である。

【図25】本発明の一実施の形態である半導体装置の製造工程中の平面図である。

【図26】ワイヤボンディング工程の説明図である。

【図27】ワイヤボンディング工程の説明図である。

【図28】本発明の一実施の形態である半導体装置の製造工程中の要部断面図である。

【図29】本発明の一実施の形態である半導体装置の他の要部断面図である。

【図30】本発明の他の実施の形態である半導体装置の要部断面図である。

【図31】ワイヤボンディング工程の説明図である。

【図32】ワイヤボンディング工程の説明図である。

40

【図33】ワイヤボンディング工程の説明図である。

【図34】本発明の他の実施の形態である半導体装置の要部断面図である。

【図35】図34の半導体装置の平面透視図である。

【図36】本発明の他の実施の形態である半導体装置の要部断面図である。

【図37】本発明の他の実施の形態である半導体装置の平面透視図である。

【図38】本発明の他の実施の形態である半導体装置の平面透視図である。

【図39】本発明の他の実施の形態である半導体装置の要部断面図である。

【図40】図39の半導体装置の平面透視図である。

【図41】図39の半導体装置の平面透視図である。

【図42】図39の半導体装置の製造に用いられる配線基板の製造工程を示す平面図であ

50

る。

- 【図43】図42に続く配線基板の製造工程における平面図である。

- 【図44】図43に続く配線基板の製造工程における平面図である。

- 【図45】本発明の他の実施の形態である半導体装置の要部断面図である。

- 【図46】本発明の他の実施の形態である半導体装置の平面透視図である。

- 【図47】図46の半導体装置の断面図である。

- 【図48】本発明の他の実施の形態である半導体装置の平面透視図である。

- 【図49】図48の半導体装置の断面図である。

- 【図50】図48の半導体装置の他の断面図である。

【符号の説明】

【0118】

|       |            |    |

|-------|------------|----|

| 1     | 半導体装置      | 10 |

| 1 a   | 半導体装置      |    |

| 1 b   | 半導体装置      |    |

| 1 c   | 半導体装置      |    |

| 1 d   | 半導体装置      |    |

| 1 e   | 半導体装置      |    |

| 1 f   | 半導体装置      |    |

| 1 g   | 半導体装置      |    |

| 1 h   | 半導体装置      | 20 |

| 2     | 半導体チップ     |    |

| 2 a   | 電極         |    |

| 2 b   | 表面         |    |

| 2 c   | 裏面         |    |

| 2 d   | 外周部        |    |

| 2 e   | 側面         |    |

| 2 f   | 端部         |    |

| 3     | 配線基板       |    |

| 3 a   | 上面         |    |

| 3 b   | 下面         | 30 |

| 4     | ポンディングワイヤ  |    |

| 5     | 封止樹脂       |    |

| 5 a   | 封止樹脂       |    |

| 6     | 半田ボール      |    |

| 8     | 接着材        |    |

| 1 1   | 基材層        |    |

| 1 1 a | 上面         |    |

| 1 1 b | 下面         |    |

| 1 2   | 導体層        |    |

| 1 4   | ソルダレジスト層   | 40 |

| 1 4 a | 第1ソルダレジスト部 |    |

| 1 4 b | 第2ソルダレジスト部 |    |

| 1 4 c | 第3ソルダレジスト部 |    |

| 1 5   | 接続端子       |    |

| 1 6   | ランド        |    |

| 1 7   | 開口部        |    |

| 1 8   | 領域         |    |

| 1 8 a | 領域         |    |

| 1 8 b | 領域         |    |

| 1 9   | 開口部        | 50 |

- 1 9 a 開口部

2 0 a 開口部

2 0 b 後退部

2 1 空間

3 1 配線基板

3 2 半導体装置領域

3 3 導体パターン

3 4 めつき配線

3 5 スタッドバンプ

3 6 レーザ 10

4 1 キャピラリ

6 1 第1の部分

6 2 第2の部分

7 0 半導体チップ

7 0 a 電極

7 1 接着材

1 0 1 半導体装置

1 0 3 配線基板

1 0 3 a 上面

1 1 4 ソルダレジスト層 20

2 0 1 半導体装置

2 0 3 配線基板

2 0 3 a 上面

2 1 4 ソルダレジスト層

2 1 4 a 第1ソルダレジスト部

2 1 4 b 第2ソルダレジスト部

2 1 8 領域

2 2 1 空間

3 0 1 半導体装置

【 図 1 】

【図2】

【 四 4 】

|             |                |

|-------------|----------------|

| 2:半導体チップ    | 5:封止樹脂         |

| 2a:電極       | 8:接着材          |

| 2c:裏面       | 14a:第1ワルダレジスト部 |

| 2d:外周部      | 14b:第2ワルダレジスト部 |

| 3:配線基板      | 19:開口部         |

| 3a:上面       |                |

| 4:ボンディングワイヤ |                |

【図3】

【 図 5 】

【圖 6】

【 図 7 】

【 四 8 】

【図9】

【図10】

【図 1 1】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

〔 18 〕

圖 18

【 20 】

【図21】

図21

【図22】

図22

【図23】

図23

【図25】

図25

【図24】

図24

【図26】

図26

【図27】

図27

【図28】

図28

【図29】

図29

【図30】

図30

【図32】

図32

【図31】

図31

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【 図 3 9 】

【図40】

【 図 4-1 】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図48】

【図49】

【図50】

---

フロントページの続き

(56)参考文献 特開2003-092374(JP,A)

特開平09-330943(JP,A)

特開平08-316360(JP,A)

特開2004-282098(JP,A)

特開2003-273287(JP,A)

特開2003-051511(JP,A)

特開2002-314003(JP,A)

特開2000-133742(JP,A)

特開2000-058699(JP,A)

特開平09-307043(JP,A)

特開2000-174168(JP,A)

特開2002-329807(JP,A)

特表平06-506319(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 23 / 12