(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4634045号

(P4634045)

(45) 発行日 平成23年2月16日(2011.2.16)

(24) 登録日 平成22年11月26日(2010.11.26)

|                          |                    |

|--------------------------|--------------------|

| (51) Int.Cl.             | F 1                |

| HO 1 L 21/3205 (2006.01) | HO 1 L 21/88 T     |

| HO 1 L 23/52 (2006.01)   | HO 1 L 21/88 J     |

| HO 1 L 21/60 (2006.01)   | HO 1 L 21/92 604 S |

| HO 1 L 23/12 (2006.01)   | HO 1 L 23/12 501 P |

請求項の数 48 (全 35 頁)

|              |                              |           |                                                   |

|--------------|------------------------------|-----------|---------------------------------------------------|

| (21) 出願番号    | 特願2004-13653 (P2004-13653)   | (73) 特許権者 | 000005223<br>富士通株式会社<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 |

| (22) 出願日     | 平成16年1月21日(2004.1.21)        | (74) 代理人  | 100090273<br>弁理士 國分 孝悦                            |

| (65) 公開番号    | 特開2005-64451 (P2005-64451A)  | (72) 発明者  | 表 孝司<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内        |

| (43) 公開日     | 平成17年3月10日(2005.3.10)        | (72) 発明者  | 水越 正孝<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内       |

| 審査請求日        | 平成19年1月22日(2007.1.22)        |           |                                                   |

| (31) 優先権主張番号 | 特願2003-284368 (P2003-284368) |           |                                                   |

| (32) 優先日     | 平成15年7月31日(2003.7.31)        |           |                                                   |

| (33) 優先権主張国  | 日本国(JP)                      |           |                                                   |

|              |                              | 審査官       | 村岡 一磨                                             |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法、貫通電極の形成方法、半導体装置、複合半導体装置、及び実装構造体

## (57) 【特許請求の範囲】

## 【請求項 1】

一方の主面に半導体素子が形成された半導体基板において、前記半導体基板の他方の主面から前記半導体素子の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の主面に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記接続部位の一部を露出させる工程と、

前記半導体基板の前記他方の主面上に、前記第1の開孔よりも大きい第2の開孔を有してなるフィルム状の第2の絶縁膜を、前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

前記第2の絶縁膜上に、前記第1及び第2の開孔を共に埋め込むように導電膜を形成する工程と、

前記導電膜の表面及び前記第2の絶縁膜の表面を連続して平坦化し、前記第1及び第2の開孔を充填して前記接続部位と接続されてなる貫通電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法。

## 【請求項 2】

一方の主面に半導体素子が形成された半導体基板において、前記半導体基板の他方の主面から前記半導体素子の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の主面に第1の絶縁膜

10

20

を形成する工程と、

前記第1の絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記接続部位の一部を露出させる工程と、

前記半導体基板の前記他方の主面上に、前記第1の開孔よりも大きい第2の開孔を有してなるフィルム状の第2の絶縁膜を、前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

少なくとも前記第1及び第2の開孔に導電材を充填して、前記接続部位と電気的に接続する導電膜を形成する工程と、

前記導電膜の表面及び前記第2の絶縁膜の表面を連続して平坦化し、前記接続部位と電気的に接続されてなる貫通電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法。

【請求項3】

前記貫通電極を形成するに際して、前記導電膜及び前記第2の絶縁膜を切削加工し、前記導電膜の表面及び前記第2の絶縁膜の表面を連続して平坦化することを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

前記第1の開孔を形成する前に、前記半導体素子上に、前記半導体基板の前記一方の正面から突出する突起電極を形成する工程を更に含むことを特徴とする請求項1～3のいずれか1項に記載の半導体装置の製造方法。

【請求項5】

前記突起電極の上部を切削加工により除去し、前記突起電極の上面を平坦な鏡面状態とすることを特徴とする請求項4に記載の半導体装置の製造方法。

【請求項6】

前記第2の絶縁膜は個々の前記半導体素子に対応した大きさのものであり、個々の前記半導体素子ごとに前記各第2の絶縁膜を貼り付けることを特徴とする請求項1～5のいずれか1項に記載の半導体装置の製造方法。

【請求項7】

前記第2の絶縁膜は個々の複数の前記半導体素子からなるブロックに対応した大きさのものであり、個々の前記ブロックごとに前記各第2の絶縁膜を貼り付けることを特徴とする請求項1～5のいずれか1項に記載の半導体装置の製造方法。

【請求項8】

一方の正面に第1の電子回路が形成された半導体基板において、前記半導体基板の他方の正面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の正面に絶縁膜を形成する工程と、

前記絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記第1の接続部位の一部を露出させる工程と、

前記第1の開孔よりも大きい第2の開孔を有し、第2の電子回路が絶縁材料内に埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出してなるフィルムを、前記半導体基板の前記他方の主面上に前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

前記フィルム上に、前記第1及び第2の開孔を共に埋め込むように導電膜を形成する工程と、

前記導電膜の表面及び前記フィルムの表面を連続して平坦化し、前記第1及び第2の開孔を充填して前記第1及び第2の接続部位と接続されてなる貫通電極を形成する工程とを含むことを特徴とする半導体装置の製造方法。

【請求項9】

一方の正面に第1の電子回路が形成された半導体基板において、前記半導体基板の他方の正面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔を形成する工程

10

20

30

40

50

と、

前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の主面に絶縁膜を形成する工程と、

前記絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記第1の接続部位の一部を露出させる工程と、

前記第1の開孔よりも大きい第2の開孔を有し、内部に第2の電子回路が埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出してなるフィルムを、前記半導体基板の前記他方の主面上に前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

少なくとも前記第1及び第2の開孔に導電材を充填して、前記第1及び第2の接続部位と電気的に接続する導電膜を形成する工程と、

前記導電膜の表面及び前記フィルムの表面を連続して平坦化し、前記第1及び第2の接続部位と電気的に接続されてなる貫通電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法。

【請求項10】

前記貫通電極を形成するに際して、前記導電膜及び前記フィルムを切削加工し、前記導電膜の表面及び前記フィルムの表面を連続して平坦化することを特徴とする請求項8又は9に記載の半導体装置の製造方法。

【請求項11】

前記第1の開孔を形成する前に、前記第1の電子回路上に、前記半導体基板の前記一方の主面から突出する突起電極を形成する工程を更に含むことを特徴とする請求項8～10のいずれか1項に記載の半導体装置の製造方法。

【請求項12】

前記突起電極の上部を切削加工により除去し、前記突起電極の上面を平坦な鏡面状態とすることを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項13】

前記第2の絶縁膜は個々の前記第1の電子回路に対応した大きさのものであり、個々の前記第1の電子回路ごとに前記各第2の絶縁膜を貼り付けることを特徴とする請求項8～12のいずれか1項に記載の半導体装置の製造方法。

【請求項14】

前記第2の絶縁膜は個々の複数の前記第1の電子回路からなるブロックに対応した大きさのものであり、個々の前記ブロックごとに前記各第2の絶縁膜を貼り付けることを特徴とする請求項8～12のいずれか1項に記載の半導体装置の製造方法。

【請求項15】

前記フィルムは、前記第2の開孔と隣接して前記第2の電子回路の第3の接続部位を露出させる第3の開孔を有しており、

前記導電膜を前記第1及び第2の開孔と共に前記第3の開孔を埋め込むように形成し、前記第3の接続部位と電気的に接続されてなる電極を前記貫通電極と共に形成することを特徴とする請求項8～14のいずれか1項に記載の半導体装置の製造方法。

【請求項16】

前記フィルムは、前記第2の電子回路が多層構造とされてなるものであることを特徴とする請求項8～15のいずれか1項に記載の半導体装置の製造方法。

【請求項17】

前記フィルムは、前記第2の開孔の内壁面がテーパ状とされ、上面の孔径が前記半導体基板に貼付される下面の孔径よりも大きいものであることを特徴とする請求項8～16のいずれか1項に記載の半導体装置の製造方法。

【請求項18】

前記フィルムは、前記第2の電子回路の前記第2の接続部位が前記第2の開孔の内壁面から上面及び側面を露出するように形成されているものであることを特徴とする請求項8～16のいずれか1項に記載の半導体装置の製造方法。

10

20

30

40

50

## 【請求項 19】

前記フィルムは、前記第2の電子回路の前記第2の接続部位が前記第2の開孔の内壁面から突出するように形成されているものであることを特徴とする請求項8～16のいずれか1項に記載の半導体装置の製造方法。

## 【請求項 20】

前記フィルムは、前記第2の電子回路の前記第2の接続部位が前記第2の開孔の内壁面を覆うように形成されているものであることを特徴とする請求項8～16のいずれか1項に記載の半導体装置の製造方法。

## 【請求項 21】

前記一方の主面が前記半導体基板の表面であり、前記他方の主面が前記半導体基板の裏面であることを特徴とする請求項1～20のいずれか1項に記載の半導体装置の製造方法。

10

## 【請求項 22】

前記導電膜を形成するに際して、メッキ法により金属を堆積させることを特徴とする請求項1～21のいずれか1項に記載の半導体装置の製造方法。

## 【請求項 23】

前記導電膜を形成するに際して、蒸着法により金属を堆積させることを特徴とする請求項1～21のいずれか1項に記載の半導体装置の製造方法。

## 【請求項 24】

前記導電膜を形成するに際して、金属ペーストを前記第1及び第2の開孔に埋め込み、前記金属ペーストを固化させることを特徴とする請求項1～21のいずれか1項に記載の半導体装置の製造方法。

20

## 【請求項 25】

前記貫通電極上にハンダバンプを形成する工程を更に含むことを特徴とする請求項1～24のいずれか1項に記載の半導体装置の製造方法。

## 【請求項 26】

一方の主面に半導体素子が形成された半導体基板と、

前記半導体基板に、当該半導体基板の他方の主面から前記半導体素子の接続部位を露出させる第1の開孔が形成され、前記第1の開孔の内壁面を覆い底面の一部から前記接続部位の一部を露出させるように前記半導体基板の前記他方の主面に形成されてなる第1の絶縁膜と、

30

前記第1の開孔よりも大きい第2の開孔を有し、前記第2の開孔が前記第1の開孔を含むように前記半導体基板の前記他方の主面上に貼付されてなる、前記第1の絶縁膜よりも厚いフィルム状の第2の絶縁膜と、

前記第1及び第2の開孔を充填して前記接続部位と接続されてなる貫通電極とを含み、

前記貫通電極の表面及び前記第2の絶縁膜の表面が連続して平坦化されてなることを特徴とする半導体装置。

## 【請求項 27】

前記半導体素子上で前記半導体基板の前記一方の主面から突出してなる突起電極を含むことを特徴とする請求項26に記載の半導体装置。

40

## 【請求項 28】

前記突起電極の上面が平坦な鏡面状態とされてなることを特徴とする請求項27に記載の半導体装置。

## 【請求項 29】

前記貫通電極上に形成されてなるバンプを含むことを特徴とする請求項26～28のいずれか1項に記載の半導体装置。

## 【請求項 30】

請求項27又は28に記載の半導体装置を少なくとも2つ含み、

着目する一組の前記半導体装置において、一方の前記半導体装置の前記貫通電極と他方

50

の前記半導体装置の前記突起電極とが接続され、積層一体化されていることを特徴とする複合半導体装置。

【請求項 3 1】

前記各半導体装置は前記貫通電極上にバンプを有しており、

着目する一組の前記半導体装置において、一方の前記半導体装置の前記バンプと他方の前記半導体装置の前記突起電極とが接続され、積層一体化されていることを特徴とする請求項 3 0 に記載の複合半導体装置。

【請求項 3 2】

一方の主面に第 1 の電子回路が形成された半導体基板と、

前記半導体基板に、当該半導体基板の他方の主面から前記第 1 の電子回路の第 1 の接続部位を露出させる第 1 の開孔が形成され、前記第 1 の開孔の内壁面を覆い底面の一部から前記第 1 の接続部位の一部を露出させるように前記半導体基板の前記他方の主面に形成されてなる絶縁膜と、

前記第 1 の開孔よりも大きい第 2 の開孔を有し、第 2 の電子回路が絶縁材料内に埋設されるとともに前記第 2 の電子回路の第 2 の接続部位が前記第 2 の開孔の内壁面から露出してなり、前記第 2 の開孔が前記第 1 の開孔を含むように前記半導体基板の前記他方の主面上に貼付されてなるフィルムと、

前記第 1 及び第 2 の開孔を充填して前記第 1 及び第 2 の接続部位と接続されてなる貫通電極と

を含み、

前記貫通電極の表面及び前記フィルムの表面が連続して平坦化されてなることを特徴とする半導体装置。

【請求項 3 3】

前記フィルムは、前記第 2 の開孔と隣接して前記第 2 の電子回路の第 3 の接続部位を露出させる第 3 の開孔を有しており、

前記第 3 の開孔を充填して前記第 3 の接続部位と電気的に接続されてなる電極を含み、

前記貫通電極の表面、前記電極の表面及び前記フィルムの表面が連続して平坦化されてなることを特徴とする請求項 3 2 に記載の半導体装置。

【請求項 3 4】

前記フィルムは、前記第 2 の開孔の内壁面がテーパ状とされ、上面の孔径が前記半導体基板に貼付される下面の孔径よりも大きいものであることを特徴とする請求項 3 2 又は 3 3 に記載の半導体装置。

【請求項 3 5】

前記フィルムは、前記第 2 の電子回路の前記第 2 の接続部位が前記第 2 の開孔の内壁面から上面及び側面を露出するように形成されているものであることを特徴とする請求項 3 2 又は 3 3 に記載の半導体装置。

【請求項 3 6】

前記フィルムは、前記第 2 の電子回路の前記第 2 の接続部位が前記第 2 の開孔の内壁面から突出するように形成されているものであることを特徴とする請求項 3 2 又は 3 3 に記載の半導体装置。

【請求項 3 7】

前記フィルムは、前記第 2 の電子回路の前記第 2 の接続部位が前記第 2 の開孔の内壁面を覆うように形成されているものであることを特徴とする請求項 3 2 又は 3 3 に記載の半導体装置。

【請求項 3 8】

前記第 1 の電子回路上で前記半導体基板の前記一方の主面から突出してなる突起電極を含むことを特徴とする請求項 3 2 ~ 3 7 のいずれか 1 項に記載の半導体装置。

【請求項 3 9】

前記突起電極の上面が平坦な鏡面状態とされてなることを特徴とする請求項 3 8 に記載の半導体装置。

10

20

30

40

50

## 【請求項 4 0】

前記貫通電極上に形成されてなるバンプを含むことを特徴とする請求項3 2 ~ 3 9のいずれか1項に記載の半導体装置。

## 【請求項 4 1】

請求項 3 8 又は 3 9 に記載の半導体装置を少なくとも 2 つ含み、

着目する一組の前記半導体装置において、一方の前記半導体装置の前記貫通電極と他方の前記半導体装置の前記突起電極とが接続され、積層一体化されていることを特徴とする複合半導体装置。

## 【請求項 4 2】

前記各半導体装置は前記貫通電極上にバンプを有しており、

10

着目する一組の前記半導体装置において、一方の前記半導体装置の前記バンプと他方の前記半導体装置の前記突起電極とが接続され、積層一体化されていることを特徴とする請求項 4 1 に記載の複合半導体装置。

## 【請求項 4 3】

一方の主面に素子が形成された基板において、前記基板の他方の主面から前記素子の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記基板の前記他方の主面に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記接続部位の一部を露出させる工程と、

20

前記基板の前記他方の主面上に、前記第1の開孔よりも大きい第2の開孔を有してなるフィルム状の第2の絶縁膜を、前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

前記第2の絶縁膜上に、前記第1及び第2の開孔を共に埋め込むように導電膜を形成する工程と、

前記導電膜の表面及び前記第2の絶縁膜の表面を連続して平坦化し、前記第1及び第2の開孔を充填して前記接続部位と接続されてなる貫通電極を形成する工程と

を含むことを特徴とする貫通電極の形成方法。

## 【請求項 4 4】

一方の主面に素子が形成された基板において、前記基板の他方の主面から前記素子の接続部位を露出させる第1の開孔を形成する工程と、

30

前記第1の開孔の内壁面を覆うように前記基板の前記他方の主面に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記接続部位の一部を露出させる工程と、

前記基板の前記他方の主面上に、前記第1の開孔よりも大きい第2の開孔を有してなるフィルム状の第2の絶縁膜を、前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

少なくとも前記第1及び第2の開孔に導電材を充填して、前記接続部位と電気的に接続する導電膜を形成する工程と、

40

前記導電膜の表面及び前記第2の絶縁膜の表面を連続して平坦化し、前記接続部位と電気的に接続されてなる貫通電極を形成する工程と

を含むことを特徴とする貫通電極の形成方法。

## 【請求項 4 5】

一方の主面に第1の電子回路が形成された基板において、前記基板の他方の主面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記基板の前記他方の主面に絶縁膜を形成する工程と、

前記絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記第1の接続部位の一部を露出させる工程と、

50

前記第1の開孔よりも大きい第2の開孔を有し、第2の電子回路が絶縁材料内に埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出してなるフィルムを、前記基板の前記他方の主面上に前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

前記フィルム上に、前記第1及び第2の開孔を共に埋め込むように導電膜を形成する工程と、

前記導電膜の表面及び前記フィルムの表面を連続して平坦化し、前記第1及び第2の開孔を充填して前記第1及び第2の接続部位と接続されてなる貫通電極を形成する工程とを含むことを特徴とする貫通電極の形成方法。

【請求項46】

10

一方の主面に第1の電子回路が形成された基板において、前記基板の他方の主面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記基板の前記他方の主面上に絶縁膜を形成する工程と、

前記絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記第1の接続部位の一部を露出させる工程と、

前記第1の開孔よりも大きい第2の開孔を有し、内部に第2の電子回路が埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出してなるフィルムを、前記基板の前記他方の主面上に前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

20

少なくとも前記第1及び第2の開孔に導電材を充填して、前記第1及び第2の接続部位と電気的に接続する導電膜を形成する工程と、

前記導電膜の表面及び前記フィルムの表面を連続して平坦化し、前記第1及び第2の接続部位と電気的に接続されてなる貫通電極を形成する工程と

を含むことを特徴とする貫通電極の形成方法。

【請求項47】

一方の主面に素子が形成された基板と、

前記基板に、当該基板の他方の主面から前記素子の接続部位を露出させる第1の開孔が形成され、前記第1の開孔の内壁面を覆い底面の一部から前記接続部位の一部を露出させるように前記基板の前記他方の主面上に形成されてなる第1の絶縁膜と、

30

前記第1の開孔よりも大きい第2の開孔を有し、前記第2の開孔が前記第1の開孔を含むように前記基板の前記他方の主面上に貼付されてなる、前記第1の絶縁膜よりも厚いフィルム状の第2の絶縁膜と、

前記第1及び第2の開孔を充填して前記接続部位と接続されてなる貫通電極とを含み、

前記貫通電極の表面及び前記第2の絶縁膜の表面が連続して平坦化されてなることを特徴とする実装構造体。

【請求項48】

一方の主面に第1の電子回路が形成された基板と、

前記基板に、当該基板の他方の主面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔が形成され、前記第1の開孔の内壁面を覆い底面の一部から前記第1の接続部位の一部を露出させるように前記基板の前記他方の主面上に形成されてなる絶縁膜と、

40

前記第1の開孔よりも大きい第2の開孔を有し、第2の電子回路が絶縁材料内に埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出してなり、前記第2の開孔が前記第1の開孔を含むように前記基板の前記他方の主面上に貼付されてなるフィルムと、

前記第1及び第2の開孔を充填して前記第1及び第2の接続部位と接続されてなる貫通電極とを含み、

前記貫通電極の表面及び前記フィルムの表面が連続して平坦化されてなることを特徴とする実装構造体。

【発明の詳細な説明】

50

**【技術分野】****【0001】**

本発明は、半導体基板を貫通する貫通電極を備えた半導体装置及びその製造方法、複数の半導体装置を積層一体化してなる複合半導体装置、更には貫通電極の形成方法、及び実装構造体に関する。

**【背景技術】****【0002】**

近時では、複数のLSIチップを積層一体化してなる複合半導体デバイスが開発されている。この複合半導体デバイスを作製するには、LSIチップにこれを貫通する接続電極を形成する必要がある。この形成法としては、半導体基板（ウェーハ）の裏面から例えばRIEによりエッチングしてLSI電極に達する開孔（スルーホール）を形成し、ウェーハ裏面及び開孔内部を同時にCVD等の手法で絶縁し、開孔底部の電極部分について選択的に絶縁膜を除去する。そして、開孔内部にTaNやTiNなどのバリアメタル層を形成した後、ウェーハ裏面にフィルム状のレジストを貼り付け、開孔上部のレジストを露光現像して除去し、バリアメタル層をシードとして、メッキ法で金属を充填する方法が知られている。

10

**【0003】**

また、LSIチップの表面からRIEあるいはレーザにより深いビア孔を形成した後、ビア孔内面を絶縁し、メッキ等により金属を充填する。そして、ウェーハ裏側からこれを研削してドライエッチングし、ビア孔先端の金属を露出させて接続電極とする方法も試みられている。

20

**【0004】**

【特許文献2】特開2003-78080号公報

【特許文献2】特開昭62-72161号公報

【特許文献3】特開平5-29483号公報

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

貫通電極を形成するに際して、上述したような従来の方法では、接続電極の導電材料を開孔に充填させた後に化学機械研磨法(CMP)による接続電極表面の鏡面加工が必要である。また、ウェーハ裏面にフィルム状のレジストを貼り付けてフォトリソグラフィーのプロセスを行うことが必須である。従ってレジストを除去した後には、ウェーハ上にはSiO<sub>2</sub>やSiN等の膜厚1μm以下の絶縁膜が露出した状態となり、ウェーハの裏側にその薄い絶縁膜を補強するために、突起状に形成された貫通電極の周囲に、新たなカバー膜を形成することが必要となる。また、メッキ法により貫通電極を形成する場合には、その中央部分が壅んだ形状に形成され、高さについて、ウェーハ全面でバラツキが発生するという問題もある。特に近年では、貫通電極を有する半導体装置として、ウェーハの表面に形成された電子回路の外部接続を貫通電極により実現するものが提案されており、これを確実に実現するためにも信頼性の高い半導体装置及び製造方法の案出が待たれる現況にある。

30

**【0006】**

本発明は、上述の諸問題に鑑みてなされたものであり、半導体基板との絶縁及び機械強度を十分に確保する貫通電極を容易且つ確実に形成し、信頼性の高い半導体装置及びその製造方法、ひいては複数の前記半導体装置が積層一体化されてなる複合半導体装置を提供することを目的とする。

**【0007】**

また本発明は、半導体基板の第1の主面（例えば表面）には第1の電子回路が設けられるとともに、第2の主面（例えば裏面）には第2の電子回路を内包するフィルムが形成されてなる半導体装置において、第1及び第2の電子回路を貫通電極により接続するに際して、半導体基板の裏面のCMP研磨工程及びフォトリソグラフィーのプロセスによる配線

40

50

形成工程等を簡略化し、半導体基板との絶縁及び機械強度を十分に確保する貫通電極を容易且つ確実に形成する信頼性の高い半導体装置及びその製造方法を提供することを目的とする。

【0008】

更に本発明は、併設された各貫通電極の高さのバラツキを容易且つ高度に解消し、しかも同時に貫通電極の表面をこれを埋め込む絶縁膜の表面と連続して平坦化することにより、貫通電極を有する半導体装置を積層一体化する際の低ストレス化が可能となり、半導体装置の更なる耐性を確実に確保することを目的とする。

【課題を解決するための手段】

【0009】

本発明の半導体装置の製造方法は、一方の主面に半導体素子が形成された半導体基板において、前記半導体基板の他方の主面から前記半導体素子の接続部位を露出させる第1の開孔を形成する工程と、前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の主面に第1の絶縁膜を形成する工程と、前記第1の絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記接続部位の一部を露出させる工程と、前記半導体基板の前記他方の主面上に、前記第1の開孔よりも大きい第2の開孔を有してなるフィルム状の第2の絶縁膜を、前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、前記第2の絶縁膜上に、前記第1及び第2の開孔を共に埋め込むように導電膜を形成する工程と、前記導電膜の一部及び前記第2の絶縁膜の一部を除去し、前記第1及び第2の開孔を充填して前記接続部位と接続されてなる貫通電極を形成する工程とを含む。

【0010】

この場合、前記貫通電極を形成するに際して、前記導電膜及び前記第2の絶縁膜を切削加工し、前記導電膜の表面及び前記第2の絶縁膜の表面を連続して平坦化することが好適である。

【0011】

本発明の半導体装置の製造方法は、一方の主面に第1の電子回路が形成された半導体基板において、前記半導体基板の他方の主面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔を形成する工程と、前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の主面に絶縁膜を形成する工程と、前記絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記第1の接続部位の一部を露出させる工程と、前記第1の開孔よりも大きい第2の開孔を有し、内部に第2の電子回路が埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出してなるフィルムを、前記半導体基板の前記他方の主面上に前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、少なくとも前記第1及び第2の開孔に導電材を充填して、前記第1及び第2の接続部位と電気的に接続する導電膜を形成する工程と、前記導電膜の一部及び前記フィルムの一部を除去し、前記第1及び第2の接続部位と電気的に接続されてなる貫通電極を形成する工程とを含む。

【0012】

この場合、前記フィルムは、前記第2の開孔と隣接して前記第2の電子回路の第3の接続部位を露出させる第3の開孔を有しており、前記導電膜を前記第1及び第2の開孔と共に前記第3の開孔を埋め込むように形成し、前記第3の接続部位と電気的に接続されてなる電極を前記貫通電極と共に形成することが好適である。

【0013】

この場合、前記貫通電極を形成するに際して、前記導電膜及び前記フィルムを切削加工し、前記導電膜の表面及び前記フィルムの表面を連続して平坦化することが好適である。

【0014】

本発明の半導体装置は、一方の主面に半導体素子が形成された半導体基板と、前記半導体基板に、当該半導体基板の他方の主面から前記半導体素子の接続部位を露出させる第1の開孔が形成され、前記第1の開孔の内壁面を覆い底面の一部から前記接続部位の一部を露出させるように前記半導体基板の前記他方の主面上に形成されてなる第1の絶縁膜と、前

記第1の開孔よりも大きい第2の開孔を有し、前記第2の開孔が前記第1の開孔を含むように前記半導体基板の前記他方の主面上に塗付されてなる、前記第1の絶縁膜よりも厚いフィルム状の第2の絶縁膜と、前記第1及び第2の開孔を充填して前記接続部位と接続されてなる貫通電極とを含み、前記貫通電極の表面及び前記第2の絶縁膜が連続して平坦化されてなるものである。

#### 【0015】

本発明の半導体装置は、一方の主面に第1の電子回路が形成された半導体基板と、前記半導体基板に、当該半導体基板の他方の主面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔が形成され、前記第1の開孔の内壁面を覆い底面の一部から前記第1の接続部位の一部を露出させるように前記半導体基板の前記他方の主面に形成されてなる絶縁膜と、前記第1の開孔よりも大きい第2の開孔を有し、第2の電子回路が絶縁材料内に埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出してなり、前記第2の開孔が前記第1の開孔を含むように前記半導体基板の前記他方の主面上に貼付されてなるフィルムと、前記第1及び第2の開孔を充填して前記第1及び第2の接続部位と接続されてなる貫通電極とを含み、前記貫通電極の表面及び前記フィルムの表面が連続して平坦化されてなるものである。

#### 【0016】

この場合、前記フィルムは、前記第2の開孔と隣接して前記第2の電子回路の第3の接続部位を露出させる第3の開孔を有しており、前記第3の開孔を充填して前記第3の接続部位と電気的に接続されてなる電極を含み、前記貫通電極の表面、前記電極の表面及び前記フィルムの表面が連続して平坦化されてなるものであることが好適である。

#### 【0017】

本発明の複合半導体装置は、前記半導体装置を少なくとも2つ含み、着目する一組の前記半導体装置において、一方の前記半導体装置の前記貫通電極と他方の前記半導体装置の突起電極とが接続され、積層一体化されている。

#### 【発明の効果】

#### 【0018】

本発明によれば、半導体基板との絶縁及び機械強度を十分に確保する貫通電極を容易且つ確実に形成し、信頼性の高い半導体装置及びその製造方法、ひいては複数の前記半導体装置が積層一体化されてなる複合半導体装置が実現する。

#### 【0019】

また本発明によれば、半導体基板の第1の主面（例えば表面）には第1の電子回路が設けられるとともに、第2の主面（例えば裏面）には第2の電子回路を内包するフィルムが形成されてなる半導体装置において、第1及び第2の電子回路を貫通電極により接続するに際して、半導体基板の裏面のC M P研磨工程及びフォトリソグラフィーのプロセスによる配線形成工程等を簡略化し、半導体基板との絶縁及び機械強度を十分に確保する貫通電極を容易且つ確実に形成する信頼性の高い半導体装置が実現する。

#### 【0020】

更に本発明によれば、併設された各貫通電極の高さのバラツキを容易且つ高度に解消し、しかも同時に貫通電極の表面をこれを埋め込む絶縁膜の表面と連続して平坦化することにより、貫通電極を有する半導体装置を積層一体化する際の低ストレス化が可能となり、半導体装置の更なる耐性を確実に確保することができる。

#### 【発明を実施するための最良の形態】

#### 【0021】

- 本発明の基本骨子 -

本発明者は、ウェーハに貫通電極を形成するに際して、これに十分な絶縁性及び機械的強度を確保すべく、ウェーハ上で平坦となるように貫通電極を絶縁膜内に充填形成することに想到した。

#### 【0022】

この場合、ウェーハの裏面から半導体素子の接続部位まで形成された第1の開孔の内壁

10

20

30

40

50

を含むウェーハ表面との絶縁を確保し、第1の開孔の底部のみで接続部位との接続を得るため、貫通電極を形成する前に当該表面に第1の絶縁膜（接続部位のみで開孔される）を形成する必要がある。この第1の絶縁膜は第1の開孔の内壁を覆うことから、後ほど、孔底の第1の絶縁膜のみ選択的に除去するため、適度に薄く（1 μm以下）形成する必要がある。そのため、貫通電極の埋め込み時における機械的強度の確保及び半導体装置の裏面の十分な絶縁の確保が困難となる。

【0023】

そこで本発明では、貫通電極の機械的衝撃に対する耐性及び十分な絶縁を確保するため、第2の絶縁膜を形成する。この第2の絶縁膜は、第1の開孔よりも大きい第2の開孔を有し、これが第1の開孔の形成位置に整合するように形成されてなる絶縁フィルムであり、この第2の絶縁膜を第2の開孔が第1の開孔を含むように半導体基板の裏面上に貼付する。この状態で、メッキ法や蒸着法、または金属ペーストを用いた手法により第1及び第2の開孔を埋め込むように導電膜を形成する。

【0024】

そして、導電膜及び第1の絶縁膜、第2の絶縁膜を機械加工、より好適にはバイト等の加工器具を用いて切削加工し、導電膜の表面及び第2の絶縁膜の表面を連続して平坦化することにより、第1の開孔内では第1の絶縁膜、ウェーハの裏面上で第1の絶縁膜と共に周囲を厚い第2の絶縁膜で覆われ、第1及び第2の開孔を充填してなる機械的衝撃に対して強い貫通電極が形成される。ここで特に、切削加工法を用いることにより、ウェーハ上で高速且つ精緻な平坦化・鏡面処理が可能となり、複数の貫通電極を高さのバラツキが皆無な状態に容易且つ確実に形成することができる。

【0025】

本発明は、基板の第1の主面（例えば表面）には第1の電子回路が設けられるとともに、第2の主面（例えば裏面）には第2の電子回路を内包するフィルムが形成されてなる半導体装置に適用される。このフィルムは、第1の開孔よりも大きい第2の開孔を有し、第2の電子回路の第2の接続部位が第2の開孔の内壁面から露出する構成のものであり、上記と同様にこのフィルムの第2の開孔が第1の開孔を含むように半導体基板の裏面上に貼付する。この状態で、メッキ法や蒸着法、または金属ペーストを用いた手法により第1及び第2の開孔を埋め込むように導電膜を形成する。

【0026】

そして、導電膜及び第1の絶縁膜、フィルムを機械加工、より好適にはバイト等の加工器具を用いて切削加工し、導電膜の表面及びフィルムの表面を連続して平坦化することにより、第1の開孔内では第1の絶縁膜、ウェーハの裏面上で第1の絶縁膜と共に周囲を厚い第2の絶縁膜で覆われ、第1及び第2の開孔を充填して第1の電子回路の第1の接続部位及び第2の電子回路の第2の接続部位と電気的に接続されてなる機械的衝撃に対して強い貫通電極が形成される。ここで特に、切削加工法を用いることにより、ウェーハ上で高速且つ精緻な平坦化・鏡面処理が可能となり、C M Pによる鏡面処理及び貫通電極と第2の電子回路との接続を図るためのフォトリソグラフィーによる配線形成工程を不要として、複数の貫通電極を高さのバラツキが皆無な状態に容易且つ確実に形成することができる。更にこの場合、第1の電子回路の形成と第2の電子回路の形成とを個別に行うことができるため、並列作業が可能となって製造時間が短縮して歩留まりが向上し、回路の組み合わせのバリエーションが豊富になる。

【0027】

- 本発明の具体的な諸実施形態 -

（第1の実施形態）

本実施形態では、貫通電極を有する半導体装置の具体的な一例についてその製造方法と共に説明する。

【0028】

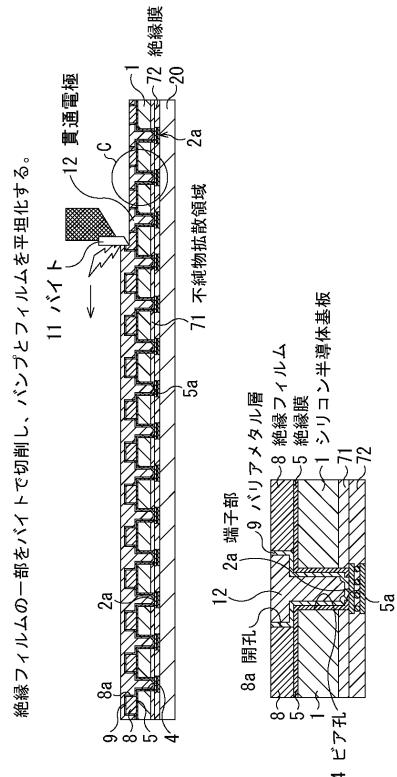

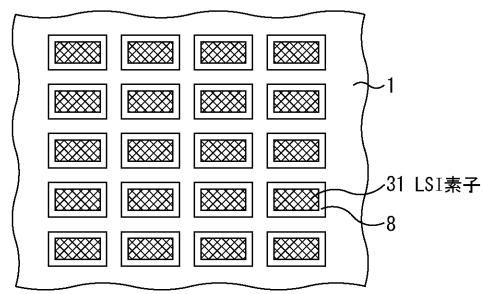

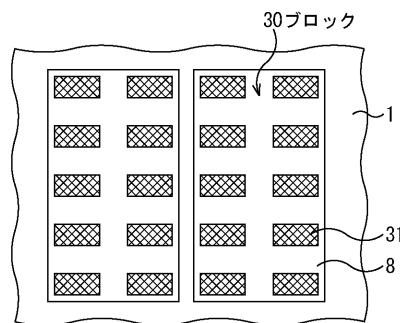

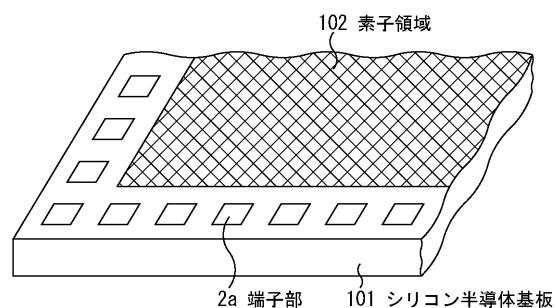

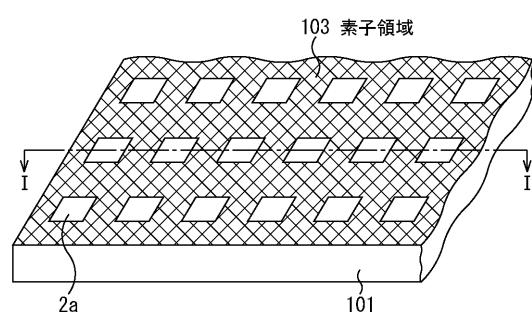

本実施形態の半導体装置としては、図8及び図9に示すような形態のものがある。図8の半導体装置は、シリコン半導体基板101において、複数（多数）の半導体素子（MOS

10

20

30

40

50

Sトランジスタ等)が形成されてなる素子領域102の周囲を取り囲むように端子部2aが形成され、各半導体素子と端子部2aとが電気的に接続されてなるものである。他方、図9の半導体装置は、シリコン半導体基板101において、複数の端子部2aがマトリクス状に形成され、各端子部2aの間に複数(多数)の半導体素子が形成されてなるものである。即ち図9の場合、端子部2aの間の領域が素子領域103となる。本発明は、図8及び図9の半導体装置の双方に適用可能であるが、以下の説明では便宜上、図9に示す形態の半導体装置を例示し、例えば図9の一点鎖線I-Iに沿った概略断面の様子を図1以降で示す。

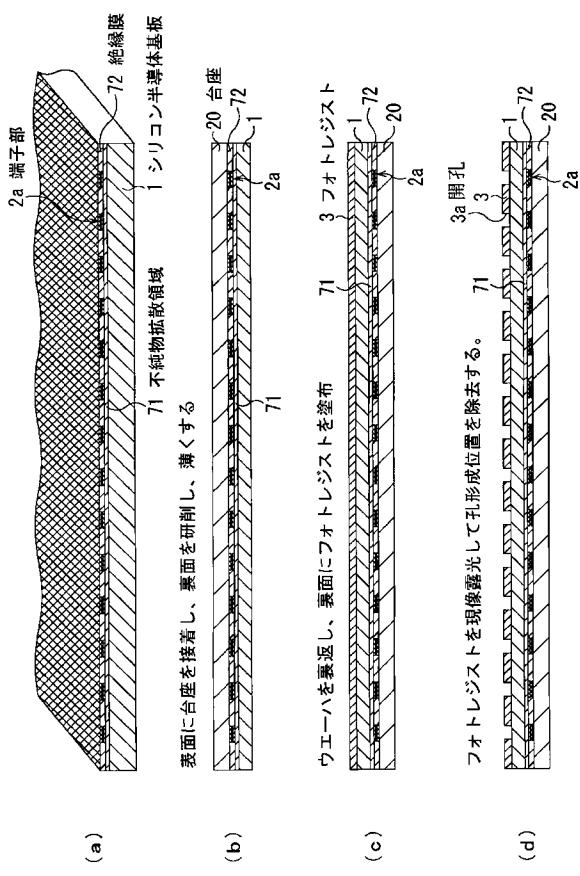

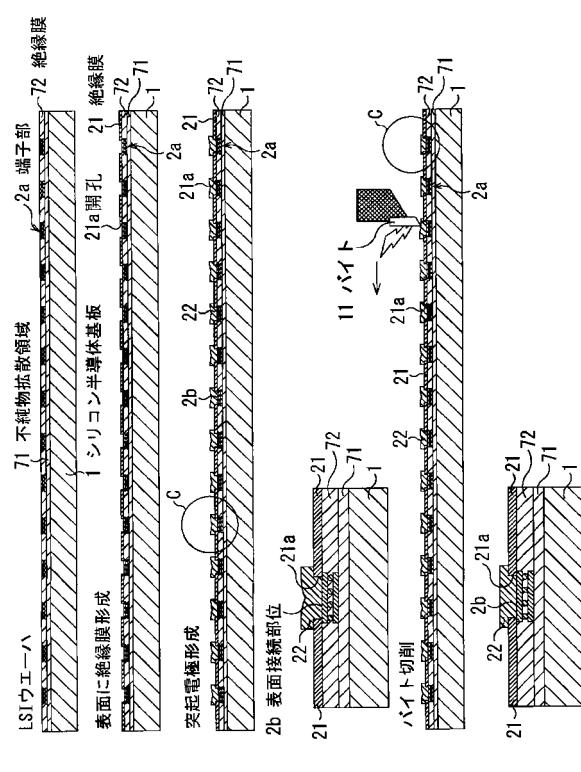

#### 【0029】

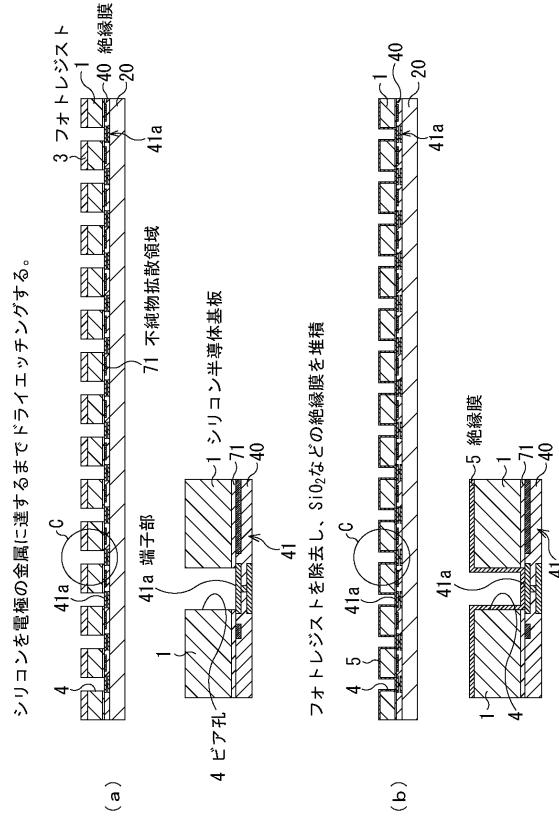

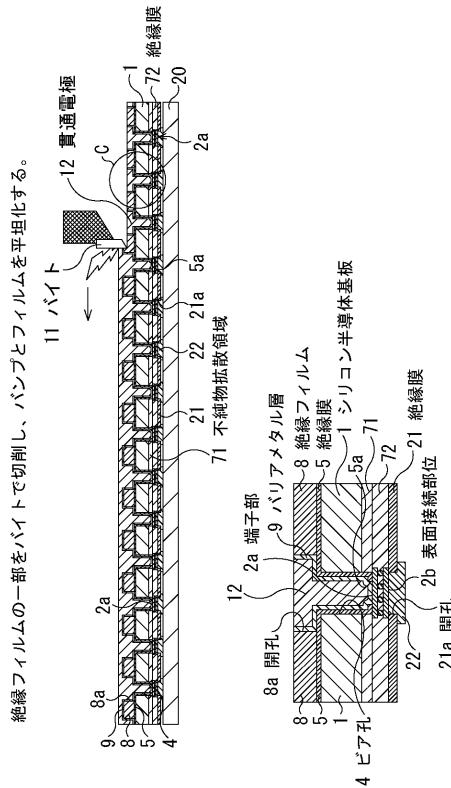

図1～図5は、第1の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。なお、図2～図5の各図では、前段の図において円Cで囲まれた部分(1つの端子部2aの周辺部に相当する。)を拡大した様子を後段に示す。

10

#### 【0030】

先ず、図1(a)に示すように、シリコン半導体基板1を用意する。そして、基板表面に各半導体素子の不純物拡散層が形成されてなる不純物拡散領域71を、不純物拡散領域71上に例えば無機物による絶縁膜72内に埋設され、表面が露出してなる端子部2aをそれぞれ形成する。なお図示の例では、隣接する端子部2a間の領域が図9の素子領域103となる。素子領域103は、MOSトランジスタ等の半導体素子、及びキャパシタやインダクタ等の受動素子などのLSI素子が形成されてなる領域であり、端子部2aは2層の導体パターンをビアで接続してなる。この場合、素子領域103は、各々の隣接する端子部2a間の領域を総括するものである。

20

#### 【0031】

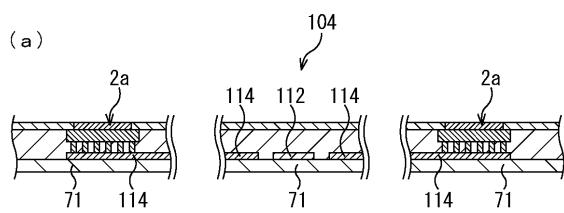

ここで、図1(a)では便宜上、各半導体素子の図示を省略している。より正確には、図10(a)に示すように、素子領域103に複数(多数)の半導体素子、ここではMOSトランジスタ104が形成されている。各MOSトランジスタ104は、図10(b)に示すように、素子領域103の表面上にゲート絶縁膜111を介してゲート電極112がパターン形成され、このゲート電極112の両側における不純物拡散領域71に不純物が導入されてソース/ドレインとなる一対の不純物拡散層113が形成されて構成される。そして、素子領域103の表面上で各不純物拡散層113と接続されるように配線114がパターン形成されており、これら配線114が端子部2aの一部を構成する。なお、不純物拡散領域71は、多数のMOSトランジスタの多数の不純物拡散層が形成されてなる領域であり、実際には不純物拡散層の存する箇所と存しない箇所とがあるが、図示の便宜上、一括して不純物拡散領域として表現した領域である。

30

#### 【0032】

MOSトランジスタ104は、隣接する端子部2a間の一の領域のみでも極めて多数形成されることから、図1(a)及び以下の各図では便宜上、MOSトランジスタ104の図示を省略する。

#### 【0033】

続いて、図1(b)に示すように、シリコン半導体基板1の表面を石英やガラスの台座20にUVテープ等により貼り付け、シリコン半導体基板1の裏面を研削及びエッティングし、シリコン半導体基板1を50μm～200μm程度の厚みに調節する。ここで、初期のシリコン半導体基板1の厚みが一様でない場合、または一様でないことに加えてうねりを伴う場合のような場合には、支持面が平坦とされた基板支持台(不図示)を用意し、この支持面に吸着、例えば真空吸着によりシリコン半導体基板1の表面を吸着させてシリコン半導体基板1を基板支持台に固定する。このとき、シリコン半導体基板1の表面は支持面への吸着により強制的に平坦とされており、これにより当該表面が裏面の平坦化の基準面となる。このように、シリコン半導体基板1の表面を裏面平坦化の基準面として裏面を機械研削し、裏面の凸部を研削除去して平坦化処理し、厚み調節を行うようにしても良い。

40

#### 【0034】

続いて、図1(c)に示すように、シリコン半導体基板1の裏面上にフォトレジスト3

50

を塗付する。

【0035】

続いて、図1(d)に示すように、フォトレジスト3をフォトリソグラフィーにより加工し、各端子部2a上に相当する部分に開孔3aを形成する。

【0036】

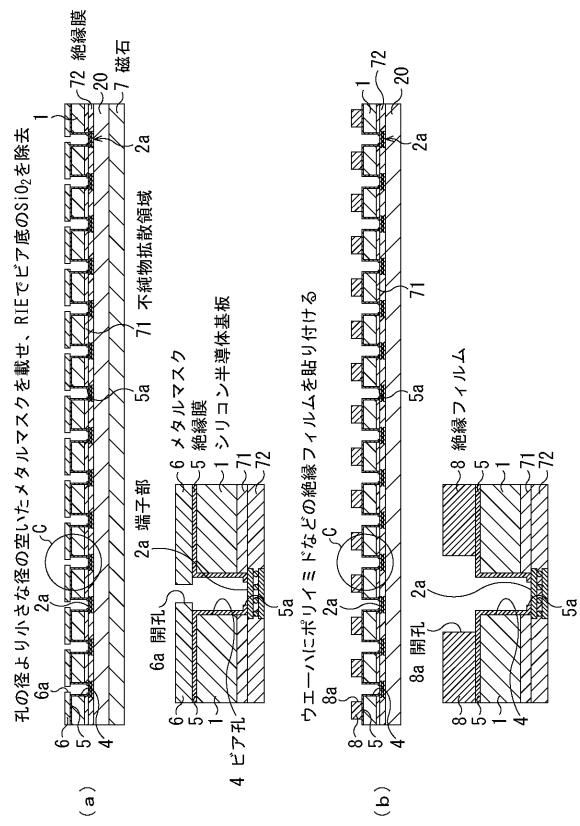

続いて、図2(a)に示すように、フォトレジスト3をマスクとしてシリコン半導体基板1を裏面からエッティング加工する。例えば、フッ素系あるいは塩素系のガスを用いたドライエッティングにより加工し、各端子部2aの表面の一部を露出させるピア孔4を形成する。

【0037】

続いて、フォトレジスト3を灰化処理等により除去する。なお、この灰化処理等の工程では、例えばフォトレジスト3をアルカリ溶液に曝した後、酸素プラズマを照射して、残渣をアッシング(灰化処理)することにより、フォトレジスト3を除去する。その後、図2(b)に示すように、ピア孔4の内壁面を覆うようにシリコン半導体基板1の裏面上にCVD法等によりSiO<sub>2</sub>やSiN等からなる絶縁膜5を膜厚1μm程度に形成する。

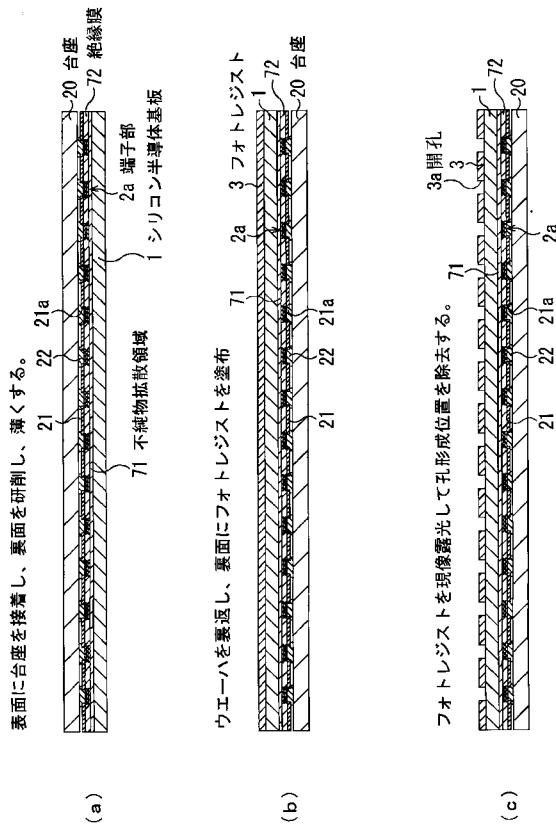

【0038】

続いて、図3(a)に示すように、絶縁膜5上にメタルマスク6を載置する。このメタルマスク6は、ピア孔4に整合した位置にピア孔4よりも径の小さい開孔6aが形成されており、ピア孔4に開孔6aが含まれる(即ち、開孔6aの外周がピア孔4の外周の内側に位置する)ようにシリコン半導体基板1の裏面上で位置合わせしてメタルマスク6を絶縁膜5上に重ね、台座20の下部に設けた磁石7の磁力によりメタルマスク6の位置を固定する。

【0039】

そして、メタルマスク6を用いて絶縁膜5をドライエッティングする。このとき、絶縁膜5のピア孔4の底部上に位置する開孔6aに相当する部分5aがエッティング除去され、端子部2aの表面の一部が露出する。

【0040】

続いて、メタルマスク6を除去した後、図3(b)に示すように、絶縁膜5上にこれよりも厚い切削可能な有機絶縁材料、ここでは膜厚30μm程度のポリイミド等からなる絶縁フィルム8を貼り付ける。この絶縁フィルム8は、ピア孔4に整合した位置にピア孔4よりも径の大きい開孔8aが形成されており、開孔8aにピア孔4が含まれるようにシリコン半導体基板1の裏面上で位置合わせして絶縁フィルム8を例えれば糊を介して貼り付ける。絶縁フィルム8及びこの糊の耐熱温度は、後述する貫通電極の形成プロセス時における最大温度を超える値である。

【0041】

ここで、具体的な絶縁フィルム8の貼り付け方法としては、図6に示すように、絶縁フィルム8を個々のLSI素子31に対応したサイズのものとして、個々のLSI素子31ごとに絶縁フィルム8を位置合わせして貼り付ける方法や、図7に示すように、絶縁フィルム8を複数のLSI素子31のブロック30に対応したサイズのものとして、ブロック30ごとに絶縁フィルム8を位置合わせして貼り付ける方法等が好適である。なお本実施形態では、主に図7の場合を例示している。

【0042】

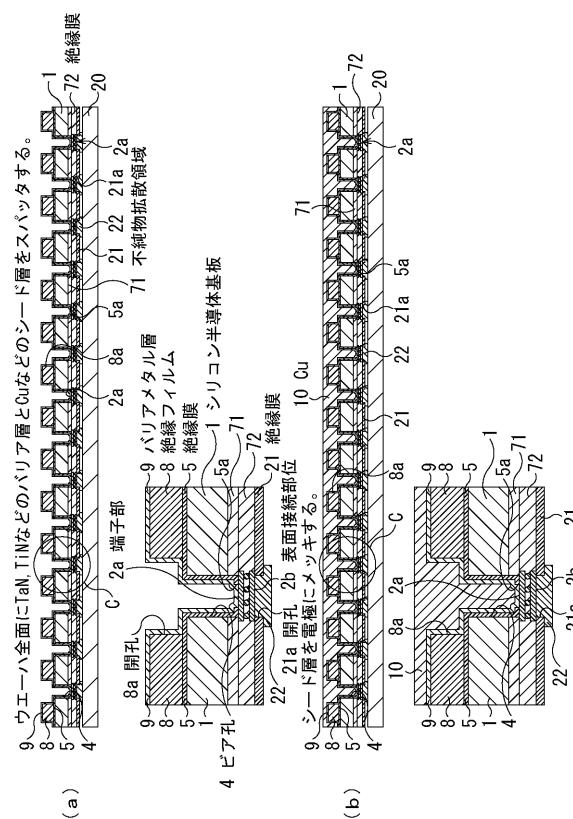

続いて、図4(a)に示すように、ピア孔4及び開孔8aの内壁面を覆うように絶縁フィルム8上にTaNやTiN等からなるバリアメタル層9をCVD法又はスパッタ法等により形成した後、導電材、ここではCuからなるメッキシード層(不図示)をCVD法又はスパッタ法等により形成する。

【0043】

続いて、図4(b)に示すように、メッキ法によりピア孔4及び開孔8aを埋め込むようにバリアメタル層9上に導電材、ここではCu10を堆積する。なお導電材として、例えばCuの替わりにAu, Ag, Ni, Sn、またはCuとこれらとを適宜の割合で使用

10

20

30

40

50

した合金等を用いても良い。

【0044】

また、導電材を堆積させる手法としては、メッキ法の替わりに蒸着法や金属ペースト法を用いてもよい。金属ペースト法は、金属ペーストを開孔8aの絶縁フィルム8表面(近傍)まで充填して固化させる方法である。

【0045】

そして、図5に示すように、Cu10及び絶縁フィルム8にダイアモンド等からなる硬質のバイト11を用いた切削加工を施し、Cu10の絶縁フィルム8上の部分及び絶縁フィルム8の上層部分を除去する。これにより、Cu10の表面及び絶縁フィルム8の表面が連続して平坦とされ、ピア孔4及び開孔8aをCuで充填し、高さが揃えられてなる各貫通電極12が形成される。貫通電極12は、シリコン半導体基板1を裏面から貫通し、ピア孔4の底部で端子部2aを介してLSI素子と電気的に接続されてなるものである。

【0046】

このように、本実施形態によれば、シリコン半導体基板1との絶縁及び機械強度を十分に確保する貫通電極12を容易且つ確実に形成し、信頼性の高い半導体装置を実現することが可能となる。更に、併設された各貫通電極12の高さのバラツキを容易且つ高度に解消し、しかも同時に貫通電極12の表面を貫通電極12を埋め込む絶縁フィルム8の表面と連続して平坦化することにより、貫通電極12の機械的衝撃に対する更なる耐性を確実に確保することが可能となる。

【0047】

(第2の実施形態)

本実施形態では、基板表面に電子回路を内包するフィルムが設けられ、この電子回路と接続される貫通電極を有する半導体装置の具体的な一例についてその製造方法と共に説明する。

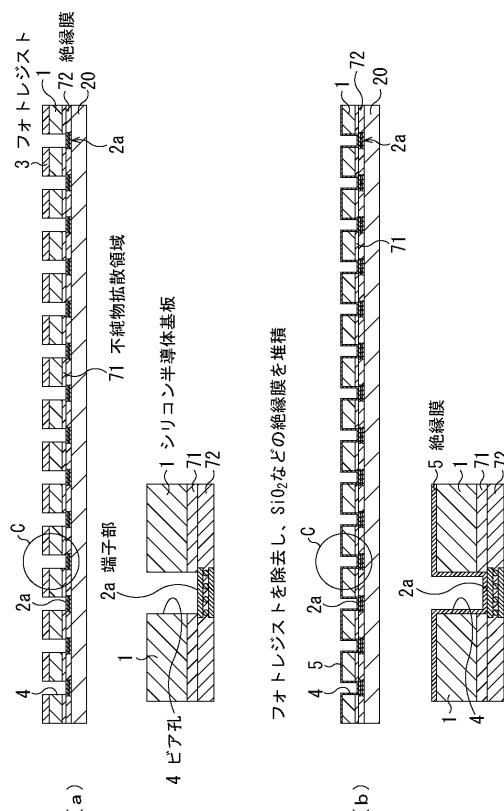

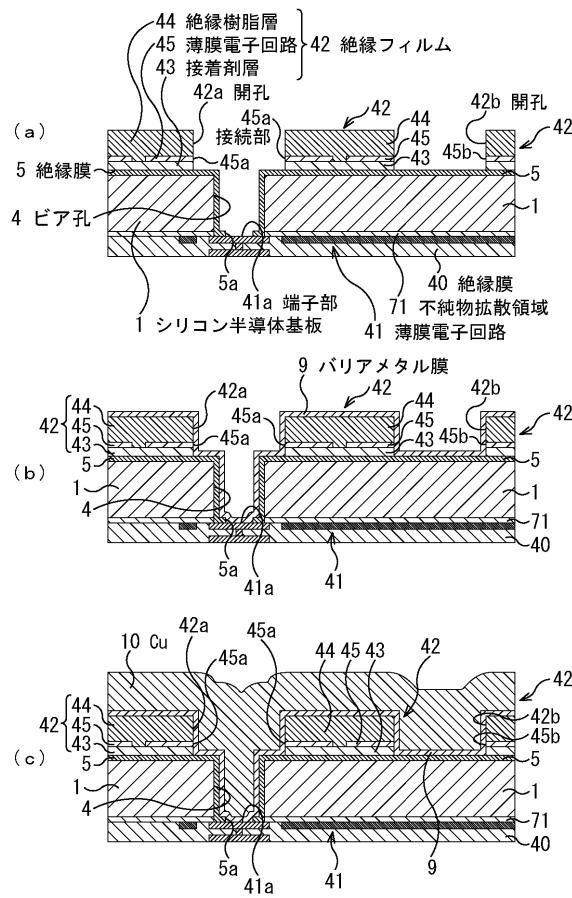

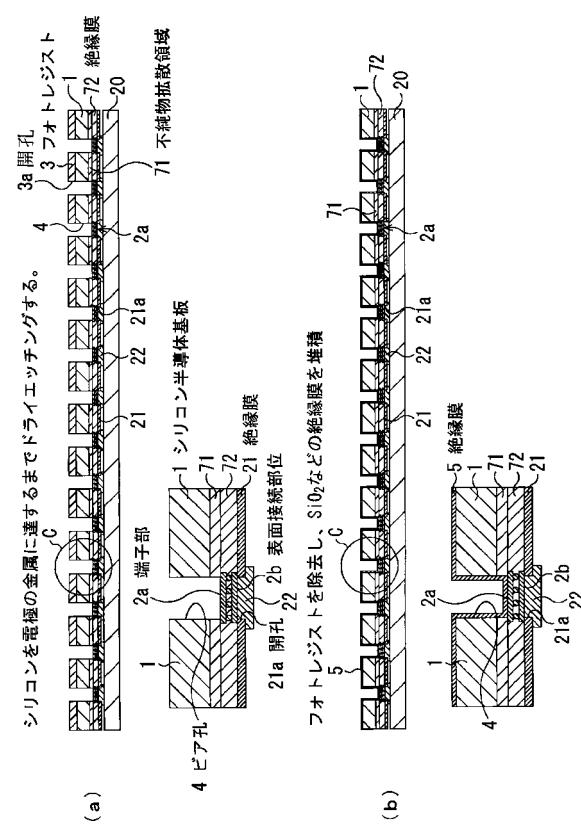

【0048】

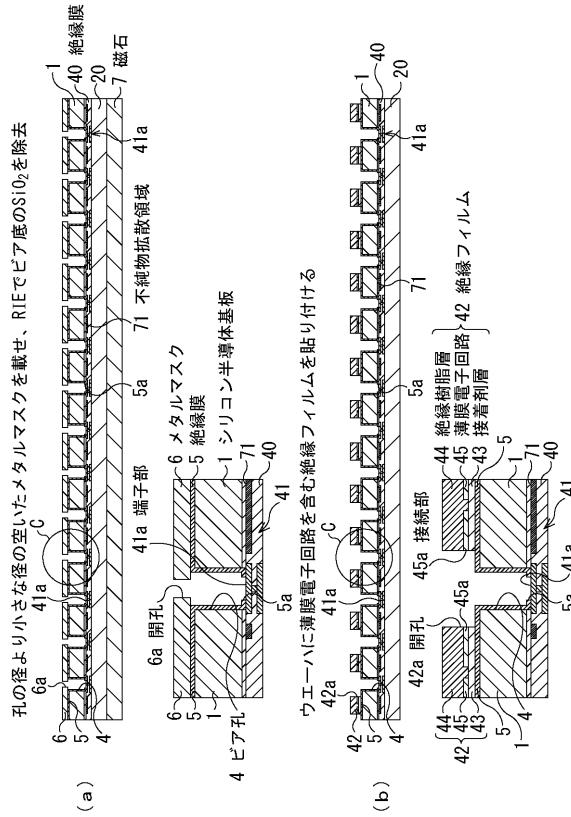

図11～図16は、第2の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。なお、図11、図13～図16の各図では、前段の図において円Cで囲まれた部分(1つの端子部41aの周辺部に相当する。)を拡大した様子を後段に示す。

【0049】

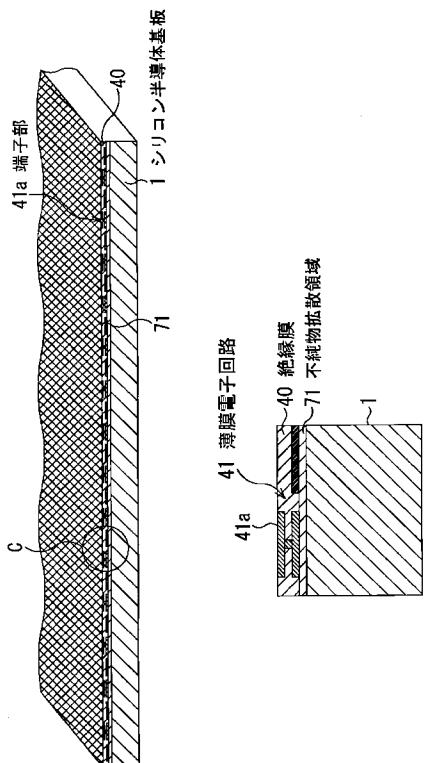

先ず、図11に示すように、厚み100μm程度のシリコン半導体基板1を用意する。そして、基板表面に各半導体素子の不純物拡散層が形成されてなる不純物拡散領域71が設けられ、不純物拡散領域71上に絶縁膜40内に複数のLSI素子等が埋設されてなる薄膜電子回路41を形成する。薄膜電子回路41には端子部41aが形成されており、端子部41aは2層の導体パターンをピアで接続してなる。なお、図11、図13～図16の各図における前段の図では、図示の便宜上、絶縁膜40の記載を省略している。

【0050】

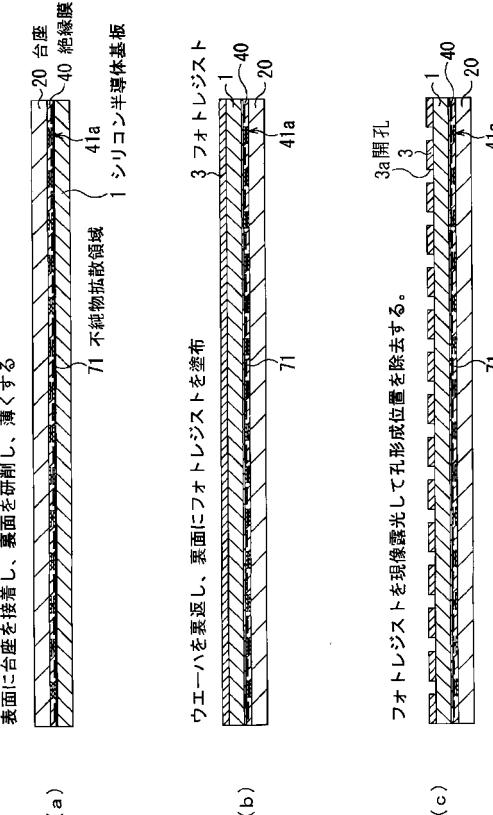

続いて、図12(a)に示すように、シリコン半導体基板1の表面を石英やガラスの台座20にUVテープ等により貼り付け、シリコン半導体基板1の裏面を研削及びエッチングし、シリコン半導体基板1を50μm～200μm程度の厚みに調節する。ここで、初期のシリコン半導体基板1の厚みが一様でない場合、または一様でないことに加えてうねりを伴う場合のような場合には、支持面が平坦とされた基板支持台(不図示)を用意し、この支持面に吸着、例えば真空吸着によりシリコン半導体基板1の表面を吸着させてシリコン半導体基板1を基板支持台に固定する。このとき、シリコン半導体基板1の表面は支持面への吸着により強制的に平坦とされており、これにより当該表面が裏面の平坦化の基準面となる。このように、シリコン半導体基板1の表面を裏面平坦化の基準面として裏面を機械研削し、裏面の凸部を研削除去して平坦化処理し、厚み調節を行うようにしても良い。

【0051】

続いて、図12(b)に示すように、シリコン半導体基板1の裏面上にフォトレジスト3を塗付する。

10

20

30

40

50

## 【0052】

続いて、図12(c)に示すように、フォトレジスト3をフォトリソグラフィーにより加工し、各端子部41a上に相当する部分に開孔3aを形成する。

## 【0053】

続いて、図13(a)に示すように、フォトレジスト3をマスクとしてシリコン半導体基板1及び絶縁膜40を裏面からエッティング加工する。例えば、ICP装置により、C<sub>4</sub>F<sub>8</sub>ガス及びSF<sub>6</sub>ガスを交互に用いた10分間のドライエッティングにより加工し、各端子部41aの表面の一部を露出させる直径50μm程度、深さ100μm程度のビア孔4を形成する。

## 【0054】

続いて、フォトレジスト3を灰化処理等により除去する。なお、この灰化処理等の工程では、例えばフォトレジスト3をアルカリ溶液に曝した後、酸素プラズマを照射して、残渣をアッティング(灰化処理)することにより、フォトレジスト3を除去する。その後、図13(b)に示すように、ビア孔4の内壁面を覆うようにシリコン半導体基板1の裏面上にCVD法等によりSiO<sub>2</sub>やSiN等からなる絶縁膜5を膜厚200nm程度に形成する。

10

## 【0055】

続いて、図14(a)に示すように、絶縁膜5上にメタルマスク6を載置する。このメタルマスク6は、ビア孔4に整合した位置にビア孔4よりも径の小さい開孔6aが形成されており、ビア孔4に開孔6aが含まれる(即ち、開孔6aの外周がビア孔4の外周の内側に位置する)ようにシリコン半導体基板1の裏面上で位置合わせしてメタルマスク6を絶縁膜5上に重ね、台座20の下部に設けた磁石7の磁力によりメタルマスク6の位置を固定する。

20

## 【0056】

そして、メタルマスク6を用いて絶縁膜5をドライエッティング、ここではICP装置により、C<sub>4</sub>F<sub>8</sub>ガス及びSF<sub>6</sub>ガスの混合ガスを用いた5分間のドライエッティングを行う。このとき、絶縁膜5のビア孔4の底部上に位置する開孔6aに相当する部分5aがエッティング除去され、端子部41aの表面の一部が露出する。

## 【0057】

続いて、メタルマスク6を除去した後、図14(b)に示すように、絶縁膜5上にこれよりも厚い絶縁フィルム42を貼り付ける。この絶縁フィルム42は、下層にエポキシ樹脂等からなる接着剤層43が設けられ、上層に切削可能な有機絶縁材料、ここではポリイミド等からなる絶縁樹脂層44が設けられてなる。絶縁層44の内部にはキャパシタやインダクタ、配線層等の薄膜電子回路45が内包されている。ここでは、薄膜電子回路45を例えばCu配線とし、接着剤層43、薄膜電子回路45、絶縁樹脂層44の厚みがそれぞれ10nm、5nm、20nm程度とされている。この絶縁フィルム42は、ビア孔4に整合した位置にビア孔4よりも径の大きい開孔42aが形成され、開孔42aの内壁面から薄膜電子回路45の接続部45aが露出しており、開孔42aにビア孔4が含まれるようシリコン半導体基板1の裏面上で位置合わせして絶縁フィルム42を接着剤層43によりシリコン半導体基板1の裏面に貼り付ける(170℃で1時間のペーク処理)。絶縁フィルム42の耐熱温度は、後述する貫通電極の形成プロセス時における最大温度を超える値である。

30

40

## 【0058】

ここで、具体的な絶縁フィルム8の貼り付け方法としては、第1の実施形態で説明した図6と同様に、絶縁フィルム42を薄膜電子回路45の所定のLSI素子に対応したサイズのものとして、所定のLSI素子ごとに絶縁フィルム42を位置合わせして貼り付ける方法や、図7と同様に、絶縁フィルム42を複数のLSI素子のブロック30に対応したサイズのものとして、ブロック30ごとに絶縁フィルム42を位置合わせして貼り付ける方法等が好適である。なお本実施形態では、主に図7の場合を例示している。

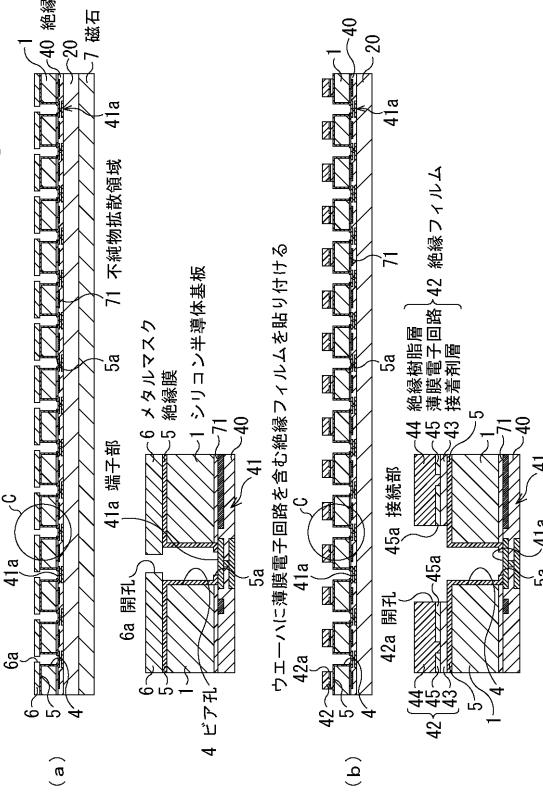

## 【0059】

50

続いて、図15(a)に示すように、ピア孔4及び開孔42aの内壁面を覆うように絶縁フィルム42上にTaNやTiN等からなるバリアメタル層9をCVD法又はスパッタ法等により形成した後、導電材、ここではCuからなるメッキシード層(不図示)をCVD法又はスパッタ法等により形成する。メッキシード層としては、Cr/Cuで膜厚を100nm/20nm程度とする。

#### 【0060】

続いて、図15(b)に示すように、メッキ法によりピア孔4及び開孔42aを埋め込むようにバリアメタル層9上に導電材、ここではCu10を堆積する。なお導電材として、例えばCuの替わりにAu, Ag, Ni, Sn、またはCuとこれらとを適宜の割合で使用した合金等を用いても良い。

10

#### 【0061】

また、導電材を堆積させる手法としては、メッキ法の替わりに蒸着法や金属ペースト法を用いてもよい。金属ペースト法は、金属ペーストを開孔42aの絶縁フィルム42表面(近傍)まで充填して固化させる方法である。

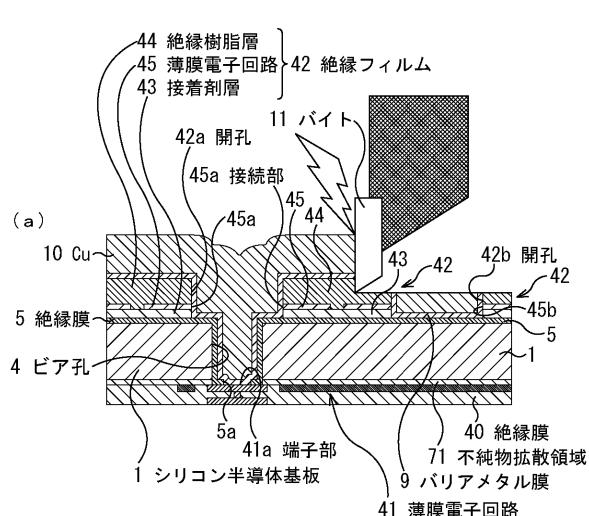

#### 【0062】

そして、図16に示すように、Cu10及び絶縁フィルム42にダイアモンド等からなる硬質のバイト11を用いた切削加工を施し、Cu10の絶縁フィルム42上の部分及び絶縁フィルム42の絶縁樹脂層44の上層部分、ここでは厚み4μm程度の部分を切削除去する。これにより、Cu10の表面及び絶縁フィルム42の表面が連続して平坦とされ、ピア孔4及び開孔42aをCuで充填し、高さが揃えられてなる各貫通電極12が形成される。貫通電極12は、シリコン半導体基板1を裏面から貫通し、ピア孔4の内壁面の底部で端子部41aを介して薄膜電子回路41と、開孔42aの内壁面の側部で接続部45aを介して薄膜電子回路45と、それぞれ電気的に接続されてなるものである。

20

#### 【0063】

このように、本実施形態によれば、シリコン半導体基板1の第1の主面(例えば表面)には薄膜電子回路41が設けられるとともに、第2の主面(例えば裏面)には薄膜電子回路45を内包する絶縁フィルム42が形成されてなる半導体装置であって、電子回路41, 45を貫通電極12により接続するに際して、貫通電極表面のCMP研磨工程及びフォトリソグラフィーのプロセスによる配線形成工程等を簡略化し、シリコン半導体基板1との絶縁及び機械強度を十分に確保する貫通電極12を容易且つ確実に形成し、信頼性の高い半導体装置を実現することが可能となる。更に、併設された各貫通電極12の高さのバラツキを容易且つ高度に解消し、しかも同時に貫通電極12の表面をこれを埋め込む絶縁フィルム42の表面と連続して平坦化することにより、貫通電極12の機械的衝撃に対する更なる耐性を確実に確保することが可能となる。

30

#### 【0064】

##### -変形例-

ここで、第2の実施形態の諸変形例について説明する。

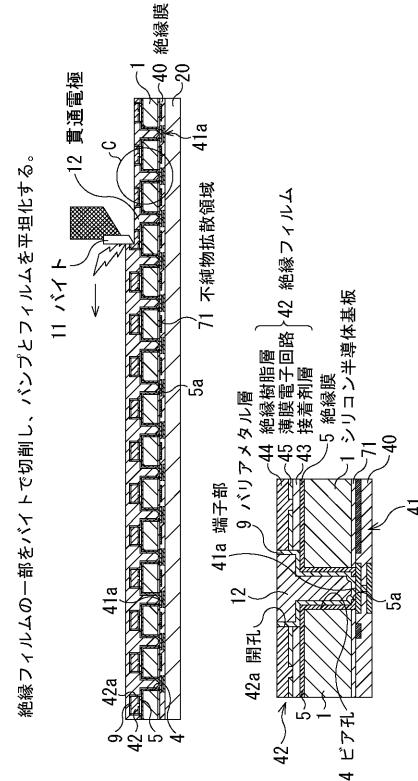

#### 【0065】

##### (変形例1)

この変形例1では、第2の実施形態において、貫通電極12と隣接してシリコン半導体基板1の裏面上で薄膜電子回路45と接続される電極を形成する場合を図17及び図18を用いて例示する。なお、図17及び図18の各図においては図示の便宜上、端子部41aの近傍を拡大して示す。

40

先ず、第2の実施形態の図11～図14(a)と同様の工程を経て、絶縁膜5のピア孔4の底部上に位置する開孔6aに相当する部分5aをエッティング除去し、端子部41aの表面の一部を露出させる。

#### 【0066】

続いて、メタルマスク6を除去した後、図17(a)に示すように、絶縁膜5上にこれよりも厚い絶縁フィルム42を貼り付ける。この絶縁フィルム42は、下層に接着剤層43が設けられ、上層に切削可能な有機絶縁材料、ここではエポキシ樹脂等からなる絶縁樹

50

脂層44が設けられてなる。絶縁層44の内部にはキャパシタやインダクタ、配線層等の薄膜電子回路45が内包されている。ここでは、薄膜電子回路45を例えればCu配線とし、接着剤層43、薄膜電子回路45、絶縁樹脂層44の厚みがそれぞれ10nm、5nm、20nm程度とされている。この絶縁フィルム42は、ビア孔4よりも径の大きい開孔42aと、ビア孔4に隣接した開孔42bとが形成され、開孔42aの内壁面から薄膜電子回路45の接続部45aが、開孔42bの内壁面から薄膜電子回路45の接続部45bがそれぞれ露出している。この絶縁フィルム42を、開孔42aをビア孔4の位置に整合させて開孔42aにビア孔4が含まれるようにシリコン半導体基板1の裏面上で位置合わせして、絶縁フィルム42を接着剤層43によりシリコン半導体基板1の裏面に貼り付ける。絶縁フィルム42の耐熱温度は、後述する貫通電極の形成プロセス時における最大温度を超える値である。

10

## 【0067】

続いて、図17(b)に示すように、ビア孔4、開孔42a、及び42bの内壁面を覆うように絶縁フィルム42上にTaNやTiN等からなるバリアメタル層9をCVD法又はスパッタ法等により形成した後、導電材、ここではCuからなるメッキシード層(不図示)をCVD法又はスパッタ法等により形成する。

## 【0068】

続いて、図17(c)に示すように、メッキ法によりビア孔4、開孔42a、及び42bを埋め込むようにバリアメタル層9上に導電材、ここではCu10を堆積する。なお導電材として、例えばCuの替わりにAu、Ag、Ni、Sn、またはCuとこれらとを適宜の割合で使用した合金等を用いても良い。

20

## 【0069】

また、導電材を堆積させる手法としては、メッキ法の替わりに蒸着法や金属ペースト法を用いてもよい。金属ペースト法は、金属ペーストを開孔42a、42bの絶縁フィルム42表面(近傍)まで充填して固化させる方法である。

## 【0070】

そして、図18(a)に示すように、Cu10及び絶縁フィルム42にダイアモンド等からなる硬質のバイト11を用いた切削加工を施し、Cu10の絶縁フィルム42上の部分及び絶縁フィルム42の絶縁樹脂層44の上層部分を除去する。これにより、図18(b)に示すように、Cu10の表面及び絶縁フィルム42の表面が連続して平坦とされ、ビア孔4及び開孔42aをCuで充填し、高さが揃えられてなる各貫通電極12が形成されるとともに、開孔42bをCuで充填し、高さが揃えられてなる各電極51が形成される。貫通電極12は、シリコン半導体基板1を裏面から貫通し、ビア孔4の内壁面の底部で端子部41aを介して薄膜電子回路41と、開孔42aの内壁面の側部で接続部45aを介して薄膜電子回路45と、それぞれ電気的に接続されてなるものである。他方、電極51は、開孔42bの内壁面の側部で接続部45bを介して薄膜電子回路45と接続されてなるものである。なおここで、貫通電極12と電極51とは、薄膜電子回路45内で電気的に接続されている場合もあれば、接続されない場合もある。

30

## 【0071】

このように、本実施形態によれば、シリコン半導体基板1の第1の正面(例えば表面)には薄膜電子回路41が設けられるとともに、第2の正面(例えば裏面)には薄膜電子回路45を内包する絶縁フィルム42が形成されてなる半導体装置であって、電子回路41、45と貫通電極12とを接続するとともに、電子回路45と電極51とを接続するに際して、貫通電極及び電極表面のCMP研磨工程及びフォトリソグラフィーのプロセスによる配線形成工程等を簡略化し、シリコン半導体基板1との絶縁及び機械強度を十分に確保する貫通電極12及び電極51を容易且つ確実に同時形成し、信頼性の高い半導体装置を実現することが可能となる。更に、併設された各貫通電極12及び各電極51の高さのバラツキを容易且つ高度に解消し、しかも同時に貫通電極12及び電極51の表面をこれを埋め込む絶縁フィルム42の表面と連続して平坦化することにより、貫通電極12及び電極51の機械的衝撃に対する更なる耐性を確実に確保することが可能となる。

40

50

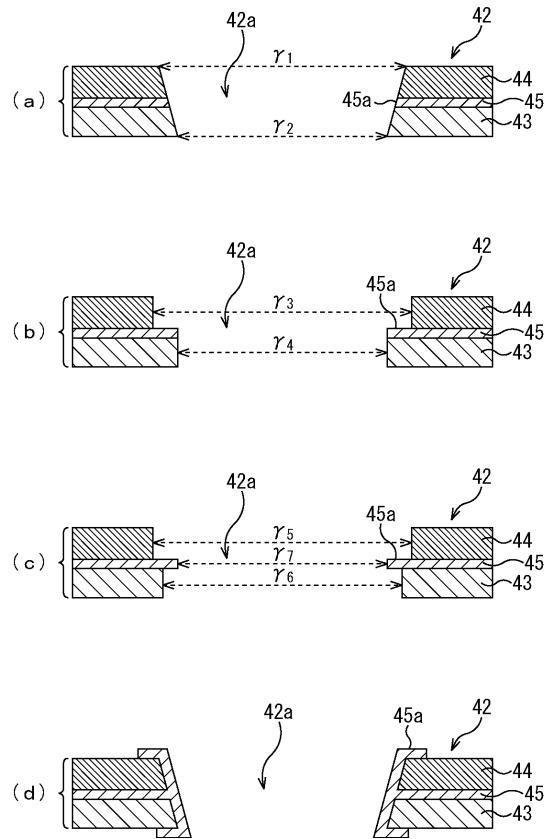

## 【0072】

## (変形例2)

この変形例2では、第2の実施形態において、絶縁フィルム42の開孔42aの形状が異なるいくつかの場合について、図19を用いて例示する。なお、図19の各図においては図示の便宜上、絶縁フィルム42のみを示す。

## 【0073】

(1) 図19(a)では、絶縁フィルム42において、開孔42aの内壁面がテープ状とされ、開孔42aの上面の孔径 $r_1$ がシリコン半導体基板1に貼付される下面の孔径 $r_2$ よりも大きく形成されている場合を開示する。このように開孔42aを形成することにより、開孔42aをCu10で確実に埋め込むことができるとともに、Cu10と薄膜電子回路45の接続部45aとの確実な接続を得ることが可能となる。

10

## 【0074】

(2) 図19(b)では、絶縁フィルム42において、開孔42aの絶縁樹脂層44の孔径 $r_3$ よりも接続部45a及び接着剤層43の孔径 $r_4$ の方が小さく形成されている場合を開示する。これにより、開孔42aの側壁面から接続部45aの側面部及び上面部が露出することになり、Cu10との接触面積が大きくなつて更に確実な接続を得ることが可能となる。なお、このような形状に開孔42aを形成するには、例えば先ず接続部45a及び接着剤層43の径で絶縁フィルム42に開孔形成した後、絶縁樹脂層44の開孔部位のみをアッシング処理して径を拡大することが考えられる。

20

## 【0075】

(3) 図19(c)では、絶縁フィルム42において、開孔42aの絶縁樹脂層44の孔径 $r_5$ 及び接着剤層43の孔径 $r_6$ よりも接続部45aの孔径 $r_7$ の方が大きく形成されている場合を開示する。これにより、開孔42aの側壁面から接続部45aが突出して露出することになり、Cu10との接触面積が大きくなつて更に確実な接続を得ることが可能となる。なお、このような形状に開孔42aを形成するには、例えば先ず接続部45aの径で絶縁フィルム42に開孔形成した後、絶縁樹脂層44の開孔部位及び接着剤層43の開孔部位をそれぞれアッシング処理して径を拡大することが考えられる。

30

## 【0076】

(4) 図19(d)では、絶縁フィルム42において、例えば)図15(a)のように開孔42aの内壁面がテープ状に形成するとともに、開孔42aの側壁面を覆うように接続部45aが形成されている場合を開示する。これにより、Cu10との接触面積が極めて大きくなつて更に確実な接続を得ることが可能となる。

## 【0077】

## (第3の実施形態)

本実施形態では、第1の実施形態で説明した貫通電極を有する複数の半導体装置を接続し積層してなる複合半導体装置の具体的な一例についてその製造方法と共に説明する。

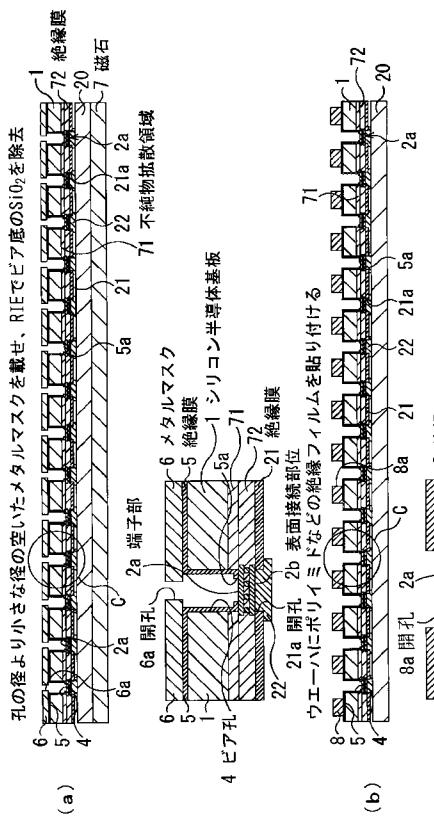

## 【0078】

図20～図26は、第3の実施形態による複合半導体装置の製造方法を工程順に示す概略断面図である。なお、図20(c), 図20(d), 図22～図25の各図, 図26(a)では、前段の図において円Cで囲まれた部分(1つの端子部2aの周辺部に相当する。)を拡大した様子を後段に示す。また、図26(b)では前記拡大図に相当する概略断面図のみを示す。ここで、第1の実施形態と同一の構成部材等については同符号を記す。

40

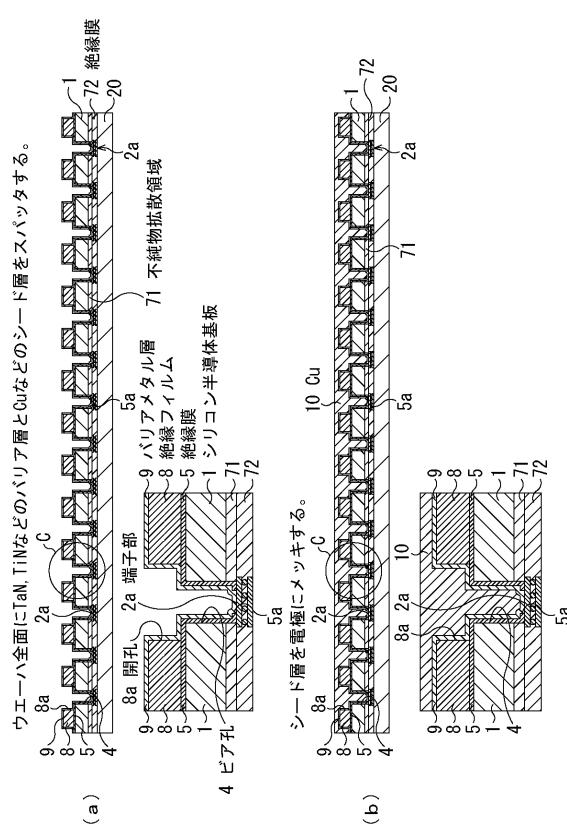

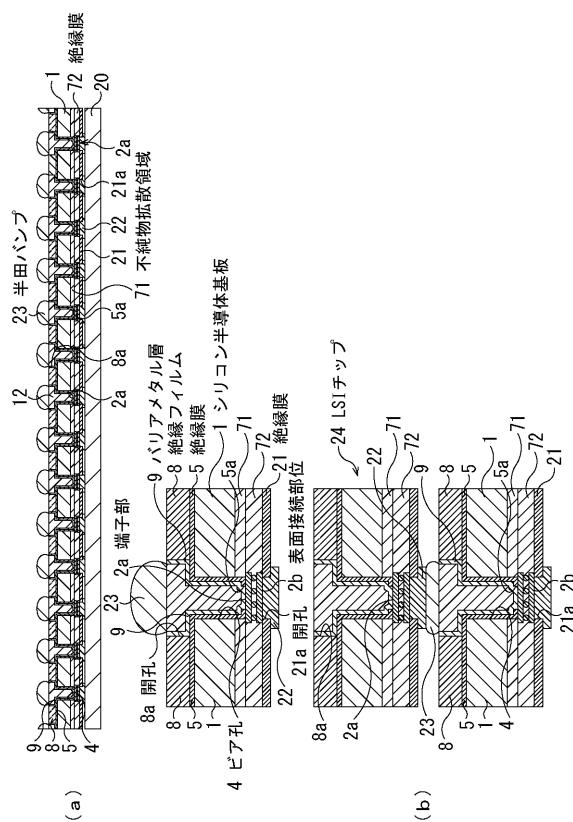

## 【0079】

先ず、図20(a)に示すように、シリコン半導体基板1を用意する。そして、基板表面に各半導体素子の不純物拡散層が形成されてなる不純物拡散領域71を、不純物拡散領域71上に例えば無機物よりなる絶縁膜72内に埋設され、表面が露出してなる端子部2aをそれぞれ形成する。なお図示の例では、隣接する端子部2a間の領域が第1の実施形態で説明した図9の素子領域103となる。素子領域103は、MOSトランジスタ等の半導体素子、及びキャパシタやインダクタ等の受動素子などのLSI素子が形成されてなる領域であり、LSI素子には端子部2aが形成されており、端子部2aは2層の導体パ

50

ターンをピアで接続してなる。この場合、素子領域 103 は、各々の隣接する端子部 2a 間の領域を総括するものである。

【0080】

続いて、図 20 (b) に示すように、シリコン半導体基板 1 の表面に  $\text{SiO}_2$  や  $\text{SiN}$  等からなる絶縁膜 21 を CVD 法等により形成した後、フォトリソグラフィー及びそれに続くドライエッチングにより絶縁膜 21 をパターニングし、端子部 2a の表面接続部位 2b の一部を露出させる開孔 21a を形成する。

【0081】

続いて、図 20 (c) に示すように、絶縁膜 21 上に Au, Cu, Ag, Ni, Sn、またはこれらを適宜の割合で使用した合金等からなる金属膜を CVD 法又はスパッタ法により堆積し、これをパターニングして、端子部 2a 上で開孔 21a を介して表面接続部位 2b と接続されてなる突起電極 22 をパターン形成する。

10

【0082】

続いて、図 20 (d) に示すように、シリコン半導体基板 1 の表面にダイアモンド等からなる硬質のバイト 11 を用いた切削加工を施し、各突起電極 22 の上層部分を除去する。これにより、各突起電極 22 の表面は鏡面状に平坦化されるとともに、各々の高さが正確に揃えられて高さのバラツキが解消される。

【0083】

続いて、図 21 (a) に示すように、突起電極 22 の形成されたシリコン半導体基板 1 の表面を石英やガラスの台座 20 に UV テープ等により貼り付け、シリコン半導体基板 1 の裏面を研削及びエッチングし、シリコン半導体基板 1 を  $50 \mu\text{m} \sim 200 \mu\text{m}$  程度の厚みに調節する。ここで、初期のシリコン半導体基板 1 の厚みが一様でない場合、または一様でないことに加えてうねりを伴う場合のような場合には、支持面が平坦とされた基板支持台（不図示）を用意し、この支持面に吸着、例えば真空吸着によりシリコン半導体基板 1 の表面を吸着させてシリコン半導体基板 1 を基板支持台に固定する。このとき、シリコン半導体基板 1 の表面は支持面への吸着により強制的に平坦とされており、これにより当該表面が裏面の平坦化の基準面となる。このように、シリコン半導体基板 1 の表面を裏面平坦化の基準面として裏面を機械研削し、裏面の凸部を研削除去して平坦化処理し、厚み調節を行うようにしても良い。

20

【0084】

続いて、図 21 (b) に示すように、シリコン半導体基板 1 の裏面上にフォトレジスト 3 を塗付する。

30

【0085】

続いて、図 21 (c) に示すように、フォトレジスト 3 をフォトリソグラフィーにより加工し、端子部 2a 上に相当する部分に開孔 3a を形成する。

【0086】

続いて、図 22 (a) に示すように、フォトレジスト 3 をマスクとしてシリコン半導体基板 1 を裏面からエッチング加工する。例えば、フッ素系あるいは塩素系のガスを用いたドライエッチングにより加工し、各端子部 2a の表面の一部を露出させるピア孔 4 を形成する。

40

【0087】

続いて、フォトレジスト 3 を灰化処理等により除去する。なお、この灰化処理等の工程では、例えばフォトレジスト 3 をアルカリ溶液に曝した後、酸素プラズマを照射して、残渣をアッシング（灰化処理）することにより、フォトレジスト 3 を除去する。その後、図 22 (b) に示すように、ピア孔 4 の内壁面を覆うようにシリコン半導体基板 1 の裏面上に CVD 法等により  $\text{SiO}_2$  や  $\text{SiN}$  等からなる絶縁膜 5 を膜厚  $1 \mu\text{m}$  程度に形成する。

【0088】

続いて、図 23 (a) に示すように、絶縁膜 5 上にメタルマスク 6 を載置する。このメタルマスク 6 は、ピア孔 4 に整合した位置にピア孔 4 よりも径の小さい開孔 6a が形成されており、ピア孔 4 に開孔 6a が含まれる（即ち、開孔 6a の外周がピア孔 4 の外周の内

50

側に位置する)ようにシリコン半導体基板1の裏面上で位置合わせしてメタルマスク6を絶縁膜5上に重ね、台座20の下部に設けた磁石7の磁力によりメタルマスク6の位置を固定する。

【0089】

そして、メタルマスク6を用いて絶縁膜5をドライエッティングする。このとき、絶縁膜5のビア孔4の底部上に位置する開孔6aに相当する部分がエッティング除去され、端子部2aの表面の一部が露出する。

【0090】

続いて、メタルマスク6を除去した後、図23(b)に示すように、絶縁膜5上にこれよりも厚い切削可能な有機絶縁材料、ここでは膜厚30μm程度のポリイミド等からなる絶縁フィルム8を貼り付ける。この絶縁フィルム8は、ビア孔4に整合した位置にビア孔4よりも径の大きい開孔8aが形成されており、開孔8aにビア孔4が含まれるようにシリコン半導体基板1の裏面上で位置合わせして絶縁フィルム8を例えれば糊を介して貼り付ける。絶縁フィルム8及びこの糊の耐熱温度は、後述する貫通電極の形成プロセス時における最大温度を超える値である。

10

【0091】

ここで、第1の実施形態と同様に、例えば図6に示すように、絶縁フィルム8を個々のLSI素子31に対応したサイズのものとして、個々のLSI素子31ごとに絶縁フィルム8を位置合わせして貼り付けるようにしたり、図7に示すように、絶縁フィルム8を複数のLSI素子31のブロック30に対応したサイズのものとして、ブロック30ごとに絶縁フィルム8を位置合わせして貼り付けても良い。

20

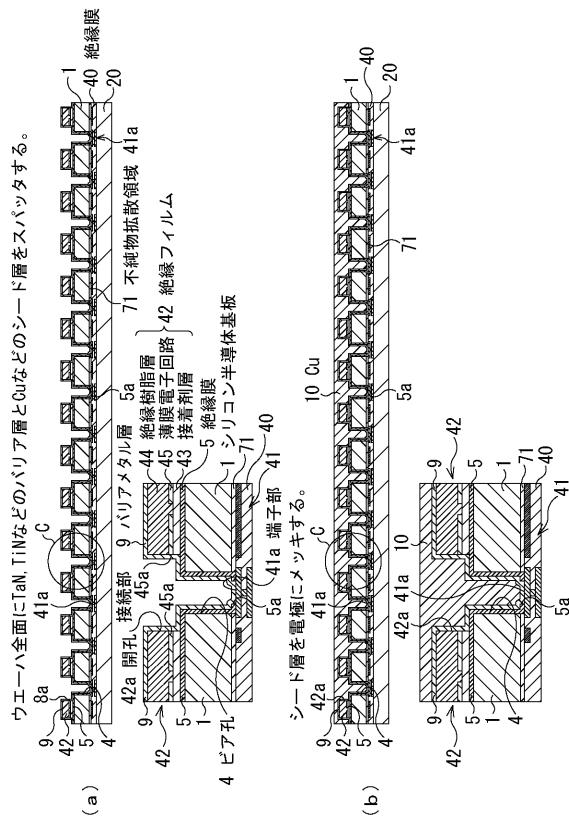

【0092】

続いて、図24(a)に示すように、ビア孔4及び開孔8aの内壁面を覆うように絶縁フィルム8上にTaNやTiN等からなるバリアメタル層9をCVD法又はスパッタ法等により形成した後、導電材、ここではCuからなるメッキシード層(不図示)をCVD法又はスパッタ法等により形成する。

【0093】

続いて、図24(b)に示すように、メッキ法によりビア孔4及び開孔8aを埋め込むようにバリアメタル層9上に導電材、ここではCu10を堆積する。なお導電材として、例えばCuの替わりにAu, Ag, Ni, Sn、またはCuとこれらとを適宜の割合で使用した合金等を用いても良い。

30

【0094】

また、導電材を堆積させる手法としては、メッキ法の替わりに蒸着法や金属ペースト法を用いてもよい。金属ペースト法は、金属ペーストを開孔8aの絶縁フィルム8表面(近傍)まで充填して固化させる方法である。

【0095】

続いて、図25に示すように、Cu10及び絶縁フィルム8にダイアモンド等からなる硬質のバイト11を用いた切削加工を施し、Cu10の絶縁フィルム8上の部分及び絶縁フィルム8の上層部分を除去する。これにより、Cu10の表面及び絶縁フィルム8の表面が連続して平坦とされ、ビア孔4及び開孔8aをCuで充填し、高さが揃えられてなる各貫通電極12が形成される。貫通電極12は、シリコン半導体基板1を裏面から貫通し、ビア孔4の底部で端子部2aを介してLSI素子と電気的に接続されてなるものである。

40

【0096】

続いて、図26(a)に示すように、各貫通電極12上にバンプ、ここでは半田バンプ23を形成する。

【0097】

そして、図26(b)に示すように、図20～図26(a)と同様の工程を経た後、例えばLSI素子ごとにシリコン半導体基板1からLSIチップ24として切り出し、各LSIチップ24を同様に図20～図26(a)の工程を経たシリコン半導体基板1上に積

50

層する。具体的には、シリコン半導体基板1の半田バンプ23上にLSIチップ24の突起電極22を、例えば熱処理、超音波処理及びプラズマ活性化処理し、接続して積層一体化する。これにより、一対の端子部2aが貫通電極12を介して接続されることになる。

【0098】

なお、上記の例ではLSI素子2を2層に積層する場合について説明したが、3層以上に積層してなる複合半導体装置を作製する場合もある。

【0099】

このように、本実施形態によれば、シリコン半導体基板1との絶縁及び機械強度を十分に確保する貫通電極12を容易且つ確実に形成し、容易且つ確実にチップを積層一体化することにより、信頼性の高い複合半導体装置を実現することが可能となる。更に、併設された各貫通電極12の高さのバラツキを容易且つ高度に解消し、しかも同時に貫通電極12の表面を、これを埋め込む絶縁フィルム8の表面と連続して平坦化することにより、貫通電極12の機械的衝撃に対する更なる耐性を確実に確保することが可能となる。

10

【0100】

なお、本実施形態では第1の実施形態の貫通電極を有する複数の半導体装置を接続し積層してなる複合半導体装置を例示したが、第2の実施形態の貫通電極を有する複数の半導体装置から複合半導体装置を構成しても良い。

【0101】

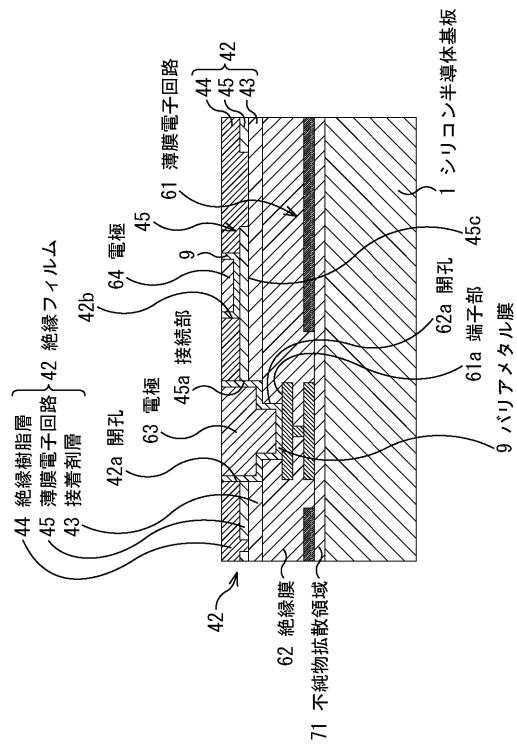

また、第1～第3の実施形態では、貫通電極をシリコンウェーハの裏面（第2の主面）に形成する場合を例示したが、電極を表面（第1の主面）に形成する場合にも、本発明は適用可能である。この場合、例えば第2の実施形態の半導体装置に適用した例を図27に示す。

20

【0102】

ここでは、シリコン半導体基板1上に不純物拡散領域71と、絶縁膜62に埋設された薄膜電子回路61とを形成する。次に、絶縁膜62に薄膜電子回路61の端子部61aの表面の一部を露出させるビア孔62aを形成する。そして、ビア孔4よりも径の大きい開孔42aと、ビア孔4に隣接した開孔42bとが形成された絶縁フィルム42を用い、開孔42aにビア孔62aが含まれるように位置合わせて絶縁膜62上に絶縁フィルム42を接着剤層43により貼り付ける。絶縁フィルム42は、開孔42aの側表面から薄膜電子回路45の接続部45aが、開孔42bの底面から薄膜電子回路45の接続部45cがそれぞれ露出している。

30

【0103】

そして、バリアメタル層9を形成し、開孔42a及び42cを埋め込むようにバリアメタル層9上に導電材、ここではCu10を堆積する。そして、Cu10及び絶縁フィルム42にダイアモンド等からなる硬質のバイトを用いた切削加工を施し、Cu10の絶縁フィルム42上の部分及び絶縁フィルム42の絶縁樹脂層44の上層部分を除去する。これにより、Cu10の表面及び絶縁フィルム42の表面が連続して平坦とされ、ビア孔62a及び開孔42aをCuで充填し、高さが揃えられてなる各電極63が形成されるとともに、開孔42bをCuで充填し、高さが揃えられてなる各電極64が形成される。電極63は、ビア孔62aの内壁面の底部で端子部61aを介して薄膜電子回路61と、開孔42aの内壁面の側部で接続部45aを介して薄膜電子回路45と、それぞれ電気的に接続されてなるものである。他方、電極64は、開孔42bの内壁面の底部で接続部45cを介して薄膜電子回路45と接続されてなるものである。

40

【0104】

以上説明した第1～第3の実施形態の（複合）半導体装置は、様々なデバイスに適用可能である。適用の具体例を図28に示す。

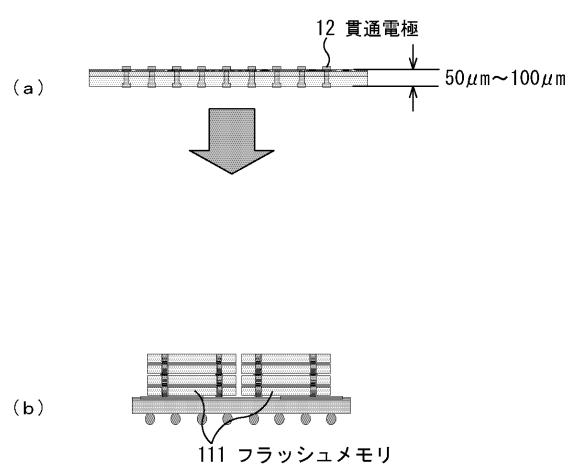

図28(b)には、図28(a)に示す本実施形態の複合型半導体装置をスタック型のフラッシュメモリ111として本実施形態の半導体装置を適用し、大記憶容量化を実現する例を示す。

【0105】

50

このように、本実施形態の（複合）半導体装置を各種デバイスに適用することにより、貫通電極で最短距離の配線を形成する。これにより更なる高速化が実現し、併せて超小型化に寄与する。

【0106】

- 付記 -

以下、本発明の諸態様を付記としてまとめて記載する。

【0107】

（付記1）一方の主面に半導体素子が形成された半導体基板において、前記半導体基板の他方の主面から前記半導体素子の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の主面に第1の絶縁膜を形成する工程と、10

前記第1の絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記接続部位の一部を露出させる工程と、

前記半導体基板の前記他方の主面上に、前記第1の開孔よりも大きい第2の開孔を有してなるフィルム状の第2の絶縁膜を、前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

前記第2の絶縁膜上に、前記第1及び第2の開孔を共に埋め込むように導電膜を形成する工程と、

前記導電膜の一部及び前記第2の絶縁膜の一部を除去し、前記第1及び第2の開孔を充填して前記接続部位と接続されてなる貫通電極を形成する工程と20

を含むことを特徴とする半導体装置の製造方法。

【0108】

（付記2）一方の主面に半導体素子が形成された半導体基板において、前記半導体基板の他方の主面から前記半導体素子の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の主面に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記接続部位の一部を露出させる工程と、

前記半導体基板の前記他方の主面上に、前記第1の開孔よりも大きい第2の開孔を有してなるフィルム状の第2の絶縁膜を、前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、30

少なくとも前記第1及び第2の開孔に導電材を充填して、前記接続部位と電気的に接続する導電膜を形成する工程と、

前記導電膜の一部及び前記第2の絶縁膜の一部を除去し、前記接続部位と電気的に接続されてなる貫通電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法。

【0109】

（付記3）前記貫通電極を形成するに際して、前記導電膜及び前記第2の絶縁膜を切削加工し、前記導電膜の表面及び前記第2の絶縁膜の表面を連続して平坦化することを特徴とする付記1又は2に記載の半導体装置の製造方法。40

【0110】

（付記4）一方の主面に第1の電子回路が形成された半導体基板において、前記半導体基板の他方の主面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の主面に絶縁膜を形成する工程と、

前記絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記第1の接続部位の一部を露出させる工程と、

前記第1の開孔よりも大きい第2の開孔を有し、第2の電子回路が絶縁材料内に埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出し50

てなるフィルムを、前記半導体基板の前記他方の主面上に前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

前記フィルム上に、前記第1及び第2の開孔を共に埋め込むように導電膜を形成する工程と、

前記導電膜の一部及び前記フィルムの一部を除去し、前記第1及び第2の開孔を充填して前記第1及び第2の接続部位と接続されてなる貫通電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法。

【0111】

(付記5) 一方の主面に第1の電子回路が形成された半導体基板において、前記半導体基板の他方の主面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔を形成する工程と、

前記第1の開孔の内壁面を覆うように前記半導体基板の前記他方の主面に絶縁膜を形成する工程と、

前記絶縁膜の前記第1の開孔の底面に位置する部分を除去して、前記第1の接続部位の一部を露出させる工程と、

前記第1の開孔よりも大きい第2の開孔を有し、内部に第2の電子回路が埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出してなるフィルムを、前記半導体基板の前記他方の主面上に前記第2の開孔が前記第1の開孔を含むように位置合わせして貼り付ける工程と、

少なくとも前記第1及び第2の開孔に導電材を充填して、前記第1及び第2の接続部位と電気的に接続する導電膜を形成する工程と、

前記導電膜の一部及び前記フィルムの一部を除去し、前記第1及び第2の接続部位と電気的に接続されてなる貫通電極を形成する工程と

を含むことを特徴とする半導体装置の製造方法。

【0112】

(付記6) 前記フィルムは、前記第2の開孔と隣接して前記第2の電子回路の第3の接続部位を露出させる第3の開孔を有しており、

前記導電膜を前記第1及び第2の開孔と共に前記第3の開孔を埋め込むように形成し、前記第3の接続部位と電気的に接続されてなる電極を前記貫通電極と共に形成することを特徴とする付記4又は5に記載の半導体装置の製造方法。

【0113】

(付記7) 前記フィルムは、前記第2の電子回路が多層構造とされてなるものであることを特徴とする付記4~6のいずれか1項に記載の半導体装置の製造方法。

【0114】

(付記8) 前記フィルムは、前記第2の開孔の内壁面がテープ状とされ、上面の孔径が前記半導体基板に貼付される下面の孔径よりも大きいものであることを特徴とする付記4~7のいずれか1項に記載の半導体装置の製造方法。

【0115】

(付記9) 前記フィルムは、前記第2の電子回路の前記第2の接続部位が前記第2の開孔の内壁面から上面及び側面を露出するように形成されているものであることを特徴とする付記4~7のいずれか1項に記載の半導体装置の製造方法。

【0116】

(付記10) 前記フィルムは、前記第2の電子回路の前記第2の接続部位が前記第2の開孔の内壁面から突出するように形成されているものであることを特徴とする付記4~7のいずれか1項に記載の半導体装置の製造方法。

【0117】

(付記11) 前記フィルムは、前記第2の電子回路の前記第2の接続部位が前記第2の開孔の内壁面を覆うように形成されているものであることを特徴とする付記4~7のいずれか1項に記載の半導体装置の製造方法。

【0118】

10

20

30

40

50

(付記12) 前記貫通電極を形成するに際して、前記導電膜及び前記フィルムを切削加工し、前記導電膜の表面及び前記フィルムの表面を連続して平坦化することを特徴とする付記4～11のいずれか1項に記載の半導体装置の製造方法。

【0119】

(付記13) 前記第1の正面が前記半導体基板の表面であり、前記第2の正面が前記半導体基板の裏面であることを特徴とする付記1～12のいずれか1項に記載の半導体装置の製造方法。

【0120】

(付記14) 前記導電膜を形成するに際して、メッキ法により金属を堆積させることを特徴とする付記1～13のいずれか1項に記載の半導体装置の製造方法。

10

【0121】

(付記15) 前記導電膜を形成するに際して、蒸着法により金属を堆積させることを特徴とする付記1～13のいずれか1項に記載の半導体装置の製造方法。

【0122】

(付記16) 前記導電膜を形成するに際して、金属ペーストを前記第1及び第2の開孔に埋め込み、前記金属ペーストを固化させることを特徴とする付記1～13のいずれか1項に記載の半導体装置の製造方法。

【0123】

(付記17) 前記第1の開孔を形成する前に、前記半導体素子上に、前記半導体基板の前記一方の正面から突出する突起電極を形成する工程を更に含むことを特徴とする付記1～16のいずれか1項に記載の半導体装置の製造方法。

20

【0124】

(付記18) 前記突起電極の上部を切削加工により除去し、前記突起電極の上面を平坦な鏡面状態とすることを特徴とする付記17に記載の半導体装置の製造方法。

【0125】

(付記19) 前記貫通電極上にハンダバンプを形成する工程を更に含むことを特徴とする付記1～18のいずれか1項に記載の半導体装置の製造方法。

(付記20) 前記第2の絶縁膜は個々の前記半導体素子に対応した大きさのものであり、個々の前記半導体素子ごとに前記各第2の絶縁膜を貼り付けることを特徴とする付記1～19のいずれか1項に記載の半導体装置の製造方法。

30

【0126】

(付記21) 前記第2の絶縁膜は個々の複数の前記半導体素子からなるブロックに対応した大きさのものであり、個々の前記ブロックごとに前記各第2の絶縁膜を貼り付けることを特徴とする付記1～19のいずれか1項に記載の半導体装置の製造方法。

【0127】

(付記22) 一方の正面に半導体素子が形成された半導体基板と、

前記半導体基板に、当該半導体基板の他方の正面から前記半導体素子の接続部位を露出させる第1の開孔が形成され、前記第1の開孔の内壁面を覆い底面の一部から前記接続部位の一部を露出させるように前記半導体基板の前記他方の正面に形成されてなる第1の絶縁膜と、

40

前記第1の開孔よりも大きい第2の開孔を有し、前記第2の開孔が前記第1の開孔を含むように前記半導体基板の前記他方の主面上に塗付されてなる、前記第1の絶縁膜よりも厚いフィルム状の第2の絶縁膜と、

前記第1及び第2の開孔を充填して前記接続部位と接続されてなる貫通電極とを含み、

前記貫通電極の表面及び前記第2の絶縁膜の表面が連続して平坦化されてなることを特徴とする半導体装置。

【0128】

(付記23) 前記半導体素子上で前記半導体基板の前記一方の正面から突出してなる突起電極を含むことを特徴とする付記22に記載の半導体装置。

50

## 【0129】

(付記24) 一方の主面に第1の電子回路が形成された半導体基板と、

前記半導体基板に、当該半導体基板の他方の主面から前記第1の電子回路の第1の接続部位を露出させる第1の開孔が形成され、前記第1の開孔の内壁面を覆い底面の一部から前記第1の接続部位の一部を露出させるように前記半導体基板の前記他方の主面に形成されてなる絶縁膜と、

前記第1の開孔よりも大きい第2の開孔を有し、第2の電子回路が絶縁材料内に埋設されるとともに前記第2の電子回路の第2の接続部位が前記第2の開孔の内壁面から露出してなり、前記第2の開孔が前記第1の開孔を含むように前記半導体基板の前記他方の主面上に貼付されてなるフィルムと、

前記第1及び第2の開孔を充填して前記第1及び第2の接続部位と接続されてなる貫通電極と

を含み、

前記貫通電極の表面及び前記フィルムの表面が連続して平坦化されてなることを特徴とする半導体装置。

## 【0130】

(付記25) 前記フィルムは、前記第2の開孔と隣接して前記第2の電子回路の第3の接続部位を露出させる第3の開孔を有しており、

前記第3の開孔を充填して前記第3の接続部位と電気的に接続されてなる電極を含み、

前記貫通電極の表面、前記電極の表面及び前記フィルムの表面が連続して平坦化されてなることを特徴とする付記24に記載の半導体装置。

## 【0131】

(付記26) 前記フィルムは、前記第2の開孔の内壁面がテーパ状とされ、上面の孔径が前記半導体基板に貼付される下面の孔径よりも大きいものであることを特徴とする付記24又は25に記載の半導体装置。

## 【0132】

(付記27) 前記フィルムは、前記第2の電子回路の前記第2の接続部位が前記第2の開孔の内壁面から上面及び側面を露出するように形成されているものであることを特徴とする付記24又は25に記載の半導体装置。

## 【0133】

(付記28) 前記フィルムは、前記第2の電子回路の前記第2の接続部位が前記第2の開孔の内壁面から突出するように形成されているものであることを特徴とする付記24又は25に記載の半導体装置。

## 【0134】

(付記29) 前記フィルムは、前記第2の電子回路の前記第2の接続部位が前記第2の開孔の内壁面を覆うように形成されているものであることを特徴とする付記24又は25に記載の半導体装置。

## 【0135】

(付記30) 前記突起電極の上面が平坦な鏡面状態とされてなることを特徴とする付記24～29のいずれか1項に記載の半導体装置。

## 【0136】

(付記31) 前記貫通電極上に形成されてなるバンプを含むことを特徴とする付記24～30のいずれか1項に記載の半導体装置。

## 【0137】

(付記32) 付記22～31のいずれか1項に記載の半導体装置を少なくとも2つ含み、

着目する一組の前記半導体装置において、一方の前記半導体装置の前記貫通電極と他方の前記半導体装置の突起電極とが接続され、積層一体化されていることを特徴とする複合半導体装置。

## 【0138】

10

20

30

40

50

(付記33)各半導体装置は前記貫通電極上にバンプを有しており、着目する一組の前記半導体装置において、一方の前記半導体装置の前記バンプと他方の前記半導体装置の突起電極とが接続され、積層一体化されていることを特徴とする付記32に記載の複合半導体装置。

【図面の簡単な説明】

【0139】

【図1】第1の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図2】図1に引き続き、第1の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図3】図2に引き続き、第1の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図4】図3に引き続き、第1の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図5】図4に引き続き、第1の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図6】絶縁フィルムをシリコンウェーハに貼り付ける具体的な一例を示す概略平面図である。

【図7】絶縁フィルムをシリコンウェーハに貼り付ける具体的な他の例を示す概略平面図である。

【図8】本発明が適用される半導体装置の概観を示す概略斜視図である。

20

【図9】本発明が適用され、本実施形態において開示される半導体装置の概観を示す概略斜視図である。

【図10】素子領域にMOSトランジスタが形成された様子を示す概略断面図である。

【図11】第2の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図12】図11に引き続き、第2の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図13】図12に引き続き、第2の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図14】図13に引き続き、第2の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

30

【図15】図14に引き続き、第2の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図16】図15に引き続き、第2の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図17】第2の実施形態による半導体装置の製造方法の変形例1を工程順に示す概略断面図である。

【図18】図17に引き続き、第2の実施形態による半導体装置の製造方法の変形例1を工程順に示す概略断面図である。

【図19】第2の実施形態による半導体装置の変形例2を示す概略断面図である。

40

【図20】第3の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図21】図20に引き続き、第3の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図22】図21に引き続き、第3の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図23】図22に引き続き、第3の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図24】図23に引き続き、第3の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

50

【図25】図24に引き続き、第3の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図26】図25に引き続き、第3の実施形態による半導体装置の製造方法を工程順に示す概略断面図である。

【図27】本発明の半導体装置の他の例を示す概略断面図である。

【図28】第1～第3の実施形態の(複合)半導体装置を各種デバイスに適用する具体例を示す模式図である。

【符号の説明】

【0140】

|                                         |               |    |

|-----------------------------------------|---------------|----|

| 1                                       | シリコンウェーハ      | 10 |

| 2                                       | L S I 素子の形成領域 |    |

| 2 a , 4 1 a , 6 1 a                     | 端子部           |    |

| 2 b                                     | 表面接続部位        |    |

| 3                                       | フォトレジスト       |    |

| 3 a , 6 a , 8 a , 2 1 a , 4 2 a , 4 2 b | 開孔            |    |

| 4 , 6 2 a                               | ビア孔           |    |

| 5 , 2 1 , 6 2                           | 絶縁膜           |    |

| 6                                       | メタルマスク        |    |

| 7                                       | 磁石            |    |

| 8 , 4 2                                 | 絶縁フィルム        | 20 |

| 9                                       | バリアメタル層       |    |

| 1 0                                     | C u           |    |

| 1 1                                     | バイト           |    |

| 1 2                                     | 貫通電極          |    |

| 2 0                                     | 台座            |    |

| 2 2                                     | 突起電極          |    |

| 2 3                                     | 半田バンプ         |    |

| 2 4                                     | L S I チップ     |    |

| 3 0                                     | ブロック          |    |

| 3 1                                     | L S I 素子      | 30 |

| 4 1 , 4 5 , 6 1                         | 薄膜電子回路        |    |

| 4 3                                     | 接着剤層          |    |

| 4 4                                     | 絶縁樹脂層         |    |

| 4 5 a , 4 5 b , 4 5 c                   | 接続部           |    |

| 5 1 , 6 3 , 6 4                         | 電極            |    |

| 1 1 1                                   | スタック型フラッシュメモリ |    |

【図1】

【図3】

【図2】

【図4】

【 図 5 】

【 四 6 】

【 四 7 】

【 図 8 】

【 囮 1 0 】

【 図 9 】

【図 1 1】

【図 1 2】

【図 1 3】

シリコンを電極の金属に達するまでドライエッティングする。

【図 1 4】

孔の径より小さな穴の空いたメタルマスクを載せ、RIEでピア底のSiO<sub>2</sub>を除去

【図15】

【図17】

【図16】

【 図 1 8 】

【図19】

【図20】

【図21】

【図22】

【図23】

【図25】

【図24】

【図26】

【図27】

【図28】

---

フロントページの続き

(56)参考文献 特開2004-014657(JP,A)

特開2002-064161(JP,A)

特開2000-323810(JP,A)

特開2005-039014(JP,A)

特開2001-060654(JP,A)

特開2000-299340(JP,A)

特開2000-031145(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3205

H01L 21/60

H01L 23/12

H01L 23/52