(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5566200号

(P5566200)

(45) 発行日 平成26年8月6日(2014.8.6)

(24) 登録日 平成26年6月27日(2014.6.27)

|              |            |

|--------------|------------|

| (51) Int.Cl. | F 1        |

| HO5K 3/46    | (2006.01)  |

| HO5K 3/28    | (2006.01)  |

| HO1L 23/12   | (2006.01)  |

| HO5K 3/34    | (2006.01)  |

|              | HO5K 3/46  |

|              | HO5K 3/28  |

|              | HO1L 23/12 |

|              | HO5K 3/34  |

|              | HO5K 3/34  |

請求項の数 7 (全 23 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2010-138906 (P2010-138906) |

| (22) 出願日  | 平成22年6月18日 (2010.6.18)       |

| (65) 公開番号 | 特開2012-4399 (P2012-4399A)    |

| (43) 公開日  | 平成24年1月5日 (2012.1.5)         |

| 審査請求日     | 平成25年4月2日 (2013.4.2)         |

|           |                                           |

|-----------|-------------------------------------------|

| (73) 特許権者 | 000190688<br>新光電気工業株式会社<br>長野県長野市小島田町80番地 |

| (74) 代理人  | 100091672<br>弁理士 岡本 啓三                    |

| (72) 発明者  | 近藤 人資<br>長野県長野市小島田町80番地 新光電気<br>工業株式会社内   |

| (72) 発明者  | 下平 朋幸<br>長野県長野市小島田町80番地 新光電気<br>工業株式会社内   |

| (72) 発明者  | 佐藤 雅子<br>長野県長野市小島田町80番地 新光電気<br>工業株式会社内   |

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

コア基板をもたないコアレスタイプの配線基板であって、一方の面側に最外層として形成され、黒色又は灰色を呈する第1絶縁層と、前記第1絶縁層から露出して形成された第1接続パッドと、他方の面側に最外層として形成され、黒色又は灰色を呈する樹脂層の厚み方向の中央部にガラスクロスが形成された第2絶縁層と、

前記第2絶縁層から露出して形成された第2接続パッドとを有し、前記第2絶縁層に曲面状の側壁面を有する接続ホールが形成され、前記接続ホールの底部に、表面に凹部が設けられた前記第2接続パッドが露出しており、

前記接続ホール内の前記樹脂層及びガラスクロスの側壁面と前記第2接続パッドの凹部の側面とは連続する同一面を構成しており、かつ

前記第1接続パッドの外面が前記第1絶縁層の外面から露出しており、前記第1接続パッドの側面と前記外面の反対面とが前記第1絶縁層に接していることを特徴とする配線基板。

## 【請求項 2】

前記接続ホールの上端の角部が丸みを帯びた面取り部となっていることを特徴とする請求項1に記載の配線基板。

## 【請求項 3】

前記第1接続パッド及び前記第2接続パッドのいずれか一方が半導体チップをフリップ

チップ接続するためのチップ接続用パッドであり、他方が外部接続端子を接続するための外部接続用パッドであり、

前記チップ接続用パッドの配列ピッチは前記外部接続用パッドの配列ピッチより狭いことを特徴とする請求項1又は2に記載の配線基板。

【請求項4】

接続パッドを備えた配線基板の上に、前記接続パッドを被覆する黒色又は灰色を呈する樹脂層の厚み方向の中央部にガラスクロスが形成された絶縁層を形成する工程と、

前記接続パッドの上に開口部が配置されたレジストを前記絶縁層の上に形成する工程と、

ウェットプラスト法によって、前記レジストの開口部を通して前記絶縁層に、前記接続パッドに到達する接続ホールを形成する工程とを有し、

前記接続ホールを形成する工程において、前記接続ホールの底部の前記接続パッドに凹部が形成され、かつ

前記接続ホール内の前記樹脂層及びガラスクロスの側壁面と前記接続パッドの凹部の側面とが連続する同一面となって形成されることを特徴とする配線基板の製造方法。

【請求項5】

前記接続パッドを備えた配線基板は、

支持体の上に下側接続パッドを形成する工程と、

前記下側接続パッドの上に黒色又は灰色を呈する下側絶縁層を形成する工程と、

前記下側絶縁層を加工して前記下側接続パッドに到達するビアホールを形成する工程と、

前記ビアホールを介して前記下側接続パッドに接続され、最上層として前記接続パッドを含むn層(nは1以上の整数)の配線層を前記下側絶縁層の上に形成する工程とを含む方法から得られ、

前記接続ホールを形成する工程の後に、前記支持体を除去する工程をさらに有することを特徴とする請求項4に記載の配線基板の製造方法。

【請求項6】

両面側の前記接続パッドのいずれか一方が半導体チップを接続するためのチップ接続用パッドであり、他方が外部接続端子を接続するための外部接続用パッドであり、前記チップ接続用パッドの配列ピッチは前記外部接続用パッドの配列ピッチより狭く設定されることを特徴とする請求項5に記載の配線基板の製造方法。

【請求項7】

前記接続ホールを形成する工程の後に、

前記レジストを除去する工程と、

前記絶縁層の表面及び前記接続ホール内をウエットプラスト法で研削することにより、前記接続ホールの上端の角部を丸みを帯びた面取り部とする工程とを有することを特徴とする請求項4に記載の配線基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は配線基板及びその製造方法に係り、さらに詳しくは、両面側に接続パッドとそれを露出させるように設けられた絶縁層とをそれぞれ備えた配線基板及びその製造方法に関する。

【背景技術】

【0002】

従来、半導体チップを実装するための多層配線基板がある。多層配線基板では、一方の面に半導体チップを実装するためのチップ接続用パッドが設けられ、他方の面に外部接続端子を接続するための外部接続用パッドが設けられている。

【0003】

特許文献1には、絶縁基板の表面に接続端子を接合するためのパッドが設けられたプリ

10

20

30

40

50

ント配線板において、絶縁基板の表面に接続パッドの外周部を含めて黒色のソルダレジストで被覆することにより、電子部品からの熱を効率よく放熱させることが記載されている。

#### 【0004】

特許文献2には、プリント配線板などに使用されるソルダレジストにおいて、優れた耐熱性と反りの少ないソルダレジストを採用する際に、解像性を上げるために露光量を増やす必要がある白色又は黒色のソルダレジストを併用することが有効であることが記載されている。

#### 【先行技術文献】

##### 【特許文献】

10

##### 【0005】

【特許文献1】特開2002-171050号公報

【特許文献2】特開2008-257044号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0006】

後述するように、関連技術の配線基板では、配線基板の最外には接続パッドが露出するようにしてソルダレジストが形成されており、一般的にソルダレジストは緑系の色を呈している。配線基板の接続パッドには半導体チップがはんだ付けによってフリップチップ接続される。

20

##### 【0007】

関連技術の配線基板では、半導体チップをフリップチップ接続する時などの加熱処理によってソルダレジストが酸化されて茶色に変色しやすい問題がある。ソルダレジストが変色すると見た目が悪いばかりではなく、その後のアセンブリ工程で画像認識による位置合わせを行う際に画像のコントラストが悪くなり、位置合わせが困難になる場合がある。

##### 【0008】

本発明は以上の課題を鑑みて創作されたものであり、最外層として形成される絶縁層の加熱処理による変色を防止できる配線基板及びその製造方法を提供することを目的とする。

30

#### 【課題を解決するための手段】

##### 【0009】

上記課題を解決するため、本発明は配線基板に係り、一方の面側に最外層として形成され、黒色又は灰色を呈する第1絶縁層と、前記第1絶縁層から露出して形成された第1接続パッドと、他方の面側に最外層として形成され、黒色又は灰色を呈する第2絶縁層と、前記第2絶縁層から露出して形成された第2接続パッドとを有し、前記第2絶縁層に曲面状の側壁面を有する接続ホールが形成され、前記接続ホールの底部に前記第2接続パッドが露出していることを特徴とする。

##### 【0010】

本発明の配線基板では、一方の面側に最外層として黒色又は灰色を呈する第1絶縁層が形成され、第1絶縁層から第1接続パッドが露出して形成されている。また、他方の面側に最外層として黒色又は灰色を呈する第2絶縁層が形成され、第2絶縁層から第2接続パッドが露出して形成されている。

40

##### 【0011】

そして、第2絶縁層に曲面状の側壁面を有する接続ホールが形成され、接続ホールの底部に第2接続パッドが露出している。接続ホールは第2絶縁層がウェットプラスト法によって研削されて形成されるため、曲面状の側壁面が得られる。

##### 【0012】

コア基板をもたないコアレス配線基板を採用する場合は、第1接続パッドの外面が第1絶縁層の外面から露出しており、第1接続パッドの側面と外面の反対面とが第1絶縁層に接している。

50

## 【0013】

あるいは、コア基板の両面側に配線層が形成された配線基板を採用する場合は、両面側の接続パッド上の黒色又は灰色の絶縁層にウェットプラスト法によって接続ホールが形成されて、両面側の接続パッドが接続ホールからそれぞれ露出している。

## 【0014】

このように、本発明の配線基板では両面側の絶縁層が黒色又は灰色を呈するので、半導体チップを実装する際などの加熱処理で絶縁層が変色することが防止される。これにより、半導体チップを実装した後に配線基板の色合いが変化して見た目が悪くなるといった不具合が解消される。

## 【0015】

さらに、半導体チップを実装した後に各種のアセンブリ工程があり、それらの工程では位置合わせを行う必要がある。本発明では、黒色又は灰色の絶縁層を使用することから接続パッド（金パッドや銅パッド）と絶縁層との間で光の反射率が大きく異なるので、位置合わせマークの画像のコントラストが良好となり、位置合わせを安定して行うことができる。

## 【0016】

また、第2接続パッドの上にウェットプラスト法で形成される接続ホールでは、その底面の第2接続パッドに凹部が設けられ、接続ホールの側壁面と第2接続パッドの凹部の側面とは連続する同一面を構成する。しかも、ウェットプラスト法を使用することにより、デスマニア処理が不要であるので、接続ホールの底部の接続パッドがエッチングされて食い込み部が形成されるおそれもない。

## 【0017】

従って、接続ホール内の第2接続パッドに無電解めっきによってニッケル／金めっき層などのコンタクト層を信頼性よく形成することができる。

## 【0018】

また、上記課題を解決するため、本発明は配線基板の製造方法に係り、接続パッドを備えた配線基板の上に、前記接続パッドを被覆する黒色又は灰色を呈する絶縁層を形成する工程と、前記接続パッドの上に開口部が配置されたレジストを前記絶縁層の上に形成する工程と、ウェットプラスト法によって、前記レジストの開口部を通して前記絶縁層に、前記接続パッドに到達する接続ホールを形成する工程とを有することを特徴とする。

## 【0019】

本発明の製造方法を使用することにより、上記した配線基板を容易に製造することができる。コアレス配線基板を製造する場合は、仮基板としての支持体の上にビルトアップ配線が形成された後に、支持体が除去される。

## 【発明の効果】

## 【0020】

以上説明したように、本発明の配線基板では、最外に設けられる絶縁層の加熱処理による変色を防止できる。

## 【図面の簡単な説明】

## 【0021】

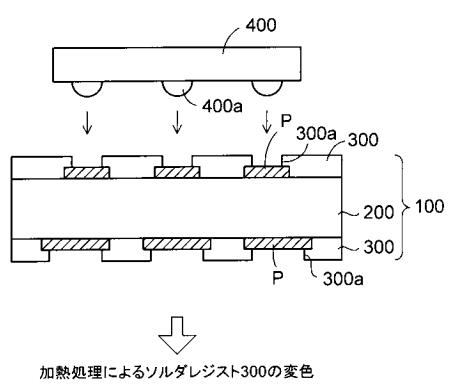

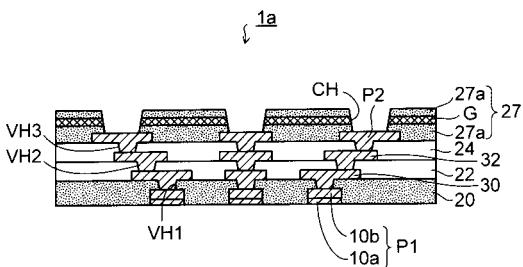

【図1】図1は関連技術の配線基板の問題点を説明するための断面図である。

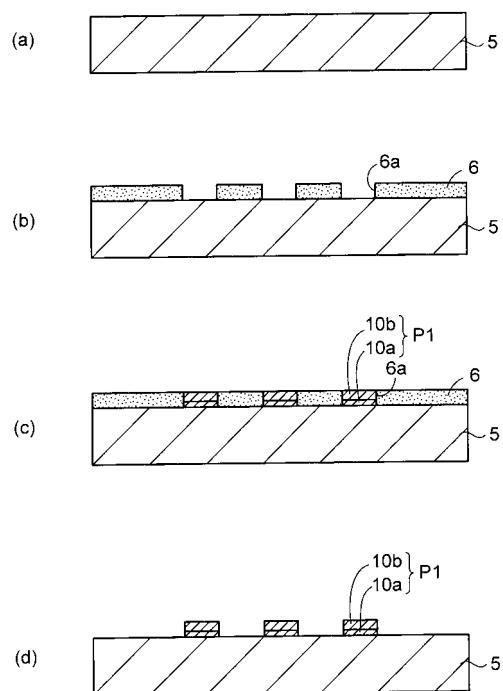

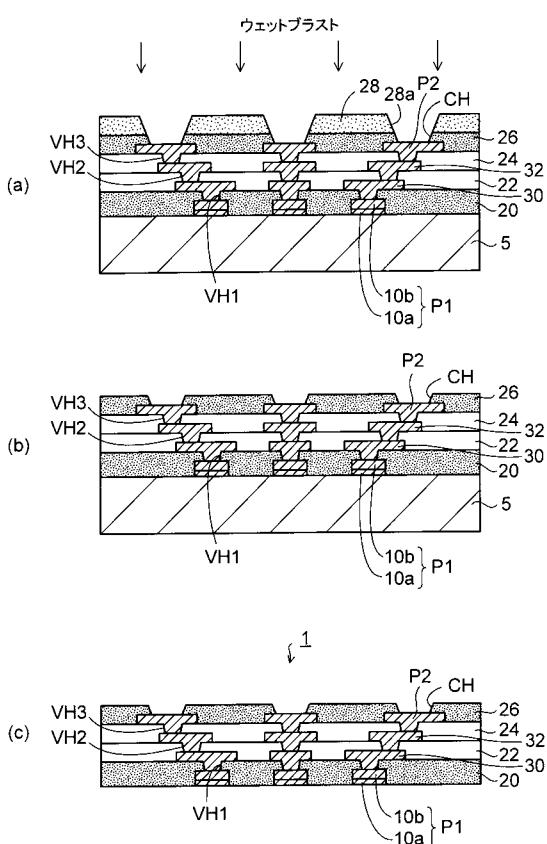

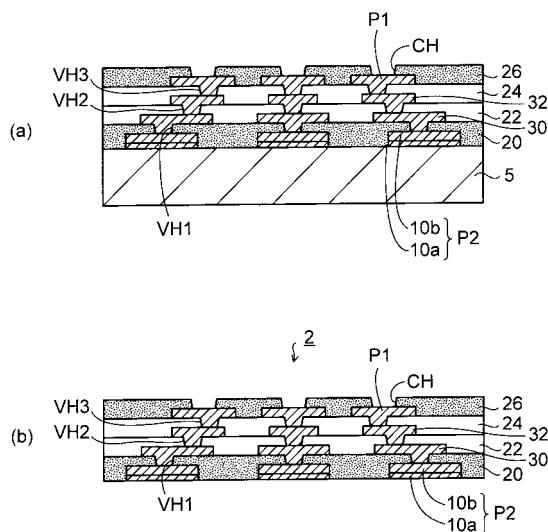

【図2】図2（a）～（d）は本発明の第1実施形態の配線基板の製造方法を示す断面図（その1）である。

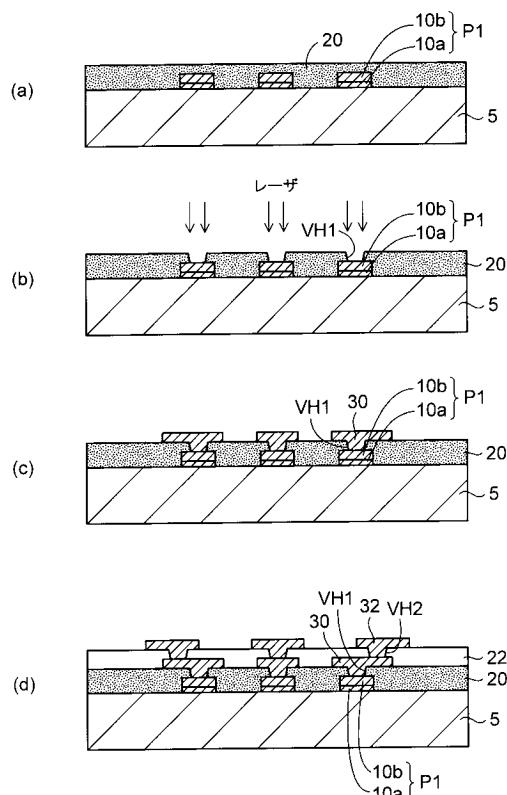

【図3】図3（a）～（d）は本発明の第1実施形態の配線基板の製造方法を示す断面図（その2）である。

【図4】図4（a）～（c）は本発明の第1実施形態の配線基板の製造方法を示す断面図（その3）である。

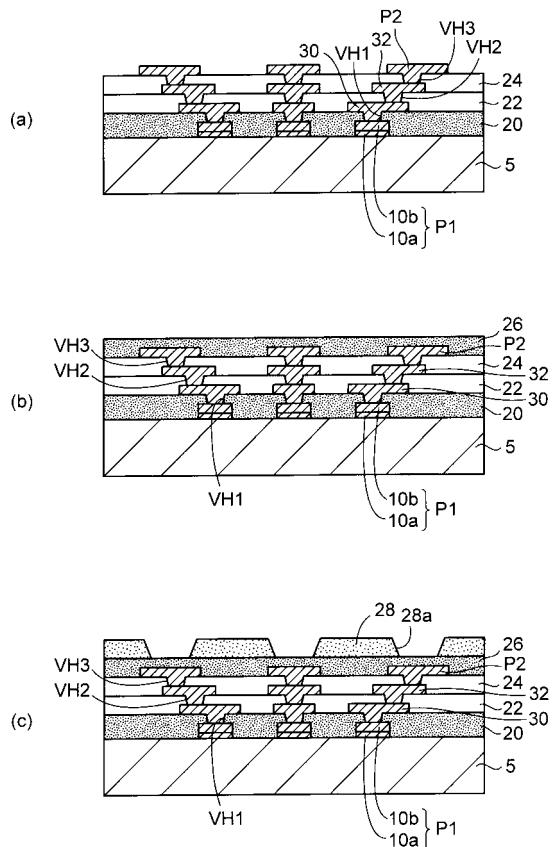

【図5】図5（a）～（c）は本発明の第1実施形態の配線基板の製造方法を示す断面図（その4）である。

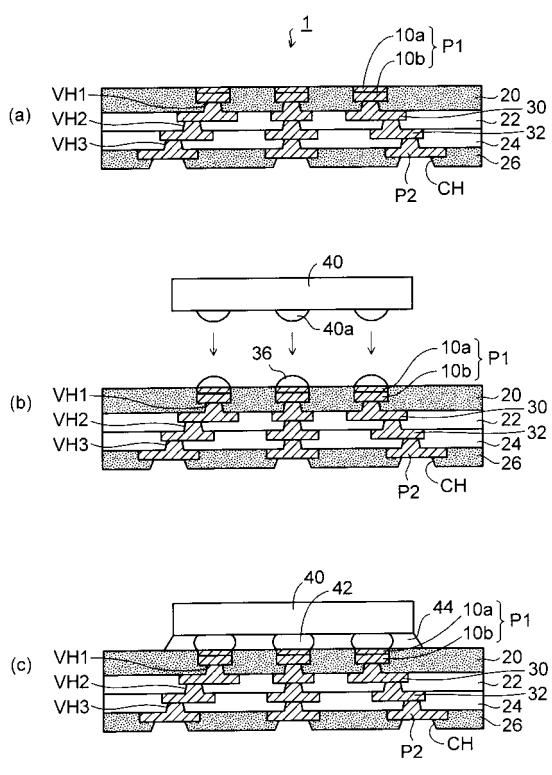

【図6】図6（a）～（c）は本発明の第1実施形態の配線基板に半導体チップを実装す

10

20

30

40

50

る方法を示す断面図である。

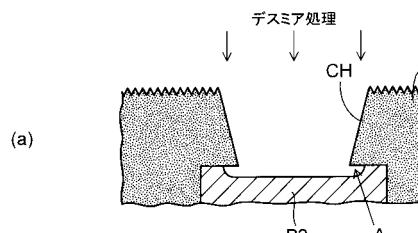

【図7】図7(a)及び(b)は本発明の第1実施形態の配線基板の製造方法において接続ホールを形成する際のウェットプラスト法の優位性を説明する断面図である。

【図8】図8は本発明の第1実施形態の変形例の配線基板を示す断面図である。

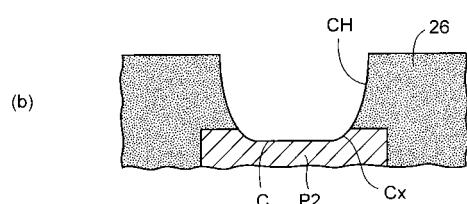

【図9】図9は本発明の第1実施形態の変形例の配線基板の製造方法において接続ホールを形成する際のウェットプラスト法の優位性を説明する断面図である。

【図10】図10(a)～(c)は本発明の第1実施形態の配線基板の製造方法においてはんだボールを振り込みやすくする接続ホールを得るための製法を示す断面図(その1)である。

【図11】図11(a)及び(b)は本発明の第1実施形態の配線基板の製造方法においてはんだボールを振り込みやすくする接続ホールを得るための製法を示す断面図(その2)である。

【図12】図12(a)及び(b)は本発明の第2実施形態の配線基板の製造方法を示す断面図である。

【図13】図13は本発明の第2実施形態の変形例の配線基板を示す断面図である。

【図14】図14は本発明の第2実施形態の配線基板に半導体チップが実装された様子を示す断面図である。

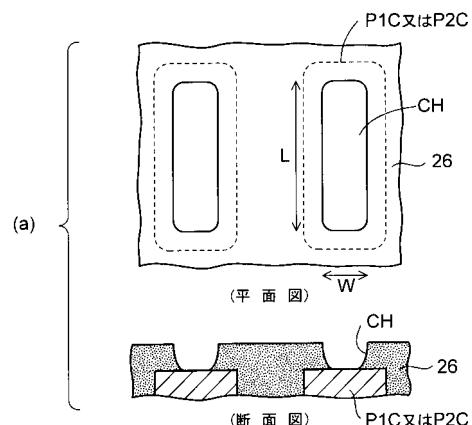

【図15】図15(a)及び(b)は本発明の第2実施形態の配線基板にチップキャパシタが実装される様子を示す平面図及び断面図である。

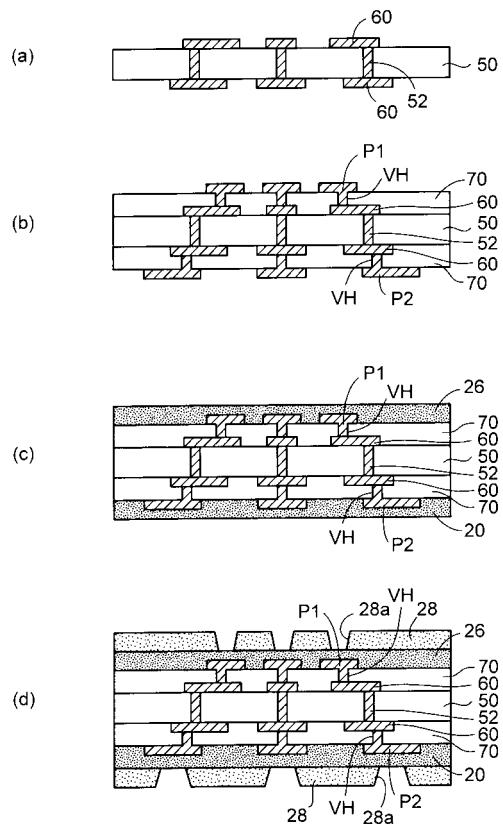

【図16】図16(a)～(d)は本発明の第3実施形態の配線基板の製造方法を示す断面図である。

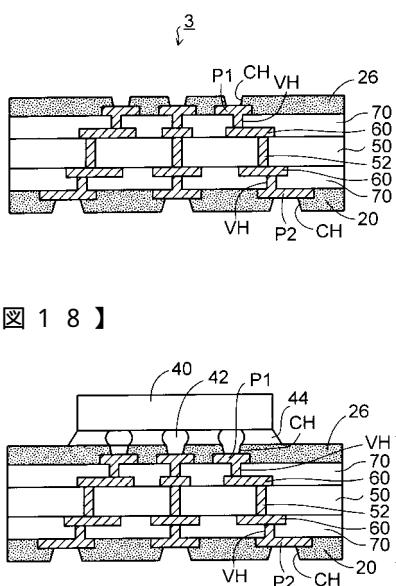

【図17】図17は本発明の第3実施形態の配線基板を示す断面図である。

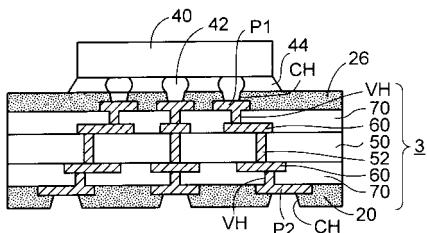

【図18】図18は本発明の第3実施形態の配線基板に半導体チップが実装された様子を示す断面図である。

#### 【発明を実施するための形態】

##### 【0022】

以下、本発明の実施の形態について、添付の図面を参照して説明する。

##### 【0023】

###### (関連技術)

本発明の実施形態を説明する前に、本発明に関連する関連技術について説明する。図1は関連技術の配線基板を示す断面図である。

##### 【0024】

図1に示すように、関連技術の配線基板100では、多層配線部200の両面側に接続パッドPをそれぞれ備えており、両面側に接続パッドPを露出させる開口部300aが設けられたソルダレジスト300がそれぞれ形成されている。一般的に、ソルダレジスト300は緑系の色を呈している。

##### 【0025】

そして、半導体チップ400のバンプ電極400aが配線基板100の接続パッドPにはんだ付けによってフリップチップ接続される。このとき、はんだ付けの加熱処理によってソルダレジスト300が酸化して茶色に変色しやすい問題がある。

##### 【0026】

半導体チップ400が配線基板100に実装された後にも、半導体チップ400と配線基板100との間に充填されるアンダーフィル樹脂の加熱による硬化などの各種の加熱処理を行う工程があり、加熱処理を繰り返すにつれて変色が顕著になる傾向がある。

##### 【0027】

ソルダレジスト300が変色すると見た目が悪くなるばかりではなく、その後のアセンブリ工程(補強板や放熱板の取り付けなど)で画像認識による位置合わせを行う際に画像のコントラストが悪くなり、位置合わせが困難になる場合がある。

##### 【0028】

本願発明者は以上の問題点について鋭意研究した結果、ソルダレジストの色を黒又は灰

10

20

30

40

50

色の無彩色にすることにより、加熱処理による変色を防止できることを見出した。

【0029】

(第1実施の形態)

図2～図5は本発明の第1実施形態の配線基板の製造方法を示す断面図、図6は同じく配線基板に半導体チップを実装する方法を示す断面図である。

【0030】

第1実施形態では、コア基板をもたないコアレス配線基板において両面側の絶縁層(ソルダレジスト)の色を黒色又は灰色の無彩色にする形態について製造方法を参照しながら説明する。

【0031】

図2(a)に示すように、まず、銅(Cu)などの金属板又は金属箔からなる支持体5を用意する。支持体5は仮の基板であり、支持体5の上にビルドアップ配線が形成された後に除去される。

【0032】

次いで、図2(b)に示すように、支持体5の上に、チップ接続用パッドが配置される部分に開口部6aが設けられためっきレジスト6を形成する。さらに、図2(c)に示すように、支持体5をめっき給電経路に利用する電解めっきにより、めっきレジスト6の開口部6a内の支持体5の上に金(Au)層10a及びニッケル(Ni)層10bを順に形成する。その後に、めっきレジスト6が除去される。

【0033】

これにより、図2(d)に示すように、Au層10a及びNi層10bから構成されるチップ接続用パッドP1(第1接続パッド(又は下側接続パッド))が支持体5の上に形成される。

【0034】

あるいは、支持体5上に下から順に、金(Au)層/ニッケル(Ni)層/銅(Cu)層、金(Au)層/パラジウム(Pd)層/ニッケル(Ni)層、又は金(Au)層/パラジウム(Pd)層/ニッケル(Ni)層/銅(Cu)層などの各種の積層膜を形成して、チップ接続用パッドP1としてもよい。

【0035】

又は、チップ接続用パッドP1として、支持体5上に下から順に、ニッケル(Ni)層(犠牲層)/銅(Cu)層を形成してもよい。この場合は、後述するように支持体5を除去した後に、ニッケル(Ni)層(犠牲層)がニッケルを選択的にエッチングできるエッチング液で除去され、チップ接続用パッドP1が銅(Cu)層のみから形成される。

【0036】

チップ接続用パッドP1は半導体チップが接続される電極であり、例えば、平面視して円形に形成され、その径は50～100μmであり、その配列ピッチは90～150μmに設定される。

【0037】

次いで、図3(a)に示すように、支持体5の上にチップ接続用パッドP1を被覆する第1黒色絶縁層20(黒色又は灰色を呈する下側絶縁層)を形成する。第1黒色絶縁層20を例示するが、灰色もしくは黒に近い灰色などでもよく、灰色～黒色の間の無彩色を呈する絶縁層を形成すればよい。第1黒色絶縁層20はソルダレジストとして機能する。

【0038】

黒色又は灰色の無彩色の絶縁層としては、波長が380～780nmの可視光線の光吸収率が60%以上(好適には70%以上)から100%のものが使用される。

【0039】

光吸収率が60%以上から70%未満で灰色(又は暗灰色)に視認され、光吸収率が70%以上で黒色に視認される。

【0040】

黒色又は灰色の絶縁層は、エポキシやポリイミドなどの樹脂に以下の顔料のいずれか又

10

20

30

40

50

はそれらを組わせた顔料を含有させることにより得られる。そのような顔料としては、カーボンブラック系、黒鉛系、酸化鉄系、アンスラキノン系、酸化コバルト系、酸化銅系、マンガン系、酸化アンチモン系、酸化ニッケル系、又はペリレン系などがある。

【0041】

樹脂中への顔料の含有量は、0.01～20質量%、好適には0.1～10質量%である。

【0042】

第1黒色絶縁層20は、例えば、エポキシやポリイミドなどの熱硬化性樹脂に黒色の顔料を含有させた樹脂フィルムを積層し、真空プレス装置などで加熱・加圧することにより得られる。あるいは、黒色の顔料を含有させたエポキシやポリイミドなどの液状の熱硬化性樹脂を塗布し、加熱によって硬化させてもよい。10

【0043】

第1黒色絶縁層20は光を吸収しやすい特性を有するため、フォトリソグラフィで精度よくホールパターンを形成することは困難な場合が多い。このため、第1黒色絶縁層20は非感光性の樹脂から形成され、開口部を形成する際は、レーザやウェットblast法によって加工される。

【0044】

次いで、図3(b)に示すように、第1黒色絶縁層20をレーザで加工することにより、チップ接続用パッドP1に到達する第1ビアホールVH1を形成する。続いて、図3(c)に示すように、第1ビアホールVH1(ビア導体)を介してチップ接続用パッドP1に接続される第1配線層30を第1黒色絶縁層20の上に形成する。20

【0045】

第1配線層30は例えばセミアディティブ法によって形成される。詳しく説明すると、まず、第1黒色絶縁層20上及び第1ビアホールVH1内に銅などからなるシード層(不図示)を無電解めっきやスパッタ法により形成する。続いて、シード層の上に、第1配線層30が配置される部分に開口部が設けられためっきレジスト(不図示)を形成する。

【0046】

さらに、シード層をめっき給電経路に利用する電解めっきにより、めっきレジストの開口部に銅などの金属パターン層(不図示)を形成する。次いで、めっきレジストを除去した後に、金属パターン層をマスクにしてシード層をエッチングすることにより、シード層及び金属パターン層により構成される第1配線層30が得られる。30

【0047】

次いで、図3(d)に示すように、第1配線層30の上に第1層間絶縁層22を形成した後に、第1層間絶縁層22をレーザで加工することにより第1配線層30に到達する第2ビアホールVH2を形成する。第1層間絶縁層22は黒色又は灰色に着色されている必要はなく、通常のエポキシ樹脂又はポリイミド樹脂などから形成される。

【0048】

さらに、第1配線層30の形成方法と同様な方法により、第2ビアホールVH2(ビア導体)を介して第1配線層30に接続される第2配線層32を第1層間絶縁層22の上に形成する。40

【0049】

続いて、図4(a)に示すように、第2配線層32の上に第2層間絶縁層24を形成した後に、第2層間絶縁層24をレーザで加工することにより第2配線層32に到達する第3ビアホールVH3を形成する。第2層間絶縁層24は、第1層間絶縁層22と同様に、黒色又は灰色に着色されている必要はなく、通常のエポキシ樹脂又はポリイミド樹脂などから形成される。

【0050】

上記した第1層間絶縁層22及び第2層間絶縁層24は、樹脂フィルムを積層し、真空プレス装置などで加熱・加圧することによって形成される。

【0051】

10

20

30

40

50

さらに、第1配線層30の形成方法と同様な方法により、第3ビアホールVH3(ビア導体)を介して第2配線層32に接続される外部接続用パッドP2(第2接続パッド)を第3配線層として第2層間絶縁層24の上に形成する。外部接続用パッドP2は各第3ビアホールVH3の上に島状に配置されていてもよいし、あるいは第3ビアホールVH3から外側に延在する配線の一端に繋がっていてもよい。

#### 【0052】

外部接続用パッドP2は外部接続端子が接続される電極であり、例えば、平面視して円形に形成され、その径は350~550μmであり、その配列ピッチは600~900μmに設定される。このようにして、チップ接続用パッドP1の比較的狭いピッチが、実装基板(マザーボードなど)の接続部に対応するように外部接続用パッドP2の比較的広いピッチに第1、第2配線層30, 32を介してピッチ変換される。

#### 【0053】

以上により、第1ビアホールVH1(ビア導体)を介してチップ接続用パッドP1に接続されて、最上層として外部接続用パッドP2(第2接続パッド)を含むビルドアップ配線が第1黒色絶縁層20の上に形成される。

#### 【0054】

本実施形態では、チップ接続用パッドP1の上に3層(第1、第2配線層30, 32、外部接続用パッドP2)のビルドアップ配線を形成しているが、n層(nは1以上の整数)で任意の積層数で形成することができる。

#### 【0055】

次いで、図4(b)に示すように、第2層間絶縁層24の上に外部接続用パッドP2を被覆する第2黒色絶縁層26を形成する。第2黒色絶縁層26は、前述した第1黒色絶縁層20の形成方法と同様な方法で形成され、黒色以外に灰色であってもよい。

#### 【0056】

続いて、図4(c)に示すように、第2黒色絶縁層26の上に、外部接続用パッドP2の上に開口部28aが設けられたドライフィルムレジストなどのレジスト28を形成する。

#### 【0057】

さらに、図5(a)に示すように、ウェットプラスト法により、レジスト28の開口部28aを通して第2黒色絶縁層26を研削して除去することにより、外部接続用パッドP2に到達する接続ホールCH(開口部)を形成する。接続ホールCHは、平面視して円形の開口部として形成される。

#### 【0058】

ウェットプラスト処理では、アルミナ砥粒やシリカ砥粒からなる研磨剤を水などの溶媒に分散させ、対象物(黒色絶縁層)に高圧で噴射して研削が行われる。例えば、粒径が5~20μmのアルミナ砥粒やシリカ砥粒の研磨剤を14v01%程度の濃度で水に分散させ、0.25MPa程度の圧力で対象物(黒色絶縁層)に噴射して研削が行われる。

#### 【0059】

その後に、図5(b)に示すように、レジスト28が除去される。さらに、必要に応じて、接続ホールCH内の外部接続用パッドP2に無電解めっきによってNi層/Au層を順に形成するなどしてコンタクト層(不図示)を形成する。コンタクト層として、下から順に、ニッケル(Ni)層/パラジウム(Pd)層/金(Au)層を積層して形成してもよく、めっきによって形成される各種の積層膜を採用してもよい。

#### 【0060】

次いで、図5(c)に示すように、図5(b)の構造体から支持体5をウェットエッティングにより除去する。支持体5が銅からなる場合は、塩化第二銅水溶液などの銅のエッチャントが使用される。

#### 【0061】

支持体5は、チップ接続用パッドP1(最下がAu層10a)及び第1黒色絶縁層20に対して選択的にエッティングされて除去される。

10

20

30

40

50

## 【0062】

以上により、第1実施形態の配線基板1が得られる。図5(c)に示すように、第1実施形態の配線基板1では、最下の第1黒色絶縁層20にチップ接続用パッドP1(第1接続パッド)が埋設されており、チップ接続用パッドP1の外面と第1黒色絶縁層20の外面とが同一面を構成している。

## 【0063】

チップ接続用パッドP1上の第1黒色絶縁層20には第1ビアホールVH1が形成されており、第1黒色絶縁層20の上には第1ビアホールVH1(ビア導体)を介してチップ接続用パッドP1に接続される第1配線層30が形成されている。

## 【0064】

第1配線層30の上にはその接続部上に第2ビアホールVH2が設けられた第1層間絶縁層22が形成されている。第1層間絶縁層22の上には第2ビアホールVH2(ビア導体)を介して第1配線層30に接続される第2配線層32が形成されている。

## 【0065】

第2配線層32の上にはその接続部上に第3ビアホールVH3が設けられた第2層間絶縁層24が形成されている。第2層間絶縁層24の上には第3ビアホールVH3(ビア導体)を介して第2配線層32に接続される外部接続用パッドP2(第2接続パッド)が形成されている。

さらに、第2層間絶縁層24の上には外部接続用パッドP2の上に接続ホールCHが設けられた第2黒色絶縁層26が形成されている。

## 【0066】

第1実施形態の配線基板1は、コア基板をもたないコアレス配線基板であり、チップ接続用パッドP1に3層のビルトアップ配線(第1、第2配線層30, 32、外部接続用パッドP2)が接続されている。両面側の各最外にはソルダレジストとして第1黒色絶縁層20及び第2黒色絶縁層26がそれぞれ形成されている。

## 【0067】

チップ接続用パッドP1は、その外面が第1黒色絶縁層20の外面と同一面を構成することで第1黒色絶縁層20から露出している。チップ接続用パッドP1の側面とビア接続面とが第1黒色絶縁層20に接し、外面(ビア接続面と反対面)が第1黒色絶縁層20から露出している。

## 【0068】

あるいは、前述したように、図2(c)の工程で、チップ接続用パッドP1としてニッケル(Ni)層(犠牲層)/銅(Cu)層を形成し、支持体5を除去した後に、ニッケル層(犠牲層)を除去する場合は、チップ接続用パッドP1が銅層のみから形成される。

## 【0069】

この場合は、チップ接続用パッドP1の外面が第1黒色絶縁層20の外面から凹んだ位置に配置される。つまり、第1黒色絶縁層20に形成された凹部の底部にチップ接続用パッドP1が配置される。

## 【0070】

この場合においても、チップ接続用パッドP1の側面とビア接続面とが第1黒色絶縁層20に接し、外面(ビア接続面と反対面)が第1黒色絶縁層20から露出した状態となる。

## 【0071】

また、外部接続用パッドP2の上には、ウェットプラスト法によって第2黒色絶縁層26に形成された接続ホールCHが配置されている。外部接続用パッドP2の周縁部は第2黒色絶縁層26で被覆されており、外部接続用パッドP2の中央部が接続ホールCHから露出している。

## 【0072】

また、第1黒色絶縁層20及び第1、第2層間絶縁層22, 24に形成された第1～第3ビアホールVH1, VH2, VH3は、第2黒色絶縁層26側に開口されている。これ

に加えて、第1～第3ビアホールVH1, VH2, VH3は、チップ接続用パッドP1及び第1、第2配線層30, 32の表面によって底面が構成され、先端の開口面積が底面面積より大きい円錐台状の凹部となって形成されている。そして、第1～第3ビアホールVH1, VH2, VH3の中にビア導体が形成（充填）されている。

【0073】

なお、接続パッド（チップ接続用パッドP1及び外部接続用パッドP2）が黒色絶縁層20, 26から露出していることは、各接続パッドの表面が黒色絶縁層20, 26で被覆されていないことを意味する。従って、接続パッド（チップ接続用パッドP1及び外部接続用パッドP2）が半導体チップや外部接続端子で覆われている構造も含む。

【0074】

また、本実施形態では、両面側の最外の絶縁層のみを黒色又は灰色にしたが、内部の絶縁層（図5(c)）では第1、第2層間絶縁層22, 24においても同様に黒色又は灰色の絶縁層にしてもよい。つまり、配線基板の絶縁層の全層が黒色又は灰色を呈するようにしてもよい。

【0075】

次に、第1実施形態の配線基板1に半導体チップを実装する方法について説明する。

【0076】

図6(a)に示すように、図5(c)の配線基板1を上下反転させてチップ接続用パッドP1を上側に向けた状態とする。

【0077】

次いで、図6(b)に示すように、配線基板1のチップ接続用パッドP1の上にはんだ36を塗布する。さらに、半導体チップ40の接続電極40aを配線基板1のチップ接続用パッドP1上のはんだ36に配置し、230～270の温度でリフロー加熱してはんだ付けを行う。

【0078】

これにより、図6(c)に示すように、半導体チップ40がバンプ電極42によって配線基板1のチップ接続用パッドP1にフリップチップ接続される。その後に、半導体チップ40の下側の隙間にアンダーフィル樹脂44が充填される。これにより、半導体パッケージが構成される。

【0079】

BGA型の半導体パッケージを構成する場合は、半導体チップ40を実装する前又は後に、外部接続用パッドP2に外部接続端子としてはんだボールが接続される。また、PGA型パッケージを構成する場合は、半導体チップ40を実装する前又は後に、外部接続用パッドP2に外部接続端子として接続ピンが接続される。あるいは、LGA型パッケージを構成する場合は、外部接続用パッドP2自体が外部接続端子として使用される。

【0080】

また、半導体チップ40を実装する前に、チップキャパシタを配線基板1に実装してもよい。この場合は、配線基板1にチップ接続用パッドP1又は外部接続用パッドP2を形成する際に、それらと同一層からなるチップキャパシタ搭載用のキャパシタ接続用パッドが形成される。

【0081】

本願発明者は、灰色～黒色の絶縁層を実際に260程度の温度で加熱処理して色が変化するかどうか目視検査を行った。その結果によれば、加熱処理を10回繰り返しても灰色～黒色の絶縁層の色はほとんど変化しなかった。このように、灰色～黒色の絶縁層は加熱処理によって酸化するとしても変色しにくい特性がある。

【0082】

従って、上記した図6(b)及び(c)において、配線基板1に半導体チップ40をフリップチップ接続する工程で配線基板1が加熱されるとしても、両面側の第1、第2黒色絶縁層20, 26の色は黒色のままでほとんど変色しない。また、上記したアンダーフィル樹脂44を加熱して硬化させる際にも第1、第2黒色絶縁層20, 26に変色は発生し

10

20

30

40

50

ない。

#### 【0083】

これにより、半導体チップ40を実装した後に配線基板1の色合いが変化して見た目が悪くなるといった不具合が解消される。しかも、半導体チップ40を実装した後に、さらに加熱処理を伴う工程を遂行する場合であっても第1、第2黒色絶縁層20, 26の色はほとんど変化しないことが分かる。

#### 【0084】

また、半導体チップ40を実装した後に、位置合わせを必要とするアセンブリ工程（補強板や放熱板を取り付ける工程など）が行われる場合が多い。位置合わせは、配線基板1に形成された位置合わせマークを画像認識することに基づいて行われる。位置合わせマークは接続ホールCHと大きさは異なる場合があるが同一の構造である。

10

#### 【0085】

このとき、本実施形態と違って、ソルダレジストが茶色に変色していると画像のコントラストが悪くなり、位置合わせが困難になる場合がある。

#### 【0086】

本実施形態では、ソルダレジストとして黒色絶縁層を使用することから接続パッド（金パッドや銅パッド）と黒色絶縁層との間で光の反射率が大きく異なるので、位置合わせマークの画像のコントラストが良好となり、位置合わせを安定して行うことができる。これにより、補強板や放熱板の取り付け工程などのアセンブリ工程を安定して遂行することができる。

20

#### 【0087】

また、前述した配線基板1の製造工程において、第1、第2黒色絶縁層20, 26や第1、第2層間絶縁層22, 24を積層するたびに、加熱処理が行われる。さらには、第1、第2配線層30, 32の形成工程においてもレジスト形成時に加熱処理が行われる。よって、特に第1黒色絶縁層20には複数回の加熱処理が施されることになるが、第1黒色絶縁層20に変色は生じない。

#### 【0088】

また、チップ接続用パッドP1に半導体チップ40を実装したり、外部接続用パッドP2にはんだボールなどの外部接続端子を接合する際に、画像認識による位置決めが行われる。このとき、接続パッド（チップ接続用パッドP1及び外部接続用パッドP2）と黒色絶縁層20, 26とのコントラストが良好になり、精度よく安定して位置決めを行うことができる。

30

#### 【0089】

さらには、接続パッド（チップ接続用パッドP1及び外部接続用パッドP2）の表面損傷や異物付着などの表面状態を検査する際ににおいても、接続パッド（チップ接続用パッドP1及び外部接続用パッドP2）と黒色絶縁層20, 26とのコントラストが良好になり、精度よく安定して検査を行うことができる。

#### 【0090】

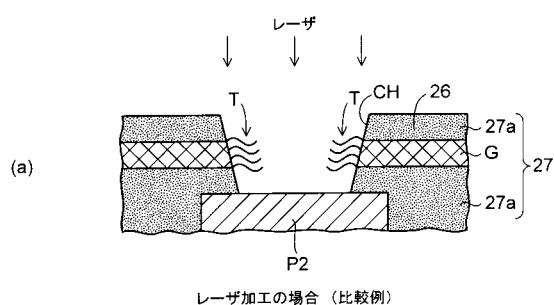

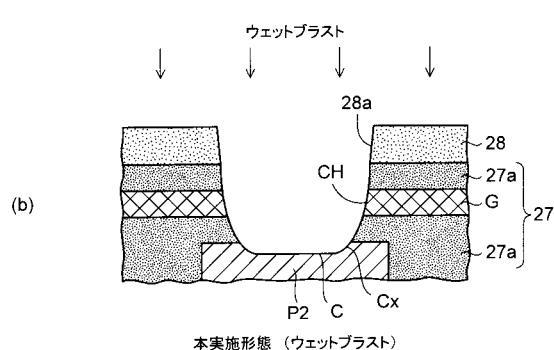

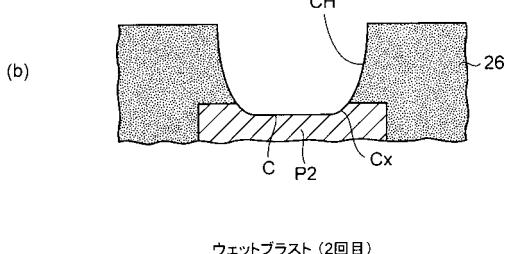

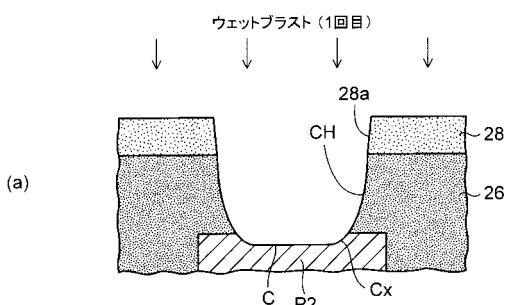

次に、ウェットブラスト法によって第2黒色絶縁層26を研削して接続ホールCHを形成する工程（前述した図5（a）の工程）についてさらに詳しく説明する。

40

#### 【0091】

一般的に、ソルダレジストに接続ホール（開口部）を形成する方法としては、感光性のソルダレジストをフォトリソグラフィでパターン化する方法、又は非感光性のソルダレジストをレーザで加工する方法などがある。

#### 【0092】

前述したように、第2黒色絶縁層26は光を吸収しやすい特性を有するため、感光性樹脂で黒色絶縁層を形成する場合、フォトリソグラフィで精度よくホールパターンを形成することは困難な場合が多い。

#### 【0093】

また、図7（a）に示すように、レーザで第2黒色絶縁層26を加工して接続ホールCH

50

Hを形成する場合は、レーザ加工の後に接続ホールCH内に樹脂スミアが発生するので、過マンガン酸法などのデスマニア処理によって樹脂スミアを除去する必要ある。

【0094】

このとき、デスマニア処理によって接続ホールCHの底部の外部接続用パッドP2(銅)が等方的にエッティングされるため、接続ホールCH近傍の第2黒色絶縁層26の下に食い込み部Aが生じる。

【0095】

このため、外部接続用パッドP2上に無電解めっきによってコンタクト層(Ni/Au層など)を形成する際に、食い込み部Aにボイドが発生しやすくなるため、外部接続用パッドP2に外部接続端子を設ける際に電気接続の信頼性が問題になるおそれがある。

10

【0096】

しかも、デスマニア処理によって第2黒色絶縁層26の表面がエッティングされて凹凸が形成されてしまう(表面粗さ(Ra):500nm程度)。第2黒色絶縁層26の表面に凹凸が形成されると、外部接続用パッドP2に無電解めっきによってコンタクト層(Ni/Au層など)を形成する際に、めっきの選択成長が損なわれ、第2黒色絶縁層26の上にもめっきが析出する場合がある。

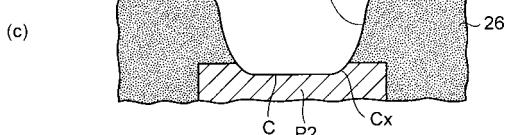

【0097】

これに対して、図7(b)に示すように、ウェットプラスト法によって第2黒色絶縁層26に接続ホールCHを形成すると、第2黒色絶縁層26の研削が終了した後に、外部接続用パッドP2(銅)が0.4~5μm程度除去されて微小な凹部Cが設けられる。接続ホールCHの側壁面と外部接続用パッドP2の凹部Cの側面Cxとは、それらの境界部で不連続面が形成されることなく、連続した同一面を構成して形成される。

20

【0098】

接続ホールCHは、外部接続用パッドP2(第2接続パッド)の外周側方向に突出又は湾曲する曲面状の側壁面を有して形成され、かつ、第2黒色絶縁層26の外面に開口する開口部の面積が、底面の面積より大きくなって形成される。接続ホールCHの曲面状の側壁面と外部接続用パッドP2の凹部Cの曲面状の側面Cxとによって連続した同一の曲面が構成される。

【0099】

また、接続ホールCHの側壁面の断面形状は、外部接続用パッドP2の外周方向に突出する円弧状となっている。

30

【0100】

そして、ウェットプラスト法で第2黒色絶縁層26を除去した後に、水洗を行うだけで、外部接続用パッドP2の表面をクリーンな状態で露出させることができる。

【0101】

つまり、ウェットプラスト法を使用することによりデスマニア処理を行う必要がないので、接続ホールCHの底部に外部接続用パッドP2の食い込み部Aが発生するおそれがない。

【0102】

また、デスマニア処理を省略することで、第2黒色絶縁層26の表面に凹凸が形成されず平滑な状態(表面粗さ(Ra):10~150nm以下)が維持される。このため、外部接続用パッドP2上に無電解めっきによってコンタクト層(Ni/Auめっき層など)を形成する際に、めっきの選択成長が損なわれるおそれもない。

40

【0103】

また、ウェットプラスト法で形成された接続ホールCHの側壁面は表面粗さ(Ra)が150~500nmとなって適度に粗化させるため、はんだ接合する際にはんだが密着性よく形成される利点もある。

【0104】

このように、ウェットプラスト法を使用することにより接続ホールCHの内面を連続面として形成できると共に、デスマニア処理を省略できるので、外部接続用パッドP2に食い

50

込み部 A が発生したり、第 2 黒色絶縁層 2 6 の表面に不要な凹凸が形成されるおそれがない。従って、外部接続用パッド P 2 に無電解めっきによってコンタクト層 ( Ni / Au めっき層など) が信頼性よく形成されるようになる。

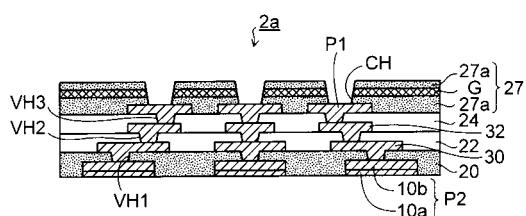

【 0 1 0 5 】

図 8 には第 1 実施形態の変形例の配線基板 1 a が示されている。図 8 に示すように、変形例の配線基板 1 a では、前述した図 5 ( c ) の配線基板 1 において、第 2 黒色絶縁層 2 6 の代わりに、黒色樹脂 2 7 a の厚み方向の中央部にガラスクロス G が形成されたガラスクロス含有黒色絶縁層 2 7 が使用される。

【 0 1 0 6 】

ガラスクロス含有黒色絶縁層 2 7 は、ガラスクロス G に黒色樹脂 2 7 a を含浸させてプリプレグを構成し、プリプレグを外部接続用パッド P 2 上に貼付した後に、加熱処理して黒色樹脂 2 7 a を硬化させればよい。

10

【 0 1 0 7 】

ガラスクロス含有黒色絶縁層 2 7 を使用することにより、コア基板をもたない配線基板 1 a の剛性を強化できると共に、配線基板 1 a の反りの発生を防止することができる。

【 0 1 0 8 】

図 8 において、第 2 黒色絶縁層 2 6 の代わりにガラスクロス含有黒色絶縁層 2 7 を使用すること以外は、前述した図 5 ( c ) の配線基板 1 と同一である。

【 0 1 0 9 】

ガラスクロス含有黒色絶縁層 2 7 を使用する場合においても接続ホール C H を形成する際にウェットプラスト法が適している。

20

【 0 1 1 0 】

図 9 ( a ) にはレーザでガラスクロス含有黒色絶縁層 2 7 を加工して接続ホール C H を形成した様子が示されている。この場合、黒色樹脂 2 7 a とガラスクロス G とのレーザでの加工性の違いから、接続ホール C H の側壁面から内側にガラスクロス G の突出部 T が形成される。また、デスマニア処理を行うことでガラスクロス G の突出が顕著になる。

【 0 1 1 1 】

ガラスクロス G が接続ホール C H の側壁面から突出していると、外部接続用パッド P 2 上に無電解めっきによってコンタクト層 ( Ni / Au めっき層など) を形成する際に、接続ホール C H の底部までめっき液が十分に供給されないため、ガラスクロス G の突出部 T の下側にめっきが上手く施されなくなる。また、外部接続用パッド P 2 に外部接続端子としてはんだボールやピン端子を取り付ける際に取り付けが困難になる問題もある。

30

【 0 1 1 2 】

しかしながら、図 9 ( b ) に示すように、本実施形態では、ウェットプラスト法を使用することにより、ガラスクロス G と黒色樹脂 2 7 a とを同等に研削して加工することができる。このため、ガラスクロス G の研削面を黒色樹脂 2 7 a の研削面と同一面にすることができる、接続ホール C H 内にガラスクロス G の突出部 T が形成されるおそれはない。

【 0 1 1 3 】

従って、ガラスクロス含有黒色絶縁層 2 7 を使用する場合であっても、正常な接続ホール C H を容易に形成できるので、外部接続用パッド P 2 に無電解めっきによってコンタクト層 ( Ni / Au めっき層など) を信頼性よく形成することができる。

40

【 0 1 1 4 】

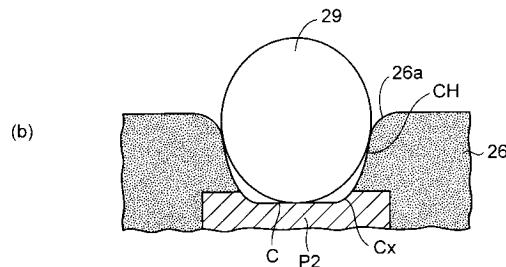

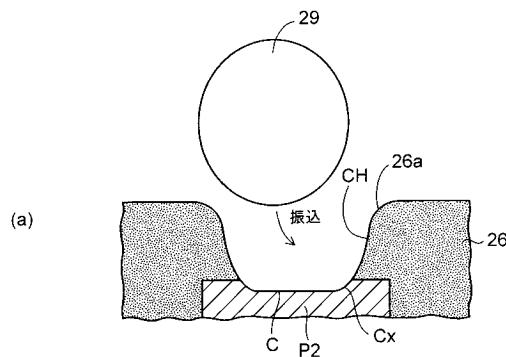

次に、前述した本実施形態の配線基板 1 , 1 a において、外部接続端子となるはんだボールやリードピンを接続ホール C H に振込治具を使用して振り込む際に有利な構造を形成する方法について説明する。

【 0 1 1 5 】

図 10 ( a ) に示すように、まず、前述した図 5 ( a ) で説明したように、ウェットプラスト法によってレジスト 2 8 の開口部 2 8 a を通して第 2 黒色絶縁層 2 6 を研削することにより、外部接続用パッド P 2 に到達する接続ホール C H を形成する ( 1 回目のウェットプラスト処理 )。その後に、図 10 ( b ) に示すように、レジスト 2 8 を除去する。

50

## 【0116】

さらに、図10(c)に示すように、第2黒色絶縁層26の表面及び接続ホールCH内をウェットブラスト法によって研削する(2回目のウェットブラスト処理)。このとき、第2黒色絶縁層26の表面が0.5~4μm程度で除去される条件に設定される。

## 【0117】

これにより、接続ホールCHの上端の角部が丸みを帯びた形状に加工されて面取り部26a(R面とも呼ばれる)となる。

## 【0118】

図11(a)及び(b)に示すように、接続ホールCHの上部の角部を面取り部26aとすることにより、振込治具(不図示)からはんだボール29を接続ホールCHに振り込む際に、多少位置ずれが生じた場合であっても接続ホールCH内に容易にはんだボール29が振り込まれるようになる。また、リードピンを接続ホールCHに振り込んで取り付ける際にも振り込みやすくなる。

## 【0119】

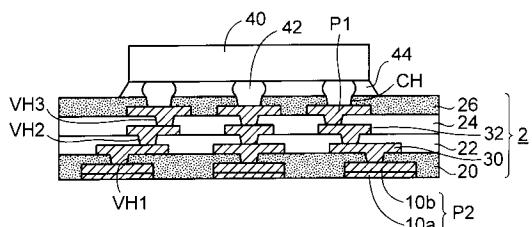

(第2の実施の形態)

図12は本発明の第2実施形態の配線基板の製造方法を示す断面図である。

## 【0120】

前述した第1実施形態では、支持体5の上に最初にピッチの狭いチップ接続用パッドP1を形成し、その上にビルトアップ配線を介してピッチの広い外部接続用パッドP2を形成している。第2実施形態では、その逆に、支持体5の上に最初にピッチの広い外部接続用パッドP2を形成し、その上にビルトアップ配線を介してピッチの狭いチップ接続用パッドP1を形成する。

## 【0121】

第2実施形態では、図12(a)に示すように、まず、支持体5の上に第1実施形態と同様な方法で下から順にAu層10a/ Ni層10bを形成することにより、外部接続用パッドP2(第1接続パッド)を得る。

## 【0122】

次いで、外部接続用パッドP2の上に第1黒色絶縁層20を形成した後に、第1黒色絶縁層20に外部接続用パッドP2に到達する第1ビアホールVH1を形成する。

## 【0123】

続いて、第1実施形態と同様に、第1ビアホールVH1(ビア導体)を介して外部接続用パッドP2に接続される第1配線層30を第1黒色絶縁層20の上に形成する。

## 【0124】

さらに、第1実施形態と同様に、第1層間絶縁層22の第2ビアホールVH2を介して第1配線層30に接続される第2配線層32を第1層間絶縁層22の上に形成する。その後に、第1実施形態と同様に、第2層間絶縁層24の第3ビアホールVH3を介して第2配線層32に接続されるチップ接続用パッドP1(第2接続パッド)を第3配線層として第2層間絶縁層24の上に形成する。

## 【0125】

次いで、第1実施形態と同様な方法により、チップ接続用パッドP1を被覆する第2黒色絶縁層26を形成した後に、レジストの開口部を通してウェットブラスト法によって第2黒色絶縁層26を除去する。これにより、チップ接続用パッドP1に到達する接続ホールCHが得られる。

## 【0126】

その後に、図12(b)に示すように、第1実施形態と同様に、支持体5をウェットエッチングによって除去する。

## 【0127】

これにより、第2実施形態の配線基板2が得られる。第2実施形態の配線基板2では、実装基板(マザーボードなど)の接続部に対応する外部接続用パッドP2の比較的広いピッチが、第1、第2配線層30, 32を介してチップ接続用パッドP1の比較的狭いピッ

10

20

30

40

50

チにピッチ変換される。

【0128】

第2実施形態の配線基板2では、最下の第1黒色絶縁層20に外部接続用パッドP2(第1接続パッド)が埋設されており、第1黒色絶縁層20の外面と外部接続用パッドP2の外面とが同一面を構成することで外部接続用パッドP2が第1黒色絶縁層20から露出している。

【0129】

外部接続用パッドP2の側面とビア接続面とが第1黒色絶縁層20に接し、外面(ビア接続面と反対面)が第1黒色絶縁層20から露出している。

【0130】

また、第1黒色絶縁層20及び第1、第2層間絶縁層22, 24に形成された第1～第3ビアホールVH1, VH2, VH3は、第2黒色絶縁層26側に開口されている。これに加えて、第1～第3ビアホールVH1, VH2, VH3は、外部接続用パッドP2及び第1、第2配線層30, 32の表面によって底面が構成され、先端の開口面積が底面面積より大きい円錐台状の凹部となって形成されている。そして、第1～第3ビアホールVH1, VH2, VH3の中にビア導体が形成(充填)されている。

【0131】

また、チップ接続用パッドP1(第2接続パッド)上には、ウェットプラスト法によって第2黒色絶縁層26に形成された接続ホールCHが配置されている。チップ接続用パッドP1の周縁部は第2黒色絶縁層26で被覆されおり、チップ接続用パッドP1の中央部が接続ホールCHから露出している。

【0132】

第2実施形態においても、チップ接続用パッドP1(第2接続パッド)上に配置される接続ホールCHは、第1実施形態の図7(b)で説明した形状と同様に形成される。

【0133】

図13には第2実施形態の変形例の配線基板2aが示されている。図13に示すように、前述した第1実施形態の変形例の配線基板1a(図8)と同様に、図12(b)の配線基板2において第1黒色絶縁層26の代わりに黒色樹脂27aの中央部にガラスクロスGが形成されたガラスクロス含有黒色絶縁層27を使用してもよい。

【0134】

そして、図14に示すように、図12(b)の配線基板2のチップ接続用パッドP1に半導体チップ40がバンプ電極42によってフリップチップ接続された後に、下側の隙間にアンダーフィル樹脂44が充填される。これにより、半導体パッケージが構成される。

【0135】

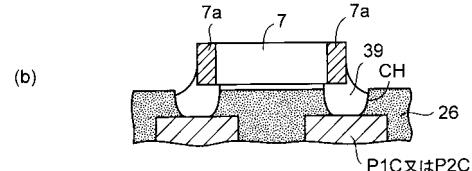

第2実施形態においても、第1実施形態と同様に、配線基板2が加熱処理される際に、第1、第2黒色絶縁層20, 26の変色はほとんど発生しない。これにより、見た目が悪くなる不具合が解消されると共に、その後のアセンブリ工程での画像認識に基づく位置合わせを安定して行うことができる。

【0136】

次に、第1、第2実施形態の配線基板1, 2(図6(a)、図12(b))をチップキャパシタを実装するための配線基板として使用する際の優位性について説明する。第1実施形態の配線基板1(図6(a))を使用する場合は、外部接続用パッドP2と同一層から形成されるキャパシタ接続用パッドP2Cにチップキャパシタが接続される。

【0137】

また、第2実施形態の配線基板2(図12(b))を使用する場合は、チップ接続用パッドP1と同一層から形成されるキャパシタ接続用パッドP1Cにチップキャパシタが接続される。

【0138】

図15(a)の平面図及び断面図に示すように、チップキャパシタを実装するための配線基板では、両端に接続電極を備えたチップキャパシタに対応するように一対の矩形状の

10

20

30

40

50

キャパシタ接続用パッドP1C又はP2Cが採用され、第2黒色絶縁層26に設けられる接続ホールCHはキャパシタ接続用パッドP1C又はP2Cの上に矩形状に開口される。例えば、矩形状の接続ホールCHの長さLが1.4mm程度であり、幅Wが0.65mmであり、比較的大きな面積の接続ホールCHが必要となる。

【0139】

そして、図15(b)に示すように、例えば、セラミックからなる直方体のキャパシタ本体を有し、キャパシタ本体の対向する側面に接続電極7aを備えたチップキャパシタ7を用意する。そして、両端の接続電極7aが一対の接続ホールCHの上に配置されるようチップキャパシタ7が配線基板に配置され、はんだ39によってチップキャパシタ7の接続電極7aがキャパシタ接続用パッドP1C又はP2Cに接続される。

10

【0140】

本実施形態と違って、レーザで第2黒色絶縁層26を加工して矩形状の接続ホールCHを形成する場合は、レーザの光束が円形であることからも一つの矩形状の接続ホールCHを形成するにあたり少なくとも数回のショットが必要である。従って、加工時間がかなり長くなって生産効率が低下するため、コスト高を招く問題がある。

【0141】

しかしながら、本実施形態で使用するウェットプラスト法は、研削面積の大小にほとんど依存せずに第2黒色絶縁層26を一括で除去できるので、研削面積の比較的大きな矩形状の接続ホールCHであっても処理時間が増大することなく容易に形成することができる。

20

【0142】

(第3の実施の形態)

図16及び図17は本発明の第3実施形態の配線基板の製造方法を示す断面図である。

【0143】

第3実施形態の配線基板はコア基板を有し、コア基板の両面側にビルドアップ配線を形成し、その両面側の最外にソルダレジストとして黒色絶縁層をそれぞれ形成する。

【0144】

第3実施形態では、図16(a)に示すように、まず、両面側に第1配線層60がそれぞれ形成されたコア基板50を用意する。コア基板50には厚み方向に貫通する貫通電極52が設けられており、両面側の第1配線層60は貫通電極52を介して相互接続されている。コア基板50はガラスエポキシ樹脂などの絶縁基板からなる。

30

【0145】

次いで、図16(b)に示すように、コア基板50の両面側に、層間絶縁層70をそれぞれ形成した後に、第1配線層60に到達するビアホールVHを層間絶縁層70にそれぞれ形成する。さらに、コア基板50の下面側の層間絶縁層70の上に、ビアホールVH(ビア導体)を介して第1配線層60に接続される外部接続用パッドP2(第1接続パッド)を第2配線層として形成する。

【0146】

また、コア基板50の上面側の層間絶縁層70の上に、ビアホールVH(ビア導体)を介して第1配線層60に接続されるチップ接続用パッドP1(第2接続パッド)を第2配線層として形成する。

40

【0147】

外部接続用パッドP2及びチップ接続用パッドP1は、各ビアホールVHの上に島状に配置されてもよいし、ビアホールVHから外側に延在する配線の一端に繋がっていてよい。

【0148】

続いて、図16(c)に示すように、コア基板50の下面側に、外部接続用パッドP2を被覆する第1黒色絶縁層20を形成する。さらに、コア基板60の上面側に、チップ接続用パッドP1を被覆する第2黒色絶縁層26を形成する。

【0149】

50

次いで、図16(d)に示すように、コア基板50の上面側に、チップ接続用パッドP1上に開口部28aが設けられたドライフィルムレジストなどのレジスト28を形成する。同様に、コア基板50の下面側に、外部接続用パッドP2上に開口部28aが設けられたレジスト28を形成する。

【0150】

次いで、図17に示すように、コア基板50の両面側において、ウェットプラスト法によってレジスト28の開口部28aを通して第1、第2黒色絶縁層20, 26をそれぞれ研削して除去する。その後に、レジスト28が除去される。

【0151】

これにより、コア基板50の下面側の第1黒色絶縁層20に、外部接続用パッドP2(第1接続パッド)に到達する接続ホールCHが形成される。また、コア基板60の上面側の第2黒色絶縁層26に、チップ接続用パッドP1(第2接続パッド)に到達する接続ホールCHが形成される。

【0152】

その後に、必要に応じて、チップ接続用パッドP1及び外部接続用パッドP2に無電解めっきによりNi層/Au層を形成するなどしてコンタクト層(不図示)を設ける。

【0153】

これにより、第3実施形態の配線基板3が得られる。

【0154】

第3実施形態の配線基板3では、実装基板(マザーボードなど)の接続部に対応する外部接続用パッドP2の比較的広いピッチが、コア基板50の両面に形成された第1配線層60を介してチップ接続用パッドP1の比較的狭いピッチにピッチ変換される。

【0155】

図17の例では、コア基板50の両面側に2層の配線層を形成しているが、配線層の積層数は任意に設定することができる。

【0156】

第3実施形態の配線基板3では、コア基板50の両面側にビルトアップ配線を形成するので、両面側の接続パッド(チップ接続用パッドP1及び外部接続用パッドP2)上の黒色絶縁層20, 26に接続ホールCHがそれぞれ形成されて両面側の接続パッドが露出する。

【0157】

第3実施形態においても、接続パッド(チップ接続用パッドP1及び外部接続用パッドP2)上にそれぞれ配置される接続ホールCHは、第1実施形態の図7(b)で説明した形状と同様に形成される。

【0158】

そして、図18に示すように、図17の配線基板3のチップ接続用パッドP1に半導体チップ40がバンプ電極42によってフリップチップ接続された後に、下側の隙間にアンダーフィル樹脂44が充填される。これにより、半導体パッケージが構成される。

【0159】

第3実施形態においても、第1実施形態と同様に、配線基板3が加熱処理される際に、第1、第2黒色絶縁層20, 26の変色はほとんど発生しない。これにより、見た目が悪くなる不具合が解消されると共に、その後のアセンブリ工程での画像認識に基づく位置合わせを安定して行うことができる。

【符号の説明】

【0160】

1, 1a, 2, 2a, 3...配線基板、5...支持体、6...めっきレジスト、6a, 28a...開口部、7...チップキャパシタ、7a, 40a...接続電極、10a...金(Au層)、10b...ニッケル(Ni)層、20...第1黒色絶縁層、27...ガラスクロス含有黒色絶縁層、22...第1層間絶縁層、24...第2層間絶縁層、26...第2黒色絶縁層、26a...面取り部、27a...黒色樹脂、28...レジスト、29...はんだボール、30, 60...第1配線層

10

20

30

40

50

、32…第2配線層、36, 39…はんだ、40…半導体チップ、42…バンプ電極、50…コア基板、52…貫通電極、70…層間絶縁層、VH1…第1ビアホール、VH2…第2ビアホール、VH3…第3ビアホール、A…食い込み部、C…凹部、Cx…側面、G…ガラスクロス、P1…チップ接続用パッド、P2…外部接続用パッド、P1C, P2C…キャパシタ接続用パッド。

【図1】

↓

加熱処理によるソルダレジスト300の変色

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

レーザ加工の場合（比較例）

本実施形態（ウェットブラスト）

【図8】

【図9】

レーザ加工の場合（比較例）

本実施形態（ウェットブラスト）

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

審査官 沼生 泰伸

(56)参考文献 特開2009-105393(JP, A)

特開2006-093438(JP, A)

特開2002-290022(JP, A)

国際公開第2010/010910(WO, A1)

特開2009-200356(JP, A)

特開2001-094260(JP, A)

特開2008-140886(JP, A)

国際公開第2006/059363(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H05K 3/46

H05K 3/28

H05K 3/32-3/34

H01L 23/12-23/15