(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6480761号

(P6480761)

(45) 発行日 平成31年3月13日(2019.3.13)

(24) 登録日 平成31年2月15日(2019.2.15)

(51) Int.Cl.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO1L 21/336  | (2006.01) | HO1L 29/78  | 627F |

| HO1L 29/786  | (2006.01) | HO1L 29/78  | 618B |

| HO1L 21/8234 | (2006.01) | HO1L 29/78  | 618C |

| HO1L 27/088  | (2006.01) | HO1L 27/088 | E    |

| HO1L 21/8238 | (2006.01) | HO1L 27/092 | G    |

請求項の数 1 (全 101 頁) 最終頁に続く

(21) 出願番号 特願2015-44197(P2015-44197)

(22) 出願日 平成27年3月6日(2015.3.6)

(65) 公開番号 特開2015-181162(P2015-181162A)

(43) 公開日 平成27年10月15日(2015.10.15)

審査請求日 平成30年2月15日(2018.2.15)

(31) 優先権主張番号 特願2014-43577(P2014-43577)

(32) 優先日 平成26年3月6日(2014.3.6)

(33) 優先権主張国 日本国(JP)

(31) 優先権主張番号 特願2014-43574(P2014-43574)

(32) 優先日 平成26年3月6日(2014.3.6)

(33) 優先権主張国 日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 本堂 英

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山出 直人

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 市川 武宜

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

トランジスタを有する半導体装置の作製方法であって、

略平面を有する基板上に酸化物半導体膜を形成し、

前記酸化物半導体膜を選択的にエッティングして、酸化物半導体層を形成し、

前記酸化物半導体層に酸素イオンを注入し、

前記酸化物半導体層上に絶縁層を形成し、

前記酸化物半導体層を加熱処理して、前記酸化物半導体層中に酸素を拡散させる工程を有し、

前記酸素イオンの注入は、前記略平面に対して垂直な角度( )を0°、前記略平面に対して平行な角度( )を90°としたとき、10° < < 85°の角度から、前記トランジスタのチャネル幅方向の略平面に対して垂直な断面における側面と、前記酸化物半導体層の上面とに対して行うことを特徴とする半導体装置の作製方法。

10

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明の一態様は、酸化物半導体を用いた半導体装置およびその作製方法に関する。

## 【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明

20

の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、液晶表示装置、発光装置、照明装置、蓄電装置、記憶装置、それらの駆動方法、または、それらの製造方法、を一例として挙げることができる。

#### 【0003】

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタ、半導体回路は半導体装置の一態様である。また、記憶装置、表示装置、電子機器は、半導体装置を有する場合がある。

#### 【背景技術】

10

#### 【0004】

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。当該トランジスタは集積回路（I C）や画像表示装置（単に表示装置とも表記する）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜として、シリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

#### 【0005】

例えば、酸化物半導体として酸化亜鉛、またはIn-Ga-Zn系酸化物半導体を用いてトランジスタを作製する技術が開示されている（特許文献1および特許文献2参照）。

#### 【先行技術文献】

20

#### 【特許文献】

#### 【0006】

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

本発明の一態様は、半導体装置に良好な電気特性を付与することを課題の一つとする。または、オン電流の高い半導体装置を提供することを目的の一つとする。または、高速動作に適した半導体装置を提供することを課題の一つとする。または、集積度の高い半導体装置を提供することを目的の一つとする。または、低消費電力の半導体装置を提供することを目的の一つとする。または、信頼性の高い半導体装置を提供することを目的の一つとする。または、電源が遮断されてもデータが保持される半導体装置を提供することを目的の一つとする。または、新規な半導体装置を提供することを目的の一つとする。または、上記半導体装置の作製方法を提供することを目的の一つとする。

30

#### 【0008】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

40

#### 【課題を解決するための手段】

#### 【0009】

本発明の一態様は、酸化物半導体層をチャネル形成領域に有するトランジスタに関する。

#### 【0010】

本発明の一態様は、略平面を有する基板上に酸化物半導体膜を形成し、酸化物半導体膜を選択的にエッチングすることにより酸化物半導体層を形成し、酸化物半導体層に酸素イオンを注入し、酸化物半導体層上に絶縁層を形成し、酸化物半導体層を加熱処理することにより酸化物半導体層中に酸素を拡散させることを特徴とする半導体装置の作製方法である。

#### 【0011】

50

また、本発明の他の一態様は、略平面を有する基板上に酸化物半導体膜を形成し、酸化物半導体膜を選択的にエッティングすることにより酸化物半導体層を形成し、酸化物半導体層上に絶縁層を形成し、絶縁層を介して酸化物半導体層に酸素イオンを注入し、酸化物半導体層を加熱処理することにより酸化物半導体層中に酸素を拡散させることを特徴とする半導体装置の作製方法である。

#### 【0012】

上記略平面に対して垂直な角度(θ)を0°、略平面に対して平行な角度(φ)を90°としたとき、酸素イオンの注入は、0° < φ < 90°の角度から酸化物半導体層の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して行うことが好ましい。

10

#### 【0013】

また、略平面に対して垂直な角度(θ)を0°、略平面に対して平行な角度(φ)を90°としたとき、酸素イオンの注入は、0° < φ < 90°の角度で行い、かつ略平面に垂直な軸を中心に基板を回転させながら行ってもよい。

#### 【0014】

また、略平面に対して垂直な角度(θ)を0°、略平面に対して平行な角度(φ)を90°としたとき、酸素イオンの注入は、略0°および0° < φ < 90°の角度から酸化物半導体層の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して複数回行ってもよい。

#### 【0015】

上記酸化物半導体層としては、InとZnと、M(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)を有することが好ましい。

20

#### 【0016】

また、酸化物半導体層は、基板側から第1の酸化物半導体層、第2の酸化物半導体層の順で形成された積層であってもよい。第1および第2の酸化物半導体層はInとZnと、M(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)とを有し、第1の酸化物半導体層は、Inに対するMの原子数比が第2の酸化物半導体層よりも大きいことが好ましい。

#### 【0017】

なお、本明細書等における「第1」、「第2」等の序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではない。

30

#### 【0018】

また、酸化物半導体層は、基板側から第1の酸化物半導体層、第2の酸化物半導体層、第3の酸化物半導体層の順で形成された積層であってもよい。第1乃至第3の酸化物半導体層はInとZnと、M(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)とを有し、第1の酸化物半導体層および第3の酸化物半導体層は、Inに対するMの原子数比が第2の酸化物半導体層よりも大きいことが好ましい。

#### 【0019】

酸化物半導体層のチャネル幅方向の略平面に対して垂直な断面は、頂部と側部が曲率をして結合している形状であってもよい。

40

#### 【0020】

また、本発明の他の一態様は、略平面を有する基板上に第1の酸化物半導体膜、第2の酸化物半導体膜を順に形成し、第1の酸化物半導体膜および第2の酸化物半導体膜を選択的にエッティングすることにより第1の酸化物半導体層および第2の酸化物半導体層からなる積層を形成し、積層に酸素イオンを注入し、積層上に第3の酸化物半導体膜を形成し、酸化物半導体層を加熱処理することにより酸化物半導体層中に酸素を拡散させることを特徴とする半導体装置の作製方法である。

#### 【0021】

また、本発明の他の一態様は略平面を有する基板上に第1の酸化物半導体膜、第2の酸化物半導体膜を順に形成し、第1の酸化物半導体膜および第2の酸化物半導体膜を選択的に

50

エッチングすることにより第1の酸化物半導体層および第2の酸化物半導体層からなる積層を形成し、積層上に第3の酸化物半導体膜を形成し、第3の酸化物半導体層を介して積層に酸素イオンを注入し、酸化物半導体層を加熱処理することにより酸化物半導体層中に酸素を拡散させることを特徴とする半導体装置の作製方法である。

#### 【0022】

上記略平面に対して垂直な角度( )を0°、略平面に対して平行な角度( )を90°としたとき、酸素イオンの注入は、0° < < 90°の角度から積層の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して行うことが好ましい。

#### 【0023】

また、略平面に対して垂直な角度( )を0°、略平面に対して平行な角度( )を90°としたとき、酸素イオンの注入は、0° < < 90°の角度で行い、かつ略平面に垂直な軸を中心に基板を回転させながら行ってもよい。 10

#### 【0024】

また、略平面に対して垂直な角度( )を0°、略平面に対して平行な角度( )を90°としたとき、酸素イオンの注入は、略0°および0° < < 90°の角度から積層の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して複数回行ってもよい。

#### 【0025】

第1乃至第3の酸化物半導体層は、InとZnと、M(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)とを有し、第1の酸化物半導体層および第3の酸化物半導体層は、Inに対するMの原子数比が第2の酸化物半導体層よりも大きいことが好ましい。 20

#### 【0026】

また、積層のチャネル幅方向の略平面に対して垂直な断面は、頂部と側部が曲率を有して結合している形状であってもよい。

#### 【発明の効果】

#### 【0027】

本発明の一態様を用いることにより、半導体装置に良好な電気特性を付与することができる。または、オン電流の高い半導体装置を提供することができる。または、高速動作に適した半導体装置を提供することができる。集積度の高い半導体装置を提供することができる。または、低消費電力の半導体装置を提供することができる。または、信頼性の高い半導体装置を提供することができる。または、電源が遮断されてもデータが保持される半導体装置を提供することができる。または、新規な半導体装置を提供することができる。または、上記半導体装置の作製方法を提供することができる。 30

#### 【0028】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

#### 【図面の簡単な説明】

#### 【0029】

【図1】半導体層を説明する上面図および断面図。

【図2】半導体層を説明する断面図。

【図3】トランジスタを説明する上面図および断面図。

【図4】トランジスタを説明する上面図および断面図。

【図5】トランジスタを説明する上面図および断面図。

【図6】トランジスタを説明する上面図および断面図。

【図7】トランジスタを説明する上面図および断面図。

【図8】トランジスタを説明する上面図および断面図。

【図9】トランジスタのチャネル幅方向の断面を説明する図。 40

50

【図 1 0】トランジスタのチャネル長方向の断面を説明する図。

【図 1 1】トランジスタのチャネル長方向の断面を説明する図。

【図 1 2】トランジスタのチャネル幅方向の断面を説明する図。

【図 1 3】半導体層を説明する上面図および断面図。

【図 1 4】半導体層を説明する上面図および断面図。

【図 1 5】トランジスタを説明する上面図および断面図。

【図 1 6】トランジスタを説明する上面図および断面図。

【図 1 7】トランジスタを説明する上面図および断面図。

【図 1 8】トランジスタを説明する上面図および断面図。

【図 1 9】トランジスタを説明する上面図および断面図。

10

【図 2 0】トランジスタを説明する上面図および断面図。

【図 2 1】トランジスタのチャネル幅方向の断面を説明する図。

【図 2 2】トランジスタのチャネル長方向の断面を説明する図。

【図 2 3】トランジスタのチャネル長方向の断面を説明する図。

【図 2 4】トランジスタのチャネル幅方向の断面を説明する図。

【図 2 5】トランジスタの作製方法を説明する図。

【図 2 6】トランジスタの作製方法を説明する図。

【図 2 7】トランジスタの作製方法を説明する図。

【図 2 8】トランジスタの作製方法を説明する図。

【図 2 9】C A A C - O S の断面における C s 補正高分解能 T E M 像、および C A A C - O S の断面模式図。

20

【図 3 0】C A A C - O S の平面における C s 補正高分解能 T E M 像。

【図 3 1】C A A C - O S および単結晶酸化物半導体の X R D による構造解析を説明する図。

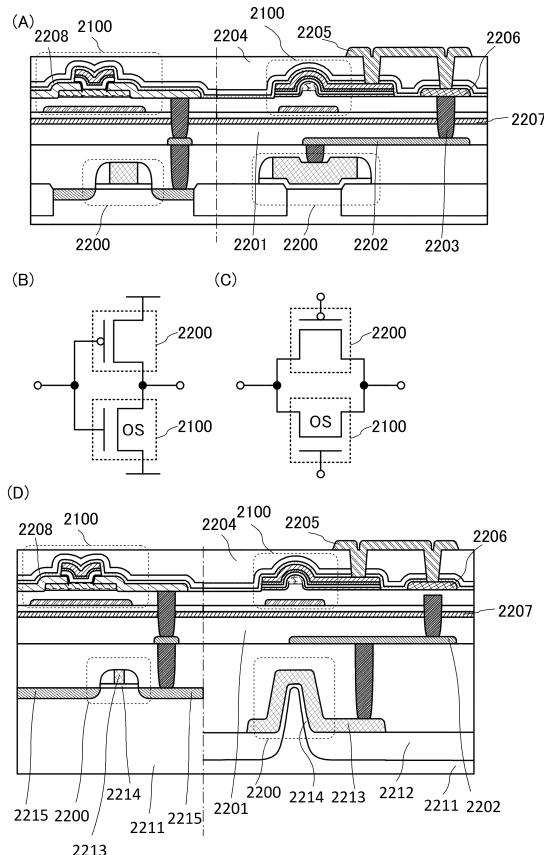

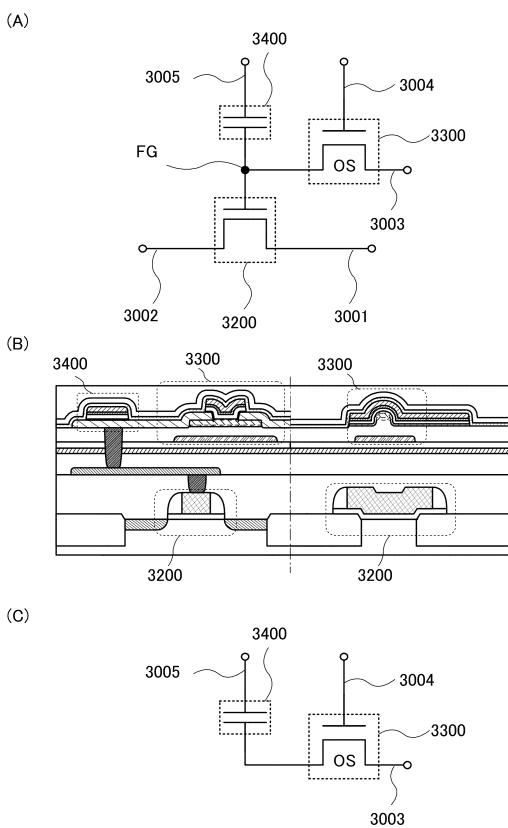

【図 3 2】半導体装置の断面図および回路図。

【図 3 3】記憶装置の断面図および回路図。

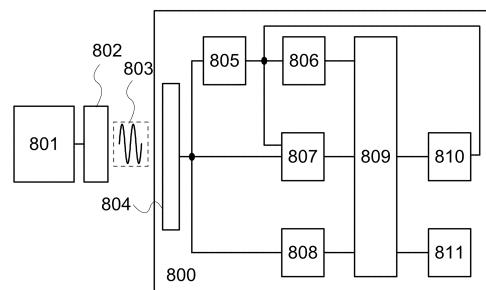

【図 3 4】R F タグの構成例を説明する図。

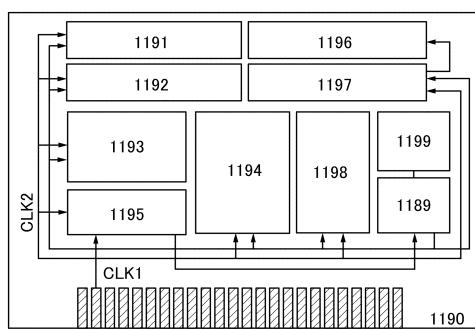

【図 3 5】C P U の構成例を説明する図。

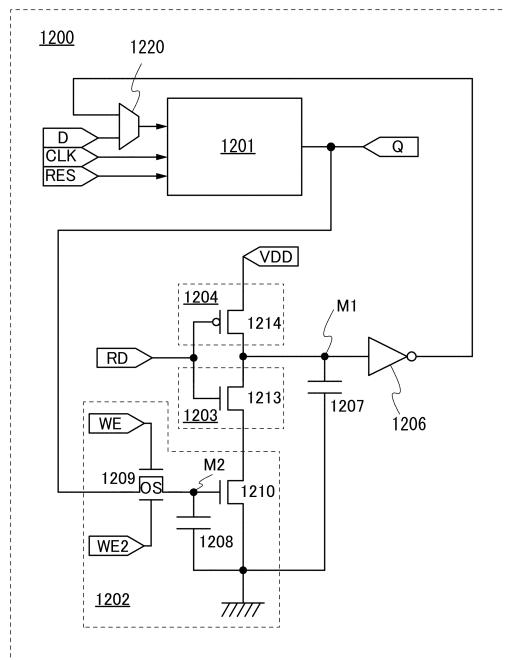

【図 3 6】記憶素子の回路図。

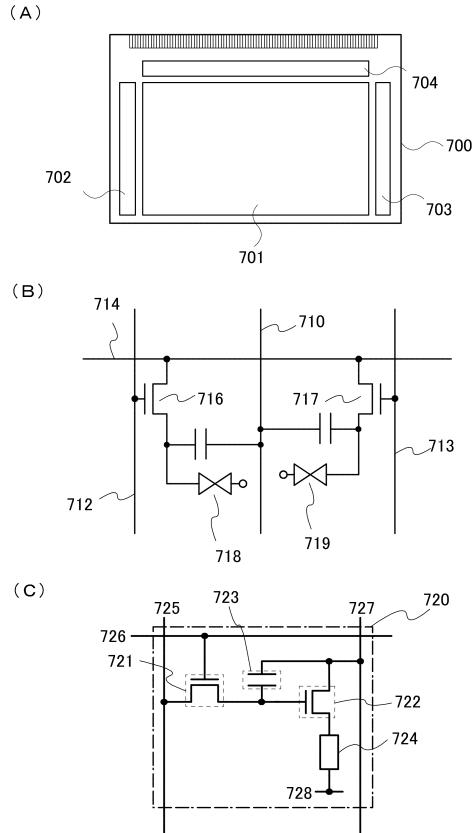

【図 3 7】表示装置の構成例を説明する図および画素の回路図。

30

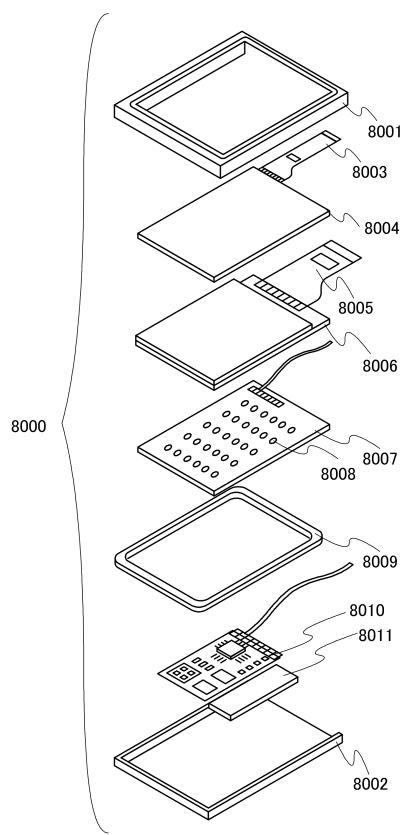

【図 3 8】表示モジュールを説明する図。

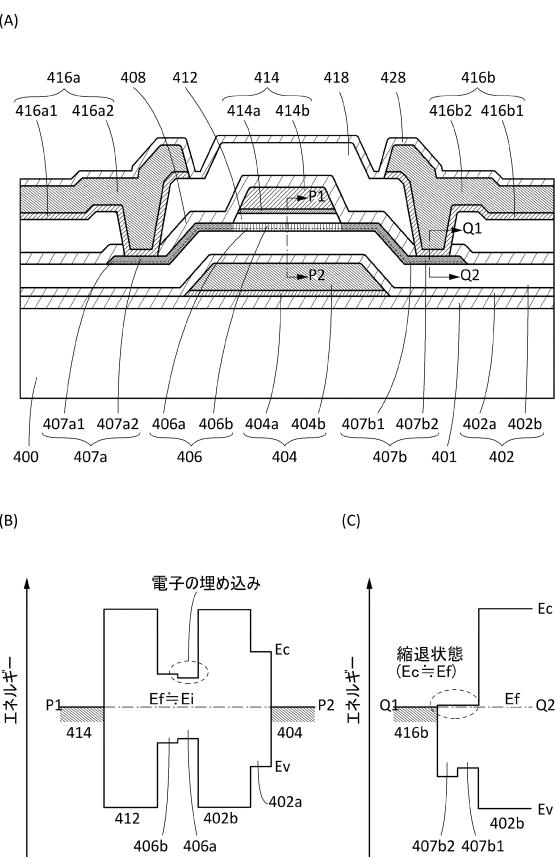

【図 3 9】トランジスタの断面図およびバンド構造。

【図 4 0】計算モデルを説明する図。

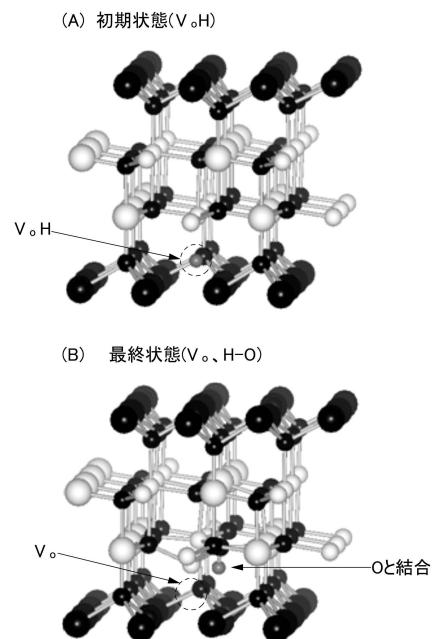

【図 4 1】初期状態と最終状態を説明する図。

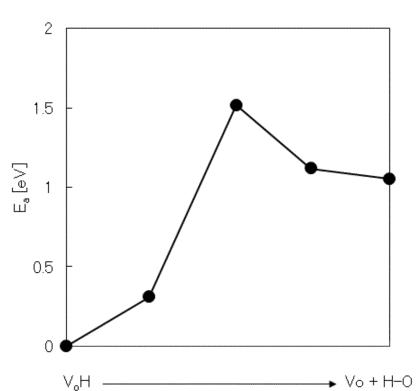

【図 4 2】活性化障壁を説明する図。

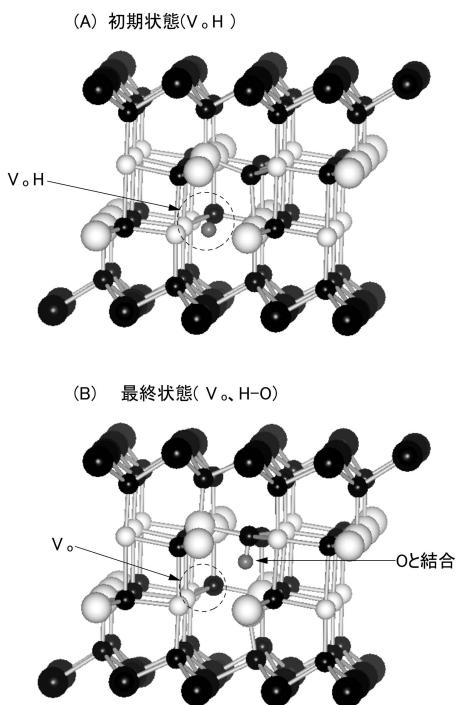

【図 4 3】初期状態と最終状態を説明する図。

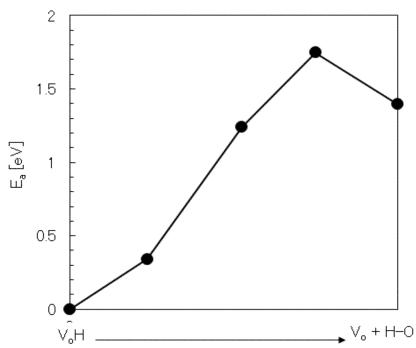

【図 4 4】活性化障壁を説明する図。

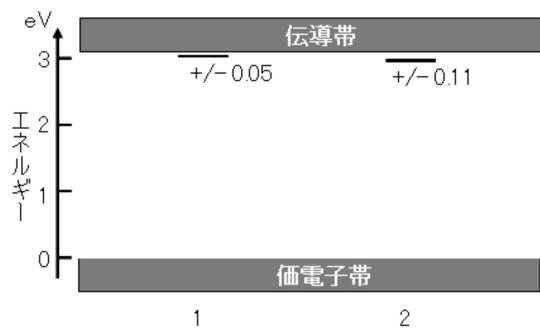

【図 4 5】V 。 H の遷移レベルを説明する図。

【図 4 6】C A A C - O S の成膜モデルを説明する模式図、ペレットおよび C A A C - O S の断面図。

40

【図 4 7】n c - O S の成膜モデルを説明する模式図、およびペレットを示す図。

【図 4 8】ペレットを説明する図。

【図 4 9】被形成面においてペレットに加わる力を説明する図。

【図 5 0】被形成面におけるペレットの動きを説明する図。

【図 5 1】I n G a Z n O<sub>4</sub> の結晶を説明する図。

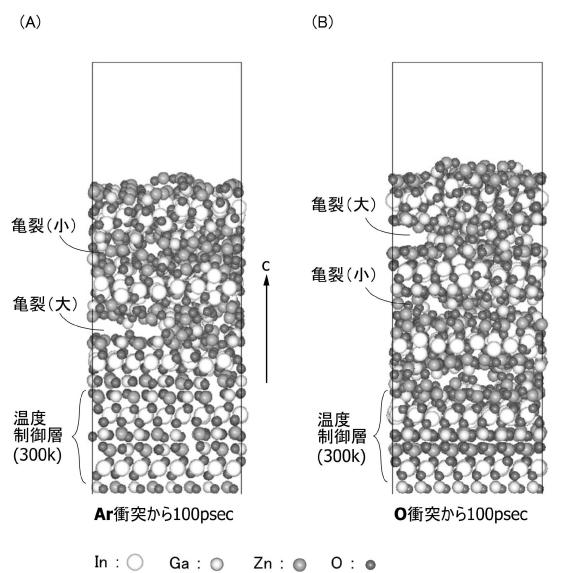

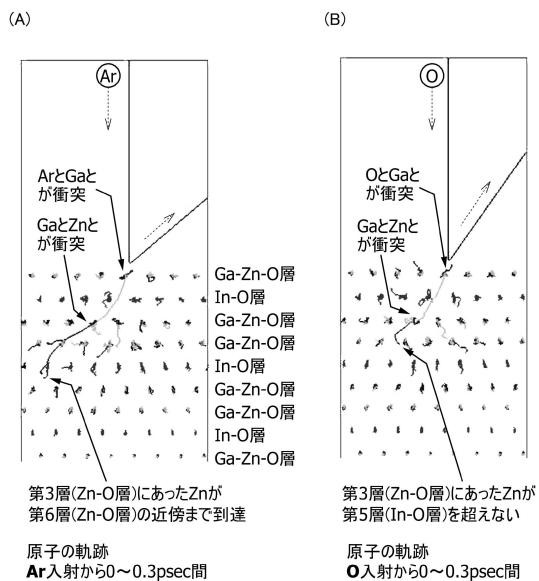

【図 5 2】原子が衝突する前の I n G a Z n O<sub>4</sub> の構造などを説明する図。

【図 5 3】原子が衝突した後の I n G a Z n O<sub>4</sub> の構造などを説明する図。

【図 5 4】原子が衝突した後の原子の軌跡を説明する図。

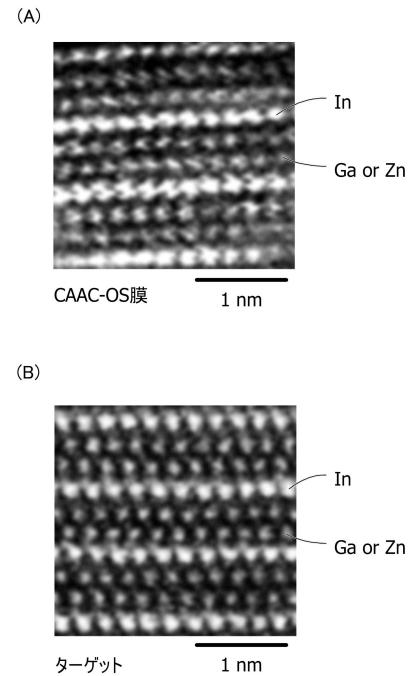

【図 5 5】C A A C - O S およびターゲットの断面 H A A D F - S T E M 像。

【図 5 6】電子機器を説明する図。

50

- 【図57】R F タグの使用例を説明する図。

- 【図58】トランジスタを説明する上面図。

- 【図59】In - Ga - Zn 酸化物膜のX線回折スペクトル。

- 【図60】過剰酸素の移動の計算に用いたモデル図。

- 【図61】過剰酸素の移動の計算結果を説明する図。

- 【図62】酸素欠損の移動の計算に用いたモデル図。

- 【図63】酸素欠損の移動の計算結果を説明する図。

- 【図64】In - Ga - Zn 酸化物膜中の<sup>18</sup>O のデプスプロファイル。

- 【図65】In - Ga - Zn 酸化物中の酸素の移動経路を説明する図。

- 【図66】トランジスタを説明する断面図。 10

- 【図67】トランジスタを説明する断面図。

- 【図68】トランジスタを説明する断面図。

- 【図69】半導体層を説明する上面図および断面図。

- 【図70】半導体層を説明する断面図。

- 【図71】トランジスタの作製方法を説明する図。

- 【図72】トランジスタの作製方法を説明する図。

- 【図73】C A A C - O S の電子回折パターンを示す図。

- 【図74】In - Ga - Zn 酸化物の電子照射による結晶部の変化を示す図。

- 【発明を実施するための形態】

- 【0030】 20

- 実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。なお、図を構成する同じ要素のハッチングを異なる図面間で適宜省略または変更する場合もある。

- 【0031】

- なお、本明細書等において、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とを含むものとする。ここで、X、Yは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。 30

- 【0032】

- XとYとが電気的に接続されている場合の一例としては、XとYとの電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオード、表示素子、発光素子、負荷など）が、XとYとの間に1個以上接続されることが可能である。なお、スイッチは、オンオフが制御される機能を有している。つまり、スイッチは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有している。または、スイッチは、電流を流す経路を選択して切り替える機能を有している。 40

- 【0033】

- XとYとが機能的に接続されている場合の一例としては、XとYとの機能的な接続を可能とする回路（例えば、論理回路（インバータ、NAND回路、NOR回路など）、信号変換回路（D/A変換回路、A/D変換回路、ガンマ補正回路など）、電位レベル変換回路（電源回路（昇圧回路、降圧回路など）、信号の電位レベルを変えるレベルシフト回路など）、電圧源、電流源、切り替え回路、增幅回路（信号振幅または電流量などを大きくできる回路、オペアンプ、差動增幅回路、ソースフォロワ回路、バッファ回路など）、信号生成回路、記憶回路、制御回路など）が、XとYとの間に1個以上接続されることが可能であ 50

る。なお、一例として、XとYとの間に別の回路を挟んでいても、Xから出力された信号がYへ伝達される場合は、XとYとは機能的に接続されているものとする。

#### 【0034】

なお、XとYとが接続されている、と明示的に記載する場合は、XとYとが電気的に接続されている場合（つまり、XとYとの間に別の素子または別の回路を挟んで接続されている場合）と、XとYとが機能的に接続されている場合（つまり、XとYとの間に別の回路を挟んで機能的に接続されている場合）と、XとYとが直接接続されている場合（つまり、XとYとの間に別の素子または別の回路を挟まずに接続されている場合）とを含むものとする。つまり、電気的に接続されている、と明示的に記載する場合は、単に、接続されている、とのみ明示的に記載されている場合と同じであるとする。

10

#### 【0035】

なお、回路図上は独立している構成要素同士が電気的に接続しているように図示されている場合であっても、1つの構成要素が、複数の構成要素の機能を併せ持っている場合もある。例えば配線の一部が電極としても機能する場合は、一の導電膜が、配線の機能、および電極の機能の両方の構成要素の機能を併せ持っている。したがって、本明細書における電気的に接続とは、このような、一の導電膜が、複数の構成要素の機能を併せ持っている場合も、その範疇に含める。

#### 【0036】

なお、例えば、トランジスタのソース（または第1の端子など）が、Z1を介して（または介さず）、Xと電気的に接続され、トランジスタのドレイン（または第2の端子など）が、Z2を介して（または介さず）、Yと電気的に接続されている場合や、トランジスタのソース（または第1の端子など）が、Z1の一部と直接的に接続され、Z1の別の一部がXと直接的に接続され、トランジスタのドレイン（または第2の端子など）が、Z2の一部と直接的に接続され、Z2の別の一部がYと直接的に接続されている場合では、以下のように表現することができる。

20

#### 【0037】

例えば、「XとYとトランジスタのソース（または第1の端子など）とドレイン（または第2の端子など）とは、互いに電気的に接続されており、X、トランジスタのソース（または第1の端子など）、トランジスタのドレイン（または第2の端子など）、Yの順序で電気的に接続されている。」と表現することができる。または、「トランジスタのソース（または第1の端子など）は、Xと電気的に接続され、トランジスタのドレイン（または第2の端子など）はYと電気的に接続され、X、トランジスタのソース（または第1の端子など）、トランジスタのドレイン（または第2の端子など）、Yは、この順序で電気的に接続されている」と表現することができる。または、「Xは、トランジスタのソース（または第1の端子など）とドレイン（または第2の端子など）とを介して、Yと電気的に接続され、X、トランジスタのソース（または第1の端子など）、トランジスタのドレイン（または第2の端子など）、Yは、この接続順序で設けられている」と表現することができる。これらの例と同様な表現方法を用いて、回路構成における接続の順序について規定することにより、トランジスタのソース（または第1の端子など）と、ドレイン（または第2の端子など）とを、区別して、技術的範囲を決定することができる。なお、これらの表現方法は、一例であり、これらの表現方法に限定されない。ここで、X、Y、Z1、Z2は、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。

30

#### 【0038】

なお、本明細書等において、様々な基板を用いて、トランジスタを形成することができる。基板の種類は、特定のものに限定されることはない。その基板の一例としては、半導体基板（例えば単結晶基板またはシリコン基板）、SOI基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タンゲステン基板、タンゲステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、繊維状の材料を含む紙、または基材フィルムなどがある。ガラス基板の一

40

50

例としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、またはソーダライムガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート( P E T )、ポリエチレンナフタレート( P E N )、ポリエーテルサルファン( P E S )に代表されるプラスチック、またはアクリル等の可撓性を有する合成樹脂などがある。貼り合わせフィルムの一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、またはポリ塩化ビニルなどがある。基材フィルムの一例としては、ポリエステル、ポリアミド、ポリイミド、無機蒸着フィルム、または紙類などがある。特に、半導体基板、単結晶基板、またはS O I 基板などを用いてトランジスタを製造することによって、特性、サイズ、または形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、または回路の高集積化を図ることができる。10

#### 【 0 0 3 9 】

また、基板として、可撓性基板を用い、可撓性基板上に直接、トランジスタを形成してもよい。または、基板とトランジスタの間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板より分離し、他の基板に転載するために用いることができる。その際、トランジスタは耐熱性の劣る基板や可撓性の基板にも転載できる。なお、上述の剥離層には、例えば、タングステン膜と酸化シリコン膜との無機膜の積層構造の構成や、基板上にポリイミド等の有機樹脂膜が形成された構成等を用いることができる。20

#### 【 0 0 4 0 】

つまり、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、アラミドフィルム基板、ポリイミドフィルム基板、石材基板、木材基板、布基板(天然纖維(絹、綿、麻)、合成纖維(ナイロン、ポリウレタン、ポリエステル)若しくは再生纖維(アセテート、キュプラ、レーヨン、再生ポリエステル)などを含む)、皮革基板、またはゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、または薄型化を図ることができる。30

#### 【 0 0 4 1 】

##### ( 実施の形態 1 )

本実施の形態では、本発明の一態様のトランジスタの作製方法について図面を用いて説明する。

#### 【 0 0 4 2 】

本発明の一態様のトランジスタは、シリコン(歪シリコン含む)、ゲルマニウム、シリコングルマニウム、炭化シリコン、ガリウムヒ素、アルミニウムガリウムヒ素、インジウムリン、窒化ガリウム、有機半導体、または酸化物半導体などをチャネル形成領域に用いることができる。特に、シリコンよりもバンドギャップの大きい酸化物半導体を含んでチャネル形成領域を形成することが好ましい。

#### 【 0 0 4 3 】

例えば、上記酸化物半導体として、少なくともインジウム( I n )もしくは亜鉛( Z n )を含むことが好ましい。より好ましくはI n - M - Z n 系酸化物( M はA l 、T i 、G a 、G e 、Y 、Z r 、S n 、L a 、C e またはH f 等の金属)で表記される酸化物を含む構成とする。40

#### 【 0 0 4 4 】

以下では、特に断りのない限り、一例として、チャネル形成領域に酸化物半導体を含むトランジスタについて説明する。

#### 【 0 0 4 5 】

酸化物半導体層における酸素欠損は不必要なドナーの形成に寄与するため酸素欠損が極力少ない材料を用いることが好ましい。しかしながら、形成直後の酸化物半導体層において50

酸素欠損が少ない場合でも、トランジスタの作製工程における様々な要因によって酸素欠損は増加しうる。チャネル形成領域における酸化物半導体層中の酸素欠損が増加すると、例えば、トランジスタのノーマリーオン化、リーク電流の増大、ストレス印加によるしきい値電圧のシフトなど、電気特性の不良を引き起こす場合がある。

#### 【0046】

酸化物半導体層の酸素欠損を補填するには、当該酸化物半導体層と接する下地絶縁膜から酸素を供給する方法がある。この場合、下地絶縁膜として用いる酸化物絶縁層を化学量論組成よりも多い酸素を含む組成とすることが好ましい。

#### 【0047】

また、イオン注入法などを用いて酸化物半導体層に直接酸素を注入してもよい。イオン注入法では必要量の酸素を正確に酸化物半導体層に注入することができる。10

#### 【0048】

これらの方針を用いて酸化物半導体層に酸素を供給することでトランジスタの電気特性および信頼性を向上させることができる。

#### 【0049】

また、トランジスタの微細化によってオン電流の低下が課題となるが、活性層をフィン型とすることでオン電流の低下を防止することができる。活性層をフィン型とする場合、酸化物半導体層の膜厚が厚いほど実効的なチャネル幅を拡大させることができ、オン電流は向上しやすい。

#### 【0050】

一方で、酸化物半導体層の膜厚が厚くなると下地絶縁膜から供給される酸素を膜厚方向全体に拡散させることが困難となる。20

#### 【0051】

また、膜厚が厚い酸化物半導体層に酸素イオン注入をする場合においては、膜厚方向全体に酸素を行き渡らせるためには高加速電圧かつ高ドーズ量の条件が必要となる。当該条件下で酸素を注入すると、イオン注入ダメージにより酸化物半導体層に含まれる結晶が破壊され、トランジスタの電気特性が低下してしまう。

#### 【0052】

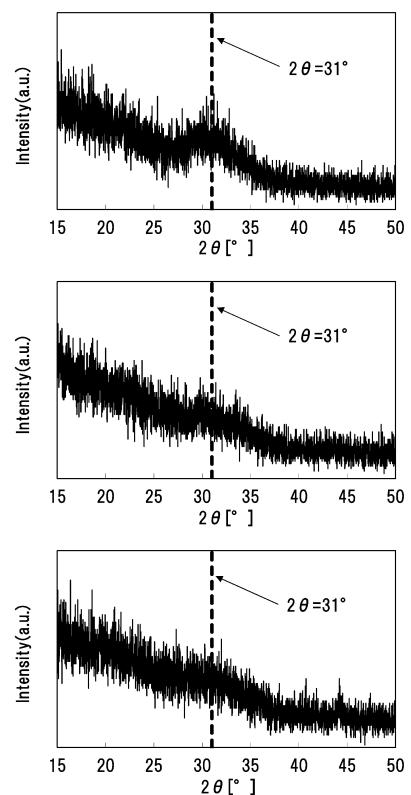

例えば、この現象はX線回折で確認することができる。図59(A)、(B)、(C)は、c軸に配向したIn-Ga-Zn酸化物膜に対する酸素イオン注入の影響をX線回折で調べた結果である。図59(A)に示すように、初期状態(酸素イオン注入なし)ではInGaZnO<sub>4</sub>結晶の(009)面配向を示す2θ = 31°近傍のピークが見られるが、図59(B)に示すようにイオン種を<sup>16</sup>O<sup>+</sup>、加速電圧を5kV、ドーズ量を1E16 cm<sup>-2</sup>とした条件で注入すると2θ = 31°近傍のピークが消失してしまう。また、図59(C)に示すようにイオン種を<sup>16</sup>O<sup>+</sup>、加速電圧を5kV、ドーズ量を1E15 cm<sup>-2</sup>とした条件で注入した場合も同じである。なお、上記いずれの条件より少ないドーズ量においては結晶状態の維持は確認されているが、膜厚方向全体に酸素を供給することは困難となる。30

#### 【0053】

そこで、本発明の一態様では、酸化物半導体層の側面に対して酸素のイオン注入を行うことにより、結晶を破壊することなく、かつ効率良く酸素を酸化物半導体層に供給する手段を用いる。40

#### 【0054】

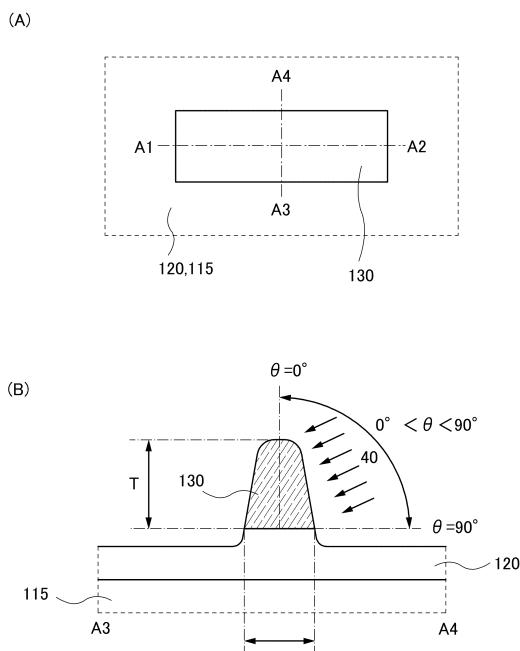

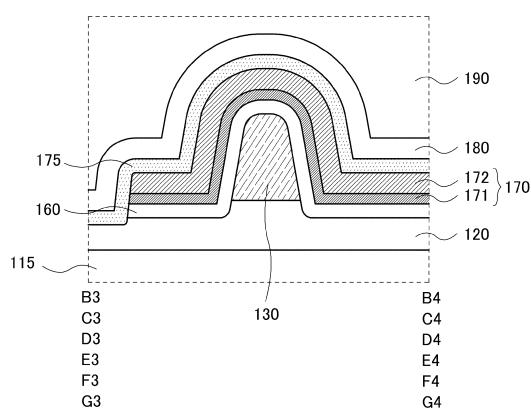

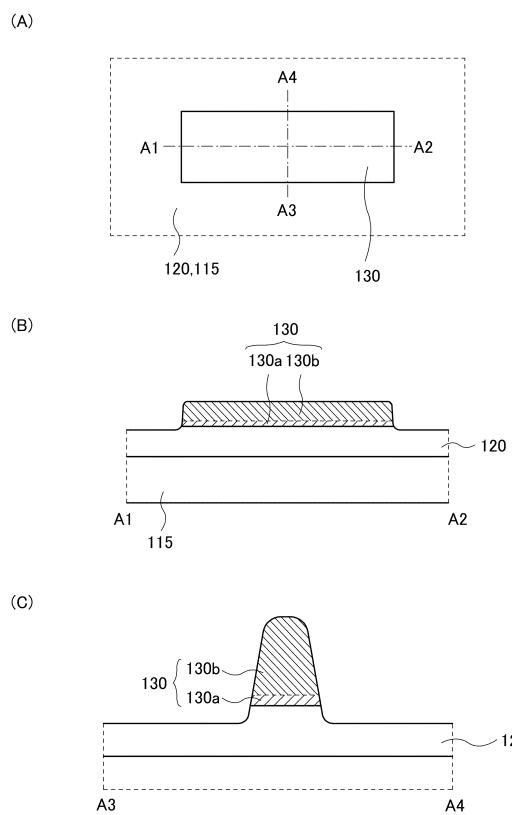

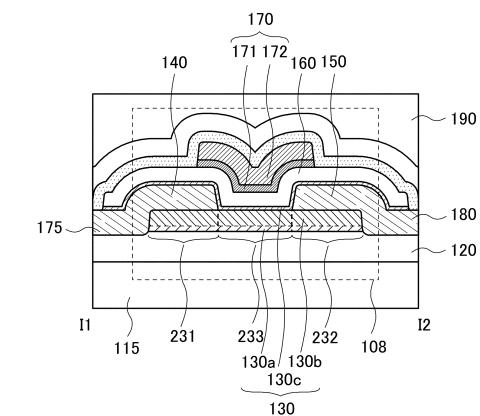

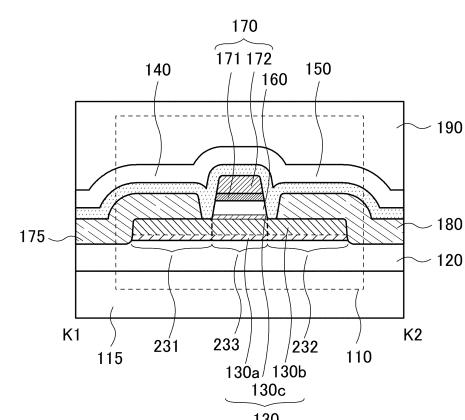

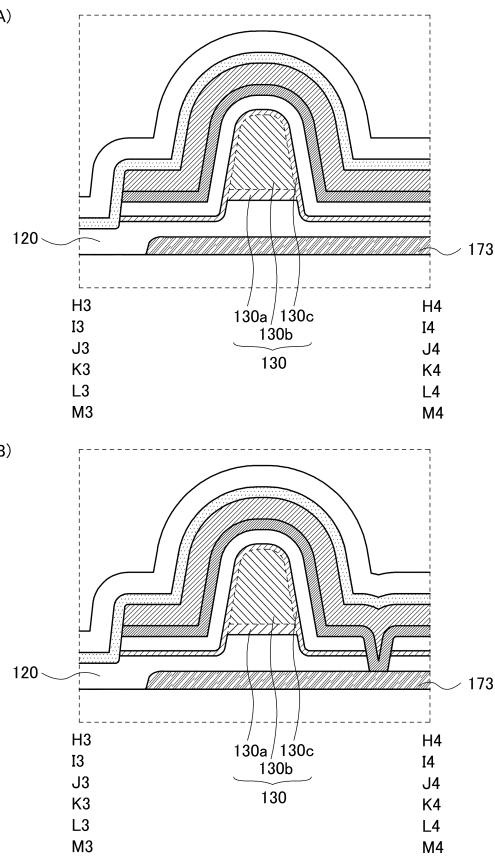

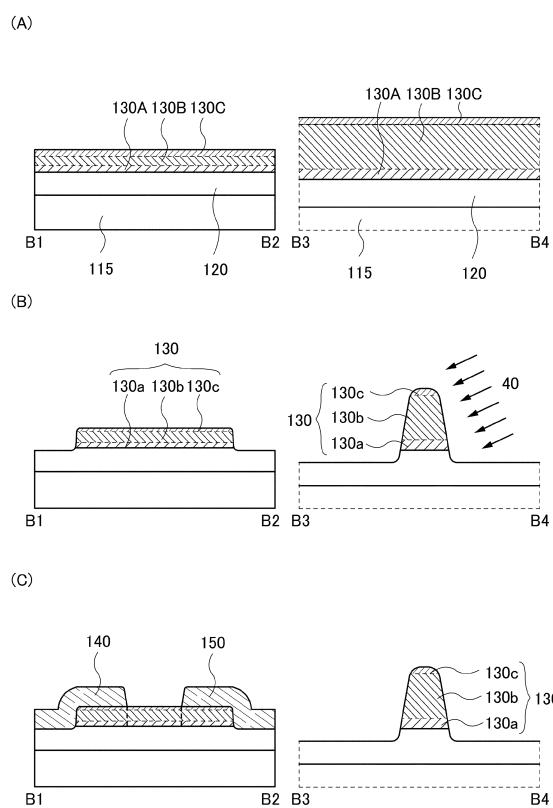

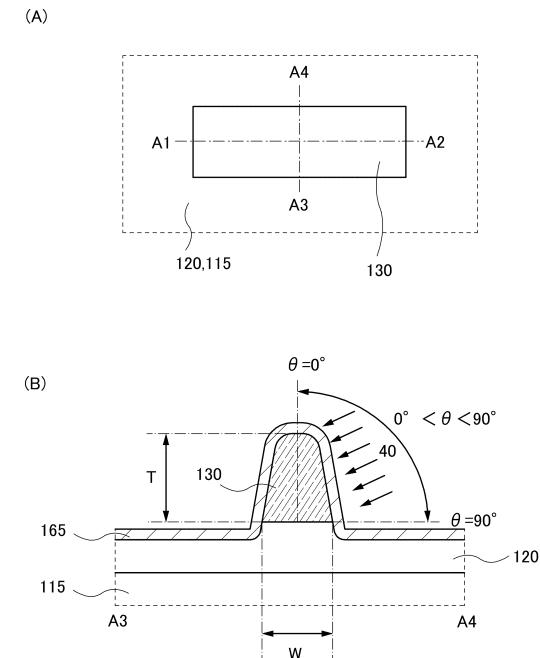

図1(A)、(B)は、本発明の一態様のトランジスタに用いられる酸化物半導体層130の上面図および断面図である。図1(A)は上面図であり、図1(A)に示す一点鎖線A3-A4方向の断面が図1(B)に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線A1-A2方向をチャネル長方向、一点鎖線A3-A4方向をチャネル幅方向と呼称する場合がある。

#### 【0055】

略平面を有する基板115上に絶縁層120が形成され、絶縁層120上に酸化物半導体50

層 130 が形成されている。ここで、絶縁層 120 は上述した酸素供給源となる下地絶縁膜として作用させるため、過剰の酸素を含む絶縁膜であることが好ましい。少なくとも酸化物半導体層 130 の絶縁層 120 と接する領域近傍は絶縁層 120 からの酸素拡散によって酸素欠損を低減することができる。

#### 【 0 0 5 6 】

また、図 69 (A)、(B) は上記とは異なる形態であり、本発明の一態様のトランジスタに用いられる酸化物半導体層 130 およびブロック層 165 の上面図および断面図である。図 69 (A) は上面図であり、図 69 (A) に示す一点鎖線 A3 - A4 方向の断面が図 69 (B) に相当する。

#### 【 0 0 5 7 】

略平面を有する基板 115 上に絶縁層 120 が形成され、絶縁層 120 上に酸化物半導体層 130 が形成され、酸化物半導体層 130 に接してブロック層 165 が形成されている。ここで、絶縁層 120 は上述した酸素供給源となる下地絶縁膜として作用させるため、過剰の酸素を含む絶縁膜であることが好ましい。少なくとも酸化物半導体層 130 の絶縁層 120 と接する領域近傍は絶縁層 120 からの酸素拡散によって酸素欠損を低減することができる。また、ブロック層 165 はイオン注入による酸化物半導体層 130 のダメージを緩和する効果を有する。

#### 【 0 0 5 8 】

なお、略平面とは、大意として故意に凹凸やうねりを形成しない平面を指す。また、微視的な凹凸やうねりを有する平面は略平面に含まれる。したがって、略平面を有する基板 115 上に形成された絶縁層 120 も略平面を有する。

#### 【 0 0 5 9 】

本発明の一態様において、酸化物半導体層 130 はチャネル幅方向の断面において膜厚 (T) がチャネル幅 (W) よりも大きい形状 ( $T > W$ ) とする。また、酸化物半導体層 130 はチャネル幅方向の断面において略台形であり、頂部と側部が曲率を有して結合している形状であることが好ましい。上記形状とすることで、オン電流を向上させることに加え、酸化物半導体層 130 に対するゲート絶縁膜 (絶縁層 160) の被覆性が向上するため、ゲート絶縁膜の薄膜化を容易とすることができます。また、酸化物半導体層 130 に電界が集中するような局部的な凸部または凹部をなくすことができるために、ゲート耐圧の高いトランジスタを形成することができる。

#### 【 0 0 6 0 】

また、本発明の一態様において酸化物半導体層 130 は、基板 115 または絶縁層 120 の略平面に対して垂直方向に c 軸配向した結晶 (C AAC - OS : C Axis Aligned Crystalline Oxide Semiconductor) を有する膜であることが好ましい。CAC - OS 膜を用いることで、トランジスタの電気特性および信頼性を向上させることができる。

#### 【 0 0 6 1 】

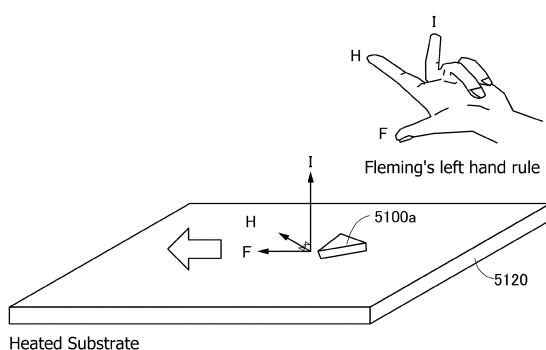

そして、基板 115 または絶縁層 120 が有する略平面に対して垂直な角度 ( ) を 0°、当概略平面に対して平行な角度 ( ) を 90° としたとき、酸素イオン 40 の注入を 0° < < 90°、好ましくは 10° < < 85°、さらに好ましくは 20° < < 80° の角度から酸化物半導体層の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して行う (図 1 (B) 参照)。また、最も好ましくは、酸化物半導体層のチャネル幅方向の略平面に対して垂直な断面における側面に対して垂直となる角度から行う。また、酸素イオンの注入処理中に角度を変化させてもよい。なお、図 69 (A)、(B) に示す形態においては、上記同様の角度からブロック層 165 を介して酸化物半導体層の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して行う。

#### 【 0 0 6 2 】

また、イオン注入の条件としては、例えば、イオン種を  $^{16}\text{O}_2^+$ 、加速電圧を 5 kV、ドーズ量を  $1 \times 10^{-6} \text{ cm}^{-2}$  より少ない条件、またはイオン種を  $^{16}\text{O}^+$ 、加速電圧を 5 kV、ドーズ量を  $1 \times 10^{-5} \text{ cm}^{-2}$  より少ない条件で行えばよい。

10

20

30

40

50

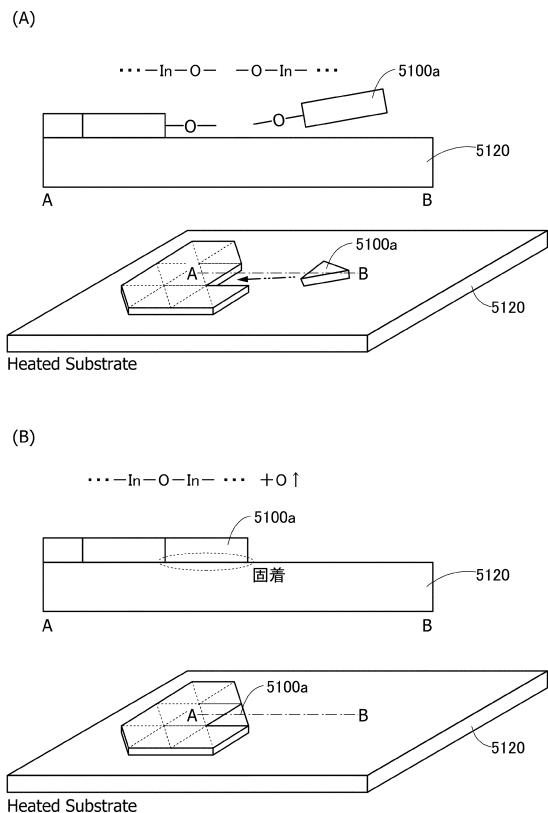

## 【0063】

上記のように酸化物半導体層の側面に酸素イオン40を注入することで、酸化物半導体層130の膜厚が厚い場合においても結晶を破壊させずに、かつ膜厚方向全体に酸素を供給することができる。特に、CAC-O<sub>5</sub>膜を用いた場合は、c軸方向と直交する方向に酸素が拡散しやすいため、酸化物半導体層130の側面に酸素イオン40を注入することで効率良く膜厚方向全体に酸素を供給することができる。

## 【0064】

CAC-O<sub>5</sub>膜におけるc軸方向と直交する方向（横方向）に酸素が拡散しやすい特徴について説明する。

## 【0065】

ここでは、CAC-O<sub>5</sub>膜の一例として、In-Ga-Zn酸化物（以下、IGZOと呼ぶ。）膜における、過剰酸素（化学量論比を越えて存在している酸素原子）および酸素欠損の動きやすさについて、科学計算結果を参照して説明する。

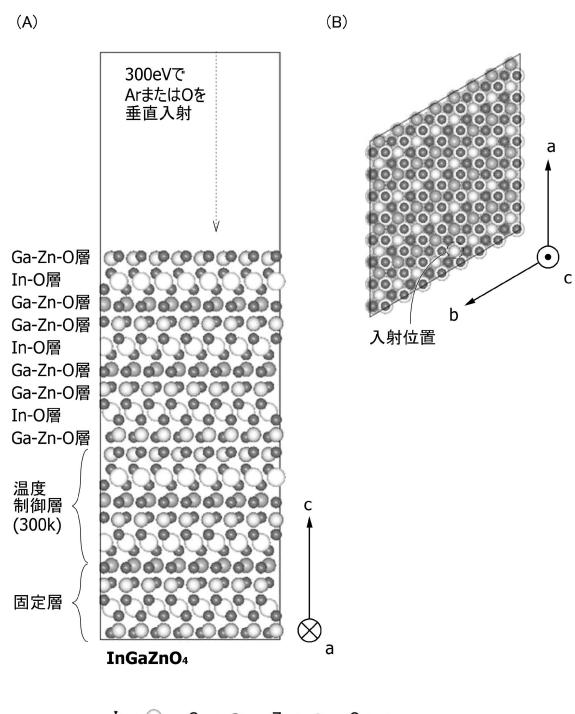

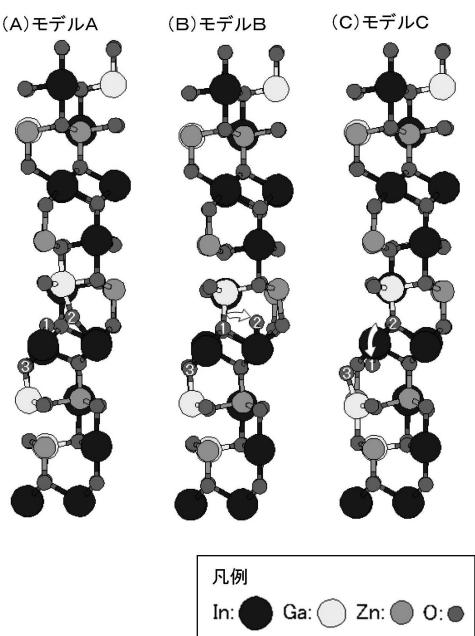

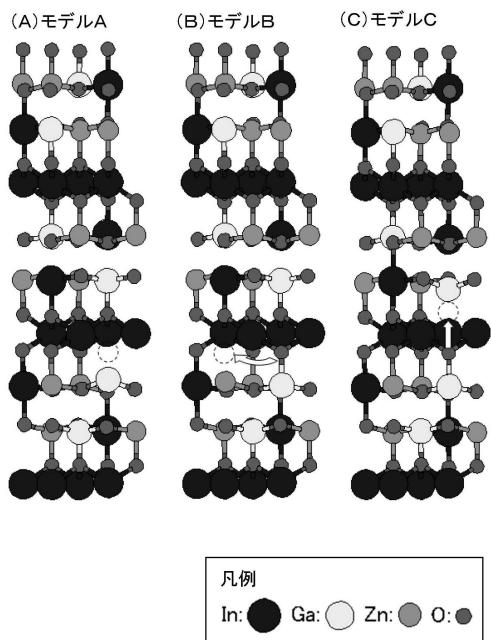

## 【0066】

なお、計算は、原子数比がIn:Ga:Zn=3:1:2となるIGZOのIn-O面に過剰酸素または酸素欠損が一つ存在するモデルを構造最適化によって作成（図60（A）乃至（C）および図62（A）乃至（C）を参照）し、NEB（Nudged Elastic Band）法を用いて最小エネルギー経路に沿った中間構造に対するエネルギーをそれぞれ算出した。

## 【0067】

計算は、密度汎関数理論（DFT）に基づく計算プログラムソフト「OpenMX」を用いて行った。パラメータについて以下に説明する。

## 【0068】

基底関数には、擬原子局在基底関数を用いた。この基底関数は、分極基底系STO（Slater Type Orbital）に分類される。

## 【0069】

汎関数には、GGA/PBE（Generalized-Gradient-Approximation/Perdew-Burke-Ernzerhof）を用いた。

## 【0070】

カットオフエネルギーは200 Ryとした。

## 【0071】

サンプリングk点は、5×5×3とした。

## 【0072】

過剰酸素の動きやすさについての計算では、計算モデル内に存在する原子の数を85個とし、酸素欠損の動きやすさについての計算では、計算モデル内に存在する原子の数を83個とした。

## 【0073】

過剰酸素または酸素欠損の動きやすさは、過剰酸素または酸素欠損が各々のサイトへ移動する際に越えることを要するエネルギーbarrierの高さE<sub>b</sub>を計算することにより評価する。すなわち、移動に際して越えるエネルギーbarrierの高さE<sub>b</sub>が高ければ移動しにくく、エネルギーbarrierの高さE<sub>b</sub>が低ければ移動しやすい。

## 【0074】

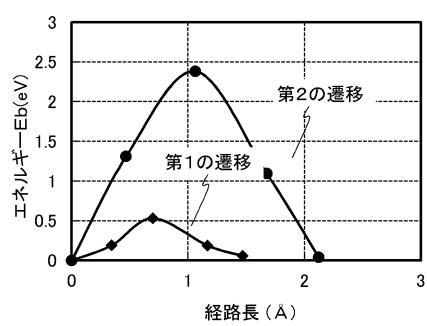

まず、過剰酸素の移動について説明する。過剰酸素の移動の計算に用いたモデルを図60に示す。なお、モデルの縦方向が結晶軸のc軸である。計算は、以下の2つの遷移形態について行った。計算結果は、図61に示す。図61では、横軸を（過剰酸素の移動の）経路長とし、縦軸を図60（A）のモデルAの状態のエネルギーに対する（移動に要する）エネルギーとしている。

## 【0075】

過剰酸素の移動について、上記2つの遷移形態のうち、第1の遷移は、モデルAからモデルBへの遷移である。第2の遷移は、モデルAからモデルCへの遷移である。

10

20

30

40

50

## 【0076】

なお、図60(A)乃至(C)中の”1”と表記されている酸素原子をモデルAの第1の酸素原子と呼ぶ。図60(A)乃至(C)中の”2”と表記されている酸素原子をモデルAの第2の酸素原子と呼ぶ。図60(A)乃至(C)中の”3”と表記されている酸素原子をモデルAの第3の酸素原子と呼ぶ。

## 【0077】

図61から明らかなように、第1の遷移のエネルギー・バリアの高さ $E_b$ の最大値( $E_{b_{max}}$ )は、0.53eVであり、第2の遷移のエネルギー・バリアの高さ $E_b$ の最大値( $E_{b_{max}}$ )は、2.38eVである。そのため、第1の遷移では第2の遷移よりもエネルギー・バリアの高さ $E_b$ の最大値( $E_{b_{max}}$ )が低い。そのため、第1の遷移に要するエネルギーは第2の遷移に要するエネルギーよりも小さく、第1の遷移のほうが第2の遷移よりも起こりやすいといえる。10

## 【0078】

すなわち、モデルAの第1の酸素原子の移動は、モデルAの第3の酸素原子を押し出す方向よりも、モデルAの第2の酸素原子を押し出す方向に移動しやすいといえる。したがって、酸素原子はインジウム原子の層を横断して移動するよりもインジウム原子の層に沿って移動しやすいといえる。

## 【0079】

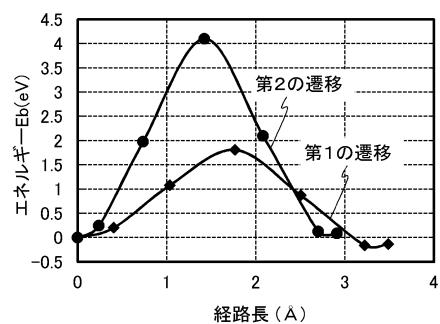

次に、酸素欠損の移動について説明する。酸素欠損の移動の計算に用いたモデルを図62に示す。計算は、以下の2つの遷移形態について行った。計算結果は、図63に示す。図63では、横軸を(酸素欠損の移動の)経路長とし、縦軸を図62(A)のモデルAの状態のエネルギーに対する(移動に要する)エネルギーとしている。20

## 【0080】

酸素欠損の移動について、上記2つの遷移形態のうち、第1の遷移は、モデルAからモデルBへの遷移である。第2の遷移は、モデルAからモデルCへの遷移である。

## 【0081】

なお、図62(A)乃至(C)中の点線で描画している丸は、酸素欠損を表している。

## 【0082】

図63から明らかなように、第1の遷移のエネルギー・バリアの高さ $E_b$ の最大値( $E_{b_{max}}$ )は、1.81eVであり、第2の遷移のエネルギー・バリアの高さ $E_b$ の最大値( $E_{b_{max}}$ )は、4.10eVである。そのため、第1の遷移では第2の遷移よりもエネルギー・バリアの高さ $E_b$ の最大値( $E_{b_{max}}$ )が低い。そのため、第1の遷移に要するエネルギーは第2の遷移に要するエネルギーよりも小さく、第1の遷移のほうが第2の遷移よりも起こりやすいといえる。30

## 【0083】

すなわち、モデルAの酸素欠損はモデルCの酸素欠損の位置よりも、モデルBの酸素欠損の位置のほうが移動しやすいといえる。したがって、酸素欠損もインジウム原子の層を横断して移動するよりもインジウム原子の層に沿って移動しやすいといえる。

## 【0084】

次に、前述した4つの遷移形態の起こりやすさを別の側面から比較するために、これらの遷移の温度依存性について説明する。前述した4つの遷移形態は、(1)過剰酸素の第1の遷移(2)過剰酸素の第2の遷移(3)酸素欠損の第1の遷移(4)酸素欠損の第2の遷移の4つである。40

## 【0085】

これらの遷移の温度依存性は、単位時間あたりの移動頻度により比較する。ここで、ある温度T(K)における移動頻度Z( /秒)は、化学的に安定な位置における酸素原子の振動数 $Z_0$ ( /秒)を用いると、以下の式で表される。

## 【0086】

## 【数1】

$$Z = Z_0 \cdot \exp\left(-\frac{E_{b_{\max}}}{kT}\right)$$

## 【0087】

なお、上記式において、 $E_{b_{\max}}$  は各遷移におけるエネルギー障壁の高さ  $E_b$  の最大値であり、 $k$  はボルツマン定数である。また、 $Z_0 = 1.0 \times 10^{13}$  ( /秒) を計算に用いる。

## 【0088】

過剰酸素または酸素欠損が 1 秒間あたりに 1 度だけエネルギー障壁の高さ  $E_b$  の最大値 ( $E_{b_{\max}}$ ) を越えて移動する場合 ( $Z = 1$  ( /秒) の場合)、 $T$  について式(1)を解くと以下の通りである。

- (1) 過剰酸素の第 1 の遷移  $Z = 1$  において  $T = 206\text{ K}$  (-67)

- (2) 過剰酸素の第 2 の遷移  $Z = 1$  において  $T = 923\text{ K}$  (650)

- (3) 酸素欠損の第 1 の遷移  $Z = 1$  において  $T = 701\text{ K}$  (428)

- (4) 酸素欠損の第 2 の遷移  $Z = 1$  において  $T = 1590\text{ K}$  (1317)

## 【0089】

一方、 $T = 300\text{ K}$  (27) の場合の  $Z$  は、以下の通りである。

- (1) 過剰酸素の第 1 の遷移  $T = 300\text{ K}$  において  $Z = 1.2 \times 10^4$  ( /秒)

- (2) 過剰酸素の第 2 の遷移  $T = 300\text{ K}$  において  $Z = 1.0 \times 10^{-27}$  ( /秒)

- (3) 酸素欠損の第 1 の遷移  $T = 300\text{ K}$  において  $Z = 4.3 \times 10^{-18}$  ( /秒)

- (4) 酸素欠損の第 2 の遷移  $T = 300\text{ K}$  において  $Z = 1.4 \times 10^{-56}$  ( /秒)

## 【0090】

また、 $T = 723\text{ K}$  (450) の場合の  $Z$  は、以下の通りである。

- (1) 過剰酸素の第 1 の遷移  $T = 723\text{ K}$  において  $Z = 2.0 \times 10^9$  ( /秒)

- (2) 過剰酸素の第 2 の遷移  $T = 723\text{ K}$  において  $Z = 2.5 \times 10^{-4}$  ( /秒)

- (3) 酸素欠損の第 1 の遷移  $T = 723\text{ K}$  において  $Z = 2.5$  ( /秒)

- (4) 酸素欠損の第 2 の遷移  $T = 723\text{ K}$  において  $Z = 2.5 \times 10^{-16}$  ( /秒)

## 【0091】

上記計算結果に鑑みると、過剰酸素は、 $T = 300\text{ K}$  においても  $T = 723\text{ K}$  においても、インジウム原子の層を横断して移動するよりもインジウム原子の層に沿って移動しやすいといえる。また、酸素欠損も、 $T = 300\text{ K}$  においても  $T = 723\text{ K}$  においても、インジウム原子の層を横断して移動するよりもインジウム原子の層に沿って移動しやすいといえる。

## 【0092】

また、 $T = 300\text{ K}$  において、インジウム原子の層に沿った過剰酸素の移動は非常に起こりやすいが、他の遷移形態は起こりにくい。 $T = 723\text{ K}$  においては、インジウム原子の層に沿う過剰酸素の移動のみならず、インジウム原子の層に沿う酸素欠損の移動も起こりやすいが、過剰酸素についても酸素欠損についてもインジウム原子の層を横断する移動は困難である。

## 【0093】

したがって、例えば C A A C - O S 膜のように、インジウム原子の層が当該膜の被形成面または表面に平行な面上に存在する場合には、過剰酸素および酸素欠損のいずれも当該膜の被形成面または表面に沿って移動しやすいといえる。

## 【0094】

以上説明したように、C A A C - O S 膜では当該膜の被形成面または表面に沿って過剰酸素は移動しやすい。したがって、酸化物半導体層が C A A C - O S 膜である場合、c 軸方向 (縦方向) よりも c 軸方向と直交する方向 (横方向) に酸素が拡散しやすいといえる。

## 【0095】

10

20

30

40

50

なお、上述した説明では過剰酸素または酸素欠損がインジウム原子の層を横断する場合について説明したが、酸化物半導体膜に含まれるインジウム以外の金属についても同様である。

#### 【0096】

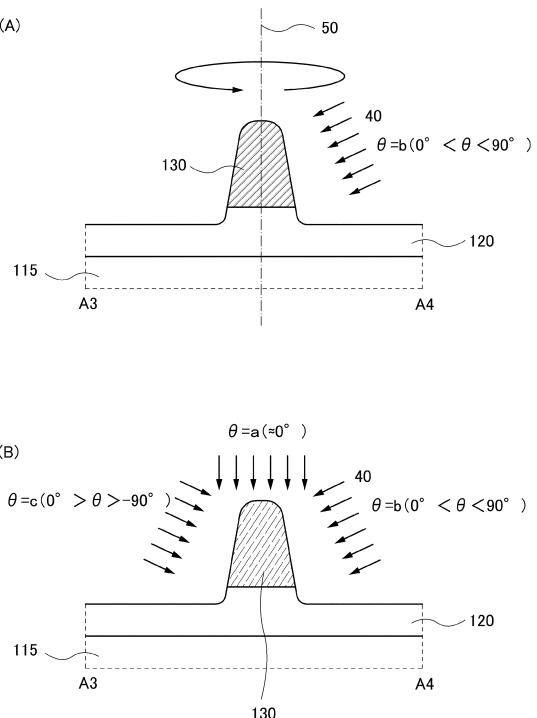

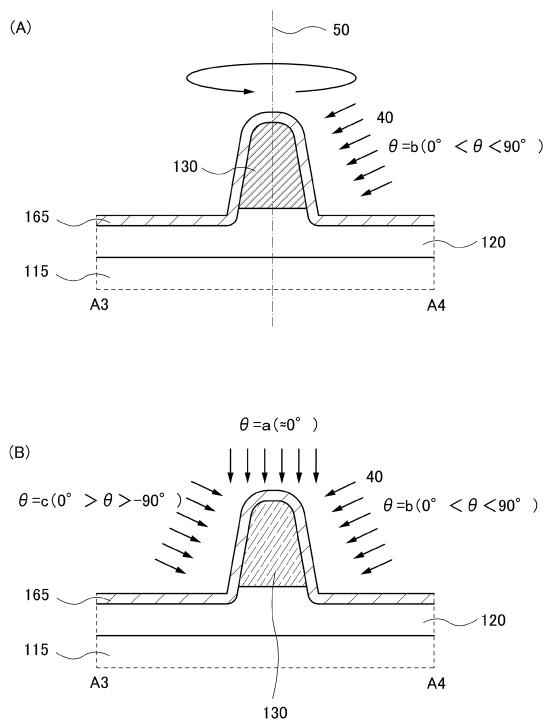

また、本発明に一態様においては、図2(A)に示すように、酸素イオン40の注入の角度を $0^\circ < \theta < 90^\circ$ 、好ましくは $10^\circ < \theta < 85^\circ$ 、さらに好ましくは $20^\circ < \theta < 80^\circ$ 、最も好ましくは酸化物半導体層130のチャネル幅方向の略平面に対して垂直な断面における側面に対して垂直となる角度とし、基板115または絶縁層120が有する略平面に垂直な軸50を中心に基板115を回転させながら行ってもよい。また、酸素イオン40の注入処理中に上記いずれかの範囲で角度を変化させながら基板115を回転させててもよい。なお、図69(A)、(B)に示す形態においては、図70(A)に示すように、ブロック層165を介して酸化物半導体層130に酸素イオン注入を行う。10

#### 【0097】

上記のように基板115を回転させながら酸素イオン40の注入を行うことにより、均一性よく酸化物半導体層130の膜厚方向全体に酸素を供給することができる。

#### 【0098】

また、本発明に一態様においては、図2(B)に示すように、酸素イオン40の注入の角度を略 $0^\circ$ の条件、および $0^\circ < \theta < 90^\circ$ 、好ましくは $10^\circ < \theta < 85^\circ$ 、さらに好ましくは $20^\circ < \theta < 80^\circ$ 、最も好ましくは酸化物半導体層130のチャネル幅方向の略平面に対して垂直な断面における側面に対して垂直となる角度の条件から酸化物半導体層130の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して複数回行ってもよい。例えば、 $\alpha = a$ (略 $0^\circ$ )で酸化物半導体層130の上面に対して酸素イオン40の注入を行い、 $\beta = b$ ( $0^\circ < \beta < 90^\circ$ )および $\gamma = c$ ( $0^\circ > \gamma > -90^\circ$ )で酸化物半導体層130の側面に対して酸素イオン40の注入を行う。また、酸素イオン注入を $\alpha = a$ および $\beta = b$ の組み合わせのみで行ってもよい。また、さらに複数の角度で酸素イオン注入を行ってもよい。また、基板115または絶縁層120が有する略平面に垂直な軸を中心に基板115を回転させながら行ってもよい。なお、図69(A)、(B)に示す形態においては、図70(B)に示すように、ブロック層165を介して酸化物半導体層130に酸素イオン注入を行う。20

#### 【0099】

上記のように複数の角度から酸化物半導体層130の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して複数回、酸素イオン40の注入を行うことにより、均一性よく酸化物半導体層130の膜厚方向全体に酸素を供給することができる。30

#### 【0100】

なお、酸化物半導体層130に注入した酸素イオン40(酸化物半導体層130中において酸素原子または酸素分子である状態を含む)を酸化物半導体層130の膜厚方向全体に拡散させるには熱処理を行うことが好ましい。ただし、酸素イオン40を注入した直後に熱処理を行うと酸化物半導体層130から酸素の脱離が起こりやすいため、酸素を通しつくい膜を酸化物半導体層130を覆うように設けてから熱処理を行うことが好ましい。なお、熱処理は、炉などで行うほか、RTA(Rapid thermal anneal)法で行ってもよい。図69(A)、(B)に示す形態における酸化物半導体層130に接するブロック層165は、酸素脱離を抑える効果も有する。40

#### 【0101】

ブロック層165としては、酸化シリコン膜や酸化窒化シリコン膜などの酸化膜を用いることができる。この場合、当該酸化膜はゲート絶縁膜として用いることもできる。

#### 【0102】

また、ブロック層165として酸化物半導体層を用いることができる。例えば、チャネルが形成される領域を第1の酸化物半導体層とし、当該第1の酸化物半導体層がInと、Znと、M(MはAl、Ti、Ga、Y、Zr、La、Ce、NdまたはHf)とを有する場合、ブロック層には、Inに対するMの原子数比が第1の酸化物半導体層よりも大きい50

第2の酸化物半導体層を用いることができる。また、第2の酸化物半導体層には、酸化ガリウムなどの酸化物半導体を用いることもできる。

#### 【0103】

具体的には、第1の酸化物半導体層は  $In : Ga : Zn = 1 : 1 : 1$  (原子数比) で形成し、第2の酸化物半導体層は  $In : Ga : Zn = 1 : 3 : 2$  (原子数比) や  $In : Ga : Zn = 1 : 3 : 4$  (原子数比) などで形成すればよい。また、第2の酸化物半導体層は第1の酸化物半導体層の表面に対して垂直方向に c 軸配向している結晶を有することが好ましい。

#### 【0104】

上記第2の酸化物半導体層が酸素をブロックする層として適用可能であることを説明する。

10

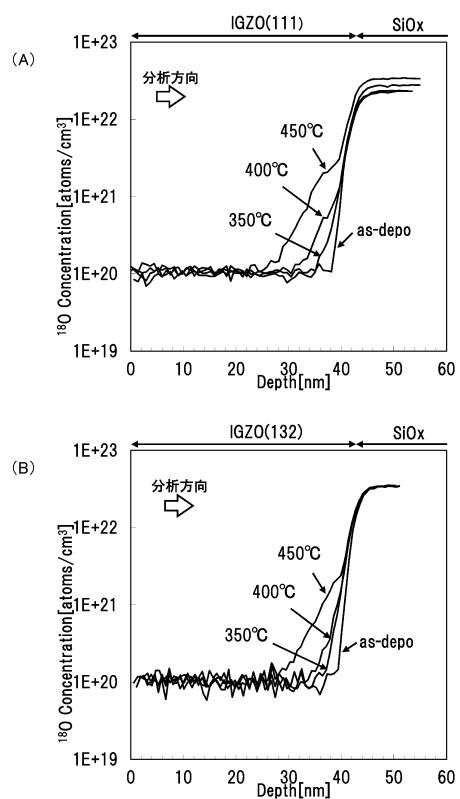

#### 【0105】

図64(A)、(B)は酸化シリコン膜上に組成の異なる酸化物半導体膜を形成し、各種熱処理を施した後の酸素のSIMS (Secondary Ion Mass Spectrometry) 分析結果である。なお、当該酸化シリコン膜は酸素の同位体である  $^{18}O_2$  をスペッタガスとして用いたスペッタ法で形成したものであり、酸化物半導体膜中の酸素は  $^{18}O$  を分析することで酸化シリコン膜から酸化物半導体膜に拡散する酸素を定量することができる。また、熱処理は 350、400、450 の各温度において、窒素雰囲気で 1 時間、酸素雰囲気で 1 時間行っている。

#### 【0106】

図64(A)は、上記第1の酸化物半導体層として用いることのできる  $In : Ga : Zn = 1 : 1 : 1$  (原子数比) の酸化物半導体膜の  $^{18}O$  のデプスプロファイルである。また、図64(B)は、上記第2の酸化物半導体層として用いることのできる  $In : Ga : Zn = 1 : 3 : 2$  (原子数比) の酸化物半導体膜の  $^{18}O$  のデプスプロファイルである。両者を比べると  $In : Ga : Zn = 1 : 3 : 2$  (原子数比) の酸化物半導体膜の方が酸素 ( $^{18}O$ ) の拡散量が少ないことがわかる。すなわち、 $In : Ga : Zn = 1 : 3 : 2$  (原子数比) の酸化物半導体膜は相対的に酸素が拡散しにくいといえる。

20

#### 【0107】

また、 $In - Ga - Zn$  酸化物の結晶性と酸素透過性との関係を説明する。

#### 【0108】

$In - Ga - Zn$  酸化物の結晶における、過剰酸素 (酸素) の移動に係るエネルギー障壁について計算により求める。計算には、密度汎関数理論に基づく平面波基底第一原理計算ソフトVASP (Vienna ab initio simulation package) を用いる。なお、汎関数としてはGGA-PBEを用いる。また、平面波のカットオフエネルギーを 400 eV とする。また、PAW (Projector Augmented Wave) 法により内殻電子の効果を取り入れる。

30

#### 【0109】

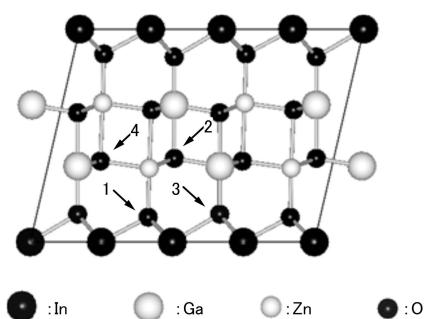

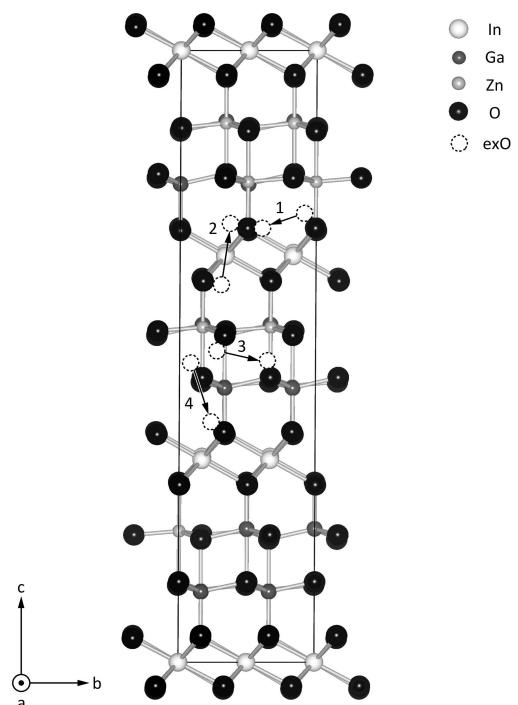

ここでは、図65に示す $In - Ga - Zn$  酸化物の結晶において、過剰酸素 (酸素) の移動経路1、移動経路2、移動経路3および移動経路4の移動しやすさを計算する。

#### 【0110】

なお、移動経路1は、三つのインジウム原子および一つの亜鉛原子と結合した酸素に結合した過剰酸素 (酸素) が、隣接する三つのインジウム原子および一つの亜鉛原子と結合した酸素に結合する経路である。また、移動経路2は、三つのインジウム原子および一つのガリウム原子と結合した酸素に結合した過剰酸素 (酸素) が、インジウムおよび酸素を含む層を横切って、隣接する三つのインジウム原子および一つの亜鉛原子と結合した酸素に結合する経路である。また、移動経路3は、二つのガリウム原子および一つの亜鉛原子と結合した酸素に結合した過剰酸素 (酸素) が、隣接する二つの亜鉛原子および一つのガリウム原子と結合した酸素に結合する経路である。また、移動経路4は、二つのガリウム原子および一つの亜鉛原子と結合した酸素に結合した過剰酸素 (酸素) が、ガリウム、亜鉛および酸素を含む層を横切って、隣接する三つのインジウム原子および一つのガリウム原

40

50

子と結合した酸素に結合する経路である。

【0111】

単位時間当たりに拡散のエネルギー障壁  $E_a$  を越える頻度を拡散頻度 R とすると、R は下に示す式で表すことができる。

【0112】

$$R = \cdot e \times p [ - E_a / (k_B T) ]$$

【0113】

なお、 $\cdot$  は拡散原子の熱振動の振動数、 $k_B$  はボルツマン定数、T は絶対温度である。

にデバイ振動数として  $10^{13} [1/\text{sec}]$  を与えた場合の、350 および 450

における拡散頻度 R は表 1 のようになる。

【0114】

【表 1】

|       | エネルギー障壁<br>[eV] | 拡散頻度 R [1/sec]       |                      |

|-------|-----------------|----------------------|----------------------|

|       |                 | 350°C                | 450°C                |

| 移動経路1 | 0.50            | $9.0 \times 10^8$    | $3.3 \times 10^9$    |

| 移動経路2 | 1.97            | $1.2 \times 10^{-3}$ | $1.9 \times 10^{-1}$ |

| 移動経路3 | 0.53            | $5.2 \times 10^8$    | $2.0 \times 10^9$    |

| 移動経路4 | 0.56            | $3.0 \times 10^8$    | $1.3 \times 10^9$    |

【0115】

表 1 に示すように、インジウムおよび酸素を含む層を横切る移動経路 2 において、他の移動経路よりも高いエネルギー障壁を有することがわかる。これは、In-Ga-Zn 酸化物の結晶は、c 軸方向における過剰酸素（酸素）の移動が起こりにくいことを示している。即ち、CAAC-OS などのように、c 軸配向性を有し、被形成面または上面に概略垂直な方向を向いている構造を有する場合、被形成面または上面に概略垂直な方向における過剰酸素（酸素）の移動が起こりにくいことを示している。

【0116】

つまり、第 2 の酸化物半導体層として、第 1 の酸化物半導体層の表面に対して垂直方向に c 軸配向している酸化物半導体層を用いることで酸素のブロック性を高めることができる。

【0117】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0118】

（実施の形態 2）

本実施の形態では、実施の形態 1 で説明した酸化物半導体層に酸素を供給する方法を用いて作製することのできるトランジスタについて図面を用いて説明する。

【0119】

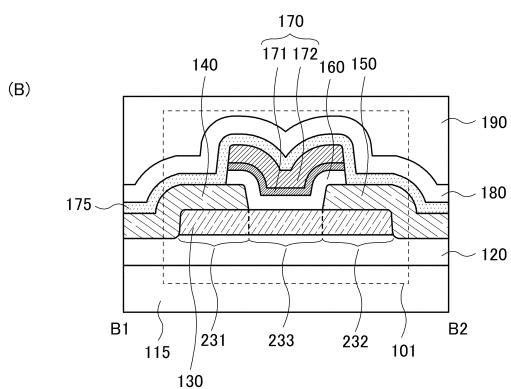

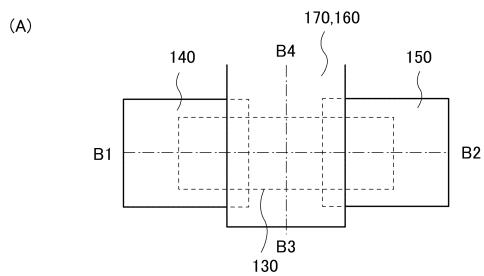

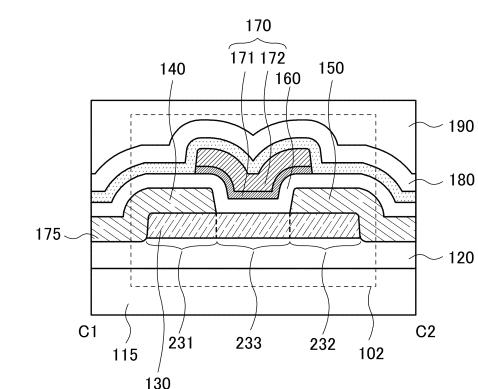

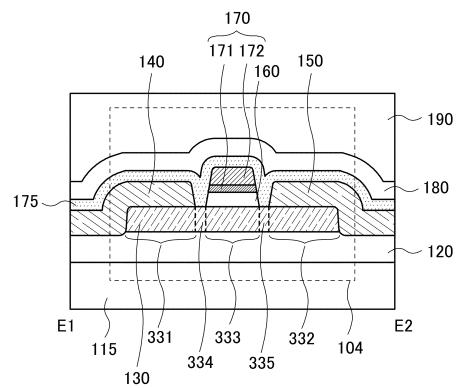

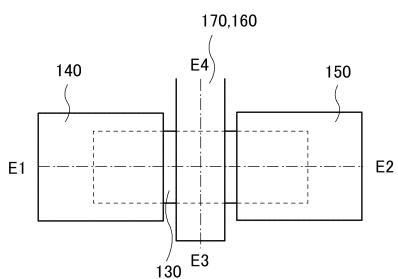

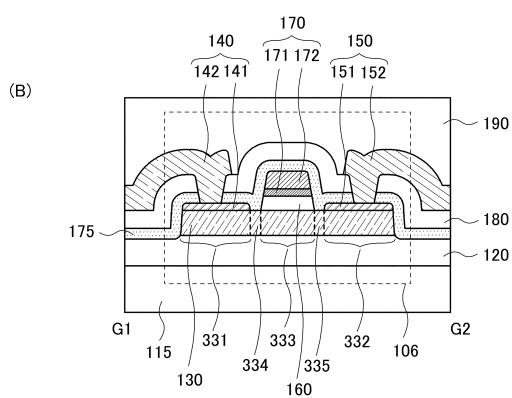

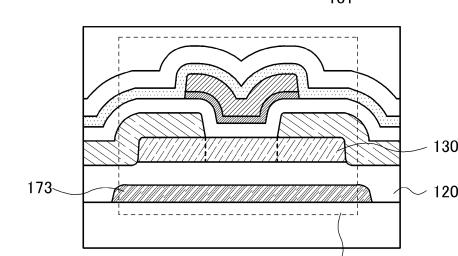

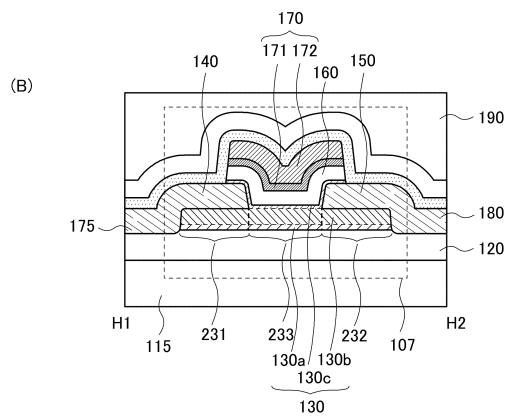

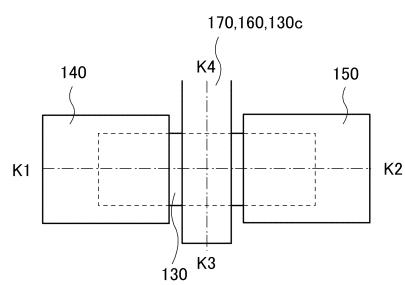

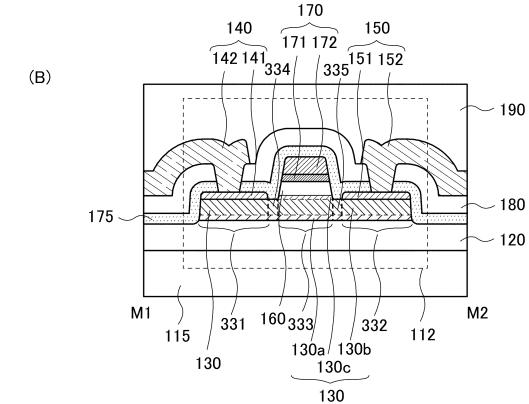

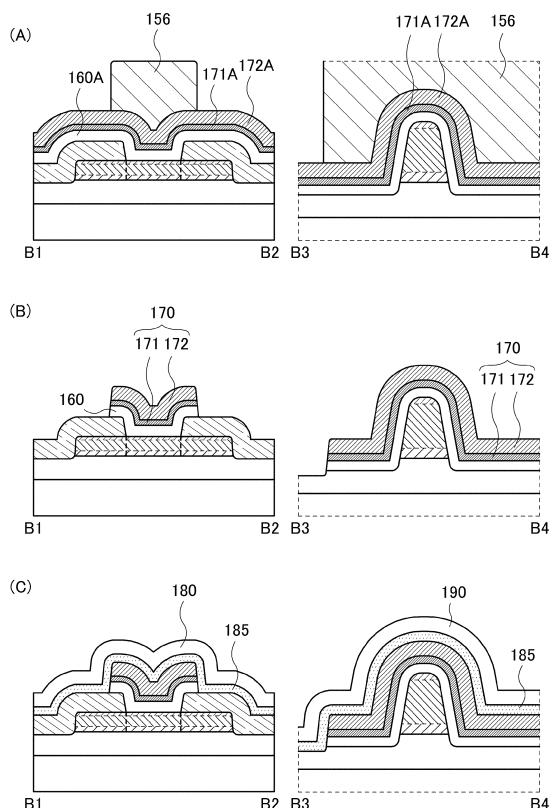

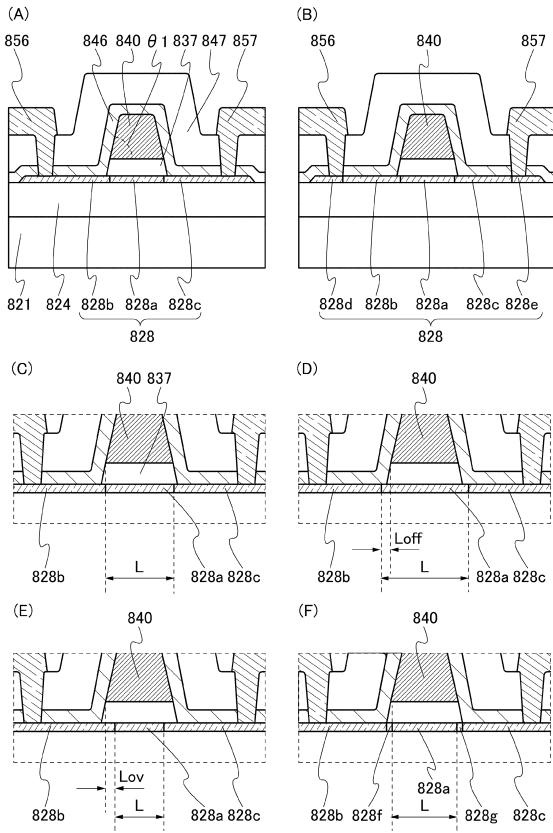

図 3 (A)、(B) は、本発明の一態様のトランジスタ 101 の上面図および断面図である。図 3 (A) は上面図であり、図 3 (A) に示す一点鎖線 B1-B2 方向の断面が図 3 (B) に相当する。また、図 3 (A) に示す一点鎖線 B3-B4 方向の断面が図 9 に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線 B1-B2 方向をチャネル長方向、一点鎖線 B3-B4 方向をチャネル幅方向と呼称する場合がある。

【0120】

トランジスタ 101 は、基板 115 と接する絶縁層 120 と、絶縁層 120 と接する酸化物半導体層 130 と、酸化物半導体層 130 と電気的に接続する導電層 140 および導電層 150 と、酸化物半導体層 130 、導電層 140 および導電層 150 と接する絶縁層 1

10

20

30

40

50

60と、絶縁層160と接する導電層170と、導電層140、導電層150、絶縁層160および導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、を有する。また、必要に応じて絶縁層180に接する絶縁層190(平坦化膜)などを有していてもよい。

#### 【0121】

ここで、導電層140はソース電極層、導電層150はドレイン電極層、絶縁層160はゲート絶縁膜、導電層170はゲート電極層としてそれぞれ機能することができる。

#### 【0122】

また、図3(B)に示す領域231はソース領域、領域232はドレイン領域、領域233はチャネル形成領域として機能することができる。領域231および領域232は導電層140および導電層150とそれぞれ接しており、例えば導電層140および導電層150として酸素と結合しやすい導電材料を用いれば領域231および領域232を低抵抗化することができる。

10

#### 【0123】

具体的には、酸化物半導体層130と導電層140および導電層150とが接することで酸化物半導体層130内に酸素欠損が生じ、当該酸素欠損と酸化物半導体層130内に残留または外部から拡散する水素との相互作用により、領域231および領域232は低抵抗のn型となる。

#### 【0124】

なお、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合には入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。また、「電極層」は、「配線」と言い換えることもできる。

20

#### 【0125】

また、導電層170は、導電層171および導電層172の二層で形成される例を図示しているが、一層または三層以上の積層であってもよい。当該構成は本実施の形態で説明する他のトランジスタにも適用できる。

#### 【0126】

また、導電層140および導電層150は単層で形成される例を図示しているが、二層以上の積層であってもよい。当該構成は本実施の形態で説明する他のトランジスタにも適用できる。

30

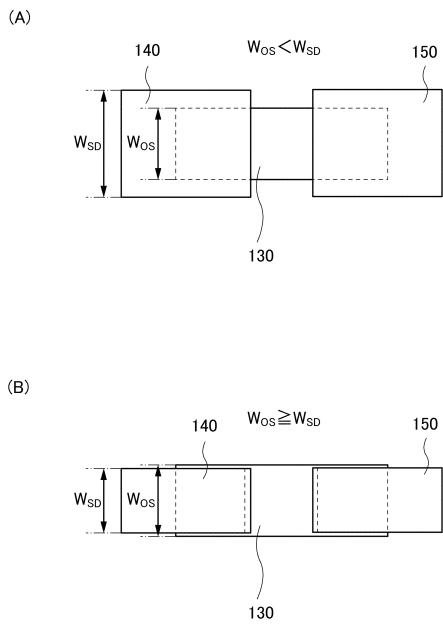

#### 【0127】

また、本発明の一態様のトランジスタにおける導電層140(ソース電極層)および導電層150(ドレイン電極層)は、図58(A)、(B)に示す上面図(酸化物半導体層130、導電層140および導電層150のみを図示)のように酸化物半導体層の幅( $W_{o_s}$ )よりも導電層140および導電層150の幅( $W_{s_D}$ )が長く形成されていてもよいし、短く形成されていてもよい。 $W_{o_s} > W_{s_D}$ ( $W_{s_D}$ は $W_{o_s}$ 以下)とすることで、ゲート電界が酸化物半導体層130全体にかかりやすくなり、トランジスタの電気特性を向上させることができる。当該構成は本実施の形態で説明する他のトランジスタにも適用できる。

40

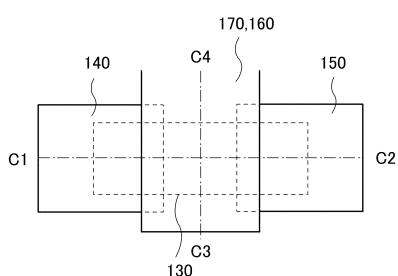

#### 【0128】

また、本発明の一態様のトランジスタは、図4(A)、(B)に示す構成であってもよい。図4(A)はトランジスタ102の上面図であり、図4(A)に示す一点鎖線C1-C2方向の断面が図4(B)に相当する。また、図4(A)に示す一点鎖線C3-C4方向の断面は、図9に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線C1-C2方向をチャネル長方向、一点鎖線C3-C4方向をチャネル幅方向と呼称する場合がある。

#### 【0129】

トランジスタ102は、ゲート絶縁膜として作用する絶縁層160がゲート電極層として

50

作用する導電層 170 と端部を一致させない点を除き、トランジスタ 101 と同様の構成を有する。トランジスタ 102 の構造は、導電層 140 および導電層 150 が絶縁層 160 で広く覆われているため、導電層 140 および導電層 150 と導電層 170 との間の抵抗が高く、ゲートリーク電流の少ない特徴を有している。

#### 【0130】

トランジスタ 101 およびトランジスタ 102 は、導電層 170 と導電層 140 および導電層 150 が重なる領域を有するトップゲート構造である。当該領域のチャネル長方向の幅は、寄生容量を小さくするために 3 nm 以上 300 nm 未満とすることが好ましい。一方で、酸化物半導体層 130 にオフセット領域が形成されないため、オン電流の高いトランジスタを形成しやすい。

10

#### 【0131】

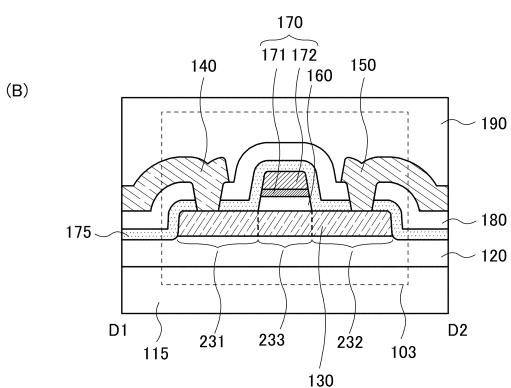

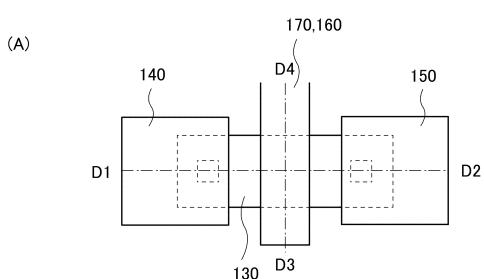

また、本発明の一態様のトランジスタは、図 5 (A)、(B) に示す構成であってもよい。図 5 (A) はトランジスタ 103 の上面図であり、図 5 (A) に示す一点鎖線 D1 - D2 方向の断面が図 5 (B) に相当する。また、図 5 (A) に示す一点鎖線 D3 - D4 方向の断面は、図 9 に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線 D1 - D2 方向をチャネル長方向、一点鎖線 D3 - D4 方向をチャネル幅方向と呼称する場合がある。

#### 【0132】

トランジスタ 103 は、基板 115 と接する絶縁層 120 と、絶縁層 120 と接する酸化物半導体層 130 と、酸化物半導体層 130 と接する絶縁層 160 と、絶縁層 160 と接する導電層 170 と、酸化物半導体層 130 、絶縁層 160 および導電層 170 を覆う絶縁層 175 と、絶縁層 175 と接する絶縁層 180 と、絶縁層 175 および絶縁層 180 に設けられた開口部を通じて酸化物半導体層 130 と電気的に接続する導電層 140 および導電層 150 を有する。また、必要に応じて絶縁層 180 、導電層 140 および導電層 150 に接する絶縁層 190 (平坦化膜)などを有していてもよい。

20

#### 【0133】

ここで、導電層 140 はソース電極層、導電層 150 はドレイン電極層、絶縁層 160 はゲート絶縁膜、導電層 170 はゲート電極層としてそれぞれ機能することができる。

#### 【0134】

また、図 5 (B) に示す領域 231 はソース領域、領域 232 はドレイン領域、領域 233 はチャネル形成領域として機能することができる。領域 231 および領域 232 は絶縁層 175 と接しており、例えば絶縁層 175 として水素を含む絶縁材料を用いれば領域 231 および領域 232 を低抵抗化することができる。

30

#### 【0135】

具体的には、絶縁層 175 を形成するまでの工程により領域 231 および領域 232 に生じる酸素欠損と、絶縁層 175 から領域 231 および領域 232 に拡散する水素との相互作用により、領域 231 および領域 232 は低抵抗の n 型となる。なお、水素を含む絶縁材料としては、例えば窒化シリコン膜や窒化アルミニウム膜などを用いることができる。

#### 【0136】

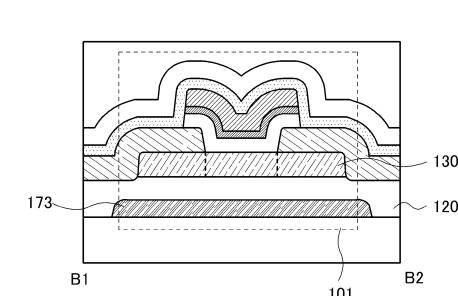

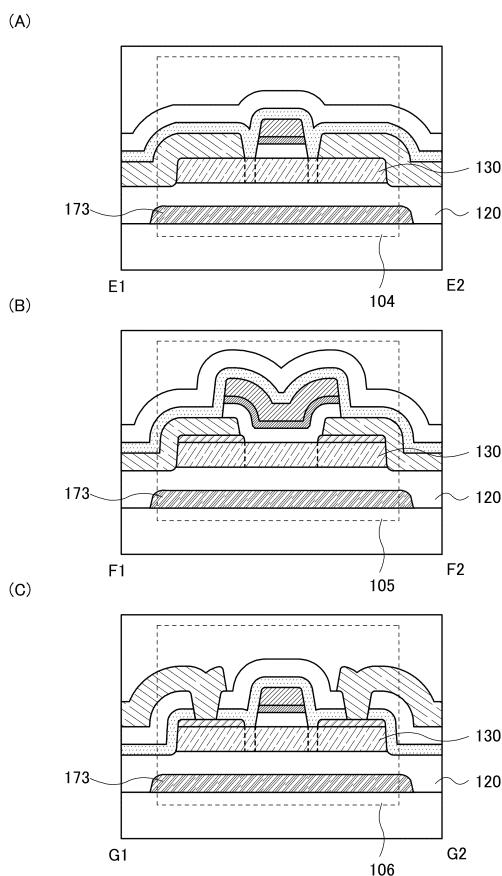

また、本発明の一態様のトランジスタは、図 6 (A)、(B) に示す構成であってもよい。図 6 (A) はトランジスタ 104 の上面図であり、図 6 (A) に示す一点鎖線 E1 - E2 方向の断面が図 6 (B) に相当する。また、図 6 (A) に示す一点鎖線 E3 - E4 方向の断面は、図 9 に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線 E1 - E2 方向をチャネル長方向、一点鎖線 E3 - E4 方向をチャネル幅方向と呼称する場合がある。

40

#### 【0137】

トランジスタ 104 は、導電層 140 および導電層 150 が酸化物半導体層の端部を覆うように接している点を除き、トランジスタ 103 と同様の構成を有する。

#### 【0138】

また、図 6 (B) に示す領域 331 および領域 334 はソース領域、領域 332 および領

50

域335はドレイン領域、領域333はチャネル形成領域として機能することができる。領域331および領域332はトランジスタ101における領域231および領域232と同様に低抵抗化することができる。また、領域334および領域335はトランジスタ103における領域231および領域232と同様に低抵抗化することができる。なお、チャネル長方向における領域334および領域335の幅が100nm以下、好ましくは50nm以下の場合には、ゲート電界の寄与によりオン電流は大きく低下しないため、上述したような低抵抗化を行わない構成とすることもできる。

#### 【0139】

トランジスタ103およびトランジスタ104は、導電層170と導電層140および導電層150が重なる領域を有さないセルフアライン構造である。10セルフアライン構造のトランジスタはゲート電極層とソース電極層およびドレイン電極層間の寄生容量が極めて小さいため、高速動作用途に適している。

#### 【0140】

また、本発明の一態様のトランジスタは、図7(A)、(B)に示す構成であってもよい。20図7(A)はトランジスタ105の上面図であり、図7(A)に示す一点鎖線F1-F2方向の断面が図7(B)に相当する。また、図7(A)に示す一点鎖線F3-F4方向の断面は、図9に相当。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線F1-F2方向をチャネル長方向、一点鎖線F3-F4方向をチャネル幅方向と呼称する場合がある。

#### 【0141】

トランジスタ105は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130と、酸化物半導体層130と電気的に接続する導電層141および導電層151と、酸化物半導体層130、導電層141、導電層151と接する絶縁層160と、絶縁層160と接する導電層170と、酸化物半導体層130、導電層141、導電層151、絶縁層160および導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する。また、必要に応じて絶縁層180、導電層142および導電層152に接する絶縁層190(平坦化膜)などを有していてもよい。

#### 【0142】

ここで、導電層141および導電層151は、酸化物半導体層130の上面と接し、側面には接しない構成となっている。

#### 【0143】

トランジスタ105は、導電層141および導電層151を有する点、および絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する点を除き、トランジスタ101と同様の構成を有する。導電層140(導電層141および導電層142)はソース電極層として作用させることができ、導電層150(導電層151および導電層152)はドレイン電極層として作用させることができる。

#### 【0144】

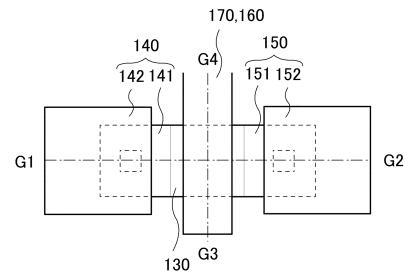

また、本発明の一態様のトランジスタは、図8(A)、(B)に示す構成であってもよい。40図8(A)はトランジスタ106の上面図であり、図8(A)に示す一点鎖線G1-G2方向の断面が図8(B)に相当する。また、図8(A)に示す一点鎖線G3-G4方向の断面は、図9に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線G1-G2方向をチャネル長方向、一点鎖線G3-G4方向をチャネル幅方向と呼称する場合がある。

#### 【0145】

トランジスタ106は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130と、酸化物半導体層130と電気的に接続する導電層141および導電層151と、酸化物半導体層130と接する絶縁層160と、絶縁層160と接する導電

10

20

30

40

50

層 170 と、絶縁層 120、酸化物半導体層 130、導電層 141、導電層 151、絶縁層 160、導電層 170 と接する絶縁層 175 と、絶縁層 175 と接する絶縁層 180 と、絶縁層 175 および絶縁層 180 に設けられた開口部を通じて導電層 141 および導電層 151 とそれぞれ電気的に接続する導電層 142 および導電層 152 を有する。また、必要に応じて絶縁層 180、導電層 142 および導電層 152 に接する絶縁層 190（平坦化膜）などを有していてもよい。

#### 【0146】

ここで、導電層 141 および導電層 151 は、酸化物半導体層 130 の上面と接し、側面には接しない構成となっている。

#### 【0147】

トランジスタ 106 は、導電層 141 および導電層 151 を有する点を除き、トランジスタ 103 と同様の構成を有する。導電層 140（導電層 141 および導電層 142）はソース電極層として作用させることができ、導電層 150（導電層 151 および導電層 152）はソース電極層として作用させることができる。

#### 【0148】

トランジスタ 105 およびトランジスタ 106 の構成では、導電層 140 および導電層 150 が絶縁層 120 と接しない構成であるため、絶縁層 120 中の酸素が導電層 140 および導電層 150 に奪われにくくなり、絶縁層 120 から酸化物半導体層 130 中への酸素の供給を容易とすることができます。

#### 【0149】

なお、トランジスタ 103 における領域 231 および領域 232、トランジスタ 104 およびトランジスタ 106 における領域 334 および領域 335 には、酸素欠損を形成し導電率を高めるための不純物を添加してもよい。酸化物半導体層に酸素欠損を形成する不純物としては、例えは、リン、砒素、アンチモン、ホウ素、アルミニウム、シリコン、窒素、ヘリウム、ネオン、アルゴン、クリプトン、キセノン、インジウム、フッ素、塩素、チタン、亜鉛、および炭素のいずれかから選択される一つ以上を用いることができる。当該不純物の添加方法としては、プラズマ処理法、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。

#### 【0150】

不純物元素として、上記元素が酸化物半導体層に添加されると、酸化物半導体層中の金属元素および酸素の結合が切断され、酸素欠損が形成される。酸化物半導体膜に含まれる酸素欠損と酸化物半導体層中に残存または後から添加される水素の相互作用により、酸化物半導体層の導電率を高くすることができる。

#### 【0151】

なお、不純物元素の添加により酸素欠損が形成された酸化物半導体に水素を添加すると、酸素欠損サイトに水素が入り伝導帯近傍にドナー準位が形成される。その結果、酸化物導電体を形成することができる。このため、酸化物導電体は透光性を有する。なお、ここでは、導電体化された酸化物半導体を酸化物導電体という。

#### 【0152】

酸化物導電体は、縮退半導体であり、伝導帯端とフェルミ準位とが一致または略一致していると推定される。このため、酸化物導電体層とソース電極層およびドレイン電極層として機能する導電層との接触はオーミック接触であり、酸化物導電体層とソース電極層およびドレイン電極層として機能する導電層との接触抵抗を低減することができる。

#### 【0153】

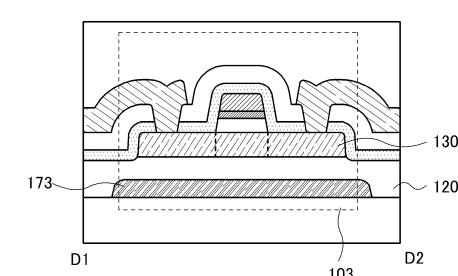

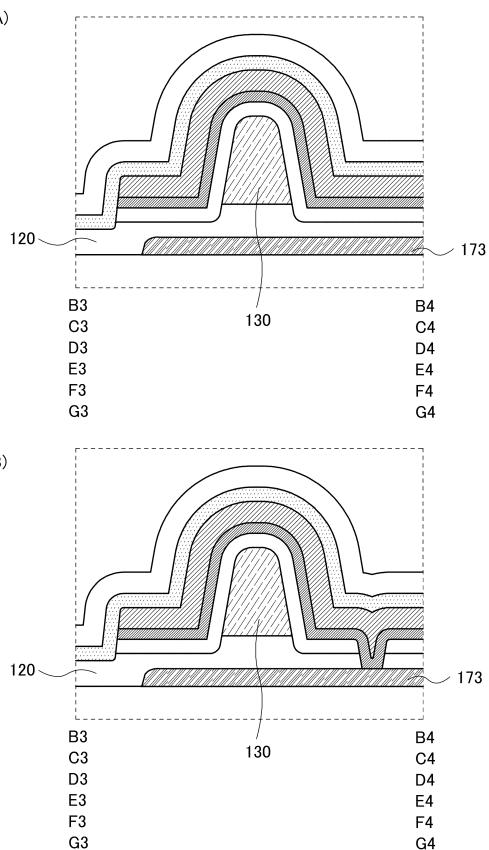

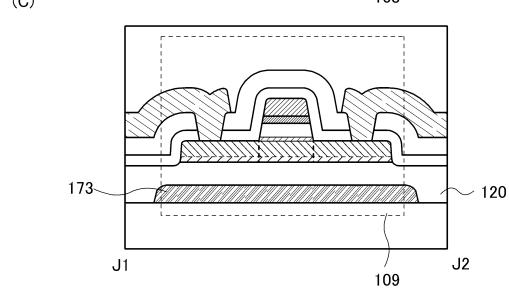

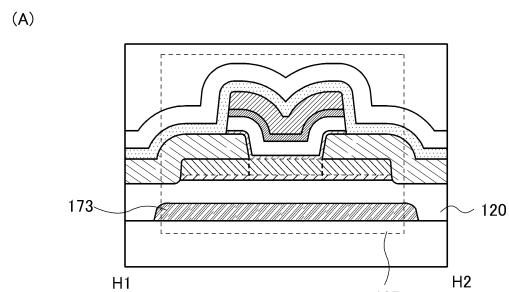

また、本発明の一態様のトランジスタは、図 10(A)、(B)、(C) および図 11(A)、(B)、(C) に示すチャネル長方向の断面図、ならびに図 12(A)、(B) に示すチャネル幅方向の断面図のように、酸化物半導体層 130 と基板 115 との間に導電層 173 を備えていてもよい。当該導電層を第 2 のゲート電極層（バックゲート）として用いることで、更なるオン電流の増加や、しきい値電圧の制御を行うことができる。なお、図 10(A)、(B)、(C) および図 11(A)、(B)、(C) に示す断面図にお

10

20

30

40

50

いて、導電層 173 の幅を酸化物半導体層 130 よりも短くしてもよい。さらに、導電層 173 の幅を導電層 170 の幅よりも短くしてもよい。

#### 【0154】

オン電流を増加させるには、例えば、導電層 170 と導電層 173 を同電位とし、ダブルゲートトランジスタとして駆動させればよい。また、しきい値電圧の制御を行うには、導電層 170 とは異なる定電位を導電層 173 に供給すればよい。導電層 170 と導電層 173 を同電位とするには、例えば、図 12 (B) に示すように、導電層 170 と導電層 173 とをコンタクトホールを介して電気的に接続すればよい。

#### 【0155】

また、図 3 乃至図 8 におけるトランジスタ 101 乃至トランジスタ 106 では、酸化物半導体層 130 が単層である例を図示したが、酸化物半導体層 130 は積層であってもよい。トランジスタ 101 乃至トランジスタ 106 の酸化物半導体層 130 は、図 13 または図 14 に示す酸化物半導体層 130 に入れ替えることができる。

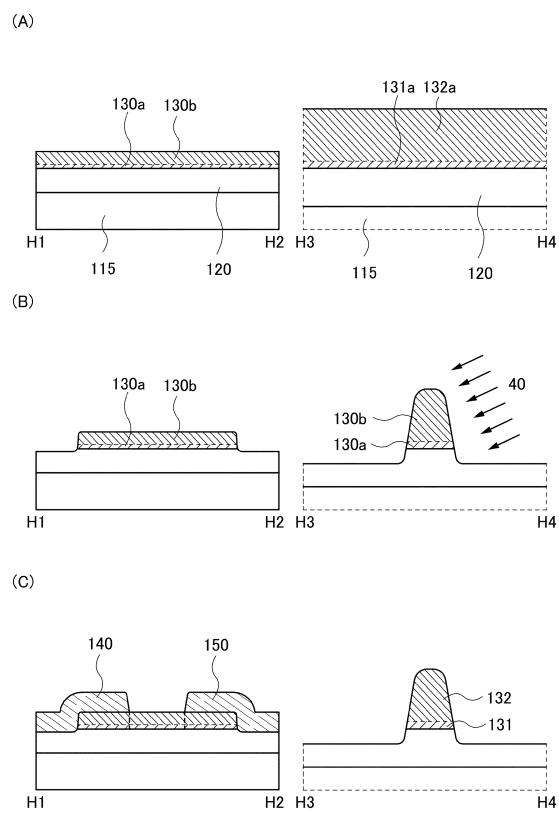

#### 【0156】

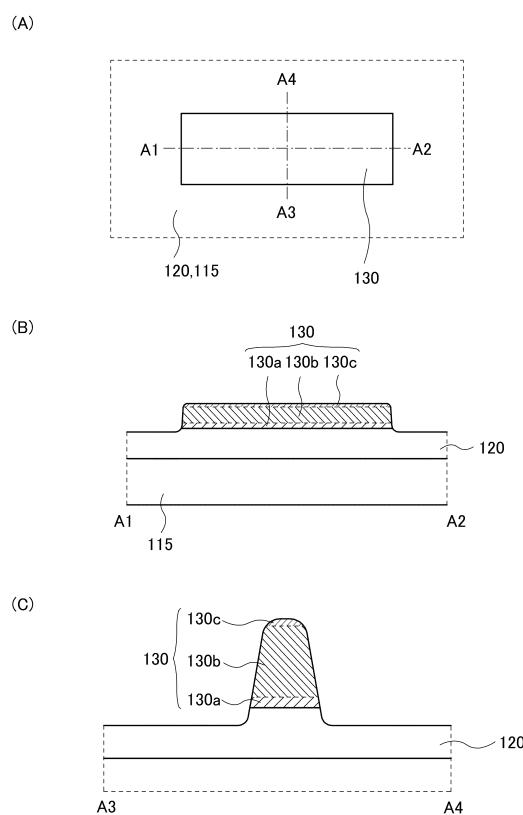

図 13 (A)、(B)、(C) は、二層構造である酸化物半導体層 130 の上面図および断面図である。図 13 (A) は上面図であり、図 13 (A) に示す一点鎖線 A1 - A2 方向の断面が図 13 (B) に相当する。また、図 13 (A) に示す一点鎖線 A3 - A4 方向の断面が図 13 (C) に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。

#### 【0157】

また、図 14 (A)、(B)、(C) は、三層構造である酸化物半導体層 130 の上面図および断面図である。図 14 (A) は上面図であり、図 14 (A) に示す一点鎖線 A1 - A2 方向の断面が図 14 (B) に相当する。また、図 14 (A) に示す一点鎖線 A3 - A4 方向の断面が図 14 (C) に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。

#### 【0158】

酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c には、それぞれ組成の異なる酸化物半導体層などを用いることができる。

#### 【0159】

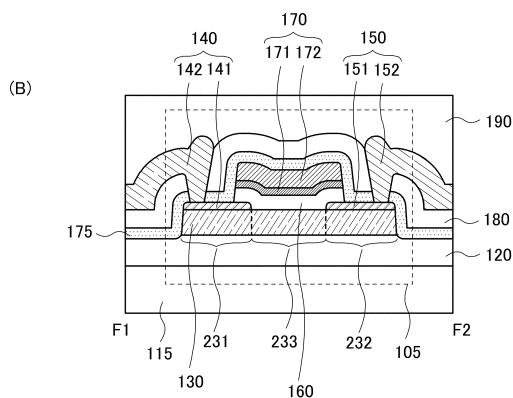

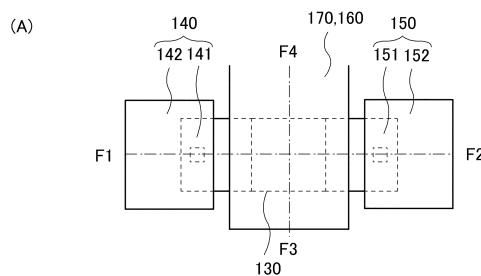

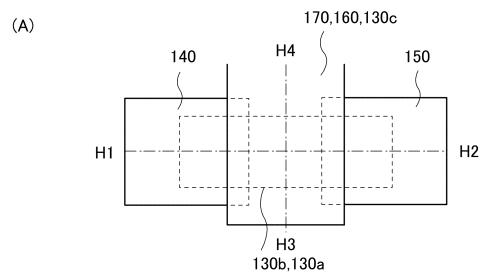

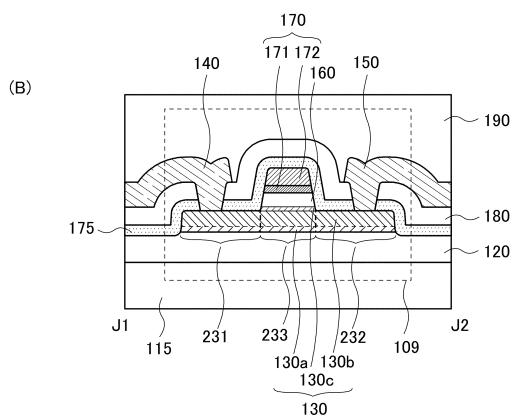

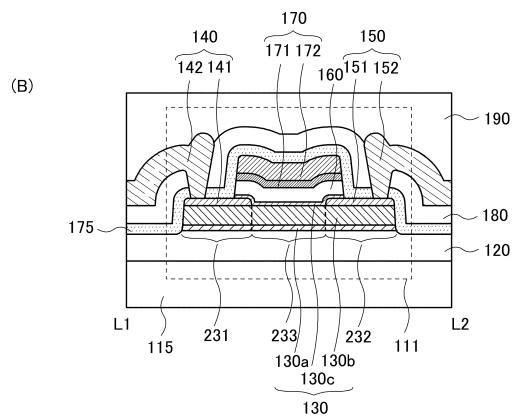

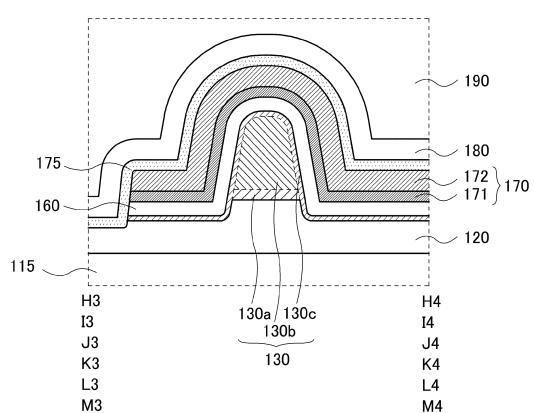

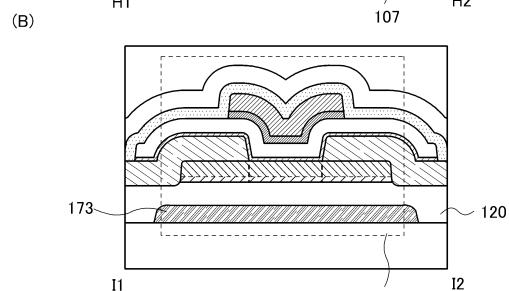

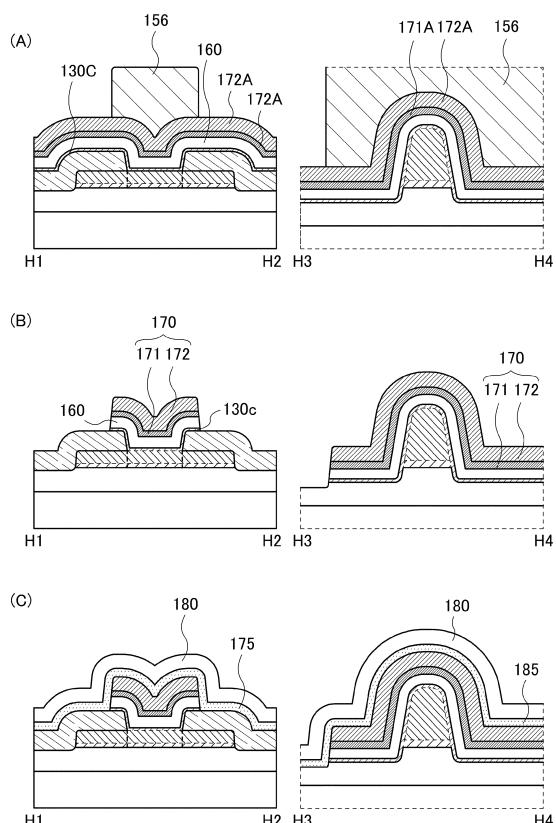

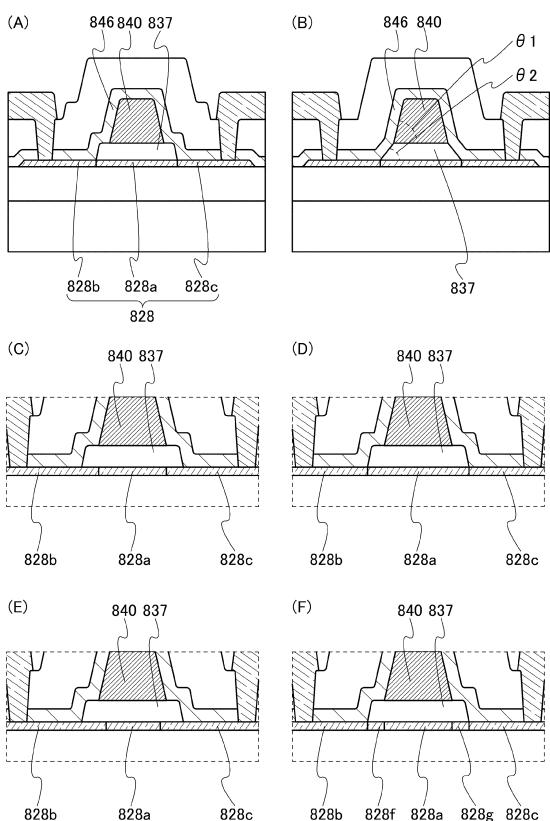

また、本発明の一態様のトランジスタは、図 15 (A)、(B) に示す構成であってもよい。図 15 (A) はトランジスタ 107 の上面図であり、図 15 (A) に示す一点鎖線 H1 - H2 方向の断面が図 15 (B) に相当する。また、図 15 (A) に示す一点鎖線 H3 - H4 方向の断面が図 21 に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線 H1 - H2 方向をチャネル長方向、一点鎖線 H3 - H4 方向をチャネル幅方向と呼称する場合がある。

#### 【0160】

トランジスタ 107 は、基板 115 と接する絶縁層 120 と、絶縁層 120 と接する酸化物半導体層 130a および酸化物半導体層 130b からなる積層と、当該積層と電気的に接続する導電層 140 および導電層 150 と、当該積層、導電層 140 および導電層 150 と接する酸化物半導体層 130c と、酸化物半導体層 130c と接する絶縁層 160 と、絶縁層 160 と接する導電層 170 と、導電層 140、導電層 150、酸化物半導体層 130c、絶縁層 160 および導電層 170 と接する絶縁層 175 と、絶縁層 175 と接する絶縁層 180 と、を有する。また、必要に応じて絶縁層 180 に接する絶縁層 190 (平坦化膜) などを有していてもよい。

#### 【0161】

トランジスタ 107 は、領域 231 および領域 232 において酸化物半導体層 130 が二層 (酸化物半導体層 130a、酸化物半導体層 130b) である点、領域 233 において酸化物半導体層 130 が三層 (酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c) である点、および導電層 140 および導電層 150 と絶縁層 160 との間に酸化物半導体層の一部 (酸化物半導体層 130c) が介在している点を除き、ト

10

20

30

40

50

ランジスタ101と同様の構成を有する。

**【0162】**

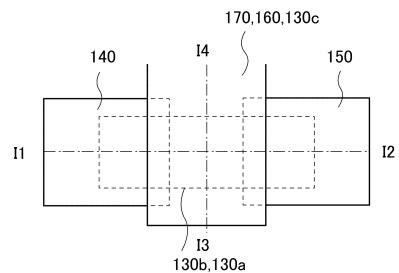

また、本発明の一態様のトランジスタは、図16(A)、(B)に示す構成であってもよい。図16(A)はトランジスタ108の上面図であり、図16(A)に示す一点鎖線I1-I2方向の断面が図16(B)に相当する。また、図16(A)に示す一点鎖線I3-I4方向の断面が図21に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線I1-I2方向をチャネル長方向、一点鎖線I3-I4方向をチャネル幅方向と呼称する場合がある。

**【0163】**

トランジスタ108は、領域231および領域232において酸化物半導体層130が二層（酸化物半導体層130a、酸化物半導体層130b）である点、領域233において酸化物半導体層130が三層（酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c）である点、および導電層140および導電層150と絶縁層160との間に酸化物半導体層の一部（酸化物半導体層130c）が介在している点を除き、トランジスタ102と同様の構成を有する。10

**【0164】**

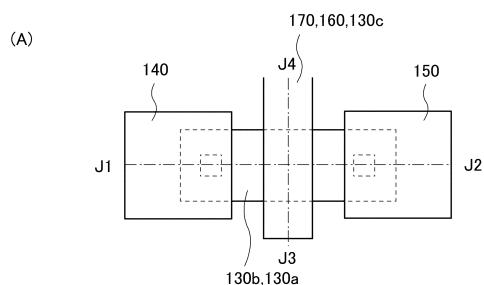

また、本発明の一態様のトランジスタは、図17(A)、(B)に示す構成であってもよい。図17(A)はトランジスタ109の上面図であり、図17(A)に示す一点鎖線J1-J2方向の断面が図17(B)に相当する。また、図17(A)に示す一点鎖線J3-J4方向の断面が図21に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線J1-J2方向をチャネル長方向、一点鎖線J3-J4方向をチャネル幅方向と呼称する場合がある。20

**【0165】**

トランジスタ109は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130aおよび酸化物半導体層130bからなる積層と、当該積層と接する酸化物半導体層130cと、酸化物半導体層130cと接する絶縁層160と、絶縁層160と接する導電層170と、当該積層、酸化物半導体層130c、絶縁層160および導電層170を覆う絶縁層175と、絶縁層175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて当該積層と電気的に接続する導電層140および導電層150を有する。また、必要に応じて絶縁層180、導電層140および導電層150に接する絶縁層190（平坦化膜）などを有していてもよい。30

**【0166】**

トランジスタ109は、領域231および領域232において酸化物半導体層130が二層（酸化物半導体層130a、酸化物半導体層130b）である点、領域233において酸化物半導体層130が三層（酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c）である点を除き、トランジスタ103と同様の構成を有する。

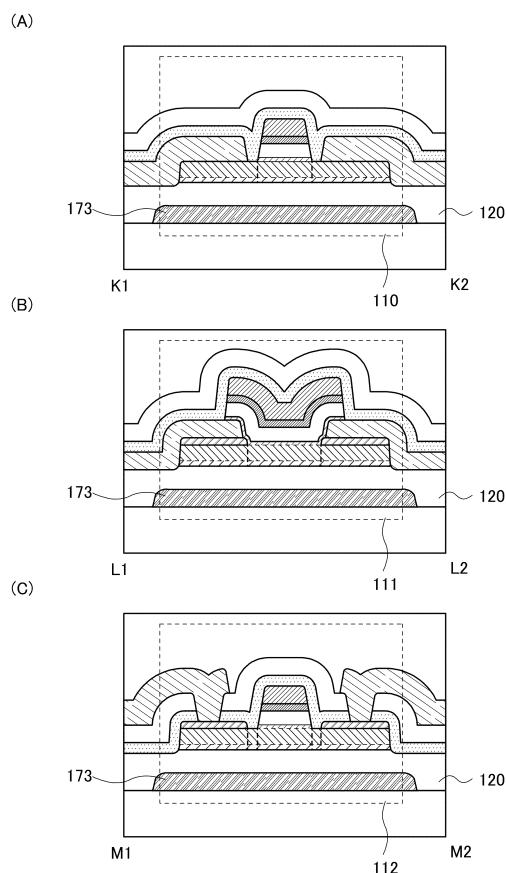

**【0167】**

また、本発明の一態様のトランジスタは、図18(A)、(B)に示す構成であってもよい。図18(A)はトランジスタ110の上面図であり、図18(A)に示す一点鎖線K1-K2方向の断面が図18(B)に相当する。また、図18(A)に示す一点鎖線K3-K4方向の断面が図21に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線K1-K2方向をチャネル長方向、一点鎖線K3-K4方向をチャネル幅方向と呼称する場合がある。40

**【0168】**

トランジスタ110は、領域231および領域232において酸化物半導体層130が二層（酸化物半導体層130a、酸化物半導体層130b）である点、領域233において酸化物半導体層130が三層（酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c）である点を除き、トランジスタ104と同様の構成を有する。

**【0169】**

また、本発明の一態様のトランジスタは、図19(A)、(B)に示す構成であってもよ50

い。図19(A)はトランジスタ111の上面図であり、図19(A)に示す一点鎖線K1-K2方向の断面が図19(B)に相当する。また、図19(A)に示す一点鎖線K3-K4方向の断面が図21に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線K1-K2方向をチャネル長方向、一点鎖線K3-K4方向をチャネル幅方向と呼称する場合がある。

#### 【0170】

トランジスタ111は、基板115と接する絶縁層120と、絶縁層120と接する酸化物半導体層130aおよび酸化物半導体層130bからなる積層と、当該積層と電気的に接続する導電層141および導電層151と、当該積層、導電層141および導電層151と接する酸化物半導体層130cと、酸化物半導体層130cと接する絶縁層160と、絶縁層160と接する導電層170と、当該積層、導電層141、導電層151、酸化物半導体層130c、絶縁層160および導電層170と接する絶縁層175と、絶縁層175と接する絶縁層180と、絶縁層175および絶縁層180に設けられた開口部を通じて導電層141および導電層151とそれぞれ電気的に接続する導電層142および導電層152を有する。また、必要に応じて絶縁層180、導電層142および導電層152に接する絶縁層190(平坦化膜)などを有していてもよい。

10

#### 【0171】

トランジスタ111は、領域231および領域232において酸化物半導体層130が二層(酸化物半導体層130a、酸化物半導体層130b)である点、領域233において酸化物半導体層130が三層(酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c)である点、および導電層141および導電層151と絶縁層160との間に酸化物半導体層の一部(酸化物半導体層130c)が介在している点を除き、トランジスタ105と同様の構成を有する。

20

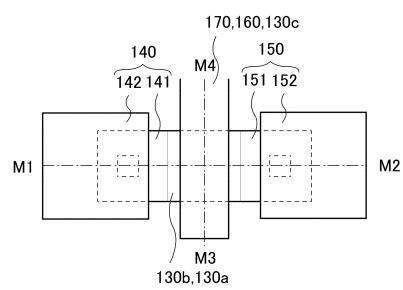

#### 【0172】

また、本発明の一態様のトランジスタは、図20(A)、(B)に示す構成であってもよい。図20(A)はトランジスタ112の上面図であり、図20(A)に示す一点鎖線M1-M2方向の断面が図20(B)に相当する。また、図20(A)に示す一点鎖線M3-M4方向の断面が図21に相当する。なお、上記図面では、明瞭化のために一部の要素を拡大、縮小、または省略して図示している。また、一点鎖線M1-M2方向をチャネル長方向、一点鎖線M3-M4方向をチャネル幅方向と呼称する場合がある。

30

#### 【0173】

トランジスタ112は、領域331、領域332、領域334および領域335において酸化物半導体層130が二層(酸化物半導体層130a、酸化物半導体層130b)である点、領域333において酸化物半導体層130が三層(酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c)である点を除き、トランジスタ106と同様の構成を有する。

#### 【0174】

また、本発明の一態様のトランジスタは、図22(A)、(B)、(C)および図23(A)、(B)、(C)に示すチャネル長方向の断面図、ならびに図24(A)、(B)に示すチャネル幅方向の断面図のように、酸化物半導体層130と基板115との間に導電層173を備えていてもよい。当該導電層を第2のゲート電極層(バックゲート)として用いることで、更なるオン電流の増加や、しきい値電圧の制御を行うことができる。なお、図22(A)、(B)、(C)および図23(A)、(B)、(C)に示す断面図において、導電層173の幅を酸化物半導体層130よりも短くしてもよい。さらに、導電層173の幅を導電層170の幅よりも短くしてもよい。

40

#### 【0175】

本発明の一態様のトランジスタ(トランジスタ101乃至トランジスタ109)では、いずれの構成においても、ゲート電極層である導電層170は、ゲート絶縁膜である絶縁層160を介して酸化物半導体層130のチャネル幅方向の略平面に対して垂直な断面を電気的に取り囲み、オン電流が高められる。このようなトランジスタの構造を、surro

50

u n d e d c h a n n e l ( s - c h a n n e l ) 構造とよぶ。

【 0 1 7 6 】

また、酸化物半導体層 130b および酸化物半導体層 130c を有するトランジスタ、ならびに酸化物半導体層 130a、酸化物半導体層 130b および酸化物半導体層 130c を有するトランジスタにおいては、酸化物半導体層 130 を構成する二層または三層の材料を適切に選択することで酸化物半導体層 130b に電流を流すことができる。酸化物半導体層 130b に電流が流れることで、界面散乱の影響を受けにくく、高いオン電流を得ることができる。なお、酸化物半導体層 130b を厚くすると、オン電流を向上させることができる。例えば、酸化物半導体層 130b の膜厚を 100 nm 乃至 200 nm としてもよい。

10

【 0 1 7 7 】

以上の構成のトランジスタを用いることにより、半導体装置に良好な電気特性を付与することができる。

【 0 1 7 8 】

なお、本明細書において、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレン領域またはドレイン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

20

【 0 1 7 9 】

また、チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

30

【 0 1 8 0 】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（以下、実効的なチャネル幅と呼ぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅と呼ぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の上面に形成されるチャネル領域の割合に対して、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。

40

【 0 1 8 1 】

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるために、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

【 0 1 8 2 】

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅（SCW：Surrounded Channel Width）」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合に

50

は、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面T E M像などを取得して、その画像を解析することなどによって、値を決定することができる。

#### 【0183】

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求めの場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

#### 【0184】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

#### 【0185】

(実施の形態3)

本実施の形態では、実施の形態2に示したトランジスタの構成要素について詳細を説明する。

#### 【0186】

基板115は、単なる支持材料に限らず、他のトランジスタなどのデバイスが形成された基板であってもよい。この場合、トランジスタのゲート電極層(導電層170)、ソース電極層(導電層140)、およびドレイン電極層(導電層150)の一つ以上は、上記の他のデバイスと電気的に接続されていてもよい。

#### 【0187】

例えば、基板115には、ガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンからなる単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムからなる化合物半導体基板、SOI(Silicon On Insulator)基板などを用いることができる。

#### 【0188】

絶縁層120は、基板115からの不純物の拡散を防止する役割を有するほか、酸化物半導体層130に酸素を供給する役割を担うことができる。したがって、絶縁層120は酸素を含む絶縁膜であることが好ましく、化学量論組成よりも多い酸素を含む絶縁膜であることがより好ましい。例えば、表面温度が100以上700以下、好ましくは100

以上500以下の加熱処理で行われるTDS法にて、酸素原子に換算しての酸素の放出量が $1.0 \times 10^{19} \text{ atoms/cm}^3$ 以上である膜とする。また、上述のように基板115が他のデバイスが形成された基板である場合、絶縁層120は、層間絶縁膜としての機能も有する。その場合は、表面が平坦になるようにCMP(Chemical Mechanical Polishing)法等で平坦化処理を行うことが好ましい。

#### 【0189】

例えば、絶縁層120には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、またはこれらの混合材料を用いることができる。また、上記材料の積層であってもよい。

#### 【0190】

なお、本実施の形態では、トランジスタが有する酸化物半導体層130が酸化物半導体層130a、酸化物半導体層130bおよび酸化物半導体層130cを絶縁層120側から順に積んだ三層構造である場合を主として詳細を説明する。

#### 【0191】

なお、酸化物半導体層130が单層の場合は、上記酸化物半導体層130bに相当する層を用いればよい。

10

20

30

40

50

## 【0192】

また、酸化物半導体層130が二層の場合は、酸化物半導体層130bに相当する層および酸化物半導体層130cに相当する層を絶縁層120側から順に積んだ積層を用いればよい。この構成の場合、酸化物半導体層130bと酸化物半導体層130cとを入れ替えることもできる。

## 【0193】

また、酸化物半導体層130が四層以上である場合は、例えば、本実施の形態で説明する三層構造の酸化物半導体層130に対して他の酸化物半導体層を積む構成や当該三層構造におけるいずれかの界面に他の酸化物半導体層を挿入する構成とすることができる。

## 【0194】

一例としては、酸化物半導体層130bには、酸化物半導体層130aおよび酸化物半導体層130cよりも電子親和力（真空準位から伝導帯下端までのエネルギー）が大きい酸化物半導体を用いる。電子親和力は、真空準位と価電子帯上端とのエネルギー差（イオン化ポテンシャル）から、伝導帯下端と価電子帯上端とのエネルギー差（エネルギーギャップ）を差し引いた値として求めることができる。

10

## 【0195】

酸化物半導体層130aおよび酸化物半導体層130cは、酸化物半導体層130bを構成する金属元素を一種以上含み、例えば、伝導帯下端のエネルギーが酸化物半導体層130bよりも、0.05eV、0.07eV、0.1eV、0.15eVのいずれか以上であって、2eV、1eV、0.5eV、0.4eVのいずれか以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。

20

## 【0196】

このような構造において、導電層170に電界を印加すると、酸化物半導体層130のうち、伝導帯下端のエネルギーが最も小さい酸化物半導体層130bにチャネルが形成される。

## 【0197】

また、酸化物半導体層130aは、酸化物半導体層130bを構成する金属元素を一種以上含んで構成されるため、酸化物半導体層130bと絶縁層120が接した場合の界面と比較して、酸化物半導体層130bと酸化物半導体層130aとの界面には界面準位が形成されにくくなる。該界面準位はチャネルを形成することができるため、トランジスタのしきい値電圧が変動することがある。したがって、酸化物半導体層130aを設けることにより、トランジスタのしきい値電圧などの電気特性のばらつきを低減することができる。また、当該トランジスタの信頼性を向上させることができる。

30

## 【0198】

また、酸化物半導体層130cは、酸化物半導体層130bを構成する金属元素を一種以上含んで構成されるため、酸化物半導体層130bとゲート絶縁膜（絶縁層160）が接した場合の界面と比較して、酸化物半導体層130bと酸化物半導体層130cとの界面ではキャリアの散乱が起こりにくくなる。したがって、酸化物半導体層130cを設けることにより、トランジスタの電界効果移動度を高くすることができます。

40

## 【0199】

酸化物半導体層130aおよび酸化物半導体層130cには、例えば、Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHfを酸化物半導体層130bよりも高い原子数比で含む材料を用いることができる。具体的には、当該原子数比を1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。前述の元素は酸素と強く結合するため、酸素欠損が酸化物半導体層に生じることを抑制する機能を有する。すなわち、酸化物半導体層130aおよび酸化物半導体層130cは、酸化物半導体層130bよりも酸素欠損が生じにくいということができる。

## 【0200】

また、酸化物半導体層130a、酸化物半導体層130b、および酸化物半導体層130cとして用いることのできる酸化物半導体は、少なくともインジウム（In）もしくは亜

50

鉛 (Zn) を含むことが好ましい。または、InとZnの双方を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーを含むことが好ましい。

#### 【0201】

スタビライザーとしては、ガリウム (Ga)、スズ (Sn)、ハフニウム (Hf)、アルミニウム (Al)、またはジルコニウム (Zr) 等がある。また、他のスタビライザーとしては、ランタノイドである、ラントン (La)、セリウム (Ce)、プラセオジム (Pr)、ネオジム (Nd)、サマリウム (Sm)、ユウロピウム (Eu)、ガドリニウム (Gd)、テルビウム (Tb)、ジスプロシウム (Dy)、ホルミウム (Ho)、エルビウム (Er)、ツリウム (Tm)、イッテルビウム (Yb)、ルテチウム (Lu) 等がある。10

#### 【0202】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化ガリウム、酸化亜鉛、In-Zn酸化物、Sn-Zn酸化物、Al-Zn酸化物、Zn-Mg酸化物、Sn-Mg酸化物、In-Mg酸化物、In-Ga酸化物、In-Ga-Zn酸化物、In-Al-Zn酸化物、In-Sn-Zn酸化物、Sn-Ga-Zn酸化物、Al-Ga-Zn酸化物、Sn-Al-Zn酸化物、In-Hf-Zn酸化物、In-La-Zn酸化物、In-Ce-Zn酸化物、In-Pr-Zn酸化物、In-Nd-Zn酸化物、In-Sm-Zn酸化物、In-Eu-Zn酸化物、In-Gd-Zn酸化物、In-Tb-Zn酸化物、In-Dy-Zn酸化物、In-Ho-Zn酸化物、In-Er-Zn酸化物、In-Tm-Zn酸化物、In-Yb-Zn酸化物、In-Lu-Zn酸化物、In-Sn-Ga-Zn酸化物、In-Hf-Ga-Zn酸化物、In-Al-Ga-Zn酸化物、In-Sn-Al-Zn酸化物、In-Sn-Hf-Zn酸化物、In-Hf-Al-Zn酸化物を用いることができる。20

#### 【0203】

なお、ここで、例えば、In-Ga-Zn酸化物とは、InとGaとZnを主成分として有する酸化物という意味である。また、InとGaとZn以外の金属元素が入っていてもよい。また、本明細書においては、In-Ga-Zn酸化物で構成した膜をIGZO膜とも呼ぶ。

#### 【0204】

また、 $InMO_3(ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Y、Zr、La、Ce、またはNdから選ばれた一つの金属元素または複数の金属元素を示す。また、 $In_2SnO_5(ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数) で表記される材料を用いてもよい。30

#### 【0205】

なお、酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130cが、少なくともインジウム、亜鉛およびM (Al、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属) を含むIn-M-Zn酸化物であるとき、酸化物半導体層130aを $In : M : Zn = x_1 : y_1 : z_1$  [原子数比]、酸化物半導体層130bを $In : M : Zn = x_2 : y_2 : z_2$  [原子数比]、酸化物半導体層130cを $In : M : Zn = x_3 : y_3 : z_3$  [原子数比] とすると、 $y_1 / x_1$  および  $y_3 / x_3$  が  $y_2 / x_2$  よりも大きくなることが好ましい。 $y_1 / x_1$  および  $y_3 / x_3$  は  $y_2 / x_2$  よりも1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。このとき、酸化物半導体層130bにおいて、 $y_2$  が  $x_2$  以上であるとトランジスタの電気特性を安定させることができる。ただし、 $y_2$  が  $x_2$  の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、 $y_2$  は  $x_2$  の3倍未満であることが好ましい。40

#### 【0206】

酸化物半導体層130aおよび酸化物半導体層130cにおけるZnおよびOを除いた場合において、InおよびMの原子数比率は、好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが750

5 atomic %以上とする。また、酸化物半導体層130bのZnおよびOを除いてのInおよびMの原子数比率は、好ましくはInが25 atomic %以上、Mが75 atomic %未満、さらに好ましくはInが34 atomic %以上、Mが66 atomic %未満とする。

#### 【0207】

また、酸化物半導体層130bは、酸化物半導体層130aおよび酸化物半導体層130cよりもインジウムの含有量を多くするとよい。酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることにより、より多くのs軌道が重なるため、InがMよりも多い組成となる酸化物はInがMと同等または少ない組成となる酸化物と比較して移動度が高くなる。そのため、酸化物半導体層130bにインジウムの含有量が多い酸化物を用いることで、高い電界効果移動度のトランジスタを実現することができる。10

#### 【0208】

酸化物半導体層130aの厚さは、3nm以上100nm以下、好ましくは5nm以上50nm以下、さらに好ましくは5nm以上25nm以下とする。また、酸化物半導体層130bの厚さは、3nm以上200nm以下、好ましくは10nm以上150nm以下、さらに好ましくは15nm以上100nm以下とする。また、酸化物半導体層130cの厚さは、1nm以上50nm以下、好ましくは2nm以上30nm以下、さらに好ましくは3nm以上15nm以下とする。また、酸化物半導体層130bは、酸化物半導体層130aおよび酸化物半導体層130cより厚い方が好ましい。20

#### 【0209】

なお、酸化物半導体層をチャネルとするトランジスタに安定した電気特性を付与するためには、酸化物半導体層中の不純物濃度を低減し、酸化物半導体層を真性または実質的に真性(i型)にすることが有効である。ここで、実質的に真性とは、酸化物半導体層のキャリア密度が、 $1 \times 10^{15} / \text{cm}^3$ 未満であること、好ましくは $1 \times 10^{13} / \text{cm}^3$ 未満であること、さらに好ましくは $8 \times 10^{11} / \text{cm}^3$ 未満であること、さらに好適には $1 \times 10^8 / \text{cm}^3$ 未満 $1 \times 10^{-9} / \text{cm}^3$ 以上であることとする。

#### 【0210】

また、酸化物半導体層において、水素、窒素、炭素、シリコン、および主成分以外の金属元素は不純物となる。例えば、水素および窒素はドナー準位の形成に寄与し、キャリア密度を増大させてしまう。また、シリコンは酸化物半導体層中で不純物準位の形成に寄与する。当該不純物準位はトラップとなり、トランジスタの電気特性を劣化させることがある。したがって、酸化物半導体層130a、酸化物半導体層130bおよび酸化物半導体層130cの層中や、それぞれの界面において不純物濃度を低減させることが好ましい。30

#### 【0211】

酸化物半導体層を真性または実質的に真性と/orするためには、SIMS(Secondary Ion Mass Spectrometry)分析において、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を $1 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 未満、さらに好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 未満とする。また、水素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $2 \times 10^{20} \text{ atoms/cm}^3$ 以下、好ましくは $5 \times 10^{19} \text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{19} \text{ atoms/cm}^3$ 以下、さらに好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 以下とする。また、窒素濃度は、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、 $5 \times 10^{19} \text{ atoms/cm}^3$ 未満、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{18} \text{ atoms/cm}^3$ 以下、さらに好ましくは $5 \times 10^{17} \text{ atoms/cm}^3$ 以下とする。40

#### 【0212】

また、酸化物半導体層が結晶を含む場合、シリコンや炭素が高濃度で含まれると、酸化物

10

20

30

40

50

半導体層の結晶性を低下させことがある。酸化物半導体層の結晶性を低下させないためには、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、シリコン濃度を  $1 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、好ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 未満、さらに好ましくは  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 未満とする部分を有していればよい。また、例えば、酸化物半導体層のある深さにおいて、または、酸化物半導体層のある領域において、炭素濃度を  $1 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、好ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 未満、さらに好ましくは  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 未満とする部分を有していればよい。

#### 【0213】

また、上述のように高純度化された酸化物半導体膜をチャネル形成領域に用いたトランジスタのオフ電流は極めて小さい。例えば、ソースとドレインとの間の電圧を 0.1V、5V、または、10V 程度とした場合に、トランジスタのチャネル幅で規格化したオフ電流を数 y A / μm 乃至数 z A / μm にまで低減することが可能となる。

#### 【0214】

なお、トランジスタのゲート絶縁膜としては、シリコンを含む絶縁膜が多く用いられるため、上記理由により酸化物半導体層のチャネルとなる領域は、本発明の一態様のトランジスタのようにゲート絶縁膜と接しない構造が好ましいということができる。また、ゲート絶縁膜と酸化物半導体層との界面にチャネルが形成される場合、該界面でキャリアの散乱が起こり、トランジスタの電界効果移動度が低くなることがある。このような観点からも、酸化物半導体層のチャネルとなる領域はゲート絶縁膜から離すことが好ましいといえる。

#### 【0215】

したがって、酸化物半導体層 130 を酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c の積層構造とすることで、酸化物半導体層 130b にチャネルを形成することができ、高い電界効果移動度および安定した電気特性を有したトランジスタを形成することができる。

#### 【0216】

酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c のバンド構造においては、伝導帯下端のエネルギーが連続的に変化する。これは、酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c の組成が近似することにより、酸素が相互に拡散しやすい点からも理解される。したがって、酸化物半導体層 130a、酸化物半導体層 130b、酸化物半導体層 130c は組成が異なる層の積層体ではあるが、物性的に連続であるということもでき、本明細書の図面において、当該積層体のそれぞれの界面は点線で表している。

#### 【0217】

主成分を共通として積層された酸化物半導体層 130 は、各層を単に積層するのではなく連続接合（ここでは特に伝導帯下端のエネルギーが各層の間で連続的に変化する U 字型の井戸構造（U Shape Well））が形成されるように作製する。すなわち、各層の界面にトラップ中心や再結合中心のような欠陥準位を形成するような不純物が存在しないように積層構造を形成する。仮に、積層された酸化物半導体層の層間に不純物が混在していると、エネルギーバンドの連続性が失われ、界面でキャリアがトラップあるいは再結合により消滅してしまう。

#### 【0218】

例えば、酸化物半導体層 130a および酸化物半導体層 130c には In : Ga : Zn = 1 : 3 : 2、1 : 3 : 3、1 : 3 : 4、1 : 3 : 6、1 : 4 : 5、1 : 6 : 4 または 1 : 9 : 6（原子数比）、酸化物半導体層 130b には In : Ga : Zn = 1 : 1 : 1、2 : 1 : 3、5 : 5 : 6、または 3 : 1 : 2（原子数比）などの In - Ga - Zn 酸化物などを用いることができる。なお、酸化物半導体層 130a、酸化物半導体層 130b、および酸化物半導体層 130c の原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス 20% の変動を含む。

10

20

30

40

50

## 【0219】

酸化物半導体層130における酸化物半導体層130bはウェル(井戸)となり、酸化物半導体層130を用いたトランジスタにおいて、チャネルは酸化物半導体層130bに形成される。なお、酸化物半導体層130は伝導帯下端のエネルギーが連続的に変化しているため、U字型井戸とも呼ぶことができる。また、このような構成で形成されたチャネルを埋め込みチャネルということもできる。

## 【0220】

また、酸化物半導体層130aおよび酸化物半導体層130cと、酸化シリコン膜などの絶縁層との界面近傍には、不純物や欠陥に起因したトラップ準位が形成され得る。酸化物半導体層130aおよび酸化物半導体層130cがあることにより、酸化物半導体層130bと当該トラップ準位とを遠ざけることができる。10

## 【0221】

ただし、酸化物半導体層130aおよび酸化物半導体層130cの伝導帯下端のエネルギーと、酸化物半導体層130bの伝導帯下端のエネルギーとの差が小さい場合、酸化物半導体層130bの電子が該エネルギー差を越えてトラップ準位に達することができる。電子がトラップ準位に捕獲されることで、絶縁層界面にマイナスの電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。

## 【0222】

したがって、トランジスタのしきい値電圧の変動を低減するには、酸化物半導体層130aおよび酸化物半導体層130cの伝導帯下端のエネルギーと、酸化物半導体層130bの伝導帯下端のエネルギーとの間に一定以上の差を設けることが必要となる。それぞれの当該エネルギー差は、0.1eV以上が好ましく、0.15eV以上がより好ましい。20

## 【0223】

酸化物半導体層130a、酸化物半導体層130bおよび酸化物半導体層130cには、結晶部が含まれることが好ましい。特にc軸に配向した結晶を用いることでトランジスタに安定した電気特性を付与することができる。また、c軸に配向した結晶は歪曲に強く、フレキシブル基板を用いた半導体装置の信頼性を向上させることができる。

## 【0224】

ソース電極層として作用する導電層140およびドレイン電極層として作用する導電層150には、例えば、Al、Cr、Cu、Ta、Ti、Mo、W、Ni、Mn、Nd、Sc、および当該金属材料の合金から選ばれた材料の単層、または積層を用いることができる。代表的には、特に酸素と結合しやすいTiや、後のプロセス温度が比較的高くできることなどから、融点の高いWを用いることがより好ましい。また、低抵抗のCuやCu-Mnなどの合金と上記材料との積層を用いてもよい。なお、トランジスタ105、トランジスタ106、トランジスタ111、トランジスタ112においては、例えば、導電層141および導電層151にW、導電層142および導電層152にTiとAlとの積層膜などを用いることができる。30

## 【0225】

上記材料は酸化物半導体膜から酸素を引き抜く性質を有する。そのため、上記材料と接した酸化物半導体層の一部の領域では酸化物半導体膜中の酸素が脱離し、酸素欠損が形成される。膜中に僅かに含まれる水素と当該酸素欠損が結合することにより当該領域は顕著にn型化する。したがって、n型化した当該領域はトランジスタのソースまたはドレインとして作用させることができる。40

## 【0226】

ゲート絶縁膜として作用する絶縁層160には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、絶縁層160は上記材料の積層であってもよい。なお、絶縁層160に、ランタン(La)、窒素、ジルコニア(Zr)などを、不純物として含んでいてもよい。なお、絶縁層50

160はブロック層165としても作用させることができる。

#### 【0227】

また、絶縁層160の積層構造の一例について説明する。絶縁層160は、例えば、酸素、窒素、シリコン、ハフニウムなどを有する。具体的には、酸化ハフニウム、および酸化シリコンまたは酸化窒化シリコンを含むと好ましい。

#### 【0228】

酸化ハフニウムおよび酸化アルミニウムは、酸化シリコンや酸化窒化シリコンと比べて比誘電率が高い。したがって、等価酸化膜厚に対して物理的な膜厚を大きくできるため、等価酸化膜厚を10nm以下または5nm以下とした場合でも、トンネル電流によるリーク電流を小さくすることができる。即ち、オフ電流の小さいトランジスタを実現することができる。さらに、結晶構造を有する酸化ハフニウムは、非晶質構造を有する酸化ハフニウムと比べて高い比誘電率を備える。したがって、オフ電流の小さいトランジスタとするためには、結晶構造を有する酸化ハフニウムを用いることが好ましい。結晶構造の例としては、単斜晶系や立方晶系などが挙げられる。ただし、本発明の一態様は、これらに限定されない。

10

#### 【0229】

ところで、結晶構造を有する酸化ハフニウムの被形成面は、欠陥に起因した界面準位を有する場合がある。該界面準位はトラップセンターとして機能する場合がある。そのため、酸化ハフニウムがトランジスタのチャネル領域に近接して配置されるとき、該界面準位によってトランジスタの電気特性が劣化する場合がある。そこで、該界面準位の影響を低減するために、トランジスタのチャネル領域と酸化ハフニウムとの間に、別の膜を配置することによって互いに離間させることができることが好ましい場合がある。この膜は、緩衝機能を有する。緩衝機能を有する膜は、絶縁層160に含まれる膜であってもよいし、酸化物半導体膜に含まれる膜であってもよい。即ち、緩衝機能を有する膜としては、酸化シリコン、酸化窒化シリコン、酸化物半導体などを用いることができる。なお、緩衝機能を有する膜には、たとえば、チャネル領域となる半導体よりもエネルギーギャップの大きい半導体または絶縁体を用いる。または、緩衝機能を有する膜には、たとえば、チャネル領域となる半導体よりも電子親和力の小さい半導体または絶縁体を用いる。または、緩衝機能を有する膜には、たとえば、チャネル領域となる半導体よりもイオン化工エネルギーの大きい半導体または絶縁体を用いる。

20

#### 【0230】

一方、上述した結晶構造を有する酸化ハフニウムの被形成面における界面準位（トラップセンター）に電荷をトラップさせることで、トランジスタのしきい値電圧を制御できる場合がある。該電荷を安定して存在させるためには、たとえば、チャネル領域と酸化ハフニウムとの間に、酸化ハフニウムよりもエネルギーギャップの大きい絶縁体を配置すればよい。または、酸化ハフニウムよりも電子親和力の小さい半導体または絶縁体を配置すればよい。または、緩衝機能を有する膜には、酸化ハフニウムよりもイオン化工エネルギーの大きい半導体または絶縁体を配置すればよい。このような絶縁体を用いることで、界面準位にトラップされた電荷の放出が起こりにくくなり、長期間に渡って電荷を保持することができる。

30

#### 【0231】

そのような絶縁体として、例えば、酸化シリコン、酸化窒化シリコンが挙げられる。絶縁層160内の界面準位に電荷を捕獲させるためには、酸化物半導体層130からゲート電極層（導電層170）に向かって電子を移動させればよい。具体的な例としては、高い温度（例えば、125以上450以下、代表的には150以上300以下）の下で、ゲート電極層（導電層170）の電位をソース電極やドレイン電極の電位より高い状態にて1秒以上、代表的には1分以上維持すればよい。

40

#### 【0232】

このように絶縁層160などの界面準位に所望の量の電子を捕獲させたトランジスタは、しきい値電圧がプラス側にシフトする。ゲート電極層（導電層170）の電圧や、電圧を

50

印加する時間を調整することによって、電子を捕獲させる量（しきい値電圧の変動量）を制御することができる。なお、電荷を捕獲させることができれば、絶縁層160内でなくても構わない。同様の構造を有する積層膜を、他の絶縁層に用いても構わない。

### 【0233】

また、酸化物半導体層130と接する絶縁層120および絶縁層160においては、酸化物半導体のエネルギーギャップ内における窒素酸化物の準位密度が低い領域を有していてもよい。窒素酸化物の準位密度が低い酸化物絶縁層として、窒素酸化物の放出量の少ない酸化窒化シリコン膜、または窒素酸化物の放出量の少ない酸化窒化アルミニウム膜等を用いることができる。

### 【0234】

なお、窒素酸化物の放出量の少ない酸化窒化シリコン膜は、昇温脱離ガス分析法（TDS（Thermal Desorption Spectroscopy））において、窒素酸化物の放出量よりアンモニアの放出量が多い膜であり、代表的にはアンモニアの放出量が $1 \times 10^{18}$ 個/cm<sup>3</sup>以上 $5 \times 10^{19}$ 個/cm<sup>3</sup>以下である。なお、アンモニアの放出量は、膜の表面温度が50以上650以下、好ましくは50以上550以下の加熱処理による放出量とする。

### 【0235】

絶縁層120および絶縁層160として、上記酸化物絶縁層を用いることで、トランジスタのしきい値電圧のシフトを低減することが可能であり、トランジスタの電気特性の変動を低減することができる。

### 【0236】

ゲート電極層として作用する導電層170には、例えば、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、Mn、Nd、Sc、TaおよびWなどの導電膜を用いることができる。また、上記材料の合金や上記材料の導電性窒化物を用いてもよい。また、上記材料、上記材料の合金、および上記材料の導電性窒化物から選ばれた複数の材料の積層であってもよい。代表的には、タンゲステン、タンゲステンと窒化チタンの積層、タンゲステンと窒化タンタルの積層などを用いることができる。また、低抵抗のCuまたはCu-Mnの合金や上記材料とCuまたはCu-Mnの合金との積層を用いてもよい。本実施の形態では、導電層171に窒化タンタル、導電層172にタンゲステンを用いて導電層170を形成する。

### 【0237】

絶縁層175には、水素を含む窒化シリコン膜または窒化アルミニウム膜などを用いることができる。実施の形態2に示したトランジスタ103、トランジスタ104、トランジスタ106、トランジスタ109、トランジスタ110、およびトランジスタ112では、絶縁層175として水素を含む絶縁膜を用いることで酸化物半導体層の一部をn型化することができる。また、窒化絶縁膜は水分などのプロッキング膜としての作用も有し、トランジスタの信頼性を向上させることができる。

### 【0238】

また、絶縁層175としては酸化アルミニウム膜を用いることもできる。特に、実施の形態2に示したトランジスタ101、トランジスタ102、トランジスタ105、トランジスタ107、トランジスタ108、およびトランジスタ111では絶縁層175に酸化アルミニウム膜を用いることが好ましい。酸化アルミニウム膜は、水素、水分などの不純物、および酸素の両方に対して膜を透過させない遮断効果が高い。したがって、酸化アルミニウム膜は、トランジスタの作製工程中および作製後において、トランジスタの電気特性の変動要因となる水素、水分などの不純物の酸化物半導体層130への混入防止、酸化物半導体層130を構成する主成分材料である酸素の酸化物半導体層からの放出防止、絶縁層120からの酸素の不必要的放出防止の効果を有する保護膜として用いることに適している。また、酸化アルミニウム膜に含まれる酸素を酸化物半導体層中に拡散させることもできる。

### 【0239】

10

20

30

40

50

また、絶縁層 175 上には絶縁層 180 が形成されていることが好ましい。当該絶縁層には、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを一種以上含む絶縁膜を用いることができる。また、当該酸化物絶縁層は上記材料の積層であってもよい。

#### 【0240】

ここで、絶縁層 180 は絶縁層 120 と同様に化学量論組成よりも多くの酸素を有することが好ましい。絶縁層 180 から放出される酸素は絶縁層 160 を経由して酸化物半導体層 130 のチャネル形成領域に拡散させることができることから、チャネル形成領域に形成された酸素欠損に酸素を補填することができる。したがって、安定したトランジスタの電気特性を得ることができる。10

#### 【0241】

半導体装置を高集積化するにはトランジスタの微細化が必須である。一方、トランジスタの微細化によりトランジスタの電気特性が悪化することが知られており、チャネル幅が縮小するとオン電流は低下する。

#### 【0242】

本発明の一態様のトランジスタ 107 乃至トランジスタ 112 では、チャネルが形成される酸化物半導体層 130b を覆うように酸化物半導体層 130c が形成されており、チャネル形成層とゲート絶縁膜が接しない構成となっている。そのため、チャネル形成層とゲート絶縁膜との界面で生じるキャリアの散乱を抑えることができ、トランジスタのオン電流を大きくすることができます。20

#### 【0243】

また、本発明の一態様のトランジスタでは、前述したように酸化物半導体層 130 のチャネル幅方向の略平面に対して垂直な断面を電気的に取り囲むようにゲート電極層（導電層 170）が形成されているため、酸化物半導体層 130 に対しては垂直方向からのゲート電界に加えて、側面方向からのゲート電界が印加される。すなわち、チャネル形成層に対して全体的にゲート電界が印加されることになり実効チャネル幅が拡大するため、さらにオン電流を高められる。

#### 【0244】

また、本発明の一態様における酸化物半導体層 130 が二層または三層のトランジスタでは、チャネルが形成される酸化物半導体層 130b を酸化物半導体層 130a 上に形成することで界面準位を形成しにくくする効果を有する。また、本発明の一態様における酸化物半導体層 130 が三層のトランジスタでは、酸化物半導体層 130b を三層構造の中間に位置する層として上下からの不純物混入の影響を排除できる効果などを併せて有する。そのため、上述したトランジスタのオン電流の向上に加えて、しきい値電圧の安定化や、S 値（サブスレッショルド値）を小さくすることができる。したがって、ゲート電圧 V<sub>G</sub> が 0 V 時の電流を下げることができ、消費電力を低減させることができる。また、トランジスタのしきい値電圧が安定化することから、半導体装置の長期信頼性を向上させることができる。また、本発明の一態様のトランジスタは、微細化にともなう電気特性の劣化が抑えられることから、集積度の高い半導体装置の形成に適しているといえる。3040

#### 【0245】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

#### 【0246】

##### (実施の形態 4)

本実施の形態では、実施の形態 2 で説明したトランジスタ 102、およびトランジスタ 107 の作製方法を説明する。

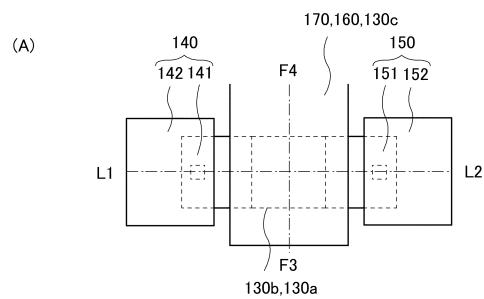

#### 【0247】

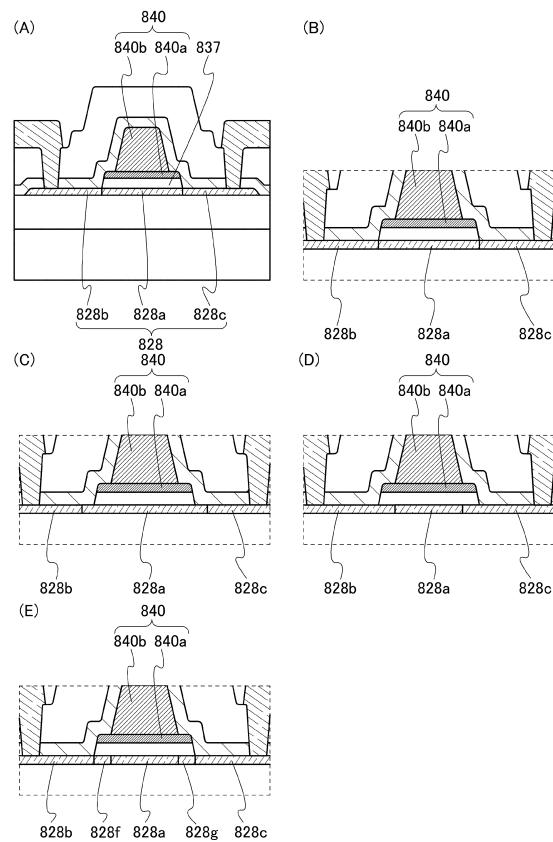

まず、図 25 および図 26 を用いてトランジスタ 102 の作製方法を説明する。なお、図面の左側にはトランジスタのチャネル長方向の断面を示し、右側にはチャネル幅方向の断

面を示す。また、チャネル幅方向の断面の図面は拡大図のため、各要素の見かけ上の膜厚は左右の図面で異なる。

#### 【 0 2 4 8 】

酸化物半導体層 130 は、酸化物半導体層 130 a、酸化物半導体層 130 b および酸化物半導体層 130 c の三層構造である場合を例示する。酸化物半導体層 130 が二層構造の場合は、酸化物半導体層 130 a および酸化物半導体層 130 b の二層とし、酸化物半導体層 130 が単層構造の場合は、酸化物半導体層 130 b の一層とすればよい。

#### 【 0 2 4 9 】

まず、基板 115 上に絶縁層 120 を形成する。基板 115 の種類および絶縁層 120 の材質は実施の形態 3 の説明を参照することができる。なお、絶縁層 120 は、スパッタ法、CVD 法、MBE 法などを用いて形成することができる。10

#### 【 0 2 5 0 】

また、絶縁層 120 にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理法などを用いて酸素を添加してもよい。酸素を添加することによって、絶縁層 120 から酸化物半導体層 130 への酸素の供給をさらに容易にすることができます。

#### 【 0 2 5 1 】

なお、基板 115 の表面が絶縁体であり、後に設ける酸化物半導体層 130 への不純物拡散の影響が無い場合は、絶縁層 120 を設けない構成とすることができる。

#### 【 0 2 5 2 】

次に、絶縁層 120 上に酸化物半導体層 130 a となる酸化物半導体膜 130 A、酸化物半導体層 130 b となる酸化物半導体膜 130 B、および酸化物半導体層 130 c となる酸化物半導体膜 130 C をスパッタ法、CVD 法、MBE 法などを用いて成膜する（図 25 (A) 参照）。

#### 【 0 2 5 3 】

酸化物半導体層 130 が積層構造である場合、酸化物半導体膜はロードロック室を備えたマルチチャンバー方式の成膜装置（例えばスパッタ装置）を用いて各層を大気に触れさせることなく連続して積層することが好ましい。スパッタ装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべく、クライオポンプのような吸着式の真空排気ポンプを用いて高真空排気（ $5 \times 10^{-7}$  Pa 乃至  $1 \times 10^{-4}$  Pa 程度まで）できること、かつ、成膜される基板を 100 以上、好ましくは 500 以上に加熱できることができることが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に炭素成分や水分等を含む気体が逆流しないようにしておくことが好ましい。また、ターボ分子ポンプとクライオポンプを組み合わせた排気系を用いてもよい。

#### 【 0 2 5 4 】

高純度真性酸化物半導体を得るためにには、チャンバー内を高真空排気するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が -40 以下、好ましくは -80 以下、より好ましくは -100 以下にまで高純度化したガスを用いることで酸化物半導体膜に水分等が取り込まれることを可能な限り防ぐことができる。30

#### 【 0 2 5 5 】

酸化物半導体膜 130 A、酸化物半導体膜 130 B、および酸化物半導体膜 130 C には、実施の形態 3 で説明した材料を用いることができる。例えば、酸化物半導体膜 130 A に In : Ga : Zn = 1 : 3 : 6、1 : 3 : 4、1 : 3 : 3 または 1 : 3 : 2 [ 原子数比 ] の In - Ga - Zn 酸化物、酸化物半導体膜 130 B に In : Ga : Zn = 1 : 1 : 1、3 : 1 : 2 または 5 : 5 : 6 [ 原子数比 ] の In - Ga - Zn 酸化物、酸化物半導体膜 130 C に In : Ga : Zn = 1 : 3 : 6、1 : 3 : 4、1 : 3 : 3 または 1 : 3 : 2 [ 原子数比 ] の In - Ga - Zn 酸化物を用いることができる。また、酸化物半導体膜 130 A、および酸化物半導体膜 130 C には、酸化ガリウムのような酸化物半導体を用いて4050

もよい。なお、酸化物半導体膜 130A、酸化物半導体膜 130B、および第3の酸化物半導体膜 130C の原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス 20% の変動を含む。また、成膜法にスパッタ法を用いる場合は、上記材料をターゲットとして成膜することができる。

#### 【0256】

ただし、実施の形態3に詳細を記したように、酸化物半導体膜 130B には酸化物半導体膜 130A および酸化物半導体膜 130C よりも電子親和力が大きい材料を用いる。

#### 【0257】

なお、酸化物半導体膜の成膜には、スパッタ法を用いることが好ましい。スパッタ法としては、RFスパッタ法、DCスパッタ法、ACスパッタ法等を用いることができる。

#### 【0258】

酸化物半導体膜 130C の形成後に、第1の加熱処理を行ってもよい。第1の加熱処理は、250 以上 650 以下、好ましくは 300 以上 500 以下の温度で、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上含む雰囲気、または減圧状態で行えばよい。また、第1の加熱処理の雰囲気は、不活性ガス雰囲気で加熱処理した後に、脱離した酸素を補うために酸化性ガスを 10 ppm 以上含む雰囲気で行ってもよい。第1の加熱処理によって、酸化物半導体膜 130A、酸化物半導体膜 130B、および酸化物半導体膜 130C の結晶性を高め、さらに絶縁層 120、酸化物半導体膜 130A、酸化物半導体膜 130B、および酸化物半導体膜 130C から水素や水などの不純物を除去することができる。なお、第1の加熱処理は、後述する酸化物半導体層 130a、酸化物半導体層 130b、および酸化物半導体層 130c を形成するエッチングの後に行ってもよい。

#### 【0259】

次に、酸化物半導体膜 130A 上に第1の導電層を形成する。第1の導電層は、例えば、次の方法を用いて形成することができる。

#### 【0260】

まず、酸化物半導体膜 130A 上に第1の導電膜を形成する。第1の導電膜としては、Al、Cr、Cu、Ta、Ti、Mo、W、Ni、Mn、Nd、Sc、および当該金属材料の合金から選ばれた材料の単層、または積層を用いることができる。

#### 【0261】

次に、第1の導電膜上にネガ型のレジスト膜を形成し、当該レジスト膜に対して電子ビーム露光、液浸露光、EUV露光などの方法を用いて露光し、現像処理を行うことで第1のレジストマスクを形成する。なお、第1の導電膜とレジスト膜の間には密着剤として有機塗布膜を形成することが好ましい。また、ナノインプリントリソグラフィ法を用いて第1のレジストマスクを形成してもよい。

#### 【0262】

次に、第1のレジストマスクを用いて、第1の導電膜を選択的にエッチングし、第1のレジストマスクをアッシングすることにより導電層を形成する。

#### 【0263】

次に、上記導電層をハードマスクとして用い、酸化物半導体膜 130A、酸化物半導体膜 130B、および酸化物半導体膜 130C を選択的にエッチングし、上記導電層を取り除いて酸化物半導体層 130a、酸化物半導体層 130b、および酸化物半導体層 130c の積層からなる酸化物半導体層 130 を形成する。なお、上記導電層を形成せずに、第1のレジストマスクを用いて酸化物半導体層 130 を形成してもよい。なお、上記導電層を利用してトランジスタ 105 の構造を形成することもできる。

#### 【0264】

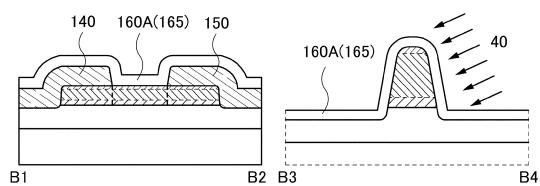

次に、基板 115 または絶縁層 120 が有する略平面に対して垂直な角度( )を 0°、当該略平面に対して平行な角度( )を 90° としたとき、例えば 45° の角度から酸化物半導体層の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して酸素イオン 40 の注入を行う(図 25(B) 参照)。

#### 【0265】

10

20

30

40

50

酸素イオン注入の条件は、例えば、イオン種を $^{16}\text{O}_2^+$ 、加速電圧を0.2kV乃至5kVとし、ドーザ量を $1\text{E}13\text{cm}^{-2}$ 以上 $1\text{E}16\text{cm}^{-2}$ より少ない条件、またはイオン種を $^{16}\text{O}^+$ 、加速電圧を0.2kV乃至5kVとし、ドーザ量を $1\text{E}13\text{cm}^{-2}$ 以上 $1\text{E}15\text{cm}^{-2}$ より少ない条件で行えばよい。

#### 【0266】

次に、酸化物半導体層130を覆うように第2の導電膜を形成する。第2の導電膜としては、実施の形態3で説明した導電層140および導電層150に用いることのできる材料で形成すればよい。第2の導電膜の形成には、スパッタ法、CVD法、MBE法などを用いることができる。

#### 【0267】

次に、ソース領域およびドレイン領域となる部分の上に第2のレジストマスクを形成する。そして、第2の導電膜の一部をエッチングし、導電層140および導電層150を形成する(図25(C)参照)。

#### 【0268】

次に、酸化物半導体層130、導電層140および導電層150上にゲート絶縁膜となる絶縁膜160Åを形成する。絶縁膜160Åは、実施の形態3で説明した絶縁層160に用いることのできる材料で形成すればよい。絶縁膜160Åの形成には、スパッタ法、CVD法、MBE法などを用いることができる。

#### 【0269】

次に、第2の加熱処理を行ってもよい。第2の加熱処理は、第1の加熱処理と同様の条件で行うことができる。第2の加熱処理により、酸化物半導体層130に注入した酸素を酸化物半導体層130の全体に拡散させることができる。なお、第2の加熱処理を行わずに、第3の加熱処理で上記効果を得てもよい。

#### 【0270】

次に、絶縁膜160Å上に導電層170となる第3の導電膜171Åおよび第4の導電膜172Åを形成する。第3の導電膜171Åおよび第4の導電膜172Åは、実施の形態3で説明した導電層171および導電層172に用いることのできる材料で形成すればよい。第3の導電膜171Åおよび第4の導電膜172Åの形成には、スパッタ法、CVD法、MBE法などを用いることができる。

#### 【0271】

次に、第4の導電膜172Å上に第3のレジストマスク156を形成する(図26(A)参照)。そして、当該レジストマスクを用いて、第3の導電膜171Å、第4の導電膜172Åおよび絶縁膜160Åを選択的にエッチングし、導電層171および導電層172からなる導電層170、および絶縁層160を形成する(図26(B)参照)。なお、絶縁膜160Åをエッチングしない構造とすれば、トランジスタ102を作製することができる。

#### 【0272】

次に、酸化物半導体層130、導電層140、導電層150、絶縁層160および導電層170上に絶縁層175を形成する。絶縁層175の材質は、実施の形態3の説明を参照することができる。トランジスタ101の場合は、酸化アルミニウム膜を用いることが好ましい。絶縁層175は、スパッタ法、CVD法、MBE法などで形成することができる。

#### 【0273】

次に、絶縁層175上に絶縁層180を形成する(図26(C)参照)。絶縁層180の材質は、実施の形態3の説明を参照することができる。また、絶縁層180は、スパッタ法、CVD法、MBE法などで形成することができる。

#### 【0274】

また、絶縁層175および/または絶縁層180にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理法などを用いて酸素を添加してもよい。酸素を添加することによって、絶縁層175および/または絶縁層1

10

20

30

40

50

80から酸化物半導体層130への酸素の供給をさらに容易にすることができます。

**【0275】**

次に、第3の加熱処理を行ってもよい。第3の加熱処理は、第1の加熱処理と同様の条件で行うことができる。第3の加熱処理により、絶縁層120、絶縁層175、絶縁層180から過剰酸素が放出されやすくなり、酸化物半導体層130の酸素欠損を低減することができる。

**【0276】**

なお、図69(A)、(B)の形態を用いる場合には、ゲート絶縁膜となる絶縁膜160Aを形成した後に絶縁膜160A(ブロック層165)を介して酸化物半導体層の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して酸素イオン40の注入を行えばよい(図71参照)。

10

**【0277】**

次に、図15に示すトランジスタ107の作製方法について説明する。なお、上述したトランジスタ102の作製方法と重複する工程の詳細な説明は省略する。

**【0278】**

基板115上に絶縁層120を形成し、当該絶縁層上に酸化物半導体層130aとなる酸化物半導体膜130A、および酸化物半導体層130bとなる酸化物半導体膜130Bをスパッタ法、CVD法、MBE法などを用いて成膜する(図27(A)参照)。

20

**【0279】**

次に、第1の導電膜を酸化物半導体膜130B上に形成し、前述した方法と同様に第1のレジストマスクを用いて導電層を形成する、そして、当該導電層をハードマスクとして酸化物半導体膜130Aおよび酸化物半導体膜130Bを選択的にエッチングし、酸化物半導体層130aおよび酸化物半導体層130bからなる積層を形成する。なお、ハードマスクを形成せずに、第1のレジストマスクを用いて当該積層を形成してもよい。

**【0280】**

次に、上記導電層を取り除き、基板115または絶縁層120が有する略平面に対して垂直な角度( )を0°、当概略平面に対して平行な角度( )を90°としたとき、例えば45°の角度から上記積層の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して酸素イオン40の注入を行う(図27(B)参照)。なお、上記導電層を利用してトランジスタ111の構造を形成することもできる。

30

**【0281】**

酸素イオン注入の条件は、前述したトランジスタ107の作製方法と同様の条件を用いることができる。

**【0282】**

次に、上記積層を覆うように第2の導電膜を形成する。そして、ソース領域およびドレン領域となる部分の上に第2のレジストマスクを形成し、当該第2のレジストマスクを用いて第2の導電膜の一部をエッチングし、導電層140および導電層150を形成する(図27(C)参照)。

**【0283】**

次に、酸化物半導体層130aおよび酸化物半導体層130bの積層上、ならびに導電層140および導電層150上に酸化物半導体層130cとなる酸化物半導体膜130Cを形成する。さらに、酸化物半導体膜130C上にゲート絶縁膜となる絶縁膜160A、および導電層170となる第3の導電膜171Aおよび第4の導電膜172Aを形成する。

40

**【0284】**

次に、第4の導電膜172A上に第3のレジストマスク156を形成する(図28(A)参照)。そして、当該レジストマスクを用いて、第3の導電膜171A、第4の導電膜172A、絶縁膜160A、および酸化物半導体膜130Cを選択的にエッチングし、導電層171および導電層172からなる導電層170、絶縁層160、および酸化物半導体層130cを形成する(図28(B)参照)。なお、絶縁膜160Aおよび酸化物半導体膜130Cを第4のレジストマスクを用いてエッチングすることで、トランジスタ108

50

を作製することができる。

**【0285】**

次に、絶縁層120、酸化物半導体層130（酸化物半導体層130a、酸化物半導体層130b、酸化物半導体層130c）、導電層140、導電層150、絶縁層160および導電層170上に絶縁層175および絶縁層180を形成する（図28（C）参照）。

**【0286】**

なお、図69（A）、（B）の形態を用いる場合には、酸化物半導体膜130Cを形成した後に酸化物半導体膜130C（ブロック層165）を介して積層（酸化物半導体層130aおよび酸化物半導体層130bの）の上面およびチャネル幅方向の略平面に対して垂直な断面における側面に対して酸素イオン40の注入を行えばよい（図72参照）。 10

**【0287】**

以上の工程において、図15に示したトランジスタ107を作製することができる。

**【0288】**

なお、本実施の形態で説明した金属膜、半導体膜、無機絶縁膜など様々な膜は、代表的にはスパッタ法やプラズマCVD法により形成することができるが、他の方法、例えば、熱CVD（Chemical Vapor Deposition）法により形成してもよい。熱CVD法の例としては、MOCVD（Metal Organic Chemical Vapor Deposition）法やALD（Atomic Layer Deposition）法などがある。 20

**【0289】**

熱CVD法は、プラズマを使わない成膜方法のため、プラズマダメージにより欠陥が生成されることが無いという利点を有する。

**【0290】**

また、熱CVD法では、原料ガスと酸化剤を同時にチャンバー内に送り、チャンバー内を大気圧または減圧下とし、基板近傍または基板上で反応させて基板上に堆積させることで成膜を行ってもよい。

**【0291】**

ALD法は、チャンバー内を大気圧または減圧下とし、反応のための原料ガスが順次にチャンバーに導入され、そのガス導入の順序を繰り返すことで成膜を行ってもよい。例えば、それぞれのスイッチングバルブ（高速バルブとも呼ぶ）を切り替えて2種類以上の原料ガスを順番にチャンバーに供給し、複数種の原料ガスが混ざらないように第1の原料ガスと同時またはその後に不活性ガス（アルゴン、或いは窒素など）などを導入し、第2の原料ガスを導入する。なお、同時に不活性ガスを導入する場合には、不活性ガスはキャリアガスとなり、また、第2の原料ガスの導入時にも同時に不活性ガスを導入してもよい。また、不活性ガスを導入する代わりに真空排気によって第1の原料ガスを排出した後、第2の原料ガスを導入してもよい。第1の原料ガスが基板の表面に吸着して第1の層を成膜し、後から導入される第2の原料ガスと反応して、第2の層が第1の層上に積層されて薄膜が形成される。このガス導入順序を制御しつつ所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、ガス導入順序を繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なFETを作製する場合に適している。 30

**【0292】**

MOCVD法やALD法などの熱CVD法は、これまでに記載した実施形態に開示された金属膜、半導体膜、無機絶縁膜など様々な膜を形成することができ、例えば、In-Ga-ZnO<sub>x</sub>（X>0）膜を成膜する場合には、トリメチルインジウム、トリメチルガリウム、およびジメチル亜鉛を用いることができる。なお、トリメチルインジウムの化学式は、In(CH<sub>3</sub>)<sub>3</sub>である。また、トリメチルガリウムの化学式は、Ga(CH<sub>3</sub>)<sub>3</sub>である。また、ジメチル亜鉛の化学式は、Zn(CH<sub>3</sub>)<sub>2</sub>である。また、これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム（化学式Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>）を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛（化学式Zn(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>） 40

$H_5)_2$ )を用いることもできる。

【0293】

例えば、ALDを利用する成膜装置により酸化ハフニウム膜を形成する場合には、溶媒とハフニウム前駆体化合物を含む液体(ハフニウムアルコキシド溶液、代表的にはテトラキスジメチルアミドハフニウム(TDMAH))を気化させた原料ガスと、酸化剤としてオゾン( $O_3$ )の2種類のガスを用いる。なお、テトラキスジメチルアミドハフニウムの化学式は $Hf[N(CH_3)_2]_4$ である。また、他の材料液としては、テトラキス(エチルメチルアミド)ハフニウムなどがある。

【0294】

例えば、ALDを利用する成膜装置により酸化アルミニウム膜を形成する場合には、溶媒とアルミニウム前駆体化合物を含む液体(トリメチルアルミニウムTMAなど)を気化させた原料ガスと、酸化剤として $H_2O$ の2種類のガスを用いる。なお、トリメチルアルミニウムの化学式は $Al(CH_3)_3$ である。また、他の材料液としては、トリス(ジメチルアミド)アルミニウム、トリイソブチルアルミニウム、アルミニウムトリス(2,2,6,6-テトラメチル-3,5-ヘプタンジオナート)などがある。

【0295】

例えば、ALDを利用する成膜装置により酸化シリコン膜を形成する場合には、ヘキサクロロジシランを被成膜面に吸着させ、吸着物に含まれる塩素を除去し、酸化性ガス( $O_2$ 、一酸化二窒素)のラジカルを供給して吸着物と反応させる。

【0296】

例えば、ALDを利用する成膜装置によりタンクステン膜を成膜する場合には、 $WF_6$ ガスと $B_2H_6$ ガスを順次繰り返し導入して初期タンクステン膜を形成し、その後、 $WF_6$ ガスと $H_2$ ガス同時に導入してタンクステン膜を形成する。なお、 $B_2H_6$ ガスに代えて $SiH_4$ ガスを用いてもよい。

【0297】

例えば、ALDを利用する成膜装置により酸化物半導体膜、例えば $In-Ga-ZnO_x$ ( $X > 0$ )膜を成膜する場合には、 $In(CH_3)_3$ ガスと $O_3$ ガスを順次繰り返し導入して $In-O$ 層を形成し、その後、 $Ga(CH_3)_3$ ガスと $O_3$ ガスを同時に導入して $GaO$ 層を形成し、更にその後 $Zn(CH_3)_2$ と $O_3$ ガスを同時に導入して $ZnO$ 層を形成する。なお、これらの層の順番はこの例に限らない。また、これらのガスを混ぜて $In-Ga-O$ 層や $In-Zn-O$ 層、 $Ga-Zn-O$ 層などの混合化合物層を形成しても良い。なお、 $O_3$ ガスに変えて $Ar$ 等の不活性ガスでバーピングして得られた $H_2O$ ガスを用いても良いが、 $H$ を含まない $O_3$ ガスを用いる方が好ましい。また、 $In(CH_3)_3$ ガスにかえて、 $In(C_2H_5)_3$ ガスを用いても良い。また、 $Ga(CH_3)_3$ ガスにかえて、 $Ga(C_2H_5)_3$ ガスを用いても良い。また、 $Zn(CH_3)_2$ ガスを用いても良い。

【0298】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0299】

(実施の形態5)

本実施の形態では、本発明の一態様であるトランジスタに使用することができる酸化物半導体膜について説明する。

【0300】

なお、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。

【0301】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す

10

20

30

40

50

。

### 【0302】

<酸化物半導体の構造>

以下では、酸化物半導体の構造について説明する。

### 【0303】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体とに分けられる。非単結晶酸化物半導体としては、C AAC - OS ( C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、n c - OS (nanocrystalline Oxide Semiconductor)、擬似非晶質酸化物半導体 (a - like OS : amorphous like Oxide Semiconductor)、非晶質酸化物半導体などがある。

10

### 【0304】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体とに分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、C AAC - OS、多結晶酸化物半導体、n c - OSなどがある。

### 【0305】

非晶質構造の定義としては、一般に、準安定状態で固定化していないこと、等方的であつて不均質構造を持たないことなどが知られている。また、結合角度が柔軟であり、短距離秩序性は有するが、長距離秩序性を有さない構造言い換えることもできる。

### 【0306】

逆の見方をすると、本質的に安定な酸化物半導体の場合、完全な非晶質 (completely amorphous) 酸化物半導体と呼ぶことはできない。また、等方的でない(例えば、微小な領域において周期構造を有する)酸化物半導体を、完全な非晶質酸化物半導体と呼ぶことはできない。ただし、a - like OSは、微小な領域において周期構造を有するものの、鬆(ボイドともいう。)を有し、不安定な構造である。そのため、物性的には非晶質酸化物半導体に近いといえる。

20

### 【0307】

< C AAC - OS >

まずは、C AAC - OSについて説明する。

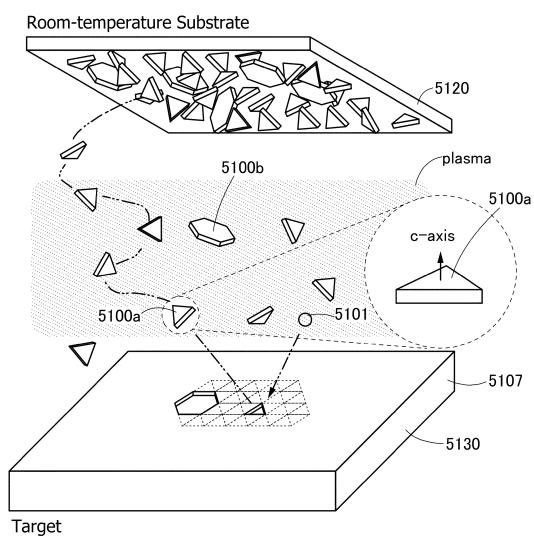

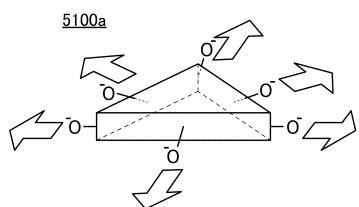

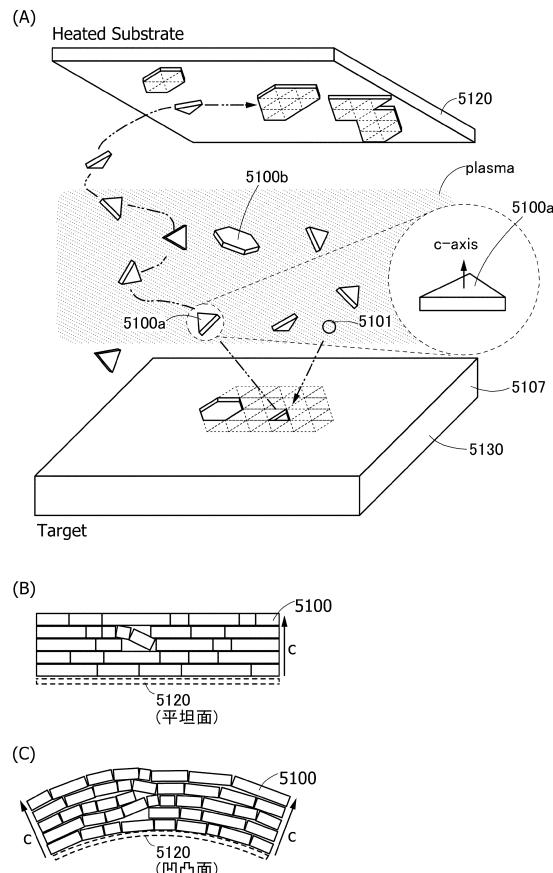

### 【0308】

C AAC - OSは、c 軸配向した複数の結晶部(ペレットともいう。)を有する酸化物半導体の一つである。

30

### 【0309】

透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって、C AAC - OSの明視野像と回折パターンとの複合解析像(高分解能TEM像ともいう。)を観察すると、複数のペレットを確認することができる。一方、高分解能TEM像ではペレット同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を明確に確認することができない。そのため、C AAC - OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

### 【0310】

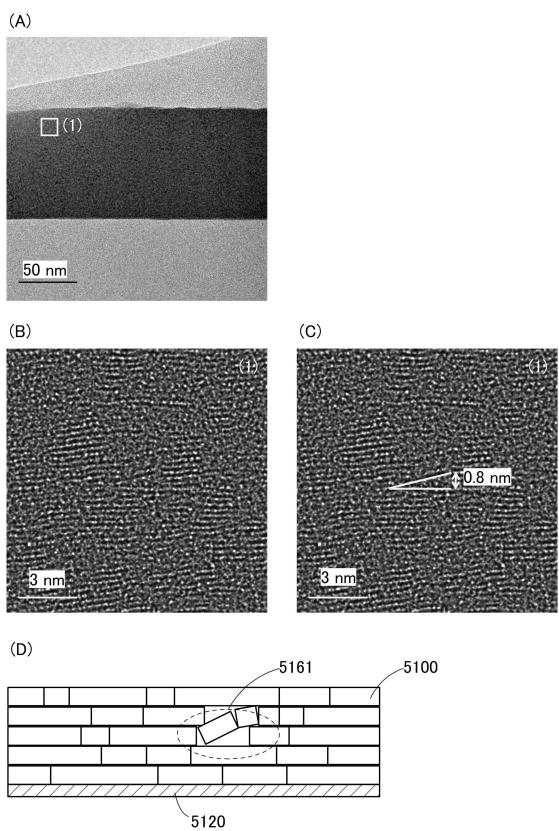

以下では、TEMによって観察したC AAC - OSについて説明する。図29(A)に、試料面と略平行な方向から観察したC AAC - OSの断面の高分解能TEM像を示す。高分解能TEM像の観察には、球面収差補正(Spherical Aberration Corrector)機能を用いた。球面収差補正機能を用いた高分解能TEM像を、特にCs補正高分解能TEM像と呼ぶ。Cs補正高分解能TEM像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡JEM - ARM200Fなどによって行うことができる。

40

### 【0311】

図29(A)の領域(1)を拡大したCs補正高分解能TEM像を図29(B)に示す。

図29(B)より、ペレットにおいて、金属原子が層状に配列していることを確認できる

50

。金属原子の各層の配列は、 C A A C - O S の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映しており、 C A A C - O S の被形成面または上面と平行となる。

### 【 0 3 1 2 】

図 2 9 ( B ) に示すように、 C A A C - O S は特徴的な原子配列を有する。図 2 9 ( C ) は、特徴的な原子配列を、補助線で示したものである。図 2 9 ( B ) および図 2 9 ( C ) より、ペレット一つの大きさは 1 nm 以上 3 nm 以下程度であり、ペレットとペレットとの傾きにより生じる隙間の大きさは 0.8 nm 程度であることがわかる。したがって、ペレットを、ナノ結晶 ( n c : n a n o c r y s t a l ) と呼ぶこともできる。また、 C A A C - O S を、 C A N C ( C - A x i s A l i g n e d n a n o c r y s t a l s ) を有する酸化物半導体と呼ぶこともできる。

10

### 【 0 3 1 3 】

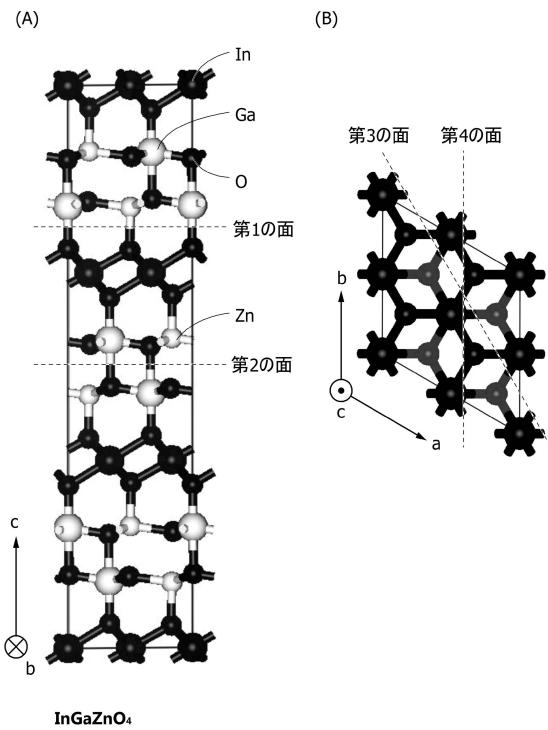

ここで、 Cs 補正高分解能 TEM 像をもとに、基板 5120 上の C A A C - O S のペレット 5100 の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる（図 2 9 ( D ) 参照。）。図 2 9 ( C ) で観察されたペレットとペレットとの間で傾きが生じている箇所は、図 2 9 ( D ) に示す領域 5161 に相当する。

### 【 0 3 1 4 】

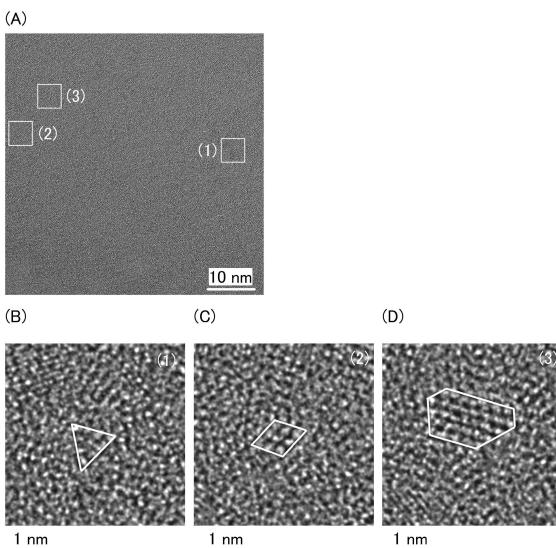

また、図 3 0 ( A ) に、試料面と略垂直な方向から観察した C A A C - O S の平面の Cs 補正高分解能 TEM 像を示す。図 3 0 ( A ) の領域 ( 1 ) 、領域 ( 2 ) および領域 ( 3 ) を拡大した Cs 補正高分解能 TEM 像を、それぞれ図 3 0 ( B ) 、図 3 0 ( C ) および図 3 0 ( D ) に示す。図 3 0 ( B ) 、図 3 0 ( C ) および図 3 0 ( D ) より、ペレットは、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なるペレット間で、金属原子の配列に規則性は見られない。

20

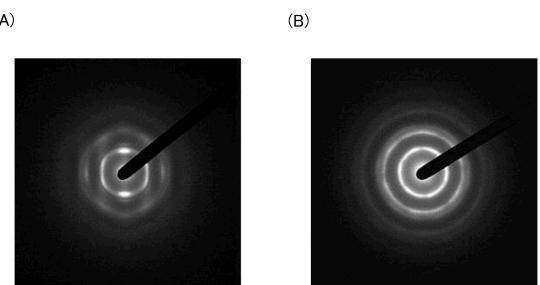

### 【 0 3 1 5 】

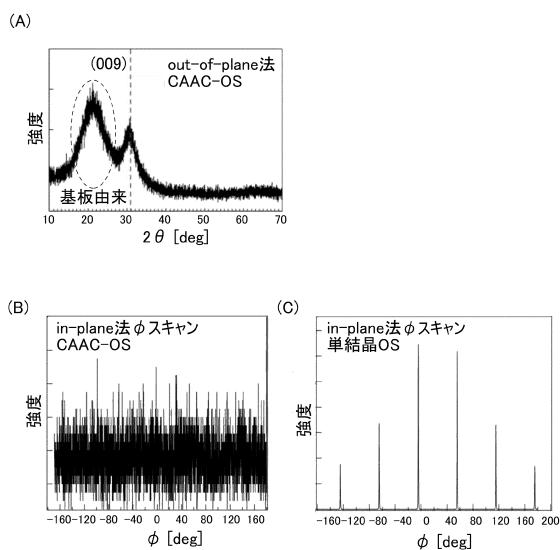

次に、 X 線回折 ( X R D : X - R a y D i f f r a c t i o n ) によって解析した C A A C - O S について説明する。例えば、 I n G a Z n O<sub>4</sub> の結晶を有する C A A C - O S に対し、 o u t - o f - p l a n e 法による構造解析を行うと、図 3 1 ( A ) に示すように回折角 ( 2θ ) が 31° 。近傍にピークが現れる場合がある。このピークは、 I n G a Z n O<sub>4</sub> の結晶の ( 009 ) 面に帰属されることから、 C A A C - O S の結晶が c 軸配向性を有し、 c 軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

30

### 【 0 3 1 6 】

なお、 C A A C - O S の o u t - o f - p l a n e 法による構造解析では、 2θ が 31° 。近傍のピークの他に、 2θ が 36° 。近傍にもピークが現れる場合がある。 2θ が 36° 。近傍のピークは、 C A A C - O S 中の一部に、 c 軸配向性を有さない結晶が含まれることを示している。より好ましい C A A C - O S は、 o u t - o f - p l a n e 法による構造解析では、 2θ が 31° 。近傍にピークを示し、 2θ が 36° 。近傍にピークを示さない。

### 【 0 3 1 7 】

一方、 C A A C - O S に対し、 c 軸に略垂直な方向から X 線を入射させる i n - p l a n e 法による構造解析を行うと、 2θ が 56° 。近傍にピークが現れる。このピークは、 I n G a Z n O<sub>4</sub> の結晶の ( 110 ) 面に帰属される。 C A A C - O S の場合は、 2θ を 56° 。近傍に固定し、試料面の法線ベクトルを軸 ( c 軸) として試料を回転させながら分析 ( スキャン ) を行っても、図 3 1 ( B ) に示すように明瞭なピークは現れない。これに対し、 I n G a Z n O<sub>4</sub> の単結晶酸化物半導体であれば、 2θ を 56° 。近傍に固定してスキャンした場合、図 3 1 ( C ) に示すように ( 110 ) 面と等価な結晶面に帰属されるピークが 6 本観察される。したがって、 X R D を用いた構造解析から、 C A A C - O S は、 a 軸および b 軸の配向が不規則であることが確認できる。

40

### 【 0 3 1 8 】

次に、電子回折によって解析した C A A C - O S について説明する。例えば、 I n G a Z n O<sub>4</sub> の結晶を有する C A A C - O S に対し、試料面に平行にプローブ径が 300 nm の電子線を入射させると、図 7 3 ( A ) に示すような回折パターン ( 制限視野透過電子回折パターンともいう。 ) が現れる場合がある。この回折パターンには、 I n G a Z n O<sub>4</sub> の

50

結晶の(009)面に起因するスポットが含まれる。したがって、電子回折によつても、CAAC-OSに含まれるペレットがc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いてることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が300nmの電子線を入射させたときの回折パターンを図73(B)に示す。図73(B)より、リング状の回折パターンが確認される。したがって、電子回折によつても、CAAC-OSに含まれるペレットのa軸およびb軸は配向性を有さないことがわかる。なお、図73(B)における第1リングは、InGaZnO<sub>4</sub>の結晶の(010)面および(100)面などに起因すると考えられる。また、図73(B)における第2リングは(110)面などに起因すると考えられる。

## 【0319】

10

上述したように、CAAC-OSは結晶性の高い酸化物半導体である。酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、逆の見方をするとCAAC-OSは不純物や欠陥(酸素欠損など)の少ない酸化物半導体ともいえる。

## 【0320】

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

20

## 【0321】

酸化物半導体が不純物や欠陥を有する場合、光や熱などによって特性が変動する場合がある。例えば、酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。また、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

## 【0322】

不純物および酸素欠損の少ないCAAC-OSは、キャリア密度の低い酸化物半導体である。具体的には、 $8 \times 10^{11} / \text{cm}^3$ 未満、好ましくは $1 \times 10^{11} / \text{cm}^3$ 未満、さらに好ましくは $1 \times 10^{10} / \text{cm}^3$ 未満であり、 $1 \times 10^{-9} / \text{cm}^3$ 以上のキャリア密度の酸化物半導体とすることができます。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。CAAC-OSは、不純物濃度が低く、欠陥準位密度が低い。即ち、安定な特性を有する酸化物半導体であるといえる。

30

## 【0323】

&lt;nc-OS&gt;

次に、nc-OSについて説明する。

## 【0324】

nc-OSは、高分解能TEM像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。nc-OSに含まれる結晶部は、1nm以上10nm以下、または1nm以上3nm以下の大きさであることが多い。なお、結晶部の大きさが10nmより大きく100nm以下である酸化物半導体を微結晶酸化物半導体と呼ぶことがある。nc-OSは、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、CAAC-OSにおけるペレットと起源を同じくする可能性がある。そのため、以下ではnc-OSの結晶部をペレットと呼ぶ場合がある。

40

## 【0325】

nc-OSは、微小な領域(例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域)において原子配列に周期性を有する。また、nc-OSは、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、nc-OSは、分析方法によっては、a-like OSや非晶質酸化物半導体と区別が付かない場合がある。例えば、nc-OSに対し、ペレットよりも大きい径のX

50

線を用いた場合、out-of-plane法による解析では、結晶面を示すピークは検出されない。また、nc-OSに対し、ペレットよりも大きいプロープ径（例えば50nm以上）の電子線を用いる電子回折を行うと、ハローパターンのような回折パターンが観測される。一方、nc-OSに対し、ペレットの大きさと近いかペレットより小さいプロープ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、nc-OSに対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。さらに、リング状の領域内に複数のスポットが観測される場合がある。

#### 【0326】

このように、ペレット（ナノ結晶）間では結晶方位が規則性を有さないことから、nc-OSを、RANC（Random Aligned nanocrystals）を有する酸化物半導体、またはNANC（Non-Aligned nanocrystals）を有する酸化物半導体と呼ぶこともできる。10

#### 【0327】

nc-OSは、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、nc-OSは、a-like OSや非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、nc-OSは、異なるペレット間で結晶方位に規則性が見られない。そのため、nc-OSは、CAAC-OSと比べて欠陥準位密度が高くなる。

#### 【0328】

<a-like OS>20

a-like OSは、nc-OSと非晶質酸化物半導体との間の構造を有する酸化物半導体である。

#### 【0329】

a-like OSは、高分解能TEM像において鬆が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。

#### 【0330】

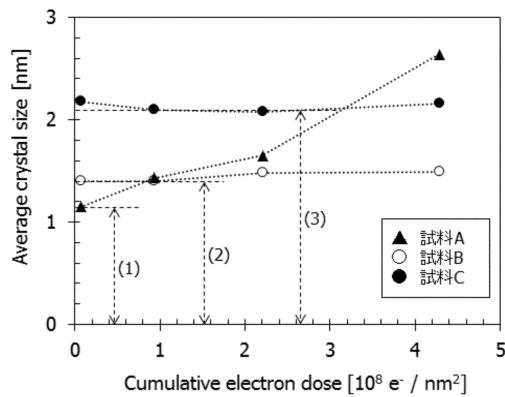

鬆を有するため、a-like OSは、不安定な構造である。以下では、a-like OSが、CAAC-OSおよびnc-OSと比べて不安定な構造であることを示すため、電子照射による構造の変化を示す。30

#### 【0331】

電子照射を行う試料として、a-like OS（試料Aと表記する。）、nc-OS（試料Bと表記する。）およびCAAC-OS（試料Cと表記する。）を準備する。いずれの試料もIn-Ga-Zn酸化物である。

#### 【0332】