(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3732914号

(P3732914)

(45) 発行日 平成18年1月11日(2006.1.11)

(24) 登録日 平成17年10月21日(2005.10.21)

(51) Int.C1.

F 1

|              |           |             |      |

|--------------|-----------|-------------|------|

| HO3K 19/0948 | (2006.01) | HO3K 19/094 | B    |

| HO3K 17/08   | (2006.01) | HO3K 17/08  | C    |

| HO3K 17/22   | (2006.01) | HO3K 17/22  | E    |

| HO3K 19/00   | (2006.01) | HO3K 19/00  | A    |

| HO1L 27/092  | (2006.01) | HO1L 27/08  | 321D |

請求項の数 8 (全 18 頁) 最終頁に続く

(21) 出願番号

特願平9-45235

(22) 出願日

平成9年2月28日(1997.2.28)

(65) 公開番号

特開平10-242839

(43) 公開日

平成10年9月11日(1998.9.11)

審査請求日

平成15年10月24日(2003.10.24)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100089071

弁理士 玉村 静世

(74) 代理人 100075096

弁理士 作田 康夫

(74) 代理人 100068504

弁理士 小川 勝男

(72) 発明者 伊藤 清男

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(54) 【発明の名称】半導体装置

最終頁に続く

## (57) 【特許請求の範囲】

## 【請求項1】

CMOS回路を有する半導体装置において、

上記CMOS回路は第1動作状態と第2動作状態とを有し、上記MOSFETに印加されるウェル電圧は上記第1動作状態において上記第2動作状態におけるよりも浅く制御されることで、上記第1動作状態における上記MOSFETのしきい値電圧の絶対値は上記第2動作状態における上記MOSFETのしきい値電圧の絶対値が小さくなるよう制御され、

電源投入過程において、上記MOSFETに所定のウェル電位を印加することにより上記MOSFETのソース・ウェル間のpn接合が順方向にバイアスされることによるCMOSラッチアップを防止した後に、上記CMOS回路の電源電圧を印加することを特徴とする半導体装置。

## 【請求項2】

請求項1において、

上記MOSFETはサブスレッショルド電流により、上記第1動作状態において実質的に十分カットオフできないMOSFETであることを特徴とする半導体装置。

## 【請求項3】

請求項1または2において、

上記ウェル電圧を制御するウェル電圧制御回路を有し、

電源遮断過程において、上記CMOS回路の電源電圧を遮断した後に、上記ウェル電圧 20

制御回路の電源電圧を遮断することを特徴とする半導体装置。

【請求項 4】

ウェル電圧制御回路と CMOS 回路とを有し、

上記 CMOS 回路は第 1 動作状態と第 2 動作状態とを有し、上記 MOSFET に印加されるウェル電圧は上記第 1 動作状態において上記第 2 動作状態におけるよりも浅く制御されることで、上記第 1 動作状態における上記 MOSFET のしきい値電圧の絶対値は上記第 2 動作状態における上記 MOSFET のしきい値電圧の絶対値が小さくなるよう制御され、

電源投入過程において、上記ウェル電圧制御回路により上記 MOSFET のウェル電位を駆動した後に、上記 CMOS 回路の電源電圧を印加することを特徴とする半導体装置。 10

【請求項 5】

請求項 4 において、

上記ウェル電圧制御回路の電源電圧は上記 CMOS 回路の電源電圧よりも大きいことを特徴とする半導体装置。

【請求項 6】

請求項 4 または 5 において、

上記 MOSFET はサブスレッショルド電流により、上記第 1 動作状態において実質的に十分カットオフできない MOSFET であることを特徴とする半導体装置。

【請求項 7】

請求項 4 乃至 6 のいずれかにおいて、

電源遮断過程において、上記 CMOS 回路の電源電圧を遮断した後に、上記ウェル電圧制御回路の電源電圧を遮断することを特徴とする半導体装置。 20

【請求項 8】

請求項 1 乃至 7 のいずれかにおいて、

上記 CMOS 回路の電源電圧は 2V 以下であることを特徴とする半導体装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は半導体装置に関し、特に高速性と低電力性を兼ね備えた半導体装置に適した技術である。 30

【0002】

【従来の技術】

基板バイアス制御による低電力技術としては、例えば、1996 アイ・イー・イー・イー・インターナショナル ソリッド ステート サーキット ダイジェスト オブ テクニカル ペーパーズ、第 166 頁から第 167 頁(1996 IEEE International Solid-State Circuit, Digest of Technical Papers(1996) pp.166-167)に記載されている。

【0003】

【発明が解決しようとする課題】

近年、CMOS LSI(Complementary Metal Oxide Semiconductor Large Scale Integrated Circuit)の低電圧動作に伴い、MOSFET(トランジスタ)のしきい値電圧  $V_T$  を動作電圧の低下に応じて小さくし高速動作を維持する動きが活発になっている。しかし、電源電圧が 2V 以下になり、それに応じてしきい値電圧  $V_T$  を 0.5V 以下に小さくするとトランジスタが完全にカットオフできなくなる、いわゆるサブスレッショルドリーク電流が増加する。このため LSI チップのスタンバイ電流が増大し、例えば、電池動作を前提とする CMOS LSI チップから構成されるシステムを設計する際のあい路となっている。しきい値電圧  $V_T$  がさらに小さくなるにつれ通常動作時の電流までも増大するとさえいわれている。 40

【0004】

このあい路を開くために、通常動作期間はチップ内のすべての MOSFET のしきい値電圧  $V_T$  を小さくして高速動作させ、スタンバイ時にはしきい値電圧  $V_T$  を十分大きな値にしてスタンバイ電流を低減する方式がよく知られている。しかし、この方式には以下の 3 つの

問題点がある。

【0005】

(1) 従来は電源投入時にラッチアップなどによって過大電流が流れ、CMOS LSIチップ内の配線が溶断したりする。あるいは電源の電流容量を越え、正常な電源電圧が印加できなかったりする。MOSFETの基板(ウェル)とソースが等電位とはならないレイアウトと結線になっていることに起因する。例えば、そのソースに正の電圧電源を与えるpチャネルMOSFET(PMOSFET)を例にとろう。ソース(p層)に正の電圧電源(例えば、1.8V)が印加されると、その直前まではウェル(nウェル)はフローティング0Vであるから、ソース・ウェル間のpn接合は順方向に過度にバイアスされてCMOSラッチアップの原因となる。従来までの2V以上のCMOS LSIの製品では、MOSFETのウェルとソースができるだけ等電位になるように両者を近くで結線しているから、電源投入過程でも、その後の通常動作時と同様に上記pn接合は順方向にバイアスされることはない。しかも、しきい値電圧 $V_T$ は常に一定でありその値がほぼ0.5V以上に設定されているのでサブスレッショルド電流が問題になることもない。nチャネルMOSFET(NMOSFET)でも同様だがPMOSFETほどには深刻な問題とはならない。そのドレインに電源電圧が印加された場合、その直前まではNMOSFETの基板(pウェル)はフローティング0Vでソースも0Vのアース電位に固定されているので、ドレインとウェルで形成されるpn接合が順方向にバイアスされないためである。ただし、ドレイン・ソース間には、しきい値電圧 $V_T$ が0.5V以下ではサブスレッショルド電流は流れる。ウェルとソースを分離・制御することを特長とした上記従来の技術に記載した文献には、このような電源投入時の問題は述べられておらず、CMOS LSIの低しきい値電圧 $V_T$ 化に伴う新たな課題である。

10

20

【0006】

(2) 通常動作モードからスタンバイモードへの切り換え時間、あるいはスタンバイモードから通常動作モードへの切り換え時間が $\mu$ sオーダとなりきわめて長い。例えば、基板電圧を同じチップ内部で発生する場合を考えてみよう。基板電圧は、チップ内のキャパシタをポンピングするいわゆるチャージポンピング回路をもとに作られるから、その出力電流は低く限定される。一方、基板電源端子はチップ内のトランジスタで共通に結線されているために、合計の基板容量はきわめて大きな値(100pF以上)となる。したがって、上記のようにモード切り換え時には、電流駆動能力の低い基板電圧発生回路で大きな負荷(基板)容量を駆動することになり、その応答時間が長くなる。

30

【0007】

(3) 通常動作期間中に、入出力の電圧変化のない(いわゆる非活性状態にある)CMOS回路あるいは回路ブロック内のトランジスタのしきい値電圧 $V_T$ は小さいので、CMOS回路といえどもサブスレッショルド電流がいたるところに流れ、チップ全体の動作電流を増大させる。

【0008】

本発明は、これらの諸問題を解決するトランジスタの基板(あるいはウェル)電圧の制御法に関する。

【0009】

本発明の目的は、低しきい値電圧のMOSFETを含むCMOS回路の電源投入時あるいは電源遮断時に起こすラッチアップを阻止することにある。

40

【0010】

本発明の他の目的は、通常動作中のサブスレッショルド電流を低減することにある。

【0011】

本発明の他の目的は、2V以下の低電圧動作のCMOS回路およびそれを用いたLSIならびに半導体装置において、高速性を維持したままで低消費電力ならびに高安定動作を図ることにある。

【0012】

本発明の前記並びにその他の目的と新規な特徴は、本明細書の記述及び添付図面から明かになるであろう。

【0013】

50

【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0014】

すなわち、CMOS回路のウェル電圧を電源投入、通常動作ならびに電源遮断時にわたって制御する。

【0015】

(1) 半導体装置は、通常動作時には実質的に十分カットオフできないMOSFETから成るCMOS回路のウェルに該MOSFETがカットオフできるようにウェル電圧を印加した後に、該CMOS回路に電源電圧を印加する。 10

【0016】

(2) 半導体装置は、第1と第2の電源電圧から成り、第1の電源電圧で動作する電圧変換回路を含む回路によって発生された第3の電源電圧を、通常動作時には実質的に十分カットオフできないMOSFETから成るCMOS回路のウェルに該MOSFETがカットオフできるようにウェル電圧として印加した後に、該CMOS回路に第2の電源電圧を印加する。

【0017】

(3) 半導体装置は、通常動作時には実質的にカットオフできないMOSFETを含むCMOS回路のウェル電位を固定する回路と、該CMOS回路の入力信号の変化に応じて該MOSFETのウェル電位を容量結合によって変化させる回路を具備する。

【0018】

(4) 半導体装置は、1個のMOSFETとキャパシタから成るダイナミックメモリセルとCMOS回路を含み、通常動作中には、該CMOS回路を構成するMOSFETのウェル電位はパルス変化させられるものであり、該ダイナミックメモリセルの基板電圧は実質的に直流電源電圧である。 20

【0019】

(5) 半導体装置は、大きな電圧で動作し、かつ大きなしきい値電圧のMOSFETから成るスタティックメモリセルと小さな電圧で動作し、かつ小さなしきい値電圧のMOSFETから成るCMOS回路を含み、該CMOS回路内のMOSFETのウェル電位をパルス変化させる。

【0020】

(6) 半導体装置は、少なくとも一つのCMOS回路と、スタンバイ制御回路と、電圧変換回路を含み、該電圧変換回路によって発生された電圧を該スタンバイ制御回路に供給し、該スタンバイ制御回路は該電圧を用いて該CMOS回路のウェル電位を動作状態によって変化させ、該ウェル容量よりも大きな容量のキャパシタを該電圧変換回路の出力に接続している。 30

【0021】

【発明の実施の形態】

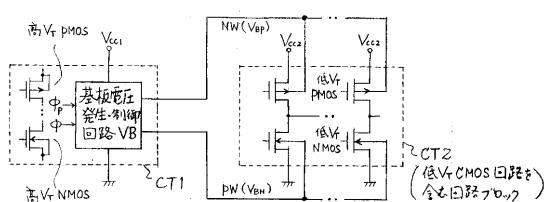

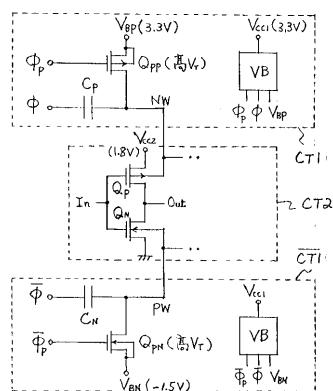

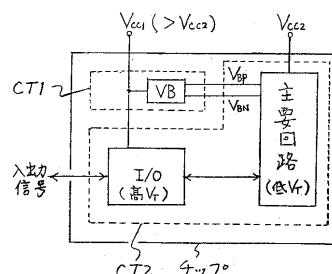

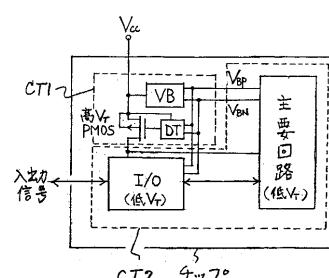

図1は本発明の一実施例である。高い電源電圧Vcc1(例えば、3.3V)で動作する回路ブロックCT1では、その内部トランジスタの動作時のしきい値電圧V<sub>T</sub>は例えば、0.5Vと十分大きく選べる。十分高い電源(動作)電圧なので、わざわざ、しきい値電圧V<sub>T</sub>を0.1Vなどと低くしなくとも高速動作は可能なのである。したがって、通常動作時とスタンバイ時のしきい値電圧V<sub>T</sub>をわざわざ切り換えなくてもサブスレッショルド電流は無視できるほど小さいので、それらトランジスタのソースと基板は同じ電圧を与えるように結線することができる。ここでVBはコントロール信号P、で制御される基板電圧発生・制御回路である。 40

【0022】

一方、低い電源電圧Vcc2(例えば、1.8V)で動作する回路ブロックCT2では、その内部トランジスタのしきい値電圧V<sub>T</sub>を通常動作時には例えば、0.1Vと小さくして高速動作させ、スタンバイ時には例えば、0.5Vと大きくしてスタンバイ電流を減らさなければならない。このしきい値電圧V<sub>T</sub>の制御はトランジスタの基板NW、PWを制御することで行う。

【0023】

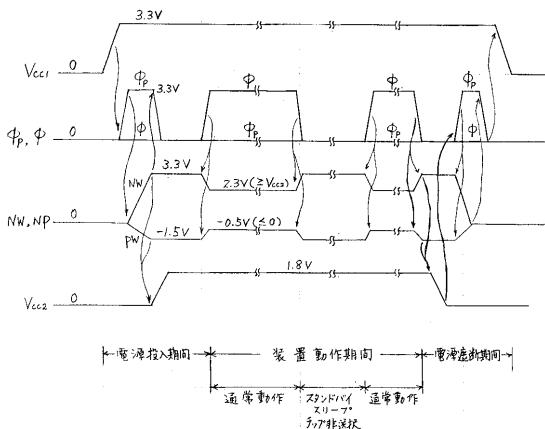

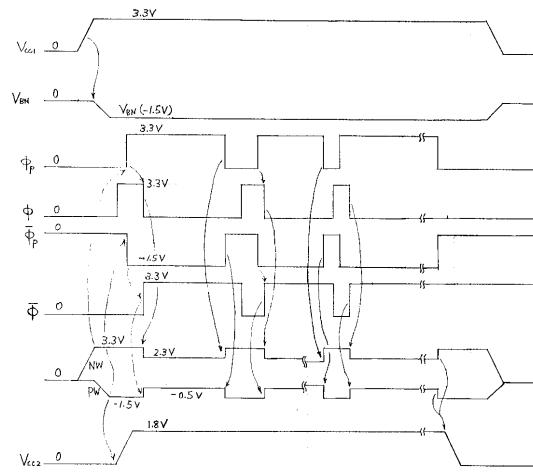

この場合、電源投入時の回路ブロックCT2内トランジスタの基板電圧は図2のように制御される。

10

20

30

40

50

## 【0024】

基板NW、PWの電圧 $V_{BP}$ 、 $V_{BN}$ は最初に投入された3.3Vをもとに作られるが、この電圧は低い電源電圧で動作する回路ブロックCT2内のトランジスタを十分カットオフする値に選ばれる。例えば、PMOSFETに対しては3.3Vで、NMOSFETに対しては-1.5Vである。まず、この基板電圧を回路ブロックCT2に与え、その後で低い電源電圧 $V_{CC2}$ を与える。したがって、低い電源電圧を投入する過程では、回路ブロックCT2内トランジスタのしきい値電圧 $V_T$ は十分大きいので各トランジスタからのサブスレッショルド電流が累積されて過大なチップ電流になることもないし、各トランジスタの基板電圧は0V程度のフローティング状態とはならないのでラッチアップを起こすことはない。

## 【0025】

10

その後、基板NW、PWの電圧 $V_{BP}$ 、 $V_{BN}$ を浅くすることで(例えば、2.3Vと-0.5V程度)、回路ブロックCT2内のトランジスタのしきい値電圧 $V_T$ を低くして通常動作に移行させ、主要回路の動作を開始させる。回路ブロック内のクロックを停止する(クロックをハイレベル又はローレベルに固定する)スタンバイ時、スリープ時あるいはチップの非選択時には基板電圧 $V_{BP}$ 、 $V_{BN}$ を深く(例えば、3.3Vと-1.5V)することで回路ブロックCT2内のトランジスタのしきい値電圧 $V_T$ を高くする。これによりサブスレッショルド電流による消費電力増加を減少させることができる。

## 【0026】

20

電源遮断時には基板電圧 $V_{BP}$ 、 $V_{BN}$ を十分深くしてから $V_{CC2}$ をオフにし、その後に電源電圧 $V_{CC1}$ をオフにする。ここで電源電圧の印加順序は、例えば、高い電源電圧 $V_{CC1}$ が印加されてから、タイマーなどによって時間間隔を作り、その後、低い電源電圧 $V_{CC2}$ を入力すればよい。また回路ブロックCT1と回路ブロックCT2は異なる半導体チップで構成しても、あるいは同一チップ上に集積してもよい。

## 【0027】

20

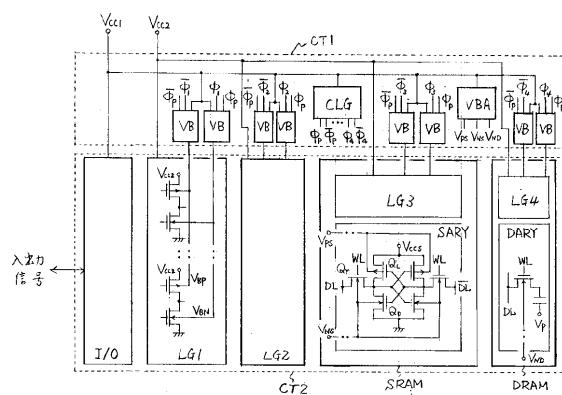

図3は回路ブロックCT1と回路ブロックCT2を同一チップ上に集積した実施例である。I/Oはチップ外とのインターフェース回路、LG1からLG4は基板電圧を制御させる回路ブロックで、低しきい値電圧 $V_T$ トランジスタを含む回路で構成されている。SRAMはスタティックメモリセルで構成されたメモリアレイSARYを含むスタティックメモリで、 $V_{CCS}$ はメモリセルへの電力供給電源電圧である。DRAMは1個のMOSFETとキャパシタから成るダイナミックメモリセルで構成されたメモリアレイDARYを含むダイナミックメモリで、 $V_P$ はキャパシタ電極電圧である。DL、/DLはデータ線で、WLはワード線である。

30

## 【0028】

30

とくに限定しないが、メモリアレイSARYおよびメモリアレイDARYはここでは高しきい値 $V_T$ トランジスタで構成されているものとする。VBは基板電圧発生回路で、基板電圧制御回路CLGからのコントロール信号群( p、/ p、 1、/ 1、 2、/ 2、 3、/ 3、 4、/ 4)によって制御されている。VBAはメモリアレーへの基板電圧発生回路であり、メモリアレイSARYおよびメモリアレイDARY内の基板電圧 $V_{PS}$ 、 $V_{NS}$ 、 $V_{ND}$ を供給している。これらの基板電圧 $V_{PS}$ 、 $V_{NS}$ 、 $V_{ND}$ は通常は直流電圧あるいは準直流電圧である。ここで基板電圧発生回路VB、基板電圧制御回路CLGおよび基板電圧発生回路VBAからなる回路ブロックCT1の主要部は高しきい値電圧 $V_T$ のMOSFETで構成されている。また、インターフェース回路I/Oおよび基板電圧発生回路VBには高い電源電圧( $V_{CC1}$ )が供給され、他の回路ブロックには低い電源電圧( $V_{CC2}$ )が供給されている。

40

## 【0029】

ここでメモリアレイSARYおよびメモリアレイDARYは他の回路とは異なる性質を持っているので、基板電圧の与え方は異なっている。すなわち、メモリアレイ部はチップ全体に占める面積の割合が大きいので、一般に高密度が望ましい。このためには素子間分離幅を狭くしなければならない。これは一般にメモリアレイ全体に一定の実質的に直流である基板電圧を与える基板バイアス方式と併用されて実現されることが多い。もしこの部分の基板容量を駆動すると素子分離特性が劣化する以外に、この基板容量が大きいためにチップ全体の消費電力を増大するなどといった問題点が生じるためである。したがって、通常はメモ

50

リアレイSARY内の基板電圧 $V_{NS}$ は0Vに、基板電圧 $V_{PS}$ は電源電圧 $V_{CCS}$ に等しく設定され、またメモリアレイDARYでは基板電圧 $V_{ND}$ は-1.5V程度の実質的に直流である電圧が与えられる。ここでメモリアレイSARY内のメモリセルはフリップフロップなので、それを構成するトランジスタのしきい値電圧 $V_T$ が小さすぎるとセル内のサブスレッショルド電流が増加する。メモリアレイSARYは多数のメモリセルで構成されるからメモリアレイSARY全体としてはこの電流は大きな値となる。そこでこれらセル内トランジスタのしきい値電圧 $V_T$ は例えば0.5V程度と大きくし、その大きなしきい値電圧 $V_T$ に見合うだけの高い電源電圧 $V_{CCS}$ に設定するとセルは高速に動作する。例えば電源電圧 $V_{CCS}$ は電源電圧 $V_{CC2}$ (1.8V)よりも大きな電源電圧 $V_{CC1}$ (3.3V)にするのも電源電圧の数を増やすないので有効である。

## 【0030】

10

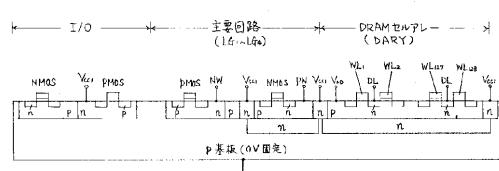

図4は、図3の代表的なデバイス断面構造の概略図である。スタティックメモリSRAMのメモリアレイ部ならびにダイナミックメモリDRAMのメモリアレイ部のキャパシターについては図面を分かり易くするために省略している。

## 【0031】

以下図3のチップを前提に、内部の各回路ブロックに上述した発明を具体的に適用した例を述べる。

## 【0032】

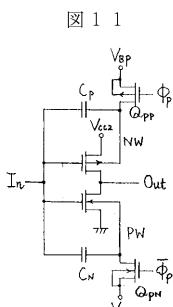

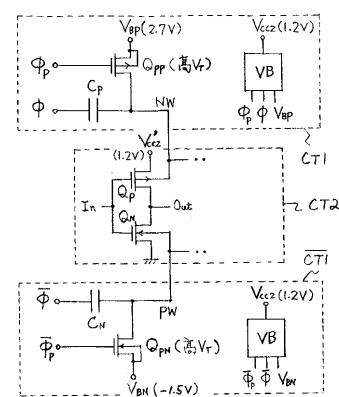

図5は図3の回路ブロック(LG1からLG4)内部のサブ回路ブロックに適用した本発明の一実施例である。回路ブロックCT2内の低しきい値電圧 $V_T$ を有するMOSFETの基板(NW、PW)電圧は、回路ブロックCT1および回路ブロック/CT1によって制御されている。本実施例では、この制御をキャパシタ( $C_P, C_N$ )を利用して行うことに特長がある。基板電圧発生・制御回路VBは、コントロール信号( $p, /p, /p, /p$ )と基板バイアス電圧( $V_{BP}, V_{BN}$ )を高い電源電圧 $V_{CC1}$ (例えば3.3V)から発生し、出力するようにされる。 $p$ チャネルトランジスタ(PMOSFET) $Q_{PP}$ および $n$ チャネルトランジスタ(NMOSFET) $Q_{PN}$ は高しきい値電圧 $V_T$ を有するトランジスタである。

20

## 【0033】

図6に図5の回路の動作を示す。基板バイアス電圧 $V_{BP}, V_{BN}$ は一般には基板電圧発生・制御回路VBによって最初に投入された3.3Vをもとに作られるが、基板バイアス電圧 $V_{BP}$ として直接 $V_{CC1}$ (3.3V)で代用する例で説明する。まず、この基板バイアス電圧 $V_{BP}$ を回路ブロックCT2に与え、その後で低い電源電圧 $V_{CC2}$ を与える。したがって、低い電源電圧 $V_{CC2}$ を投入する過程では、回路ブロックCT2内のトランジスタのしきい値電圧 $V_T$ は例えば、0.5Vと十分大きく、pn接合は順方向にバイアスされることはないので、各トランジスタからのサブスレッショルド電流が累積されて過大なチップ電流になることはないし、ラッチャップを起こすこともない。通常動作に移行する際には、制御信号 $p$ および $/p$ をそれぞれ高い電圧('H')、低い電圧('L')レベルにしトランジスタ $Q_{PP}$ および $Q_{PN}$ をオフさせ、その後、制御信号 $p$ および $/p$ をそれぞれ'L', 'H'レベルにする。かくてキャパシタ( $C_P, C_N$ )結合で基板(NW, PW)電圧は変化し、それぞれ例えば2.3Vおよび-0.5V程度になる。基板の電圧が浅くなるので、回路ブロックCT2内のトランジスタのしきい値電圧 $V_T$ が小さくなる。したがって、高速動作が可能となる。次にこの状態からスタンバイ、スリープあるいはチップの非選択モードに移行するには、制御信号 $p$ および $/p$ を'L'および'H'にしてトランジスタ $Q_{PP}$ および $Q_{PN}$ をオンさせ、その後、制御信号 $p$ および $/p$ をそれぞれ'H', 'L'レベルに戻す。基板に深い電圧がかかるために回路ブロックCT2内のトランジスタのしきい値電圧 $V_T$ が例えば、0.5Vと大きくなる。したがって、サブスレッショルド電流による消費電力増加をなくすことができる。

30

## 【0034】

40

このように動作モードに応じて基板電圧を変える動作は、コンデンサ( $C_P, C_N$ )による容量結合で行われるので瞬時に行える利点がある。しかし、ソースやドレインのpn接合リーケ電流あるいはMOSFETの基板電流によって基板電圧は徐々に浅くなる。特にこの基板電流は、動作周波数に比例して大きくなる。図6の基板(ウェル)リフレッシュはこれを2.3Vと-0.5Vに復帰させるための動作である。特に限定しないが、基板電圧をモニタしたり、あ

50

るいはタイマによって決められた時間でこのリフレッシュ動作を行う。このリフレッシュ動作は、通常動作状態にある回路を、一度スタンバイ状態にして再度通常動作状態に戻すという動作である。尚、チップを高速動作させる場合のリフレッシュ間隔を、低速動作させる場合のそれよりも短くするといったように、基板電流の大きさに応じてリフレッシュ間隔を可変にすることも動作の信頼性を向上させるのに有効である。

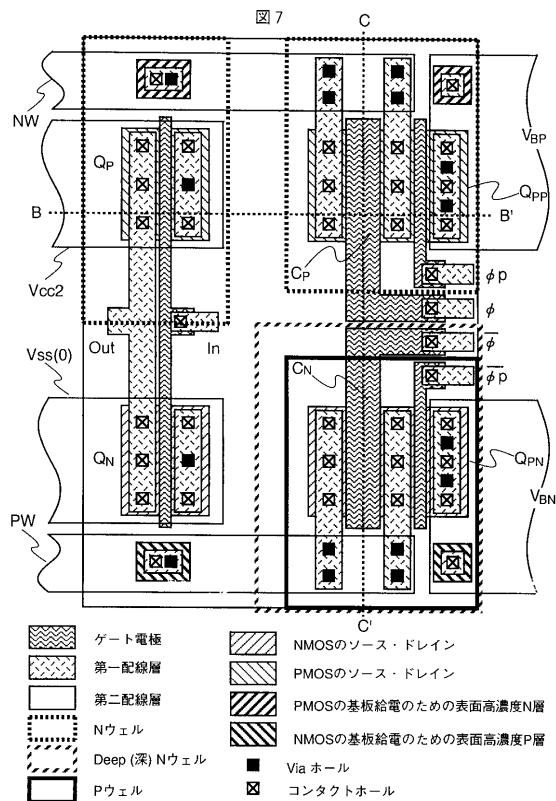

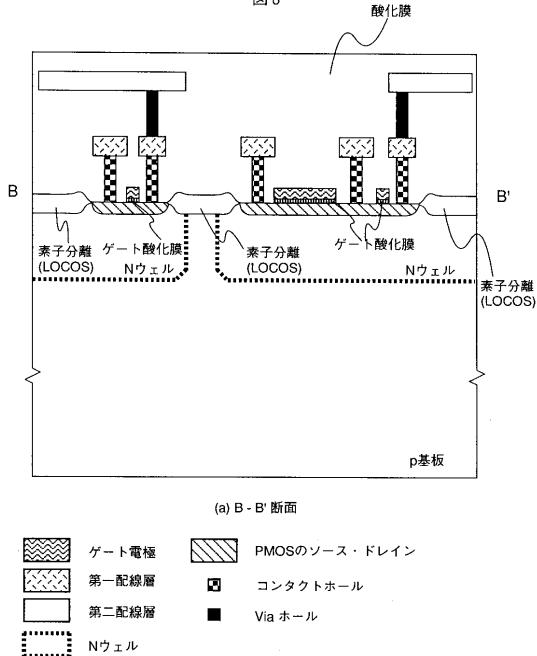

#### 【0035】

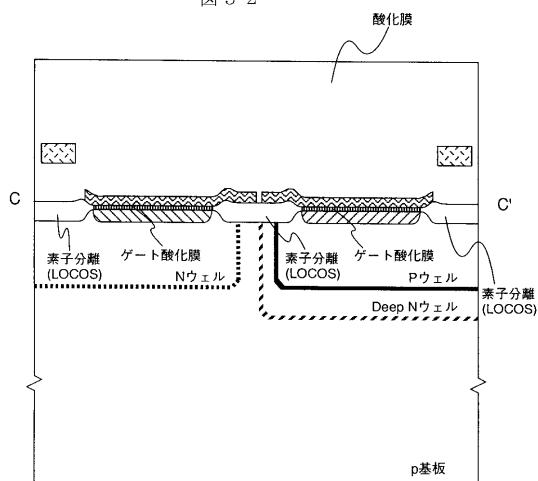

図7は図5のトランジスタ( $Q_{PP}$ ,  $Q_{PN}$ )及びキャパシタ( $C_P$ ,  $C_N$ )のレイアウト例である。図8は図7のレイアウトの断面図(B---B'断面)である。図32は図7のレイアウトの断面図(C---C'断面)である。基板バイアス電圧 $V_{BP}$ ,  $V_{BN}$ は第二配線層(第二金属配線層)でトランジスタ $Q_{PP}$ 及び $Q_{PN}$ のソースに接続される。トランジスタ $Q_{PP}$ 及び $Q_{PN}$ のドレインは第二配線層に接続され、主要回路に給電する基板電圧NWおよびPWを出力する。また、キャパシタ $C_P$ ,  $C_N$ はMOS容量によって形成されている。

10

#### 【0036】

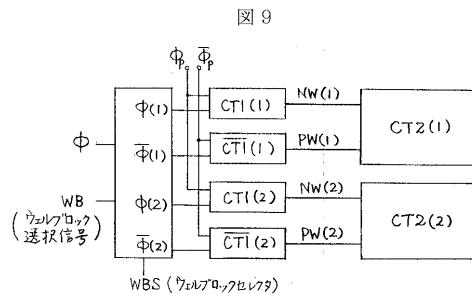

図9は図5の応用例で、2個のサブ回路ブロックCT2(1), CT2(2)のいずれか一方を選択駆動する例である。ウエルブロック選択信号WBと起動クロックによって選択サブ回路、例えば、サブ回路ブロックCT2(1)に属する基板電圧発生回路CT1(1), /CT1(1)のみが選択駆動され、それに属するウエルNW(1), PW(1)の電圧はCT2(1)内のMOSFETのしきい値電圧 $V_T$ を低下させるように駆動される。一方非選択サブ回路ブロックCT2(2)のウエルは駆動されないのでサブ回路ブロックCT2(2)内のMOSFETのしきい値電圧 $V_T$ は大きな値のままである。このように分割選択駆動しないと、サブ回路ブロックCT2(1)とサブ回路ブロックCT2(2)の全体のウエルを駆動する必要があるし、通常動作中に低しきい値電圧 $V_T$ によって流れるサブスレッショルド電流はサブ回路ブロックCT2(1)とサブ回路ブロックCT2(2)内のすべてのMOSFETから流れる。したがって、本実施例ではパルス駆動に伴う電力もサブスレッショルド電流も半減することになる。

20

#### 【0037】

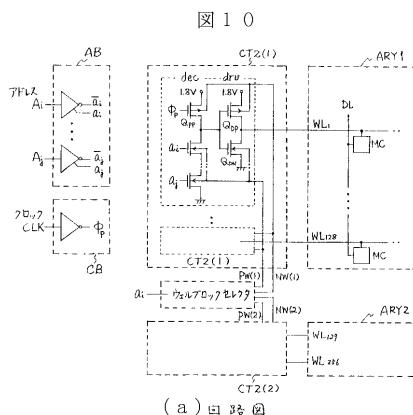

図10は、図9の例をメモリ(DRAM, SRAM)の行デコーダとドライバに適用した例である。通常メモリアレーは多数のサブアレーに分割され、サブアレー対応に行デコーダとワード線駆動回路(ワードドライバ)が配置されている。しかし、実際に選択・駆動されるサブアレーは少数であることに着目すると、選択されるサブアレーに属する行デコーダとワードドライバ内のMOSFETのウエルはしきい値電圧 $V_T$ が小さくなるように駆動し、他の大部分の非選択サブアレーのそれは駆動せずにしきい値電圧 $V_T$ が大きなままに保持しておけば、全体としては消費電力もサブスレッショルド電流も激減する。

30

#### 【0038】

図10では2個のサブアレーARY1, ARY2の例を概念的に示した。サブアレーARY1, ARY2はそれぞれ128本のワード線(WL)と複数のデータ線DL(図中では簡単のため1本のみ示した)から成り、その交点にメモリセルMCが接続されている。それぞれのワード線(WL)にはCMOSインバータ( $Q_{DP}$ ,  $Q_{DN}$ )から成るワードドライバdrvとワード線を選択する行デコーダdecが接続されている。デコーダdecはNMOSFETが直列接続されたNAND論理で、それぞれのゲートには内部アドレス信号 $ai, \dots, aj$ などが入力されている。

#### 【0039】

40

外部クロックCLKが'H'(3.3V)の状態ではプリチャージされている。その後クロックCLKが'L'(0V)になるとPMOSFET  $Q_{PP}$ はオフとなり、内部アドレス信号は外部アドレス $ai, \dots, aj$ の論理状態に応じて0Vから1.8Vあるいは0Vとなる。例えば、ワード線 $WL_1$ を選択するアドレス信号の場合には、ワード線 $WL_1$ に接続されたデコーダdecのNMOSFETのすべてがオンとなり、ワードドライバdrvの入力は0Vに放電しPMOSFET  $Q_{DP}$ はオンする。この結果ワード線 $WL_1$ には1.8Vのパルス電圧が出力される。ここで選択されたワード線 $WL_1$ を含む回路ブロックCT2(1)内のウエルNW(1), PW(1)をしきい値電圧 $V_T$ を小さくするように駆動しておけば、デコーダdecからワード線 $WL_1$ にパルスが出力するまでの時間は高速化できる。また非選択回路ブロックCT2(2)内のウエルは駆動されることはないので、パルス駆動に伴う電力の増加やサブスレッショルド電流の増加はない。ウエルブロックセレクタは、内部アドレス

50

信号によっていずれの回路ブロックのウエルを駆動するかを選択する。

【0040】

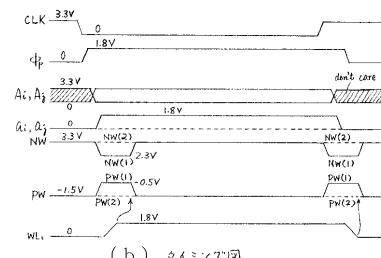

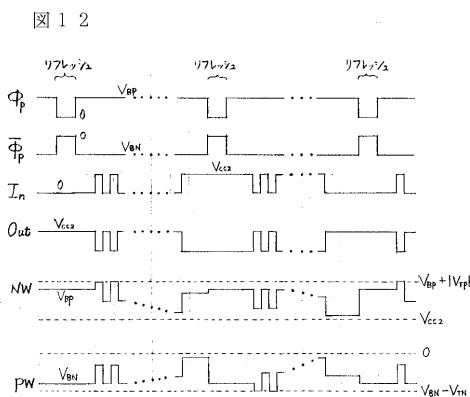

図11は図5の回路ブロックCT2を一個のインバータにし、さらに制御信号  $\rho$  および  $\rho'$  を入力信号  $I_N$  から生成した場合の実施例である。入力信号  $I_N$  が 'L' から 'H' に変化すると、基板 (NW, PW) の電圧はそれぞれキャパシタ ( $C_P, C_N$ ) によるカップリングで高くなる。したがって、PMOSFETのしきい値電圧  $V_T$  は大きくなるのでサブスレッショルド電流が小さくなる。また、NMOSFETのしきい値電圧  $V_T$  が低くなるのでインバータの負荷駆動力が増加する。逆に、入力信号  $I_N$  が 'H' から 'L' に変化すると、基板電圧は逆に低くなる。したがって、今度はPMOSFETのしきい値電圧  $V_T$  は低くなり、負荷駆動力が増加し、また、NMOSFETのしきい値電圧  $V_T$  が高くなるのでサブスレッショルド電流が小さくなる。このように入力信号によって自動的にMOSFETのしきい値電圧  $V_T$  が変化し、サブスレッショルド電流を抑えながら、インバータの負荷駆動力を増加させることができる。制御信号  $\rho$  および  $\rho'$  は電源投入時などあるいは前述したリフレッシュに用いる。基板は図5と同様、基板 (ウェル) リフレッシュが必要である。以上の動作の詳しいタイミングチャートを図12に示す。 $V_{TP}$  ならびに  $V_{TN}$  はそれぞれPMOSFETとNMOSFETのしきい値電圧  $V_T$  で、ここでは区別して表現している。ウェル (NW, PW) の最高電圧と最低電圧は、トランジスタ  $Q_{PP}$  と  $Q_{PN}$  がダイオードとして働くために、それぞれ  $V_{BP} + V_{TP}$ ,  $V_{BN} - V_{TN}$  にクランプされる。

10

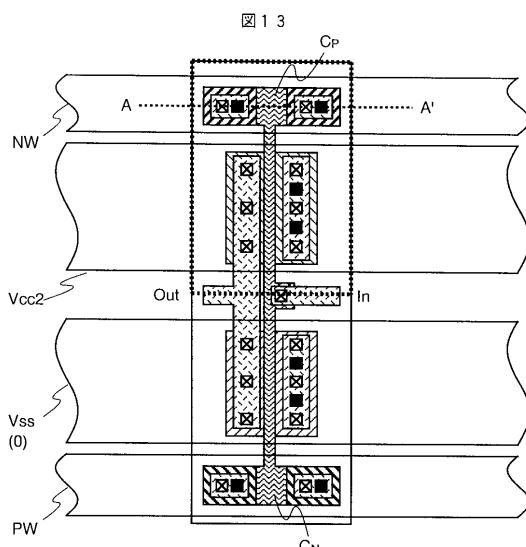

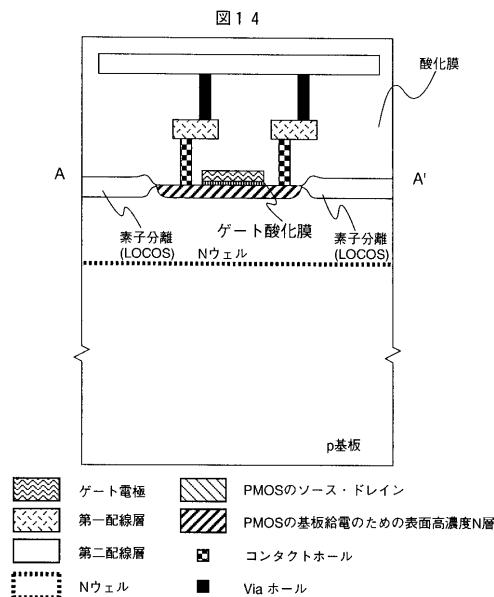

【0041】

図13は図11の回路のレイアウト例である。図14は図11のレイアウトの断面図である。トランジスタ  $Q_{PP}$ ,  $Q_{PN}$  はウェルを分離して形成する必要があり、またキャパシタ  $C_P$ ,  $C_N$  は、基板を給電している表面高濃度層までゲート電極を延長することで実現している。

20

【0042】

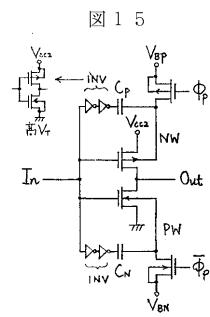

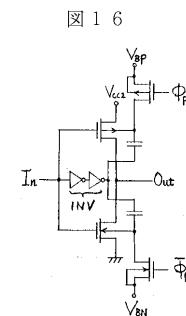

図15は図11の回路と同様の機能を持つ他の実施例である。キャパシタ  $C_P, C_N$  はインバータ列 INV を介して接続されている。このインバータ列 INV は、それらの消費電力を小さくするために高いしきい値電圧  $V_T$  のMOSFETで構成されていてもよいし、あるいは低いしきい値電圧  $V_T$  のMOSFETであるが、ゲート幅  $W$  / ゲート長  $L$  の小さなMOSFETで構成されていてもよい。図11ではインバータの入力容量はキャパシタ  $C_P, C_N$  によって大きくなるが、本実施例ではインバータがバッファになるのでそれを抑えることができる。図16は2個のインバータ列 INV を一つにまとめた実施例で、入力容量と面積をさらに小さくすることができる。

30

【0043】

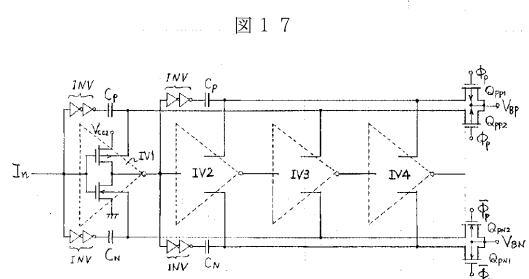

図17は図15の発明を複数のインバータ列に適用した実施例、すなわち、インバータ IV1, IV2, IV3, IV4 が直列に接続された回路の例である。トランジスタ  $Q_{PP}$ ,  $Q_{PN}$  とキャパシタ  $C_P, C_N$  を複数のインバータで共用しているので実効的に小面積になる。すなわち、導通させるMOSFETのしきい値電圧  $V_T$  を小さくし、非導通にさせるMOSFETのしきい値電圧  $V_T$  は大きくするため、基板 (ウェル) は1個毎に結線した2種のウェル配線が必要になるが、トランジスタ  $Q_{PP1}$ ,  $Q_{PN1}$  ならびにインバータ列 INV とキャパシタ  $C_P$  はインバータ IV2 と IV4 で、またトランジスタ  $Q_{PP2}$ ,  $Q_{PN2}$  ならびにインバータ列 INV とキャパシタ  $C_N$  はインバータ IV1 と IV3 で共用している。このような共用は図11及び図16の実施例にも適用できることは言うまでない。

30

【0044】

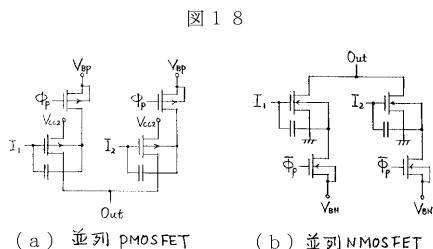

図18は図11の発明をNOR論理回路に応用した例である。図中 (a)、(b) はそれぞれPMOSFET、NMOSFETで構成している。(a)では入力 ( $I_1, I_2$ ) の少なくとも一方が 'L' になるとそれまで 'L' であった出力  $0_{out}$  には 'H' が出力される。(b)では入力の少なくとも一方が 'H' になるとそれまで 'H' であった出力  $0_{out}$  には 'L' が出力される。

40

【0045】

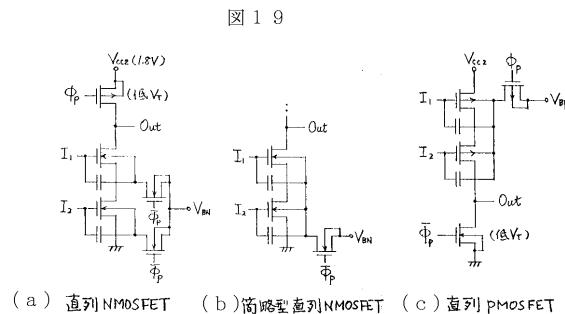

図19は図11の発明をNAND論理回路へ応用した例である。出力  $0_{out}$  は最初プリチャージ信号  $\rho$  と低しきい値電圧  $V_T$  のPMOSFETで1.8Vにプリチャージされ、入力 ( $I_1, I_2$ ) はすべて 'L' (0V) である。その後入力のすべてが 'H' (1.8V) になると直列接続されたNMOSFETはすべて導通し、フローティング 'H' であった出力は0Vに放電する。この回路は図10の行デコーダにも応用できる。(b)はウェルのプリチャージMOSFETを共有し面積を減らした

50

例である。ウエルの容量が(a)に比べて2倍になっても入力I<sub>1</sub>と入力I<sub>2</sub>に接続された2個のキャパシタでウエルを駆動する。したがって、ウエル電位の変化は(a)と同じとなって出力Outを高速に放電することができる。(c)はPMOSFETで構成したものである。入力I<sub>1</sub>, I<sub>2</sub>が同時に'L'になると、それまで0Vにプリチャージされていた出力Outは'H'に充電される。

#### 【0046】

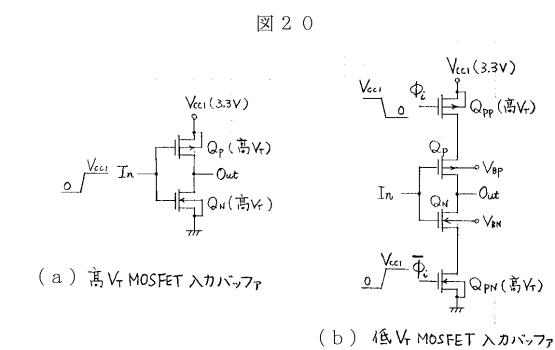

次に図3のインターフェース回路I/Oへの応用について述べる。図20はチップ外からの入力(In)バッファである。(a)は高い電流電圧3.3Vと高いきい値電圧V<sub>T</sub>のMOSFETを用いたよく知られた回路である。(b)はトランジスタQ<sub>P</sub>とQ<sub>N</sub>に小さなしきい値電圧V<sub>T</sub>のMOSFETを用いた例である。トランジスタQ<sub>PP</sub>とQ<sub>PN</sub>は大きなしきい値電圧V<sub>T</sub>でスイッチの役目をする。10入力バッファが不必要的時間帯はトランジスタQ<sub>PP</sub>, Q<sub>PN</sub>をオフにして、電源電圧V<sub>CC1</sub>とアース間に流れるトランジスタQ<sub>P</sub>とQ<sub>N</sub>のサブスレッショルド電流を阻止する。有効な信号が入力される時間帯ではトランジスタQ<sub>PP</sub>, Q<sub>PN</sub>をオンにする。

#### 【0047】

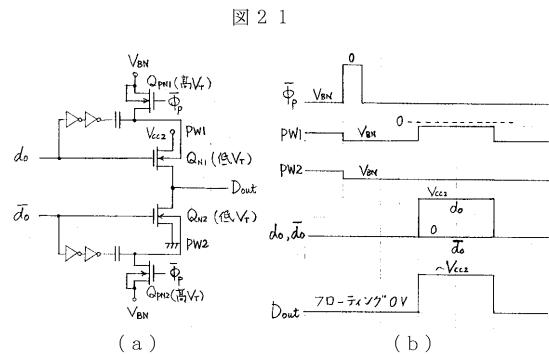

図21は、インターフェース回路I/Oのデータ出力段に図11の発明を適用したものである。汎用のダイナミックメモリ(DRAM)チップなどに多用されているように、CMOSラッチアップ等のノイズ耐性を向上するために、インターフェース回路I/O内のデータ出力段を同極性例えば、NMOSFETで構成し低電源電圧V<sub>CC2</sub>で駆動した例である。出力(Dout)部は、同じ様な出力バッファ回路が複数個共通に接続されたWired OR(ワイアド・オア)回路になっている。Wired OR接続では、ある1個の出力回路が選択されて共通結線された出力Dout部にデータが出力されている期間中は、他の出力バッファ回路は完全にオフである必要がある。またすべての出力バッファ回路が非選択の場合には共通出力(Dout)部は完全にオフでなければならない。低電圧・低しきい値電圧V<sub>T</sub>動作のもとでこれを実現するには上述した発明が有効である。図ではトランジスタQ<sub>N1</sub>およびQ<sub>N2</sub>は低しきい値電圧V<sub>T</sub>の出力段NMOSFETで、それらの基板(ウェル)電圧を与えるトランジスタQ<sub>PN1</sub>およびQ<sub>PN2</sub>は高しきい値電圧V<sub>T</sub>のPMOSFETである。この回路の特長は、対となるデータ出力信号do, /doの情報に応じて出力段MOSFET(Q<sub>N1</sub>, Q<sub>N2</sub>)のしきい値電圧V<sub>T</sub>を変えることにある。まず、トランジスタQ<sub>PN1</sub>, Q<sub>PN2</sub>をオンすることで基板PW1およびPW2を基板バイアス電圧V<sub>BN</sub>の電位にプリチャージする。この電位ではトランジスタQ<sub>N1</sub>, Q<sub>N2</sub> Q<sub>N</sub>間に流れるサブスレッショルド電流は無視できる値になるように設定しておく。その後、出力信号do, /doが情報に応じて'H'と'L', あるいは'L'と'H'の組み合わせになることで出力Doutにデータが出力される。その際、導通する方のNMOSFETの基板電圧はキャパシタによるカップリングでそのしきい値電圧V<sub>T</sub>が低くなるので負荷駆動能力が向上し高速になる。駆動されない他方のNMOSFETのしきい値電圧V<sub>T</sub>は高いままなのでサブスレッショルド電流は無視できる。

#### 【0048】

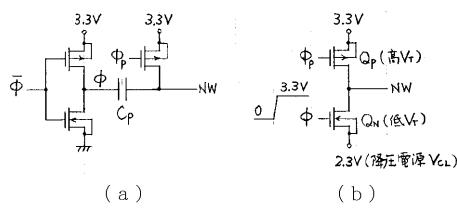

図22はウエル(NW)駆動回路の具体例である。(a)は図5の制御信号をCMOSインバータから発生させる例である。ウエルの寄生容量とキャパシタC<sub>P</sub>の比を調整することによって、例えば、図6のウエルNWの電圧2.3Vを発生させることができる。(b)はキャパシタC<sub>P</sub>を使わずに、直接2.3V電源電圧をウエルNWに印加する回路である。制御信号は0Vから3.3Vの電圧範囲をとり、トランジスタQ<sub>N</sub>のソース電圧は2.3Vである。したがって、制御信号が0VでトランジスタQ<sub>N</sub>は低しきい値電圧V<sub>T</sub>でもトランジスタQ<sub>N</sub>は十分にカットオフできる。また、制御信号3.3Vになると低しきい値電圧V<sub>T</sub>なので高速にウエルNWを駆動できる。ここで2.3Vは、外部電圧3.3Vをチップ内部で降圧させて作ることができること。

#### 【0049】

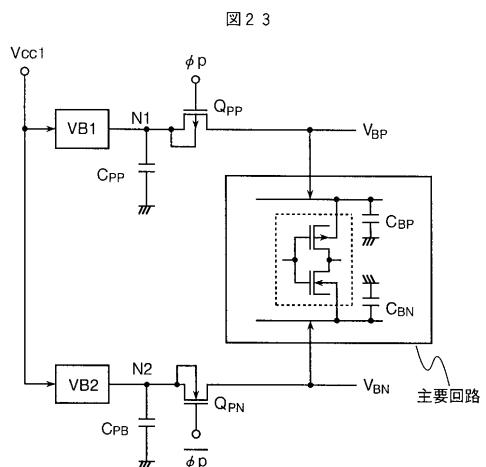

図23は本発明の他の実施例である。VB1, VB2は電源電圧V<sub>CC1</sub>からチップ内部で基板(ウェル)電圧を発生させる回路(後述)である。大きなしきい値電圧V<sub>T</sub>であるMOSFET(Q<sub>PP</sub>, Q<sub>PN</sub>)は、発生させた基板電圧を主要回路のMOSFETの基板に給電するときにオンするスイッチの役目をする。例えば、前述したようにスタンバイ時等である。キャパシタC<sub>BP</sub>, C<sub>BN</sub>は主要回路のMOSFETの基板容量である。キャパシタC<sub>PP</sub>, C<sub>PB</sub>は、キャパシタC<sub>BP</sub>およびC<sub>BN</sub>よりも十分大きな値に選ばれるようにされるので、上記スイッチがオンしても基板電圧の変動

10

20

30

40

50

は小さい。これらのキャパシタは他の回路と同一チップ上に形成してもよいし、チップ外で例えばタンタルコンデンサや電解コンデンサで形成してもよい。チップ外で形成する場合には図中のノードN1,N2がパッケージ端子となり、そこにキャパシタが外付けされるので端子数が増加する。しかし容易に大きな容量を得ることができる。このためキャパシタ $C_{PP}$ , $C_{PB}$ に予め蓄えられた大量の電荷のほんの一部をキャパシタ $C_{PB}$ , $C_{BN}$ に移すだけでよいので、高速にスタンバイ状態に必要な基板電圧に設定できる。基板電圧発生回路VB1およびVB2の電源容量は一般に小さいので、それらを通してキャパシタ $C_{PB}$ および $C_{BN}$ を充電するといった問題点はない。もちろん、基板電圧発生回路VB1,VB2は使わずに、ノードN1,N2にチップ外部からパッケージ端子を介して直接に所要基板電圧を印加することもできる。

10

#### 【0050】

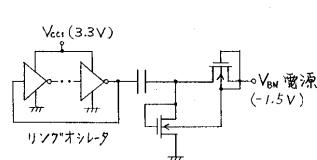

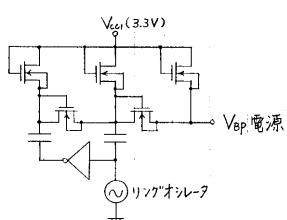

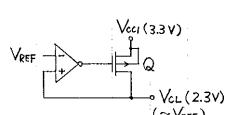

図24～図26は、これまで使用を前提としてきた基板バイアス電圧 $V_{BN}$ 、基板バイアス電圧 $V_{BP}$ 、降圧電圧 $V_{CL}$ を発生する電源回路の概念図である。詳細は単行本「超LSIメモリ」(伊藤清男著、培風館、1994年11月5日発行、239～328頁)に記載されている。図24は3.3V電源をもとに負電圧(例えば、-1.5V)電源を作る例である。リングオシレータとダイオード接続のMOSFETから成る。図25は3.3V電源をもとに3.3V以上の昇圧電源を作る例である。チップ内のリングオシレータと昇圧キャパシタを用いる。尚、これまで $V_{BP}=3.3V$ を仮定した説明が多かったが、この場合にはこのような昇圧電源はもちろん不要である。しかし基板バイアス電圧 $V_{BP}$ などの値はMOSFETの特性で決められるので、一般にはこのような $V_{CC1}$ (3.3V)以上の昇圧電源が必要である。図26は3.3V電源を用いて降圧電圧 $V_{CL}$ (2.3V)を得る例である。降圧電圧 $V_{CL}$ の値はチップ内で発生させた参照電圧 $V_{REF}$ とコンパレータで決めることができる。

20

#### 【0051】

以上、図3の内部回路への適用例を中心に述べてきたが、本発明の適用はこれに限定されることはない。図27は図3に示した実施例をより簡単に図示したもので、これをもとに他の実施例を述べる。インターフェース回路I/Oはチップ外部とのインターフェースを行い、主に高しきい値電圧 $V_T$ のMOSFETで構成されており、高い電源電圧 $V_{CC1}$ が印加されている。基板電圧発生回路VBには、高い電源電圧 $V_{CC1}$ (> $V_{CC2}$ )が印加され、基板バイアス電圧 $V_{BP}$ および $V_{BN}$ を発生するようにされる。主要回路は低しきい値電圧 $V_T$ のMOSFETで構成され、低い電源電圧( $V_{CC2}$ )が印加されている。当然ながら前述したように、I/Oは全てが高い $V_T$ のMOSFETで構成されていなくてもよいし、主要回路の全てが低しきい値電圧 $V_T$ のMOSFETで構成されている必要はない。また、基板電圧発生回路VBの出力であるPMOSFETの基板バイアス電圧 $V_{BP}$ は、主要回路内のPMOSFETのしきい値電圧 $V_T$ を十分高い値(実際にはPMOSFETなのでしきい値電圧 $V_T$ は絶対値)にできれば電源電圧 $V_{CC1}$ を直接基板バイアス電圧 $V_{BP}$ とみなして使うこともできる。

30

#### 【0052】

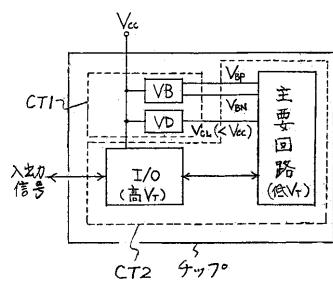

図28は図2で説明した本発明の電源投入に関する発明を单一電源のチップに適用した例である。基板バイアスモニタ回路DTは、電源投入時に基板電位が十分安定に供給できたことを検出する回路である。その検出出力によって高しきい値電圧 $V_T$ のPMOSFETをオンさせ、インターフェース回路I/Oと主要回路に電源電圧 $V_{CC}$ を供給している。

40

#### 【0053】

図29は降圧電源回路VDを用いた実施例である。高い電源電圧 $V_{CC}$ から低い電源電圧 $V_{CL}$ を降圧電源回路VDによって生成し、主要回路に給電している。この場合、单一電源で、主要回路を構成するデバイスの最適動作電圧になるように降圧電圧 $V_{CL}$ 、基板バイアス電圧 $V_{BP}$ , $V_{BN}$ を内部で調整できる利点がある。もちろんこの場合にも基板バイアス電圧 $V_{BP}$ と $V_{BN}$ が印加されてから降圧電圧 $V_{CL}$ を印加する。

#### 【0054】

図30は外部電源が2種( $V_{CC1}$ , $V_{CC2}$ )の場合にでもユーザに電源投入順序に対する制約を与えない方式例である。低しきい値電圧 $V_T$ を多用する主要回路には図28の発明を適用し低電圧( $V_{CC2}$ )電源で動作させる。一方、高しきい値電圧 $V_T$ のMOSFETを多用するインターフェ

50

ース回路I/Oは他の電源電圧（例えば、 $V_{CC1}$ ）で動作させ。インターフェース回路I/Oと主要回路間には動作電圧の差があるので小規模な電圧レベル変換回路が必要であるが、電源電圧 $V_{CC1}$ で動作する回路ブロックと電源電圧 $V_{CC2}$ で動作する回路ブロックはほぼ独立に動作し、低しきい値電圧 $V_T$ の主要回路のラッチアップも防げるから、ユーザにとって使い易いチップが実現できる。

#### 【0055】

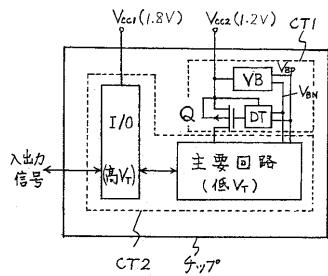

図31はこの場合の内部回路の動作を示している。図5に対応した回路である。本例ではインターフェース回路I/Oは1.8Vの高電圧電源で動作し、主要回路は1.2Vの低電圧電源で動作するものとしている。電源電圧 $V_{CC2}$ で動作する昇圧回路によって昇圧( $V_{BP}=2.7V$ )電源を作り、制御信号 $\phi_P$ は0Vから基板バイアス電圧 $V_{BP}$ までのパルス振幅をとる。また、制御信号 $\phi_N$ は、例えば、0Vから基板バイアス電圧 $V_{BP}$ までのパルス振幅をとる。負電圧電源回路によって $V_{BN}(-1.5V)$ がつくられ、制御信号 $\phi_N$ は0Vから基板バイアス電圧 $V_{BP}$ までのパルス振幅をとる。したがって、電源電圧 $V_{CC2}$ が電源投入時にトランジスタ $Q_{PP}$ と $Q_{PN}$ がオンとなって低しきい値電圧 $V_T$ のトランジスタ $Q_P$ 、 $Q_N$ に十分なウエル電圧が与えられてから、図30のトランジスタ $Q$ がオンになって図31の低しきい値電圧 $V_T$ の主要回路に電源電圧 $V_{CC2}$ ( $V_{CC2}$ 印加よりも遅れて印加されるので $V_{CC2}$ と区別してある)が印加される。

#### 【0056】

以上の実施例では、トランジスタの構造およびその基板構造は特に限定しない。SOI(Silicon(Semiconductor) on Insulator)構造のようなMOSFETを用いてもよい。要は基板電圧によってしきい値電圧 $V_T$ が制御できるような構造のトランジスタであればよい。また大きな電源電圧（例えば、 $V_{CC1}$ ）が印加されるMOSFETのゲート酸化膜を、小さな電源電圧（例えば、 $V_{CC2}$ ）が印加されるMOSFETのそれよりも厚くすれば、チップ全体として高信頼性が保証されることは言うまでもない。また図3ではあらゆる機能ブロックをチップ内に集積した例を示したが、それぞれ独立したチップ、例えば、ダイナミックメモリ(DRAM)チップ、スタティックメモリ(SRAM)チップあるいはマイクロプロセッサチップにでも本発明を適用できる。

#### 【0057】

##### 【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

#### 【0058】

すなわち、高速・低消費電力で動作の安定なCMOS回路、及びそれで構成されたCMOS LSIチップならびに半導体装置が実現できる。

##### 【図面の簡単な説明】

【図1】本発明によるCMOS半導体装置を示す。

【図2】本発明によるCMOS半導体装置の動作タイミングを示す。

【図3】本発明によるCMOS LSIチップを示す。

【図4】本発明によるCMOS LSIチップの断面の概略を示す。

【図5】本発明によるCMOS回路を示す。

【図6】本発明によるCMOS回路の動作タイミングを示す。

【図7】図5の回路のレイアウトを示す。

【図8】図5の回路のレイアウトの断面の概略を示す。

【図9】本発明による回路サブブロックの選択・駆動法を示す。

【図10】本発明による行選択回路とその動作タイミングを示す。

【図11】本発明によるCMOSインバータを示す。

【図12】本発明によるCMOSインバータの動作タイミングを示す。

【図13】図11の回路のレイアウトならびにその断面を示す。

【図14】図11の回路のレイアウトの断面を示す。

【図15】図11の回路の変形例を示す。

【図16】図11の回路の変形例を示す。

10

20

30

40

50

【図17】本発明をインバータ列に適用した例を示す。

【図18】本発明によるNOR論理回路を示す。

【図19】本発明によるNAND論理回路を示す。

【図20】入力バッファ回路の例を示す。

【図21】本発明によるデータ出力回路を示す。

【図22】本発明によるウエル駆動回路を示す。

【図23】本発明によるウエル電圧の印加方式を示す。

【図24】負電圧電源回路の従来例を示す。

【図25】昇圧電源回路の従来例を示す。

【図26】降圧電源回路の従来例を示す。

【図27】本発明による2電源チップの構成を示す。

【図28】本発明による単一電源チップを示す。

【図29】本発明による単一電源チップを示す。

【図30】本発明による2電源チップの構成を示す。

【図31】本発明による2電源チップの内部回路を示す。

【図32】図5の回路のレイアウトの別の断面の概略を示す。

【符号の説明】

, / ,  $\phi_p$ , /  $\phi_n$ ...ウエル電圧制御信号、NW...PMOSFETのウエル、

PW...NMOSFETのウエル、 $V_{Bp}$ ...PMOSFETのウエル用電源電圧、

$V_{BN}$ ...NMOSFETのウエル用電源電圧。

10

20

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

電源投入 通常動作 スタートパワースリープ 通常動作 基板(ウエル)リフレッシュ

通常動作 通常動作 通常動作 通常動作

【図7】

図7

【図8】

図8

|               |               |

|---------------|---------------|

| ゲート電極         | PMOSのソース・ドレイン |

| 第一配線層         | コンタクトホール      |

| 第二配線層         | Viaホール        |

| Nウェル          | コンタクトホール      |

| Deep (深) Nウェル |               |

| Pウェル          |               |

【図9】

【図10】

(a) 例 3 ②

(b) タイミング

【図11】

【図12】

【図13】

|            |                      |

|------------|----------------------|

| ゲート電極      | NMOSのソース・ドレイン        |

| 第一配線層      | PMOSのソース・ドレイン        |

| 第二配線層      | PMOSの基板給電のための表面高濃度N層 |

| Nウェル       | NMOSの基板給電のための表面高濃度P層 |

| □ コンタクトホール | ▀ Viaホール             |

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

【図23】

【図22】

図22

【図24】

【図25】

図25

【図26】

図26

【図27】

図27

【図28】

図28

【図29】

図29

【図30】

図30

【図31】

図31

【図32】

図32

(b) C - C' 断面

|  |       |  |               |

|--|-------|--|---------------|

|  | ゲート電極 |  | PMOSのソース・ドレイン |

|  | 第一配線層 |  | NMOSのソース・ドレイン |

|  | Nウェル  |  | Deep Nウェル     |

|  | Pウェル  |  |               |

---

フロントページの続き

(51)Int.Cl. F I

**H 0 1 L 21/8238 (2006.01)**

(72)発明者 水野 弘之

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

審査官 宮島 郁美

(56)参考文献 特開昭59-153331 (JP, A)

特開平07-254685 (JP, A)

特開平08-083487 (JP, A)

特開平08-017183 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H03K 19/00-19/00 103, 19/01-19/082,

19/092-19/096

H03K 17/00-17/70

H01L 27/06-27/08

G11C 11/34