(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-276931

(P2005-276931A)

(43) 公開日 平成17年10月6日(2005.10.6)

(51) Int.Cl.<sup>7</sup>

**H01L 21/76**

**H01L 21/3065**

**H01L 21/8247**

**H01L 27/115**

**H01L 29/788**

F 1

H01L 21/76

H01L 27/10 434

H01L 29/78 371

H01L 21/302 105A

テーマコード(参考)

5FO04

5FO32

5FO83

5FO1

審査請求 未請求 請求項の数 5 O L (全 9 頁) 最終頁に続く

(21) 出願番号

(22) 出願日

特願2004-85052 (P2004-85052)

平成16年3月23日 (2004.3.23)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100071135

弁理士 佐藤 強

(74) 代理人 100119769

弁理士 小川 清

(72) 発明者 伊藤 克也

三重県四日市市山之一色町800番地 株式会社東芝四日市工場内

(72) 発明者 角田 弘昭

三重県四日市市山之一色町800番地 株式会社東芝四日市工場内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】異なる開口幅の狭いトレンチを浅く、開口幅の広いトレンチを深く形成して絶縁膜の埋め込み性を高めると共に絶縁距離を確保できる構造を得る。

【解決手段】シリコン基板1に開口幅の狭いトレンチ3と開口幅の広いトレンチ5をRIE法により形成するエッティング加工で、エッティングガスとしてハロゲン系ガス、フロロカーボン系ガス、O<sub>2</sub>を混合したガスを用いて同時に形成する。トレンチ5の底面端部5aの深さd<sub>2</sub>は底面中央部5bの深さd<sub>1</sub>よりも深く形成され、絶縁耐圧を確保できる。また、トレンチ3の深さd<sub>1</sub>は、シリコン酸化膜8の埋め込み性を良好にする深さとすることができる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

半導体基板と、

この半導体基板上に形成され開口幅の異なる複数のトレンチとを備え、

前記複数のトレンチのうちで、開口幅の狭いトレンチは第1の深さに形成され、開口幅の広いトレンチは、底面端部が前記第1の深さよりも深い第2の深さに掘り下げられると共に、底面中央部が前記第2の深さよりも浅く形成されていることを特徴とする半導体装置。

**【請求項 2】**

メモリセル領域および周辺回路領域を有する半導体基板と、

前記メモリセル領域に形成され、第1の開口幅を有し、前記半導体基板表面から第1の深さに掘り下げられた第1の素子分離用トレンチと、

前記周辺回路領域に形成され、前記第1の開口幅より幅の広い第2の開口幅を有し、底面端部が前記第1の深さよりも深い第2の深さに掘り下げられ、底面中央部は前記第2の深さよりも浅く形成された第2の素子分離用トレンチと

を具備したことを特徴とする半導体装置。

**【請求項 3】**

半導体基板に開口幅の異なるトレンチ形成用のマスク材をパターニングする工程と、

このマスク材をマスクとしてRIE法によりハロゲン系ガス、フロロカーボン系ガス、O<sub>2</sub>からなる反応性プラズマを用いて前記半導体基板をエッチング加工して前記開口幅の異なるトレンチを同時形成する工程とを備えたことを特徴とする半導体装置の製造方法。

**【請求項 4】**

半導体基板にゲート絶縁膜、多結晶シリコン膜もしくは非晶質シリコン膜、シリコン窒化膜、シリコン酸化膜を順次積層する工程と、

前記半導体基板の上面に開口幅の異なるトレンチ形成用のレジストをパターニングする工程と、

このレジストをマスクとしてRIE法により前記半導体基板に形成したシリコン酸化膜およびシリコン窒化膜をエッチング加工する工程と、

エッチング加工されたシリコン酸化膜およびシリコン窒化膜をマスク材としてRIE法によりハロゲン系ガス、フロロカーボン系ガス、Ar、O<sub>2</sub>からなる反応性プラズマを用いて前記多結晶シリコン膜もしくは非晶質シリコン膜、ゲート絶縁膜および半導体基板をエッチング加工して前記開口幅の異なるトレンチを同時形成する工程とを備えたことを特徴とする半導体装置の製造方法。

**【請求項 5】**

請求項3または4に記載の半導体装置の製造方法において、

前記トレンチを形成する工程で前記シリコン基板のエッチングに用いるエッチングガスは、ハロゲン系ガスとしてHBr、Cl<sub>2</sub>、フロロカーボン系ガスとしてCHF<sub>3</sub>を用いることを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、開口幅の広いトレンチおよび狭いトレンチを備えた構成の半導体装置およびその製造方法に関する。

**【背景技術】****【0002】**

フラッシュメモリなどの不揮発性記憶装置においては、メモリセル領域に形成するセルトランジスタに対して、これらを駆動するために周辺部に形成される周辺回路部には、高耐圧のトランジスタを設ける関係から絶縁距離をメモリセル領域のセルトランジスタよりも長くした構成を採用する必要がある。これらの各素子は、STI(Shallow Trench Iso

10

20

30

40

50

lation)により分離形成したシリコン基板の活性領域に設けられている。

#### 【0003】

近年、設計ルールが微細化に進むにしたがって、STIの高アスペクト比化が進みつつある。そこで、高耐圧を必要としないセルトランジスタについてはできるだけ浅いトレンチによりSTIを形成することでSTI幅を狭くすると共に、高耐圧を必要とする周辺回路領域のトランジスタについてはSTI幅を広くすると共にトレンチ深さも深くすることで特性を満足するようにしている。

#### 【0004】

このため、メモリセル領域と周辺回路領域とでSTI形成用のトレンチ深さを異なるように形成する必要があり、実際のトレンチ形成工程ではエッチング処理を例えれば2回行うことによってこれを実現している。具体的には、例えば次のようにして形成している。

10

まず、シリコン基板上に第1のシリコン酸化膜、第1の多結晶シリコン膜、シリコン窒化膜、第2のシリコン酸化膜を順次堆積し、この後フォトトリソグラフィ処理によりフォトレジストを所定のパターンに加工する。このフォトレジストをマスクにしてRIE(Reactive Ion Etching)法により第2のシリコン酸化膜、シリコン窒化膜をエッチング加工し、フォトレジストを除去した後、第2のシリコン酸化膜をマスクにして多結晶シリコン膜、第1のシリコン酸化膜およびシリコン基板をエッチング加工する。このとき、シリコン基板には均一な深さのトレンチが形成される。

#### 【0005】

次に、周辺回路領域側のトレンチを深く形成するために、メモリセル領域に対応した部分にフォトトリソグラフィ処理によりフォトレジストをパターニングしこれをマスクにして周辺回路領域のトレンチを所定深さまでエッチングすることで異なる深さのトレンチを形成する。

20

上記のようにして、トレンチの深さを作り分けるので、メモリセル領域ではSTIの幅寸法をアスペクト比に応じた最小幅に狭めることができ、周辺回路領域では耐圧に応じた深さ寸法を確保したものとして得られるようになる。

#### 【0006】

このようなトレンチの底面部の高さが異なるような形成方法としては、上記以外に、例えば特許文献1に示すものがある。これは、半導体基板に開口幅が広いトレンチと狭いトレンチとを形成するもので、開口幅が広いトレンチでは、底部中央領域を高く形成するようにした半導体装置の製造方法である。

30

#### 【特許文献1】特開2000-156402号公報

##### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0007】

上記の特許文献1のものでは、トレンチを形成するためのフォトトリソグラフィ処理は1回でエッチング処理も1回で行うことができるという利点があるが、この方法では前述した形状を得ることができない。すなわち、前述した目的では、開口幅の狭いトレンチを浅く、開口幅の広いトレンチを深く形成する必要があるのに対して、特許文献1のものでは、両者の深さ寸法を同じとしながら、開口幅の広いトレンチについては底面中央領域の高さを高くするというものであるから、全く逆の条件のトレンチ形状を形成するものとなってしまうので採用することができない。

40

#### 【0008】

一方、前述した従来の製造方法では、メモリセル領域および周辺回路領域のトレンチを同時に形成することが不可能であるから、少なくとも2回のフォトトリソグラフィ処理とエッチング工程が必要であるから、このトレンチ形成における製造工程の削減が図れず、製造歩留まりの向上や製造コストの低下を図ることができないものであった。

本発明は、上記事情を考慮してなされたもので、その目的は、開口幅が狭いトレンチを浅く、開口幅が広いトレンチを実質的に深く形成されたトレンチを備えた半導体装置、およびこれらのトレンチを1回のフォトトリソグラフィ処理により形成することができる半導

50

体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0009】

本発明の半導体装置は、半導体基板と、この半導体基板上に形成され開口幅の異なる複数のトレンチとを備え、前記複数のトレンチのうちで、開口幅の狭いトレンチを第1の深さに形成し、開口幅の広いトレンチを、底面端部が前記第1の深さよりも深い第2の深さに掘り下げると共に、底面中央部が前記第2の深さよりも浅く形成したところに特徴を有する。

【0010】

また、本発明の半導体装置の製造方法は、半導体基板に開口幅の異なるトレンチ形成用のマスク材をパターニングする工程と、このマスク材をマスクとしてRIE法によりハロゲン系ガス、フロロカーボン系ガス、O<sub>2</sub>からなる反応性プラズマを用いて前記半導体基板をエッティング加工して前記開口幅の異なるトレンチを同時形成する工程とを備えたところに特徴を有する。

【発明の効果】

【0011】

本発明の半導体装置によれば、トレンチ内部に絶縁膜を埋め込んで素子分離領域を形成する場合に、開口幅の狭いトレンチでは埋め込み性が良好な第1の深さに形成されており、開口幅の広いトレンチでは底面端部で耐圧を確保するのに十分な第2の深さに形成されているので、開口幅の狭いトレンチの形成領域で集積度を高めることができる。

また、本発明の半導体装置の製造方法によれば、上記の半導体装置を形成するのに、1回のエッティング加工工程で開口幅の狭いトレンチを第1の深さに、開口幅の広いトレンチを底面端部が第1の深さよりも深い第2の深さに掘り下げると共に、底面中央部が第2の深さよりも浅く形成することができる。

【発明を実施するための最良の形態】

【0012】

以下、本発明を不揮発性半導体記憶装置であるフラッシュメモリに適用した場合の一実施形態について図1～図3を参照して説明する。

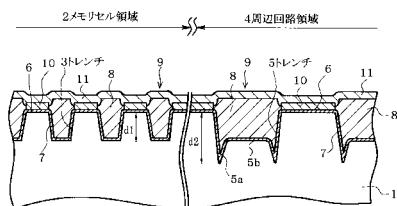

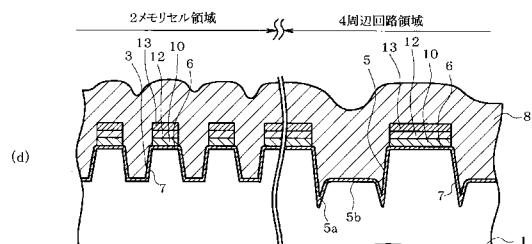

図1は全体構成を示す模式的な断面図で、フラッシュメモリに素子分離領域を形成した状態を示している。この図1において、半導体基板としてのシリコン基板1には、メモリセル領域2に開口幅が狭いトレンチ3（第1の素子分離用トレンチ）が形成され、周辺回路領域4に開口幅の広いトレンチ5（第2の素子分離用トレンチ）が形成されている。トレンチ3の深さは、シリコン基板1の表面から100nm（第1の深さd1）に形成されている。トレンチ5の深さは、底面端部5aでシリコン基板1の表面から170nm（第2の深さd2）に形成され、底面中央部5bで100nm（第1の深さd1）に形成されている。すなわち、トレンチ5の底面端部5aの深さはトレンチ3の深さより深く、底面中央部5bの深さはトレンチ5の底面端部の深さより浅く形成されている。

【0013】

シリコン基板1の平坦な部分の表面には、ゲート絶縁膜としてシリコン酸化膜6が膜厚10nm程度で形成され、各トレンチ3、5の表面にはシリコン酸化膜7が膜厚6nm程度で形成されている。トレンチ3、5の内部には絶縁膜としてシリコン酸化膜8が埋め込み形成されている。これにより、STI9が形成されている。シリコン酸化膜6の上面には多結晶シリコン膜10が積層されている。そして、多結晶シリコン膜10およびシリコン酸化膜8を全面に覆うように多結晶シリコン膜11が膜厚100nmで形成されている。

【0014】

上記構成によれば、メモリセル領域2のトレンチ3はアスペクト比が高く設定されているが、深さd1は比較的浅いのでシリコン酸化膜8を埋め込み形成するのに埋め込み性を良好な状態とすることができます。また、周辺回路部4のトレンチ5はアスペクト比が低く設定されており、底面端部5aの深さd2は底面中央部5bの深さd1よりも深く形成さ

10

20

30

40

50

れているので、シリコン酸化膜8を埋め込み形成した状態では、絶縁距離を長くすることができるようになり、形成する素子の耐圧を高くすることができる。

#### 【0015】

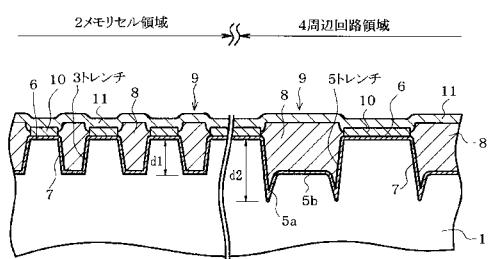

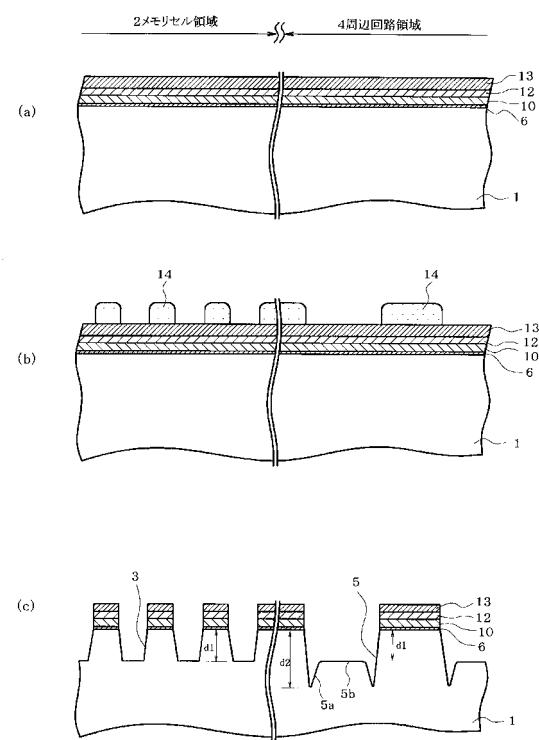

次に、上記構成の製造工程について説明する。図2および図3は、製造工程の各段階で示す模式的断面図である。まず、図2(a)において、シリコン基板1上に膜厚10nmの第1のシリコン酸化膜6、膜厚60nmの第1の多結晶シリコン膜10、シリコン窒化膜12、第2のシリコン酸化膜13を順次堆積する。

次に、図2(b)に示すように、通常のフォトリソグラフィ処理によりフォトレジスト14を所定のパターンに加工する。これは、メモリセル領域2および周辺回路領域4のそれぞれに対応して素子分離領域を形成するパターンを形成するものである。形成されたフォトレジスト14のパターンをマスク材としてRIE法により第2のシリコン酸化膜13とシリコン窒化膜12をエッティング加工する。

10

#### 【0016】

続いて、O<sub>2</sub>プラズマ中にシリコン基板1をさらして、フォトレジスト14を除去した後、第2のシリコン酸化膜13をマスク材にして多結晶シリコン膜12と第1のシリコン酸化膜6とシリコン基板1をRIE法で同一チャンバー内にて連続的にエッティング加工し、図2(c)に示すようにトレンチ3とトレンチ5を同時形成する。

トレンチ同時形成において、多結晶シリコン膜12のエッティング時のエッティングガスとしては、例えばHBr、Cl<sub>2</sub>、O<sub>2</sub>、CF<sub>4</sub>を混合したガスを用いる。引き続き、シリコン酸化膜6のエッティング時のエッティングガスとしては、Ar、CHF<sub>3</sub>を混合したガスを用いる。また、シリコン基板1をエッティングするときに用いるエッティングガスとしては、ハロゲン系ガスとしてHBr、Cl<sub>2</sub>、フロロカーボン系ガスとしてCHF<sub>3</sub>を用いるとともに、他にO<sub>2</sub>を混合したガスを用いる。

20

#### 【0017】

多結晶シリコン膜12のエッティング時のエッティングガスとしては、HBr、Cl<sub>2</sub>に代えて、HC1、NF<sub>3</sub>、SF<sub>6</sub>などを用いることができる。また、シリコン酸化膜6のエッティング時のエッティングガスとしては、CHF<sub>3</sub>に代えて、CF<sub>4</sub>、CH<sub>2</sub>F<sub>2</sub>、CH<sub>3</sub>F、C<sub>4</sub>F<sub>8</sub>、C<sub>5</sub>F<sub>8</sub>、C<sub>4</sub>F<sub>6</sub>とこれにCO、Xeを加えたガスを用いることができる。さらに、シリコン基板1をエッティングするときに用いるエッティングガスとしては、CHF<sub>3</sub>に代えて、CF<sub>4</sub>、CH<sub>2</sub>F<sub>2</sub>、CH<sub>3</sub>F、C<sub>4</sub>F<sub>8</sub>、C<sub>5</sub>F<sub>8</sub>、C<sub>4</sub>F<sub>6</sub>等を用いることができる。

30

#### 【0018】

なお、多結晶シリコン膜12のエッティングからシリコン酸化膜6のエッティングへの移行、およびシリコン酸化膜6のエッティングからシリコン基板1のエッティングへの移行は、プラズマの発光特性を自動検出し、発光特性が変化する時点で自動的に行う。なお、シリコン基板1のエッティングは時間で管理する。

このエッティング加工では、シリコン基板1中にトレンチ3、5を同時に形成しており、開口幅の広いトレンチ5においては、底面部端部5aの深さd<sub>2</sub>が底面中央部5bの深さd<sub>1</sub>よりも深くなるような形状に形成している。その後、O<sub>2</sub>雰囲気、1000で加熱し、6nmの第3のシリコン酸化膜7を形成する。

40

#### 【0019】

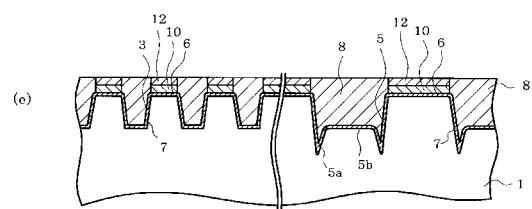

次に、図3(d)に示すように、HDP(High Density Plasma)法により第4のシリコン酸化膜8を堆積してトレンチ3、5を埋め込むように形成する。この後、図3(e)に示すように、CMP(Chemical Mechanical Polish)法により第4のシリコン酸化膜8を平坦化し、続いて900の窒素雰囲気中で熱処理をする。続いて、NH<sub>4</sub>F溶液に浸した後、150のリン酸処理によりシリコン窒化膜12を除去し、減圧CVD法によりリンが添加された第2の多結晶シリコン膜11を膜厚100nmで堆積することにより図1に示すような構成を得る。なお、フラッシュメモリの製造工程としては、この後、ゲート絶縁膜、制御ゲート電極を形成する工程、配線パターンの形成工程などを経ることでウエハ工程が終了する。

50

## 【0020】

このような加工工程を採用することで、シリコン基板1にトレンチ3、5を形成する場合に、1回のリソグラフィ処理とRIEエッティング処理により深さの異なる形状に加工することができるようになる。この場合、トレンチ3は底面がほぼフラットで深さd1に形成され、トレンチ5は、底面端部5aで深さd2（深さd1よりも深い）となり、底面中央部5bで深さd1となるように形成されている。

## 【0021】

この実施形態においては、トレンチ3の深さd1を100nm、トレンチ5の底面端部5aの深さd2を175nmとした。なお、深さd1とd2の差については、エッティングガスの混合比を調整することで制御することができるので、形成するトレンチのアスペクト比、開口幅寸法、トレンチの深さ寸法などの条件に応じてエッティング条件を適宜選択して適切な条件を選ぶことができる。10

## 【0022】

このような本実施形態によれば、メモリセル領域2のトレンチ3の深さd1に対して周辺回路領域4のトレンチ5を底面端部5aで深く（深さd2）、底面中央部5bで同程度（深さd1）に同時に加工することができるので、素子の特性を満足させる構成を1回の加工工程を実施することで形成することができる。これにより、工程数を削減して製造コストの低減を図るとともに、歩留まりの向上も図ることができるようになる。

## 【0023】

また、このようにフォトレジスト14をパターニングするための1回のフォトリソグラフィ処理を経るだけで形成することができるので、従来のようなトレンチ掘り分けのためのパターニングをする必要がなくなることで、境界領域部分に段差を生ずることがなくなり、またそのことにより、境界領域に段差を生じても素子特性に影響を与えないようなダミー領域を設ける必要がなくなるので、素子面積の縮小化も図ができるようになる。20

## 【0024】

## (他の実施形態)

本発明は、上記実施例にのみ限定されるものではなく、次のように変形または拡張できる。

上記実施形態では、トレンチ3の深さd1がトレンチ5の底面中央部5bの深さd1と同じになる場合で示したが、必ずしも一致するように形成する必要はなく、エッティング加工上の条件やばらつきの範囲内でほぼ同程度の深さになれば良いものである。30

## 【0025】

さらには、トレンチ5の底面端部5aが耐圧を確保できる深さd2に形成することができれば、底面中央部5bがトレンチ3の深さd1よりも深く形成されたり、浅く形成されることは何ら支障を来すものではない。

上記実施形態においては、多結晶シリコン膜10、11を用いる構成としているが、これに代えて、非晶質シリコン膜を用いることもできる。

## 【0026】

上記実施形態においては、マスク材を加工した後にフォトレジスト14を剥離して多結晶シリコン膜12と第1のシリコン酸化膜6とシリコン基板1をエッティング加工するプロセスとしたが、フォトレジスト14を残したまま多結晶シリコン膜12と第1のシリコン酸化膜6とシリコン基板1をエッティング加工してもよい。40

フラッシュメモリ以外にも異なる深さのトレンチを形成する構成の半導体装置に適用することができる。

## 【図面の簡単な説明】

## 【0027】

## 【図1】本発明の一実施形態を示す模式的断面図

## 【図2】製造工程の各段階で示す模式的断面図（その1）

【図3】製造工程の各段階で示す模式的断面図（その2）50

## 【符号の説明】

## 【0028】

図面中、1はシリコン基板(半導体基板)、2はメモリセル領域、3はトレンチ、4は周辺回路領域、5はトレンチ、5aは底面端部、5bは底面中央部、6はシリコン酸化膜(ゲート絶縁膜)、7、8、13はシリコン酸化膜、9はSTI、10、11は多結晶シリコン膜、12シリコン窒化膜、14はフォトレジストである。

【図1】

【図2】

【図3】

---

フロントページの続き

(51)Int.Cl.<sup>7</sup>

H 01 L 29/792

F I

テーマコード(参考)

(72)発明者 松本 孝典

三重県四日市市山之一色町800番地 株式会社東芝四日市工場内

F ターム(参考) 5F004 BA04 DA00 DA01 DA04 DA15 DA16 DA17 DA18 DA26 DB01

DB02 DB03 EA32 EB04 EB08

5F032 AA34 AA44 AA45 AA66 AA77 BA02 BA03 CA17 CA23 CA24

CA25 DA04 DA23 DA24 DA33 DA53 DA74 DA78

5F083 EP02 EP23 JA19 NA01 PR03 PR33 PR40 PR41

5F101 BA01 BB05 BD35 BH14 BH16 BH21