(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5448603号

(P5448603)

(45) 発行日 平成26年3月19日(2014.3.19)

(24) 登録日 平成26年1月10日(2014.1.10)

(51) Int.Cl.

H01L 29/786 (2006.01)

H01L 21/336 (2006.01)

F 1

H01L 29/78 618 E

H01L 29/78 618 Z

請求項の数 4 (全 77 頁)

(21) 出願番号 特願2009-152189 (P2009-152189)

(22) 出願日 平成21年6月26日 (2009.6.26)

(65) 公開番号 特開2011-9506 (P2011-9506A)

(43) 公開日 平成23年1月13日 (2011.1.13)

審査請求日 平成24年3月21日 (2012.3.21)

(31) 優先権主張番号 特願2008-169286 (P2008-169286)

(32) 優先日 平成20年6月27日 (2008.6.27)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2009-46433 (P2009-46433)

(32) 優先日 平成21年2月27日 (2009.2.27)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2009-129313 (P2009-129313)

(32) 優先日 平成21年5月28日 (2009.5.28)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 伊佐 敏行

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 神保 安弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 手塚 祐朗

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 大力 浩二

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面を有する基板上に、ゲート電極を覆うゲート絶縁層と、

前記ゲート絶縁層に接する半導体層と、

前記半導体層の上にあり、当該半導体層の一部に接し、ソース領域及びドレイン領域を

形成する不純物半導体層と、

を有し、

前記半導体層において、前記ゲート絶縁層側には、微結晶半導体が形成され、

前記半導体層において、前記不純物半導体層側には、非晶質構造の中に結晶領域が離散

し、

前記結晶領域は、前記ゲート絶縁層側から前記不純物半導体層側に向けて、略放射状に

成長した逆錐形状の結晶領域を有することを特徴とする薄膜トランジスタ。

## 【請求項 2】

絶縁表面を有する基板上に、ゲート電極を覆うゲート絶縁層と、

前記ゲート絶縁層に接する第1半導体層と、

前記第1半導体層に積層される第2半導体層と、

前記第2半導体層の上にあり、当該第2半導体層の一部に接し、ソース領域及びドレイ

ン領域を形成する不純物半導体層と、

を有し、

前記第1半導体層は、分散された微結晶半導体または網状の微結晶半導体であり、

10

20

前記第2半導体層は、非晶質構造の中に結晶領域を有する半導体層で形成され、前記結晶領域は、前記ゲート絶縁層側から前記不純物半導体層側に向けて、略放射状に成長した逆錐形状の結晶領域を有することを特徴とする薄膜トランジスタ。

【請求項3】

請求項2において、前記逆錐形状の結晶領域は、前記第1半導体層及び前記第2半導体層の界面から前記第2半導体層が堆積される方向に向けて、略放射状に成長した逆錐形状の結晶領域であることを特徴とする薄膜トランジスタ。

【請求項4】

請求項1乃至3のいずれか一において、前記結晶領域は、粒径が1nm以上10nm以下の結晶粒を有することを特徴とする薄膜トランジスタ。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜トランジスタ及びその作製方法、並びに該薄膜トランジスタを用いた半導体装置及び表示装置に関する。

【背景技術】

【0002】

電界効果トランジスタの一種として、絶縁表面を有する基板上に形成された半導体層にチャネル形成領域が形成される薄膜トランジスタが知られている。薄膜トランジスタに用いられる半導体層として、非晶質シリコン、微結晶シリコン及び多結晶シリコンを用いる技術が開示されている（特許文献1乃至5参照）。薄膜トランジスタの代表的な応用例は、液晶テレビジョン装置であり、表示画面を構成する各画素のスイッチングトランジスタとして実用化されている。

20

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001-053283号公報

【特許文献2】特開平5-129608号公報

【特許文献3】特開2005-049832号公報

【特許文献4】特開平7-131030号公報

30

【特許文献5】特開2005-191546号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

非晶質シリコン層でチャネル形成領域が形成される薄膜トランジスタは、電界効果移動度及びオン電流が低いといった問題がある。一方、微結晶シリコン層でチャネル形成領域が形成される薄膜トランジスタは、非晶質シリコン層でチャネル形成領域が形成される薄膜トランジスタと比較して、電界効果移動度が向上するもののオフ電流が高くなってしまい、十分なスイッチング特性が得られないといった問題がある。

40

【0005】

多結晶シリコン層がチャネル形成領域となる薄膜トランジスタは、上記二種類の薄膜トランジスタよりも電界効果移動度が格段に高く、高いオン電流が得られるといった特性がある。この薄膜トランジスタは、前記した特性により、画素に設けられるスイッチング用のトランジスタのみならず、高速動作が要求されるドライバ回路をも構成することができる。

【0006】

しかし、多結晶シリコン層がチャネル形成領域となる薄膜トランジスタは、非晶質シリコン層でチャネル形成領域が形成される薄膜トランジスタを形成する場合に比べ半導体層の結晶化工程が必要となり、製造コストが増大することが問題となっている。例えば、多結晶シリコン層の製造のために必要なレーザアニール技術は、レーザビームの照射面積が小

50

さく大画面の液晶パネルを効率良く生産することができないといった問題がある。

【0007】

ところで、表示パネルの製造に用いられているガラス基板は、第3世代( $550\text{mm} \times 650\text{mm}$ )、第3.5世代( $600\text{mm} \times 720\text{mm}$ 、または $620\text{mm} \times 750\text{mm}$ )、第4世代( $680\text{mm} \times 880\text{mm}$ 、または $730\text{mm} \times 920\text{mm}$ )、第5世代( $1100\text{mm} \times 1300\text{mm}$ )、第6世代( $1500\text{mm} \times 1850\text{mm}$ )、第7世代( $1870\text{mm} \times 2200\text{mm}$ )、第8世代( $2200\text{mm} \times 2400\text{mm}$ )と年々大型化が進んでおり、今後は第9世代( $2400\text{mm} \times 2800\text{mm}$ 、 $2450\text{mm} \times 3050\text{mm}$ )、第10世代( $2950\text{mm} \times 3400\text{mm}$ )へと大面積化が進むと予測されている。ガラス基板の大型化はコストミニマム設計の思想に基づいている。

10

【0008】

これに対して、第10世代( $2950\text{mm} \times 3400\text{mm}$ )におけるような大面積のマザーガラス基板に、高速動作が可能な薄膜トランジスタを、生産性良く製造することができる技術は依然として確立されておらず、そのことが産業界の問題となっている。

【0009】

そこで本発明の一態様は、薄膜トランジスタのオン電流及びオフ電流に係る上記問題点を解決することを課題とする。

【課題を解決するための手段】

【0010】

本発明の一態様は、薄膜トランジスタにおいて、ゲート絶縁層と、ソース領域及びドレイン領域との間であって、少なくともソース領域及びドレイン領域側に、非晶質構造の中に結晶領域を有する半導体層をバッファ層として有することを要旨とする。

20

【0011】

また、本発明の一態様は、薄膜トランジスタにおいて、ゲート絶縁層と、ゲート絶縁層に接する半導体層と、半導体層とソース領域及びドレイン領域の間に有するバッファ層とを有し、バッファ層は、非晶質構造の中に結晶領域を有することを要旨とする。

【0012】

また、本発明の一態様は、薄膜トランジスタにおいて、ゲート絶縁層と、ゲート絶縁層に接するバッファ層と、バッファ層に一部接するソース領域及びドレイン領域とを有し、バッファ層は、非晶質構造の中に少なくとも粒径が $1\text{nm}$ 以上 $10\text{nm}$ 以下の結晶粒(微小結晶粒ともいう。)を有することを要旨とする。

30

【0013】

また、本発明の一態様は、薄膜トランジスタにおいて、ゲート電極を覆うゲート絶縁層と、ゲート絶縁層に接する半導体層と、半導体層の一部に接し、ソース領域及びドレイン領域を形成する不純物半導体層と、を有し、半導体層において、ゲート絶縁層側には、微結晶半導体が形成され、半導体層において、不純物半導体層側には、非晶質構造の中に結晶領域が離散していることを要旨とする。

【0014】

当該バッファ層は、ゲート絶縁層と接する面とは反対側、所謂バックチャネル側に配設される。

40

【0015】

非晶質構造の中に結晶領域を有する半導体層において、窒素が含まれる。このときの、二次イオン質量分析法によって計測される窒素濃度は、 $1 \times 10^{20}\text{cm}^{-3}$ 乃至 $1 \times 10^{21}\text{cm}^{-3}$ 、好ましくは $2 \times 10^{20}\text{cm}^{-3}$ 乃至 $1 \times 10^{21}\text{cm}^{-3}$ 、より好ましくは $3 \times 10^{20}\text{cm}^{-3}$ 乃至 $1 \times 10^{21}\text{cm}^{-3}$ である。

【0016】

また、非晶質構造の中に結晶領域を有する半導体層は、低温フォトルミネッセンス分光によるスペクトルのピーク領域は、 $1.31\text{eV}$ 以上 $1.39\text{eV}$ 以下である。

【0017】

また、非晶質構造の中に結晶領域を有する半導体層は、非晶質半導体、代表的にはアモル

50

ファスシリコンのバンドギャップのバンドテールと比較して、傾斜が急峻である。このため、バンドギャップが広くなり、従来の非晶質半導体層と比較して、トンネル電流が流れにくくなる。

【0018】

非晶質構造の中に結晶領域を有する半導体層は、微結晶半導体の生成が可能な混合比で半導体材料ガス（例えば、水素化シリコンガス、フッ化シリコンガス、塩化シリコンガス、水素化ゲルマニウムガス、フッ化ゲルマニウムガス、塩化ゲルマニウムガス等）と希釈ガスを反応ガスとして用いて形成される。当該反応ガスが導入された、酸素濃度を低減させた超高真空反応室内において、所定の圧力を維持してグロー放電プラズマを生成する。これにより反応室内に置かれた基板に被膜が堆積されるが、結晶核の生成または成長を妨げる不純物元素を反応室中に含ませて、当該不純物元素の濃度を制御することで、非晶質構造の中に結晶領域として錐形状結晶領域及び／または微小結晶粒を形成する。

10

【0019】

基板上に被膜が堆積される際に、結晶核の生成を低減するように不純物元素の濃度を制御して、結晶核を生成し、その結晶核を基に逆錐形状結晶領域を形成する。また、基板上に被膜が堆積される際に、結晶核の生成を抑制するように不純物元素の濃度を制御して、結晶核の生成を抑制して、微小結晶粒を形成する。また、被膜の下地層が結晶性を有する半導体層の場合、結晶成長を低減するように不純物元素の濃度を制御して、結晶成長を低減しつつ非晶質構造を堆積することで、順錐形結晶領域を形成する。

20

【0020】

結晶核の生成、及び結晶成長を低減または抑制する不純物元素としては、窒素若しくは窒化物が好ましい。

【0021】

非晶質構造の中に結晶領域を有する半導体層において、二次イオン質量分析法によって計測される窒素濃度を  $3 \times 10^{20} \text{ cm}^{-3}$  乃至  $1 \times 10^{21} \text{ cm}^{-3}$  とすることで、結晶核の生成を制御して、結晶核を生成しないようにして、微小結晶粒を形成する。

【0022】

また、非晶質構造の中に結晶領域を有する半導体層において、二次イオン質量分析法によって計測される窒素濃度を  $1 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下、好ましくは  $2 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下とすることで、錐形状結晶領域の成長端となる結晶核の生成位置と生成密度を制御する。または錐形状結晶領域の結晶成長を制御する。

30

【0023】

結晶領域の一形態である錐形状結晶領域には、ボトムゲート型の薄膜トランジスタの場合、ゲート絶縁層からソース領域及びドレイン領域に向かって幅が狭まる錐形状の結晶領域（以下、順錐形ともいう。）がある。また、ゲート絶縁層、またはゲート絶縁層に接する半導体層と、結晶領域を有する半導体層の界面から、ソース領域及びドレイン領域に向けて、略放射状に成長した逆錐形がある。

【0024】

ここで、順錐形とは、（i）多数の平面から構成される面と、（ii）前記面の外周と前記面の外に存在する頂点とを結ぶ線の集合によって作られる立体的形状であって、該頂点が多数の平面から構成される面よりソース領域及びドレイン領域側に存在するものをいう。即ち、非晶質構造の中に結晶領域を有する半導体層が堆積される方向に向けて、幅が狭まった形状である。これは、非晶質構造の中に結晶領域を有する半導体層の下地となる半導体層が、微結晶半導体層または結晶性半導体層の場合、半導体層を種結晶として、部分的に結晶成長させる条件で非晶質構造の中に結晶領域を有する半導体層を堆積させることで、結晶領域の幅が狭まるように結晶成長するため形成される。

40

【0025】

ここで、逆錐形とは、（i）多数の平面から構成される面と、（ii）前記面の外周と前記面の外に存在する頂点とを結ぶ線の集合によって作られる立体的形状であって、該頂点

50

が多数の平面から構成される面より基板側に存在するものをいう。即ち、非晶質構造の中に結晶領域を有する半導体層が堆積される方向に向けて、略放射状に成長した形状である。離散的に形成された結晶核のそれぞれが、被膜の堆積と共に結晶の方位に沿って成長することで、結晶領域は、結晶核を起点として非晶質構造の中に結晶領域を有する半導体層が堆積される方向と垂直な面の面内方向に拡がるように成長する。

【0026】

また、錐形状結晶領域内には単結晶または双晶を含む。また、非晶質構造内において錐形状結晶領域は、離散しているため、結晶粒界が少ない。なお、双晶とは、結晶粒界において異なる二つの結晶粒が極めて整合性よく接合していることをいう。即ち、結晶粒界において結晶格子が連続的に連なり、結晶欠陥等に起因するトラップ準位を非常に作りにくい構成となっている。従って、この様な結晶構造を有する領域は実質的に結晶粒界が存在しないと見なすことができる。

【0027】

結晶領域の一形態である微小結晶粒は、粒径が 1 nm 以上 10 nm 以下、好ましくは 1 nm 以上 5 nm 以下の結晶粒である。堆積原料ガスに窒素を含ませることにより、結晶核の生成を妨げるため、結晶核にならない微小結晶粒を形成することができる。また、半導体層中の微小結晶粒の密度を高めることにより、結晶成分比が高くなる。

【0028】

以上のことから、薄膜トランジスタにおいて、チャネル形成領域と、ソース領域及びドレイン領域との間にバッファ層として、非晶質構造の中に結晶領域を有する半導体層を設けることにより、ソース領域またはドレイン領域に電圧が印加されたときのバッファ層の厚さ方向における抵抗を下げることが可能である。特に、バッファ層としてソース領域及びドレイン領域の直下に非晶質構造の中に結晶領域を有する半導体層を設けることにより、非晶質半導体層をゲート絶縁層と、ソース領域及びドレイン領域との間に設けた薄膜トランジスタと比較して、薄膜トランジスタのオン電流を高めることができる。

【0029】

また、非晶質構造の中に結晶領域を有する半導体層は、非晶質半導体、代表的にはアモルファスシリコンのバンドギャップのバンドテールと比較して、傾斜が急峻となり、バンドギャップが広くなり、トンネル電流が流れにくくなる。このため、オフ電流が流れる領域にバッファ層として非晶質構造の中に結晶領域を有する半導体層を設けることにより、微結晶半導体をゲート絶縁層と、ソース領域及びドレイン領域との間に設けた薄膜トランジスタと比較して、オフ電流を低減することができる。

【0030】

なお、シリコン中にあって、シリコンの配位数を減らし、ダングリングボンドを生成する不純物元素、例えば酸素のような不純物元素の濃度は、低減させる。すなわち、酸素については二次イオン質量分析法によって計測される濃度を  $5 \times 10^{-8} \text{ cm}^{-3}$  以下とすることが好ましい。

【0031】

なお、ここでは、他の計測法が示されていない濃度は、S I M S ( Secondary Ion Mass Spectrometry ) の測定値によるものである。

【0032】

なお、オン電流とは、トランジスタがオン状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、n型のトランジスタの場合には、ゲート電圧がトランジスタの閾値電圧よりも高いときにソース電極とドレイン電極との間に流れる電流である。

【0033】

また、オフ電流とは、トランジスタがオフ状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、n型のトランジスタの場合には、ゲート電圧がトランジスタの閾値電圧よりも低いときにソース電極とドレイン電極との間に流れる電流である。

【発明の効果】

【0034】

10

20

30

40

50

以上により、非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオン電流を高めると共に、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオフ電流を低減することができる。

【図面の簡単な説明】

【0035】

【図1】本発明の一形態に係る薄膜トランジスタの一例を説明する図である。

【図2】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図3】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図4】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図5】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図6】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図7】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図8】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図9】本発明の一形態に係る薄膜トランジスタの一例を説明する図である。

【図10】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

。

【図11】本発明の一形態に係る薄膜トランジスタの一例を説明する図である。

【図12】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

。

【図13】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

。

【図14】本発明の一形態に係る薄膜トランジスタの一例を説明する図である。

【図15】本発明の一形態に係る薄膜トランジスタの作製方法の一例を説明する図である。

。

【図16】本発明の一形態に係る薄膜トランジスタの作製方法の一例を説明する図である。

。

【図17】本発明の一形態に係る薄膜トランジスタの作製方法の一例を説明する図である。

。

【図18】本発明の一形態に係る薄膜トランジスタの作製方法の一例を説明する図である。

。

【図19】本発明の一形態に係る薄膜トランジスタの作製方法に適用可能な装置を説明する図である。

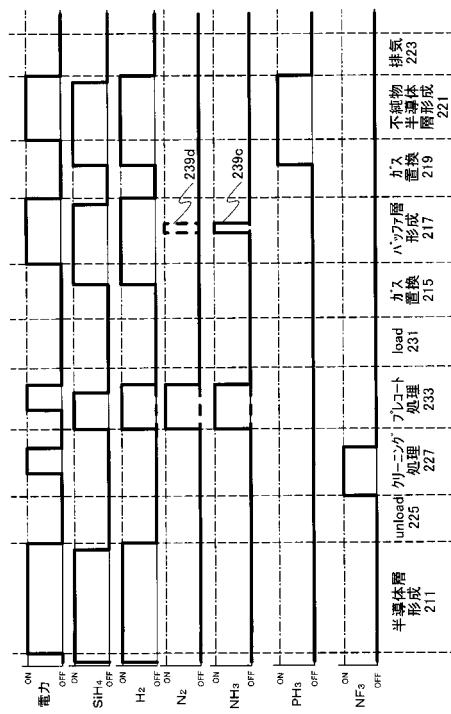

【図20】本発明の一形態に係る薄膜トランジスタの作製方法のタイムチャートの一例を説明する図である。

【図21】本発明の一形態に係る薄膜トランジスタの作製方法のタイムチャートの一例を説明する図である。

【図22】本発明の一形態に係る薄膜トランジスタの作製方法のタイムチャートの一例を説明する図である。

【図23】本発明の一形態に係る薄膜トランジスタの作製方法のタイムチャートの一例を説明する図である。

【図24】本発明の一形態に係る薄膜トランジスタの作製方法のタイムチャートの一例を説明する図である。

【図25】本発明の一形態に係る薄膜トランジスタの作製方法のタイムチャートの一例を説明する図である。

【図26】本発明の一形態に係る薄膜トランジスタの作製方法の一例を説明する図である。

。

【図27】本発明の一形態に係る薄膜トランジスタの作製方法の一例を説明する図である。

。

【図28】本発明の一形態に係る薄膜トランジスタの作製方法の一例を説明する図である。

。

10

20

30

40

50

【図29】本発明の一形態に係る薄膜トランジスタの作製方法の一例を説明する図である。

【図30】本発明の一形態に適用可能な多階調マスクを説明する図である。

【図31】本発明の一形態の薄膜トランジスタを適用可能な表示パネルを説明する図である。

【図32】本発明の一形態の薄膜トランジスタを適用可能な電子機器等を説明する図である。

【図33】本発明の一形態の薄膜トランジスタを適用可能な電子機器等を説明する図である。

【図34】本発明の一形態の薄膜トランジスタを適用可能な電子機器等を説明する図である。

【図35】実施例1で作製した薄膜トランジスタの断面構造を説明する図である。

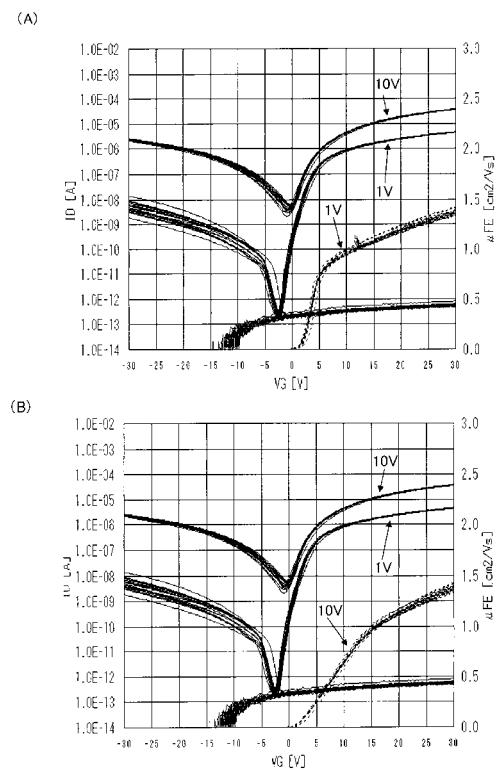

【図36】実施例2で作製した薄膜トランジスタの電気特性を説明する図である。

【図37】実施例2で作製した薄膜トランジスタの信頼性を説明する図である。

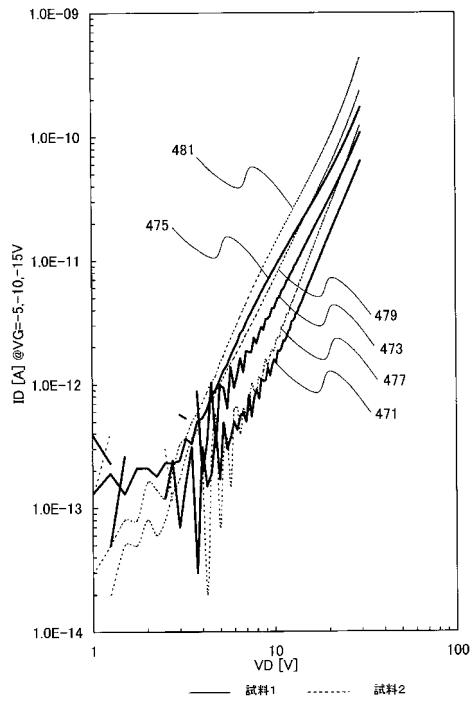

【図38】実施例3で作製した薄膜トランジスタの電気特性を説明する図である。

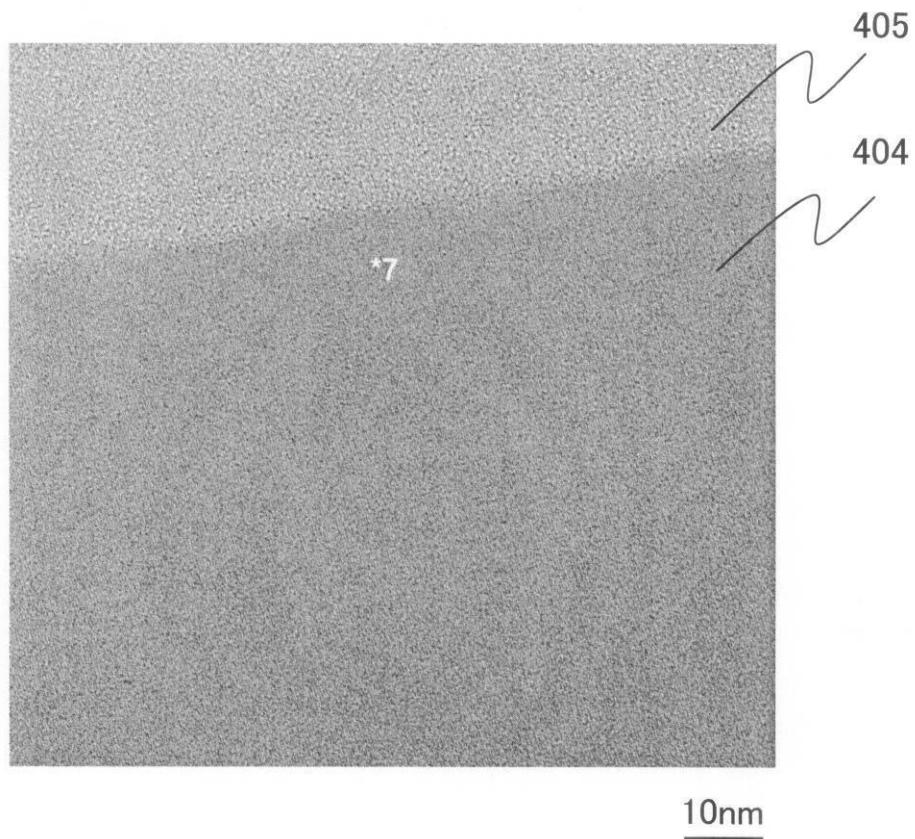

【図39】実施例4で示す断面TEM像を説明する図である。

【図40】実施例4で示す断面TEM像を説明する図である。

【図41】実施例4で示す断面TEM像を説明する図である。

【図42】実施例4で示す断面TEM像を説明する図である。

【図43】半導体層の原子軌道を説明する図である。

【図44】半導体層の原子軌道を説明する図である。

【図45】実施例5で作製した薄膜トランジスタの電気特性を説明する図である。

【図46】比較例で作製した薄膜トランジスタの電気特性を説明する図である。

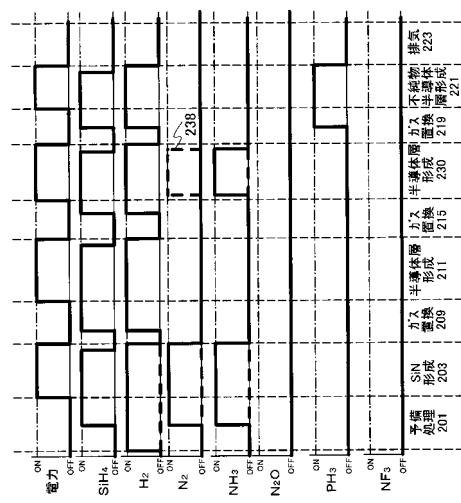

【図47】実施例6で作製した薄膜トランジスタの電気特性を説明する図である。

【図48】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図49】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図50】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図51】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

【図52】本発明の一形態に係る薄膜トランジスタが有する半導体層を説明する図である。

#### 【発明を実施するための形態】

##### 【0036】

実施の形態について、図面を参照して以下に説明する。ただし、本発明は以下の説明に限定されるものではない。本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解されるからである。したがって、本発明は以下に示す実施の形態の記載内容のみに限定して解釈されるものではない。なお、図面を用いて本発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。また、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

##### 【0037】

##### (実施の形態1)

本実施の形態では、薄膜トランジスタの形態の一例について、図面を参照して説明する。

##### 【0038】

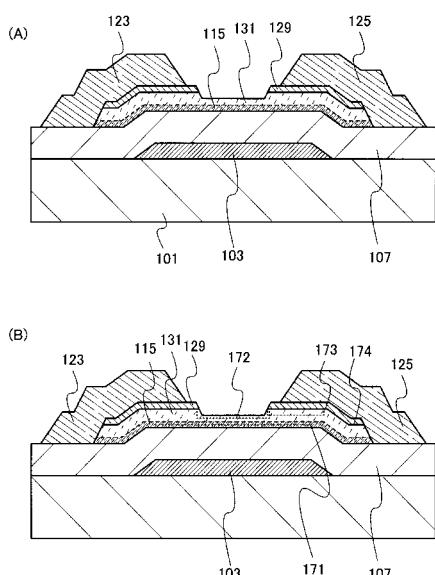

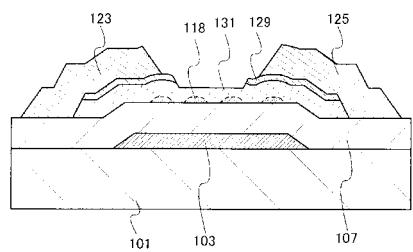

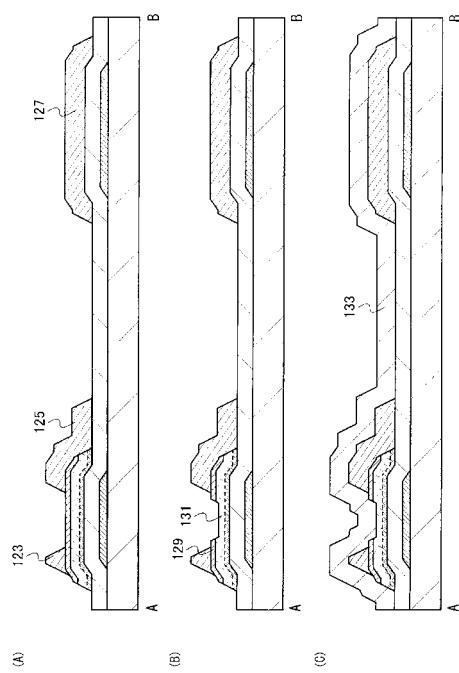

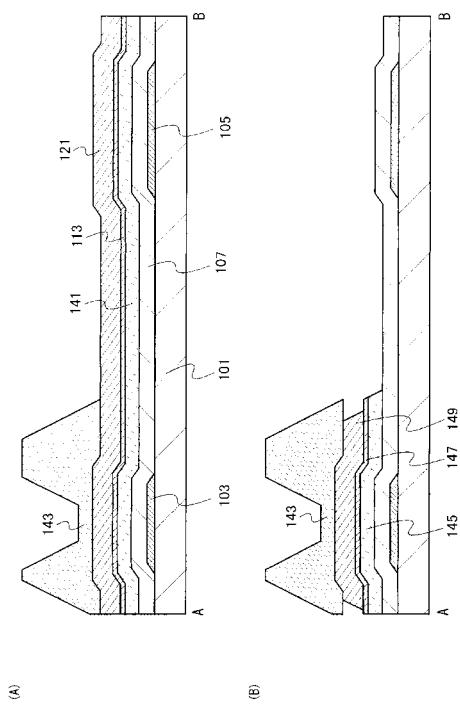

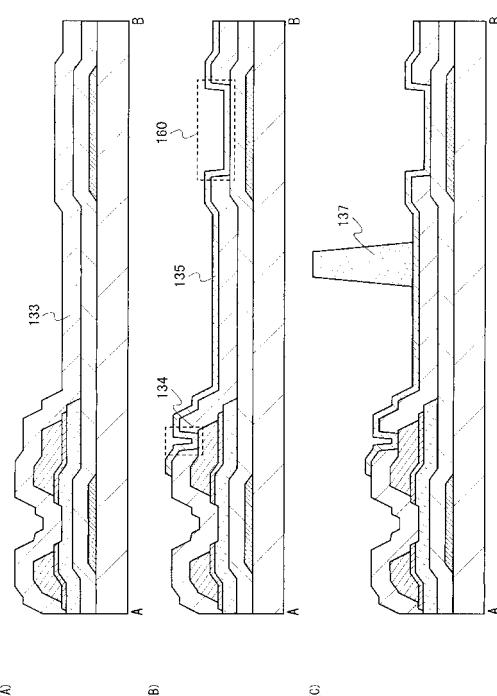

図1は、本実施の形態にかかる薄膜トランジスタの断面図を示す。図1(A)に示す薄膜トランジスタは、基板101上にゲート電極層103を有し、ゲート電極層103を覆うゲート絶縁層107を有し、ゲート絶縁層107上に接するチャネル形成領域として機能

10

20

30

40

50

する半導体層 115 を有し、半導体層 115 上にバッファ層 131 を有し、バッファ層 131 上の一部に接するソース領域及びドレイン領域 129 を有する。また、ソース領域及びドレイン領域 129 上に接する配線層 123、125 を有する。配線層 123、125 はソース電極及びドレイン電極を構成する。また、各層は所望の形状にパターン形成されている。ここでは、バッファ層 131 を、非晶質構造の中に結晶領域を有する半導体層で形成することを特徴とする。

【0039】

図 1 (B) に示すように、半導体層 115 において、ゲート電極層 103 と重畳する領域であり、且つゲート絶縁層 107 側の領域 171 が、チャネルとして機能する。また、バッファ層 131 において、ゲート絶縁層 107 と反対側であり、且つソース領域及びドレイン領域 129 に接しない領域 172 がバックチャネルとして機能する。また、バッファ層 131 において、ドレイン領域に接する側の領域 173 が空乏層となる。また、バッファ層 131 と、ソース領域またはドレイン領域とが接する領域 174 が接合領域である。

【0040】

基板 101 としては、ガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板等を用いることができる。また、基板に透光性を要しない場合には、ステンレス合金等の金属の基板の表面に絶縁層を設けたものを用いてもよい。ガラス基板としては、例えば、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス若しくはアルミニケイ酸ガラス等の無アルカリガラス基板を用いるとよい。

【0041】

ゲート電極層 103 は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体層や Ag Pd Cu 合金を用いてもよい。

【0042】

例えば、ゲート電極層 103 の 2 層の積層構造としては、アルミニウム層上にモリブデン層が積層された二層構造、銅層上にモリブデン層が積層された二層構造、銅層上に窒化チタン層若しくは窒化タンタル層が積層された二層構造、または窒化チタン層とモリブデン層とが積層された二層構造とすることが好ましい。三層の積層構造としては、タングステン層または窒化タングステン層と、アルミニウムとシリコンの合金またはアルミニウムとチタンの合金の層と、窒化チタン層またはチタン層とが積層された積層とすることが好ましい。電気的抵抗が低い層上にバリア層として機能する金属層が積層されることで、電気的抵抗が低い層から半導体層への金属元素の拡散を防止することができる。

【0043】

ゲート絶縁層 107 は、CVD 法またはスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層または窒化酸化シリコン層を単層でまたは積層して形成することができる。また、ゲート絶縁層 107 を酸化窒化シリコン層により形成することで、半導体層 115 に微結晶半導体層を形成した場合、薄膜トランジスタの閾値電圧の変動を低減することができる。

【0044】

なお、本明細書において、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法 (RBS : Rutherford Backscattering Spectrometry) 及び水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合に、組成範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 1.5 原子%、シリコンが 2.5 ~ 3.5 原子%、水素が 0.1 ~ 1.0 原子% の範囲で含まれるものという。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS 及び HFS を用いて測定した場合に、組成範囲として酸素が 5 ~ 3.0 原子%、窒素が 2.0 ~ 5.5 原子%、シリコンが 2.5 ~ 3.5 原子%、水素が 1.0 ~ 3.0 原子% の範囲で含まれるものという。ただし、酸化窒化シリコンまたは窒化酸化シリコ

10

20

30

40

50

ンを構成する原子の合計を 100 原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

【0045】

半導体層 115 は、微結晶半導体層、非晶質半導体層、または非晶質構造の中に結晶領域を有する半導体層を用いて形成する。微結晶半導体層、非晶質半導体層、または非晶質構造の中に結晶領域を有する半導体層としては、シリコン、ゲルマニウム、またはシリコンゲルマニウムを用いることができる。なお、半導体層 115 は、n 型の導電性を付与するリンまたは p 型の導電性を付与するボロンが添加されてもよい。また、半導体層 115 は、チタン、ジルコニウム、ハフニウム、バナジウム、ニオブ、タンタル、クロム、モリブデン、タングステン、コバルト、ニッケル、白金等のシリコンと反応してシリサイドを形成する金属元素が添加されていてもよい。半導体層 115 に n 型の導電性を付与するリン、p 型の導電性を付与するボロン、またはシリコンと反応してシリサイドを形成する金属元素等を添加することにより、半導体層のキャリア移動度を高めることができるため、当該半導体層をチャネル形成領域とする薄膜トランジスタの電界効果移動度を高めることができる。半導体層 115 の厚さを、3 ~ 100 nm、または 5 ~ 50 nm とすることが好ましい。

【0046】

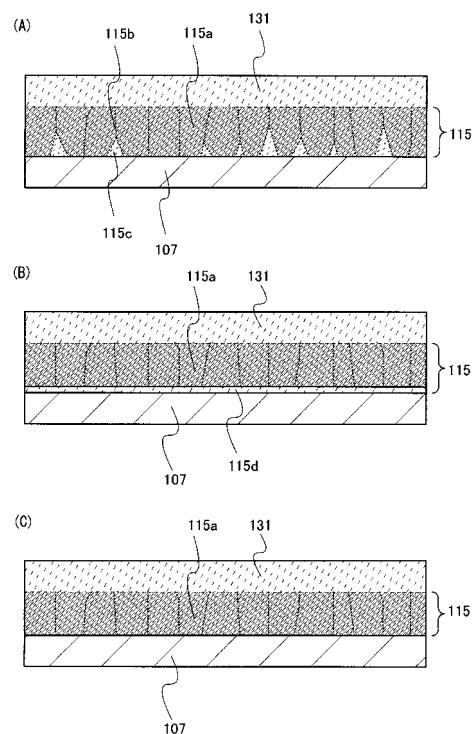

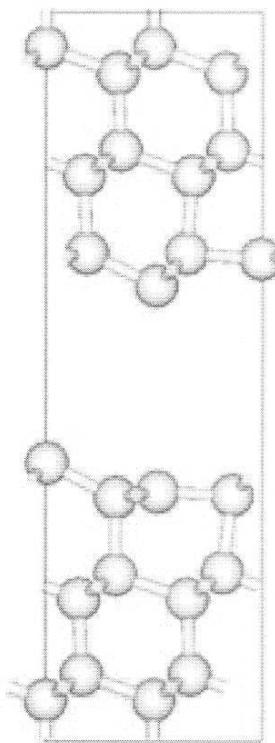

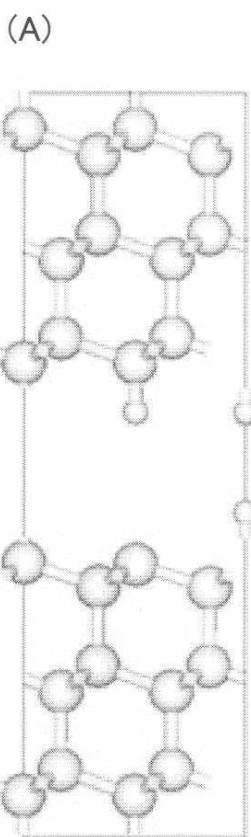

微結晶半導体層とは、非晶質と結晶構造（単結晶、多結晶を含む）の中間的な構造の半導体を含む層である。微結晶半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な半導体であり、結晶粒径が 2 nm 以上 200 nm 以下、好ましくは 10 nm 以上 80 nm 以下、より好ましくは、20 nm 以上 50 nm 以下の柱状結晶または針状結晶 115a が基板表面に対して法線方向に成長している。このため、柱状結晶または針状結晶 115a の界面には、結晶粒界 115b が形成される。また、柱状結晶または針状結晶 115a の間には、非晶質構造 115c が存在している。（図 2 (A) 参照）。

【0047】

また、微結晶半導体層に含まれる酸素及び窒素の二次イオン質量分析法によって計測される濃度は、 $1 \times 10^{-8} \text{ cm}^{-3}$  未満とすることが好ましい。

【0048】

また、微結晶半導体層において、ゲート絶縁層 107 との界面において、非晶質層 115d が形成され、その上に柱状結晶または針状結晶 115a が形成されても良い（図 2 (B) 参照）。

【0049】

また、図 2 (C) に示すように、ゲート絶縁層 107 と半導体層 115 との界面において、非晶質構造が無く、ゲート絶縁層 107 の表面から柱状結晶または針状結晶 115a が形成されてもよい。このようにゲート絶縁層 107 と半導体層 115 との界面に非晶質構造がないことで、結晶性の高い柱状結晶または針状結晶 115a をキャリアが移動するため、薄膜トランジスタのオン電流及び電界効果移動度を上昇させることができる。

【0050】

微結晶半導体の代表例である微結晶シリコンは、そのラマンスペクトルが単結晶シリコンを示す  $520 \text{ cm}^{-1}$  よりも低波数側に、シフトしている。即ち、単結晶シリコンを示す  $520 \text{ cm}^{-1}$  とアモルファスシリコンを示す  $480 \text{ cm}^{-1}$  の間に微結晶シリコンのラマンスペクトルのピークがある。また、未結合手（ダンギングボンド）を終端するため水素またはハロゲンを少なくとも 1 原子% またはそれ以上含ませてもよい。さらに、ヘリウム、アルゴン、クリプトン、またはネオンなどの希ガス元素を含ませてもよく、これにより格子歪みをさらに助長させることで、微結晶の構造の安定性が増し良好な微結晶半導体が得られる。このような微結晶半導体に関する記述は、例えば、米国特許 4,409,134 号で開示されている。

【0051】

ここで、本実施の形態の主要な特徴の一つであるバッファ層 131 の構造に関し、図 3 に

10

20

30

40

50

示す。バッファ層 131 は、非晶質構造の中において、結晶領域を有する。結晶領域とは、錐形状の結晶領域及び/または微小結晶粒である。また、結晶領域は分散している。即ち、結晶領域は離散している。バッファ層 131 の厚さは、50 ~ 350 nm、または 120 ~ 250 nm とすることが好ましい。

【0052】

また、バッファ層 131 は、二次イオン質量分析法によって計測される窒素濃度は、 $1 \times 10^{-2.0} \text{ cm}^{-3}$  乃至  $1 \times 10^{-2.1} \text{ cm}^{-3}$ 、 $2 \times 10^{-2.0} \text{ cm}^{-3}$  乃至  $1 \times 10^{-2.1} \text{ cm}^{-3}$ 、 $3 \times 10^{-2.0} \text{ cm}^{-3}$  乃至  $1 \times 10^{-2.1} \text{ cm}^{-3}$  である。

【0053】

また、バッファ層 131 は、低温フォトルミネッセンス分光によるスペクトルのピーク領域は、1.31 eV 以上 1.39 eV 以下である。なお、微結晶半導体層、代表的には微結晶シリコン層を低温フォトルミネッセンス分光により測定したスペクトルのピーク領域は、0.98 eV 以上 1.02 eV 以下であり、非晶質構造の中に結晶領域を有する半導体層は、微結晶半導体層とは異なる。

【0054】

錐形状の結晶領域は、半導体層 115 及びバッファ層 131 の界面から、バッファ層 131 が堆積される方向に向けて、略放射状に成長した錐形状（逆錐形）と、半導体層 115 及びバッファ層 131 の界面から、バッファ層 131 が堆積される方向に向けて、幅が狭まる錐形状（順錐形）とがある。

【0055】

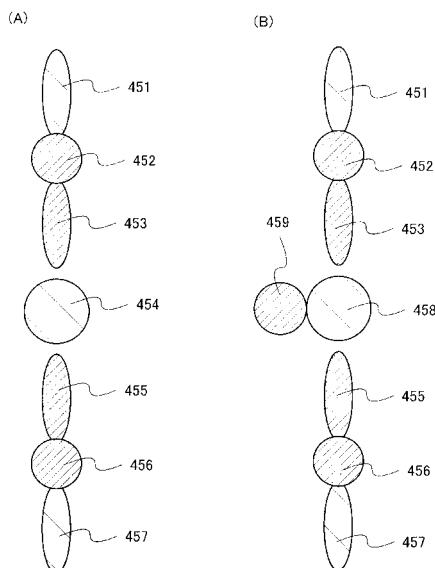

はじめに、逆錐形について図 3 を用いて示す。

【0056】

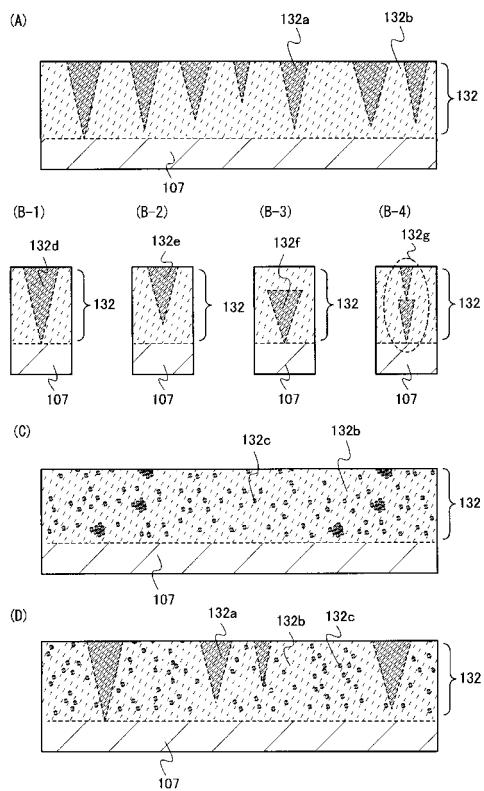

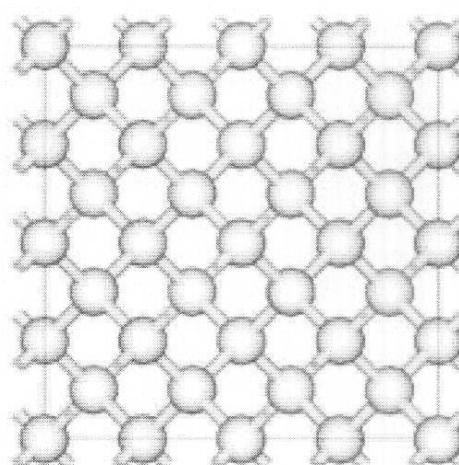

図 3 (A) に示すように、バッファ層 131 においては、非晶質構造 131b 中で結晶領域 131a が分散する。即ち、結晶領域 131a が離散している。

【0057】

図 3 に示す結晶領域 131a の形状は、逆錐形である。ここで、逆錐形とは、(i) 多数の平面から構成される面と、(ii) 前記面の外周と前記面の外に存在する頂点とを結ぶ線の集合によって作られる立体的形状であって、該頂点が多数の平面から構成される面より基板 101 側に存在するものをいう。即ち、バッファ層 131 が堆積される方向に向けて、略放射状に成長した形状である。離散的に形成された結晶核のそれぞれが、バッファ層の形成と共に結晶の方位に沿って成長することで、結晶領域は、結晶核を起点としてバッファ層 131 が堆積される方向と垂直な面の面内方向に拡がるように成長する。また、結晶領域 131a 内には単結晶または双晶を含む。

【0058】

バッファ層に含まれる結晶領域の一形態は、図 3 (B-1) に示すように、結晶領域 131d の頂点が半導体層 115 と接するように形成し、且つ結晶成長がバッファ層の堆積方向に連続的に成長している。

【0059】

このような結晶領域は、バッファ層の堆積初期における窒素濃度を  $1 \times 10^{-2.0} \text{ cm}^{-3}$  以上  $1 \times 10^{-2.1} \text{ cm}^{-3}$  以下、好ましくは  $2 \times 10^{-2.0} \text{ cm}^{-3}$  以上  $1 \times 10^{-2.1} \text{ cm}^{-3}$  以下とし、堆積方向に対して徐々に窒素の濃度を低減することにより、形成することができる。バッファ層に上記濃度の窒素を有することで、結晶領域の高さを制御することができる。結晶領域の高さのばらつきを低減することができる。この結果、複数の薄膜トランジスタにおけるトランジスタ特性のばらつきを低減することができる。

【0060】

バッファ層に含まれる結晶領域の一形態は、図 3 (B-2) に示すように、結晶領域 131e の頂点が半導体層 115 と接せず、一定の距離を置いてから頂点が形成され、且つ結晶成長がバッファ層の堆積方向に連続的に成長している。

【0061】

このような結晶領域は、バッファ層の堆積初期における窒素濃度を  $3 \times 10^{-2.0} \text{ cm}^{-3}$

10

20

30

40

50

乃至  $1 \times 10^{21} \text{ cm}^{-3}$  とし、堆積方向に対して徐々に窒素の濃度を低減することにより、形成される。

【0062】

バッファ層に含まれる結晶領域の一形態は、図3(B-3)に示すように、結晶領域131fの頂点が半導体層115と接するように形成し、且つ結晶成長がバッファ層の堆積方向の途中で途切れしており、結晶領域131f上に非晶質構造が形成される。

【0063】

このような結晶領域は、バッファ層の堆積初期における窒素濃度を  $1 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下、好ましくは  $2 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下とし、堆積方向に対して徐々に窒素の濃度を低減して、結晶を成長させた後、窒素濃度を  $3 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下まで高めることで、形成される。

【0064】

なお、図3(B-3)においては、結晶領域の頂点が半導体層115に接しているが、図3(B-2)と同様の条件により、頂点が半導体層115に接せず、且つ堆積方向の途中で成長が途切れた結晶領域となりうる。

【0065】

バッファ層に含まれる結晶領域の一形態は、図3(B-4)に示すように、堆積方向に対して複数の逆錐形の結晶領域が積み重なった構造131gとなりうる。

【0066】

このような結晶領域は、バッファ層の堆積初期における窒素濃度を  $1 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下、好ましくは  $2 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下とし、堆積方向に対して徐々に窒素の濃度を低減して、結晶を成長させた後、窒素濃度を  $3 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下まで高める。この後、窒素濃度を低減することで形成される。

【0067】

なお、図3(B-4)においては、結晶領域の頂点が半導体層115に接しているが、図3(B-2)と同様の条件により、頂点が半導体層115に接しない構造となりうる。

【0068】

なお、結晶領域131a、131d～131gに、窒素が含まれる。また、NH基またはNH<sub>2</sub>基が含まれる場合がある。また、非晶質構造131bには、窒素が含まれる。NH基またはNH<sub>2</sub>基が含まれる場合がある。

【0069】

また、バッファ層131は、図3(C)に示すように、非晶質構造131b中に微小結晶粒131cが分散する形態がある。微小結晶粒131cとは上記結晶領域の成長核とならない程度の微小な大きさ、代表的には1nm以上10nm以下、好ましくは1nm以上5nm以下の微小な大きさの結晶粒である。微小結晶粒はバッファ層131中の窒素の濃度を制御することで形成することができる。また、微小結晶粒の外側、即ち、非晶質構造131bと接する側には、多くの窒素が偏析しやすい。このため、窒素、好ましくはNH基またはNH<sub>2</sub>基が微小結晶粒131c及び非晶質構造131bの界面において多く存在する場合がある。

【0070】

なお、バッファ層131中において、微小結晶粒131cは、分散していてもよい。または、バッファ層131中において微小結晶粒131cが凝集していてもよい。更には、分散した微小結晶粒131c及び凝集した微小結晶粒131cが存在してもよい。

【0071】

また、バッファ層131は、図3(D)に示すように、非晶質構造131bで結晶領域131a及び微小結晶粒131cが分散する形態がある。

【0072】

なお、微小結晶粒131cに窒素が含まれる。また、NH基またはNH<sub>2</sub>基が含まれる場

10

20

30

40

50

合がある。

【0073】

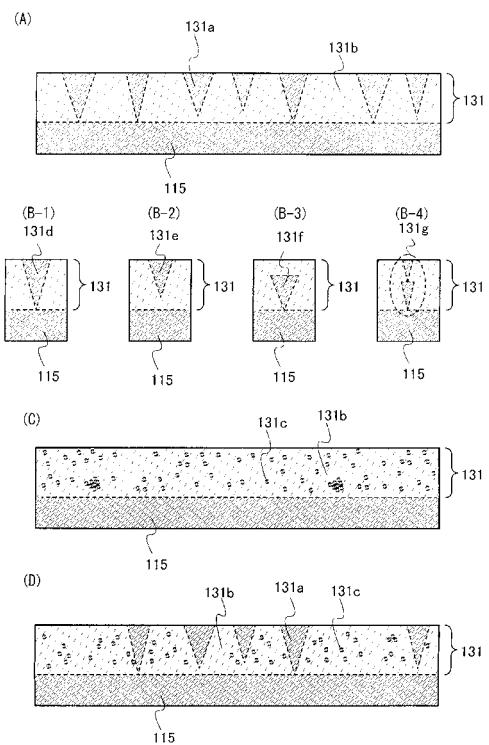

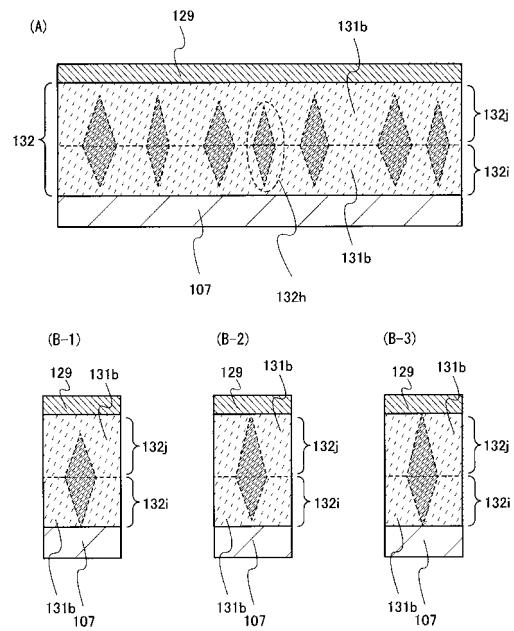

次に、順錐形の結晶領域について図4を用いて示す。

【0074】

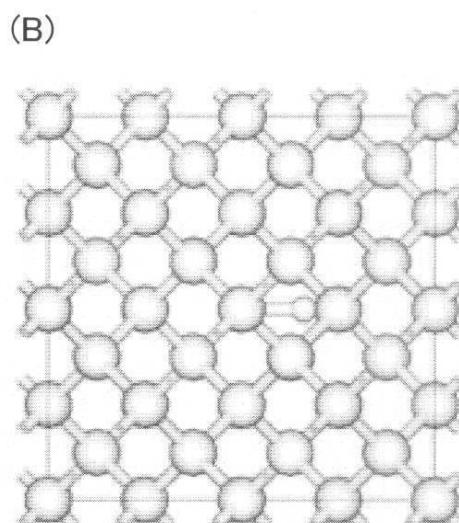

図4(A)に示すように、半導体層115上に、非晶質構造131b中に順錐形の結晶領域131hを有するバッファ層131が形成される。バッファ層131中では、非晶質構造131b内で結晶領域131hが分散する。即ち、結晶領域131hが離散している。

【0075】

図4に示す結晶領域131hの形状は、順錐形である。ここで、順錐形とは、(i)多数の平面から構成される面と、(ii)前記面の外周と前記面の外に存在する頂点とを結ぶ線の集合によって作られる立体的形状であって、該頂点が多数の平面から構成される面よりソース領域及びドレイン領域129側に存在するものをいう。即ち、バッファ層131が堆積される方向に向けて、幅が狭まった形状である。これは、半導体層115が微結晶半導体層または結晶性半導体層の場合、半導体層115を種結晶として、部分的に結晶成長させる条件でバッファ層131を堆積させることで、結晶領域131hの幅が狭まるよう結晶成長するため形成される。ここでは、便宜的に半導体層115と、結晶領域131hが接するように破線で示しているが、半導体層115の一部成長した領域が結晶領域131hとなる。また、結晶領域131h内には単結晶または双晶を含む。

【0076】

バッファ層に含まれる結晶領域の一形態は、図4(A)に示すように、結晶領域131hの底面が半導体層115と接し、頂点が非晶質構造131b中にある形状を有する。

【0077】

このような結晶領域は、バッファ層の堆積中における窒素濃度を $1 \times 10^{20} \text{ cm}^{-3}$ 以上 $1 \times 10^{21} \text{ cm}^{-3}$ 以下、好ましくは $2 \times 10^{20} \text{ cm}^{-3}$ 以上 $1 \times 10^{21} \text{ cm}^{-3}$ とすることにより、形成することができる。

【0078】

バッファ層に含まれる結晶領域の一形態は、図4(B)に示すように、結晶領域131i頂点がソース領域またはドレイン領域129と接する形状を有する。なお、このような場合は非晶質構造131bに対する結晶領域131iの割合が低いことが好ましい。この結果、薄膜トランジスタのオフ電流を低減することができる。

【0079】

このような結晶領域は、バッファ層の堆積中における窒素濃度を、好ましくは $1 \times 10^{20} \text{ cm}^{-3}$ 乃至 $1 \times 10^{21} \text{ cm}^{-3}$ 、好ましくは $2 \times 10^{20} \text{ cm}^{-3}$ 乃至 $1 \times 10^{21} \text{ cm}^{-3}$ とすることにより、形成される。

【0080】

なお、結晶領域131h、131iに、窒素が含まれる。また、NH基またはNH<sub>2</sub>基が含まれる場合がある。また、非晶質構造131bには、窒素が含まれる。また、NH基またはNH<sub>2</sub>基が含まれる場合がある。

【0081】

バッファ層に含まれる結晶領域の一形態は、図4(C)に示すように、非晶質構造131bにおいて結晶領域131hまたは結晶領域131iと、微小結晶粒131cとが分散する形態がある。

【0082】

以上の構造により、ソース領域またはドレイン領域に電圧が印加されたときの、バッファ層131の縦方向における抵抗、即ち、半導体層と、ソース領域またはドレイン領域との間の抵抗を下げることが可能であり、薄膜トランジスタのオン電流を高めることができ。特に、ソース領域及びドレイン領域の直下にバッファ層として非晶質構造の中に結晶領域を有する半導体層を設けることにより、薄膜トランジスタのオン電流を高めることができる。

【0083】

10

20

30

40

50

また、図4(A)乃至(C)において、半導体層115とバッファ層131の界面は、結晶領域131h及び非晶質構造131bとなっているが、図4(D)に示すように、半導体層115が微結晶半導体層の場合は、半導体層115とバッファ層131の界面は、結晶領域である場合もある。これは、バッファ層131を形成する際、半導体層115である微結晶半導体層が種結晶となり、バッファ層131の堆積初期においては、結晶成長するため、半導体層115上全面に結晶領域が成長する。その後、徐々に結晶性が抑制され、順錐形となる結晶領域131jが形成されるためである。

#### 【0084】

この場合、結晶領域131jに、窒素が含まれる。また、NH基またはNH<sub>2</sub>基が含まれる場合がある。また、非晶質構造131bには、窒素が含まれる。また、NH基またはNH<sub>2</sub>基が含まれる場合がある。

10

#### 【0085】

なお、図4(A)～図4(D)において、ゲート絶縁層107と半導体層115の界面から、結晶領域131h～131jの先端までの距離は、3～410nm、好ましくは、20～100nmであることが好ましい。また、結晶核の生成を低減または抑制する不純物元素として、酸素及び窒素があるが、シリコン中にあって、キャリアトラップを生成しない不純物元素(例えば、窒素)を選択する。一方、シリコンの配位数を減らし、ダングリングボンドを生成する不純物元素(例えば酸素)の濃度は低減させる。従って、窒素濃度を低減させず酸素濃度を低減させるとよい。具体的には、酸素については二次イオン質量分析法によって計測される濃度を $5 \times 10^{-8} \text{ cm}^{-3}$ 以下とするよ。

20

#### 【0086】

また、窒素の濃度は、バッファ層が半導体性を保つ濃度であり、且つダングリングボンドが低減し、キャリア移動度が上昇する範囲であることが好ましい。窒素の濃度が高すぎると、半導体性が低下し、絶縁性が増してしまい、オン電流が低下する。また、窒素の濃度が低すぎると、従来の非晶質半導体層と同様となり、キャリア移動度が上昇しないと共に、バッファ層の欠陥準位が増加する。

#### 【0087】

上記説明したように、錐形状の結晶領域は離散的に存在する。結晶領域を離散的に存在させるためには、結晶の核生成密度を制御することが必要である。窒素濃度を制御することで、結晶領域の核生成密度を制御し、結晶領域を離散的に存在せしめることが可能である。また、結晶領域が、バッファ層におけるソース領域及びドレイン領域方向、即ちチャネル長方向において、離散しているため、オフ電流を低減することができる。特に、バッファ層のソース領域及びドレイン領域の間ににおけるチャネル長方向において、離散しているため、オフ電流を低減することができる。

30

#### 【0088】

ソース領域及びドレイン領域129は、一導電型を付与する不純物元素が添加された半導体層(以下、不純物半導体層と示す。)を形成すればよい。nチャネル型の薄膜トランジスタを形成する場合には、一導電型を付与する不純物元素としてリンを用いればよく、代表的には、リンが含有されたアモルファスシリコンまたは微結晶シリコンを用いて形成する。また、pチャネル型の薄膜トランジスタを形成する場合には、一導電型を付与する不純物元素としてボロンを用いればよく、代表的には、ボロンが含有されたアモルファスシリコンまたは微結晶シリコンを用いて形成する。

40

#### 【0089】

一導電型を付与する不純物元素の濃度、ここではリンまたはボロンの濃度を $1 \times 10^{-9}$ ～ $1 \times 10^{-1} \text{ cm}^{-3}$ とすることで、配線層123、125とオーミックコンタクトすることができる。ソース領域及びドレイン領域として機能する。

#### 【0090】

ソース領域及びドレイン領域129は10nm以上100nm以下、好ましくは30nm以上50nm以下の厚さで形成する。ソース領域及びドレイン領域129の厚さを、薄くすることでスループットを向上させることができる。

50

## 【0091】

配線層123、125は、アルミニウム、銅、チタン、ネオジム、スカンジウム、モリブデン、クロム、タンタル若しくはタンゲステン等により単層で、または積層して形成することができる。または、ヒロック防止元素が添加されたアルミニウム合金（ゲート電極層103に用いることができるアルミニウム-ネオジム合金等）により形成してもよい。ドナーとなる不純物元素を添加した結晶性シリコンを用いてもよい。ドナーとなる不純物元素が添加された結晶性シリコンと接する側の層を、チタン、タンタル、モリブデン、タンゲステンまたはこれらの元素の窒化物により形成し、その上にアルミニウムまたはアルミニウム合金を形成した積層構造としても良い。更には、アルミニウムまたはアルミニウム合金の上面及び下面を、チタン、タンタル、モリブデン、タンゲステンまたはこれらの元素の窒化物で挟んだ積層構造としてもよい。例えば、配線層123、125として、アルミニウム層をモリブデン層で挟んだ三層の積層構造とすることができる。10

## 【0092】

本実施の形態により、非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオン電流を高めると共に、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオフ電流を低減することができる。

## 【0093】

ここで、本発明の主要な特徴の一つである非晶質構造の中に結晶領域を有する半導体層に関し考察する。20

## 【0094】

非晶質構造の中に結晶領域を有する半導体層において、Si原子のダングリングボンドを架橋したNH基を有する場合がある。または、Si原子のダングリングボンドを終端したNH<sub>2</sub>基を有する場合がある。これらについて、以下に述べる。

## 【0095】

従来の非晶質半導体は、結晶格子のように構造に一定の繰り返しパターンがない。このため、ダングリングボンドが多く含まれ、当該領域が欠陥となり、キャリアが捕獲される部位となると共に、キャリア移動度の低下が生じる。しかしながら、本実施の形態に示す非晶質構造の中に結晶領域を有する半導体層は、当該ダングリングボンドがNH基で架橋され、またはSi原子のダングリングボンドがNH<sub>2</sub>基で終端され、非晶質構造の中に結晶領域を有する半導体層においてダングリングボンドの数が低減している場合がある。即ち、欠陥準位が低減している。また、ダングリングボンドをNH基で架橋することにより、当該結合部がキャリアの通路となりうるため、従来の非晶質半導体層と比較して、キャリア移動度が上昇する。この結果、薄膜トランジスタのバッファ層に非晶質構造の中に結晶領域を有する半導体層を用いた場合には、薄膜トランジスタのオン電流及び電界効果移動度を上昇させると共に、オフ電流を低減することができる。30

## 【0096】

なお、半導体層のSi原子のダングリングボンドをNH基で架橋するとは、NH基の異なる結合手が、半導体層の異なる半導体元素とそれぞれ結合することをいう。このため、N原子の第1の結合手はH原子と結合し、N原子の第2の結合手は第1の半導体原子と結合し、N原子の第3の結合手は第2の半導体原子と結合する。また、半導体層のSi原子のダングリングボンドをNH<sub>2</sub>基で終端するとは、NH<sub>2</sub>基が、半導体層のSi原子と結合することをいう。このため、N原子の第1の結合手及び第2の結合手は、それぞれ異なるH原子と結合し、N原子の第3の結合手はSi原子と結合する。40

## 【0097】

また、上記のような錐形状の結晶領域の外側、即ち錐形状の結晶領域における非晶質構造との界面（例えば、図3(A)に示す結晶領域131aと非晶質構造131bの界面）、微小結晶粒の外側、即ち微小結晶粒と非晶質構造との界面（例えば、図3(C)に示す微小結晶粒131cと非晶質構造131bの界面）、微小結晶粒の粒界（例えば、図3(C)に示す微小結晶粒131c同士の界面）、半導体層とバッファ層の界面（例えば、図3

10

20

30

40

50

(A)に示す半導体層115とバッファ層131の界面)、バッファ層に含まれる結晶領域の界面(例えば、図4(D)に示す結晶粒界131k)等において、NH基が、シリコン原子のダングリングボンドと結合すると、欠陥準位が無くなり、キャリアが流れやすくなるモデルについて、以下に示す。

【0098】

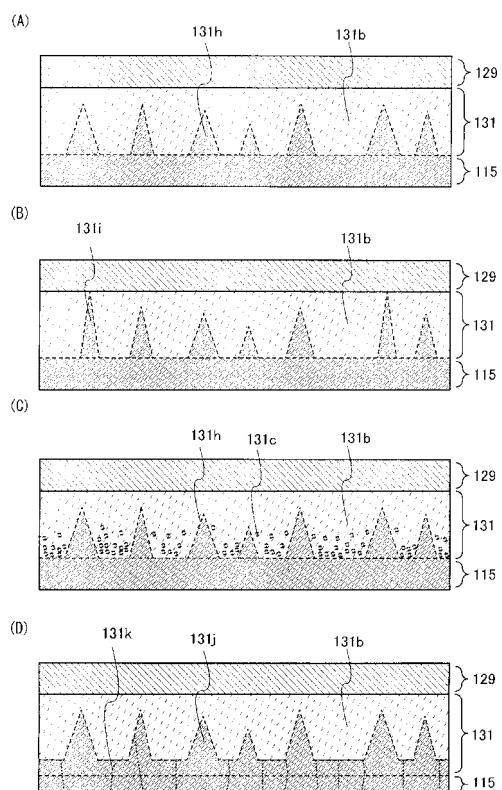

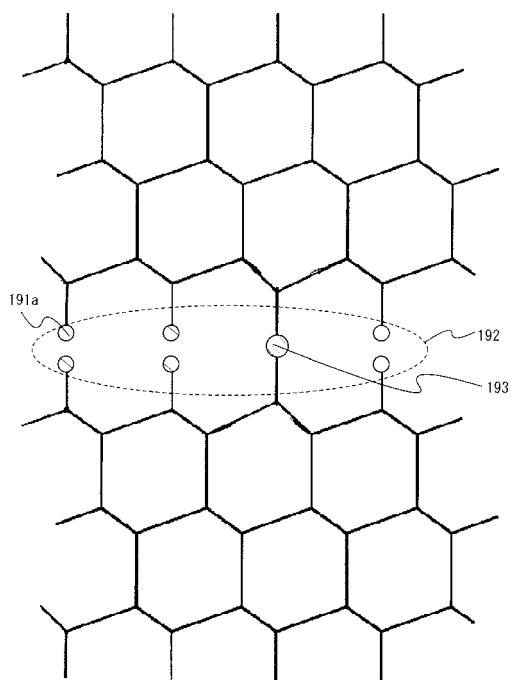

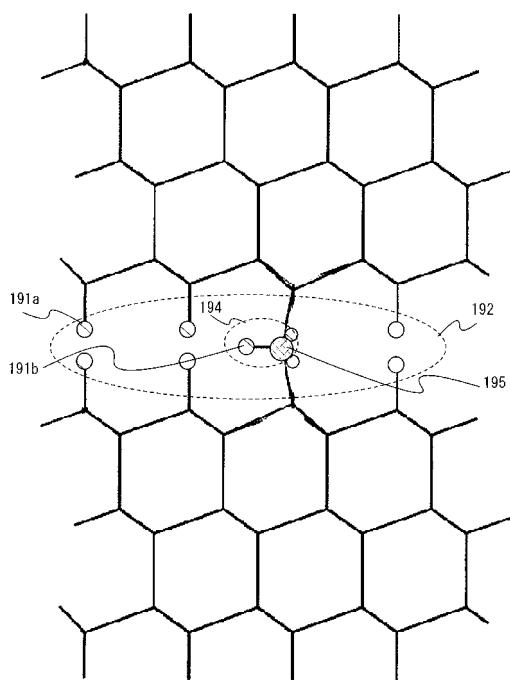

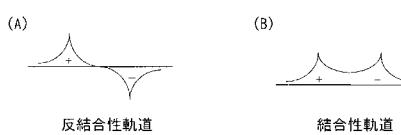

図5に示すように、Si原子のダングリングボンドがH原子191aで終端された結晶粒界192を有するシリコン層において、ダングリングボンドのペア1組がO原子193で架橋されたモデル(モデル1)と、図6に示すように、Si原子のダングリングボンドがH原子191aで終端された結晶粒界192を有するシリコン層において、一対のダングリングボンドがNH基194で架橋されたモデル(モデル2)とのそれと/orにおいて、n型キャリアの移動する準位(即ち、伝導帯における最低準位)であるシリコン層のLUMO(最低非占有軌道)のシミュレーションを行った。シミュレーション用のソフトウェアとしては、密度汎関数理論を用いた第1原理計算ソフトウェアを用いている。なお、図6において、NH基194は窒素原子195及び水素原子191bで示している。また、線の交点はシリコン原子を示し、線はシリコン原子の結合手及びダングリングボンドを示している。さらに、酸素原子及びNH基の有効性を評価するため、酸素原子またはNH基で架橋されたダングリングボンド以外のダングリングボンドは、全て水素原子で終端した。

【0099】

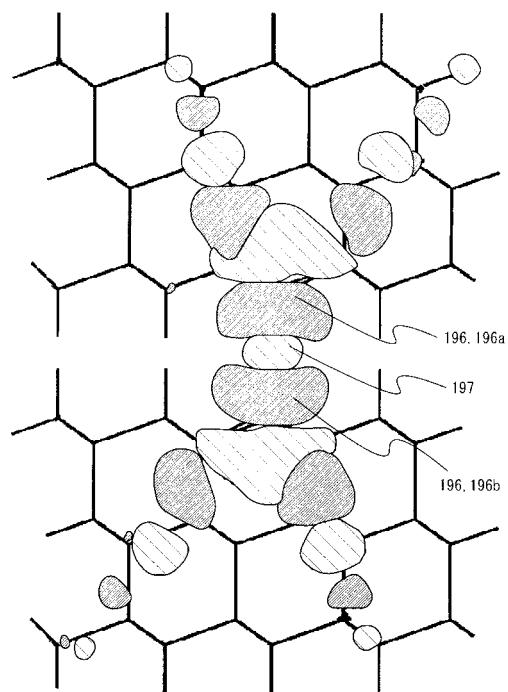

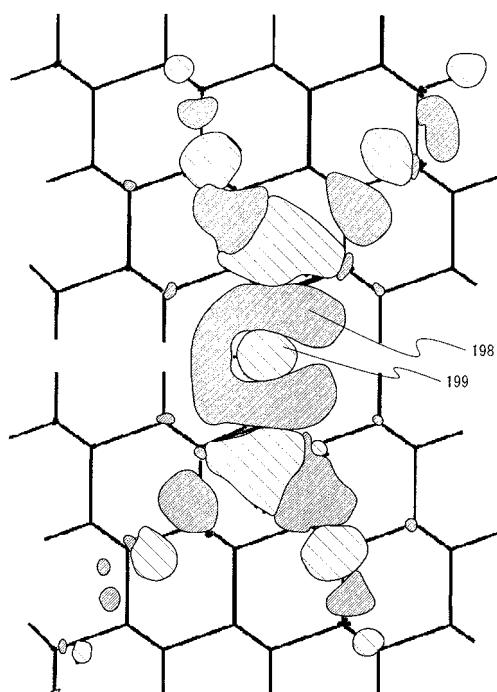

モデル1を用いて行った計算の結果について図7に示し、モデル2を用いて行った計算の結果について図8に示す。

【0100】

図7においては、Si原子のダングリングボンドをO原子で架橋した領域及びその周辺における波動関数の形状を示しており、波動関数196及び波動関数197は、互いに位相が正または負であり、且つ絶対値が等しい領域を示している。図8においては、Si原子のダングリングボンドをNH基で架橋した領域及びその周辺における波動関数の形状を示しており、波動関数198及び波動関数199は、それぞれ位相が正または負であり、且つ絶対値が等しい領域を示している。

【0101】

図7から、Si原子のダングリングボンドをO原子で架橋した場合は、波動関数の絶対値及び位相が等しい領域(例えば、波動関数196a、196b)が途切れているため、キャリアが流れにくくなっていることが分かる。即ち、シリコン層中に酸素が含まれると、キャリアの移動を妨げる結合ができ、シリコン層のキャリア移動度が低下することが分かる。

【0102】

一方、図8から、Si原子のダングリングボンドをNH基で架橋した場合は、異なるSi原子間に於いて波動関数198の絶対値及び位相が等しい領域が、隣接するダングリングボンドの両方に繋がっているため、キャリアが流れやすくなっていることがわかる。即ち、シリコン層中にNH基が含まれていると、ダングリングボンドにおいてキャリアの移動が容易となる結合ができ、シリコン層のキャリア移動度が上昇することがわかる。薄膜トランジスタの移動度が上昇すると考えられる。なお、微小結晶粒の密度が高くなると、半導体層における結晶性が高まるが、それと共にキャリアの移動を阻害する結晶粒界も増加してしまう。しかしながら、シリコン層にNH基を有し、Si原子のダングリングボンドを架橋することにより、当該結合が結晶粒界におけるキャリアの経路となるため、キャリアの移動が阻害されない。

【0103】

以上のことから、バッファ層において、窒素濃度を制御することで、更に好ましくはNH基を含有させることによって、結晶領域及び非晶質構造の界面、微小結晶粒と非晶質構造との界面、微小結晶粒同士の界面、半導体層とバッファ層の界面、バッファ層に含まれる結晶領域中の結晶粒等におけるダングリングボンドにおいて、当該ダングリングボンドを窒素、更にはNH基が架橋し、バッファ層の欠陥準位を低減することができる。また、当

10

20

30

40

50

該架橋により、キャリアが移動可能な結合が形成される。また、窒素の濃度を制御することで、逆錐形の結晶領域の核の密度を制御することができるため、逆錐形の結晶領域が離散した半導体層を形成することができる。また、窒素の濃度を制御することで、結晶成長を制御することができるため、順錐形の結晶領域を有する半導体層を形成することができる。また、微小結晶粒の密度を高めることにより、バッファ層の結晶性を高めることができる。以上のことから、バッファ層のキャリア移動度を高めることができる。

#### 【0104】

また、半導体層及びバッファ層の酸素濃度を低減することにより、結晶領域と非晶質構造との界面、微小結晶粒と非晶質構造との界面、微小結晶粒同士の界面、半導体層とバッファ層の界面、バッファ層に含まれる結晶領域中の結晶粒界、または半導体層に含まれる結晶粒界における欠陥において、キャリアの移動を阻害する結合を低減することができる。

10

#### 【0105】

以上のことから、バッファ層において、酸素濃度を低減し、窒素の濃度を制御することで、さらにはNH<sub>2</sub>基を有せしめることで、結晶領域と非晶質構造との界面、微小結晶粒及び非晶質構造の界面、微小結晶粒同士の界面、半導体層とバッファ層の界面、またはバッファ層に含まれる結晶領域中の結晶粒界等のダングリングボンドが低減する。このため、非晶質半導体層をゲート絶縁層と、ソース領域及びドレイン領域との間に設けた薄膜トランジスタと比較して、オン電流及び電界効果移動度を高めると共に、微結晶半導体層をゲート絶縁層と、ソース領域及びドレイン領域との間に設けた薄膜トランジスタと比較して、オフ電流を低減することができる。

20

#### 【0106】

隣接する結晶領域の間には非晶質構造が充填されている。即ち、結晶領域が離散しており、隣の結晶領域と接していない。このような構造により、ソース領域またはドレイン領域に電圧が印加されたときのバッファ層の縦方向における抵抗、即ち、半導体層と、ソース領域またはドレイン領域との間の抵抗を下げることが可能であり、薄膜トランジスタのオン電流を高めることができる。

#### 【0107】

また、バッファ層として非晶質構造の中に結晶領域を有する半導体層を形成することで、薄膜トランジスタのドレイン耐圧を緩和するため、薄膜トランジスタの劣化を低減することができる。また、ゲート絶縁層に接する半導体層が微結晶半導体層で形成される場合、バッファ層に非晶質構造の中に結晶領域を有する半導体層を用い、且つ微結晶半導体層及びバッファ層を連続的に形成することで、微結晶半導体層における微結晶半導体と非晶質構造の界面の酸化防止が可能であり、微結晶半導体層のキャリア移動度を高めることができる。

30

#### 【0108】

非晶質構造の中に結晶領域を有する半導体層の別の形態について考察する。ここでは、非晶質構造の中に結晶領域を有する半導体層が、NH<sub>2</sub>基を有する場合について示す。

#### 【0109】

Si原子のダングリングボンドがNH<sub>2</sub>基で終端されたモデルのオフ電流低減のメカニズムについて考察するため、欠陥準位及び結合エネルギーについて、第一原理計算を用いてシミュレーションを行った。シミュレーション用のソフトウェアとしては、accelrys社製の第一原理計算ソフトCASTEPを用いた。

40

#### 【0110】

##### (欠陥準位)

はじめに、欠陥準位について示す。ここでは、オフ電流のメカニズムとしてShockley-Read-Hall電流が支配的であると考えた。Shockley-Read-Hallメカニズムによると、キャリアの再結合確率Uは(1)式で表される。

#### 【0111】

## 【数1】

$$U = \sigma v_{th} N_t \frac{pn - n_i^2}{(n+p) + 2n_i \cosh\left(\frac{E_t - E_i}{kT}\right)}$$

## 【0112】

ここで、 $\sigma$ は電子・正孔の捕獲断面積、 $v_{th}$ はキャリアの熱速度、 $N_t$ はトラップの密度、 $E_t$ はトラップ準位、 $E_i$ は真性フェルミエネルギー、 $n_i$ は真性キャリア密度、 $p$ はp型キャリア密度、 $n$ はn型キャリア密度である。- $U$ はキャリアの生成確率になる。

## 【0113】

$p n > n_i^2$ の場合、 $U$ の確率でキャリアの再結合が起こり、 $p n < n_i^2$ の場合、- $U$ の確率でキャリアの生成が起こる。デバイスがオフの時、チャネル領域は空乏層になっているため、- $U$ の確率でキャリアの生成が起こり、オフ電流を引き起こしていると考えられる。(1)式より、 $N_t$ が大きい、または $E_t$ が $E_i$ に近い値を取る時、キャリアの生成確率が大きくなる。欠陥準位はトラップ準位として作用するので、欠陥を修復し $N_t$ を小さくすれば、オフ電流は低減すると考えられる。

10

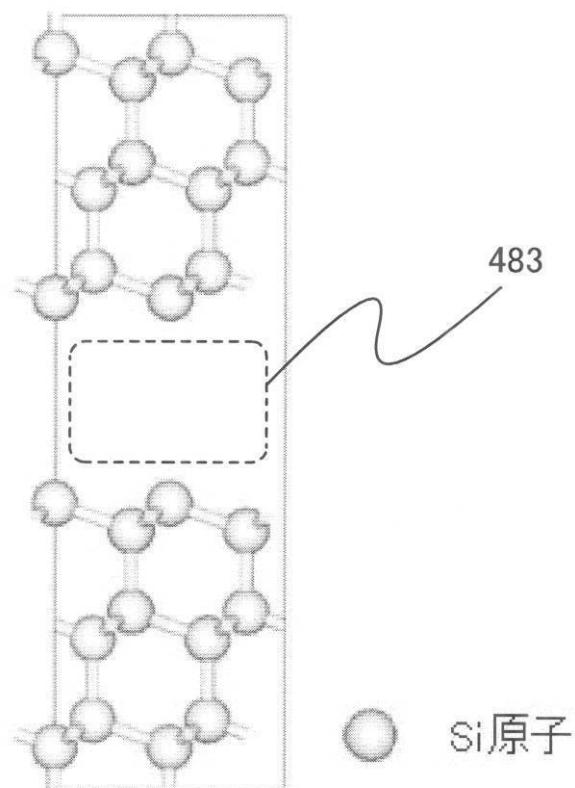

## 【0114】

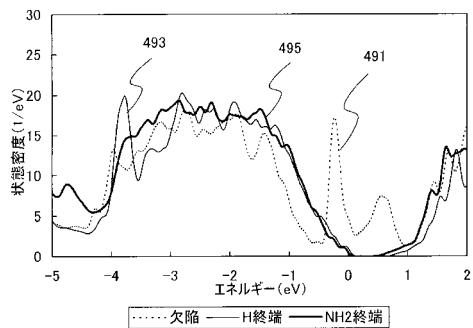

そこで、図48のような、欠陥483のあるSi結晶の欠陥準位とその修復について計算した。具体的には第一原理計算で、欠陥構造、欠陥をH原子で終端したH終端構造、及び欠陥をNH<sub>2</sub>基で終端したNH<sub>2</sub>終端構造、それぞれの原子配置に関して構造最適化を行い、それぞれの電子の状態密度を計算した。汎関数はGGA-PBE、擬ポテンシャルはウルトラソフト型を用いた。

20

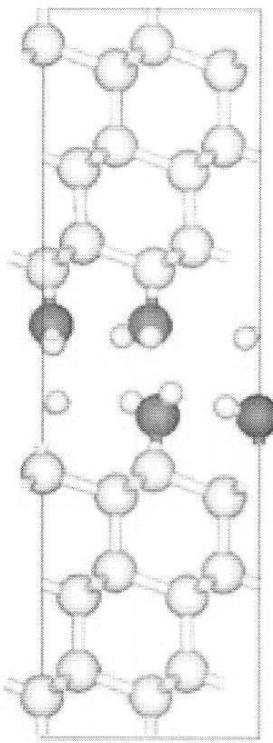

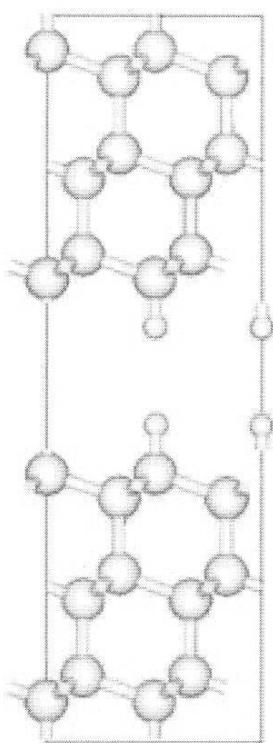

## 【0115】

最適化後の構造それぞれを図49に示す。図49(A)は欠陥構造を示し、図49(B)はH終端構造を示し、図49(C)はNH<sub>2</sub>終端構造を示す。図49(A)はダンギングボンドがあるため、エネルギー的に安定な構造を求めて、欠陥近傍の原子位置が大きく変化している。

## 【0116】

図50に、電子の状態密度を示す。破線491は欠陥構造の電子の状態密度を示し、細実線493はH終端構造の電子の状態密度を示し、太実線495はNH<sub>2</sub>終端構造の電子の状態密度を示す。エネルギーの原点をフェルミエネルギーとした。

30

## 【0117】

図50より、破線491で示すように欠陥構造では、エネルギーが0~1eVあたりのバンドギャップ中に欠陥準位ができている事が分かる。しかしながら、細実線493及び太実線495で示すように、H終端構造及びNH<sub>2</sub>終端構造では欠陥準位が消失しており、欠陥を修復できているといえる。

## 【0118】

即ち、NH<sub>2</sub>終端構造では、欠陥を修復できているため、欠陥に起因するトラップ準位が消失し、(1)式よりオフ電流が低減できるといえる。

## 【0119】

40

## (結合エネルギー)

次に、結合エネルギーについて示す。図50より、NH<sub>2</sub>終端構造では、欠陥準位を低減する事が分かった。しかし、これらが薄膜トランジスタの駆動中においても安定的に欠陥準位を低減し、劣化しないためには、結合が強固である必要がある。そこで、NH<sub>2</sub>終端構造の結合エネルギーを計算し、結合の安定性を比較した。

## 【0120】

図49(B)に示すH終端構造におけるH終端の結合エネルギーは(2)式により計算できる。

## 【0121】

(H終端の結合エネルギー) = (H終端構造からH原子を1つ切り取り、最適化した構造

50

のエネルギー(図51(A)参照) + (Si:H<sub>int</sub>のエネルギー(図51(B)参照)) - (H終端構造のエネルギー(図51(C)参照)) - (Si結晶のエネルギー(図51(D)参照)) (2)

【0122】

Si:H<sub>int</sub>はSi結晶格子間にH原子がある状態を示す。また、始状態(図51(A)及び図51(B))の組成の総和と、終状態(図51(C)及び図51(D))の組成の総和が一致している。

【0123】

NH<sub>2</sub>終端のHの結合エネルギー、NH<sub>2</sub>終端のNH<sub>2</sub>の結合エネルギーに関しても、結合が切れた状態としては、Si結晶の格子間に入った構造を用いる。

10

【0124】

図49(C)に示すNH<sub>2</sub>終端構造におけるH終端の結合エネルギーは(3)式により計算できる。

【0125】

(H終端の結合エネルギー) = (NH<sub>2</sub>終端構造からH原子を1つ切り取り、最適化した構造のエネルギー) + (Si:H<sub>int</sub>のエネルギー) - (NH<sub>2</sub>終端構造のエネルギー) - (Si結晶のエネルギー) (3)

【0126】

図49(C)に示すNH<sub>2</sub>終端構造におけるNH<sub>2</sub>終端の結合エネルギーは(4)式により計算できる。

20

【0127】

(NH<sub>2</sub>終端の結合エネルギー) = (NH<sub>2</sub>終端構造からNH<sub>2</sub>を1つ切り取り、最適化した構造のエネルギー) + (Si:NH<sub>2</sub>のエネルギー) - (NH<sub>2</sub>終端構造のエネルギー) - (Si結晶のエネルギー) (4)

(Si:NH<sub>2</sub>はSi結晶格子間にNH<sub>2</sub>基がある状態を示す。)

【0128】

上記(2)式乃至(4)式の各項の構造は原子配置に対する構造最適化により決定し、エネルギーを計算した。上記(欠陥準位)のシミュレーションと同様に、汎関数はGGA-PBE、擬ポテンシャルはウルトラソフト型を用いた。

30

【0129】

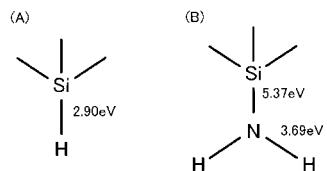

結合エネルギーの計算結果を、構造の模式図とともに図52に示す。図52(A)は、SiのダングリングボンドをHで終端したH終端構造を示し、図52(B)は、SiのダングリングボンドをNH<sub>2</sub>で終端したNH<sub>2</sub>終端構造を示す。H終端構造のSi-H結合エネルギーは2.90eVである。また、NH<sub>2</sub>終端構造のSi-N結合エネルギーは5.37eVであり、N-H結合エネルギーは3.69eVである。NH<sub>2</sub>基の2つの結合エネルギー(Si-N結合エネルギー、N-H結合エネルギー)は、SiのダングリングボンドをH原子で終端したSi-H結合エネルギーよりも大きく、安定な構造であるといえる。このため、シリコン層のダングリングボンドをNH<sub>2</sub>基で終端すると、Siに結合したNH<sub>2</sub>基やNに結合したH原子は解離しにくく、欠陥が生じにくいことが分かる。

【0130】

上記(欠陥準位)及び上記(結合エネルギー)から、Si原子のダングリングボンドがNH<sub>2</sub>基で終端されることで、シリコン層中の欠陥準位を低減し、オフ電流を低減することができることがわかる。また、Siに結合されたNH<sub>2</sub>基は、Siに結合されたH原子と比較して構造が安定であるため、当該シリコン層を有する薄膜トランジスタは、駆動による劣化が生じにくくことが分かる。即ち、非晶質構造の中に結晶領域を有する半導体層としてNH<sub>2</sub>基を有する半導体層をバッファ層として用いることで、薄膜トランジスタのオフ電流を低減することができる。

40

【0131】

(実施の形態2)

本実施の形態では実施の形態1に示す薄膜トランジスタにおいて、半導体層115に用い

50

ることが可能な形態を図9及び図10を用いて示す。

【0132】

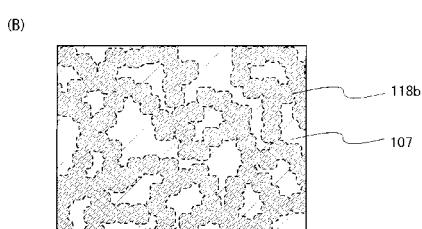

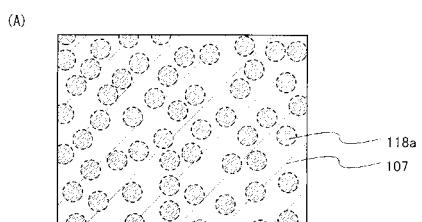

本実施の形態に示す薄膜トランジスタは、ゲート絶縁層107上に分散された微結晶半導体粒子または網状の微結晶半導体118が形成されていることを特徴とする(図9参照)。

【0133】

図10(A)に示す分散された微結晶半導体粒子118a、または図10(B)に示す網状の微結晶半導体118bは、シリコン、またはゲルマニウムより多くのシリコンを含むシリコンゲルマニウム(Si<sub>x</sub>Ge<sub>1-x</sub>、0.5 < x < 1)等で形成することができる。分散された微結晶半導体粒子118aは、図10(A)に示すように、上面形状が円であり、断面形状が図9に示すように半球状である。分散された微結晶半導体粒子の上面から見た直径を、1~30nmとし、密度を $1 \times 10^{13} \text{ cm}^{-3}$ 未満、好ましくは $1 \times 10^{10} \text{ cm}^{-3}$ 未満とすると、堆積のみで、分散された微結晶半導体粒子を形成することができる。

【0134】

また、分散された微結晶半導体粒子の直径は上記大きさに限らず、更に大きくてもよい。

【0135】

また、網状の微結晶半導体118bは、微結晶半導体が部分的に連続している形状をいい、微結晶半導体の連続部は規則的(例えば、格子状、ジグザグ状)でも不規則的でもよい。図10(B)には、不規則に微結晶半導体が連続している上面形状を示す。

【0136】

このような網状の微結晶半導体118bは、ゲート絶縁層107上に非晶質半導体または微結晶半導体を形成した後、非晶質半導体または微結晶半導体が溶融する程度のエネルギーを有するレーザビームを照射して、半導体を溶融した後凝固させることで、部分的に連続している網状の微結晶半導体118bを形成することができる。

【0137】

ゲート絶縁層107及びバッファ層131の間に分散された微結晶半導体粒子または網状の微結晶半導体118を形成することで、バッファ層131とゲート絶縁層107との密着性を高めることができる。このため、薄膜トランジスタの歩留まりを高めることができる。

【0138】

本実施の形態により、非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオン電流を高めると共に、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオフ電流を低減することができる。また、ゲート絶縁層上に分散された微結晶半導体粒子または網状の微結晶半導体を形成することでゲート絶縁層及びバッファ層の密着性が向上するため、歩留まりを高めることができる。

【0139】

(実施の形態3)

本実施の形態では、実施の形態1において、半導体層115を非晶質構造の中に結晶領域を有する半導体層で形成した薄膜トランジスタ、即ちゲート絶縁層とソース領域及びドレイン領域との間に非晶質構造の中に結晶領域を有する半導体層が形成される薄膜トランジスタについて、図11を参照して説明する。

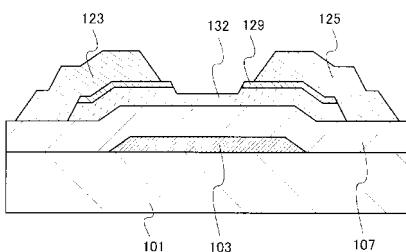

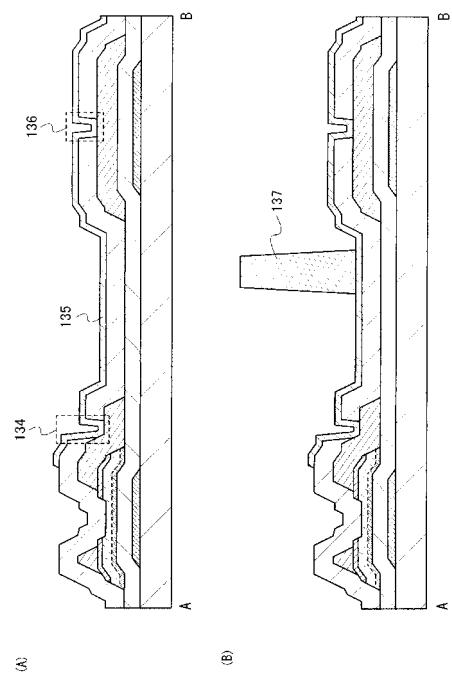

【0140】

図11は、本実施の形態にかかる薄膜トランジスタの断面図を示す。図11に示す薄膜トランジスタは、基板101上にゲート電極層103を有し、ゲート電極層103を覆うゲート絶縁層107を有し、ゲート絶縁層107上に接する半導体層132を有し、半導体層132上の一部に接するソース領域及びドレイン領域129を有する。また、ソース領域及びドレイン領域129上に接する配線層123、125を有する。配線層123、125はソース電極及びドレイン電極を構成する。また、各層は所望の形状にパターン形成

10

20

30

40

50

されている。ここでは、ゲート絶縁層 107 とソース領域及びドレイン領域 129 との間に非晶質構造の中に結晶領域を有する半導体層で形成される半導体層 132 が設けられることを特徴とする。

【0141】

半導体層 132、ソース領域及びドレイン領域 129、並びに配線層 123、125 は、それぞれ実施の形態 1 に示すバッファ層 131、ソース領域及びドレイン領域 129、並びに配線層 123、125 と同様の材料を適宜用いて形成することができる。

【0142】

ここで、本実施の形態の主要な特徴の一つである半導体層 132 について説明する。半導体層 132 は、ゲート絶縁層 107 に接する領域においては、薄膜トランジスタのチャネル形成領域として機能する。ここでは、半導体層 132 を非晶質構造の中に結晶領域を有する半導体層で形成する。ここで、半導体層 132 の構造に関し、図 12 に示す。

【0143】

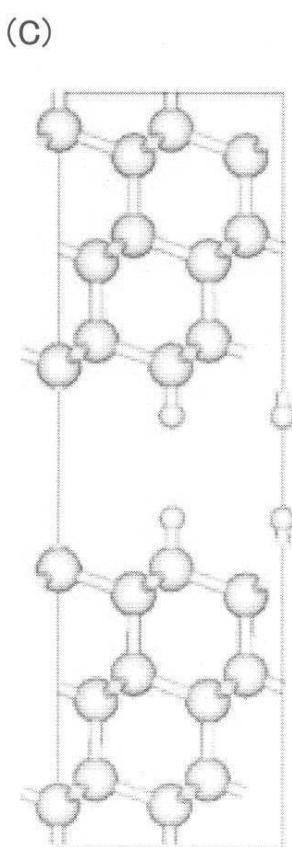

半導体層 132 に用いる非晶質構造の中に結晶領域を有する半導体層は、図 12 (A) に示すように、ゲート絶縁層 107 上に形成された層であり、非晶質構造 132b 中に結晶領域 132a が分散する。

【0144】

結晶領域 132a の形状は、逆錐形である。また、結晶領域 132a 内には単結晶または双晶を含む。

【0145】

非晶質構造の中に結晶領域を有する半導体層に含まれる結晶領域の一形態は、図 12 (B-1) に示すように、結晶領域 132d の頂点がゲート絶縁層 107 と接するように形成し、且つ結晶成長が非晶質構造の中に結晶領域を有する半導体層の堆積方向に連続的に成長している。

【0146】

このような結晶領域は、図 3 (B-1) に示す結晶領域 131d と同様に形成することができる。

【0147】

非晶質構造の中に結晶領域を有する半導体層に含まれる結晶領域の一形態は、図 12 (B-2) に示すように、結晶領域 132e の頂点がゲート絶縁層 107 と接せず、且つ結晶成長が非晶質構造の中に結晶領域を有する半導体層の堆積方向に連続的に成長している。

【0148】

このような結晶領域は、図 3 (B-2) に示す結晶領域 131e と同様に形成することができる。

【0149】

非晶質構造の中に結晶領域を有する半導体層に含まれる結晶領域の一形態は、図 12 (B-3) に示すように、結晶領域 132f の頂点がゲート絶縁層 107 と接するように形成し、且つ結晶成長が非晶質構造の中に結晶領域を有する半導体層の堆積方向の途中で途切れたり、結晶領域 132f 上に非晶質構造が形成される。

【0150】

このような結晶領域は、図 3 (B-3) に示す結晶領域 131f と同様に形成することができる。

【0151】

なお、図 12 (B-3) においては、結晶領域の頂点がゲート絶縁層 107 に接しているが、図 12 (B-2) と同様の条件により、頂点がゲート絶縁層 107 に接せず、且つ堆積方向の途中で成長が途切れた結晶領域となる。

【0152】

非晶質構造の中に結晶領域を有する半導体層に含まれる結晶領域の一形態は、図 12 (B-4) に示すように、堆積方向に対して複数の逆錐形の結晶領域が積み重なった構造 132g となっている。

10

20

30

40

50

## 【0153】

このような結晶領域は、図3(B-4)に示す構造131gの結晶領域と同様に形成することができる。

## 【0154】

なお、図12(B-4)においては、結晶領域の頂点がゲート絶縁層107に接しているが、図12(B-2)と同様の条件により、頂点がゲート絶縁層107に接せしない構造となりうる。

## 【0155】

隣接する結晶領域132aの間には非晶質構造132bが充填されている。即ち、結晶領域132aが離散しており、隣の結晶領域と接していない。このような構造により、ソース領域またはドレイン領域に電圧が印加された時の半導体層132の縦方向における抵抗を下げることが可能であり、薄膜トランジスタのオン電流を高めることができる。

10

## 【0156】

また、半導体層132に用いる非晶質構造の中に結晶領域を有する半導体層は、図12(C)に示すように、非晶質構造132b中に微小結晶粒132cが分散する形態がある。微小結晶粒132cとは上記結晶領域の成長核となれない程度の微小さな大きさ、代表的には1nm以上10nm以下、好ましくは1nm以上5nm以下の微小さな大きさの結晶粒である。微小結晶粒は半導体層132中の窒素の濃度を制御することで形成することができる。また、微小結晶粒の外側、即ち、非晶質構造と接する側には、多くの窒素が偏析しやすい。このため、窒素が微小結晶及び非晶質構造の界面において多く存在する。

20

## 【0157】

なお、半導体層132中において、微小結晶粒132cは、非晶質構造132b中で分散していてもよい。また、半導体層132中において微小結晶粒132cが凝集していてもよい。更には、分散した微小結晶粒132c及び凝集した微小結晶粒132cが存在してもよい。

## 【0158】

また、半導体層132に用いる非晶質構造の中に結晶領域を有する半導体層は、図12(D)に示すように、非晶質構造132b中で結晶領域132a及び微小結晶粒132cが分散する。このような構造により、ソース領域またはドレイン領域に電圧が印加された時の半導体層132の縦方向における抵抗、即ち、ゲート絶縁層107からソース領域またはドレイン領域の間の抵抗を下げることが可能であり、薄膜トランジスタのオン電流を高めることができる。

30

## 【0159】

なお、ここで酸素または窒素等の結晶核の生成を抑制する不純物元素は、シリコン中にあって、キャリアトラップを生成しない不純物元素(例えば、窒素)を選択する。一方、シリコンの配位数を減らし、ダングリングボンドを生成する不純物元素(例えば酸素)の濃度は低減させる。従って、窒素濃度を低減させずして酸素濃度を低減させるとよい。具体的には、酸素については二次イオン質量分析法によって計測される濃度を $5 \times 10^{-8} \text{ cm}^{-3}$ 以下とするとよい。

## 【0160】

40

また、図11に示す薄膜トランジスタの半導体層132は、図13(A)に示すように、非晶質構造131bに、四つの角が直角でない四辺形、代表的にはひし形の結晶領域132hを有する構造とすることができます。このような半導体層132は、半導体層132を2つの異なる条件を用いて形成することができる。

## 【0161】

代表的には、ゲート絶縁層107側に逆錐形の結晶領域を有する半導体層132iが形成され、その上に順錐形の結晶領域を有する半導体層132jが形成される。なお、図13に示す結晶領域132hは、半導体層132の窒素濃度を制御することで形成することができる。

## 【0162】

50

なお、結晶領域 132h の代わりに、図 13 (B-1) に示すように、半導体層 132i が有する結晶領域の頂点がゲート絶縁層 107 と接する形状とすることができます。

【0163】

また、結晶領域 132h の代わりに、図 13 (B-2) に示すように、半導体層 132j が有する結晶領域の頂点がソース領域及びドレイン領域 129 と接する形状とすることができます。

【0164】

また、結晶領域 132h の代わりに、図 13 (B-3) に示すように、半導体層 132i が有する結晶領域の頂点がゲート絶縁層 107 と接し、半導体層 132j が有する結晶領域の頂点がソース領域及びドレイン領域 129 と接する形状とすることができます。

10

【0165】

上記説明したように、結晶領域は離散的に存在する。結晶領域を離散的に存在させるためには、結晶の核生成密度を制御することが必要である。窒素濃度を制御することで、結晶領域の核生成密度を制御し、結晶領域を離散的に存在せしめることが可能である。

【0166】

本実施の形態により、非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオン電流及び電界効果移動度を高めると共に、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオフ電流を低減することができる。

【0167】

20

(実施の形態 4)

本実施の形態では、実施の形態 1 と異なる薄膜トランジスタの形態について、図 14 を参照して説明する。

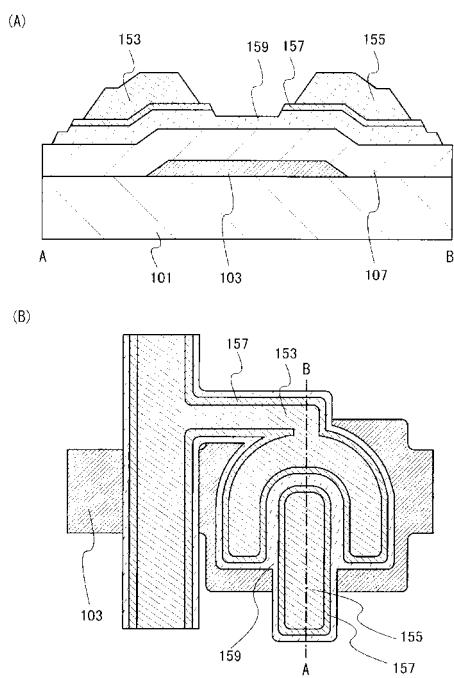

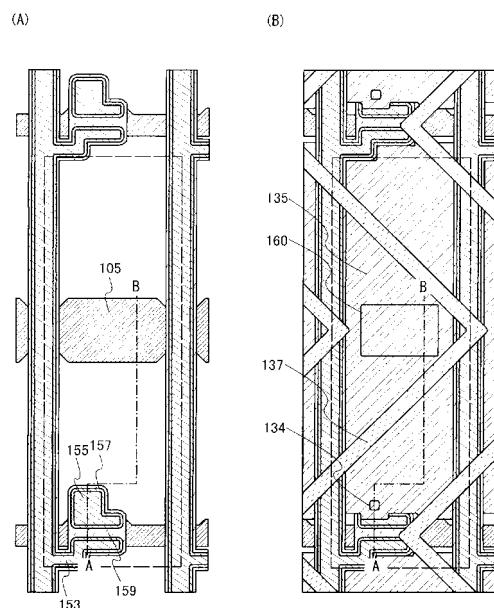

【0168】

本実施の形態にかかる薄膜トランジスタにおいて、図 14 (B) の A - B における断面図を図 14 (A) に示す。図 14 (A) に示す薄膜トランジスタは、基板 101 上にゲート電極層 103 を有し、ゲート電極層 103 を覆うゲート絶縁層 107 を有し、ゲート絶縁層 107 上に接する非晶質構造の中に結晶領域を有する半導体層 159 を有し、非晶質構造の中に結晶領域を有する半導体層 159 上の一部に接するソース領域及びドレイン領域 157 を有する。また、ソース領域及びドレイン領域 157 上に接する配線層 153、155 を有する。配線層 153、155 はソース電極及びドレイン電極を構成する。また、各層は所望の形状にパターン形成されている。

30

【0169】

また、本実施の形態の薄膜トランジスタは、図 14 (B) に示すように上面形状において、配線層 153、155 の外縁にソース領域及びドレイン領域 157 が露出していることを特徴とする。このような構造は、多階調マスクを用いたフォトリソグラフィ工程を用いることにより形成される。

【0170】

非晶質構造の中に結晶領域を有する半導体層 159、ソース領域及びドレイン領域 157、並びに配線層 153、155 は、それぞれ実施の形態 1 に示すバッファ層 131、ソース領域及びドレイン領域 129、並びに配線層 123、125 と同様の材料を適宜用いて形成することができる。

40

【0171】

本実施の形態では、ソース電極及びドレイン電極の一方は、U字型（またはコの字型、馬蹄型）の形状で設けられ、これがソース電極及びドレイン電極の他方を囲い込んでいる。ソース電極とドレイン電極との距離はほぼ一定に保たれている（図 14 (B) を参照）。

【0172】

ソース電極及びドレイン電極の一方を上記した形状とすることで、該薄膜トランジスタのチャネル幅を大きくすることができ、電流量が増大する。また、電気的特性のばらつきを低減することができる。更には、作製工程におけるマスクパターンのずれによる信頼性の

50

低下を抑制することができる。ただし、本実施の形態はこれに限定されず、ソース電極及びドレイン電極の一方は必ずしも I 字型でなく、ソース電極及びドレイン電極の対向部が直線状でもよい。また、実施の形態 1 乃至実施の形態 3 の薄膜トランジスタの上面形態を、本実施の形態と同様にすることができる。

【 0 1 7 3 】

なお、本実施の形態では、ゲート絶縁層と、ソース領域及びドレイン領域との間に、非晶質構造の中に結晶領域を有する半導体層を設けたが、実施の形態 1 及び 2 と同様に、半導体層及びバッファ層を積層してもよい。

【 0 1 7 4 】

本実施の形態により、非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオン電流を高めると共に、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、薄膜トランジスタのオフ電流を低減することができる。

10

【 0 1 7 5 】

( 実施の形態 5 )

本実施の形態では、薄膜トランジスタ及び表示装置の画素部の作製方法について、以下に示す。ここでは、表示装置として液晶表示装置を用いて説明する。薄膜トランジスタでは p 型よりも n 型の方が、キャリアの移動度が高い。また、同一の基板上に形成する薄膜トランジスタを全て同じ導電型に統一すると、工程数を抑えることができ、好ましい。そのため、本実施の形態では、n 型の薄膜トランジスタの作製方法について説明する。

20

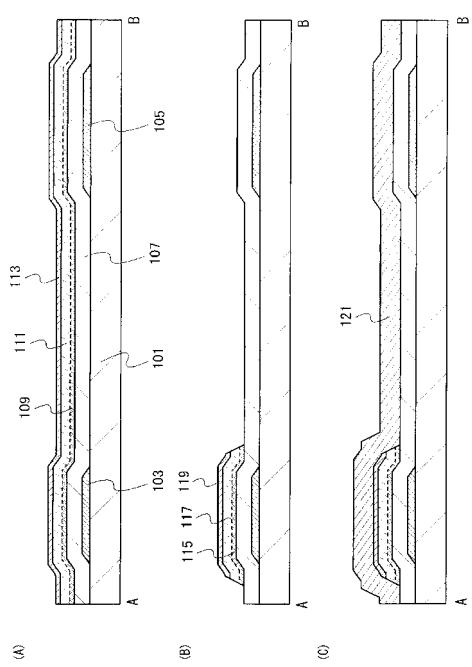

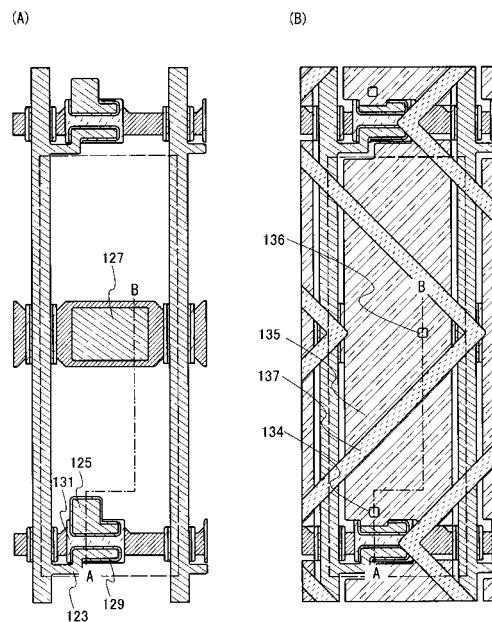

【 0 1 7 6 】

まず、基板 101 上にゲート電極層 103、及び容量配線 105 を形成する（図 15（A）を参照）。

【 0 1 7 7 】

基板 101 としては、実施の形態 1 に示す基板 101 を適宜用いることができる。

【 0 1 7 8 】

ゲート電極層 103、及び容量配線 105 は、実施の形態 1 に示すゲート電極層 103 に示す材料を適宜用いて形成する。ゲート電極層 103、容量配線 105 は、基板 101 上に、スパッタリング法または真空蒸着法を用いて上記した材料により導電層を形成し、該導電層上にフォトリソグラフィ法またはインクジェット法等によりマスクを形成し、該マスクを用いて導電層をエッチングして形成することができる。また、銀、金または銅等の導電性ナノペーストをインクジェット法により基板上に吐出し、焼成することで形成することもできる。なお、上記の金属材料の窒化物層を、基板 101 と、ゲート電極層 103、容量配線 105 との間に設けてもよい。ここでは、基板 101 上に導電層を形成し、第 1 のフォトリソグラフィ工程により形成したレジストマスクにより該導電層をエッチングして、ゲート電極層 103 及び容量配線 105 を形成する。

30

【 0 1 7 9 】

なお、ゲート電極層 103、及び容量配線 105 の側面をテーパー形状とすることで、ゲート電極層 103、容量配線 105 上に形成する半導体層及び配線層の段差の箇所における配線切れを防止することができる。ゲート電極層 103、及び容量配線 105 の側面をテーパー形状にするためには、レジストマスクを後退させつつエッチングを行えばよい。例えば、エッチングガスに酸素ガスを含ませることでレジストマスクを後退させつつエッチングを行うことが可能である。

40

【 0 1 8 0 】

また、ゲート電極層 103 を形成する工程によりゲート配線（走査線）及び容量配線 105 も同時に形成することができる。なお、走査線とは画素を選択する配線をいい、容量配線とは画素の保持容量の一方の電極に接続された配線をいう。ただし、これに限定されず、ゲート配線及び容量配線の一方または双方と、ゲート電極層 103 とは別に設けてよい。

【 0 1 8 1 】

50

次に、ゲート電極層 103 を覆ってゲート絶縁層 107、半導体層 109、バッファ層 111、及び不純物半導体層 113 を形成する。

【0182】

ゲート絶縁層 107 は、実施の形態 1 に示すゲート絶縁層 107 の材料を適宜用いて形成することができる。ゲート絶縁層 107 は、CVD 法またはスパッタリング法等を用いて形成することができる。ゲート絶縁層 107 の CVD 法による形成工程においてグロー放電プラズマの生成は、3 MHz から 30 MHz、代表的には 13.56 MHz、27.12 MHz の高周波電力、または 30 MHz より大きく 300 MHz 程度までの VHF 帯の高周波電力、代表的には 60 MHz を印加することで行われる。また、ゲート絶縁層 107 は、高周波数 (1 GHz 以上) のマイクロ波プラズマ CVD 装置を用いて形成してもよい。マイクロ波プラズマ CVD 装置を用いて高い周波数によりゲート絶縁層 107 を形成すると、ゲート電極と、ドレイン電極及びソース電極との間の耐圧を向上させることができため、信頼性の高い薄膜トランジスタを得ることができる。

【0183】

半導体層 109 は、3 nm 以上 100 nm 以下、好ましくは 5 nm 以上 50 nm 以下の厚さで形成するとよい。

【0184】

半導体層 109 は、プラズマ CVD 装置の反応室内において、シリコンまたはゲルマニウムを含む堆積性気体と、水素とを混合し、グロー放電プラズマにより、微結晶半導体層を形成する。シリコンまたはゲルマニウムを含む堆積性気体の流量に対して、水素の流量を 10 ~ 2000 倍、好ましくは 50 ~ 200 倍に希釈して微結晶半導体層を形成する。なお、微結晶半導体層は、異なる 2 以上の条件で形成してもよい。例えば、第 1 の条件で微結晶半導体層の一部を形成した後、第 1 の条件より希釈率の低い条件で微結晶半導体層の他部を形成することができる。または、第 1 の条件で微結晶半導体層の一部を形成した後、第 1 の条件より希釈率の高い条件で微結晶半導体層の他部を形成することができる。

【0185】

また、シリコンまたはゲルマニウムを含む堆積性気体の代表例としては、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、GeH<sub>4</sub>、Ge<sub>2</sub>H<sub>6</sub> 等がある。

【0186】

次に、バッファ層 111 の形成方法について説明する。

【0187】

バッファ層 111 は、上記実施の形態で示したように、非晶構造の中に微小結晶粒及び/または錐形状の結晶領域を有する。微小結晶粒及び錐形状の結晶領域は、例えば、バッファ層 111 の酸素濃度を低くし、窒素濃度を酸素濃度よりも高くし、且つ窒素濃度を制御することで、結晶領域の核生成を制御しつつ形成することができる。ここで、窒素濃度は酸素濃度よりも一桁以上高いことが好ましい。より具体的には、二次イオン質量分析法によって計測される酸素の濃度を  $5 \times 10^{-8} \text{ cm}^{-3}$  以下とする。また、窒素の濃度を  $1 \times 10^{-2} \text{ cm}^{-3}$  以上  $1 \times 10^{-1} \text{ cm}^{-3}$  以下、好ましくは  $2 \times 10^{-2} \text{ cm}^{-3}$  以上  $1 \times 10^{-1} \text{ cm}^{-3}$  以下とする。バッファ層 131 は、50 ~ 350 nm、または 120 ~ 250 nm の厚さで形成することが好ましい。

【0188】

本実施の形態では、ゲート絶縁層 107 として、窒化シリコン層上に酸化窒化シリコン層を積層した構造とし、半導体層 109 として、微結晶シリコン層を形成し、微結晶半導体層をアンモニアに曝すことで、半導体層 109 表面に窒素を供給し、バッファ層の窒素濃度を制御する。

【0189】

ここで、ゲート絶縁層 107、半導体層 109、バッファ層 111、並びに不純物半導体層 113 の形成の一例について詳細に説明する。これらの層は CVD 法等を用いて形成する。また、ゲート絶縁層 107 は、窒化シリコン層上に酸化窒化シリコン層を設けた積層構造とする。このような構造とすることで、窒化シリコン層により基板中に含まれる電気

10

20

30

40

50

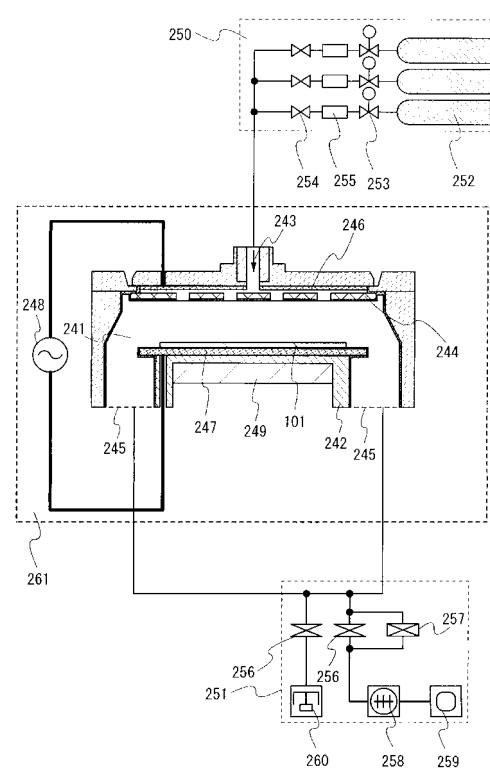

的特性に影響を及ぼす元素（基板がガラスである場合にはナトリウム等の元素）が、半導体層109等に侵入することを防止することができる。図19は、これらを形成するに際して用いるCVD装置の模式図を示す。

【0190】

図19に示すプラズマCVD装置261は、ガス供給手段250及び排気手段251に接続されている。

【0191】

図19に示すプラズマCVD装置261は、処理室241と、ステージ242と、ガス供給部243と、シャワープレート244と、排気口245と、上部電極246と、下部電極247と、交流電源248と、温度制御部249と、を具備する。

10

【0192】

処理室241は剛性のある素材で形成され、内部を真空排気できるように構成されている。処理室241には、上部電極246と下部電極247が備えられている。なお、図19では、容量結合型（平行平板型）の構成を示しているが、異なる二以上の高周波電力を印加して処理室241の内部にプラズマを生成できるものであれば、誘導結合型など他の構成を適用してもよい。

【0193】

図19に示すプラズマCVD装置により処理を行う際には、所定のガスをガス供給部243から処理室241に供給する。供給されたガスは、シャワープレート244を通って、処理室241に導入される。上部電極246と下部電極247に接続された交流電源248により、高周波電力が印加されて処理室241内のガスが励起され、プラズマが生成される。また、真空ポンプに接続された排気口245によって、処理室241内のガスが排気されている。また、温度制御部249によって、被処理物を加熱しながらプラズマ処理することができる。

20

【0194】

ガス供給手段250は、反応ガスが充填されるシリンドラ252、圧力調整弁253、ストップバルブ254、マスフローコントローラ255などで構成されている。処理室241内において、上部電極246と基板101との間には板状に加工され、複数の細孔が設けられたシャワープレート244を有する。上部電極246に供給される反応ガスは、中空構造であるシャワープレート244の細孔から処理室241内に供給される。

30

【0195】

処理室241に接続される排気手段251には、真空排気と、反応ガスを流す場合において処理室241内を所定の圧力に保持するように制御する機能が含まれている。排気手段251の構成としては、バタフライバルブ256、コンダクタンスバルブ257、ターボ分子ポンプ258、ドライポンプ259などが含まれる。バタフライバルブ256とコンダクタンスバルブ257を並列に配置する場合には、バタフライバルブ256を閉じてコンダクタンスバルブ257を動作させることで、反応ガスの排気速度を制御して処理室241の圧力を所定の範囲に保つことができる。また、コンダクタンスの大きいバタフライバルブ256を開くことで高真空排気が可能となる。

40

【0196】

なお、処理室241を $10^{-5}$ Paよりも低い圧力まで超高真空排気する場合には、クライオポンプ260を併用することが好ましい。その他、到達真空度として超高真空まで排気する場合には、処理室241の内壁を鏡面加工し、内壁からのガス放出を低減するためにベーキング用のヒータを設けても良い。

【0197】

なお、図19に示すように、処理室241の全体を覆って層が形成（被着）されるようにプレコート処理を行うと、処理室（チャンバー）内壁に付着した不純物元素、または処理室（チャンバー）内壁を構成する不純物元素が素子に混入することを防止することができる。本実施の形態では、プレコート処理はシリコンを主成分とする層を形成すればよく、例えば、非晶質シリコン層等を形成すればよい。ただし、この層には酸素が含まれないこ

50

とが好ましい。

【0198】

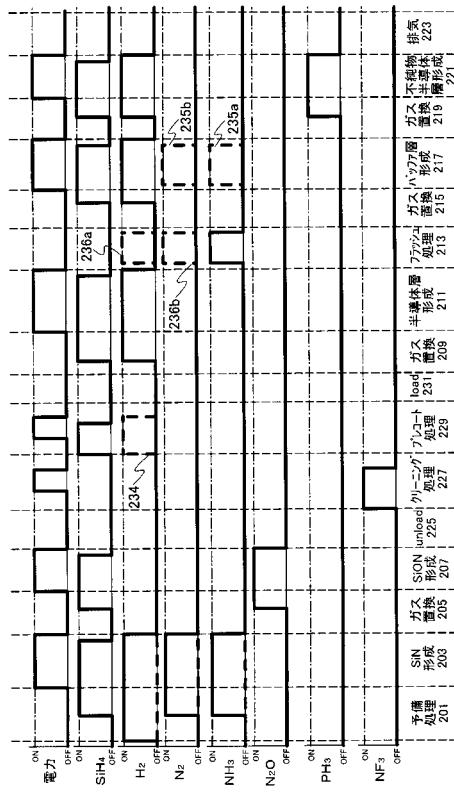

ゲート絶縁層107の形成から不純物半導体層の形成までについて、図20を参照して以下に説明する。なお、ゲート絶縁層107は、窒化シリコン層上に酸化窒化シリコン層を積層して形成する。

【0199】

まず、ゲート電極層103が形成された基板をCVD装置の処理室241内にて加熱し、窒化シリコン層を形成するために、窒化シリコン層の堆積に用いる材料ガスを処理室241内に導入する(図20の予備処理201)。はじめに、プラズマCVD法により厚さ110nmの窒化シリコン層を形成する。このときの堆積条件を以下に示す。材料ガスを、流量40sccmのSiH<sub>4</sub>、流量500sccmのH<sub>2</sub>、流量550sccmのN<sub>2</sub>、及び流量140sccmのNH<sub>3</sub>とし、処理室内の圧力を100Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を370Wとしてプラズマ放電を行う。その後、SiH<sub>4</sub>の供給のみを停止して数秒後にプラズマの放電を停止させる(図20のSiN形成203)。処理室内にSiH<sub>4</sub>が存在する状態でプラズマの放電を停止させると、シリコンを主成分とする粒状物または粉状物が形成され、歩留まりを低下させる原因となるためである。

【0200】

次に、窒化シリコン層の堆積に用いた材料ガスを排気し、酸化窒化シリコン層の堆積に用いる材料ガスを処理室241内に導入する(図20のガス置換205)。ここでは、厚さ110nmの酸化窒化シリコン層を形成する。このときの堆積条件を以下に示す。原料ガスを、流量30sccmのSiH<sub>4</sub>、及び流量1200sccmのN<sub>2</sub>Oとし、処理室内の圧力を40Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を50Wとしてプラズマ放電を行う。その後、窒化シリコン層と同様に、SiH<sub>4</sub>の導入のみを停止し、その数秒後にプラズマの放電を停止させる(図20のSiON形成207)。

【0201】

上記の工程により、ゲート絶縁層107を形成することができる。ゲート絶縁層107の形成後、基板101を処理室241から搬出する(図20のunload225)。

【0202】

基板101を処理室241から搬出した後、処理室241に、例えばNF<sub>3</sub>ガスを導入し、処理室241内をクリーニングする(図20のクリーニング処理227)。その後、処理室241に非晶質シリコン層を形成する処理を行う(図20のプレコート処理229)。後に説明するバッファ層111の形成と同様に行うが、破線234に示すように水素は処理室241内に導入してもよい。または、導入しなくてもよい。この処理により、処理室241の内壁に非晶質シリコン層が形成される。その後、基板101を処理室241内に搬入する(図20のload231)。

【0203】

次に、半導体層109の堆積に用いる材料ガスを処理室241内に導入する(図20のガス置換209)。次に、ゲート絶縁層107上に半導体層109を形成する。半導体層109は、後の工程でパターン形成されて半導体層115となるものである。ここでは、半導体層109として、厚さ50nmの微結晶シリコン層を形成する。このときの堆積条件を以下に示す。材料ガスを、流量10sccm SiH<sub>4</sub>、及び流量1500sccmのH<sub>2</sub>とし、処理室内の圧力を280Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を50Wとしてプラズマ放電を行う。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub>の供給のみを停止し、その数秒後にプラズマの放電を停止させる(図20の半導体層形成211)。

【0204】

次に、半導体層109の表面に窒素を供給する。ここでは、半導体層109の表面をアンモニアガスに曝すことで窒素を供給する(ここでは、フラッシュ処理という)(図20の

10

20

30

40

50

フラッシュ処理 213)。また、アンモニアガスには、破線 236a で示すように水素を含ませてもよい。または、アンモニアガスの代わりに破線 236b で示すように窒素ガス及び破線 236a で示すように水素ガスを用いてもよい。または、アンモニアガス及び窒素ガスを用いてもよい。ここでは、一例として、処理室 241 内の圧力は概ね 20 Pa ~ 30 Pa、基板の温度は 280 とし、処理時間は 60 秒間とするよ。また、フラッシュ処理の後に、処理室内を減圧または加圧して圧力を制御して、処理室 241 内の窒素の量を制御してもよい。なお、本工程の処理では基板 101 をアンモニアガスに曝すのみであるが、プラズマ処理を行ってもよい。その後、これらのガスを排気し、バッファ層 111 の堆積に用いるガスを導入する(図 20 のガス置換 215)。

## 【0205】

10

次に、半導体層 109 上にバッファ層 111 を形成する。バッファ層 111 は、後の工程でパターン形成されてバッファ層 131 となるものである。ここでは、バッファ層として、厚さ 55 nm の非晶質構造に結晶領域を有する半導体層を用いて形成する。このときの堆積条件を以下に示す。材料ガスを、流量 20 sccm の SiH<sub>4</sub>、及び流量 1500 sccm の H<sub>2</sub> とし、処理室内の圧力を 280 Pa、基板の温度を 280 とし、50 W の出力によりプラズマ放電を行う。当該工程において、フラッシュ処理により反応室内に導入されたアンモニアガスがプラズマ放電により分解され、バッファ層 111 に窒素を添加することができる。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub> の供給のみを停止し、その数秒後にプラズマの放電を停止させる(図 20 のバッファ層形成 217)。その後、これらのガスを排気し、不純物半導体層 113 の堆積に用いるガスを導入する(図 20 のガス置換 219)。

## 【0206】

20

なお、フラッシュ処理により反応室内に導入されたアンモニアがプラズマ放電により分解され、NH 基、または NH<sub>2</sub> 基が生成される。また、バッファ層が堆積される際に、非晶質構造に結晶領域を有する半導体層の異なるダングリングボンドが架橋される場合がある。または、非晶質構造に結晶領域を有する半導体層に含まれるダングリングボンドが終端される場合がある。なお、反応室に窒素を含有するガスとして、窒素ガスを導入した場合は、プラズマ放電により、当該窒素ガスと、非晶質構造に結晶領域を有する半導体層の原料ガスである、水素ガスとが反応し NH 基または NH<sub>2</sub> 基を生成する。また、当該 NH 基により非晶質構造に結晶領域を有する半導体層の異なるダングリングボンドが架橋される場合がある。または、非晶質構造に結晶領域を有する半導体層に含まれるダングリングボンドが終端される場合がある。

30

## 【0207】

上記の例において、バッファ層 111 の形成に用いられる材料ガスでは、SiH<sub>4</sub> の流量に対する H<sub>2</sub> の流量を 150 倍としている。そのため、シリコンは徐々に堆積される。

## 【0208】

40

本実施の形態における半導体層 109 の表面には窒素が供給されている。上記したように、窒素はシリコンの結晶核の生成を抑制する。そのため、堆積の初期段階ではシリコンの結晶核が生成されにくい。バッファ層 111 の堆積は窒素の濃度を低下させつつ進み、窒素の濃度が一定の値以下となると、結晶核が形成される。その後、その結晶核が成長し、錐形状の結晶領域が形成される。または微小結晶粒が形成される。

## 【0209】

このような方法により形成したバッファ層 111 において、二次イオン質量分析法によって計測される窒素濃度は、半導体層 109 との界面でピーク濃度を有し、半導体層 109 が堆積するにつれ、窒素濃度が低減する。

## 【0210】

50

なお、図 20 の破線 235a に示すように、バッファ層形成 217 において、アンモニアガスを反応室内に流してもよい。または、アンモニアガスの代わりに破線 235b に示すように窒素ガスを反応室内に流しても良い。または、アンモニアガス及び窒素ガスを反応室内に流しても良い。この結果、バッファ層 111 の窒素濃度が高まる。この結果、結晶領

域として微小結晶粒または逆錐状の結晶領域が形成される。なお、当該工程において、順錐形の結晶領域が形成される場合もある。

#### 【0211】

このような方法により形成したバッファ層111において、二次イオン質量分析法によって計測される窒素濃度は、半導体層109との界面でピーク濃度を有し、半導体層109の堆積方向に対して一定な濃度となる。

#### 【0212】

次に、バッファ層111上に不純物半導体層113を形成する。不純物半導体層113は、後の工程でパターン形成されてソース領域及びドレイン領域129となるものである。ここでは、不純物半導体層113として、厚さ50nmのリンが添加されたアモルファスシリコン層を形成する。このときの堆積条件を以下に示す。材料ガスを、流量100sccmのSiH<sub>4</sub>、及び流量170sccmの0.5%フォスфин(水素希釈)とし、堆積温度を280、圧力170Pa、RF電源周波数を13.56MHz、RF電源の電力を60Wとしてプラズマ放電を行う。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub>の供給のみを停止し、その数秒後にプラズマの放電を停止させる(図20の不純物半導体層形成221)。その後、これらのガスを排気する(図20の排気223)。

#### 【0213】

以上説明したように、不純物半導体層113までを形成することができる(図15(A)を参照)。

#### 【0214】

次に、第2のフォトリソグラフィ工程により形成したレジストマスクを用いて、半導体層109、バッファ層111、及び不純物半導体層113をエッチングして、半導体層115、バッファ層117及び不純物半導体層119を形成する(図15(B)を参照)。その後、レジストマスクを除去する。

#### 【0215】

次に、半導体層115、バッファ層117及び不純物半導体層119を覆う導電層121を形成する(図15(C)を参照)。

#### 【0216】

導電層121は、実施の形態1に示す配線層123、125の材料及び積層構造を適宜用いることができる。導電層121は、CVD法、スパッタリング法または真空蒸着法を用いて形成する。また、導電層121は、銀、金または銅等の導電性ナノペーストを用いてスクリーン印刷法またはインクジェット法等を用いて配置し、焼成することで形成しても良い。その後、導電層121上にレジストマスクを形成する。

#### 【0217】

次に、第3のフォトリソグラフィ工程により形成したレジストマスクを用いて導電層121をエッチングして配線層123、125、容量電極127を形成する(図16(A)を参照)。配線層123、125は、ソース電極及びドレイン電極を構成する。導電層121のエッチングは、ウエットエッチングを用いることが好ましい。ウエットエッチングにより、導電層が等方的にエッチングされる。その結果、導電層はレジストマスクよりも内側に後退し、配線層123、125が形成される。従って、配線層123、125の側面と、エッチングされたソース領域及びドレイン領域129の側面は一致せず、配線層123、125の側面の外側に、ソース領域及びドレイン領域の側面が形成される。配線層123、125は、ソース電極及びドレイン電極のみならず信号線としても機能する。ただし、これに限定されず、信号線と配線層123、125とは別に設けてもよい。

#### 【0218】

次に、第3のフォトリソグラフィ工程により形成したレジストマスクを用いてエッチングされたバッファ層117の一部と、不純物半導体層119をエッチングする(図16(B)参照)。本工程まで半導体層115、バッファ層131、並びにソース領域及びドレイン領域129が形成される。この後、レジストマスクを除去する。このときの図16(

10

20

30

40

50

B)の上面図を図18(A)に示す。

【0219】

次に、ドライエッティングを行うとよい。ドライエッティングの条件は、露出しているバッファ層131にダメージが入らず、且つバッファ層131に対するエッティングレートが低い条件を用いる。つまり、露出しているバッファ層131表面にほとんどダメージを与えず、且つ露出しているバッファ層131の厚さがほとんど減少しない条件を用いる。エッティングガスとしては、塩素系ガスを用い、代表的にはCl<sub>2</sub>ガスを用いる。また、エッティング方法については特に限定はなく、誘導結合型プラズマ( I C P : I n d u c t i v e l y C o u p l e d P l a s m a ) 方式、容量結合型プラズマ( C C P : C a p a c i t i v e l y C o u p l e d P l a s m a ) 方式、電子サイクロトロン共鳴プラズマ( E C R : E l e c t r o n C y c l o t r o n R e s o n a n c e ) 方式、反応性イオンエッティング( R I E : R e a c t i v e I o n E t c h i n g ) 方式等を用いることができる。

【0220】

ここで、用いることのできるドライエッティング条件の一例として、Cl<sub>2</sub>ガスの流量を100 sccm、チャンバー内の圧力を0.67 Pa、下部電極温度を-10°とし、上部電極のコイルに2000 WのRF(13.56 MHz)電力を投入してプラズマを生成し、基板101側には電力を投入せず0 W(すなわち、無バイアスとして)として、30秒間のエッティングを行う。チャンバー内壁の温度は約80°とすることが好ましい。

【0221】

次に、バッファ層131の表面に水プラズマ、アンモニアプラズマ、窒素プラズマ等を照射してもよい。

【0222】

水プラズマ処理は、反応空間に水蒸気(H<sub>2</sub>O蒸気)に代表される、水を主成分とするガスを導入し、プラズマを生成して、行うことができる。

【0223】

上記したように、一対のソース領域及びドレイン領域129を形成した後に、バッファ層131にダメージを与えない条件で更なるドライエッティングを行うことで、露出したバッファ層131上に存在する残渣などの不純物元素を除去することができる。また、ドライエッティングに続けて水プラズマ処理を行うことで、レジストマスクの残渣を除去することができる。水プラズマ処理を行うことで、ソース領域とドレイン領域との間の絶縁を確実なものにすことができ、完成する薄膜トランジスタのオフ電流を低減し、オン電流を向上させ、電気的特性のばらつきを低減することができる。

【0224】

なお、プラズマ処理等の工程は上記の順番に限定されず、レジストマスクを除去する前に、無バイアスでのエッティングや、プラズマ処理を行ってもよい。

【0225】

以上の工程により本実施の形態に係る薄膜トランジスタを作製することができる。本実施の形態に係る薄膜トランジスタは、実施の形態1にて説明した薄膜トランジスタと同様に、液晶表示装置に代表される表示装置の画素におけるスイッチングトランジスタに適用することができる。そのため、この薄膜トランジスタを覆って、絶縁層133を形成する。

【0226】

次に、絶縁層133に開口部134、136を形成する。この開口部134、136は、第4のフォトリソグラフィ工程により形成したレジストマスクを用いて絶縁層の一部をエッティングして、形成することができる。なお、絶縁層133が感光性樹脂で形成される場合は、第4のフォトリソグラフィ工程により絶縁層133を形成することができる。その後、当該開口部134、136を介して接続されるように、絶縁層133上に画素電極層135を設ける。このようにして図17(A)に示す表示装置の画素におけるスイッチングトランジスタを作製することができる。

【0227】

10

20

30

40

50

なお、絶縁層 133 は、ゲート絶縁層 107 と同様に形成することができる。さらには、絶縁層 133 は、大気中に浮遊する有機物、金属または水蒸気等の汚染源となりうる不純物元素の侵入を防ぐことができるよう、緻密な窒化シリコン層により設けることが好ましい。

【0228】

なお、画素電極層 135 は、透光性を有する導電性高分子（導電性ポリマーともいう。）を含む導電性組成物を用いて形成することができる。画素電極層 135 は、シート抵抗が 10000 / 以下であって、且つ波長 550 nm における透光率が 70 % 以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が 0.1 · cm 以下であることが好ましい。

10

【0229】

導電性高分子としては、いわゆる 電子共役系導電性高分子を用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、またはこれらの 2 種以上の共重合体等が挙げられる。

【0230】

画素電極層 135 は、例えば、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物（以下、ITO と示す。）、インジウム亜鉛酸化物、または酸化シリコンを添加したインジウム錫酸化物等を用いて形成することができる。

20

【0231】

画素電極層 135 は、配線層 123、125 等と同様に、第 5 のフォトリソグラフィ工程により形成したレジストマスクを用いてエッチングを行い、パターン形成すればよい。

【0232】

なお、図示していないが、絶縁層 133 と画素電極層 135 との間に、スピンドーティング法等により形成した有機樹脂からなる絶縁層を有していても良い。また、当該有機樹脂からなる絶縁層を感光性樹脂を用いて形成することで工程数を削減することができる。

【0233】

この後、VA (Vertical Alignment) 方式の液晶表示装置において、視野角拡大のために、画素を複数部分に分割し、分割された画素の各部分の液晶の配向を異ならせるマルチドメイン方式（いわゆる MVA 方式）の場合、画素電極層 135 上に突起物 137 を形成することができる。突起物 137 は、絶縁層で形成する。このときの図 17 (B) の上面図を図 18 (B) に示す。

30

【0234】

ここでは、感光性アクリルを含む組成物を塗布して厚さ 0.9 ~ 1.0 μm の組成物層を形成した後、90 ° で 120 秒加熱して組成物層を乾燥させる。次に、フォトマスクを用いて組成物層を露光した後現像して、所定の形状とする。次に、230 ° で 1 時間加熱して、アクリル樹脂層で形成される突起物 137 を形成する。

【0235】

画素電極層上に突起物 137 が形成されると、画素電極の電圧がオフの時には、液晶が配向膜表面に対して垂直に配向するが、突起部近傍の液晶は基板面に対してわずかに傾斜した配向となる。画素電極層の電圧がオンとなると、まず傾斜配向部の液晶が傾斜する。また、突起部近傍以外の液晶もこれらの液晶の影響を受け、順次同じ方向へと配列する。この結果、画素全体に対して安定した配向が得られる。即ち、突起物を起点として表示部全体の配向が制御される。

40

【0236】

また、画素電極層上に突起物を設ける代わりに、画素電極にスリットを設けてよい。この場合、電圧を画素電極層に印加すると、スリット近傍には電界の歪が生じ、突起物を画素電極層上に設けた場合と同様の電界分布及び液晶配向の制御が可能である。

【0237】

50

以上の工程により、非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、オン電流が高く、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、オフ電流の低い薄膜トランジスタを有し、且つ液晶表示装置に用いることが可能な素子基板を作製することができる。

【0238】

(実施の形態6)

本実施の形態では、実施の形態5に適用可能なバッファ層の形成工程について説明する。

【0239】

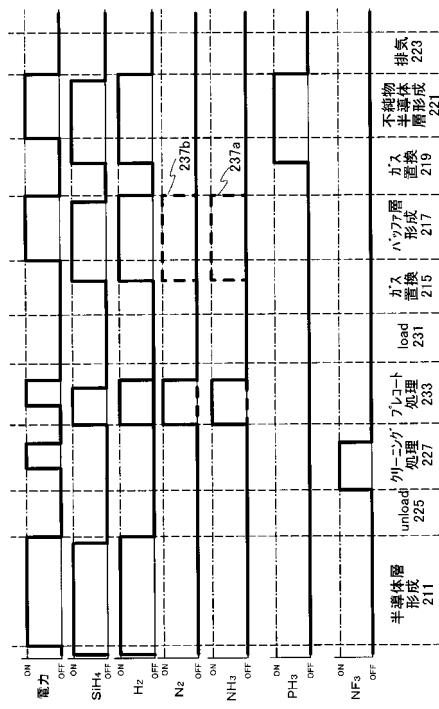

本実施の形態では、バッファ層111の堆積前に処理室内をクリーニングし、その後窒化シリコン層によりチャンバー内壁を覆うことでバッファ層111に窒素を含ませて、酸素濃度を低く抑え、バッファ層111の窒素濃度を酸素濃度よりも高くする。ゲート絶縁層107の形成から半導体層109の形成方法は実施の形態5と同様であるため、ここでは、半導体層109から不純物半導体層113の形成までについて、図21を参照して以下に説明する。

10

【0240】

ゲート絶縁層107上に半導体層109を形成する。半導体層109は、後の工程でパターン形成されて半導体層115となるものである。まず、半導体層109の堆積に用いる材料ガスを処理室内に導入する。ここでは、一例として、実施の形態5と同様の方法により、半導体層109として約50nmの微結晶半導体層を形成する。その後、プラズマの放電を停止させる(図21の半導体層形成211)。その後、基板101を処理室241から搬出する(図21のunload225)。

20

【0241】

基板101を処理室241から搬出した後、処理室241に、例えばNF<sub>3</sub>ガスを導入し、処理室241内をクリーニングする(図21のクリーニング処理227)。その後、処理室241に窒化シリコン層を形成する処理を行う(図21のプレコート処理233)。窒化シリコン層としては、実施の形態5のゲート絶縁層で形成した窒化シリコン層と同様の条件を用いる。この処理により、処理室241の内壁に窒化シリコン層が形成される。その後、基板101を処理室241内に搬入する(図21のload231)。

【0242】

次に、バッファ層111の堆積に用いる材料ガスを処理室241内に導入する(図21のガス置換215)。次に、半導体層109上の全面にバッファ層111を形成する。バッファ層111は、後の工程でパターン形成されてバッファ層131となるものである。ここで、バッファ層は、実施の形態5と同様の方法により、約80nmの非晶質構造の中に結晶領域を有する半導体層を形成することができる。その後、プラズマの放電を停止させる(図21のバッファ層形成217)。その後、これらのガスを排気し、不純物半導体層113の堆積に用いるガスを導入する(図21のガス置換219)。また、実施の形態5と同様に、不純物半導体層113を形成する(図21の不純物半導体層形成221)。

30

【0243】

本実施の形態における処理室241の表面には窒化シリコン層が形成されている。バッファ層111の形成工程において、処理室241内に形成された窒化シリコン層がプラズマに曝されると、窒素が解離し、バッファ層111の堆積初期に、窒素を混入させることができる。

40

【0244】

なお、バッファ層111の形成工程において、処理室241内に形成された窒化シリコン層がプラズマに曝されると、窒素、好ましくはNH基またはNH<sub>2</sub>基が解離し、バッファ層111の堆積初期に、窒素、好ましくはNH基またはNH<sub>2</sub>基を混入させることができる。さらには、非晶質半導体層が堆積される際に非晶質半導体層の異なるダングリングボンドを架橋する場合がある。また、非晶質半導体層が堆積される際に非晶質半導体層のダングリングボンドを終端する場合がある。

【0245】

50

このような方法により形成したバッファ層 111において、二次イオン質量分析法によって計測される窒素濃度は、半導体層 109との界面でピーク濃度を有し、半導体層 109が堆積するにつれ、窒素濃度が低減する。

【0246】

上記説明したように、少なくとも半導体層を形成する直前に処理室の内壁を窒化シリコン層により覆うことで、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くすることが可能であり、非晶質構造の中に結晶領域を含む半導体層を形成することができる。

【0247】

また、処理室の内壁を窒化シリコン層で覆うことで、処理室の内壁を構成する元素等がバッファ層に混入することをも防ぐことができる。

10

【0248】

なお、図 21 の破線 237a に示すように、バッファ層形成 217において、アンモニアガスを反応室内に流してもよい。または、アンモニアガスの代わりに破線 237b に示すように窒素ガスを用いてもよい。さらには、アンモニアガス及び窒素ガスを用いてもよい。この結果、バッファ層 111 の窒素濃度が高まる。この結果、結晶領域として微小結晶粒または / 及び錐形状の結晶領域が形成される。

【0249】

このような方法により形成したバッファ層 111において、二次イオン質量分析法によって計測される窒素濃度は、半導体層 109との界面でピーク濃度を有し、半導体層 109の堆積方向に対して一定な濃度となる。

20

【0250】

なお、上記の説明では、半導体層 109を形成した処理室と同様の処理室でバッファ層 111を形成したため、半導体層 109の形成後にクリーニング処理とプレコート処理を行う形態について説明したが、本実施の形態は、実施の形態 5と組み合わせて実施してもよい。すなわち、半導体層 109を堆積し、クリーニング処理 227、及びプレコート処理 233をして、処理室 241に窒化シリコン層を形成した後、フラッシュ処理 213してもよい。

【0251】

以上の工程により、非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、オン電流が高く、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、オフ電流の低い薄膜トランジスタを作製することができる。

30

【0252】

(実施の形態 7)

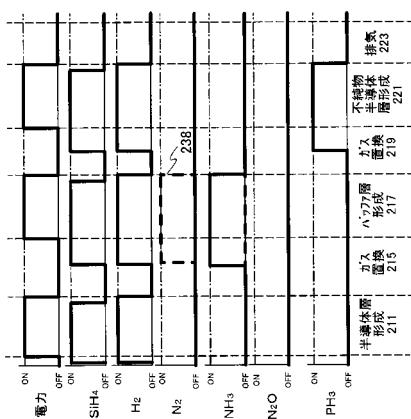

本実施の形態では、実施の形態 5に適用可能なバッファ層の形成工程について説明する。

【0253】

本実施の形態では、バッファ層 111の堆積ガスに窒素を混入させることで、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くする。ゲート絶縁層 107の形成から半導体層 109の形成方法は実施の形態 5と同様であるため、ここでは、半導体層 109から不純物半導体層 113の形成までについて、図 22 を参照して以下に説明する。

【0254】

ゲート絶縁層 107 上に半導体層 109を形成する。半導体層 109は、後の工程でパターン形成されて半導体層 115となるものである。まず、半導体層 109の堆積に用いる材料ガスを処理室内に導入する。ここでは、一例として、実施の形態 5と同様の方法により、半導体層 109として約 50 nm の微結晶シリコン層を形成する。その後、プラズマの放電を停止させる(図 22 の半導体層形成 211)。その後、これらのガスを排気し、バッファ層 111の堆積に用いるガスを導入する(図 22 のガス置換 215)。

40

【0255】

次に、半導体層 109 上にバッファ層 111を形成する。バッファ層 111は、後の工程でパターン形成されてバッファ層 131となるものである。ここでは、バッファ層 111として、厚さ 80 nm の非晶質構造の中に結晶領域を有するシリコン層を形成する。この

50

ときの堆積条件を以下に示す。材料ガスを、流量 2 0 s c c m の SiH<sub>4</sub>、流量 1 4 8 0 s c c m の H<sub>2</sub>、及び流量 2 0 s c c m の 1 0 0 0 p p m NH<sub>3</sub> (水素希釈) とし、処理室内の圧力を 2 8 0 P a、基板の温度を 2 8 0 とし、5 0 W 出力によりプラズマ放電を行う。その後、プラズマの放電を停止させる (図 2 2 のバッファ層形成 2 1 7)。その後、これらのガスを排気し、不純物半導体層 1 1 3 の堆積に用いるガスを導入する (図 2 2 のガス置換 2 1 9)。また、実施の形態 5 と同様に、不純物半導体層 1 1 3 を形成する (図 2 2 の不純物半導体層形成 2 2 1)。

## 【 0 2 5 6 】

上記の例において、半導体層 1 0 9 の形成に用いられる材料ガスでは、SiH<sub>4</sub> の流量に対する H<sub>2</sub> の流量を 1 5 0 倍としており、シリコンは徐々に堆積される。

10

## 【 0 2 5 7 】

なお、アンモニアガスの代わりに破線 2 3 8 で示すように窒素ガスを用いてもよい。

## 【 0 2 5 8 】

本実施の形態におけるバッファ層 1 1 1 の原料ガスには窒素が含まれている。上記したように、窒素は結晶成長を抑制する。このため、アンモニアガスの流量により、バッファ層 1 1 1 が堆積されるにつれ、半導体層 1 0 9 を種結晶とする結晶成長が抑制され、順錐形の結晶領域が成長する。また、微小結晶粒が形成される。なお、当該工程において、逆錐形の結晶領域が形成される場合もある。

## 【 0 2 5 9 】

このような方法により形成したバッファ層 1 1 1 において、二次イオン質量分析法によって計測される窒素濃度は、バッファ層 1 1 1 において一定の濃度を示す。

20

## 【 0 2 6 0 】

上記説明したように、バッファ層の堆積時のガスに窒素を含ませることで、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くすることが可能であり、結晶領域を含む半導体層を形成することができる。

## 【 0 2 6 1 】

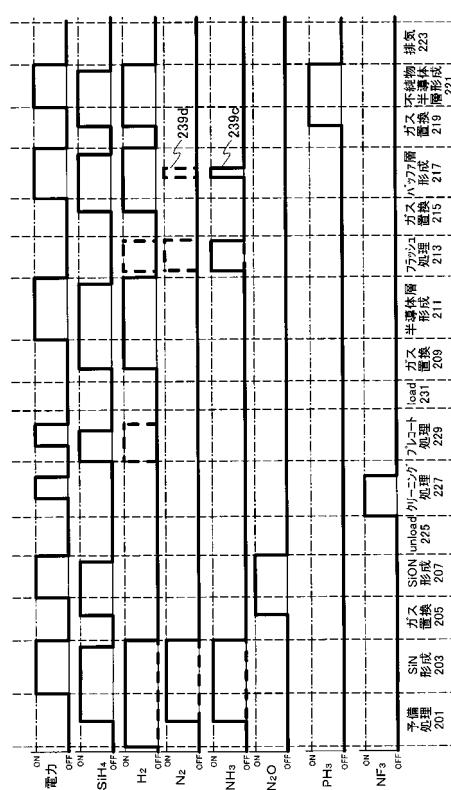

## (実施の形態 8 )

実施の形態 5 乃至実施の形態 7 と比較して、窒素濃度の分布が異なる非晶質構造の中に結晶領域を有する半導体層の作製方法について、図 2 3 及び図 2 4 を用いて示す。

## 【 0 2 6 2 】

本実施の形態では、バッファ層 1 1 1 に、窒素を添加する方法として、実施の形態 6 において、半導体層形成 2 1 1 処理の後、フラッシュ処理 2 1 3 で窒素を含有するガスを反応室内に導入すると共に、バッファ層 1 1 1 を形成している間、実線 2 3 9 c で示すように窒素を含有するガスを再度反応室内に導入する (図 2 3 参照)。窒素を含有するガスとして、ここではアンモニアガスを用いる。なお、アンモニアガスの代わりに破線 2 3 9 d に示すように窒素ガスを用いてもよい。さらには、アンモニアガス及び窒素ガスを用いてもよい。この結果、バッファ層 1 1 1 の堆積初期及び堆積途中において、窒素濃度が高くなり、結晶成長がしにくくなる。この結果、図 3 (B - 3) に示すように、結晶領域 1 3 1 f の成長がバッファ層 1 3 1 の途中で止まり、結晶領域 1 3 1 f の上面には非晶質構造が堆積する。または、結晶領域 1 3 1 f の上方に微小結晶粒が形成される。

30

## 【 0 2 6 3 】

または、図 3 (B - 4) に示すように、堆積初期から結晶領域が成長した後、窒素を含有するガスを反応室に導入したときにバッファ層 1 1 1 の窒素濃度が高くなり、結晶領域の結晶成長が停止する。この後、バッファ層 1 1 1 の窒素の濃度を低減することで、結晶核が形成され、結晶成長し、複数の逆錐形状の結晶領域が積層した構造 1 3 1 g とすることができる。

## 【 0 2 6 4 】

または、バッファ層 1 1 1 に、窒素を添加する方法として、実施の形態 7 において、半導体層を形成した後、反応室に窒化シリコン層を形成すると共に、バッファ層 1 1 1 を形成している間、実線 2 3 9 c で示すように窒素を含有するガスを再度反応室内に導入する (

40

50

図24参照)。窒素を含有するガスとして、ここではアンモニアガスを用いる。なお、アンモニアガスの代わりに破線239dに示すように窒素ガスを用いてもよい。さらには、アンモニアガス及び窒素ガスを用いてもよい。この結果、バッファ層111の堆積初期及び堆積途中において、窒素濃度が高くなり、結晶成長がしにくくなる。この結果、図3(B-3)に示すように、結晶領域131fの成長がバッファ層131の途中で止まり、結晶領域131fの上面には非晶質構造が堆積する。または、結晶領域131fの上方に微小結晶粒が形成される。

#### 【0265】

または、図3(B-4)に示すように、堆積初期から結晶領域が成長した後、窒素を含有するガスを反応室に導入したときにバッファ層111の窒素濃度が高くなり、結晶領域の結晶成長が停止する。この後、バッファ層111の窒素の濃度を低減することで、結晶核が形成され、結晶成長し、複数の逆錐形状の結晶領域が積層した構造131gとすることができます。

10

#### 【0266】

以上により、バッファ層の上側、即ちソース領域及びドレイン領域側における結晶領域の大きさを窒素濃度で制御することで、結晶領域の割合を低減することが可能であり、薄膜トランジスタのオフ電流を低減することができる。

#### 【0267】

##### (実施の形態9)

本実施の形態では、実施の形態4に示す薄膜トランジスタの作製方法について、説明する。本実施の形態においても、n型の薄膜トランジスタの作製方法について説明する。

20

#### 【0268】

実施の形態5と同様に、第1のフォトリソグラフィ工程を用いて、基板101上にゲート電極層103及び容量配線105を形成する。

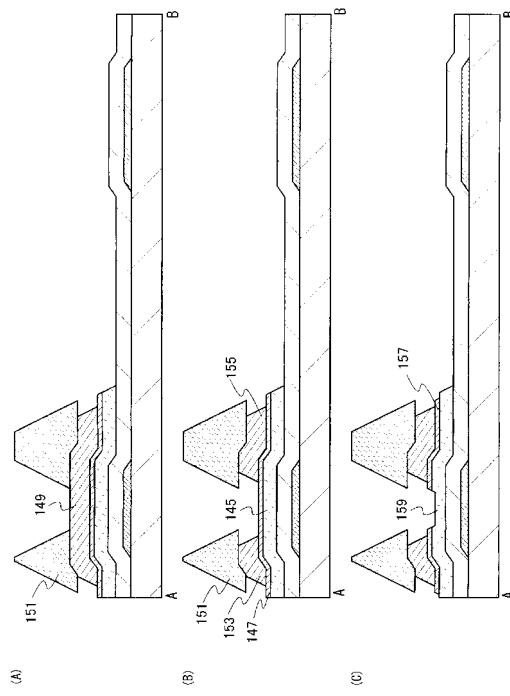

#### 【0269】

次に、ゲート電極層103を覆ってゲート絶縁層107、非晶質構造の中に結晶領域を有する半導体層141、不純物半導体層113、及び導電層121を形成する。その後、導電層121上に第2のフォトリソグラフィ工程により形成したレジストマスク143を形成する(図26(A)を参照)。

30

#### 【0270】

ゲート絶縁層107、非晶質構造の中に結晶領域を有する半導体層141、及び不純物半導体層113の形成方法としては、実施の形態5において、反応室のクリーニング処理227、プレコート処理229、1oad231、ガス置換209、及び半導体層形成211工程を除いた方法で形成すればよい。具体的には、図20において、ゲート絶縁層107の形成方法として、予備処理201からSiON形成207までの工程を行う。次に、非晶質構造の中に結晶領域を有する半導体層141の形成方法として、フラッシュ処理213からバッファ層形成217までの工程を行う。次に、不純物半導体層113の形成方法として、ガス置換219から排気223までの工程を行う。

#### 【0271】

上記形成方法に代えて、実施の形態6の半導体層形成211の工程を除いた工程を用いてもよい。具体的には、図20において、ゲート絶縁層107の形成方法として、予備処理201からSiON形成207までの工程を行う。次に、非晶質構造の中に結晶領域を有する半導体層141の形成方法として、図21において、unload225からバッファ層形成217までの工程を行う。次に、不純物半導体層113の形成方法として、ガス置換219から排気223までの工程を行う。

40

#### 【0272】

また、上記形成方法に代えて、実施の形態7の半導体層形成211の工程を除いた工程を用いてもよい。具体的には、図20において、ゲート絶縁層107として、予備処理201からSiON形成207までの工程を行う。次に、非晶質構造の中に結晶領域を有する半導体層141の形成方法として、図22において、ガス置換215及びバッファ層形成

50

217までの工程を行う。次に、不純物半導体層113の形成方法として、ガス置換219から排気223までの工程を行う。

【0273】

レジストマスク143は厚さの異なる二の領域を有し、多階調マスクを用いて形成することができる。多階調マスクを用いることで、使用するフォトマスクの枚数が低減され、作製工程数が減少するため好ましい。本実施の形態において、半導体層のパターンを形成する工程と、ソース領域とドレイン領域を分離する工程とにおいて、多階調マスクを用いることができる。

【0274】

多階調マスクとは、多段階の光量で露光を行うことが可能なマスクであり、代表的には、露光領域、半露光領域及び未露光領域の3段階の光量で露光を行う。多階調マスクを用いることで、一度の露光及び現像工程によって、複数（代表的には二種類）の厚さを有するレジストマスクを形成することができる。そのため、多階調マスクを用いることで、フォトマスクの枚数を削減することができる。

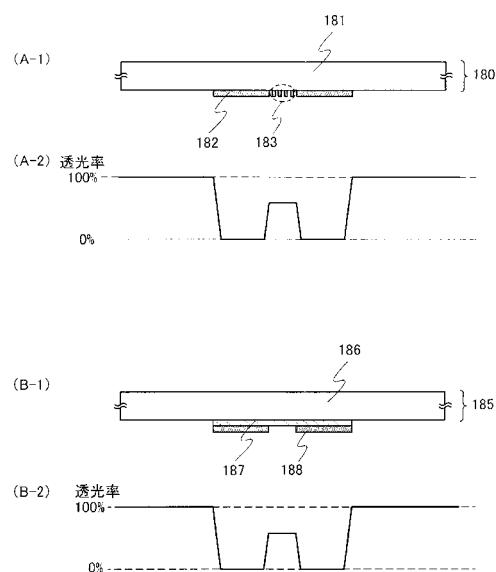

【0275】

図30(A-1)及び図30(B-1)は、代表的な多階調マスクの断面図を示す。図30(A-1)にはグレートーンマスク180を示し、図30(B-1)にはハーフトーンマスク185を示す。

【0276】

図30(A-1)に示すグレートーンマスク180は、透光性を有する基板181上に遮光層により形成された遮光部182、及び遮光層のパターンにより設けられた回折格子部183で構成されている。

【0277】

回折格子部183は、露光に用いる光の解像度限界以下の間隔で設けられたスリット、ドットまたはメッシュ等を有することで、光の透過率を制御する。なお、回折格子部183に設けられるスリット、ドットまたはメッシュは周期的なものであってもよいし、非周期的なものであってもよい。

【0278】

透光性を有する基板181としては、石英等を用いることができる。遮光部182及び回折格子部183を構成する遮光層は、クロムまたは酸化クロム等により設けられる。

【0279】

グレートーンマスク180に露光するための光を照射した場合、図30(A-2)に示すように、遮光部182に重畳する領域における透光率は0%となり、遮光部182または回折格子部183が設けられていない領域における透光率は100%となる。また、回折格子部183における透光率は、概ね10~70%の範囲であり、回折格子のスリット、ドットまたはメッシュの間隔等により調整可能である。

【0280】

図30(B-1)に示すハーフトーンマスク185は、透光性を有する基板186上に半透光層により形成された半透光部187、及び遮光層により形成された遮光部188で構成されている。

【0281】

半透光部187は、MoSiN、MoSi、MoSiO、MoSiON、CrSi等の層を用いて形成することができる。遮光部188は、グレートーンマスクの遮光層と同様、クロムまたは酸化クロム等により設けられる。

【0282】

ハーフトーンマスク185に露光するための光を照射した場合、図30(B-2)に示すように、遮光部188に重畳する領域における透光率は0%となり、遮光部188または半透光部187が設けられていない領域における透光率は100%となる。また、半透光部187における透光率は、概ね10~70%の範囲であり、形成する材料の種類または形成する厚さ等により、調整可能である。

10

20

30

40

50

## 【0283】

多階調マスクを用いて露光して現像を行うことで、厚さの異なる領域を有するレジストマスクを形成することができる。

## 【0284】

次に、レジストマスク143を用いて、非晶質構造の中に結晶領域を有する半導体層141、不純物半導体層113、及び導電層121をエッティングする。この工程により、非晶質構造の中に結晶領域を有する半導体層141、不純物半導体層113及び導電層121を素子毎に分離し、非晶質構造の中に結晶領域を有する半導体層145、不純物半導体層147、及び導電層149を形成する（図26（B）を参照）。

## 【0285】

次に、レジストマスク143を後退させて、レジストマスク151を形成する。レジストマスクの後退には、酸素プラズマによるアッシングを用いればよい。ここでは、ゲート電極上で分離するようにレジストマスク143をアッシングする。この結果、レジストマスク151は分離される（図27（A）参照）。

## 【0286】

次に、レジストマスク151を用いて導電層149をエッティングし、配線層153、155を形成する（図27（B）を参照）。配線層153、155は、ソース電極及びドレイン電極を構成する。導電層149のエッティングは、実施の形態5に示す導電層121のエッティングと同様に行なうことが好ましい。

## 【0287】

次に、レジストマスク151が形成された状態で、非晶質構造の中に結晶領域を有する半導体層145の一部及び不純物半導体層147をエッティングして、非晶質構造の中に結晶領域を有する半導体層159、並びにソース領域及びドレイン領域157を形成する（図27（C）を参照）。この後、レジストマスク151を除去する。このときの図27（C）の上面図を図29（A）に示す。

## 【0288】

次に、実施の形態1と同様に、ドライエッティングを行うとよい。更には、非晶質構造の中に結晶領域を有する半導体層159の表面に水プラズマ、アンモニアプラズマ、窒素プラズマ等を照射してもよい。

## 【0289】

以上の工程により本実施の形態に係る薄膜トランジスタを作製することができる。本実施の形態に係る薄膜トランジスタは、実施の形態5にて説明した薄膜トランジスタと同様に、液晶表示装置に代表される表示装置の画素におけるスイッチングトランジスタに適用することができる。そのため、この薄膜トランジスタを覆って、絶縁層133を形成する（図28（A）参照）。

## 【0290】

次に、絶縁層133に開口部134、160を形成する。この開口部134、160は、第3のフォトリソグラフィ工程により形成したレジストマスクを用いて形成することができる。その後、当該開口部134、160を介して接続されるように、絶縁層133上に、第4のフォトリソグラフィ工程により画素電極層135を設ける。このようにして図28（B）に示す表示装置の画素におけるスイッチングトランジスタを作製することができる。

## 【0291】

なお、図示していないが、絶縁層133と画素電極層135との間に、スピンドルティング法等により形成した有機樹脂からなる絶縁層を有していても良い。

## 【0292】

この後、実施の形態5と同様に、VA（Vertical Alignment）方式の液晶表示装置において、視野角拡大のために、画素を複数部分に分割し、分割された画素の各部分の液晶の配向を異ならせるマルチドメイン方式（いわゆるMVA方式）の場合、画素電極層135上に突起物137を形成することが好ましい（図28（C）参照）。こ

10

20

30

40

50

のときの図 28 (C) の上面図を図 29 (B) に示す。

【0293】

以上の工程により、実施の形態 5 より少ないマスク数で、非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、オン電流が高く、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、オフ電流の低い薄膜トランジスタを有し、且つ液晶表示装置に用いることが可能な素子基板を作製することができる。

【0294】

(実施の形態 10)

本実施の形態では、実施の形態 3 に示す薄膜トランジスタにおいて、図 11 に示す薄膜トランジスタの作製方法について、説明する。ここでは、非晶質構造の中に結晶領域を有する半導体層 141 を異なる 2 つの条件で形成することを特徴とする。

10

【0295】

ゲート電極層の形成方法は実施の形態 5 と同様であるため、ここでは、ゲート絶縁層 107 から不純物半導体層 113 の形成までについて、図 25 を参照して以下に説明する。

【0296】

まず、ゲート電極層 103 が形成された基板を CVD 装置の処理室 241 内にて加熱し、ゲート絶縁層 107 として窒化シリコン層を形成するために、窒化シリコン層の堆積に用いる材料ガスを処理室 241 内に導入する（図 25 の予備処理 201）。

【0297】

次に、ゲート絶縁層 107 として、窒化シリコン層を形成する。このときの堆積条件は、実施の形態 5 に示す SiN 形成 203 の条件を用いることができる。

20

【0298】

次に、非晶質構造の中に結晶領域を有する半導体層 141 の堆積に用いる材料ガスを処理室 241 内に導入する（図 25 のガス置換 209）。次に、ゲート絶縁層 107 上に第 1 の条件で非晶質構造の中に結晶領域を有する半導体層の一部を形成する（図 25 の半導体層形成 211）。この結果、図 13 に示す半導体層 132i のように、逆錐形の結晶領域を形成することができる。

【0299】

なお、ゲート絶縁層 107 の最表面が窒化シリコン層でない場合は、実施の形態 5 に示すように、ゲート絶縁層 107 を形成した後、図 20 に示すフラッシュ処理 213 を行って、ゲート絶縁層 107 の表面に窒素を吸着させた後、ガス置換 209 及び半導体層形成 211 を行ってもよい。または、実施の形態 6 に示すように、ゲート絶縁層 107 を形成した後、図 21 に示すプレコート処理 233 を行って、処理室内に窒化シリコン層を形成した後、ガス置換 209 及び半導体層形成 211 を行ってもよい。

30

【0300】

上記第 1 条件により、ゲート絶縁層 107 の表面には窒素が供給されている。上記したように、窒素はシリコンの結晶核の生成を抑制する。そのため、半導体層の堆積の初期段階ではシリコンの結晶核が生成されにくい。半導体層の堆積は窒素の濃度を低下させつつ進み、窒素の濃度が一定の値以下となると、結晶核が形成される。その後、その結晶核が成長し、錐形状の結晶領域が形成される。または微小結晶粒が形成される。

40

【0301】

次に、非晶質構造の中に結晶領域を有する半導体層 141 の堆積に用いるガスを導入する（図 25 のガス置換 215）。ここでは第 2 の条件で非晶質構造の中に結晶領域を有する半導体層の残部を形成する（図 25 の半導体層形成 230）。ここでは、実施の形態 7 に示すバッファ層形成 217 と同様に、原料ガスに、窒素を含むガスを用いる。この結果、図 13 に示す半導体層 132j のように、順錐形の結晶領域を形成することができる。

【0302】

上記第 2 の条件を用いることで、結晶成長を抑制しながら半導体層 132j を堆積するため、半導体層 132i に含まれる結晶領域を種結晶とする結晶成長が抑制され、結晶領域の幅が狭まる構造、即ち順錐形の結晶領域を形成することができる。

50

## 【0303】

次に、不純物半導体層113の形成方法として、ガス置換219から排気223までの工程を行う。

## 【0304】

以上の工程により、ゲート絶縁層107上に、非晶質構造131bに、四つの角が直角でない四辺形、代表的にはひし形の結晶領域132hを有する半導体層を形成することができる。

## 【0305】

非晶質半導体をチャネル形成領域に有する薄膜トランジスタと比較して、オン電流が高く、微結晶半導体をチャネル形成領域に有する薄膜トランジスタと比較して、オフ電流の低い薄膜トランジスタを有し、且つ液晶表示装置に用いることが可能な素子基板を作製することができる。10

## 【0306】

(実施の形態11)

本実施の形態では、コンタクト抵抗を下げることが可能な薄膜トランジスタの構造について示す。具体的には、実施の形態1乃至実施の形態9に示すソース領域及びドレイン領域を、一導電型を付与する不純物元素と、窒素とを含有する半導体層(以下、窒素を有する不純物半導体層と示す。)で形成する。

## 【0307】

窒素を有する不純物半導体層は、実施の形態5乃至実施の形態7において、不純物半導体層とバッファ層形成工程を組み合わせることで形成される。具体的には、実施の形態5に示す非晶質構造の中に結晶領域を有する半導体層の形成工程と不純物半導体層の形成工程を組み合わせる場合、図20において、バッファ層形成217及びガス置換219の間に、フラッシュ処理213を行い、バッファ層表面の窒素濃度を高めて、不純物半導体層の窒素濃度を高めればよい。20

## 【0308】

また、実施の形態6に示す非晶質構造の中に結晶領域を有する半導体層の形成工程と不純物半導体層の形成工程を組み合わせる場合、図21において、バッファ層形成217及びガス置換219の間に、unload225からload231まで行い、反応室の内側に窒化シリコン層を形成して、反応室内の窒素濃度を高めて、不純物半導体層の窒素濃度を高めればよい。30

## 【0309】

また、実施の形態7に示す非晶質構造の中に結晶領域を有する半導体層の形成工程と不純物半導体層の形成工程を組み合わせる場合、図22において、不純物半導体層形成221工程において、アンモニアガスまたは窒素ガスを導入して、不純物半導体層の窒素濃度を高めればよい。

## 【0310】

ソース領域及びドレイン領域に一導電型を付与する不純物元素と共に、窒素を含有させることで、ソース領域及びドレイン領域の欠陥準位を低減することが可能である。また、ソース領域及びドレイン領域に一導電型を付与する不純物元素と共に、NH基またはNH<sub>2</sub>基を含有する場合があり、当該構造によりソース領域及びドレイン領域の欠陥準位を低減することが可能である。これらのため、ソース領域及びドレイン領域の間の電気伝導度を向上させることができ、コンタクト抵抗を下げることが可能である。40

## 【0311】

(実施の形態12)

実施の形態1乃至実施の形態4に示す薄膜トランジスタは、発光表示装置や発光装置に用いることができる。発光表示装置や発光装置は、発光素子として代表的には、エレクトロルミネッセンスを利用する発光素子がある。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって大別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。50

## 【0312】

また、実施の形態5乃至実施の形態11に示すような素子基板上に発光素子を形成して発光表示装置や発光装置を作製することができる。

## 【0313】

本実施の形態の発光表示装置及び発光装置は、オン電流が高くオフ電流が低い薄膜トランジスタを画素トランジスタとして用いているため、画質が良好（例えば、高コントラスト）であり、且つ消費電力の低い発光表示装置及び発光装置を作製することができる。

## 【0314】

## (実施の形態13)

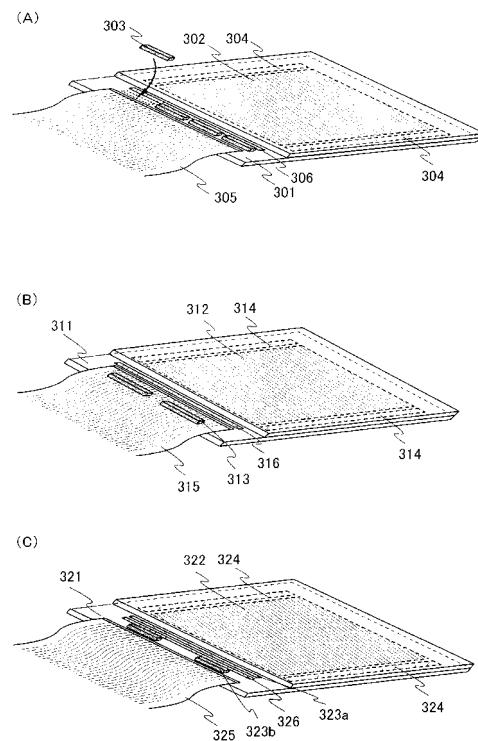

次に、上記実施の形態を適用可能な表示装置である表示パネルの構成の一例について、以下に示す。

10

## 【0315】

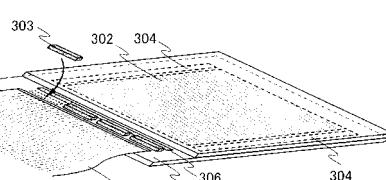

図31(A)に、信号線駆動回路303のみを別途形成し、基板301上に形成された画素部302と接続している表示パネルの形態を示す。画素部302、保護回路306、及び走査線駆動回路304が形成された素子基板は、実施の形態1乃至実施の形態12のいずれかに示す薄膜トランジスタを用いて形成する。信号線駆動回路303は、単結晶半導体をチャネル形成領域に用いたトランジスタ、多結晶半導体をチャネル形成領域に用いた薄膜トランジスタ、またはSOI(Silicon On Insulator)をチャネル形成領域に用いたトランジスタにより構成すれば良い。SOIをチャネル形成領域に用いたトランジスタにおいては、ガラス基板上に設けられた単結晶半導体層をチャネル形成領域に用いたトランジスタを含む。画素部302と、信号線駆動回路303と、走査線駆動回路304とに、それぞれ電源の電位、各種信号等が、FPC305を介して供給される。信号線駆動回路303とFPC305との間、及び信号線駆動回路303と画素部302との間の一方または双方に、実施の形態1乃至実施の形態12のいずれかに示す薄膜トランジスタで形成された保護回路306を設けてもよい。保護回路306は、その他の構造の薄膜トランジスタ、ダイオード、抵抗素子及び容量素子等から選択された1つまたは複数の素子を用いてもよい。

20

## 【0316】

なお、信号線駆動回路及び走査線駆動回路を、画素部の画素トランジスタと同じ基板上に形成しても良い。

30

## 【0317】

また、駆動回路を別途形成する場合には、必ずしも駆動回路が形成された基板を、画素部が形成された基板上に貼り合わせる必要はなく、例えばFPC上に貼り合わせるようにしても良い。図31(B)に、信号線駆動回路313のみを別途形成し、基板311上に形成された画素部312、保護回路316、及び走査線駆動回路314が形成された素子基板とFPC315が接続している表示パネルの形態を示す。画素部312、保護回路316及び走査線駆動回路314は、上記実施の形態に示す薄膜トランジスタを用いて形成する。信号線駆動回路313は、FPC315及び保護回路316を介して、画素部312に接続されている。画素部312と、信号線駆動回路313と、走査線駆動回路314それぞれに、電源の電位及び各種の信号等が、FPC315を介して供給される。FPC315と画素部312との間に、保護回路316を設けてもよい。

40

## 【0318】

また、信号線駆動回路の一部または走査線駆動回路の一部のみを、上記の実施の形態に示す薄膜トランジスタを用いて画素部と同じ基板上に形成し、残りを別途形成して画素部と電気的に接続するようにしても良い。図31(C)に、信号線駆動回路が有するアナログスイッチ323aを、画素部322、走査線駆動回路324と同じ基板321上に形成し、信号線駆動回路が有するシフトレジスタ323bを別途異なる基板に形成して貼り合わせる表示パネルの形態を示す。画素部322、保護回路326、及び走査線駆動回路324は、上記実施の形態に示す薄膜トランジスタを用いて形成する。信号線駆動回路が有するシフトレジスタ323bは、アナログスイッチ323a及び保護回路326を介して画

50

素部 322 と接続されている。画素部 322 と、信号線駆動回路と、走査線駆動回路 324 とそれに、電源の電位、各種信号等が、FPC 325 を介して供給される。FPC 325 とアナログスイッチ 323aとの間に、保護回路 326 を設けてよい。

【0319】

図 31 に示すように、本実施の形態の表示装置は、駆動回路の一部または全部を、画素部と同じ基板上に、上記実施の形態に示す薄膜トランジスタを用いて形成することができる。

【0320】

なお、別途形成した基板の接続方法は、特に限定されるものではなく、公知の COG 方式、ワイヤボンディング方式、或いは TAB 方式などを用いることができる。また接続する位置は、電気的な接続が可能であるならば、図 31 に示した位置に限定されない。また、コントローラ、CPU またはメモリ等を別途形成し、接続するようにしても良い。

10

【0321】

なお、本実施の形態で用いる信号線駆動回路は、シフトレジスタとアナログスイッチを有する。または、シフトレジスタとアナログスイッチに加え、バッファ、レベルシフタ、ソースフォロワ等、他の回路を有していても良い。また、シフトレジスタとアナログスイッチは必ずしも設ける必要はなく、例えばシフトレジスタの代わりにデコーダ回路のような信号線の選択ができる別の回路を用いても良いし、アナログスイッチの代わりにラッチ等を用いても良い。

【0322】

20

(実施の形態 14)

上記形態の薄膜トランジスタで構成される素子基板、及びそれを用いた表示装置等は、アクティブマトリクス型の表示パネルに適用することができる。すなわち、それらを表示部に組み込んだ電子機器の全てに上記実施の形態を実施できる。

【0323】

その様な電子機器としては、ビデオカメラ及びデジタルカメラ等のカメラ、ヘッドマウントディスプレイ（ゴーグル型ディスプレイ）、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話または電子書籍等）などが挙げられる。それらの一例を図 32 に示す。

【0324】

30

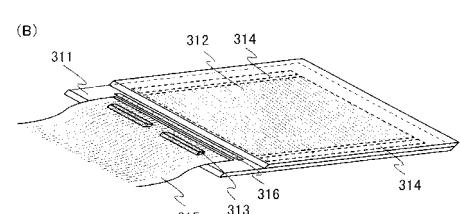

図 32 (A) はテレビジョン装置である。上記実施の形態を適用した表示パネルを筐体に組みこんで、テレビジョン装置を完成させることができる。表示パネルにより主画面 333 が形成され、その他付属設備としてスピーカ部 339、操作スイッチなどが備えられている。

【0325】

図 32 (A) に示すように、筐体 331 に表示素子を利用した表示用パネル 332 が組みこまれ、受信機 335 により一般的のテレビ放送の受信をはじめ、モデム 334 を介して有線または無線による通信ネットワークに接続することにより一方方向（送信者から受信者）または双方向（送信者と受信者間、または受信者間同士）の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチまたはリモコン操作機 336 により行うことが可能であり、このリモコン操作機 336 にも出力する情報を表示する表示部 337 が設けられていても良い。また、表示部 337 に、上記実施の形態等の薄膜トランジスタが設けられていても良い。また、主画面 333 の他にサブ画面 338 を第 2 の表示パネルで形成し、チャンネルや音量などを表示する構成が付加されていても良い。この構成において、主画面 333 及びサブ画面 338 の一方または双方に実施の形態 1 乃至実施の形態 12 のいずれかに示す薄膜トランジスタを適用することができる。

40

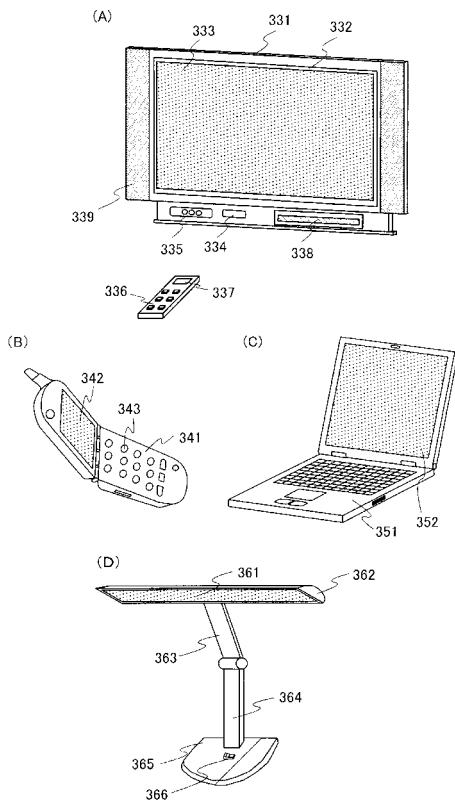

【0326】

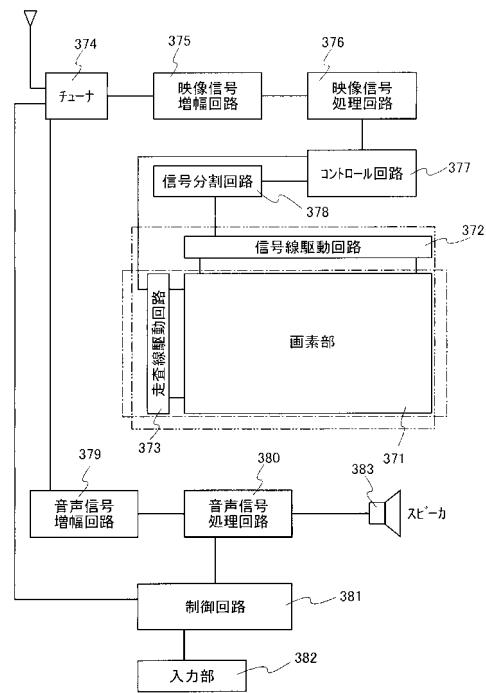

図 33 はテレビ装置の主要な構成を説明するブロック図を示している。表示パネルには、画素部 371 が形成されている。信号線駆動回路 372 と走査線駆動回路 373 は、表示パネルに COG 方式により実装されていても良い。

50

## 【0327】

また、その他の外部回路の構成として、映像信号の入力側では、チューナ374で受信した信号のうち、映像信号を増幅する映像信号增幅回路375と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路376と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路377等を有している。コントロール回路377は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路378を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

## 【0328】

チューナ374で受信した信号のうち、音声信号は、音声信号增幅回路379に送られ、その出力は音声信号処理回路380を経てスピーカ383に供給される。制御回路381は受信局(受信周波数)や音量の制御情報を入力部382から受け、チューナ374や音声信号処理回路380に信号を送出する。

10

## 【0329】

勿論、本実施の形態はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表示媒体に適用してもよい。

## 【0330】

以上説明したように、主画面333及びサブ画面338の一方または双方に、上記実施の形態で説明した薄膜トランジスタを適用することで、画質が高く、消費電力の低いテレビ装置を作製することができる。

20

## 【0331】

図32(B)は携帯電話機341の一例を示している。携帯電話機341は、表示部342、操作部343等により構成されている。表示部342に上記実施の形態で説明した薄膜トランジスタを適用することで、画質を向上させ、消費電力を低減させることができる。

## 【0332】

図32(C)に示す携帯型のコンピュータは、本体351、表示部352等を含んでいる。表示部352に、実施の形態1等で説明した薄膜トランジスタを適用することで、画質を向上させ、消費電力を低減させることができる。

30

## 【0333】

図32(D)は卓上照明器具であり、照明部361、傘362、可変アーム363、支柱364、台365、電源366を含む。上記実施の形態で説明した発光装置を照明部361に用いることにより作製される。照明部361に実施の形態1等で説明した薄膜トランジスタを適用することで、画質を向上させ、消費電力を低減させることができる。

## 【0334】

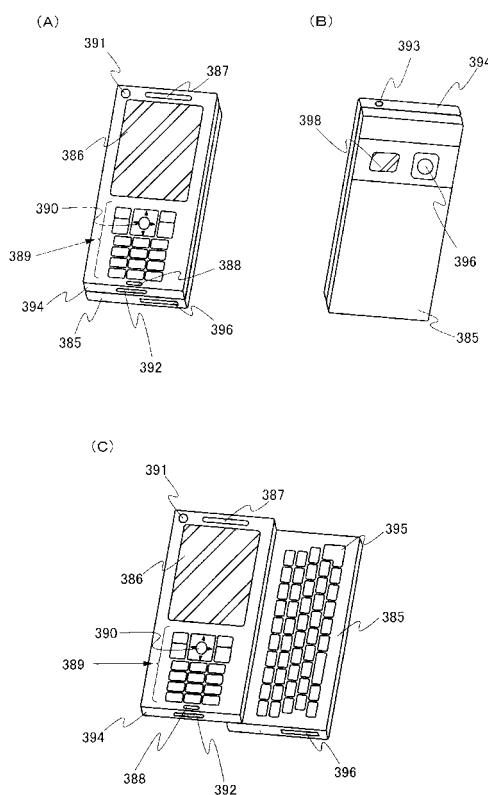

図34は携帯電話機の構成の一例を示しており、例えば表示部に、上記実施の形態で示した薄膜トランジスタを有する素子基板及びそれを有する表示装置が適用される。図34(A)が正面図、図34(B)が背面図、図34(C)が展開図である。図34に示す携帯電話機は、筐体394及び筐体385の二つの筐体で構成されている。図34に示す携帯電話機は、携帯電話と携帯情報端末の双方の機能を備えており、コンピュータを内蔵し、音声通話以外にも様々なデータ処理が可能であり、スマートフォンとも呼ばれる。

40

## 【0335】

携帯電話機は、筐体394及び筐体385の二つの筐体で構成されている。筐体394は、表示部386、スピーカ387、マイクロフォン388、操作キー389、ポインティングディバイス390、表面カメラ用レンズ391、外部接続端子ジャック392、イヤホン端子393等を備え、筐体385は、キーボード395、外部メモリスロット、裏面カメラ396、ライト398等を備える。また、アンテナは筐体394に内蔵されている。

## 【0336】

50

また、上記の構成に加えて、非接触 I C チップまたは小型記録装置等を内蔵していてよい。

【 0 3 3 7 】

図 3 4 ( A ) では筐体 3 9 4 と筐体 3 8 5 が重なり合っており、図 3 4 ( A ) の状態から筐体 3 9 4 と筐体 3 8 5 がスライドし、図 3 4 ( C ) のように展開する。表示部 3 8 6 には、上記実施の形態に示される表示装置を組み込むことが可能であり、使用形態に応じて表示の方向が適宜変化する。表示部 3 8 6 と同一面上に表面カメラ用レンズ 3 9 1 を備えているため、テレビ電話が可能である。また、表示部 3 8 6 をファインダーとして裏面カメラ 3 9 6 及びライト 3 9 8 で静止画及び動画の撮影が可能である。

【 0 3 3 8 】

スピーカ 3 8 7 及びマイクロフォン 3 8 8 は音声通話に限らず、テレビ電話、録音及び再生等の用途に使用できる。操作キー 3 8 9 では、電話の発着信、電子メール等の簡単な情報入力、画面のスクロール及びカーソル移動等が可能である。

【 0 3 3 9 】

また、書類の作成、携帯情報端末としての使用等、取り扱う情報が多い場合は、キーボード 3 9 5 を用いると便利である。重なり合った筐体 3 9 4 と筐体 3 8 5 ( 図 3 4 ( A ) ) はスライドでき、図 3 4 ( C ) のように展開して携帯情報端末として使用できる。また、キーボード 3 9 5 及びポインティングディバイス 3 9 0 を用いることで、円滑な操作が可能である。外部接続端子ジャック 3 9 2 は A C アダプタ及び U S B ケーブル等の各種ケーブルと接続可能であり、これを介して充電及びパーソナルコンピュータ等とのデータ通信が可能である。また、外部メモリスロットに記録媒体を挿入して使用することで、大量のデータの保存及び移動が可能である。

【 0 3 4 0 】

筐体 3 8 5 の裏面 ( 図 3 4 ( B ) ) には、裏面カメラ 3 9 6 及びライト 3 9 8 を備えており、表示部 3 8 6 をファインダーとし静止画及び動画の撮影が可能である。

【 0 3 4 1 】

また、上記構成に加えて、赤外線通信機能、 U S B ポート、テレビワンセグ受信機能、非接触 I C チップ、イヤホンジャック等を備えていてよい。

【 0 3 4 2 】

上記実施の形態で説明した薄膜トランジスタを画素に適用することで、画質を向上させ、消費電力を低減させることができる。

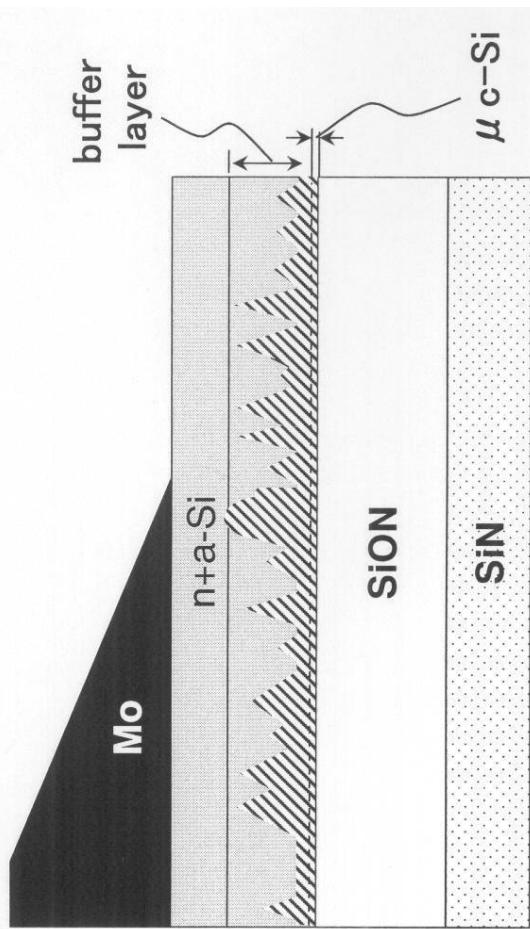

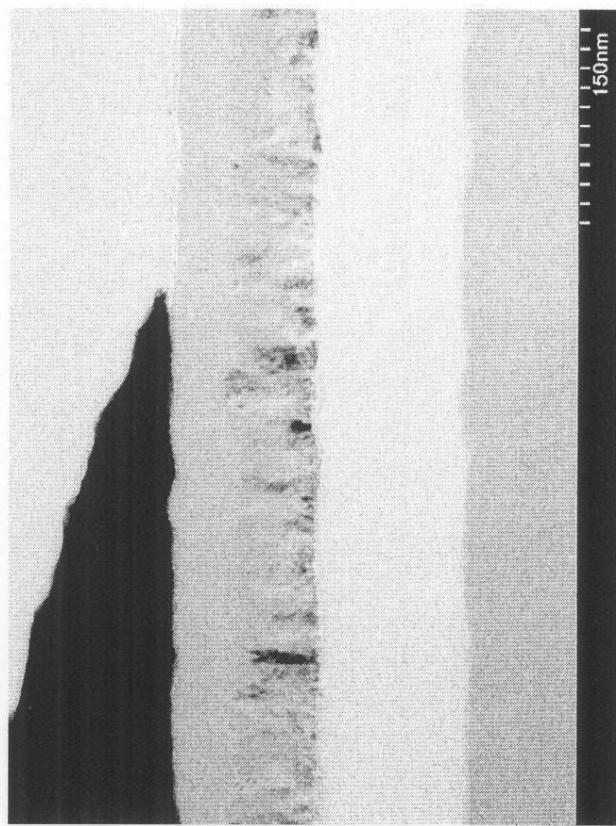

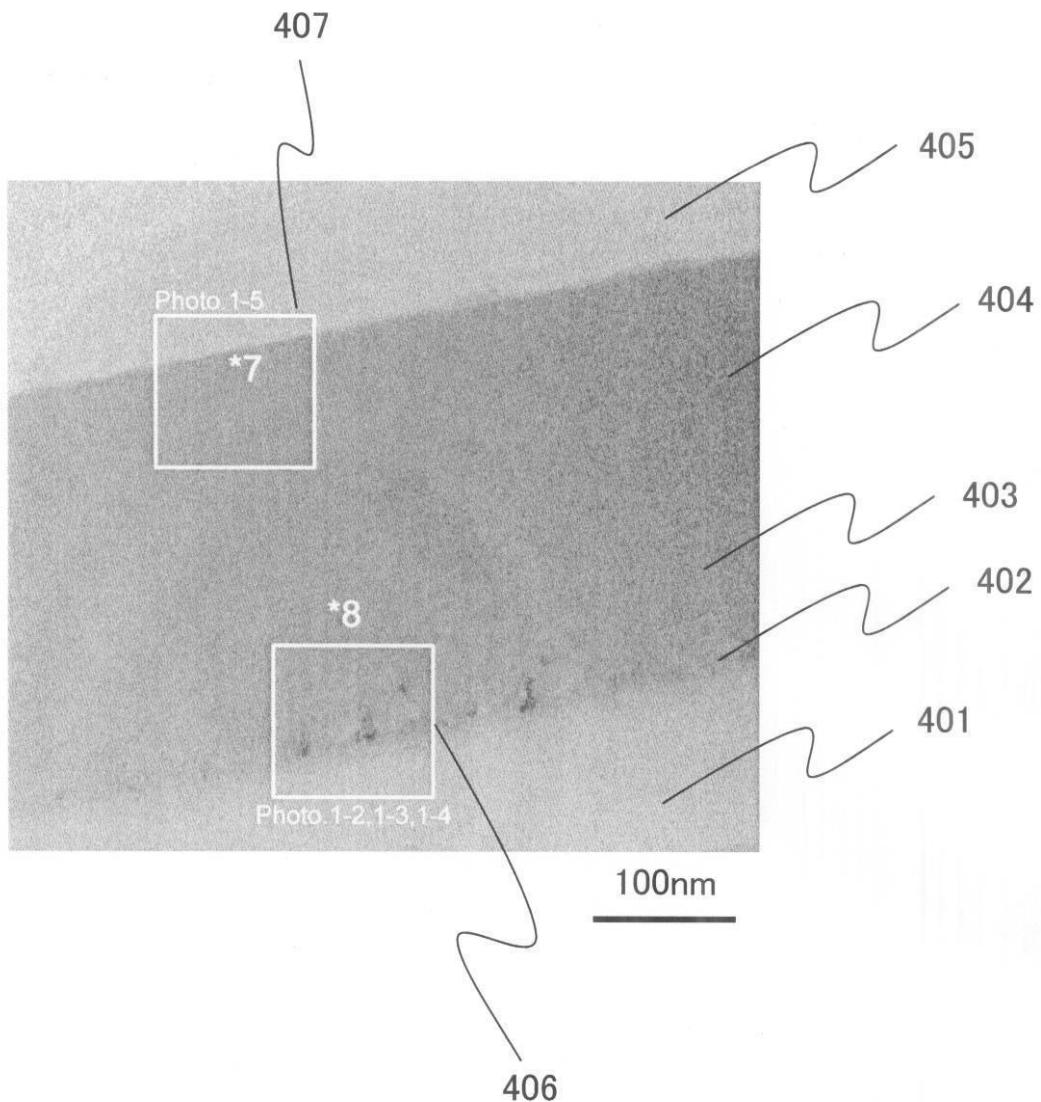

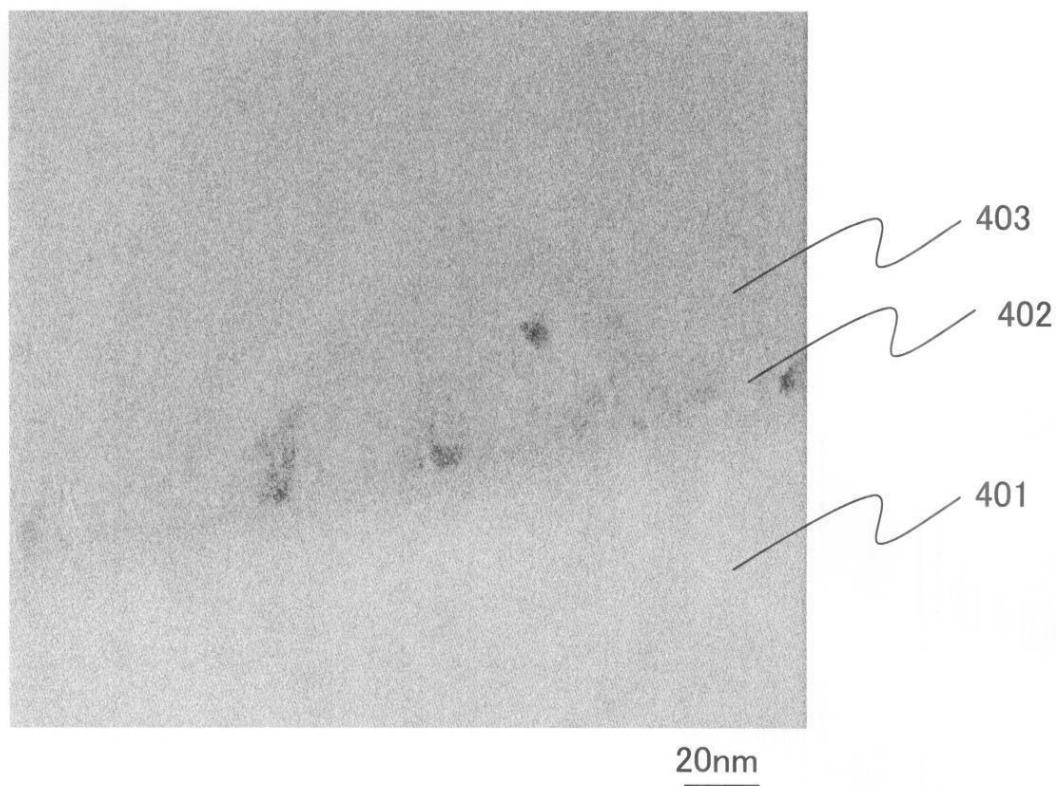

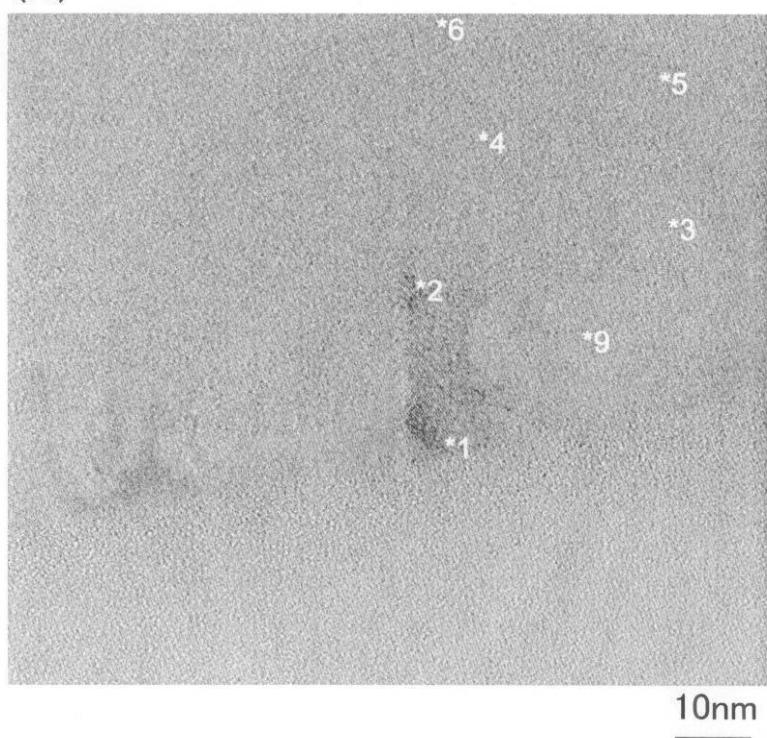

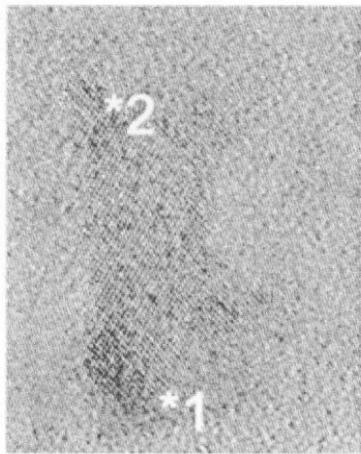

【 実施例 1 】

【 0 3 4 3 】

本実施例では、実施の形態 6 を用いて作製した薄膜トランジスタの断面形状を S T E M ( Scanning Transmission Electron Microscopy ) によって観察した像を図 3 5 に示す。

【 0 3 4 4 】

はじめに薄膜トランジスタの作製工程を、図 1 5 及び図 1 6 を用いて示す。

【 0 3 4 5 】

基板 1 0 1 上にゲート電極層 1 0 3 を形成した。

【 0 3 4 6 】

ここでは、基板 1 0 1 として、厚さ 0 . 7 m m のガラス基板 ( コーニング製 E A G L E 2 0 0 0 ) を用いた。

【 0 3 4 7 】

基板上に、モリブデンターゲットを流量 5 0 s c c m のアルゴンイオンでスパッタリングして、厚さ 1 5 0 n m のモリブデン層を形成した。次に、モリブデン層上にレジストを塗布した後、第 1 のフォトマスクを用いて露光し、現像してレジストマスクを形成した。

【 0 3 4 8 】

次に、当該レジストマスクを用いてモリブデン層をエッティングして、ゲート電極層 1 0 3 を形成した。ここでは、 I C P ( I n d u c t i v e l y C o u p l e d P l a s m

10

20

30

40

50

a：誘導結合型プラズマ）エッチング装置を用い、エッチング条件としては、ICPパワー800W、バイアスパワー100W、圧力1.5Pa、流量25sccmのフッ化炭素、流量25sccmの塩素、及び流量10sccmの酸素のエッチングガスを用いた。

【0349】

この後、レジストマスクを除去した。

【0350】

次に、ゲート電極層103及び基板101上に、ゲート絶縁層107、半導体層109、バッファ層111、及び不純物半導体層113を大気に開放せず連続して形成した（図15（A）参照）。

【0351】

ここでは、ゲート絶縁層107として、窒化シリコン層及び酸化窒化シリコン層を積層した。はじめに、プラズマCVD法により厚さ110nmの窒化シリコン層を形成した。このときの堆積条件を以下に示す。材料ガスを、流量40sccmのSiH<sub>4</sub>、流量500sccmのH<sub>2</sub>、流量550sccmのN<sub>2</sub>、及び流量140sccmのNH<sub>3</sub>とし、処理室内の圧力を100Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を370Wとしてプラズマ放電を行った。次に、プラズマCVD法により厚さ110nmの酸化窒化シリコン層を形成した。このときの堆積条件を以下に示す。原料ガスを、流量30sccmのSiH<sub>4</sub>、及び流量1200sccmのN<sub>2</sub>Oとし、処理室内の圧力を40Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を50Wとしてプラズマ放電を行った。

10

【0352】

次に、基板101を処理室から搬出し、処理室内をNF<sub>3</sub>ガスでクリーニングした後、処理室に保護層の形成に用いる材料ガスを導入し、処理室内に保護層としてアモルファスシリコン層を形成する処理を行った。このときの堆積条件を以下に示す。材料ガスを、流量300sccmのSiH<sub>4</sub>とし、処理室内の圧力を160Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を120Wとしてプラズマ放電を行った。

20

【0353】

その後、基板101を処理室内に搬入し、ゲート絶縁層107上に半導体層109として、厚さ5nmの微結晶シリコン層を形成した。このときの堆積条件を以下に示す。材料ガスを、流量10sccmのSiH<sub>4</sub>、及び流量1500sccmのH<sub>2</sub>とし、処理室内の圧力を280Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を50Wとしてプラズマ放電を行った。

30

【0354】

次に、半導体層109上にバッファ層111として、厚さ55nmの非晶質構造の中に結晶領域を有するシリコン層を形成した。このときの堆積条件を以下に示す。材料ガスを、流量20sccmのSiH<sub>4</sub>、流量1250sccmのH<sub>2</sub>、及び流量250sccmの100ppmNH<sub>3</sub>（水素希釈）とし、処理室内の圧力を280Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を50Wとしてプラズマ放電を行った。

40

【0355】

次に、バッファ層111上に不純物半導体層113として、厚さ50nmのリンが添加されたアモルファスシリコン層を形成した。このときの堆積条件を以下に示す。材料ガスを、流量100sccmのSiH<sub>4</sub>、及び流量170sccmの0.5%フォスフィン（水素希釈）とし、堆積温度を280、圧力170Pa、RF電源の周波数を13.56MHz、RF電源の電力を60Wとしてプラズマ放電を行った。

【0356】

次に、不純物半導体層113上にレジストを塗布した後、第2のフォトマスクを用いて露光し、現像してレジストマスクを形成した。次に、当該レジストマスクを用いて、半導体層109、バッファ層111、及び不純物半導体層113をエッチングして、半導体層1

50

15、バッファ層117、及び不純物半導体層119を形成した(図15(B)参照)。ここでは、ICPエッティング装置を用い、エッティング条件としては、ICPパワー150W、バイアスパワー40W、圧力1.0Pa、エッティングガスに流量100sccmの塩素を用い、エッティング時間を78秒とした。

【0357】

次に、図15(C)に示すように、ゲート絶縁層107、半導体層115、バッファ層117、不純物半導体層119を覆う導電層121を形成した。ここでは、モリブデンターゲットを流量50sccmのアルゴンイオンでスパッタリングして、厚さ300nmのモリブデン層を形成した。

【0358】

次に、導電層121上にレジストを塗布した後、第3のフォトマスクを用いて露光し、現像してレジストマスクを形成した。当該レジストマスクを用いて導電層121をウェットエッティングして、図16(A)に示すように、配線層123、125を形成した。なお、本実施例では、配線層123、125の平面形状は、直線型である。

【0359】

次に、レジストマスクを用いて不純物半導体層119をエッティングして、ソース領域及びドレイン領域129を形成した。なお、当該工程において、バッファ層117の表面も一部エッティングされ、バッファ層131となった(図16(B)参照)。ここでは、ICPエッティング装置を用い、エッティング条件を、ICPパワー150W、バイアスパワー40W、圧力1.0Pa、エッティングガスに流量100sccmの塩素を用い、エッティング時間を33秒とした。このときの、バッファ層131の厚さを40nmとした。この後レジストマスクを除去した。

【0360】

次に、バッファ層131、ソース領域及びドレイン領域129表面にフッ化炭素プラズマを照射し、バッファ層131に残留する不純物を除去した。ここでは、ICPエッティング装置を用い、エッティング条件は、ソースパワー1000W、バイアスパワー0W、圧力0.67Pa、エッティングガスに流量100sccmのフッ化炭素を用い、エッティング時間を30秒とした。

【0361】

次に、絶縁層133として、厚さ300nmの窒化シリコン層を形成した(図16(C)参照)。このときの堆積条件を以下に示す。原料ガスを、流量20sccmのSiH<sub>4</sub>、流量220sccmのNH<sub>3</sub>、流量450sccmの窒素、及び流量450sccmの水素とし、処理室内の圧力を160Pa、基板の温度を280とし、RF電源周波数を13.56MHz、RF電源の電力を150Wとしてプラズマ放電を行った。

【0362】

次に、絶縁層上にレジストを塗布した後、第4のフォトマスクを用いて露光し、現像してレジストマスクを形成した。当該レジストマスクを用いて絶縁層の一部をドライエッティングして、配線層125を露出した。また、絶縁層及びゲート絶縁層107の一部をドライエッティングして、ゲート電極層103を露出した。ここでは、ICPエッティング装置を用い、ICPパワー475W、バイアスパワー300W、圧力5.5Pa、エッティングガスに流量50sccmのCHF<sub>3</sub>、及び流量100sccmのヘリウムを用いてプラズマを発生させた後、エッティングガスとして、流量7.5sccmのCHF<sub>3</sub>、及び流量142.5sccmのヘリウムを用いてエッティング処理を行った。この後、レジストマスクを除去した。

【0363】

次に、絶縁層上に導電層を形成した。ここでは、スパッタリング法により導電層として厚さ50nmの酸化シリコンを含むITOを形成した。

【0364】

次に、導電層上にレジストを塗布した後、第5のフォトマスクを用いて露光し、現像してレジストマスクを形成した。当該レジストマスクを用いて導電層の一部をドライエッキン

10

20

30

40

50

グして、画素電極層 135 を形成した。次に、レジストマスクを除去した後、250 で 1 時間加熱して、酸化シリコンを含む ITO を焼成した。

【0365】

以上の工程により、薄膜トランジスタ及び薄膜トランジスタに接続する画素電極を作製した。

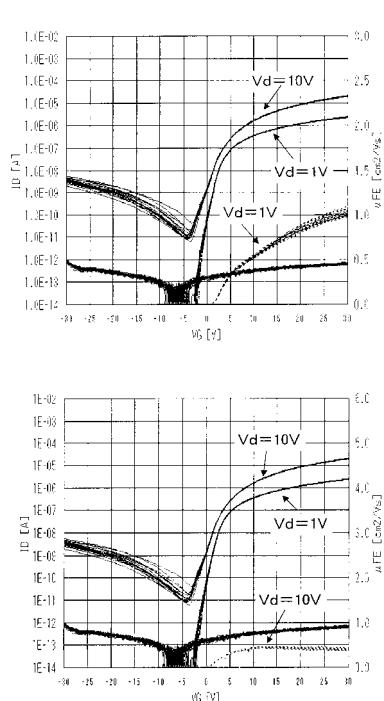

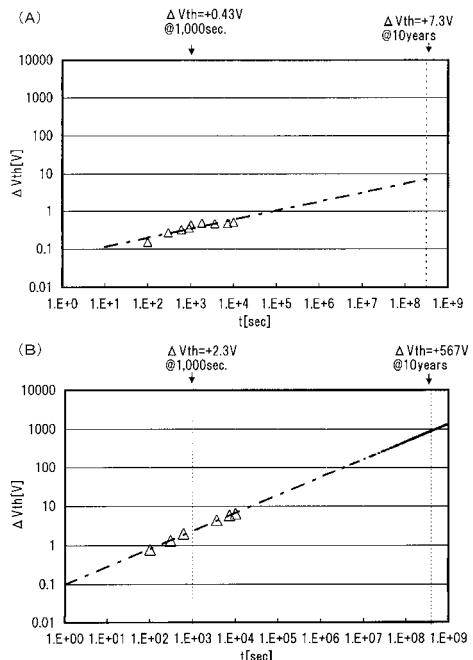

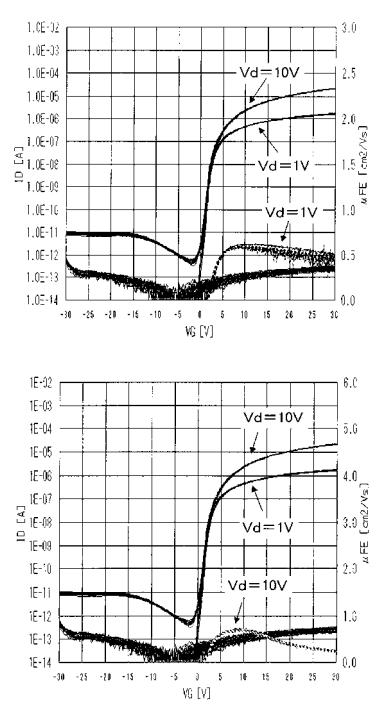

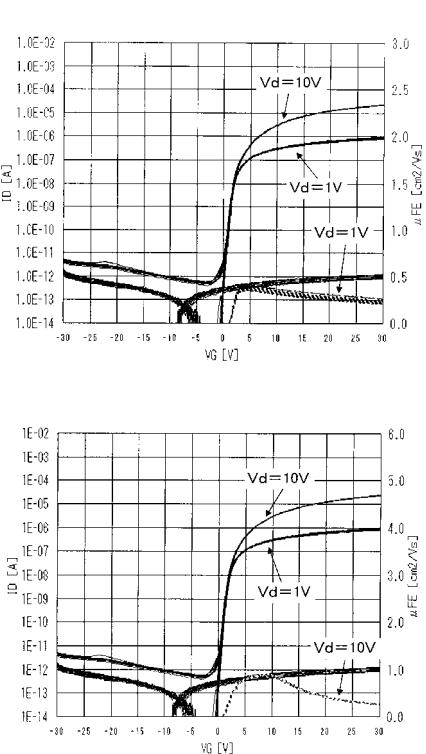

【0366】