(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5787451号

(P5787451)

(45) 発行日 平成27年9月30日(2015.9.30)

(24) 登録日 平成27年8月7日(2015.8.7)

(51) Int.Cl.

F 1

G06F 12/02 (2006.01)

G06F 12/00 (2006.01)G06F 12/02 530C

G06F 12/00 597U

請求項の数 14 (全 14 頁)

(21) 出願番号 特願2013-507977 (P2013-507977)

(86) (22) 出願日 平成23年4月4日 (2011.4.4)

(65) 公表番号 特表2013-525917 (P2013-525917A)

(43) 公表日 平成25年6月20日 (2013.6.20)

(86) 國際出願番号 PCT/US2011/031084

(87) 國際公開番号 WO2011/139452

(87) 國際公開日 平成23年11月10日 (2011.11.10)

審査請求日 平成26年4月2日 (2014.4.2)

(31) 優先権主張番号 12/769,795

(32) 優先日 平成22年4月29日 (2010.4.29)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 スクーラー、ロス エス.

アメリカ合衆国 78737 テキサス州

オースティン ジェス ドライブ 11

701

最終頁に続く

(54) 【発明の名称】エミュレート電気的消去可能(EEP)メモリおよび動作方法

## (57) 【特許請求の範囲】

## 【請求項1】

情報を記憶するための複数のセクタを有するエミュレーションメモリ、および制御手段を有するシステムにおける方法であって、

消去するために考慮されているアドレス空間内の使用されるアドレスの数を前記エミュレーションメモリの前記消去するために考慮されているアドレス空間内の有効レコードの数で除算する計算を行って分数を算出すること。

前記エミュレーションメモリの現在使用されている空間内の情報を記憶するために使用されていない残りのアドレスの量を計算すること、

計算された前記分数が第1の所定の数よりも大きいか否かを判定し、かつ前記残りのアドレスの量が第2の所定の数よりも大きいか否かを判定すること、

前記分数が前記第1の所定の数よりも大きく、かつ前記残りのアドレスの量が前記第2の所定の数よりも大きい場合には、前記エミュレーションメモリの前記現在使用されている空間を使用して任意の後続の更新要求に応答し、前記分数が前記第1の所定の数よりも小さいか、又は前記残りのアドレスの量が前記第2の所定の数よりも小さい場合は前記エミュレーションメモリの圧縮が必要であると判断し、有効データを前記エミュレーションメモリの利用可能なセクタにコピーすることを備える、方法。

## 【請求項2】

前記エミュレーションメモリの前記複数のセクタを2つのセクタとして実装することであって、前記2つのセクタのうちの第1のセクタは、利用されているアドレス指定済みの

10

20

空間から成る第1の部分および残りのアドレスから成る第2の部分を有する、前記エミュレーションメモリの前記現在使用されている空間であり、前記2つのセクタのうちの第2のセクタは空の記憶空間である、前記実装することをさらに含む、請求項1に記載の方法。

【請求項3】

多重セクタによって、前記エミュレーションメモリの前記複数のセクタを実装することであって、前記エミュレーションメモリの第1の部分はデータを保持していない複数のセクタを有し、前記エミュレーションメモリの前記複数のセクタのうちの1つまたは複数は前記エミュレーションメモリの前記現在使用されている空間として割り当てられ、前記現在使用されている空間の一部は、情報を記憶するために使用されていない前記残りのアドレスの量である、前記実装することをさらに含む、請求項1に記載の方法。10

【請求項4】

前記第1の所定の数を、現在情報を記憶していない前記エミュレーションメモリの前記現在使用されている空間内の前記残りの有効アドレスの量の関数である数として決定することをさらに含む、請求項1に記載の方法。

【請求項5】

前記第2の所定の数を、前記計算された分数の関数である数として決定することをさらに含む、請求項1に記載の方法。

【請求項6】

前記エミュレーションメモリ内のレコードの更新を求める要求に応答して前記使用されるアドレスの数を前記有効レコードの数で除算する計算を行うとともに、前記残りのアドレスの量を計算することをさらに含む、請求項1に記載の方法。20

【請求項7】

さらに、前記圧縮が、前記複数のセクタのうちの最も古いフルセクタを消去すること、および、前記消去に統いて有効情報を前記最も古いフルセクタにコピーすることをさらに含む、請求項1に記載の方法。

【請求項8】

システムであって、

情報を順次記憶するための複数のセクタを有するエミュレーションメモリと、

前記エミュレーションメモリに結合されるメモリコントローラとを備え、30

前記メモリコントローラは、

消去するために考慮されているアドレス空間内の使用されるアドレスの数を前記エミュレーションメモリの前記消去するために考慮されているアドレス空間内の有効レコードの数で除算する計算を行って分数を算出し、

前記エミュレーションメモリの現在使用されている空間内の情報を記憶するために使用されていない残りのアドレスの量を計算し、

計算された分数の割合が第1の所定の数よりも大きいか否かを判定し、

前記残りのアドレスの量が第2の所定の数よりも大きいか否かを判定し、

前記分数の割合が前記第1の所定の数よりも大きく、かつ前記残りのアドレスの量が前記第2の所定の数よりも大きい場合には、前記メモリコントローラは、前記エミュレーションメモリの前記現在使用されている空間を使用して任意の後続の更新要求に応答し、40

前記分数の割合が前記第1の所定の数よりも小さいか、または前記残りのアドレスの量が前記第2の所定の数よりも小さい場合には、前記メモリコントローラは、前記エミュレーションメモリの圧縮が必要であると判断し、有効データを前記エミュレーションメモリの利用可能なセクタにコピーする、システム。

【請求項9】

前記エミュレーションメモリはさらに2つのセクタを含み、

前記2つのセクタのうちの第1のセクタは、利用されているアドレス指定済みの空間から成る第1の部分および残りのアドレスから成る第2の部分を有する、前記エミュレーションメモリの前記現在使用されている空間であり、50

前記 2 つのセクタのうちの第 2 のセクタは空の記憶空間である、請求項 8 に記載のシステム。

【請求項 1 0】

前記エミュレーションメモリは多重セクタをさらに含み、

前記エミュレーションメモリの第 1 の部分はデータを保持していない複数のセクタを有し、

前記エミュレーションメモリの前記複数のセクタのうちの 1 つまたは複数のセクタは前記エミュレーションメモリの前記現在使用されている空間として割り当てられ、

前記現在使用されている空間の一部は、情報を記憶するために使用されていない前記残りのアドレスの量である、請求項 8 に記載のシステム。 10

【請求項 1 1】

前記メモリコントローラは、前記第 1 の所定の数を、現在情報を記憶していない前記エミュレーションメモリの前記現在使用されている空間内の前記残りの有効アドレスの量の関数である数として決定する、請求項 8 に記載のシステム。

【請求項 1 2】

前記メモリコントローラは、前記第 2 の所定の数を、前記分数の割合の関数である数として決定する、請求項 8 に記載のシステム。

【請求項 1 3】

前記メモリコントローラは、前記エミュレーションメモリ内のレコードの更新を求める要求に応答して前記計算を実行する、請求項 8 に記載のシステム。 20

【請求項 1 4】

前記メモリコントローラは、前記圧縮を、前記複数のセクタのうちの最も古いフルセクタを消去すること、および、前記消去に続いて有効情報を前記最も古いフルセクタにコピーすることによって実行する、請求項 8 に記載のシステム。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、一般的にはメモリシステムに関し、より具体的には、エミュレート電気的消去可能 (E E E) メモリの動作方法に関する。

【背景技術】 30

【0002】

エミュレート電気的消去可能 (emulated electrically erasable: E E E) メモリは一般的に、ランダムアクセスメモリと同等のサイズについて標準的な不揮発性メモリを超える改善された耐久性を有するメモリシステムを提供するために組み合わされる、ランダムアクセスメモリ、および、電気的に消去可能である不揮発性メモリを使用する。これは、ランダムアクセスメモリよりもはるかに大きい不揮発性メモリを使用して達成されるが、E E E メモリはあたかもランダムアクセスメモリのサイズしかないように動作する。従って、E E E メモリは、E E E メモリによって使用されるサイズからサイズが低減されているが耐久性は向上している電気的消去可能メモリをエミュレートする。これは、データが頻繁に更新され、不揮発的に記憶されなければならない自動車および産業用途のような、耐久性が非常に重要な状況において有用である。 40

【0003】

従って、耐久性を向上させるコストは、不揮発性メモリのメモリサイズを増大させることになり、これは、デバイスをより高価にする。従って、メモリサイズの増大に起因してさらにコストが増大することを回避しながら、有効な耐久性を達成することが継続的に必要とされている。

【図面の簡単な説明】

【0004】

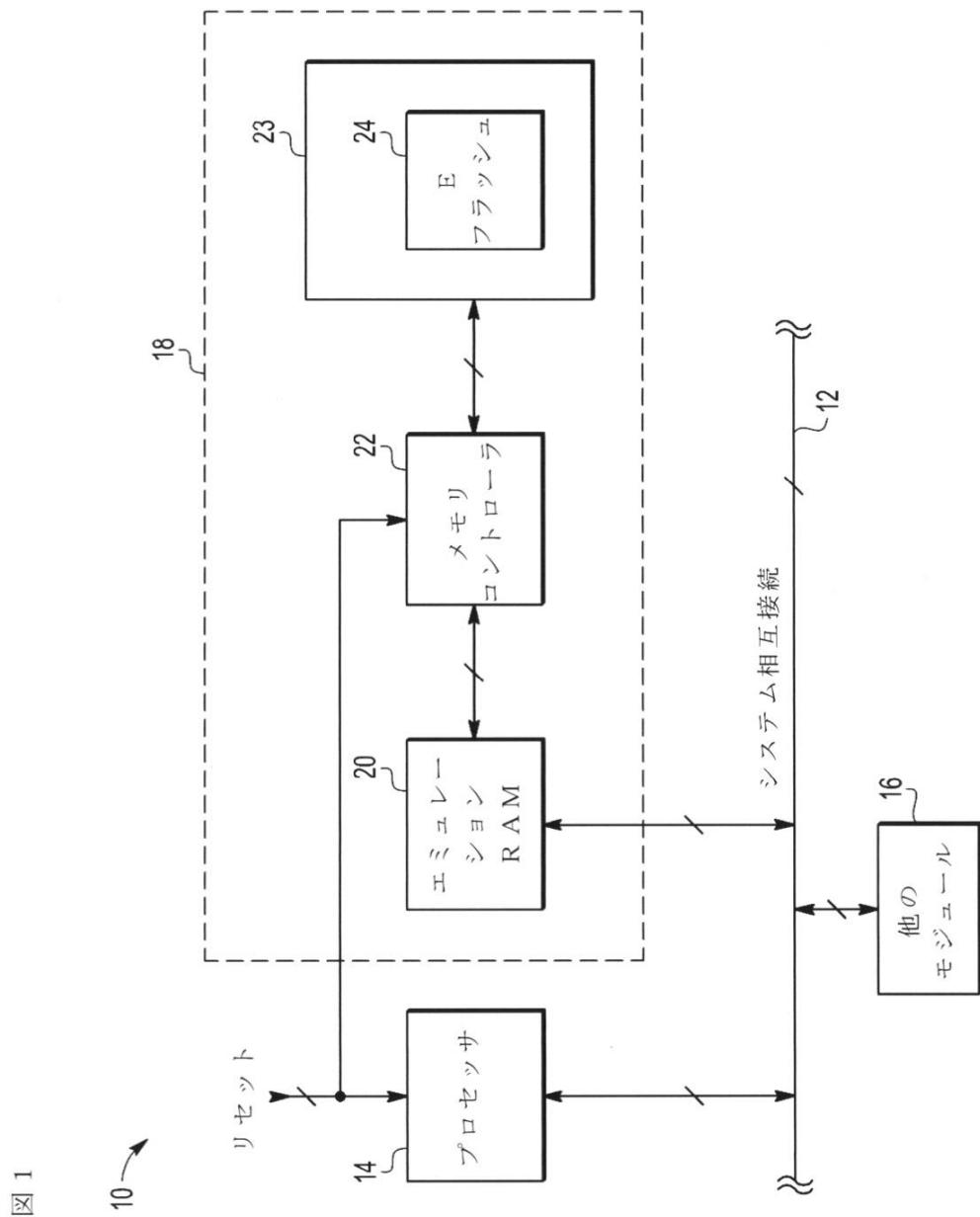

【図 1】本発明の一実施形態の実装に有用である、システム、不揮発性メモリを使用するエミュレート電気的消去可能メモリを示すブロック図である。 50

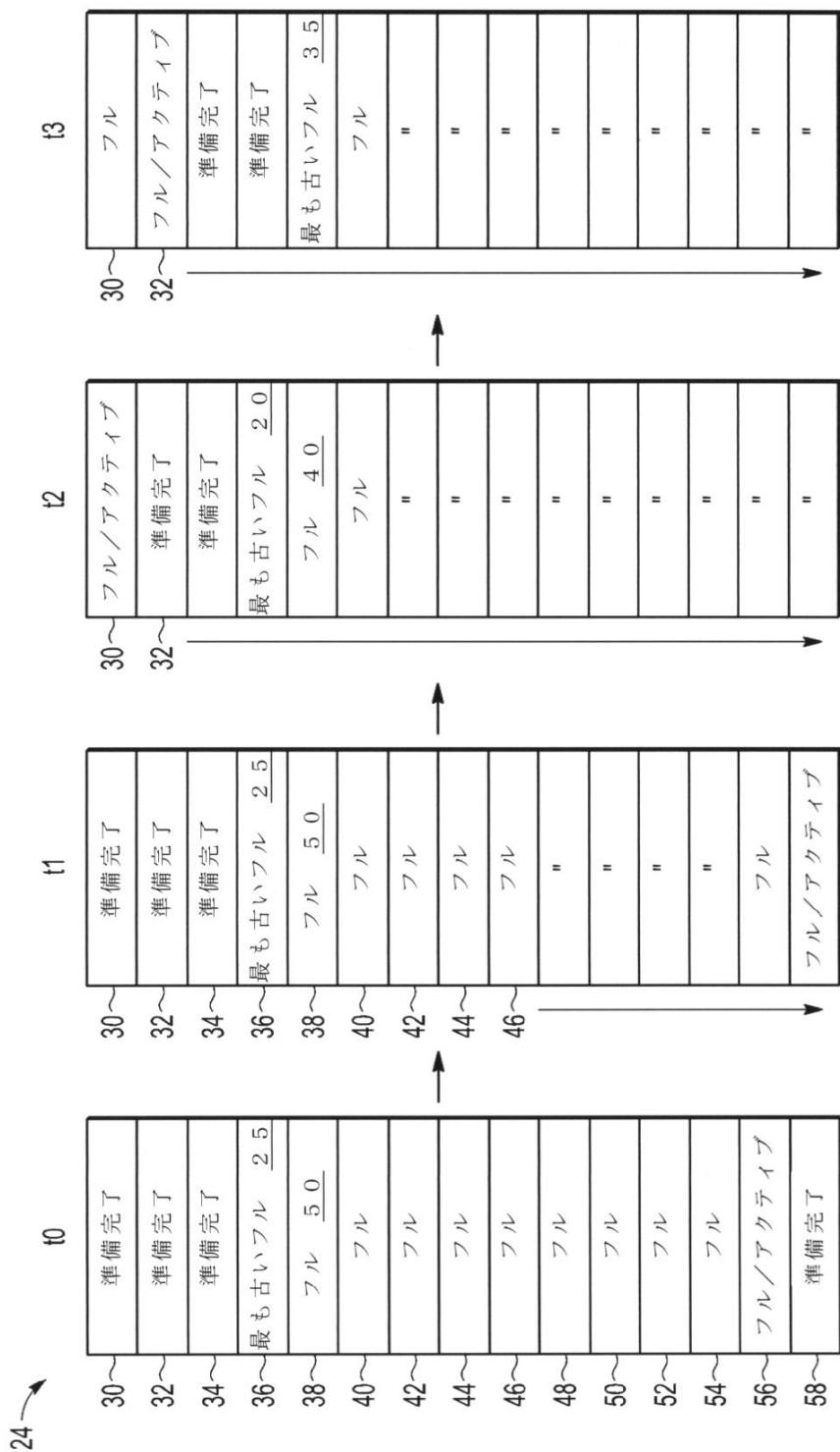

【図2】本実施形態による、動作状態が漸進的に示される不揮発性メモリのブロック図である。

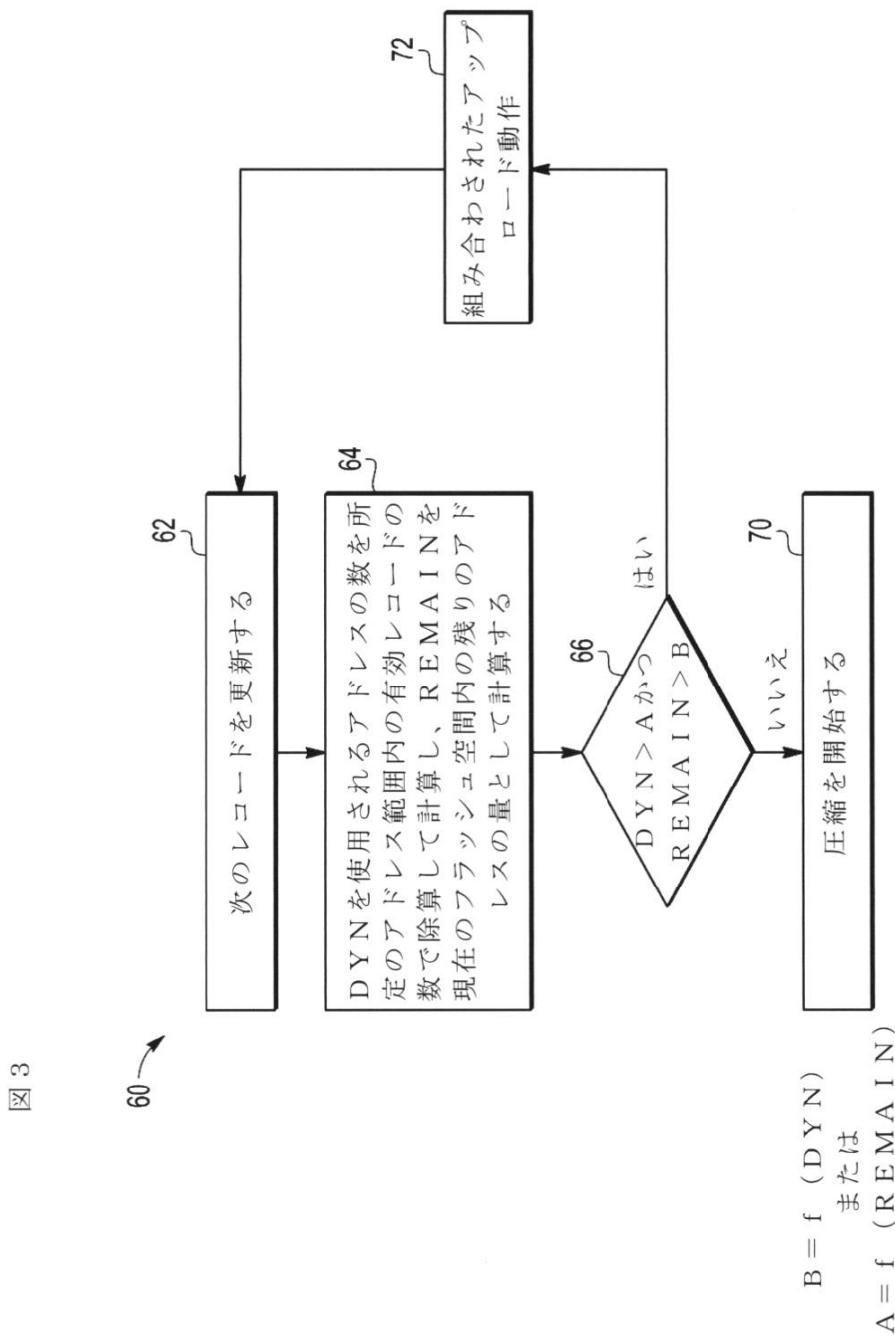

【図3】本実施形態を含むより包括的なソリューションを示す流れ図である。

【発明を実施するための形態】

【0005】

本発明は例として示されており、添付の図面によって限定されない。図面において、同様の参照符号は類似の要素を示す。図面内の要素は簡潔かつ明瞭にするために示されており、必ずしも原寸に比例して描かれてはいない。

【0006】

1つの態様において、エミュレート電気的消去可能(EEE)メモリは、RAMと、追加の容量を利用するため圧縮が使用されるRAMよりも大きい容量を有するNVMを有する。圧縮プロセスの開始のタイミングは、有益には、データが相対的に極めて動的であり、データの小さな部分が定期的に更新されるのではなくデータのほとんどが定期的に更新される場合には、遅延される。この圧縮の遅延が、特にデータが極めて動的である場合に、所与の量のNVMについてシステムの耐久性を向上させる。これは、図面および以下の明細書を参照することによってより良好に理解される。

【0007】

1つの実施形態では、フラッシュメモリがNVMとして使用される。1つの例では、そして本明細書において使用される場合、プログラミングとは、ビットセルに論理レベル0を記憶することを指し、消去とは、ビットセルに論理レベル1を記憶することを指す。しかしながら、代替の実施形態では、プログラミングがビットセルに論理レベル1を記憶することを指してもよく、消去がビットセルに論理レベル0を記憶することを指してもよい。論理レベル0は論理ローと称される場合もあり、論理レベル1は論理ハイと称される場合もある。

【0008】

本明細書において使用される場合、用語「バス」は、データ、アドレス、制御、またはステータスのような、1つまたは複数のさまざまなタイプの情報を伝送するために使用されることができる複数の信号または導体を指すために使用される。本明細書において論じられる導体は、単一の導体、複数の導体、一方向性導体、または双方向性導体であることに関連して例示または記載され得る。しかしながら、異なる実施形態は導体の実施態様を変更してもよい。例えば、双方向性導体ではなく別個の一方向性導体が使用されてもよく、その逆であってもよい。さらに、複数の導体が、並列にまたは時分割多重方式で複数の信号を伝送する单一の導体と置き換わってもよい。同様に、複数の信号を搬送する单一の導体は、これらの信号のサブセットを搬送するさまざまな異なる導体に分離されてもよい。それゆえ、信号の伝送には多くの選択肢が存在する。

【0009】

「アサート」または「セット」および「ネゲート」(または「アサート停止」もしくは「クリア」)という用語は、本明細書においては、信号、ステータスピット、または類似の装置をそれぞれ、その論理的に真または論理的に偽の状態にレンダリングすることを指す場合に使用される。論理的に真の状態が論理レベル1である場合、論理的に偽の状態は論理レベル0である。そして、論理的に真の状態が論理レベル0である場合、論理的に偽の状態は論理レベル1である。

【0010】

図1は、プロセッサ14と、主記憶装置を含むことができる他のモジュール(複数の場合もあり)16と、システム相互接続12と、EEEメモリシステム18(メモリシステムまたは不揮発性メモリシステムと称される場合もある)とを含むシステム10をブロック図形式で示す。プロセッサ14、他のモジュール(複数の場合もあり)16、およびEEEメモリシステム18の各々は、双方向的にシステム相互接続12に結合される。EEEメモリシステム18は、RAM20と、メモリコントローラ22と、Eフラッシュ24を含む不揮発性メモリ(NVM)23とを含む。RAM20は、システム相互接続12お

10

20

30

40

50

およびメモリコントローラ 22 に双方向的に結合される。メモリコントローラ 22 は NVM 23 に結合され、E フラッシュ 24 の動作を制御する。リセット信号がプロセッサ 14 およびメモリコントローラ 22 に提供される。このリセット信号は、例えば、システム 10 に対する全体的なリセット信号である。

#### 【0011】

プロセッサ 14 は、マイクロプロセッサ、デジタル信号プロセッサなどの任意のタイプのプロセッサであることができるか、または、EEE メモリシステム 18 にアクセスすることができる任意のタイプの相互接続マスタであってもよい。1つの形態では、システム相互接続 12 はシステムバスである。例えば、クロスバー、二点間接続、ならびに光および無線送信技法を含む他の形態の相互接続が使用されてもよい。他のモジュール 16 は、例えば、別のメモリ、別のプロセッサ、別の相互接続マスタ、周辺機器、入出力(I/O)デバイスなどのような、任意のタイプのモジュールを含んでもよい。代替的には、他のモジュールはシステム 10 内に存在しなくてもよい。

#### 【0012】

動作時、プロセッサ 14 はアクセス要求(読み出しまだ書き込みアクセス要求)をメモリシステム 18 に送ることができる。アクセスアドレス、および書き込み要求の場合には関連書き込みデータを含む、プロセッサ 14 からのアクセス要求は RAM 20 に提供される。読み出しアクセスの場合には、RAM 20 はプロセッサ 14 に、受け取られたアクセスアドレスのロケーションに記憶されているデータを提供する。書き込みアクセスの場合には、RAM 20 は受け取られた書き込みデータを、受け取られたアクセスアドレスのロケーションに記憶する。書き込みアクセスの場合には、メモリコントローラ 22 は、RAM 20 の更新を検出して、受け取られたアクセスアドレスおよび関連書き込みデータを E フラッシュ 24 に選択的に記憶することができる。例えば、RAM 20 に対する更新(書き込み)の場合、受け取られたアクセスアドレスおよび関連書き込みデータは、次の利用可能なロケーションにおいて E フラッシュ 24 に書き込まれるレコードを形成するために使用される。この次の利用可能なロケーションは、E フラッシュの直前のロードの間にロードされたロケーションに論理的に連続している。(なお、図 1 を参照して、受け取られたアクセスアドレスはアドレスとして NVM 23 に提供されることができ、関連書き込みデータはデータ入力として E フラッシュ 24 内に提供されることができる。) 1 つの例では、RAM 更新に対応するレコードの書き込みは、現在 RAM ロケーションに記憶されている値が、その RAM ロケーションに対する書き込みアクセス要求に関連付けられる新たな書き込み値と異なる場合にのみ実行される。このようにして、E フラッシュ 24 は、より永続的な様式で、更新されている RAM 20 の値を記憶することができる。この上記で説明された動作が、RAM 20 がエミュレーション RAM として示されている理由である。RAM 20 が電力を失うと、そのデータは失われる。電力が復旧すると、RAM の値はフラッシュメモリ 23 から復元されることができ、これは電源喪失時にそのデータを失わない。フラッシュメモリ 23 および E フラッシュ 24 は、RAM 20 よりも大きな記憶容量を有する。

#### 【0013】

RAM 20 は、2048 バイトを記憶するための容量を有する。E フラッシュメモリ 24 は 16 個のセクタを有し、各セクタが 256 個のレコードを記憶するための容量を有する。各レコードは 2 バイトを含み、この 2 バイトは RAM 20 において連続したロケーション内にある。フラッシュの利点は、高密度であることに起因する、そのコストの低さである。高密度アーキテクチャから生じるフラッシュの欠点は、消去がビット単位で、またはレコード単位でさえ利用可能でないことがある。本明細書において、セクタは、單一回の消去で消去ができるフラッシュメモリの最小単位とみなされる。單一回の消去は、50 個のような多数の消去パルスを使用して達成されることがある。各消去パルスは、消去される特定のセクタのすべてに印加される。従って、最初に、E フラッシュメモリ 24 は、すべての 1024 個のあり得る 2 バイトレコードの初期状態を記憶するために、4 つのセクタを満たすことになる。動作が継続するにつれて、フル / アクティブとし

10

20

30

40

50

て参照される、現在満たされているものを含む多数のセクタがデータで満たされることになる。別のグループのセクタは消去されて書き込まれる準備ができていることになり、これは、不揮発性メモリの場合はプログラムされる準備ができているものとして参照されることができる。データのほとんどが変更されておらず、小さな部分がほとんどの変更を受けている場合に対して保護するために、最も古いデータを有するセクタが消去される必用があるときに必要とされることになる大量の更新のために、4つのセクタを準備完了に維持しておくことが必要と考えられる。

#### 【0014】

図2には、セクタが書き込みおよび消去されるときのEフラッシュメモリ24の内容の進行が示されている。Eフラッシュ24は、セクタ30、32、34、36、38、40、42、44、46、48、50、52、54、56、および58(30～58)を含む。時刻t0は、セクタ36、38、40、42、44、46、48、50、52、および54が完全にデータで満たされており、セクタ56がフル/アクティブ状態にある、動作中の状態である。セクタ58、30、32および34は消去されて書き込まれる準備ができている。セクタ58は次に書き込まれることになる。この例における時刻t0は、セクタ56の書き込みの間の、圧縮を開始すべきか否かについて決定が為されるべき時刻である。これは、次の書き込みが、この場合はセクタ58である、次のセクタにおけるものであることになる状況であり得る。この場合における圧縮は、セクタを消去するプロセスであり、これは、書き込まれるために利用可能な空間を有するセクタ内に有効データを書き込むことを含む。この場合、次に消去されることになるセクタはセクタ36であり、これは、最も長い時間をさかのぼって書き込まれたデータを有するために最も古いセクタであると考えられる。セクタ38内のデータは、セクタ36内に書き込まれたデータよりも最近に書き込まれたデータを有する。従って、セクタ36内に存在する有効データは、まだ利用可能な空間がある場合はセクタ56内に、または利用可能な空間を有する次のセクタとしてセクタ58内に書き込まれる必要があることになる。時刻t0におけるこの例について図2に示されるように、最も古いセクタ、セクタ36は25個の有効レコードを有し、次に古いセクタ、セクタ38は50個の有効レコードを有する。セクタ36および38内のこれらの25個および50個の有効レコードは、それぞれ、定住レコード(sedentary record)と呼ばれる場合がある。セクタ30～58は各々256レコードの容量を有しており、25レコードおよび50レコードは極めて動的なレコードの例である。セクタ36を消去するために、25レコードのみが書き込まれる必要があることになり、同様にセクタ38を消去するためには50レコードのみが書き込まれる必要があることになる。セクタ56が完全に書き込まれていると想定するこの場合では、Eフラッシュ24内に書き込まれるために利用可能な4つのセクタが存在し、これは、時刻t0における現在のフラッシュ空間内に利用可能なアドレスが1024(4×256)だけ残っていることを意味し、これは利用可能な空間と呼ばれる場合がある。極めて動的なデータのこの事例では、利用可能な空間の量を所与としてセクタ36の圧縮を開始する必要はない。換言すれば、極めて動的なデータを所与とすると、必要よりも多くの利用可能な空間がある。動的アクティビティを計算する方法は、消去するために考慮されているアドレス空間内の使用されるレコードアドレスの総数を有効レコードの数で除算することである。従って、セクタ36について、時刻t0の場合、動的アクティビティは256/25である。動的アクティビティが高くなるほど、数も大きくなる。

#### 【0015】

時刻t1において示されるように、セクタ58はフル/アクティブセクタになっているが、高い動的アクティビティに起因して、最も古いセクタ、セクタ36内に存在する有効データのいずれもセクタ58内に書き込まれていない。従って、圧縮のプロセスは動的アクティビティならびにセクタ30、32、および34の利用可能な空間に起因して遅延されており、開始されていない。動作が継続するにつれて、セクタ58は、最終的に、圧縮が最も古いセクタに対して開始されるべきか否かについて決定が為される別の決定時刻に達するまでにデータ記入(filling up)を開始する。さらに動作中、セクタ3

10

20

30

40

50

6および38を含むさまざまなセクタ内の有効データのいくらかは更新されている場合があり、それらのセクタ内の有効データも低減している。

#### 【0016】

時刻  $t_2$  には、セクタ36および38の、それぞれ20および40の有効レコードの更新を示しており、セクタ36がここでも高い動的アクティビティに起因して圧縮を受けていないEフラッシュ24が示されている。このセクタ36に受けさせない決定は、セクタ38に関する相対的に高い動的アクティビティにも基づく。セクタ36に圧縮を受けさせることに関する別の決定時刻に達するまで動作は継続する。

#### 【0017】

時刻  $t_3$  においては、セクタ36が、その有効データをセクタ32に書き込まれることにより圧縮を受けており、消去されており、現在は準備ができているものとして示しているEフラッシュ24が示されている。セクタ32は現在はフル／アクティブセクタであり、セクタ58はフルである。これは、セクタ38内でもう5個多い有効レコードが別のセクタに対して更新されていることを示しており、それによって、現在セクタ38は35個の有効レコードを有する。セクタ36が時刻  $t_0$  において圧縮を受けており、その後時刻  $t_3$  においてセクタ38が圧縮を受けている場合、セクタ36について5回、セクタ38について5回の、少なくとも10回の追加の書き込みが実行されることになり、これは耐久性を低減する。

#### 【0018】

図3には、図1および図2のシステム10およびEフラッシュ24に適用されるプロセスを示す流れ図60が示されている。ステップ62において、次のレコードの更新が実行される。これが実行された後、ステップ64において、使用されるアドレスの数を所定のアドレス範囲内の有効レコードの数で除算することによって、動的アクティビティ(DYN)が計算される。この1つの例は、有り得るレコードの数を最も古いセクタ内の有効レコードの数で除算することである。この決定は、レコードが書き込まれる度に、または、フル／アクティブセクタが満たされるときのような何らかの他の時刻について為されることができる。さらに、ステップ64において、現在のEフラッシュ空間内の残りのアドレスの量(REMAIN)が計算され、これは、消去することなどによってより多くの空間を取得することなく、書き込まれるのに利用可能な空間の量である。これは、フル／アクティブセクタに加えて準備ができているセクタ内にレコードを書き込むために利用可能な空間の量であることができる。ステップ66において、圧縮を開始するか、または更新を継続するかについて決定が為される。DYNがしきい値Aを超え、かつREMAINがしきい値Bを超える場合、更新は継続される。DYNがどれだけ大きいかにかかわらず、利用可能な空間の量が非常に少なく、それによって圧縮を開始しなければならない時刻があることになる。図3において示されるように、しきい値Bはビジネスアクティビティ(business activity)の関数であるレベルにセットされることができる。代替的に、しきい値Aが利用可能な空間の関数であるレベルにセットされることがある。利用可能な空間は十分に大きくすることができ、それによって、有り得る最小の動的アクティビティでさえ、圧縮の開始を必要としないことになる。このDYNおよびREMAINの二重基準を達成する方法は、ルックアップテーブルを用いるものである。所与の利用可能な空間について、Aのしきい値はルックアップテーブル内に見出されることになる。同様に、所与の動的アクティビティについて、Bのしきい値はルックアップテーブル内に見出されることになる。

#### 【0019】

動的アクティビティを検知する別のある方法は、圧縮を受けていることを考慮した特定のアドレス範囲におけるアドレスの総数と比較した、その範囲にわたる更新された異なるアドレスの数である。

#### 【0020】

すなわち、NVMを有するエミュレーションメモリにおいて動的アクティビティを考慮に入れることによって、NVMの耐久性が向上されることができることが分かる。動的ア

10

20

30

40

50

クティビティが、そうでなければ永久的に為されている場合がある圧縮を遅延させることを可能にする状況があり、その結果、圧縮の実行の遅延から生じる耐久性の向上がもたらされる。

#### 【0021】

ここまでで、行われる際に大きな遅延を引き起こす大量のデータ伝送および完全消去プロセスを一斉に行う必要なしに、更新を実行するために利用可能な十分な空間があることを確実にするために、必要に応じ、各更新サイクルに関してデータ伝送の一部または書き込みプロセスの一部を行うことを可能にする方法が提供されたことが認識されるべきである。

#### 【0022】

方法であって、情報を記憶するための複数のセクタを有するエミュレーションメモリを有するとともに制御回路を有するシステムを使用する、方法が記載されている。方法は、使用されるアドレスの数をエミュレーションメモリの所定のアドレス範囲内の有効レコードの数で除算する計算を行って分数を算出することを含む。方法は、使用されるアドレスの数を上記エミュレーションメモリの所定のアドレス範囲内の有効レコードの数で除算する計算を行って分数を算出することをさらに含む。方法は、上記エミュレーションメモリの現在使用されている空間内の情報を記憶するために使用されていない残りのアドレスの量を計算することをさらに含む。方法は、計算された上記分数が第1の所定の数よりも大きいか否かを判定すること、および、上記残りのアドレスの量が第2の所定の数よりも大きいか否かを判定することをさらに含む。方法は、上記分数が上記第1の所定の数よりも大きく、かつ上記残りのアドレスの量が上記第2の所定の数よりも大きい場合には、上記エミュレーションメモリの上記現在使用されている空間を使用して任意の後続の更新要求に応答することをさらに含み、そうでない場合は上記エミュレーションメモリの圧縮が必要であると判断し、有効データを上記エミュレーションメモリの利用可能なセクタにコピーする。方法は、上記エミュレーションメモリの上記複数のセクタを2つのセクタとして実装することであって、上記2つのセクタのうちの第1のセクタは、利用されているアドレス指定済みの空間から成る第1の部分および残りのアドレスから成る第2の部分を有する、上記エミュレーションメモリの上記現在使用されている空間であり、上記2つのセクタのうちの第2のセクタは空の記憶空間である、実装することをさらに含むことができる。方法は、多重セクタによって、上記エミュレーションメモリの上記複数のセクタを実装することであって、上記エミュレーションメモリの第1の部分はデータを保持していない複数のセクタを有し、上記エミュレーションメモリの上記複数のセクタのうちの1つまたは複数は上記エミュレーションメモリの上記現在使用されている空間として割り当てられており、上記現在使用されている空間の一部は、情報を記憶するために使用されていない上記残りのアドレスの量である、実装することをさらに含むことができる。方法は、上記第1の所定の数を、現在情報を記憶していない上記エミュレーションメモリの上記現在使用されている空間内の上記残りの有効アドレスの量の関数である数として決定することをさらに含むことができる。方法は、上記第2の所定の数を、上記計算された分数の関数である数として決定することをさらに含むことができる。方法は、上記エミュレーションメモリ内のレコードの更新を求める要求に応答して上記使用されるアドレスの数を上記有効レコードの数で除算する計算を行うとともに、上記残りのアドレスの量を計算することをさらに含むことができる。方法は、上記圧縮が、上記複数のセクタのうちの最も古いフルセクタを消去すること、および、上記消去に続いて有効情報を上記最も古いフルセクタにコピーすることをさらに含むことをさらに特徴とすることができる。

#### 【0023】

さらに、エミュレーションメモリおよびメモリコントローラを含むシステムが記載されている。エミュレーションメモリは、情報を順次記憶するための複数のセクタを有する。上記メモリコントローラは上記エミュレーションメモリに結合され、使用されるアドレスの数を上記エミュレーションメモリの所定のアドレス範囲内の有効レコードの数で除算する計算を行って分数を算出し、上記エミュレーションメモリの現在使用されている空間内

10

20

30

40

50

の情報を記憶するために使用されていない残りのアドレスの量を計算し、計算された分數の割合が第1の所定の数よりも大きいか否かを判定し、上記残りのアドレスの量が第2の所定の数よりも大きいか否かを判定するためのものであり、上記分數の割合が上記第1の所定の数よりも大きく、かつ上記残りのアドレスの量が上記第2の所定の数よりも大きい場合には、上記メモリコントローラは、上記エミュレーションメモリの上記現在使用されている空間を使用して任意の後続の更新要求に応答し、そうでない場合は上記エミュレーションメモリの圧縮が必要であると判断し、有効データを上記エミュレーションメモリの利用可能なセクタにコピーする。上記エミュレーションメモリは2つのセクタをさらに含むことができ、上記2つのセクタのうちの第1のセクタは、利用されているアドレス指定済みの空間から成る第1の部分および残りのアドレスから成る第2の部分を有する、上記エミュレーションメモリの上記現在使用されている空間であり、上記2つのセクタのうちの第2のセクタは空の記憶空間である。上記エミュレーションメモリは多重セクタをさらに含み、上記エミュレーションメモリの第1の部分はデータを保持していない複数のセクタを有し、上記エミュレーションメモリの上記複数のセクタのうちの1つまたは複数は上記エミュレーションメモリの上記現在使用されている空間として割り当てられており、上記現在使用されている空間の一部は、情報を記憶するために使用されていない上記残りのアドレスの量である。システムは、上記メモリコントローラが、上記第1の所定の数を、現在情報を記憶していない上記エミュレーションメモリの上記現在使用されている空間内の上記残りの有効アドレスの量の関数である数として決定することをさらに特徴とすることができる。システムは、上記メモリコントローラが、上記第2の所定の数を、上記分數の割合の関数である数として決定することをさらに特徴とすることができる。システムは、上記メモリコントローラが、上記エミュレーションメモリ内のレコードの更新を求める要求に応答して上記使用されるアドレスの数を上記有効レコードの数で除算する計算を行い、上記残りのアドレスの量を計算することをさらに特徴とすることができる。システムは、上記メモリコントローラが、上記圧縮を、上記複数のセクタのうちの最も古いフルセクタを消去すること、および、上記消去に続いて有効情報を上記最も古いフルセクタにコピーすることによって実行することをさらに特徴とすることができる。システムは、上記メモリコントローラが、上記エミュレーションメモリ内のレコードの更新を求める要求に応答して上記計算を実行することをさらに特徴とすることができる。

#### 【0024】

方法であって、ランダムアクセスメモリ、情報を記憶するための複数のセクタを有するエミュレーションメモリ、およびメモリコントローラを有するシステムを使用する、方法も記載されている。方法は、第1の所定の回数を超えて更新された、上記エミュレーションメモリの所定のアドレス範囲内のレコードの数を計算することを含む。方法は、情報を記憶するために使用されていない、上記エミュレーションメモリの現在使用されている空間内の残りのアドレスの量を計算することをさらに含む。方法は、上記レコードの数が第2の所定の数よりも大きいか否かを判定すること、および、上記残りのアドレスの量が第3の所定の数よりも大きいか否かを判定することをさらに含む。方法は、上記レコードの数が上記第2の所定の数よりも大きく、かつ上記残りのアドレスの量が上記第3の所定の数よりも大きい場合には、上記エミュレーションメモリの上記現在使用されている空間を使用して任意の後続の更新要求に応答することをさらに含み、そうでない場合は上記エミュレーションメモリの圧縮が必要であると判断し、有効データを上記エミュレーションメモリの利用可能なセクタにコピーする。方法は、上記エミュレーションメモリの上記複数のセクタを2つのセクタとして実装することであって、上記2つのセクタのうちの第1のセクタは、利用されているアドレス指定済みの空間から成る第1の部分および残りのアドレスから成る第2の部分を有する、上記エミュレーションメモリの上記現在使用されている空間であり、上記2つのセクタのうちの第2のセクタは空の記憶空間である、実装することをさらに含むことができる。方法は、多重セクタによって、上記エミュレーションメモリの上記複数のセクタを実装することであって、上記エミュレーションメモリの第1の部分はデータを保持していない複数のセクタを有し、上記エミュレーションメモリの上記

複数のセクタのうちの 1 つまたは複数は上記エミュレーションメモリの上記現在使用されている空間として割り当てられており、上記現在使用されている空間の一部は、情報を記憶するために使用されていない上記残りのアドレスの量である、実装することをさらに含むことができる。方法は、上記第 2 の所定の数を、現在情報を記憶していない上記エミュレーションメモリの上記現在使用されている空間内の上記残りの有効アドレスの量の閾数である数として決定することをさらに含むことができる。方法は、上記第 3 の所定の数を、第 1 の所定の数を超えて更新された、エミュレーションメモリ内のレコードの一部の閾数である数として決定することをさらに含むことができる。方法は、上記エミュレーションメモリ内のレコードの更新を求める要求に応答して上記レコードの数を計算するとともに、上記残りのアドレスの量を計算することをさらに含むことができる。

10

#### 【 0 0 2 5 】

本発明を実装する装置は、大部分について、当業者に既知の電子コンポーネントおよび回路から構成されているため、本発明の基礎となる概念の理解および評価のために、ならびに本発明の教示を分かりにくくせず当該教示から注意を逸らせないために、回路の詳細は上記で例示されているように必要と考えられる範囲を超えては説明されない。

#### 【 0 0 2 6 】

さらに例として、1つの実施形態では、システム 10 の例示される要素は、単一の集積回路上または同じデバイス内に位置する回路である。代替的には、システム 10 は、互いに相互接続される任意の数の別個の集積回路または別個のデバイスを含んでもよい。例えば、EEPROM メモリシステム 18 は、プロセッサ 14 と同じ集積回路上に位置してもよく、または別個の集積回路上に位置してもよい。メモリシステム 18 は、埋め込みメモリシステムまたは独立型メモリシステムであってもよい。他のモジュール（複数の場合もあり）16 も、別個の集積回路またはデバイス上に位置してもよい。

20

#### 【 0 0 2 7 】

さらに、上述の動作の機能間の境界は例示にすぎないことを当業者は認識しよう。複数の動作の機能を单一の動作に組み合わせることができ、かつ / または単一の動作の機能を追加の動作に分散させることができる。その上、代替的な実施形態は、特定の動作の複数のインスタンスを含んでもよく、動作の順序はさまざまな他の実施形態においては変更してもよい。

#### 【 0 0 2 8 】

30

本明細書において、具体的な実施形態を参照して本発明を説明したが、添付の特許請求の範囲に明記されているような本発明の範囲から逸脱することなくさまざまな改変および変更を為すことができる。例えば、特定のメモリサイズ、セクタサイズ、およびレコードサイズが一例として説明されたが、他のサイズが使用されてもよい。従って、本明細書および図面は限定的な意味ではなく例示とみなされるべきであり、すべてのこのような改変が本発明の範囲内に含まれることが意図されている。本明細書において具体的な実施形態に関して記載されているいかなる利益、利点、または問題に対する解決策も、任意のまたはすべての請求項の重要な、必要とされる、または基本的な特徴または要素として解釈されるようには意図されていない。

#### 【 0 0 2 9 】

40

本明細書において使用される場合、「結合されている」という用語は、直接結合または機械的結合に限定されるようには意図されていない。

別途記載されない限り、「第 1 の」および「第 2 の」のような用語は、そのような用語が説明する要素間で適宜区別するように使用される。従って、これらの用語は必ずしも、このような要素の時間的なまたは他の優先順位付けを示すようには意図されていない。

【図1】

【図2】

図2

【図3】

---

フロントページの続き

(72)発明者 ベイカー、ジュニア フランク ケイ .

アメリカ合衆国 78735 テキサス州 オースティン リパブリック オブ テキサス ブル

バード 5700

(72)発明者 チャンドラセカラン、ベンカタギリ

アメリカ合衆国 78749 テキサス州 オースティン シャドウリッジ ラン 7500 ユ

ニット 47

審査官 塩澤 如正

(56)参考文献 特開2007-323212(JP,A)

特表2009-503744(JP,A)

米国特許出願公開第2003/0093711(US,A1)

米国特許出願公開第2005/0055496(US,A1)

米国特許出願公開第2007/0143528(US,A1)

欧州特許出願公開第01237085(EP,A1)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00 - G06F 12/06