(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3637332号

(P3637332)

(45) 発行日 平成17年4月13日(2005.4.13)

(24) 登録日 平成17年1月14日(2005.1.14)

(51) Int.C1.<sup>7</sup>

F 1

|                |               |         |

|----------------|---------------|---------|

| HO 1 L 29/78   | HO 1 L 29/78  | 3 O 1 G |

| HO 1 L 21/283  | HO 1 L 21/283 | B       |

| HO 1 L 21/318  | HO 1 L 21/318 | M       |

| HO 1 L 21/336  | HO 1 L 29/78  | 3 7 1   |

| HO 1 L 21/8242 | HO 1 L 29/58  | G       |

請求項の数 10 (全 32 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2002-155740 (P2002-155740)  |

| (22) 出願日  | 平成14年5月29日 (2002.5.29)        |

| (65) 公開番号 | 特開2003-347543 (P2003-347543A) |

| (43) 公開日  | 平成15年12月5日 (2003.12.5)        |

| 審査請求日     | 平成15年12月22日 (2003.12.22)      |

|           |                                       |

|-----------|---------------------------------------|

| (73) 特許権者 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100058479<br>弁理士 鈴江 武彦                |

| (74) 代理人  | 100084618<br>弁理士 村松 貞男                |

| (74) 代理人  | 100068814<br>弁理士 坪井 淳                 |

| (74) 代理人  | 100092196<br>弁理士 橋本 良郎                |

| (74) 代理人  | 100091351<br>弁理士 河野 哲                 |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                 |

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板と、

ゲート電極と、

前記半導体基板と前記ゲート電極との間に形成された第1の絶縁膜と、

前記ゲート電極の上面又は側面に沿って形成され、窒素、シリコン及び水素を含有した下層側シリコン窒化膜と、下層側シリコン窒化膜上に形成され、窒素、シリコン及び水素を含有した上層側シリコン窒化膜と、を含む第2の絶縁膜と、

を備えた半導体装置であって、

前記下層側シリコン窒化膜における窒素(N)とシリコン(Si)との組成比N/Siは1.32よりも高く、前記上層側シリコン窒化膜における窒素(N)とシリコン(Si)との組成比N/Siは1.32よりも低い

ことを特徴とする半導体装置。

## 【請求項2】

半導体基板と、

ゲート電極と、

前記半導体基板と前記ゲート電極との間に形成された第1の絶縁膜と、

前記ゲート電極に近接して形成され、窒素、シリコン及び水素を含有した下層側シリコン窒化膜と、下層側シリコン窒化膜上に形成され、窒素、シリコン及び水素を含有した上層側シリコン窒化膜と、を含む第2の絶縁膜と、

を備えた半導体装置であって、

前記下層側シリコン窒化膜に含有された水素の濃度の方が、前記上層側シリコン窒化膜に含有された水素の濃度よりも高い

ことを特徴とする半導体装置。

【請求項 3】

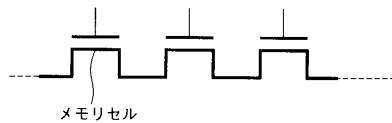

直列接続された複数のメモリセルを備えた半導体装置であって、

前記メモリセルは、

ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャネル領域と、を含む半導体基板と、

前記半導体基板上に形成された第1の絶縁膜と、

10

前記第1の絶縁膜上に形成され、前記半導体基板から前記第1の絶縁膜を通して注入された電荷を蓄積するものであって、1nm以上かつ4nm以下の厚さを有する下層側シリコン窒化膜と、下層側シリコン窒化膜上に形成された上層側シリコン窒化膜と、を含む第2の絶縁膜と、

前記第2の絶縁膜上に形成された第3の絶縁膜と、

前記第3の絶縁膜上に形成された制御ゲート電極と、

を備え、

前記下層側シリコン窒化膜における窒素(N)とシリコン(Si)との組成比N/Siは1.32よりも高く、前記上層側シリコン窒化膜における窒素(N)とシリコン(Si)との組成比N/Siは1.32よりも低い

20

ことを特徴とする半導体装置。

【請求項 4】

ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャネル領域と、を含む半導体基板と、

前記半導体基板上に形成された第1の絶縁膜と、

前記第1の絶縁膜上に形成され、前記半導体基板から前記第1の絶縁膜を通して注入された電荷を蓄積するものであって、1nm以上かつ4nm以下の厚さを有する下層側シリコン窒化膜と、下層側シリコン窒化膜上に形成された上層側シリコン窒化膜と、を含む第2の絶縁膜と、

前記第2の絶縁膜上に形成された第3の絶縁膜と、

30

前記第3の絶縁膜上に形成された制御ゲート電極と、

を備え、

前記第2の絶縁膜は、前記ソース領域近傍の第1の領域と、前記ドレイン領域近傍の第2の領域とを有し、前記第1の領域と第2の領域には互いに独立して電荷が蓄積され、

前記下層側シリコン窒化膜における窒素(N)とシリコン(Si)との組成比N/Siは1.32よりも高く、前記上層側シリコン窒化膜における窒素(N)とシリコン(Si)との組成比N/Siは1.32よりも低い

ことを特徴とする半導体装置。

【請求項 5】

前記下層側シリコン窒化膜と前記上層側シリコン窒化膜との界面における酸素濃度は1×10<sup>22</sup>/cm<sup>3</sup>よりも低い

40

ことを特徴とする請求項1乃至4のいずれかに記載の半導体装置。

【請求項 6】

半導体基板上に第1の絶縁膜を形成する工程と、

前記第1の絶縁膜を含む領域上に第2の絶縁膜を形成する工程と、

を備えた半導体装置の製造方法であって、

前記第2の絶縁膜を形成する工程は、

テトラクロロシランを含む第1のシリコンソースと、第1の窒素ソースとを用いて第1のシリコン窒化膜を形成する工程と、

前記第1のシリコン窒化膜上に、テトラクロロシラン以外の第2のシリコンソースと、

50

第 2 の窒素ソースとを用いて第 2 のシリコン窒化膜を形成する工程と、

を備え、

前記第 1 のシリコン窒化膜における窒素 (N) とシリコン (Si) との組成比 N / Si

は 1.32 よりも高く、前記第 2 のシリコン窒化膜における窒素 (N) とシリコン (Si)

との組成比 N / Si は 1.32 よりも低い

ことを特徴とする半導体装置の製造方法。

【請求項 7】

半導体基板上に第 1 の絶縁膜を形成する工程と、

前記第 1 の絶縁膜を含む領域上に第 2 の絶縁膜を形成する工程と、

を備えた半導体装置の製造方法であって、

前記第 2 の絶縁膜を形成する工程は、

テトラクロロシランを含む第 1 のシリコンソースと、第 1 の窒素ソースとを用いて第 1

のシリコン窒化膜を形成する工程と、

前記第 1 のシリコン窒化膜上に、テトラクロロシラン以外の第 2 のシリコンソースと、

第 2 の窒素ソースとを用いて第 2 のシリコン窒化膜を形成する工程と、

を備え、

前記第 1 のシリコン窒化膜と前記第 2 のシリコン窒化膜との界面における酸素濃度は 1

× 10<sup>22</sup> / cm<sup>3</sup> よりも低い

ことを特徴とする半導体装置の製造方法。

【請求項 8】

半導体基板と、

ゲート電極と、

前記半導体基板と前記ゲート電極との間に形成された第 1 の絶縁膜と、

前記ゲート電極に近接して形成され、窒素、シリコン及び水素を含有したシリコン窒化

膜を含む第 2 の絶縁膜と、

を備えた半導体装置であって、

前記シリコン窒化膜に含有された全水素の数に対する重水素の数の割合は 0.9 以上で

ある

ことを特徴とする半導体装置。

【請求項 9】

半導体基板上に第 1 の絶縁膜を形成する工程と、

前記第 1 の絶縁膜を含む領域上に第 2 の絶縁膜を形成する工程と、

を備えた半導体装置の製造方法であって、

前記第 2 の絶縁膜を形成する工程は、シリコンソースと重水素を含有した窒素ソースと

を用いてシリコン窒化膜を形成する工程を含む

ことを特徴とする半導体装置の製造方法。

【請求項 10】

半導体基板と、

制御ゲート電極と、

前記半導体基板と前記制御ゲート電極との間に形成され、シリコン、窒素及び窒素に結

合した重水素を含有したシリコン窒化膜と、

前記制御ゲート電極と前記シリコン窒化膜との間に形成され、前記半導体基板から前記

シリコン窒化膜を通して注入された電荷を蓄積する電荷蓄積膜と、

を備えたことを特徴とする半導体装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体装置及びその製造方法、特に半導体装置に設けられた絶縁膜に関する。

【0002】

【従来の技術】

10

20

30

40

50

シリコン窒化膜（SiN膜）は、半導体装置の種々の箇所に適用されている。しかしながら、ジクロロシラン（SiH<sub>2</sub>Cl<sub>2</sub>：DCS）を用いて成膜した従来のSiN膜は、次世代の半導体装置を製造する上で、様々な問題を引き起こすおそれがある。

#### 【0003】

一例として、デュアルゲートを採用した次世代のDRAMで生じる問題について説明する。次世代のDRAMでは、電極加工用のハードマスクとして、200nm程度の厚いSiN膜を用いる。DCSを用いたSiN膜（DCS-SiN膜）の場合、成膜後の高温工程によってボロンの拡散が増速されるため、PMOS素子が劣化してしまう。SiN膜起因のPMOS素子の劣化は、インテグレーション上の対策によってある程度緩和することが可能である。しかしながら、そのような対策は、トランジスタの性能を劣化させてしまうため、実際に行うのは困難である。したがって、より本質的な解決をはかるため、PMOS素子の劣化を起こさないSiN膜の開発が必要になっている。

#### 【0004】

DCS-SiN膜によって生じる素子の劣化は、テトラクロロシラン（SiCl<sub>4</sub>：TCS）を用いたSiN膜（TCS-SiN膜）を用いることで解決することが可能である。しかしながら、TCS-SiN膜は成膜速度が遅く、DCS-SiN膜の成膜速度の約1/3である。成膜速度は、成膜条件（成膜温度、成膜圧力等）を変えることによって、増加させることが一応可能である。しかしながら、膜の均一性を確保すること、膜質を劣化させないこと、ダストを抑制すること等の必要性から、成膜速度を増加させることは實際には困難である。したがって、TCS-SiN膜を用いた場合には、生産性が悪化してしまうという問題がある。

#### 【0005】

また、次世代のフラッシュメモリのセル構造として、シリコン窒化膜を電荷蓄積層として用いたMONOS型の素子が提案されている。MONOS素子は、半導体基板上にシリコン酸化膜（トンネル酸化膜、ボトム酸化膜）、シリコン窒化膜（電荷蓄積層）、シリコン酸化膜（トップ酸化膜）、電極を順次積層したものであり、M-O-N-O-S構造となる。電気的な情報（“0”又は“1”）の書き込みは、半導体基板からトンネル酸化膜を通してシリコン窒化膜に、電子又はホールを注入することによって行われる。

#### 【0006】

MONOS素子では、書き込み／消去ストレスによるデータ破壊が問題となる。また、NAND型の素子では、読み出しストレスによるデータ破壊が問題となる。不揮発性メモリでは、一般に、10万回の書き込み／消去を行った後、電荷を10年間保持する性能が求められているが、現状では十分な電荷保持特性が得られていない。

#### 【0007】

従来技術として、特開昭60-60770号公報には、電荷蓄積層として、水素含有量が互いに異なる2層のSiN膜を用いた構造が開示されている。成膜ガスには、シランとアンモニアを用いている。具体的には、Si-H結合が多いSiN膜を下層側に、Si-H結合が少ないSiN膜を上層側に設けることで、電荷保持特性が改善されるとしている。しかしながら、後述するように、このような構造が必ずしも最適な構造とは言えない。

#### 【0008】

特開平9-64205号公報には、電荷蓄積層として用いるSiN膜において、SiN膜の上面近傍にシリコン濃度のピークを、SiN膜の下面近傍に窒素濃度のピークを有する構造が開示されている。成膜ガスには、例えばDCSとアンモニアを用いている。具体的には、SiN膜の単層膜にシリコン及び窒素をイオン注入することで、シリコン及び窒素の濃度を調整している。しかしながら、SiN膜はDCS等を用いて形成された単層膜であり、このような構造も必ずしも最適とは言えない。

#### 【0009】

特公平5-48631号公報には、蓄積電荷層として、酸素を含有したシリコン窒化膜（シリコン酸窒化膜）を、ボトム酸化膜側に形成した構造が開示されている。このような構造により、電荷保持特性が向上するとされている。しかしながら、後述するように、このような構

10

20

30

40

50

造も必ずしも最適とは言えない。

【0010】

また、フラッシュメモリ等の不揮発性メモリでは、素子の微細化に伴ってトンネル絶縁膜の薄膜化が望まれている。トンネル絶縁膜としてシリコン酸化膜或いはシリコン酸窒化膜を用いた場合、直接トンネリングといわれるメカニズムによって、5MV/cm以下の低電界印加時にリーク電流が生じる。そのため、電荷保持特性が悪化してしまう。

【0011】

そこで、低電界リーク電流を低減するために、シリコン窒化膜をトンネル絶縁膜に用いることが提案されている（Non-Volatile Semiconductor Memory Workshop 1998、p.95、及び、Non-Volatile Semiconductor Memory Workshop 2001、p.67）。しかしながら、初期特性は優れているものの、書き込み／消去回数の増加にしたがって、徐々にSILC（Stress Induced Leakage Current）と呼ばれる低電界リーク電流が発生する。したがって、不揮発性メモリ素子としてのデータ保持能力が不十分である。

【0012】

【発明が解決しようとする課題】

上述したように、シリコン窒化膜をDCSを用いて形成した場合の問題は、TCSを用いることで解決可能であるが、TCSを用いた場合には、成膜速度を上げることが困難であるため、生産性が悪化するという問題があった。

【0013】

また、シリコン窒化膜を電荷蓄積層として用いた不揮発性メモリ素子が提案されているが、従来の構造では、満足できる電荷保持特性が得られないという問題があった。

【0014】

さらに、シリコン窒化膜を不揮発性メモリ素子のトンネル絶縁膜に用いることが提案されているが、従来の構造では、満足できる電荷保持特性が得られないという問題があった。

【0015】

本発明は、上記従来の課題に対してなされたものであり、シリコン窒化膜の構成や形成方法を改善することにより、特性等に優れた半導体装置及びその製造方法を提供することを目的としている。

【0016】

【課題を解決するための手段】

本発明に係る半導体装置は、半導体基板と、ゲート電極と、前記半導体基板と前記ゲート電極との間に形成された第1の絶縁膜と、前記ゲート電極の上面又は側面に沿って形成され、窒素、シリコン及び水素を含有した下層側シリコン窒化膜と、下層側シリコン窒化膜上に形成され、窒素、シリコン及び水素を含有した上層側シリコン窒化膜と、を含む第2の絶縁膜と、を備えた半導体装置であって、前記下層側シリコン窒化膜における窒素（N）とシリコン（Si）との組成比N/Siの方が、前記上層側シリコン窒化膜における窒素（N）とシリコン（Si）との組成比N/Siよりも高いことを特徴とする。

【0017】

また、本発明に係る半導体装置は、半導体基板と、ゲート電極と、前記半導体基板と前記ゲート電極との間に形成された第1の絶縁膜と、前記ゲート電極に近接して形成され、窒素、シリコン及び水素を含有した下層側シリコン窒化膜と、下層側シリコン窒化膜上に形成され、窒素、シリコン及び水素を含有した上層側シリコン窒化膜と、を含む第2の絶縁膜と、を備えた半導体装置であって、前記下層側シリコン窒化膜に含有された水素の濃度の方が、前記上層側シリコン窒化膜に含有された水素の濃度よりも高いことを特徴とする。

【0018】

また、本発明に係る半導体装置は、直列接続された複数のメモリセルを備えた半導体装置であって、前記メモリセルは、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャネル領域と、を含む半導体基板と、前記半導体基板上に形成された第1の絶縁膜と、前記第1の絶縁膜上に形成され、前記半導体基板から前記第1の

10

20

30

40

50

絶縁膜を通して注入された電荷を蓄積するものであって、1 nm以上かつ4 nm以下の厚さを有する下層側シリコン窒化膜と、下層側シリコン窒化膜上に形成された上層側シリコン窒化膜と、を含む第2の絶縁膜と、前記第2の絶縁膜上に形成された第3の絶縁膜と、前記第3の絶縁膜上に形成された制御ゲート電極と、を備えたことを特徴とする。

【0019】

また、本発明に係る半導体装置は、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とに挟まれたチャネル領域と、を含む半導体基板と、前記半導体基板上に形成された第1の絶縁膜と、前記第1の絶縁膜上に形成され、前記半導体基板から前記第1の絶縁膜を通して注入された電荷を蓄積するものであって、1 nm以上かつ4 nm以下の厚さを有する下層側シリコン窒化膜と、下層側シリコン窒化膜上に形成された上層側シリコン窒化膜と、を含む第2の絶縁膜と、前記第2の絶縁膜上に形成された第3の絶縁膜と、前記第3の絶縁膜上に形成された制御ゲート電極と、を備え、前記第2の絶縁膜は、前記ソース領域近傍の第1の領域と、前記ドレイン領域近傍の第2の領域とを有し、前記第1の領域と第2の領域には互いに独立して電荷が蓄積されることを特徴とする。

【0020】

本発明に係る半導体装置の製造方法は、半導体基板上に第1の絶縁膜を形成する工程と、前記第1の絶縁膜を含む領域上に第2の絶縁膜を形成する工程と、を備えた半導体装置の製造方法であって、前記第2の絶縁膜を形成する工程は、テトラクロロシランを含む第1のシリコンソースと、第1の窒素ソースとを用いて第1のシリコン窒化膜を形成する工程と、前記第1のシリコン窒化膜上に、テトラクロロシラン以外の第2のシリコンソースと、第2の窒素ソースとを用いて第2のシリコン窒化膜を形成する工程と、を備えたことを特徴とする。

【0021】

また、本発明に係る半導体装置は、半導体基板と、ゲート電極と、前記半導体基板と前記ゲート電極との間に形成された第1の絶縁膜と、前記ゲート電極に近接して形成され、窒素、シリコン及び水素を含有したシリコン窒化膜を含む第2の絶縁膜と、を備えた半導体装置であって、前記シリコン窒化膜に含有された全水素の数に対する重水素の数の割合は0.9以上であることを特徴とする。

【0022】

また、本発明に係る半導体装置の製造方法は、半導体基板上に第1の絶縁膜を形成する工程と、前記第1の絶縁膜を含む領域上に第2の絶縁膜を形成する工程と、を備えた半導体装置の製造方法であって、前記第2の絶縁膜を形成する工程は、シリコンソースと重水素を含有した窒素ソースとを用いてシリコン窒化膜を形成する工程を含むことを特徴とする。

【0023】

また、本発明に係る半導体装置は、半導体基板と、制御ゲート電極と、前記半導体基板と前記制御ゲート電極との間に形成され、シリコン、窒素及び窒素に結合した重水素を含有したシリコン窒化膜と、前記制御ゲート電極と前記シリコン窒化膜との間に形成され、前記半導体基板から前記シリコン窒化膜を通して注入された電荷を蓄積する電荷蓄積膜と、を備えたことを特徴とする。

【0024】

【発明の実施の形態】

以下、本発明の実施形態を図面を参照して説明する。

【0025】

【実施形態1】

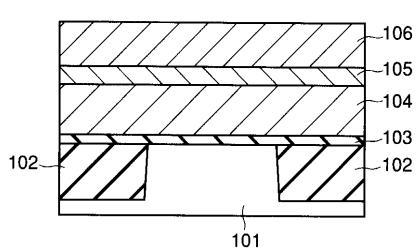

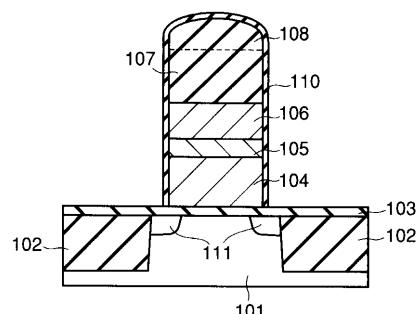

図1～図5は、本発明の第1の実施形態に係る半導体装置（MISトランジスタ）の製造方法を示した断面図である。

【0026】

まず、図1に示すように、シリコン基板101上に、素子分離領域102及びゲート絶縁膜103を形成する。ゲート絶縁膜103は、厚さ4.5nmのシリコン酸窒化膜である。続

10

20

30

40

50

いて、ゲート絶縁膜103上に、ゲート電極として、アモルファスシリコン膜104(70nm)、窒化タンゲステン膜105(5nm)及びタンゲステン膜106(40nm)の積層構造を形成する。アモルファスシリコン膜104中には、PMOS領域においてはp型不純物が、NMOS領域においてはn型不純物が添加されている。例えば、PMOS領域には、5keV、 $5 \times 10^{14} \sim 1 \times 10^{16} \text{ cm}^{-2}$ の条件でボロンがイオン注入されており、NMOS領域には、10keV、 $5 \times 10^{14} \sim 1 \times 10^{16} \text{ cm}^{-2}$ の条件でリンがイオン注入されている。このようにすることにより、PMOSのゲート電極には、ボロンが $1 \times 10^{19} / \text{cm}^3$ よりも多く且つ $1 \times 10^{21} / \text{cm}^3$ よりも少なく導入される。

#### 【0027】

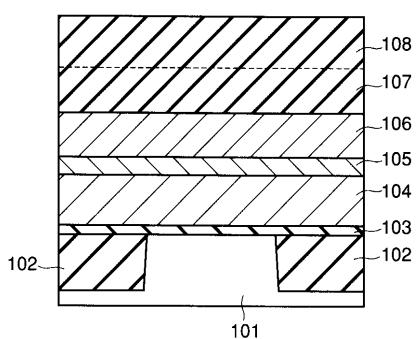

次に、図2に示すように、減圧化学気相成長(LP-CVD)法により、シリコン窒化膜(SiN膜)107及び108を、合計厚さ200nm形成する。SiN膜107及び108は、ゲート電極加工用のハードマスクである。SiN膜107及び108は、以下のようにして形成する。

#### 【0028】

まず、テトラクロロシラン(SiCl<sub>4</sub>:TCS)及びアンモニア(NH<sub>3</sub>)を用いてSiN膜107を形成する。成膜条件は、温度700~900、圧力0.01~10Torr、TCS流量/NH<sub>3</sub>流量比0.01~10である。TCSを用いたSiN膜(TCS-SiN膜)の成膜速度は、1nm/minである。成膜時間は80分であり、厚さ80nmのSiN膜107を形成した。続いて、ジクロロシラン(SiH<sub>2</sub>Cl<sub>2</sub>:DCS)及びアンモニアを用いて、SiN膜108を形成する。成膜条件は、温度600~900、圧力0.01~10Torr、DCS/NH<sub>3</sub>流量比0.01~10である。DCSを用いたSiN膜(DCS-SiN膜)の成膜速度は、3.2nm/minである。成膜時間40分であり、厚さ120nmのSiN膜108を形成した。なお、DCS-SiN膜108は、TCS-SiN膜107を形成した後、基板を大気に晒さずに同一炉内で連続的に形成する。

#### 【0029】

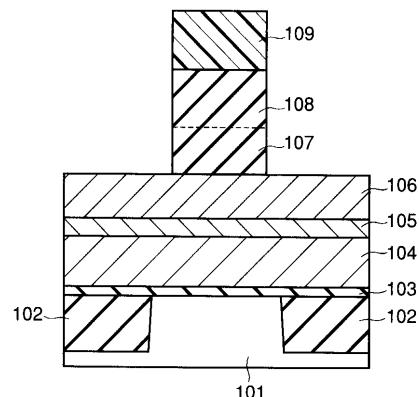

次に、図3に示すように、フォトリソグラフィ技術によってパターニングされたレジスト膜109を形成する。続いて、レジスト109をマスクとして、SiN膜107及び108をドライエッチングする。その後、レジスト109を除去する。

#### 【0030】

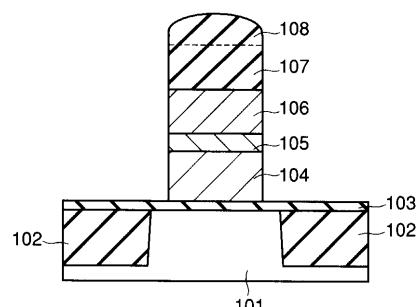

次に、図4に示すように、SiN膜107及び108をハードマスクとして、通常のドライエッチング技術を用いて、タンゲステン膜106、窒化タンゲステン膜105及びアモルファスシリコン膜104を、順次エッチングする。このとき、SiN膜108の上部はドライエッチングにより削られ、SiN膜107及び108の合計膜厚は130nm程度になる。

#### 【0031】

ここで、SiN膜を2層に分けて形成する理由を述べる。

#### 【0032】

SiN形成工程後には、不純物を活性化するための高温工程が複数回行われる。この高温工程において、電極上にDCS-SiN膜のみを形成した場合には、PMOS素子が劣化してしまう。高温工程により、電極中のボロンが、ゲート絶縁膜を突き抜けてシリコン基板まで拡散してしまうためである。このようなSiN膜起因のボロンの拡散は、TCS-SiNを適用することにより抑制することができる(M. Tanaka et al., 10-1, 2001 Symposium on VLSI Symposium, Digest of Technical Papers 参照)。つまり、TCS-SiNを用いることにより、素子特性には影響を与えることなく、ボロンの拡散を抑制することができる。

#### 【0033】

しかしながら、TCS-SiN膜のみを用いた場合には、生産性が著しく悪くなってしまう。TCS-SiN膜の成膜速度は、DCS-SiNの1/3程度である。例えば、200nmのSiN膜をTCSを用いて形成しようとすると200分程度かかり、DCSの場合(60分程度)に比べて、生産性が著しく損なわれてしまう。また、TCSは1分子あたり4個の塩

素を持っているため、化学反応によって  $\text{NH}_4\text{Cl}$  が DCS に比べて2倍生成される。 $\text{NH}_4\text{Cl}$  は固体であり、装置の排気系にダメージを与える。つまり、 $\text{NH}_4\text{Cl}$  が、配管を塞いだり、ダストとして排気ポンプ内に付着したりする。そのため、TCS を用いた場合には、メンテナンス頻度が著しく増加し、生産性を悪化させてしまう。したがって、高性能素子を実現するために TCS は必須であるが、生産性を悪化させてしまうという問題がある。

#### 【0034】

ここで、図4に注目すると、200nmの厚さで形成した  $\text{SiN}$  膜は、ゲート電極形成後には130nm程度しか残っていない。したがって、TCSのみで200nm形成する必要は無いことがわかる。そのため、電気特性に影響を及ぼす成膜初期にはTCSを用いて  $\text{SiN}$  膜を形成し、実質的にマスクとして機能する成膜後期にはDCSを用いることにより、生産性を向上させることができる。ここで考慮すべき点は、ボロンの拡散に起因するPMOS素子の劣化が生じない程度の厚さでTCS-SiNを形成する必要がある、ということである。つまり、素子特性と生産性とは、トレードオフの関係にある。

#### 【0035】

2層の  $\text{SiN}$  膜の膜厚比と素子特性の相関を検討した結果、TCS/DCSが80nm/120nmである場合、つまり  $\text{TCS/DCS} = 0.67$  の場合には、素子特性に問題が生じない。上述した例では、TCSのみで成膜した場合の成膜時間を、約40%減らすことが可能である。

#### 【0036】

ゲート電極を形成した後、側壁酸化を行う。後酸化は、タンゲステン膜106が露出する構造であることから、窒素、水素及び水の混合雰囲気中において、800、30分行う。

#### 【0037】

次に、図5に示すように、パターニングされたレジスト（図示せず）をマスクとして、セル領域、NMOS領域及びPMOS領域におけるソース/ドレイン領域111に不純物のイオン注入を行う。さらに、不純物を活性化するためのアニールを、窒素雰囲気中において、850、10秒行う。

#### 【0038】

次に、絶縁用の  $\text{SiN}$  膜110を20nm形成する。この  $\text{SiN}$  膜110は、ゲート電極と、ソース/ドレイン領域111に接続されるコンタクト電極（図示せず）との間の、リークを防止するためのものである。まずTCSを用いて下層側の  $\text{SiN}$  膜を10nm形成し、続いてDCSを用いて上層側の  $\text{SiN}$  膜を10nm形成する。DCS-SiN膜は、TCS-SiN膜を形成した後、基板を大気に晒さずに連続的に形成する。成膜条件は、いずれも、成膜温度700、成膜圧力0.5Torr、シリコンソース流量（DCS或いはTCS）100sccm、アンモニア流量1000sccmとする。この成膜条件における成膜速度は、DCSで0.8nm/min、TCSで0.3nm/minであった。その後、ドライエッ칭を行って底面の  $\text{SiN}$  膜を除去することにより、ゲート電極の周囲に選択的に  $\text{SiN}$  膜110を残す。

#### 【0039】

$\text{SiN}$  膜110は、ボロンが添加されたシリコン膜104に直接接している。そのため、先述した理由により、TCS-SiN膜とDCS-SiN膜との積層構造の適用が有効となる。検討結果によれば、TCS/DCSが10nm/10nm（膜厚比1.0）であれば、十分にボロンの拡散を抑制することできる。よって、TCS/DCSの膜厚比を1.0以下にすれば、生産性を向上させるとともに、ボロンの拡散を抑えることができる。

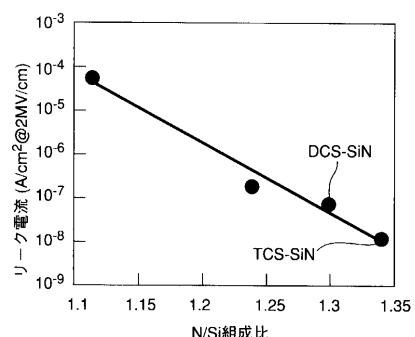

#### 【0040】

また、TCS-SiN膜を適用することにより、リークを低減することができる。TCS-SiN膜は、DCS-SiN膜に比べて、N/Si組成比が高い。すなわち、TCS-SiN膜は、DCS-SiN膜よりも窒素リッチであり、ストイキオメトリーに近い。

#### 【0041】

図6は、 $\text{SiN}$  膜におけるN/Si組成比とリーク電流との関係を示したものである。TCS-SiN膜のN/Si組成比は約1.34であり、DCS-SiN膜のN/Si組成比は約

10

20

40

50

1.30である。この図からわかるように、N/Si組成比が高くなり、シリコン窒化膜のストイキオメトリー(4/3)に近づくにしたがって、リーク電流が減少することがわかる。

#### 【0042】

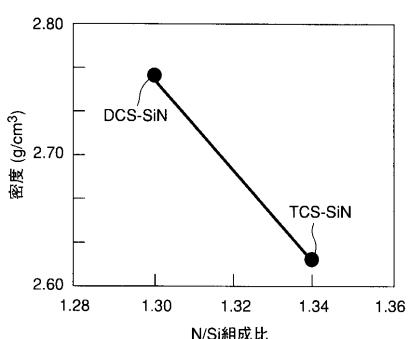

図7は、SiN膜におけるN/Si組成比と密度との関係を示したものである。TCS-SiN膜の密度は約2.62g/cm<sup>3</sup>であり、DCS-SiN膜の密度は約2.76g/cm<sup>3</sup>である。N/Si組成比が高いほど、密度が小さくなることがわかる。また、密度が小さいことから、TCS-SiN膜の比誘電率(6.8)は、DCS-SiN膜の比誘電率(7.4)より小さい。したがって、TCS-SiN膜を適用することにより、寄生容量を低減することが可能である。

10

#### 【0043】

しかしながら、図5に示したSiN膜110にTCS-SiN膜のみを用いた場合には、リーク電流の低減が実現できなくなってしまう。ゲート電極の近傍にはコンタクト電極が形成されるため、TCS-SiN膜にポリシリコン膜104が接する構造になる。コンタクト電極形成後には、活性化のための高温工程が行われる。TCS-SiN膜は、窒素が過剰に含有されているため、ポリシリコンとの反応性が高い。そのため、高温工程によって、TCS-SiN膜中の窒素がポリシリコン側に拡散してしまう。その結果、SiN膜110としてTCS-SiN膜の単層構造を用いた場合には、高温工程後にリーク電流が増加するという問題が生じる。

#### 【0044】

本例では、TCS-SiN膜形成後にDCS-SiN膜を形成するため、SiN膜110とポリシリコン膜104との反応性を低くすることが可能となり、リーク電流低減が可能となる。また、TCS-SiNとDCS-SiN膜との積層構造を用いることで、TCS-SiN単層の場合に比べて、成膜時間を約40%短縮することができる。

20

#### 【0045】

以上のように、本実施形態では、下層側のTCS-SiN膜と上層側のDCS-SiN膜の2層構造を用いることにより、ボロン拡散の抑制及びリーク電流の低減をはかることができるとともに、生産性を高めることができる。

#### 【0046】

なお、下層側のSiN膜と上層側のSiN膜に関しては、一般的に以下の態様が可能である。なお、これらの態様は、後述する第2乃至第7の実施形態についても同様に適用可能である。

30

#### 【0047】

図6及び図7に示されるように、TCS-SiN膜のN/Si組成比は約1.34であり、DCS-SiN膜のN/Si組成比は約1.30である。したがって、下層側のSiN膜の組成比N/Siは1.32よりも高く、上層側のSiN膜の組成比N/Siは1.32よりも低いことが好ましい。また、組成比N/Siが1.32のときのSiN膜の密度は約2.68g/cm<sup>3</sup>である。したがって、下層側のSiN膜の密度は2.68g/cm<sup>3</sup>よりも低く、上層側のSiN膜の密度は2.68g/cm<sup>3</sup>よりも高いことが好ましい。

#### 【0048】

40

また、後述するように(図21参照)、TCS-SiN膜に含有された水素の濃度は約 $7 \times 10^{21}/\text{cm}^3$ であり、DCS-SiN膜に含有された水素の濃度は約 $3 \times 10^{21}/\text{cm}^3$ である。したがって、下層側のSiN膜に含有された水素の濃度は $5 \times 10^{21}/\text{cm}^3$ よりも高く、上層側のSiN膜に含有された水素の濃度は $5 \times 10^{21}/\text{cm}^3$ よりも低いことが好ましい。なお、水素には、重水素(D)等の水素の同位体が含まれていてもよい。

#### 【0049】

また、TCS及びDCSには塩素が含有されていることから、TCS-SiN膜及びDCS-SiN膜にも塩素が含有されており、通常それらの塩素濃度は $1 \times 10^{19}/\text{cm}^3$ よりも高い。

#### 【0050】

50

また、DCSはSi-H結合を有しているが、TCSはSi-H結合を有していない。そのため、DCS-SiN膜は多くのSi-H結合を有しているのに対し、TCS-SiN膜はSi-H結合が少ない。フーリエ変換型赤外吸収法(FT-IR法)を用いた分析によれば、DCS-SiN膜ではSi-H結合の密度が $1 \times 10^{20}/\text{cm}^3$ よりも高いのに対し、TCS-SiN膜ではSi-H結合は観察されなかった。したがって、TCS-SiN膜では、Si-H結合の密度は $1 \times 10^{20}/\text{cm}^3$ よりも低いと考えられる。

#### 【0051】

また、下層側のSiN膜及び上層側のSiN膜には、酸素が含有されていてもよい。ただし、下層側のSiN膜と上層側のSiN膜は、大気に晒さずに連続的に形成することが好み。この場合、後述するように(図22参照)、下層側のSiN膜と上層側のSiN膜との界面における酸素濃度は $1 \times 10^{22}/\text{cm}^3$ よりも低くなる。

10

#### 【0052】

また、上層側のSiN膜には、DCSの代わりにシラン(SiH<sub>4</sub>)或いはヘキサクロロジシラン(HCD:Si<sub>2</sub>Cl<sub>6</sub>)で成膜したSiN膜を用いることも可能である。

#### 【0053】

##### [実施形態2]

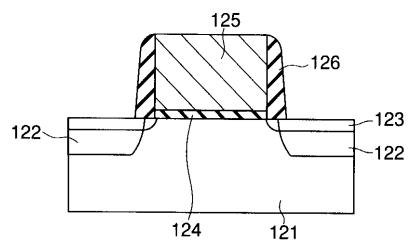

図8～図12は、本発明の第2の実施形態に係る半導体装置(MISトランジスタ)の製造方法を示した断面図である。

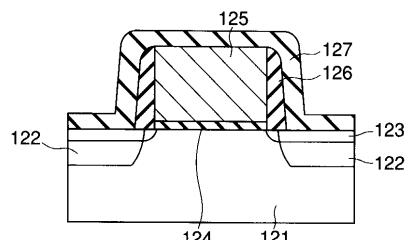

#### 【0054】

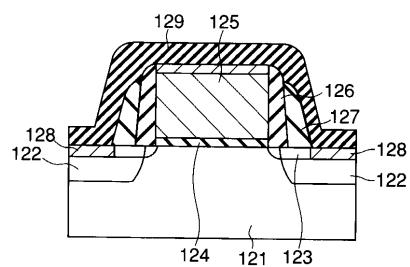

まず、図8に示すように、通常の方法を用いて、シリコン基板121上に、素子分離領域(図示せず)、ゲート絶縁膜124、ゲート電極125、側壁絶縁膜126、エクステンション領域123及びソース/ドレイン領域122を形成する。ゲート電極125はアモルファスシリコン膜で形成されており、アモルファスシリコン膜中には、PMOS領域においてはp型不純物が、NMOS領域においてはn型不純物が添加されている。アモルファスシリコン膜への不純物のイオン注入は、ソース/ドレイン領域122へのイオン注入と同時に進行。例えば、PMOS領域には、7keV、 $5 \times 10^{14} \sim 1 \times 10^{16}/\text{cm}^2$ の条件でボロンがイオン注入されており、NMOS領域には、65keV、 $5 \times 10^{14} \sim 1 \times 10^{16}/\text{cm}^2$ の条件で砒素がイオン注入されている。側壁絶縁膜126は、TEOSを用いて形成したシリコン酸化膜(SiO<sub>2</sub>膜)である。このようにすることにより、PMOSのゲート電極には、ボロンが $1 \times 10^{19}/\text{cm}^3$ よりも多く且つ $1 \times 10^{21}/\text{cm}^3$ よりも少なく導入される。

20

#### 【0055】

次に、図9に示すように、LPCVD法により、SiN膜127を厚さ70nm形成する。このSiN膜127は、下層側のTCS-SiN膜と上層側のDCS-SiN膜の積層構造である。まずTCSを用いて下層側のSiN膜を形成する。成膜条件は、温度700～900、圧力0.01～10Torr、TCS/NH<sub>3</sub>流量比0.01～10である。TCS-SiN膜の成膜速度は、1nm/minである。成膜時間は20分であり、厚さ20nmのTCS-SiN膜を形成する。続いて、DCSを用いて上層側のSiN膜を形成する。成膜条件は、温度600～900、圧力0.01～10Torr、DCS/NH<sub>3</sub>流量比0.01～1である。DCS-SiN膜の成膜速度は、3.2nm/minである。成膜時間は16分であり、厚さ50nmのDCS-SiN膜を形成する。なお、DCS-SiN膜は、TCS-SiN膜を形成した後、基板を大気に晒さずに連続的に形成する。

30

#### 【0056】

次に、図10に示すように、ドライエッティング技術により、ゲート電極の側壁上に選択的にSiN膜127を残す。側壁上に残ったSiN膜127の最大膜厚は50nm程度である。側壁SiN膜127は、シリサイドブロックとして機能するとともに、薬液処理時のエッティングストッパーとして機能する。つまり、側壁SiN膜127により、ゲート電極125とソース/ドレイン領域122上のコバルトシリサイドとの架橋反応が抑制され、かつ接合リーケの増加が抑制される。側壁SiN膜127が無い場合には、コバルトシリサイド工程前の前処理によってTEOS-SiO<sub>2</sub>膜が後退する。そのため、より電極近傍にまでコバルトシリサイドが形成されてしまい、接合リーケが増えてしまう。

40

50

## 【0057】

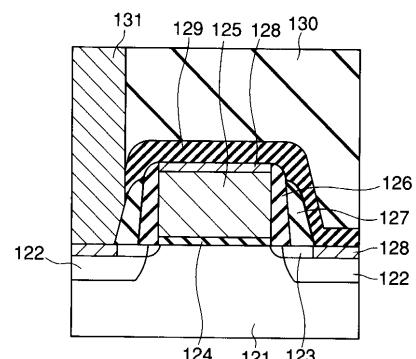

次に、図11に示すように、コバルト膜をスパッタリング法により形成する。続いて、800、30秒程度の熱工程によってコバルトとシリコンを反応させ、コバルトシリサイド膜128を形成する。さらに、シリサイド化されなかったコバルト膜を除去した後、LPCVD法によりSiN膜129を40nm形成する。このSiN膜129は、コンタクト孔を開ける時のエッチングストッパーとして機能する。

## 【0058】

次に、図12に示すように、プラズマを用いた成膜法により、層間絶縁膜としてシリコン酸化膜(TEOS-SiO<sub>2</sub>膜)130を200nm形成する。さらに、CMP法によりシリコン酸化膜130の表面を平坦化する。その後、レジストパターン(図示せず)及びSiN膜127をマスクにして、コンタクト孔を自己整合的に形成する。さらに、コンタクト孔内に導電材料を埋め込んで、コンタクト電極131を形成する。

10

## 【0059】

SiN膜127をDCS-SiN膜のみで形成した場合には、ボロンの拡散により、ゲート電極の空乏化、界面準位の増加及び電界-温度ストレスに対する耐性の劣化等が生じる。高性能化のためには、TCS-SiN膜の形成が必須である。ただし、TCS-SiN膜のみでは生産性が悪化するため、本実施形態では、素子性能を劣化させない程度に薄くTCS-SiN膜を形成し、TCS-SiN膜上にDCS-SiN膜を形成している。本実施形態でも、TCS-SiN膜/DCS-SiN膜の膜厚比を1.0以下とすることで、生産性を向上させるとともに、ボロンの拡散を抑制することができる。

20

## 【0060】

このように、本実施形態においても、下層側のTCS-SiN膜と上層側のDCS-SiN膜の2層構造を用いることにより、第1の実施形態で述べたのと同様の効果を得ることが可能である。

## 【0061】

## [実施形態3]

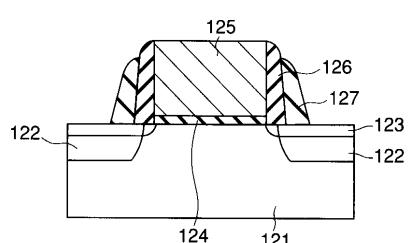

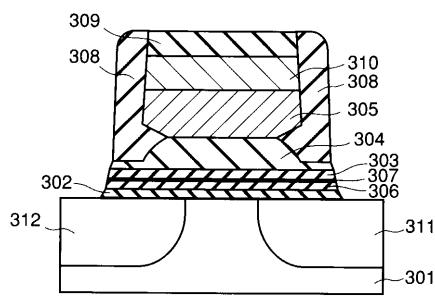

図13は、本発明の第3の実施形態に係る半導体装置(不揮発性メモリ、フラッシュメモリ)の構造を示した断面図である。

## 【0062】

図1において、シリコン基板141上には、トンネル絶縁膜142、電荷蓄積膜となる浮遊ゲート143、インターポリ絶縁膜(中間絶縁膜)144、ポリシリコン膜で形成された制御ゲート145、及びタンゲステンシリサイド膜146が形成されている。また、タンゲステンシリサイド膜146上にSiN膜147が、ゲート構造の側壁に沿ってSiN膜148が形成されている。インターポリ絶縁膜144に含まれるSiN膜、SiN膜147及びSiN膜148の少なくとも一つは、下層側のTCS-SiN膜と上層側のDCS-SiN膜との積層構造である。さらに、ゲート構造を挟んで、ソース/ドレイン拡散層149が形成されている。

30

## 【0063】

本実施形態においても、第1の実施形態で述べたのと同様の効果を得ることができる他、さらに、以下に述べるように、SiN膜形成後の高温熱工程に起因するトンネル絶縁膜の劣化を抑制することができる。

40

## 【0064】

ここでは、側壁上に形成されたSiN膜148について説明する。フラッシュメモリでは、書き込み及び消去時に20V程度の高電圧を必要とする。DCS-SiN膜中にはトラップが多い。そのため、書き込み時に注入された電子がSiN膜中にトラップされ、その結果、閾電圧が変化するという問題がある。先述したように、TCS-SiN膜では、N/Si組成比がストイキオメトリーに近く、リーケ電流が少ないとからも示唆されるように、トラップが少ない。したがって、ゲート構造に接する側にTCS-SiN膜を適用することで、書き込み時に注入された電子がSiN膜中にトラップされることが抑制される。したがって、下層側にTCS-SiN膜を適用することで、書き込み時の電子トラップ

50

に伴う閾電圧の変動を抑制することができる。

【0065】

[実施形態4]

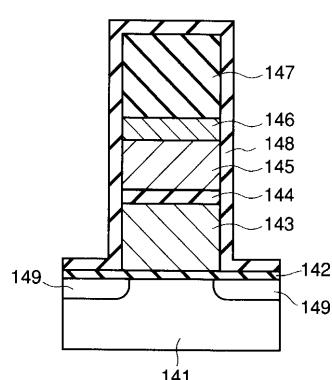

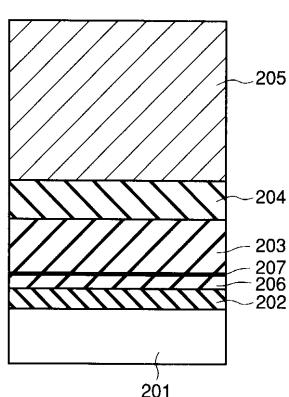

図14は、本発明の第4の実施形態に係る半導体装置(MONOS型メモリ素子)の構造を示した断面図である。

【0066】

まず、シリコン基板上201に、シリコン酸化膜202を厚さ0.5~10nm形成する。シリコン酸化膜202は、MONOS素子におけるトンネル酸化膜(ボトム酸化膜)である。このシリコン酸化膜202を通して、電子或いはホールの注入が行われる。

【0067】

次に、湿式の前処理等を行わずに、シリコン酸化膜202上に、LPCVD法により、TCS-SiN膜206を1~4nm形成する。成膜条件は、温度700~900、圧力0.01~10Torr、TCS/NH<sub>3</sub>流量比0.01~1である。続いて、LPCVD法により、DCS-SiN膜203を2~20nm形成する。成膜条件は、温度600~900、圧力0.01~10Torr、DCS/NH<sub>3</sub>流量比0.01~1である。これにより、電荷蓄積膜として、合計膜厚が12nmのシリコン窒化膜が形成される。なお、DCS-SiN膜203は、TCS-SiN膜206を形成した後、TCS-SiN膜を大気に晒さずに連続的に形成する。これにより、DCS-SiN膜203とTCS-SiN膜206との界面領域207の酸素濃度を少なくすることができる。

【0068】

次に、湿式の前処理等を行わずに、シリコン窒化膜203上にシリコン酸化膜(トップ酸化膜)204を0.5~30nm形成する。シリコン酸化膜204は、電極からの電荷注入や電荷蓄積層から電極への電荷のリークを防ぐものである。その後、トップ酸化膜204の膜質を上げるために、例えば800で酸素及び水素を用いた燃焼酸化を行う。続いて、湿式の前処理等を行わずに、シリコン酸化膜204上に制御電極205を形成する。例えば、LPCVD法により、シランを用いて、温度600で、シリコン膜を厚さ200nm形成する。引き続き、シリコン膜に不純物を導入する。さらに、活性化処理を行い、制御電極205が形成される。

【0069】

次に、上述した方法によって形成されたMONOS素子の電気特性の測定結果について述べる。

【0070】

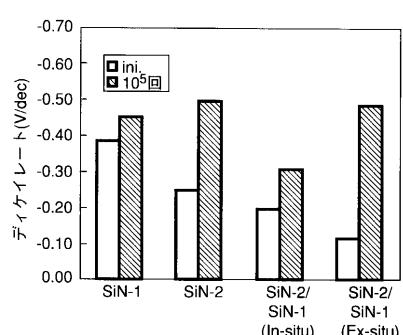

図15及び図16は、キャパシタ(面積0.01mm<sup>2</sup>)の評価結果である。フラットバンド電圧の変化が3Vになるように書き込みを行った状態で、電荷保持特性を測定した。電荷保持特性とは、蓄積電荷の経過時間に対する依存性を表したものである。電荷保持特性は、書き込み直後から所定時間経過する毎に、フラットバンド電圧を容量-電圧(C-V)測定法で決定することにより得られる。

【0071】

シリコン窒化膜中に保持された電荷は、時間の経過とともに基板側にリークする。そのため、フラットバンド電圧は、初期の書き込み電圧から、時間の経過とともに徐々に減少する。図に示してある減少率(ディケイレート)は、1桁時間あたりのフラットバンド電圧の変化量(V/dec)である。当然のことながら、ディケイレートが小さいほど優れた電荷蓄積層である。フラッシュメモリにおいては、書き込まれた情報を10年間保持すること、つまり10年後に“0”と“1”が判別できること、を保証しなければならない。ここで、10年が $3 \times 10^8$ sec、“0”と“1”とが0.5Vの差で判別可能だと仮定する。上記スペックをディケイレートに換算すると、3V書き込み時のスペックはおよそ0.3V/dec程度になる。

【0072】

図15は、4種類のシリコン窒化膜について、電荷保持特性の評価結果示したものである。SiN-1は、シリコン窒化膜をDCS-SiN膜のみで形成した場合であり、シリコンリッチなシリコン窒化膜の評価結果である。SiN-2は、シリコン窒化膜をTCS-

10

20

30

40

50

SiN膜のみで形成した場合であり、トイキオメトリーに近いシリコン窒化膜若しくは窒素リッチなシリコン窒化膜の評価結果である。また、SiN-2/SiN-1(in-situ)は、SiN-2上にSiN-1を連続して形成した場合の評価結果である。SiN-2/SiN-1(ex-situ)は、SiN-2を大気に晒した後、SiN-1を形成した場合の評価結果である。なお、4種類のシリコン窒化膜はいずれも、合計膜厚が等しい。図15の結果から明らかなように、電荷保持特性が最も良いのは、SiN-2/SiN-1(in-situ)である。

#### 【0073】

まず、ex-situよりもin-situの方がより良い原因について述べる。ex-situでは、シリコン窒化膜/シリコン窒化膜界面に多くの酸素が存在している。そのため、書き込み/消去電圧が増加してしまう。Ex-situでは、強い電界ストレスにより、10万回の書き込み/消去後の劣化が激しい。

10

#### 【0074】

SiN-2のみで形成したシリコン窒化膜が、10万回書き込み/消去後の劣化が激しい理由について述べる。SiN-2では、N/Si組成比がトイキオメトリーに近く、膜中のトラップ密度が少なく、誘電率が低い。そのため、書き込み/消去電圧が増加してしまう。したがって、SiN-2でも、強い電界ストレスによって劣化が激しくなる。

#### 【0075】

In-situ積層膜では、基板側界面に形成したSiN-2の存在によって、トラップ電子を電極側に遠ざけることが可能である。そのため、電荷保持特性が著しく改善される。また、In-situ積層膜では、膜の大部分がトラップの多いSiN-1で形成されているため、書き込み/消去電圧はほとんど増加しない。したがって、書き込み/消去時の電界ストレスも低く抑えることができる。そのため、10万回書き込み/消去後の膜の劣化を抑制することができる。

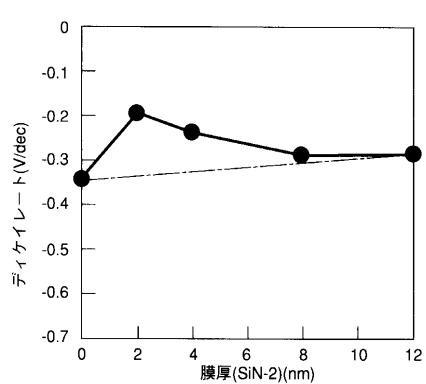

20

#### 【0076】

次に、In-situ積層膜において、SiN-2の膜厚とディケイレートとの関係について示す。図16は、SiN-2/SiN-1(in-situ)について、合計膜厚を一定にして、ディケイレートとSiN-2の膜厚との関係について調べた結果である。縦軸はディケイレート、横軸は基板側のシリコン窒化膜(SiN-2)の膜厚である。

#### 【0077】

30

SiN-2の膜厚が8nmの場合のディケイレートは、SiN-2単層膜の場合と同程度である。一方、SiN-2の膜厚を4nm及び2nmの場合には、ディケイレートの絶対値は小さい。したがって、SiN-2の膜厚が4nm以下になると、積層構造の効果が顕著になる。これは、SiN-2によって蓄積電子が基板から遠ざかる効果と、SiN-1に効率的に電子をトラップできる効果によるものと考えられる。

#### 【0078】

以上のように、本実施形態では、下層側のTCS-SiN膜と上層側のDCS-SiN膜の積層構造を用いることにより、電荷保持特性に優れた半導体装置を得ることが可能となる。

#### 【0079】

40

#### [実施形態5]

図17は、本発明の第5の実施形態に係る半導体装置(MONOS型メモリ素子)の構造を示した断面図である。

#### 【0080】

シリコン基板301は、不純物(ボロン又はインジウム)の濃度が $10^{14} \text{ cm}^{-3} \sim 10^{19} \text{ cm}^{-3}$ 程度のp型である。

#### 【0081】

シリコン基板301上には、厚さ0.5~10nmのボトム絶縁膜(トンネル絶縁膜)302が形成されている。このボトム絶縁膜302には、シリコン酸化膜又はシリコン酸窒化膜が用いられる。ボトム絶縁膜302上には、1nm以上4nm以下の厚さのTCS-SiN膜30

50

6が形成されている。TCS-SiN膜306上には、2nm以上20nm以下の厚さのDCS-SiN膜303が形成されている。これらのTCS-SiN膜306及びDCS-SiN膜303の積層構造により、電荷蓄積膜が構成される。307は、TCS-SiN膜306とDCS-SiN膜303の界面領域を示している。電荷蓄積膜上には、5nm以上30nm以下の厚さのブロック絶縁膜(トップ絶縁膜)304が形成されている。このブロック絶縁膜304には、シリコン酸化膜又はシリコン酸窒化膜が用いられる。上記ボトム絶縁膜302、電荷蓄積膜及びブロック絶縁膜304により、ONO積層膜が構成される。

#### 【0082】

ブロック絶縁膜304上には、厚さ10~500nmのゲート電極(制御電極)305が形成されている。このゲート電極305には、不純物(砒素、リン又はボロン)の濃度が $1 \times 10^1$ ~ $1 \times 10^{21} \text{ cm}^{-3}$ 程度のポリシリコン膜が用いられる。なお、ポリシリコン膜中の不純物濃度を $1 \times 10^{19} \text{ cm}^{-3}$ 以上とすると、ゲート電極305の空乏化によってONO積層膜に加わる電界が小さくなるため、消去時間の増大を防止することができる。

#### 【0083】

ゲート電極305上には、WSi(タンゲステンシリサイド)、NiSi(ニッケルシリサイド)、MoSi(モリブデンシリサイド)、TiSi(チタンシリサイド)、CoSi(コバルトシリサイド)、W又はAlからなる金属導電膜310が、10~500nmの厚さで形成されている。金属導電膜310は、複数のゲート電極を接続するゲート配線となる。

#### 【0084】

金属導電膜310上には、シリコン窒化膜或いはシリコン酸化膜からなる上層絶縁膜309が、5~500nmの厚さで形成されている。ゲート電極305の側壁上には、シリコン窒化膜又はシリコン酸化膜からなる側壁絶縁膜308が、2~200nmの厚さで形成されている。この側壁絶縁膜308と絶縁膜309とによって、ゲート電極305とソース/ドレイン領域、コンタクト(図示せず)及び上部配線層(図示せず)との間の電気的絶縁性が保たれている。

#### 【0085】

側壁絶縁膜308を形成した後、シリコン基板301にn型不純物をイオン注入することにより、ソース領域311及びドレイン領域312が形成される。この時、側壁絶縁膜308により、ゲート電極305の端部におけるイオン注入ダメージを小さくすることができる。

#### 【0086】

なお、書き込み/消去時に印加される電界のばらつきに起因するしきい電圧の広がりを防止するために、シリコン基板301とソース領域311との境界からシリコン基板301とドレイン領域312との境界までの領域において、ONO膜を構成する各膜302、306、303及び304の厚さがそれぞれ均一であることが望ましい。

#### 【0087】

上述した構成により、電荷蓄積膜に蓄積された電荷によって情報を記憶するMONOS型EEPROMメモリセルが構成される。なお、ゲート長は、 $0.5 \mu \text{m}$ 以下 $0.01 \mu \text{m}$ 以上である。また、ソース領域311及びドレイン領域312は、不純物(リン、砒素或いはアンチモン)の表面濃度が $10^{17} \text{ cm}^{-3}$ ~ $10^{21} \text{ cm}^{-3}$ となるように、拡散或いはイオン注入により形成される。また、ソース領域311及びドレイン領域312の深さは、10~500nm程度である。

#### 【0088】

以下、ONO膜の構造及び製造方法について詳述する。

#### 【0089】

まず、シリコン基板上301上に、シリコン酸化膜302を2~5nmの厚さで形成する。シリコン酸化膜302は、MONOS素子におけるトンネル酸化膜であり、シリコン酸化膜302を通して電子或いはホールが注入される。

#### 【0090】

10

20

30

40

50

次に、湿式の前処理等を行わずに、シリコン酸化膜302上に、LPCVD法により、シリコンソースとしてTCSを用いて、シリコン窒化膜(TCS-SiN膜)306を1~4nmの厚さで形成する。続いて、LPCVD法により、シリコンソースとしてDCSを用いて、シリコン窒化膜(DCS-SiN)303を2~20nmの厚さで形成する。DCS-SiN膜303は、TCS-SiN膜306を形成した後、基板を大気に晒さずに連続的に形成する。窒化種には、還元雰囲気でシリコン窒化膜306及び303を形成できるため、アンモニアを用いることが望ましい。TCS-SiN膜306の典型的な成膜条件は、温度700~900、圧力0.01torr~10Torr、TCS流量/窒化種流量の比0.01~1である。DCS-SiN膜303の典型的な成膜条件は、温度600~900、圧力0.01torr~10Torr、DCS流量/窒化種流量の比0.01~1である。

10

#### 【0091】

成膜温度が700度から900度の範囲の場合、TCSを用いて形成されたシリコン窒化膜では、Si-Hボンドの密度は $1 \times 10^{20} \text{ cm}^{-3}$ よりも小さく、N-Hボンドの密度は $7 \times 10^{21} \text{ cm}^{-3}$ 程度となる。一方、シラン或いはDCSを用いて形成されたシリコン窒化膜では、Si-Hボンドの密度は $3 \times 10^{20} \text{ cm}^{-3}$ よりも大きく、N-Hボンドの密度は $7 \times 10^{21} \text{ cm}^{-3}$ よりも小さい。このことは、蓄積状態の保持特性を向上させるためには、N-Hボンドではなく、Si-Hボンドを従来よりも減少させることが重要であることを示している。また、SiN膜中のSi-Hボンドは、シリコンソースガス中のHの割合を減らすことによって、減少できることを示している。

#### 【0092】

20

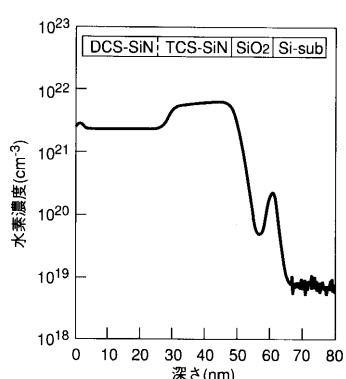

また、TCS-SiNに含有された水素の濃度は、シラン或いはDCSを用いて形成されたシリコン窒化膜に含有された水素の濃度よりも高い。図21は、シリコン基板上に、SiO<sub>2</sub>膜、TCS-SiN膜及びDCS-SiN膜を順次形成した試料の測定結果を示したものである。横軸は深さであり、縦軸は水素濃度である。図21からわかるように、TCS-SiN膜に含有される水素の濃度は $5 \times 10^{21} / \text{cm}^3$ よりも高く、DCS-SiN膜に含有される水素の濃度は $5 \times 10^{21} / \text{cm}^3$ よりも低くなっている。

#### 【0093】

30

以上のように、本実施形態では、下層側のTCS-SiN膜の方が上層側のDCS-SiN膜よりも、Si-H結合の密度は低く且つ水素濃度は高い。したがって、従来技術の項で述べた特開昭60-60770の構造とは全く異なる。また、ジクロロシランとアンモニアによって形成したSiN膜では、Si-H結合が増加すると水素濃度も増加することが、本発明者らによって確認されているが(特願2001-2975)、本実施形態はこのような構造とも基本的に異なる。また、本実施形態では、TCS-SiN膜のN/Si組成比は1.32より大きい。一方、シラン或いはジクロロシランを用いて形成されたSiN膜では、N/Si組成比は1.32より小さい。したがって、シラン或いはジクロロシランを用いて形成されたシリコン窒化膜では、本実施形態の積層構造が実現できないことは明白である。

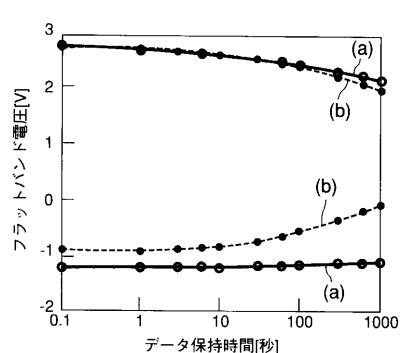

#### 【0094】

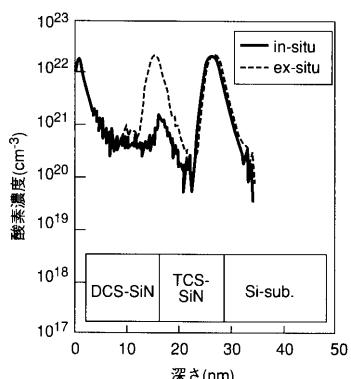

図23は、本実施形態の構造を用い、トンネル電流による書き込み/消去(W/E)を10万回行った後の電荷保持特性を示したものである。(b)は、TCS-SiN膜の形成後、DCS-SiN膜の形成前に、基板を酸素を含む雰囲気に $10^6 \text{ Langmuir}$ 以上曝した場合である。(a)は、TCS-SiN膜の形成後、DCS-SiN膜の形成前に、基板を酸素を含む雰囲気に $10^5 \text{ Langmuir}$ 以上曝さずに、TCS-SiN膜及びDCS-SiN膜を連続的に形成した場合である。ここで、中性フラットバンド電圧は、 $-0.5V \pm 0.2V$ と見積もられる。書き込み/消去後のホール及び電子の保持特性は、明らかに連続的に成膜した方が良好である。従来は、酸素結合を増やすことにより電荷保持特性が良くなると言っていたが、上述した結果から、酸素結合を減らした方が電荷保持特性が良くなることがわかる。したがって、TCS-SiN膜及びDCS-SiN膜を連続的に形成することが望ましい。

40

#### 【0095】

また、TCS-SiN膜とDCS-SiN膜との界面付近の酸素濃度が大きくなると、界

50

面を含んだ SiN 膜全体の誘電率が低下する。そのため、書き込み/消去電圧が増大してしまう。書き込み/消去電圧が増大すると、10万回の書き込み/消去後の電荷保持特性の劣化が著しくなる。図22は、シリコン基板上に、TCS-SiN 膜及びDCS-SiN 膜を順次形成した試料の測定結果を示したものである。横軸は深さであり、縦軸は酸素濃度である。図22からわかるように、基板を大気に晒さずに、TCS-SiN 膜とDCS-SiN 膜を連続的に形成した試料では、TCS-SiN 膜とDCS-SiN 膜の界面での酸素濃度は  $1 \times 10^{22} / \text{cm}^3$  よりも低くなっている。したがって、TCS-SiN 膜とDCS-SiN 膜との界面での酸素濃度を、 $1 \times 10^{22} / \text{cm}^3$  よりも低くすることが望ましい。

## 【0096】

10

また、下層側のTCS-SiN 膜は、ストイキオメトリーに近い、電荷トラップの少ない膜であることが望ましい。一方、上層側のDCS-SiN 膜は、シリコンリッチなトラップの多い膜であることが望ましい。例えば、DCS以外にも、ヘキサクロロジシラン( $\text{Si}_2\text{Cl}_6$ )などを用いても、電荷トラップの多いSiN 膜を得ることが可能である。窒化種としては、酸化還元反応を制御できるものであればよく、NOやN<sub>2</sub>O等を用いることも可能である。

## 【0097】

図17の説明にもどる。DCS-SiN 膜303を形成した後、湿式の前処理等を行わずに、DCS-SiN 膜303上にシリコン酸化膜(トップ酸化膜)304を厚さ2~10nm形成する。このシリコン酸化膜304は、電極からの電荷注入や電荷蓄積膜から電極側への電荷のリークを防ぐものである。続いて、トップ酸化膜304の膜質を向上させるため、デンシファイアニールを行う。温度850で、酸素及び水素による燃焼酸化を行ってもよい。

20

## 【0098】

次に、湿式の前処理等を行わずに、シリコン酸化膜304上にゲート電極305の形成等を行う。ゲート電極は、例えばLPCVD法により、シランを用いて、成膜温度600で、200nm程度の厚さ形成する。さらに、不純物のイオン注入工程、活性化工程等を経て、図17のMONOS構造が得られる。

## 【0099】

30

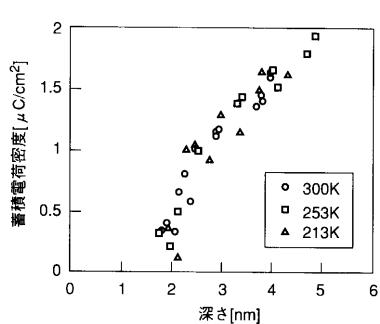

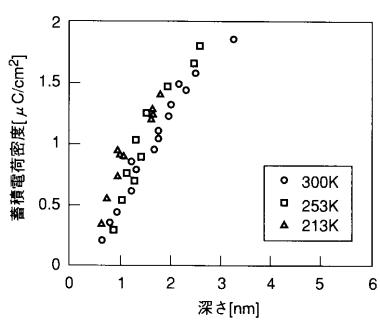

以上のようにして得られたMONOS素子において、トンネル電流による基板からの電子注入を行い、蓄積電荷の重心を調べた。図25は本実施形態の場合であり、図26はDCS-SiN 膜による単層膜の場合の比較例である。横軸は、電荷蓄積膜とボトム絶縁膜との界面からの電荷重心の深さであり、縦軸は、蓄積電荷密度である。測定温度は、213K(-60)、253K(-20)および300K(27)である。TCS-SiN 膜の厚さは $2 \pm 0.3\text{nm}$ である。

## 【0100】

図26より、DCS-SiN 単層膜では、温度を下げるにしたがって蓄積電荷の重心は基板側に近くなっていくことがわかる。温度の低下とともに電荷の重心が基板側に近くなると、低温で書き込みを行った後に、書き込み温度よりも高い温度で保持を行うと、蓄積電荷の基板側へのトンネル電流によってリークが増大する。結果として、素子特性の電荷保持特性の劣化が著しくなってしまう。そのため、単層膜を用いた素子では、低温での動作保証が困難になる。一方、図25に示すように、本実施形態の積層構造においては、電荷の深さに温度依存性はなく、-60までほぼ同じ深さを保っている。したがって、本実施形態による積層構造を用いることで、低温下での特性劣化を防止することができる。よって、氷点下、例えば-20での使用に耐える素子を実現できる。

40

## 【0101】

また、図25と図26を比較すると、本実施形態の方が、蓄積電荷の重心が深くなっている。蓄積電荷密度が $1\text{uC/cm}^2$ 以下の場合には、TCS-SiN 膜とDCS-SiN 膜の界面の位置が、ほぼ重心位置に対応している。したがって、界面に酸素が添加されていなくても、従来よりも深い位置に電荷をトラップさせることができる。これにより、蓄積電荷

50

の基板側へのトンネル電流に起因したリークを減少させることができる。

【0102】

なお、詳細な検討より、TCS-SiN膜とDCS-SiN膜の界面の深さは、図26の重心位置よりも深い、1nm以上で4nm以下が最適であることがわかった。また、界面が4nmより深いと、トンネル注入によって注入された電子がほとんどTCS-SiN膜にトラップされてしまうため、トラップ位置を深くする効果が得られないことも判明した。

【0103】

なお、ここでは、本実施形態の積層膜構造を用いることにより、トンネル注入による電荷重心を深くできることを示したが、ホットエレクトロン注入によってSiN膜にキャリアを注入する場合も、注入キャリアのエネルギーが大きいため、キャリアが界面に達する確率が増大し、同様の効果が得られる。

10

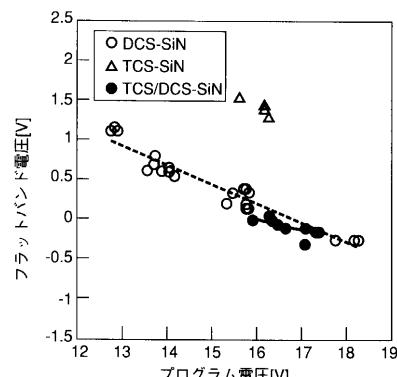

【0104】

図24は、1から5MV/cmの弱い誤書き込みストレスを印加した場合のフラットバンド電圧を示したものである。横軸は書き込みフラットバンド電圧が2Vとなるプログラム電圧値であり、縦軸は誤書き込みストレス後のフラットバンド電圧である。誤書き込みフラットバンド電圧が低い方が、誤書き込みストレスに対する耐性があることになる。なお、本特性は、 $10^5$ 回の書き込み/消去ストレスを印加した後の特性である。

【0105】

本実施形態の積層構造では、DCS-SiN膜よりも電子トラップの少ないTCS-SiN膜を、トンネル界面近傍に形成している。そのため、図24から明らかなように、本実施形態では、弱い電界ストレスを印加した場合のキャリア注入量を、TCS-SiN単層膜及びDCS-SiN単層膜の場合よりも、減少させることができる。このような積層構造の誤書き込みストレスに対する耐性は、本発明者らが発見したものであり、従来は報告されていない。

20

【0106】

上述した結果から、誤書き込みストレスが、読み出し時に必然的に加わる構造、すなわち、書き込みしきい電圧の上限よりも高い電圧が読み出し時に制御電極に印加される素子に対して、本実施形態の積層構造を有効であることがわかる。本実施形態の積層構造を用いることにより、誤書き込ストレスによるしきい電圧の変化を抑制することができ、読み出し時におけるデータ破壊を防止することができる。

30

【0107】

このような構造の例としては、特開平11-224908号公報に示されているような、複数のメモリセルの電流端子を直列接続したNAND型の素子があげられる（図27参照）。また、米国特許6215148に記載されているような、電荷蓄積膜のソース近傍の領域と電荷蓄積膜のドレイン近傍の領域とで、互いに独立して電荷が蓄積される構造を有する素子があげられる。

【0108】

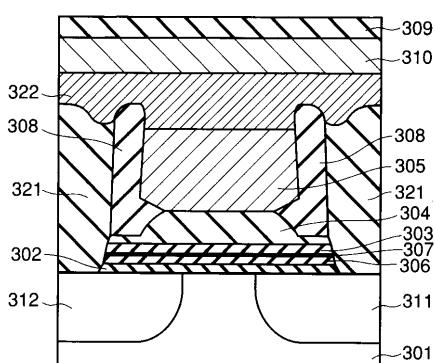

図18は、本実施形態に係るMONOS素子の第1の変形例を示した断面図である。なお、図17に示した構成要素と対応する構成要素には同一の参照番号を付している。

【0109】

40

本変形例は、ゲート電極305と金属性導電膜310との間に導電体膜322を設け、側壁絶縁膜308の側面上に絶縁膜321を設けたものである。このような構造によれば、ソース領域311からドレイン領域312に向かう方向と同一方向に、ゲート電極305に接続された制御線を形成することができる。このような構造により、AND構造やVirtual Ground Array構造を形成することもできる。なお、導電体膜322は、10~500nmの厚さのポリシリコン膜であり、不純物（砒素、リンまたはボロン）が $1 \times 10^{19} \sim 1 \times 10^{21} \text{ cm}^{-3}$ 添加されている。絶縁膜321には、シリコン酸化膜またはシリコン窒化膜が用いられる。この絶縁膜321は、ソース領域311及びドレイン領域312形成後に、隣接するゲート電極間に埋め込み形成される。

【0110】

50

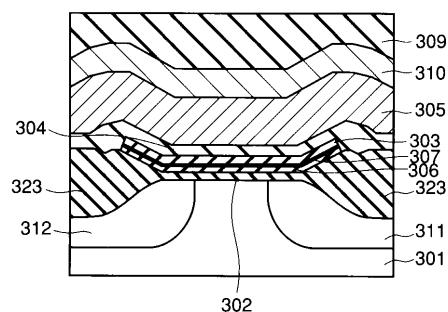

図19は、本実施形態に係るMONOS素子の第2の変形例を示した断面図である。なお、図17に示した構成要素と対応する構成要素には同一の参照番号を付している。

#### 【0111】

本変形例では、ソース領域311からドレイン領域312に向かう方向と同一方向に、金属性導電膜310からなる制御線が形成されている。また、本変形例では、シリコン酸化膜からなる素子分離絶縁膜323が、ソース領域311及びドレイン領域312上に自己整合的に形成されている。以下、本変形例を詳細に説明する。

#### 【0112】

シリコン基板301上には、厚さ0.5~10nmのボトム絶縁膜(トンネル絶縁膜)302が形成されている。このボトム絶縁膜302は、例えばストライプ状であり、その両側にはシリコン酸化膜からなる素子分離絶縁膜323(厚さ0.05~0.5μm)が形成されている。ボトム絶縁膜302及び素子分離絶縁膜323上には、1nm以上4nm以下の厚さのTCS-SiN膜306が形成されている。TCS-SiN膜306上には、2nm以上20nm以下の厚さのDCS-SiN膜303が形成されている。

#### 【0113】

このような構造は、以下のようにして得られる。まず、ボトム絶縁膜302をシリコン基板301上に形成する。続いて、TCS-SiN膜306及びDCS-SiN膜303を全面に堆積し、それらをパターニングする。その後、酸化雰囲気でシリコン基板301を酸化することにより、素子分離絶縁膜323が形成される。

#### 【0114】

素子分離絶縁膜323の下方には、深さ10~500nmのソース領域311及びドレイン領域312が設けられている。ソース領域311及びドレイン領域312は、拡散またはイオノン注入によって形成され、不純物(リン、砒素又はアンチモン)の表面濃度は $10^{17}\text{cm}^{-3}$ ~ $10^{21}\text{cm}^{-3}$ 程度である。ソース領域311及びドレイン領域312は、パターニングされた電荷蓄積層303及び306をマスクとして用いることにより、素子分離絶縁膜313に對して自己整合的に形成することができる。

#### 【0115】

上述した構造上には、厚さ5nm以上30nm以下のブロック絶縁膜304が形成されている。ブロック絶縁膜304には、シリコン酸化膜またはシリコン酸窒化膜が用いられる。ブロック絶縁膜304上には、ポリシリコン膜からなるゲート電極305が10~500nmの厚さで形成されている。ポリシリコン膜中には、不純物(リン、砒素またはボロン)が、 $1\times 10^{19}\text{cm}^{-3}$ ~ $1\times 10^{21}\text{cm}^{-3}$ 含有されている。ボロン濃度は、シリコン酸化膜中のボロンの異常拡散を防止し、p型MOSトランジスタのしきい電圧を安定化する観点から、 $1\times 10^{20}\text{cm}^{-3}$ 以下とすることが望ましい。また、ポリシリコン膜中の不純物濃度を $1\times 10^{19}\text{cm}^{-3}$ 以上とすると、ゲート電極305の空乏化によってONO積層膜に加わる電界が小さくなるため、消去時間の増大を防止することができる。

#### 【0116】

ブロック絶縁層304には、TEOSやHTOなど、堆積シリコン酸化膜を用いてもよい。あるいは、SiN膜303を酸化することによって得られるシリコン酸化膜またはシリコン酸窒化膜を用いてもよい。

#### 【0117】

ゲート電極305上には、金属性導電膜310が10~500nmの厚さで形成されている。金属性導電膜310は、複数のゲート電極を接続するゲート配線となる。金属性導電膜310上には、シリコン窒化膜やシリコン酸化膜からなる絶縁膜309が、5~500nmの厚さで形成されている。

#### 【0118】

なお、本変形例においても、書き込み/消去時に印加される電界のばらつきに起因するしきい電圧の広がりを防止するために、シリコン基板301とソース領域311との境界からシリコン基板301とドレイン領域312との境界までの領域において、ONO膜を構成する各膜302、306、303及び304の厚さがそれぞれ均一であることが望まし

10

20

30

40

50

い。

【0119】

本変形例では、図17に示したMONOS型素子で得られる効果の他、さらに以下のような効果が得られる。

【0120】

ソース領域311からドレイン領域312に向かう方向と同一方向に、ゲート電極305に接続された制御線が形成されている。そのため、隣接するメモリセルのソース領域およびドレイン領域を並列接続する構造、例えばAND型構造やVirtual Ground Array構造を実現するのに適している。また、素子分離絶縁膜323に対して、ソース領域311、ドレイン領域312、電荷蓄積層膜303及び306を自己整合的に形成することができる。10 したがって、それらの層間でのアライメントマージンを確保する必要がなく、高密度のメモリセルを実現することができる。

【0121】

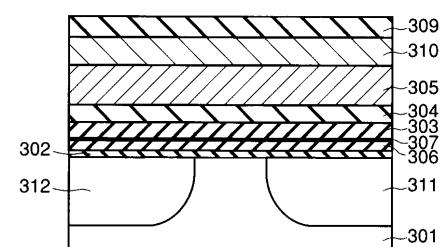

図20は、本実施形態に係るMONOS素子の第3の変形例を示した断面図である。なお、図17に示した構成要素と対応する構成要素には同一の参照番号を付している。

【0122】

本変形例は、基本的には第2の変形例と同様であるが、素子分離絶縁膜が形成されていない点が第2の変形例と異なっている。

【0123】

本変形例のメモリセルは、以下のようにして形成することができる。まず、シリコン基板301の表面領域に、ソース領域311及びドレイン領域312をイオン注入によって形成する。続いて、ボトム絶縁膜302、電荷蓄積膜306及び303、ブロック絶縁層304を、シリコン基板301上に形成する。さらに、ゲート電極305を形成するためのポリシリコン膜及び金属性導電膜310を全面に堆積する。その後、上述した各膜をパターニングする。各膜の膜厚等については、第2の変形例と同様でよい。20

【0124】

本変形例では、図17に示したMONOS型素子で得られる効果の他、さらに以下のような効果が得られる。

【0125】

ソース領域311からドレイン領域312に向かう方向と同一方向に、ゲート電極305に接続された制御線が形成されている。そのため、隣接するメモリセルのソース領域およびドレイン領域を並列接続する構造、例えばAND型構造やVirtual Ground Array構造を実現するのに適している。また、ボトム絶縁膜302、電荷蓄積膜306及び303、ブロック絶縁層304の厚さが、素子分離絶縁膜の端部で変化するこがないため、均一な厚さでメモリセルを実現することができる。したがって、書き込み/消去時のしきい電圧の分布を小さくすることができる。30

【0126】

以上のように、本実施形態によれば、下層側のTCS-SiN膜と上層側のDCS-SiN膜の積層構造を用いることにより、電荷保持特性に優れた半導体装置を得ることが可能となる。40

【0127】

[実施形態6]

本実施形態は、第5の実施形態で説明した各構造に対して、重水素(D)を導入したものである。重水素を導入することで、劣化の非常に少ない素子を実現することができる。

【0128】

第5の実施形態で説明した例えは図17のMONOS素子に対し、1%~100%重水素ガスを用いてアニールを行った。アニール条件は、常圧、850以上1000以下、1分~2時間とした。界面及び電荷蓄積膜となるSiN膜中に存在する重水素の割合は、SIMSによる分析により、全水素に対して1%以上であることが確認されている。

【0129】

10

20

30

40

50

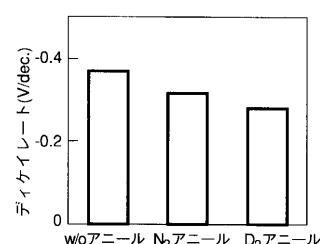

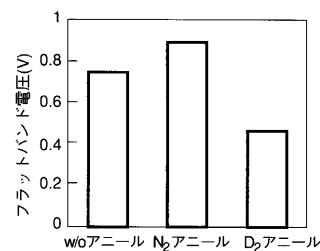

重水素アニールを行ったMONOS素子の電気特性の評価結果について、図28及び図29を用いて説明する。図28及び図29は、キャパシタ（面積0.01mm<sup>2</sup>）の評価結果であり、10万回の書き込み/消去後に測定したものである。図28は電荷保持特性であり、図29は誤書き込み特性である。また、図28及び図29には、3種類のサンプル（アニール無し、窒素アニール、重水素アニール）の評価結果を示してある。

#### 【0130】

図28は、ディケイレートの測定結果である。フラットバンド電圧の変化が3Vになるように書き込みを行った状態で、電荷保持特性を測定した。図28からわかるように、ディケイレートは、重水素アニールを行うことによって改善されている。

#### 【0131】

図29は、誤書き込み特性を示したものである。誤書き込み特性は、フラットバンド電圧が-1Vになるように消去を行い、5Vの電圧を300秒印加した後のフラットバンド電圧を測定することで評価した。NAND構造の素子においては、例えば16個のセルが直列に接続されており、あるセルを読み出す際に、残りのセルにも読み出し電圧が印加される。消去状態において5Vの電圧が300秒印加されると、わずかながら書き込みが行われ、フラットバンド電圧が上昇する（誤書き込み）。図29からわかるように、誤書き込み特性は、重水素アニールによって大きく改善されている。

#### 【0132】

上述した2つの特性値から、10年後で読み出しストレス印加後のメモリウインドウが求まる。特性が最も優れているのは、電荷保持特性および誤書き込み特性の両者が改善された重水素アニールのサンプルである。重水素アニールサンプルでは、10万回の書き込み/消去による劣化が少ない。

#### 【0133】

書き込み/消去によるストレスでは、界面および膜中に欠陥が形成されていると考えられる。これらの欠陥は、蓄積電荷の基板側へのリークを増大させることで電荷保持特性を劣化させ、基板から窒化膜中へのリークを増大させることで誤書き込み特性を劣化させる。これら特性を劣化させる欠陥の一つとして、Si-H結合（ここでは、便宜上、シリコンと軽水素との結合をSi-H結合と表す）が考えられる。Si-H結合では、書き込み/消去による電界ストレスによって軽水素原子がはずれ、シリコンのダングリングボンドが形成されてしまう。シリコンのダングリングボンドは、電子およびホールをトラップするサイトとして機能すると考えられる。重水素アニールを行った場合には、欠陥が重水素によって置換され、Si-D結合が形成されている。したがって、結合が切れにくく、書き込み/消去による欠陥生成が少ない。そのために、特性の劣化が少ないと考えられる。また、TCS-SiNでは、Si-H結合がほとんどないため、N-H結合をN-D結合で置換することにより、結合が切れにくくなっている可能性もある。いずれにせよ、SiNを積層した電荷蓄積膜やTCS-SiN膜を用いた電荷蓄積膜に重水素を含有することにより、電荷蓄積膜の特性を改善できることを、本願発明者らは初めて見いだした。

#### 【0134】

重水素の導入方法は、アニール法に限定されない。例えば、シリコン窒化膜を形成する時に、重水素を含んだシリコンソース或いは重水素を含んだ窒化種を用いるようにしてもよい。また、電極となるポリシリコン膜を形成する時に、重水素を含んだシリコンソースを用いるようにしてもよい。さらに、低温アニールでも、圧力を高くすれば重水素の導入が可能である。いずれの方法によっても、重水素導入の効果が得られる。

#### 【0135】

なお、上述した例では、TCS-SiN膜とDCS-SiN膜との積層構造としたが、重水素を含有するシリコン窒化膜の単層構造を採用することも可能である。以下、この例について説明する。

#### 【0136】

重水素を含有したシリコン窒化膜の形成方法としては、大きく分けて二つの方法があげられる。第1は、重水素を含有したシリコンソース（軽水素を重水素で置換したシリコンソ

10

20

20

30

30

40

40

50

ース)と、重水素を含有した窒素ソース(軽水素を重水素で置換した窒素ソース)を用いる方法である。第2は、水素(軽水素及び重水素)を含有しないシリコンソースと、重水素を含有した窒素ソースを用いる方法である。なお、上記重水素を含有した窒素ソースには、 $\text{ND}_3$ (軽水素を重水素で置換したアンモニア)或いは $\text{N}_2\text{D}_4$ (軽水素を重水素で置換したヒドラジン)があげられる。

【0137】

第1の方法では、重水素を含有したシリコンソースの値段が非常に高いため、量産に適用することが困難である。これに対して、第2の方法では、水素を含有しないシリコンソースとして、安価なTCS或いはヘキサクロロジシラン( $\text{HCD} : \text{Si}_2\text{Cl}_6$ )等を用いることができる。したがって、量産を考えた場合には、第2の方法を用いることが好ましい。

【0138】

水素を含有しないシリコンソースを用いれば、シリコン窒化膜に含有される重水素の量は $\text{ND}_3$ 等の純度のみに依存する。したがって、シリコン窒化膜に含有された全水素の数に対する重水素の数の割合を、容易に90%以上にすることができる。実際にHCDと $\text{ND}_3$ を用いてシリコン窒化膜を形成した結果、 $1 \times 10^{21} \text{ cm}^{-3}$ 以上の重水素を含有し、全水素に対する重水素の割合が99%以上であるシリコン窒化膜を得ることができた。なお、シリコンソースとしてTCS或いはHCDを用い、窒素ソースとして $\text{ND}_3$ を用いた場合、シリコン窒化膜中の塩素濃度は $1 \times 10^{19} \text{ /cm}^3$ よりも高くなる。

【0139】

以上のように、本実施形態によれば、シリコン窒化膜中に重水素を含有させることにより、シリコン窒化膜の欠陥を低減することができ、電荷保持特性に優れた半導体装置を得ることが可能となる。

【0140】

なお、重水素を含有したシリコン窒化膜を用いたデバイス構造は、先述した第1～第5の実施形態及び後述する第7の実施形態にも適用可能である。すなわち、各実施形態において、下層側及び上層側のシリコン窒化膜の両方に重水素を含有したシリコン窒化膜を用いることが可能である。或いは、各実施形態において、下層側シリコン窒化膜と上層側シリコン窒化膜の積層構造の代わりに、重水素を含有したシリコン窒化膜の単層構造を採用することも可能がある。

【0141】

例えば、第1～第3の実施形態において、上述したような構造を用いることにより、重水素を含有したシリコン窒化膜が軽水素のバリアとして機能する。また、シリコン窒化膜から放出される水素のほとんどが重水素となる。したがって、ゲート絶縁膜の特性や信頼性を向上させることが可能となる。

【0142】

[実施形態7]

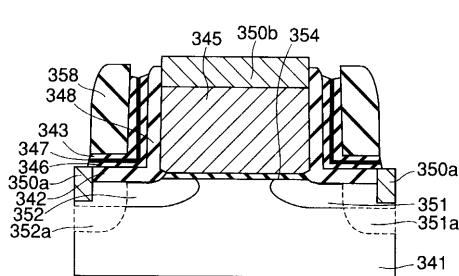

図30は、本発明の第7の実施形態に係る半導体装置の構造を示した断面図である。本実施形態は、MISFETの側壁絶縁膜としてシリコン窒化膜の積層構造を用いたものである。

【0143】

まず、ボロン濃度が $10^{15} \text{ cm}^{-3}$ のp型層を有するシリコン基板341を用意する。p型層にボロン或いはインジウムをイオン注入し、p型層の濃度を最適化してもよい。イオン注入のエネルギーは、例えば100～1000eVとする。このイオン注入により、p型層(p型ウエル)の濃度を $10^{15} \sim 10^{19} \text{ cm}^{-3}$ としてもよい。その後、トレンチ型の素子分離領域(図示せず)を形成する。

【0144】

次に、シリコン基板341の表面を1～100nm程度酸化又は窒化して、ゲート絶縁膜354を形成する。次に、ゲート電極となるポリシリコン膜345を10～200nm堆積する。さらに、ポリシリコン膜345中にリン、砒素又はボロンをイオン注入し、ポリシリコン膜3

10

20

30

40

50

45を低抵抗化する。ゲート電極の低抵抗化をはかるために、WSi膜、CoSi膜或いはW膜をポリシリコン膜345上に10~200nm程度堆積してもよい。さらに、リソグラフィと反応性イオンエッティングによりポリシリコン膜345を加工して、ゲート電極を形成する。

【0145】

次に、ゲート電極345の側壁を酸化又は酸窒化することにより、1~30nmの側壁シリコン絶縁膜348を形成する。このとき、シリコン基板341の一部も酸化され、シリコン酸化膜342が形成される。

【0146】

次に、浅いソース拡散層351及びドレイン拡散層352を形成するために、表面濃度が<sup>10</sup>  $10^{17} \text{ cm}^{-3} \sim 10^{21} \text{ cm}^{-3}$ となるように、不純物（リン、砒素又はアンチモン）をイオン注入する。イオン注入の深さは、10~500(nm)程度とする。

【0147】

次に、シリコン酸化膜342上に、LPCVD法により、TCS-SiN膜346を1nm以上4nm以下の厚さで形成する。続いて、DCS-SiN膜343を2nm~20nmの厚さで形成する。これらのSiN窒化膜343及び346は、深いソース拡散層351a及びドレイン拡散層352aを形成する際に生じる点欠陥の影響や不純物拡散の影響が、ゲート電極345下に及ばないようにするためのものである。<sup>20</sup> 347はTCS-SiN膜346とDCS-SiN膜343の界面領域である。なお、DCS-SiN膜343は、TCS-SiN膜346を形成した後、基板を大気に晒さずに連続的に形成する。

【0148】

なお、下層側のTCS-SiN膜346は、ストイキオメトリに近い、電荷トラップの少ない膜が望ましい。上層側のDCS-SiN膜343は、電荷トラップが多い、シリコンリッチな膜が好ましい。また、TCS-SiN膜346及び上層側のDCS-SiN膜343の形成条件等は、すでに述べた形成条件等と同様である。

【0149】

続いて、TEOS或いはHTOを用いて、シリコン酸化膜358を厚さ10~200nm堆積する。さらに、シリコン酸化膜358を異方性エッティングし、ゲート電極345の側壁に対応した部分にシリコン酸化膜358を残す。さらに、シリコン酸化膜358をマスクとして、シリコン窒化膜346及び343をエッティングする。<sup>30</sup>

【0150】

次に、例えばn型不純物として砒素またはリンをイオン注入して、深いソース拡散層351a及びドレイン拡散層352aを形成する。イオン注入の条件は、加速電圧1~100keV、ドーズ量 $10^{13} \sim 10^{16} \text{ cm}^{-2}$ とする。

【0151】

次に、Ni、Co又はTiからなる金属膜を、厚さ0.01~0.3μm全面に堆積する。続いて、600度以上の熱処理を行い、金属膜とシリコンとを反応させる。この熱処理により、ソース拡散層351a及びドレイン拡散層352a上には金属シリサイド膜350aが形成され、ポリシリコン膜345上には金属シリサイド膜350bが形成される。さらに、シリコンと反応せずに残った金属膜を除去する。<sup>40</sup>

【0152】

その後の工程は、図示しないが、シリコン酸化膜、PSG又はBPSGからなる層間絶縁膜を20~1000nm堆積する。続いて、リソグラフィと反応性イオンエッティングにより、配線溝及びコンタクト孔を形成する。さらに、シリサイド膜（TiSi膜、WSi膜など）或いは金属膜（Al膜、W膜など）を堆積し、配線を形成する。

【0153】

以上のように、本実施形態では、MISFETの側壁絶縁膜として、TCS-SiN膜346及びDCS-SiN膜343の積層構造を用いている。以下、図30に示したMISFETを、論理回路素子として用いた場合の効果について説明する。

【0154】

10

20

30

40

50

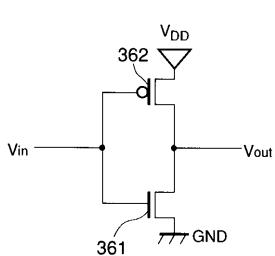

図31は、図30に示したn型MISFET361にp型MISFET362を接続して、CMOSインバータを形成した回路図である。

【0155】

インバータの入力VinがVDDからグランドGNDまで変化する場合、n型MISFET361のドレインとゲート間には $\pm V_{DD}$ の電圧ストレスが印加される。例えば、ドレイン352がGND、ゲート345がVDDの場合には、絶縁膜342をトンネル絶縁膜、SiN膜343及び346を電荷蓄積膜、側壁絶縁膜348をロック絶縁膜としたMONOS構造が形成され、ドレイン352から電荷蓄積膜に電子が注入される電界が印加される。逆に、ドレイン352がVDD、ゲート345がGNDの場合、側壁絶縁膜348をトンネル絶縁膜、SiN膜343及び346を電荷蓄積膜、絶縁膜342をロック絶縁膜としたMONOS構造が形成され、ゲート345から電荷蓄積膜に電子が注入される電界が印加される。

10

【0156】

図31のインバータを動作させると、図30のSiN膜343及び346、特にゲート絶縁膜354のごく近傍のSiN膜343及び346に、符号の異なる電界が印加される。そのため、SiN膜343及び346の劣化が生じる。しかしながら、実施形態の構造では、SiN膜343及び346の積層構造を用いることで、すでに説明したように、SiN膜への電子注入を抑制することができる。したがって、SiN膜への電子蓄積によるソース/ドレイン領域の抵抗上昇や、しきい電圧の経時変化といった問題を防ぐことができる。もちろん、先の実施形態で述べたような効果が得られることは言うまでもない。

20

【0157】

なお、上述した各実施形態は、種々の変形が可能である。例えば、素子分離膜や絶縁膜の形成方法は、シリコン基板をシリコン酸化膜やシリコン窒化膜に変換する方法以外にも、堆積したシリコン膜に酸素イオンを注入する方法や、堆積したシリコン膜を酸化する方法を用いてよい。

【0158】

また、半導体基板には、p型シリコン基板の代わりにn型シリコン基板を用いてよい。また、半導体基板として、SOI基板を用いてもよい。さらに、半導体基板として、SiGe基板、SiGeC基板など、シリコンを含む単結晶半導体基板を用いてもよい。また、n型素子の代わりにp型素子を形成してもよい。この場合、p型不純物には、インジウムやボロンを用いることができる。

30

【0159】

また、ゲート電極に用いる半導体には、Siの他、SiGeやSiGeCを用いてよい。また、ゲート電極には、W、Ta、Ti、Hf、Co、Pt、PdまたはNiなどの金属、或いはそれらの金属のシリサイドを用いてもよい。また、上記材料の積層膜を用いてもよい。Si、SiGe或いはSiGeCは、多結晶でもアモルファスでもよく、それらの積層構造でもよい。Siを含有した半導体を用いることにより、p型のゲート電極を形成することができ、ゲート電極からの電子注入を防ぐことができる。さらに、電荷蓄積層はドット状に配置されていてもよい。

【0160】

[実施形態8]

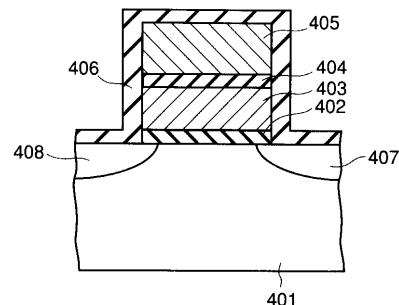

図32は、本発明の第8の実施形態に係る半導体装置（不揮発性メモリ）の構造を示した断面図である。

【0161】

シリコン基板401上には、トンネル絶縁膜402、電荷蓄積膜となる浮遊ゲート電極403、中間絶縁膜404、制御ゲート電極405が、順次形成されている。また、シリコン基板401上及びゲート構造の周囲には、側壁酸化膜406が形成されている。さらに、ゲート構造を挟んで、ソース領域407及びドレイン領域408が形成されている。図32に示した例では、トンネル絶縁膜402は、浮遊ゲート電極403の直下にのみ存在しているが、浮遊ゲート電極403の外側にまで延在していても良い。

50

## 【0162】

トンネル絶縁膜402は、シリコン窒化膜で形成され、シリコン窒化膜中には窒素に結合した水素が含まれている。この水素の主成分は重水素(D)である。また、トンネル絶縁膜12の物理的な膜厚は9nm(シリコン酸化膜の膜厚に換算した膜厚は5.5nm)である。

## 【0163】

窒素に結合した水素の90%が重水素であるメモリ素子を用いて、10万回の書き込み/消去後のデバイス信頼性を、従来技術(窒素に結合している水素の実質的に全てが軽水素であるメモリ素子)と比較した。動作時に、トンネル絶縁膜に印加される電圧は7.9Vとした。本実施形態では、従来技術と比較して、書き込み/消去時にトンネル絶縁膜に生じるSILC(Stress Induced Leakage Current)と呼ばれる低電界リーク電流が、2桁程度低下した。また、メモリ素子の誤動作発生率が1/10以下に低減され、データ保持時間が2桁程度向上した。

10

## 【0164】

上述した効果は、窒素と重水素との結合(N-D結合)が有するベンディングモードと呼ばれる固有振動波数が、シリコンと窒素との結合(Si-N結合)が有するストレッチングモードと呼ばれる固有振動波数に近いために起こると解釈できる。すなわち、書き込み/消去動作時にトンネル絶縁膜中を高エネルギーの電子が通過する際、N-D結合に与えられるエネルギーは、共振現象によって速やかに周囲のSi-N結合に分配される。そのため、N-D結合は切断されることはない。したがって、トンネル絶縁膜中に原子レベルの構造欠陥が生じることはなく、リーク電流発生が抑制されたと解釈できる。

20

## 【0165】

N-D結合のベンディングモード固有振動波数は、N-H結合(ここでは、便宜上、窒素と軽水素との結合をN-H結合と表す)のベンディングモード固有振動波数( $1190\text{cm}^{-1}$ )から見積もると、 $1190 \times 2 = 840\text{cm}^{-1}$ となる。一方、Si-N結合のストレッチングモード固有振動波数を実測したところ、LPCVD法で堆積したシリコン窒化膜では $830 \pm 100\text{cm}^{-1}$ 、シリコン基板をアンモニアガス雰囲気で熱窒化して形成したシリコン窒化膜では $850 \pm 90\text{cm}^{-1}$ 、シリコン酸化膜をアンモニアガス雰囲気で熱窒化して形成したシリコン窒化膜では $880 \pm 40\text{cm}^{-1}$ であった。これらの結果は、上記の共振現象モデルを支持する。

## 【0166】

なお、上述した効果は、トンネル窒化膜中におけるN-H結合の数を[N-H]、N-D結合の数を[N-D]として、( $[N-D] / ([N-H] + [N-D])$ )が0.5よりも大きい場合に顕著に現れる。十分な効果を得るには、上記比率が0.9よりも大きいことが望ましい。また、トンネル窒化膜中には酸素が含有されていてもよい。トンネル窒化膜中における窒素濃度を[N]、酸素濃度を[0]として、上記効果は、( $[N] / ([N] + [0])$ )が0.5よりも大きい場合に顕著に現れる。十分な効果を得るには、上記比率が0.9よりも大きいことが望ましい。

30

## 【0167】

なお、本実施形態のシリコン窒化膜は、TCS並びに軽水素を重水素(D)で置換したアンモニア( $\text{ND}_3$ )をソースガスとして用いた、LPCVD法によって形成することができる。この方法によって、 $[N-D] / ([N-H] + [N-D]) > 0.9$ 、かつ、 $[N] / ([N] + [0]) > 0.9$ のシリコン窒化膜を得ることが可能である。

40

## 【0168】

また、TCSの代わりにDCSを用いても良い。この場合には、 $[N-D] / ([N-H] + [N-D]) = 0.8 \sim 0.9$ 、 $[N] / ([N] + [0]) = 0.9$ のシリコン窒化膜を得ることができる。また、軽水素を重水素(D)で置換したシラン( $\text{SiD}_4$ )と窒素( $\text{N}_2$ )をソースガスとして、プラズマCVD法を用いても良い。この場合には、 $[N-D] / ([N-H] + [N-D]) > 0.9$ 、 $[N] / ([N] + [0]) = 0.8 \sim 0.9$ のシリコン窒化膜を得ることができる。さらに、これらのシリコン窒化膜を酸化しても良い。この場合には、膜中の酸素濃度は増加するが、膜中の水素の総量を低減することができるので、デバイスの信頼性を向上させることができる。

50

## 【0169】

なお、シリコン窒化膜中の[N-H]や[N-D]は、透過型のフーリエ変換型赤外吸収法(FT-IR法)で算出可能である。例えば、[N-H]は振動波数3340cm<sup>-1</sup>付近のストレッチングモードの振動ピークから、[N-D]は振動波数2370cm<sup>-1</sup>付近のストレッチングモードの振動ピークから、算出することができる。

## 【0170】

以上のように、本実施形態によれば、書き込み/消去時に生じるトンネル絶縁膜のリーク電流を大幅に低減させることができ、不揮発性メモリ素子の電荷保持特性を向上させることができる。

## 【0171】

10

## [実施形態9]

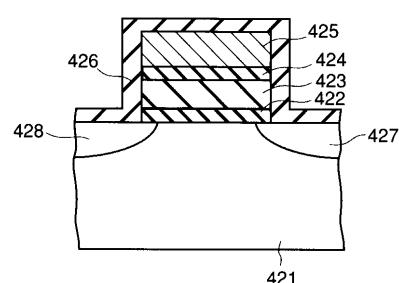

図33は、本発明の第9の実施形態に係る半導体装置(不揮発性メモリ)の構造を示した断面図である。シリコン基板421上には、トンネル絶縁膜(ボトム絶縁膜)422、電荷蓄積膜となるシリコン窒化膜423、トップ絶縁膜424及び制御ゲート電極425が、順次形成されている。また、シリコン基板421上及びゲート構造の周囲には、側壁酸化膜426が形成されている。さらに、ゲート構造を挟んで、ソース領域427及びドレイン領域428が形成されている。すなわち、本実施形態は、MONOS構造を有する不揮発性メモリに関するものである。なお、図33に示した例では、トンネル絶縁膜422は、制御ゲート電極425の直下にのみ存在しているが、制御ゲート電極425の外側にまで延在していても良い。

20

## 【0172】

トンネル絶縁膜422は、シリコン窒化膜で形成され、シリコン窒化膜中には窒素に結合した水素が含まれている。この水素の主成分は重水素(D)である。なお、トンネル絶縁膜422(シリコン窒化膜)の基本的な構成及び製造方法等については、第8の実施形態と同様である。

## 【0173】

本実施形態においても、シリコン窒化膜中に重水素を含有させることで、第8の実施形態と同様に、不揮発性メモリ素子の電荷保持特性を向上させることができる。

## 【0174】

30

以上、本発明の実施形態を説明したが、本発明は上記実施形態に限定されるものではなく、その趣旨を逸脱しない範囲内において種々変形して実施することが可能である。さらに、上記実施形態には種々の段階の発明が含まれており、開示された構成要件を適宜組み合わせることによって種々の発明が抽出され得る。例えば、開示された構成要件からいくつかの構成要件が削除されても、所定の効果が得られるものであれば発明として抽出され得る。

## 【0175】

## 【発明の効果】

本発明によれば、下層側シリコン窒化膜と上層側シリコン窒化膜との積層構造を用いることにより、特性及び生産性に優れた半導体装置を得ることが可能となる。

## 【0176】

40

また、本発明によれば、下層側シリコン窒化膜と上層側シリコン窒化膜との積層構造を用いることにより、電荷保持特性等に優れた半導体装置を得ることが可能となる。

## 【0177】

さらに、本発明によれば、シリコン窒化膜に重水素を含有させることにより、電荷保持特性等に優れた半導体装置を得ることが可能となる。

## 【図面の簡単な説明】

【図1】本発明の第1の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

【図2】本発明の第1の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

50

【図 3】本発明の第 1 の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

【図 4】本発明の第 1 の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

【図 5】本発明の第 1 の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

【図 6】本発明の実施形態に係り、SiN膜におけるN/Si組成比とリーク電流との関係を示した図である。

【図 7】本発明の実施形態に係り、SiN膜におけるN/Si組成比と密度との関係を示した図である。

【図 8】本発明の第 2 の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

【図 9】本発明の第 2 の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

【図 10】本発明の第 2 の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

【図 11】本発明の第 2 の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

【図 12】本発明の第 2 の実施形態に係る半導体装置の製造方法の一部を示した断面図である。

【図 13】本発明の第 3 の実施形態に係る半導体装置の構造を示した断面図である。

【図 14】本発明の第 4 の実施形態に係る半導体装置の構造を示した断面図である。

【図 15】本発明の実施形態に係り、各種のシリコン窒化膜について電荷保持特性を示した図である。

【図 16】本発明の実施形態に係り、シリコン窒化膜の膜厚を変化させたときの電荷保持特性を示した図である。

【図 17】本発明の第 5 の実施形態に係る半導体装置の一例を示した断面図である。

【図 18】本発明の第 5 の実施形態に係る半導体装置の他の例を示した断面図である。

【図 19】本発明の第 5 の実施形態に係る半導体装置のさらに他の例を示した断面図である。

【図 20】本発明の第 5 の実施形態に係る半導体装置のさらに他の例を示した断面図である。

【図 21】本発明の実施形態に係り、水素濃度と深さとの関係を示した図である。

【図 22】本発明の実施形態に係り、酸素濃度と深さとの関係を示した図である。

【図 23】本発明の実施形態に係り、データ保持時間とフラットバンド電圧との関係を示した図である。

【図 24】本発明の実施形態に係り、プログラム電圧とフラットバンド電圧との関係を示した図である。

【図 25】本発明の実施形態に係り、蓄積電荷の重心の深さと蓄積電荷密度との関係を示した図である。

【図 26】本発明の実施形態の比較例に係り、蓄積電荷の重心の深さと蓄積電荷密度との関係を示した図である。

【図 27】本発明の実施形態に係り、NAND型素子の構成を示した電気回路図である。

【図 28】本発明の実施形態に係り、重水素アニールの効果を示した図である。

【図 29】本発明の実施形態に係り、重水素アニールの効果を示した図である。

【図 30】本発明の第 7 の実施形態に係る半導体装置の構造を示した断面図である。

【図 31】図 30 の半導体装置をインバータに適用した例を示した電気回路図である。

【図 32】本発明の第 8 の実施形態に係る半導体装置の構造を示した断面図である。

【図 33】本発明の第 9 の実施形態に係る半導体装置の構造を示した断面図である。

【符号の説明】

10

20

30

40

50

|                                                                  |    |

|------------------------------------------------------------------|----|

| 1 0 1、 1 2 1、 1 4 1、 2 0 1、 3 0 1、 3 4 1、 4 0 1、 4 2 1 ...シリコン基板 |    |

| 1 0 2 ...素子分離領域                                                  |    |

| 1 0 3、 1 2 4、 3 5 4 ...ゲート絶縁膜                                    |    |

| 1 0 4、 1 2 5、 3 4 5 ...シリコン膜                                     |    |

| 1 0 5 ...窒化タンゲステン膜                                               |    |

| 1 0 6 ...タンゲステン膜                                                 |    |

| 1 0 7、 2 0 6、 3 0 6、 3 4 6 ...T C S - S i N 膜                    |    |

| 1 0 8、 2 0 3、 3 0 3、 3 4 3 ...D C S - S i N 膜                    |    |

| 1 0 9 ...レジスト膜                                                   |    |

| 1 1 0 ...絶縁用の S i N 膜                                            | 10 |

| 1 1 1、 1 2 2、 1 4 9 ...ソース/ドレイン領域                                |    |

| 1 2 3 ...エクステンション領域                                              |    |

| 1 2 6、 3 0 8、 3 4 8、 4 0 6、 4 2 6 ...側壁絶縁膜                       |    |

| 1 2 7、 1 4 7、 1 4 8 ...S i N 膜 ( 積層構造 )                          |    |

| 1 2 8、 3 5 0 a、 3 5 0 b ...シリサイド膜                                |    |

| 1 2 9 ...S i N 膜 ( エッティングストッパー )                                 |    |

| 1 3 0 ...層間絶縁膜                                                   |    |

| 1 3 1 ...コンタクト電極                                                 |    |

| 1 4 2、 4 0 2 ...トンネル絶縁膜                                          |    |

| 1 4 3、 4 0 3 ...浮遊電極 ( 電荷蓄積膜 )                                   | 20 |

| 1 4 4、 4 0 4 ...中間絶縁膜                                            |    |

| 1 4 5、 2 0 5、 3 0 5、 4 0 5、 4 2 5 ...制御電極                        |    |

| 1 4 6 ...シリサイド膜                                                  |    |

| 2 0 2、 3 0 2、 4 2 2 ...ボトム絶縁膜 ( トンネル絶縁膜 )                        |    |

| 2 0 4、 3 0 4、 4 2 4 ...トップ絶縁膜                                    |    |

| 2 0 7、 3 0 7、 3 4 7 ...界面領域                                      |    |

| 3 0 9 ...上層絶縁膜                                                   |    |

| 3 1 0 ...金属性導電膜                                                  |    |

| 3 1 1、 4 0 7、 4 2 7 ...ソース領域                                     |    |

| 3 1 2、 4 0 8、 4 2 8 ...ドレイン領域                                    | 30 |

| 3 2 1 ...絶縁膜                                                     |    |

| 3 2 2 ...導電体膜                                                    |    |

| 3 2 3 ...素子分離絶縁膜                                                 |    |

| 3 4 2、 3 5 8 ...シリコン酸化膜                                          |    |

| 3 5 1 ...浅いソース拡散層                                                |    |

| 3 5 1 a ...深いソース拡散層                                              |    |

| 3 5 2 ...浅いドレイン拡散層                                               |    |

| 3 5 2 a ...深いドレイン拡散層                                             |    |

| 3 6 1 ...n型M I S F E T                                           |    |

| 3 6 2 ...p型M I S F E T                                           | 40 |

| 4 2 3 ...シリコン窒化膜 ( 電荷蓄積膜 )                                       |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 13】

【図 14】

【図 11】

【図 12】

【図 15】

【図 16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図23】

【図22】

【図24】

【 図 25 】

【 図 2 6 】

〔 四 三 〇 〕

【図3-1】

【 図 27 】

【 义 2 8 】

【 図 2 9 】

【 図 3 2 】

【 义 3 3 】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

|         |         |         |       |         |

|---------|---------|---------|-------|---------|

| H 0 1 L | 21/8247 | H 0 1 L | 29/44 | S       |

| H 0 1 L | 27/108  | H 0 1 L | 27/10 | 4 3 4   |

| H 0 1 L | 27/115  | H 0 1 L | 27/10 | 6 7 1 Z |

| H 0 1 L | 29/41   | H 0 1 L | 29/78 | 3 0 1 Y |

| H 0 1 L | 29/423  | H 0 1 L | 29/78 | 3 0 1 P |

| H 0 1 L | 29/49   |         |       |         |

| H 0 1 L | 29/788  |         |       |         |

| H 0 1 L | 29/792  |         |       |         |

(74)代理人 100070437

弁理士 河井 将次

(72)発明者 田中 正幸

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 小澤 良夫

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 斎田 繁彦

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 合田 晃

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 野口 充宏

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 三谷 祐一郎

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 細島 祥隆

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

審査官 松本 貢

(56)参考文献 特開2000-349283(JP,A)

特開2002-203917(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 29/78

H01L 21/283

H01L 21/318

H01L 21/336

H01L 21/8242

H01L 21/8247

H01L 27/108

H01L 27/115

H01L 29/41

H01L 29/423

H01L 29/49

H01L 29/788

H01L 29/792