(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 102 17 290 B4 2010.04.08

(12)

## Patentschrift

(21) Aktenzeichen: 102 17 290.0

(51) Int Cl.<sup>8</sup>: G11C 11/413 (2006.01)

(22) Anmeldetag: 18.04.2002

G11C 7/00 (2006.01)

(43) Offenlegungstag: 07.11.2002

(45) Veröffentlichungstag

der Patenterteilung: 08.04.2010

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

09/845,387 30.04.2001 US

(72) Erfinder:

Naffziger, Samuel D., Fort Collins, Col., US

(73) Patentinhaber:

Samsung Electronics Co., Ltd., Suwon-si,

Gyeonggi-do, KR

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

|    |             |    |

|----|-------------|----|

| DE | 689 16 858  | T2 |

| US | 48 05 149   | A  |

| JP | 02-1 21 190 | A  |

| US | 52 85 420   | A  |

| US | 60 14 732   | A  |

(74) Vertreter:

Kuhnen & Wacker Patent- und

Rechtsanwaltsbüro, 85354 Freising

(54) Bezeichnung: Verfahren zum Schreiben in einen RAM mit Spaltenlöschung

(57) Hauptanspruch: Verfahren zum Schreiben in einen RAM mit Spaltenlöschung, wobei das Verfahren folgende Schritte aufweist:

Schreiben eines zweiten Logikzustands in mindestens eine Speicherzelle von Speicherzellen einer ersten ausgewählten Reihe in einem Array von Speicherzellen, wobei das Array in Reihen und Spalten von Speicherzellen angeordnet ist, durch:

Schreiben (202) eines ersten Logikzustands in alle der Speicherzellen einer ersten ausgewählten Reihe, wobei das Schreiben eine Zugriffsvorrichtung verwendet; und als nächstes

Löschen (204) der mindestens einen der Speicherzellen der ersten ausgewählten Reihe auf den zweiten Logikzustand, wobei das Löschen eine erste Freigabeleitung für die erste ausgewählte Reihe und eine Löschleitung für jede von mindestens einer Spalte entsprechend der mindestens einen der Speicherzellen verwendet.

## Beschreibung

**[0001]** Die vorliegende Erfindung bezieht sich allgemein auf integrierte Schaltungen und insbesondere auf Techniken und Schaltungen zum Speichern von Daten in einen statischen Direktzugriffsspeicher.

**[0002]** Aus der US 4,805,149 A ist eine Speichervorrichtung mit einer Mehrzahl von Speicherzellen bekannt, die in einer Matrix mit Zeilen und Spalten angeordnet sind. Die Speichervorrichtung enthält eine Zeilenaktivierungsschaltung zum gleichzeitigen Aktivieren aller Zeilen der Matrix sowie eine Spaltenaktivierungsschaltung zum gleichzeitigen Anlegen entweder eines Rücksetzungssignals oder eines Voreinstellungssignals an die Spalten der Matrix.

**[0003]** Aus der DE 68 916 858 T2 ist ein SRAM mit mehreren I/O-Leitungen bekannt, der ein Speicherzellenarray mit Spalten aufweist, wobei die Spalten selektiv als Funktion der assoziierten I/O-Leitung gelöscht werden können. Die Spalten sind in Paaren angeordnet, wobei jede Spalte in dem Paar mit der gleichen I/O-Leitung assoziiert ist. Ein Löschsignal wird über eine Leitung eingespeist und einen Treiber getrieben. Das Löschsignal ist nur mit dem Paar verknüpft, das mit der ausgewählten I/O-Leitung assoziiert ist. Die übrigen Spalten, die mit den nicht ausgewählten I/O-Leitungen verknüpft sind, werden nicht gelöscht.

**[0004]** JP 02-121190 A beschreibt ein SRAM-Speicherelement mit einer Matrix aus Speicherzellen, von der jede aus einer Auswahlwortleitung, zwei Bitleitungen und Flip-Flop-Schaltungen aufgebaut ist. Bei dem SRAM-Speicherelement ist ferner eine Potentialeinstellungseinrichtung vorgesehen, die ein vorbestimmtes Potential in den Flip-Flop-Schaltungen unabhängig von den Bitleitungen einstellt, wobei ferner eine oder mehrere Potentialeinstellungssteuerleitungen zum Steuern der Potentialeinstellungseinrichtung vorgesehen sind. Wenn eine Speicherzelle gelöscht werden soll, wird der Löschgong mit der Potentialeinstellungseinrichtung während der Vorladeperiode der Bitleitungen durchgeführt.

**[0005]** Aus der US 5,285,420 A ist eine Speichervorrichtung mit einem Speicherzellenarray, einer Leseorschaltung, einer Schreibschaltung und einer Rücksetzschatzung bekannt. Die Leseschaltung ist zum selektiven Auslesen der Datenbits aus den Speicherzellen betreibbar. Die Schreibschaltung ist zum selektiven Schreiben von Datenbits in die Speicherzellen betreibbar. Die Rücksetzschatzung umfasst eine Mehrzahl von einzelnen Schaltungen, die jeweils an die Speicherzellen gekoppelt sind und auf ein externes Rücksetz-Steuersignal ansprechen, um zu bewirken, dass die Schaltungen laufend die Rücksetz-Datenbits den Speicherzellen zuführen.

**[0006]** Ein statischer Direktzugriffsspeicher (SRAM; SRAM = static random access memory) wird in vielen elektronischen Systemen verwendet, um digitale Daten zu speichern, ohne einen Bedarf nach einer periodischen Aktualisierung. Der Cash-Speicher vieler Computersysteme besteht z. B. aus einem SRAM. Eine typische SRAM-Zelle, die in einem Metalloxidhalbleiter-(MOS-; MOS = metal-oxide-semiconductor)Prozeß mit einem Lese-/Schreib-Tor produziert wurde, ist oft aus sechs Transistoren hergestellt – vier Transistoren zum Halten der Daten und zwei Transistoren pro Lese-/Schreib-Tor, die als Zugriffsvorrichtungen verwendet werden. Die Zugriffsvorrichtungen werden üblicherweise durch "Wortleitungen" gesteuert, die in eine erste Richtung laufen (z. B. über eine Reihe oder in die horizontale Richtung, wenn es in eine gewisse Richtung ausgerichtet gesehen wird), und würde Daten aus "Bitleitungen" nehmen/ablegen, die in eine andere Richtung laufen (z. B. entlang einer Spalte oder in die vertikale Richtung, betrachtet aus der oben beschriebenen Ansicht). Daher erfordert eine typische SRAM-Zelle eine Wortleitung, die in die horizontale Richtung läuft, pro Reihe von SRAM-Zellen, und zwei Bitleitungen, die in die vertikale Richtung laufen, pro Spalte von SRAM-Zellen.

**[0007]** Einige spezialisierte Anwendungen erfordern jedoch eine SRAM-Zelle, die eine Funktionalität zusätzlich zu einem einzelnen Lese-/Schreib-Tor aufweist. Eine derartig spezialisierte Anwendung umfaßt die Speicherung von "physikalischen Treffervektoren", wie in der U.S. 6,014,732 beschrieben ist, die hierdurch hierin durch Bezugnahme aufgenommen wird. Diese Anwendung erfordert zwei Lese-/Schreib-Tore und die Fähigkeit, eine gesamte Spalte von SRAM-Zellen zu löschen.

**[0008]** Das Hinzufügen eines anderen Lese-/Schreib-Tors und die Fähigkeit, eine gesamte Spalte zu löschen, erhöht die Anzahl von Wortleitungen, die horizontal laufen, und die Anzahl von Bitleitungen, die vertikal laufen. Genauer gesagt würden zwei zusätzliche Bitleitungen, die vertikal laufen, für das zweite Lese-/Schreib-Tor und eine „Löschen“-Leitung für jede Spalte von SRAM-Zellen gebraucht, die ebenfalls vertikal läuft. Auf ähnliche Weise müßte eine zusätzliche Wortleitung horizontal über jede Reihe von SRAM-Zellen laufen. Dies bringt die gesamte Anzahl von Leitungen, die vertikal über eine gegebene SRAM-Zelle laufen, auf fünf, und die gesamte Anzahl von Leitungen, die horizontal laufen, auf zwei, also insgesamt sieben Leitungen, die über jede SRAM-Zelle laufen.

**[0009]** Diese Anzahl von Leitungen, insbesondere Leitungen, die in eine vertikale Richtung laufen, neigt dazu, die Größe der SRAM-Zelle bedeutend zu erhöhen und deren Betriebsfrequenz zu reduzieren. Dementsprechend besteht ein Bedarf in der Technik nach einer zweitorigen SRAM-Zelle mit einer Spalten-

löschfunktion, die weniger als fünf vertikale Leitungen und weniger als sieben Leitungen insgesamt über die Zelle aufweist.

**[0010]** Es ist die Aufgabe der vorliegenden Erfindung, ein verbessertes Verfahren zum Schreiben in ein RAM-Array zu schaffen.

**[0011]** Diese Aufgabe wird gelöst durch ein Verfahren gemäß Anspruch 1. Weiterbildungen der Erfindung sind in den Unteransprüchen angegeben.

**[0012]** Die vorliegende Erfindung schafft eine SRAM-Zelle und ein -Array, das eine Spaltenlöscherfunktion mit nur drei vertikalen Leitungen und sechs Leitungen insgesamt über eine Zelle aufweist, und ein Verfahren zum Betreiben dieser Zelle und des Arrays dieser Zellen. Anstelle von zwei Bitleitungen pro Tor und zwei Zugriffsvorrichtungen pro Tor, wie in einer herkömmlichen SRAM-Zelle, wird eine Bitleitung und eine Zugriffsvorrichtung pro Tor verwendet. Zusätzlich dazu werden eine zusätzliche Bitleitung, eine zusätzliche Wortleitung und zwei Vorrichtungen in Reihe verwendet, um den Spaltenlöscherbetrieb durchzuführen und eine Schreiboperation abzuschließen.

**[0013]** Die Zelle wird zum Durchführen von Schreiboperationen unter Verwendung eines Zwei-Schritt-Prozesses betrieben. Um ein Schreiben durchzuführen, wird jede Zelle in einer zu schreibenden Reihe während eines ersten Schritts voreingestellt. Dann wird jede Zelle, für die eine Null geschrieben werden soll, unter Verwendung der zusätzlichen Bitleitung und der zusätzlichen Wortleitung gelöscht, um die zu löschen Zellen zu adressieren. Eine Zellspalte kann durch Freigeben aller Reihen zum Löschen und durch nachfolgendes Aktivieren des Spaltenlöschersteuersignals für jede zu löschen Spalte in dem Array gelöscht werden.

**[0014]** Andere Aspekte und Vorteile der vorliegenden Erfindung werden aus der nachfolgenden, detaillierten Beschreibung offensichtlich, die in Verbindung mit den beiliegenden Zeichnungen vorliegt, die die Prinzipien der Erfindung beispielhaft darstellen.

**[0015]** Bevorzugte Ausführungsbeispiele der vorliegenden Erfindung werden nachfolgend Bezug nehmend auf die beiliegenden Zeichnungen näher erläutert. Es zeigen:

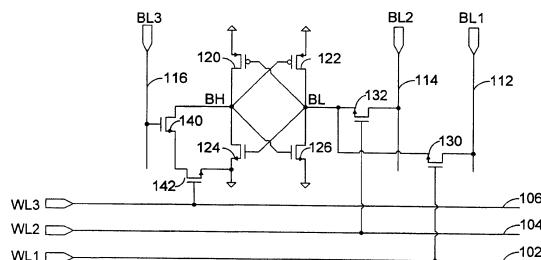

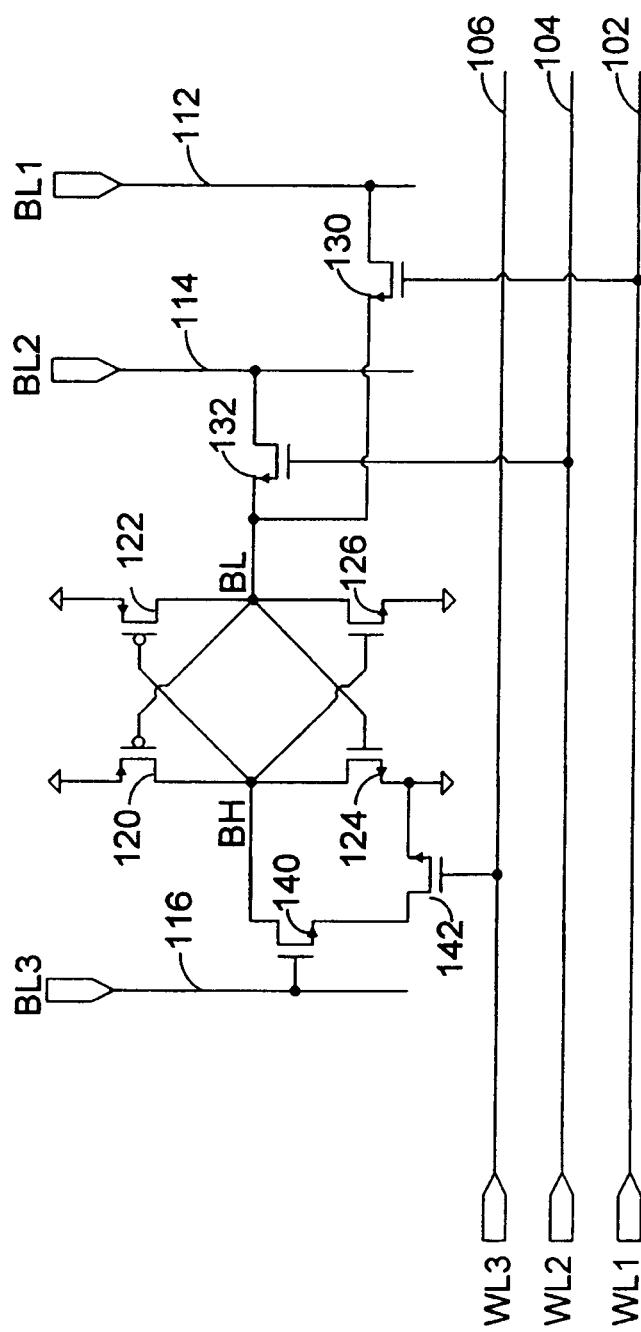

**[0016]** [Fig. 1](#) eine schematische Darstellung eines SRAM mit Spaltenlöscherfunktionalität, der insgesamt sechs Leitungen über denselben aufweist;

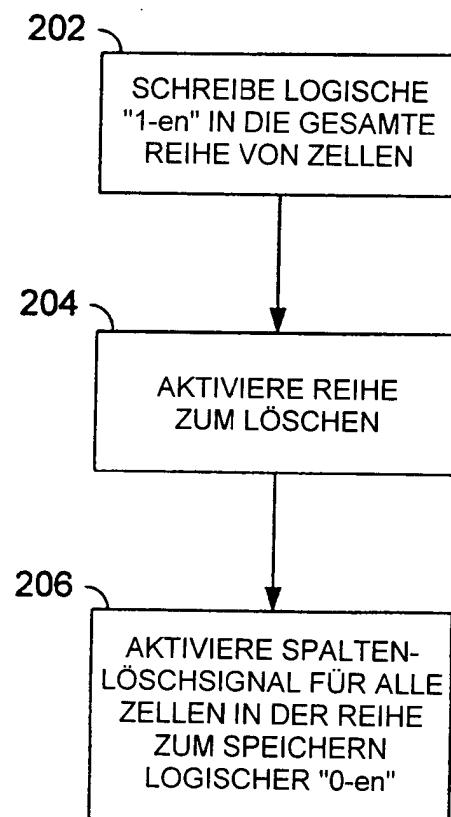

**[0017]** [Fig. 2](#) ein Flußdiagramm, das ein Verfahren zum Schreiben von Daten in eine Reihe der SRAM-Zellen darstellt, die in [Fig. 1](#) gezeigt sind; und

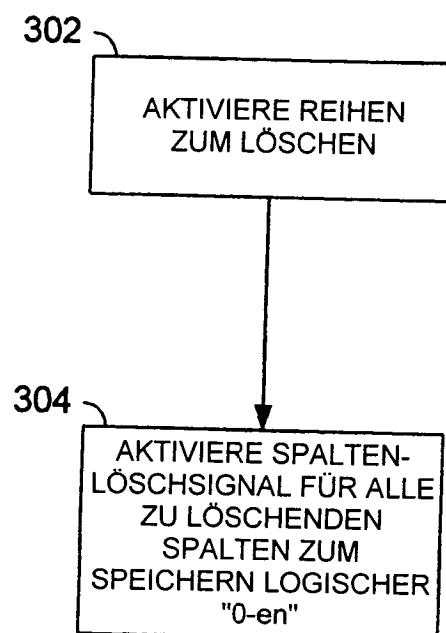

**[0018]** [Fig. 3](#) ein Flußdiagramm, das ein Verfahren

zum Löschen von mindestens einer Spalte von SRAM-Zellen darstellt, die in [Fig. 1](#) gezeigt sind.

**[0019]** [Fig. 1](#) ist eine schematische Darstellung eines SRAM mit einer Spaltenlöscherfunktionalität, der insgesamt sechs Leitungen über denselben aufweist. In [Fig. 1](#) laufen eine erste, eine zweite bzw. eine dritte Wortleitung WL1 **102**, WL2 **104**, WL3 **106** in einer ersten Richtung über die Zelle. Zu Darstellungszwecken wird diese erste Richtung hierin nachfolgend als die horizontale Richtung bezeichnet. Eine erste, eine zweite bzw. eine dritte Bitleitung BL1 **112**, BL2 **114**, BL3 **116** laufen in einer zweiten Richtung über die Zelle. Zu Darstellungszwecken wird dieselbe hierin nachfolgend als die vertikale Richtung bezeichnet. Wenn ferner die SRAM-Zellen von [Fig. 1](#) in einem zweidimensionalen Array plaziert sind, werden die zueinander benachbarten Zellen in der horizontalen Richtung derart bezeichnet, daß sie in einer Reihe sind, und die zueinander benachbarten Zellen in der vertikalen Richtung werden derart bezeichnet, daß sie sich in einer Spalte befinden. Abschließend wird darauf hingewiesen, daß die Gesamtanzahl von Leitungen, die die Zelle überqueren, sechs beträgt, und die Gesamtanzahl in der vertikalen Richtung drei ist. Dies ist vorteilhaft im Vergleich mit den insgesamt sieben und fünf Vertikalen einer herkömmlichen, zweitorigen Zelle mit Spaltenlöscherbedürfnissen.

**[0020]** Die P-Kanal-Feldeffekttransistoren (PFET; PFET = P-channel field effect transistor) **120** und **122** und die N-Kanal-Feldeffekttransistoren (NFET; NFET = N-channel field effect transistor) **124** und **126** bilden ein Paar kreuzgekoppelter CMOS-Inverter, die als ein Speicherelement der SRAM-Zelle wirken, die in [Fig. 1](#) gezeigt ist. Dies gilt ausschließlich zu Darstellungszwecken. Ein anderer Typ von Speicherelementen könnte ebenfalls verwendet werden. Die Erfindung könnte z. B. mit kreuzgekoppelten NMOS-Invertern, einem Flip-Flop, das aus NAND- oder NOR-Gattern gebildet ist, oder anderen Typen von Speicherelementen verwendet werden, die unterschiedliche Techniken verwenden, wie z. B. magnetische Direktzugriffsspeicherzellen (MRAM-Zellen; MRAM = magnetic random access memory).

**[0021]** Ein erster der quer gekoppelten Inverter ist durch den PFET **120** und den NFET **124** gebildet. Der Eingang zu diesem Inverter ist der Knoten BL und der Ausgang ist der Knoten BH. Die Quelle des PFET **120** ist mit der positiven Versorgungsspannung verbunden. Der Drain des PFET **120** ist mit dem Knoten BH verbunden, der mit dem Gatter des PFET **122**, dem Gatter des NFET **126**, dem Drain des NFET **124** und dem Drain des NFET **140** verbunden ist. Die Quelle des NFET **124** ist mit der negativen Versorgungsspannung verbunden. Die Gatter von sowohl dem PFET **120** und dem NFET **124** sind beide mit den Drains des PFET **122** und des NFET **126** verbunden.

**[0022]** Ein zweiter der quer gekoppelten Inverter ist durch den PFET **122** und den NFET **126** gebildet. Der Eingang zu diesem Inverter ist der Knoten BH und der Ausgang der Knoten BL. Die Quelle des PFET **122** ist mit der positiven Versorgungsspannung verbunden. Der Drain des PFET **122** ist mit dem Knoten BL verbunden, der mit dem Gatter des PFET **120**, dem Gatter des NFET **124**, dem Drain des NFET **126** und den Drains der NFETs **130** und **132** verbunden ist. Die Quelle des NFET **126** ist mit der negativen Versorgungsspannung verbunden. Die Gatter von sowohl dem PFET **122** und dem NFET **126** sind beide mit den Drains des PFET **120** und des NFET **124** verbunden.

**[0023]** Der NFET **130** ist eine erste Zugriffsvorrichtung. Das Gatter des NFET **130** ist mit der Wortleitung WL1 **102** verbunden. Der Drain des NFET **130** ist mit der Bitleitung BL1 **112** verbunden. Der NFET **132** ist eine zweite Zugriffsvorrichtung. Das Gatter des NFET **132** ist mit der Wortleitung **104** verbunden. Der Drain des NFET **132** ist mit der Bitleitung **114** verbunden.

**[0024]** Die NFETs **140** und **142** bilden eine Spaltenlöschlogik, die die Fähigkeit zum Löschen der Zelle liefert, wenn sie durch eine Reihe und eine Spalte richtig adressiert wird. Das Gatter des NFET **140** ist mit der Bitleitung BL3 **116** verbunden. Die Quelle des NFET **140** ist mit dem Drain des NFET **142** verbunden. Das Gatter des NFET **142** ist mit der Wortleitung WL3 **106** verbunden. Die Quelle des NFET **142** ist mit der negativen Versorgungsspannung verbunden.

**[0025]** Um die in [Fig. 1](#) gezeigte Zelle zu lesen, werden entweder eine oder beide Bitleitungen **112** und **114** vorgeladen und die Vorladevorrichtung wird ausgeschaltet, so daß die Bitleitungen **112** oder **114** auf einem Vorladepegel liegen. Wenn dann die Wortleitung **102** und/oder die Wortleitung **104** auf hoch gezogen werden, werden eine oder beide der Zugriffsvorrichtungen **130** bzw. **132** angeschaltet. Dies ermöglicht es dem Wert, der durch die Speicherelemente als Ausgangssignal an dem Knoten BL gespeichert ist, die Bitleitungen **112** oder **114** zu laden oder zu entladen. Die Bitleitungen **112** und **114** werden abhängig von dem Vorladepegel und dem Wert an dem Knoten BL geladen oder entladen. Wenn die Bitleitung **112** z. B. auf die positive Versorgungsspannung vorgeladen wurde und das Speicherelement BL auf tief getrieben hat (d. h. bei oder nahe dem negativen Versorgungsspannungspegel), dann würde die Bitleitung **112** durch die Zugriffsvorrichtung **130** und das Speicherelement entladen werden. Der gesenkten Spannungspegel der Bitleitung **112** könnte dann durch einen Leseverstärker an der Bitleitung **112** gelesen werden. Ein anderes Beispiel ist, wenn die Bitleitung **112** auf einen Zwischenwert vorgeladen wurde (d. h. nicht in der Nähe des positiven oder des negativen Versorgungsspannungspegels) und das

Speicherelement den BL auf ein Hoch getrieben hat (d. h. bei oder nahe dem positiven Versorgungsspannungspegel). In diesem Fall würde die Bitleitung **112** durch die Zugriffsvorrichtung **130** und das Speicherelement geladen werden. Dieser erhöhte Spannungspegel an der Bitleitung **112** könnte dann durch einen Leseverstärker an der Bitleitung **112** gelesen werden. Es wird darauf hingewiesen, daß zwei Lesungen gleichzeitig entweder von der gleichen oder von unterschiedlichen Reihen durchgeführt werden können, da zwei Zugriffsvorrichtungen **130**, **132** und zwei Bitleitungen **112**, **114** vorliegen.

**[0026]** Ein Verfahren zum Schreiben in eine Reihe bzw. Zeile von SRAM-Zellen gemäß [Fig. 1](#) ist durch ein Flußdiagramm dargestellt, das in [Fig. 2](#) gezeigt ist. Bei einem Schritt **202** werden logische Einsen in die gesamte Reihe von Zellen geschrieben, die geschrieben werden. Dies wird durch Treiben aller Bitleitungen BL1 **112** für die Reihe auf tief durchgeführt, während die Wortleitung WL1 **102** aktiv ist. Dies bewirkt, daß das Speichersignal eine logische Null an BL und eine logische Eins an BH hält. Es wird darauf hingewiesen, daß bei den in [Fig. 1](#) gezeigten Zellen die Wortleitungen WL1 **102**, WL2 **104**, WL3 **106** und die Bitleitung BL3 **116** aktiv sind, wenn dieselben auf hoch getrieben werden (d. h. zu der positiven Versorgungsspannung hin getrieben werden).

**[0027]** Bei einem Schritt **204** wird die Reihe zum Löschen aktiviert. Dies wird durch Freigeben von WL3 **106** durchgeführt. Um einen Treiberkampf zu verhindern, wenn WL3 aktiviert wird, sollten WL1 und WL2 deaktiviert werden.

**[0028]** Bei einem Schritt **206** werden die Spaltenlöschsignale für alle Zellen in der Reihe, die logische Nullen speichern sollen, aktiviert. Dies wird durch Aktivieren von BL3 **116** für die Spalten durchgeführt, die jeder Zelle in der Reihe entsprechen, die eine logische Null speichern soll. Dementsprechend verursacht dies, daß das Speicherelement für diese Zellen eine logische Eins auf dem BL und eine logische Null auf BH hält.

**[0029]** Ein Verfahren zum Löschen einer Spalte von SRAM-Zellen, gezeigt in [Fig. 1](#), wird durch ein Flußdiagramm dargestellt, gezeigt in [Fig. 3](#). Bei einem Schritt **302** werden alle der zu löschen Reihen in dem SRAM zum Löschen aktiviert. Dies wird durch Aktivieren von WL3 für alle zu löschen Reihen durchgeführt. Um eine gesamte Spalte zu löschen, würde die WL3 für alle Reihen aktiviert. Um die Spalten nur in einem Teilsatz von Reihen zu löschen, würde ein Teilsatz von WL3-Leitungen in dem Array aktiviert.

**[0030]** Bei einem Schritt **304** wird das Spaltenlöschesignal für die Spalten aktiviert, die gelöscht werden sollen. Dies wird durch Aktivieren von BL3 **116** für die

eine oder mehrere zu löschen Spalten durchgeführt.

### Patentansprüche

1. Verfahren zum Schreiben in einen RAM mit Spaltenlöschung, wobei das Verfahren folgende Schritte aufweist:

Schreiben eines zweiten Logikzustands in mindestens eine Speicherzelle von Speicherzellen einer ersten ausgewählten Reihe in einem Array von Speicherzellen, wobei das Array in Reihen und Spalten von Speicherzellen angeordnet ist, durch:

Schreiben (**202**) eines ersten Logikzustands in alle der Speicherzellen einer ersten ausgewählten Reihe, wobei das Schreiben eine Zugriffsvorrichtung verwendet; und als nächstes

Löschen (**204**) der mindestens einen der Speicherzellen der ersten ausgewählten Reihe auf den zweiten Logikzustand, wobei das Löschen eine erste Freigabeleitung für die erste ausgewählte Reihe und eine Löscheleitung für jede von mindestens einer Spalte entsprechend der mindestens einen der Speicherzellen verwendet.

2. Verfahren nach Anspruch 1, wobei zum Löschen der mindestens einen der Speicherzellen der ersten ausgewählten Reihe auf den zweiten Logikzustand mindestens eines aus einer Mehrzahl von Spaltenlöschsignalen (**206**) entsprechend der mindestens einen der Speicherzellen der ersten ausgewählten Reihe aktiviert wird, während ein erstes Löschfreigabesignal für die erste ausgewählte Reihe aktiv ist, wobei das Löschen nach dem Schreiben (**202**) eines ersten Logikzustands in alle der Speicherzellen einer ersten ausgewählten Reihe durchgeführt wird.

3. Verfahren gemäß Anspruch 1, bei dem das Schreiben von Daten ferner folgenden Schritt aufweist:

Aktivieren eines zweiten Löschfreigabesignals für eine zweite ausgewählte Reihe einer Mehrzahl von Speicherzellen.

4. Verfahren gemäß Anspruch 2, bei dem das Aktivieren von dem mindestens einen der Mehrzahl von Spaltenlöschsignalen (**206**), während das erste Löschfreigabesignal aktiv ist, den zweiten Logikwert in jeder Speicherzelle der Reihe der Mehrzahl von Speicherzellen speichert, die ein aktiviertes Spaltenlöschsignal (**206**) aufweist.

5. Verfahren nach Anspruch 1, wobei das Schreiben des ersten Logikzustands in alle der Speicherzellen der ersten ausgewählten Reihe folgende Schritte aufweist:

Treiben von Datenleitungen für jede Spalte des Arrays von Speicherzellen auf den ersten Logikwert; und

Aktivieren einer zweiten Freigabeleitung für die erste ausgewählte Reihe des Arrays von Speicherzellen und dadurch Speichern (**202**) des ersten Logikwerts in jede einer Mehrzahl von Speicherzellen in der ersten ausgewählten Reihe des Arrays von Speicherzellen;

und wobei das Löschen der mindestens einen der Speicherzellen der ersten ausgewählten Reihe auf den zweiten Logikzustand folgende Schritte aufweist: Aktivieren (**204**) der ersten Freigabeleitung für die erste ausgewählte Reihe des Arrays von Speicherzellen; und

Aktivieren (**206**) von mindestens einer Spaltenlöschleitung für eine Spalte des Arrays von Speicherzellen und dadurch Speichern eines zweiten Logikwerts in der mindestens einen der Mehrzahl von Speicherzellen in der Reihe des Arrays von Speicherzellen, wobei das Aktivieren der mindestens einen Spaltenlöschleitung nach dem Aktivieren der ersten Freigabeleitung durchgeführt wird.

6. Verfahren gemäß Anspruch 5, bei dem das Schreiben von Daten ferner folgende Schritte aufweist:

Aktivieren einer dritten Freigabeleitung für eine zweite Reihe des Arrays von Speicherzellen und dadurch Speichern (**202**) des ersten Logikwerts in jede einer zweiten Mehrzahl von Speicherzellen in der zweiten Reihe des Arrays von Speicherzellen; und Aktivieren (**204**) einer vierten Freigabeleitung für die zweite Reihe des Arrays von Speicherzellen.

7. Verfahren gemäß Anspruch 6, wobei durch den Schritt des Aktivierens (**206**) von der mindestens einen Spaltenlöschleitung für eine Spalte des Arrays von Speicherzellen der zweite Logikwert in mindestens einer der zweiten Mehrzahl von Speicherzellen in der zweiten Reihe des Arrays von Speicherzellen gespeichert wird.

Es folgen 3 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3