(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4283431号

(P4283431)

(45) 発行日 平成21年6月24日(2009.6.24)

(24) 登録日 平成21年3月27日(2009.3.27)

(51) Int.Cl.

F 1

|      |        |           |      |           |

|------|--------|-----------|------|-----------|

| G09G | 3/36   | (2006.01) | G09G | 3/36      |

| G02F | 1/133  | (2006.01) | G02F | 1/133 520 |

| G02F | 1/1345 | (2006.01) | G02F | 1/1345    |

| G09F | 9/00   | (2006.01) | G09F | 9/00 348Z |

| G09G | 3/20   | (2006.01) | G09G | 3/20 621M |

請求項の数 16 (全 15 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2000-332023 (P2000-332023)  |

| (22) 出願日  | 平成12年10月31日 (2000.10.31)      |

| (65) 公開番号 | 特開2002-140042 (P2002-140042A) |

| (43) 公開日  | 平成14年5月17日 (2002.5.17)        |

| 審査請求日     | 平成17年10月24日 (2005.10.24)      |

早期審査対象出願

前置審査

|           |                                                   |

|-----------|---------------------------------------------------|

| (73) 特許権者 | 000005108<br>株式会社日立製作所<br>東京都千代田区丸の内一丁目6番6号       |

| (74) 代理人  | 100083552<br>弁理士 秋田 収喜                            |

| (74) 復代理人 | 100103746<br>弁理士 近野 恵一                            |

| (72) 発明者  | 上田 和成<br>千葉県茂原市早野3300番地 株式会社<br>日立製作所 ディスプレイグループ内 |

| (72) 発明者  | 遠藤 秀介<br>千葉県茂原市早野3300番地 株式会社<br>日立製作所 ディスプレイグループ内 |

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

一対の基板と、当該一対の基板間に狭持される液晶とを有する液晶表示素子を有する液晶表示装置であって、

前記一対の基板の一方の基板上には、複数のゲート信号線と該複数のゲート信号線に交差するように配置された複数のドレイン信号線が配置されて表示領域を形成しており、

前記一方の基板の一辺側には、テープ上に搭載され、前記複数のドレイン信号線に電気的に接続されているドレインドライバが配置されており、さらに該ドレインドライバが配置されたテープは、前記一方の基板の一辺に沿って複数個並んで配置されており、

前記複数個の該ドレインドライバが配置されたテープは、前記液晶表示素子が配置されている側とは反対側において、ドレン基板により共通に接続されており、

前記一方の基板の前記一辺と隣接する別の一辺側の角部には、テープ上に搭載され、前記複数のゲート信号線に電気的に接続されたゲートドライバが配置されており、

前記一方の基板上には、前記複数のドレインドライバが搭載されたテープのうち、前記一方の基板の別の一辺側に最も近い位置に配置されたドレインドライバが搭載されたテープから、前記ゲートドライバが搭載されたテープに接続された複数の信号配線が配置されており、

前記複数の信号配線は、前記ドレン基板に接続され、タイミングコントローラ及び電源回路を搭載したタイミングコントロール基板からの信号を伝達する信号配線であり、

前記一対の基板に配置されたコモン電極に印加する電圧を供給する信号配線と、

10

20

前記ドレイン信号線と前記ゲート信号線の交点に対応して配置されている薄膜トランジスタをオンする電圧を供給する信号配線と、

前記薄膜トランジスタをオフする電圧を供給する信号配線と、

前記ゲートドライバの電源電圧を供給する信号配線と、

接地電圧を供給する信号配線とを有し、

前記複数の信号配線は、配線間隔が第一の配線間隔を有する隣接する一組の信号配線と、前記第一の配線間隔よりも狭い第二の配線間隔を有する隣接する他の一組の信号配線をしており、

前記第一の配線間隔を有する隣接する前記一組の信号配線間の電位差が、前記第二の配線間隔を有する隣接する前記他の一組の信号配線間の電位差よりも大きく、

前記コモン電極に印加する電圧 (V<sub>c o m</sub>)、

前記薄膜トランジスタをオンする電圧 (V<sub>G H</sub>)、

前記薄膜トランジスタをオフする電圧 (V<sub>G L</sub>)、

前記ゲートドライバの電源電圧 (V<sub>c c</sub>)、

接地電圧 (GND) は、

V<sub>G H</sub> > V<sub>c o m</sub> > V<sub>c c</sub> > GND > V<sub>G L</sub>、

の関係を満たすことを特徴とする液晶表示装置。

#### 【請求項 2】

前記一方の基板の別の一边側には、該別の一边に沿ってゲートドライバが搭載されたテーブが複数個配置されていることを特徴とする請求項 1 に記載の液晶表示装置。

#### 【請求項 3】

前記薄膜トランジスタをオンする電圧を供給する信号配線と、前記ゲートドライバの電源電圧を供給する信号配線とは隣接されており、

前記ゲートドライバの電源電圧を供給する信号配線と、前記接地電圧を供給する信号配線とは隣接されており、

前記薄膜トランジスタをオンする電圧を供給する信号配線と前記ゲートドライバの電源電圧を供給する信号配線の配線間隔が、前記ゲートドライバの電源電圧を供給する信号配線と前記接地電圧を供給する信号配線の配線間隔よりも広いことを特徴とする請求項 1 または請求項 2 に記載の液晶表示装置。

#### 【請求項 4】

前記接地電圧を供給する信号配線と前記薄膜トランジスタをオフする電圧を供給する信号配線とは隣接されていることを特徴とする請求項 1 または請求項 2 に記載の液晶表示装置。

#### 【請求項 5】

前記薄膜トランジスタをオンする電圧を供給する信号配線と、前記ゲートドライバの電源電圧を供給する信号配線とは隣接されており、

前記薄膜トランジスタをオンする電圧を供給する信号配線と前記ゲートドライバの電源電圧を供給する信号配線の配線間隔が、前記接地電圧を供給する信号配線と前記薄膜トランジスタをオフする電圧を供給する信号配線の配線間隔よりも広いことを特徴とする請求項 4 に記載の液晶表示装置。

#### 【請求項 6】

前記薄膜トランジスタをオンする電圧を供給する信号配線と、前記ゲートドライバの電源電圧を供給する信号配線とは隣接されており、

前記コモン電極に印加する電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線とは隣接されており、

前記薄膜トランジスタをオンする電圧を供給する信号配線と前記ゲートドライバの電源電圧を供給する信号配線の配線間隔が、前記コモン電極に印加する電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線の配線間隔よりも広いことを特徴とする請求項 1 または請求項 2 に記載の液晶表示装置。

#### 【請求項 7】

10

20

30

40

50

前記コモン電極に印加する電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線とは隣接されており、

前記薄膜トランジスタをオフする電圧を供給する信号配線と、前記接地電圧を供給する信号配線とは隣接されており、

前記コモン電極に印加する電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線の配線間隔が、前記薄膜トランジスタをオフする電圧を供給する信号配線と前記接地電圧を供給する信号配線の配線間隔よりも広いことを特徴とする請求項1または請求項2に記載の液晶表示装置。

**【請求項8】**

前記コモン電極に印加する電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線とは隣接されており、

前記接地電圧を供給する信号配線と、前記ゲートドライバの電源電圧を供給する信号配線は隣接されており、

前記コモン電極に印加する電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線の配線間隔が、前記接地電圧を供給する信号配線と前記ゲートドライバの電源電圧を供給する信号配線の配線間隔よりも広いことを特徴とする請求項1または請求項2に記載の液晶表示装置。

**【請求項9】**

前記接地電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線とは隣接されており、

前記接地電圧を供給する信号配線と、前記ゲートドライバの電源電圧を供給する信号配線は隣接されており、

前記接地電圧を供給する信号配線と前記薄膜トランジスタをオフする電圧を供給する信号配線の配線間隔が、前記接地電圧を供給する信号配線と、前記ゲートドライバの電源電圧を供給する信号配線の配線間隔よりも広いことを特徴とする請求項1または請求項2に記載の液晶表示装置。

**【請求項10】**

一対のガラス基板と、当該一対のガラス基板間に狭持される液晶とを有する液晶表示素子を有する液晶表示装置であつて、

前記一対のガラス基板の一方のガラス基板上には、複数のゲート信号線と該複数のゲート信号線に交差するように配置された複数のドレイン信号線が配置されて表示領域を形成しており、

前記一方のガラス基板の一辺側には、テープ上に搭載され、前記複数のドレイン信号線に電気的に接続されているドレインドライバが配置されており、さらに該ドレインドライバが配置されたテープは、前記一方の基板の一辺に沿って複数個並んで配置されており、

前記複数個の前記ドレインドライバが配置されたテープは、前記液晶表示素子が配置されている側とは反対側において、ドレイン基板により共通に接続されており、

前記一方のガラス基板の前記一辺と隣接する別の一辺側には、テープ上に搭載され、前記複数のゲート信号線に電気的に接続されたゲートドライバが配置されており、さらに該ゲートドライバが配置されたテープは、該別の一辺に沿って複数個並んで配置されており、

前記一方のガラス基板上には、前記複数のドレインドライバが搭載されたテープのうち、前記別の一辺側に最も近い位置に配置された前記ドレインドライバが搭載されたテープから、前記複数のゲートドライバが搭載されたテープのうち、前記一辺側に最も近い位置に配置された前記ゲートドライバが搭載されたテープに接続された複数の信号配線が配置されており、

前記複数の信号配線は、

前記一対のガラス基板に配置されたコモン電極に印加する電圧を供給する信号配線と、

前記ドレイン信号線と前記ゲート信号線の交点に対応して配置されている薄膜トランジスタをオンする電圧を供給する信号配線と、

10

20

30

40

50

前記薄膜トランジスタをオフする電圧を供給する信号配線と、

前記ゲートドライバの電源電圧を供給する信号配線と、

接地電圧を供給する信号配線とを有し、

前記コモン電極に印加する電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線とは隣接されており、

前記ゲートドライバの電源電圧を供給する信号配線と、前記接地電圧を供給する信号配線とは隣接されており、

前記コモン電極に印加する電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線の配線間隔が、前記ゲートドライバの電源電圧を供給する信号配線と前記接地電圧を供給する信号配線の配線間隔よりも広く、

前記コモン電極に印加する電圧を供給する信号配線と、前記薄膜トランジスタをオフする電圧を供給する信号配線間の電位差が、前記ゲートドライバの電源電圧を供給する信号配線と前記接地電圧を供給する信号配線間の電位差よりも大きいことを特徴とする液晶表示装置。

#### 【請求項 1 1】

前記複数の信号配線は、

前記ドレン基板に接続され、タイミングコントローラ及び電源回路を搭載したタイミングコントロール基板からの信号を伝達する信号配線である請求項1 0に記載の液晶表示装置。

#### 【請求項 1 2】

前記コモン電極に印加する電圧 (V<sub>c o m</sub>)、

前記薄膜トランジスタをオンする電圧 (V<sub>G H</sub>)、

前記薄膜トランジスタをオフする電圧 (V<sub>G L</sub>)、

前記ゲートドライバの電源電圧 (V<sub>c c</sub>)、

接地電圧 (GND) は、

V<sub>G H</sub> > V<sub>c o m</sub> > V<sub>c c</sub> > GND > V<sub>G L</sub>、

の関係を満たすことを特徴とする請求項1 0または請求項1 1に記載の液晶表示装置。

#### 【請求項 1 3】

少なくとも V<sub>G H</sub> と V<sub>G L</sub> との電位差は 24V あることを特徴とする請求項1または請求項1 2に記載の液晶表示装置。

#### 【請求項 1 4】

前記複数の信号配線のうちの少なくとも一本は、ダミー配線であることを特徴とする請求項1ないし請求項1 3のいずれか 1 項に記載の液晶表示装置。

#### 【請求項 1 5】

前記複数の信号配線は、アルミニウム、クロム、若しくはモリブデンの少なくとも 1 つを有して構成されていることを特徴とする請求項1ないし請求項1 4のいずれか 1 項に記載の液晶表示装置。

#### 【請求項 1 6】

前記一対の基板は、ガラス基板であることを特徴とする請求項1ないし請求項7、請求項9、請求項1 4、請求項1 5のいずれか 1 項に記載の液晶表示装置。

#### 【発明の詳細な説明】

##### 【0 0 0 1】

##### 【発明の属する技術分野】

本発明は、液晶表示装置に係わり、特に、液晶表示パネル上に信号線を配置する際に有効な技術に関する。

##### 【0 0 0 2】

##### 【従来の技術】

S T N (Super Twisted Nematic) 方式、あるいは T F T (Thin Film Transistor) の液晶表示モジュールは、ノート型パソコン等の表示装置として広く使用されている。

これらの液晶表示装置は、液晶表示パネルと、液晶表示パネルを駆動する駆動回路 (ドレ

10

20

30

40

50

インドライバおよびゲートドライバ)、表示制御装置(または、タイミングコントローラ)、電源回路を備えている。

なお、このような液晶表示装置は、例えば、特願平9-71328号に記載されている。

#### 【0003】

##### 【発明が解決しようとする課題】

前述した液晶表示モジュールでは、ドレインドライバ、ゲートドライバから電源電圧、および信号(パルス状電圧)を夫々印加することにより、液晶表示パネル内の画素を選択的に駆動し、画像を表示する。

その際、一般的に、フレキシブルケーブルを用いて、タイミングコントロール基板とドレン基板、および、ドレン基板とゲート基板とを接続し、タイミングコントロール基板より出力される電源電圧、および信号を、それぞれドレン基板、ゲート基板に供給し、液晶表示パネル内の画素を駆動するようにしている。10

しかしながら、タイミングコントロール基板より出力される電源電圧、および駆動電圧を、それぞれドレインドライバ、ゲートドライバに供給する方式として、フレキシブルケーブルを使用しない、所謂、フレキシブルケーブルレス方式を採用するときなどは、タイミングコントロール基板より出力される電源電圧、および駆動電圧を伝送する信号線を、液晶表示パネルの一方のガラス基板上に設ける必要がある。

#### 【0004】

前述したような場合には、それぞれの信号線に供給される電源電圧、あるいは信号の電圧値が夫々異なるために、各信号線間にはその電位差に比例する電界が発生することになる。20

この電界強度が強いと、信号線を構成する金属材料が空気中の酸素などと反応を起こし酸化、電食するといった問題が生じてしまう。

このような問題を解決するために、従来は、(1)信号線の間隔をある程度あける、あるいは、(2)信号線を保護膜で覆い、空気にさらされないようにするなどの手法を採用していた。

しかしながら、前述の(1)の方法は、信号線を配線するためのスペースが大きくなり、液晶表示パネルの狭額縫化に対応できないという欠点があり、また、前述の(2)の方法は、保護膜は密度も低く、欠陥が生じた場合には部分的に信号線が大気にさらされてしまうことになるので、信号線間の電位差が大きく、かる、その間隔が小さい場合には、強電界が発生し大気に触れた場所に電食が生じてしまうという欠点があった。30

#### 【0005】

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、液晶表示装置において、液晶表示素子の一方の基板上に複数の信号線を配置する際に、信号線を配置するスペースを大きくすることなく、かつ、保護膜に欠陥が生じても信号線の酸化、電食を防止することが可能となる技術を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

#### 【0006】

##### 【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。40

即ち、本発明は、一対の基板と、当該一対の基板間に狭持される液晶とを有する液晶表示素子と、複数の駆動回路と、表示制御装置と、電源回路とを備える液晶表示装置であって、前記液晶表示素子は、前記一対の基板の中の一方の基板上に、前記電源回路からの電源電圧、および前記表示制御装置からの信号を前記複数の駆動回路に供給する複数の信号線を有し、前記複数の信号線の少なくとも一部は、互いに隣接する信号線との間の配線間隔が均一でなく、各信号線上の電圧から決定される互いに隣接する信号線との間の電位差に応じて可変されていることを特徴とする。

また、本発明の好ましい実施の形態では、前記複数の信号線の少なくとも一部は、前記互50

いに隣接する信号線との間の電位差が大きい程、前記互いに隣接する信号線との間の配線間隔が広くされていることを特徴とする。

#### 【0007】

また、本発明は、一対の基板と、当該一対の基板間に狭持される液晶とを有する液晶表示素子と、複数の駆動回路と、表示制御装置と、電源回路とを備える液晶表示装置であって、前記液晶表示素子は、前記一対の基板の中の一方の基板上に、前記電源回路からの電源電圧、および前記表示制御装置からの信号を前記複数の駆動回路に供給する複数の信号線を有し、前記複数の信号線の一部の信号線は、互いに隣接する信号線との間の配線間隔が、各信号線上の電圧から決定される互いに隣接する信号線との間の電界強度が電食が発生しない電界強度となる間隔で配置されていることを特徴とする。 10

#### 【0008】

また、本発明は、一対の基板と、当該一対の基板間に狭持される液晶とを有する液晶表示素子と、複数の駆動回路と、表示制御装置と、電源回路とを備える液晶表示装置であって、前記液晶表示素子は、前記一対の基板の中の一方の基板上に、前記電源回路からの電源電圧、および前記表示制御装置からの信号を前記複数の駆動回路に供給する複数の信号線を有し、前記複数の信号線の一部の信号線は、互いに隣接する信号線との間の配線間隔が、各信号線上の電圧から決定される互いに隣接する信号線との間の電界強度が略同一となる間隔で配置され、当該電界強度は、電食が発生しない電界強度であることを特徴とする。

。

#### 【0009】

また、本発明の好ましい実施の形態では、前記一部の信号線は、前記液晶を駆動する際の液晶駆動用基準電圧を供給する信号線を含み、前記液晶駆動用基準電圧を供給する信号線は、前記液晶側に最も近い位置に配置され、前記一部の信号線の中の残りの信号線は、信号線上の電圧値が最も高い信号線が、前記液晶駆動用基準電圧を供給する信号線から最も遠い位置に配置されるとともに、前記信号線上の電圧値が最も高い信号線を基準に、各信号線上の電圧から決定される前記互いに隣接する信号線との間の電位差が最も小さくなるように配置されることを特徴とする。 20

また、本発明の好ましい実施の形態では、前記一部の信号線は、表示制御装置から供給される、時間の経過とともに電圧レベルが変化するパルス状電圧の信号を供給する信号線を含み、前記パルス状電圧の信号を供給する信号線上の電圧は、前記パルス状電圧の時間平均の電圧値で規定することを特徴とする。 30

#### 【0010】

前記手段によれば、表示制御装置から各駆動回路（ドレインドライバまたはゲートドライバ）に対して、電源電圧、および信号を供給する信号線を、液晶表示素子の一方基板上に配置する際に、各信号線の間隔を、各信号線上の電圧で決定される隣接する信号線との間の電界強度が電食が発生しない電界強度となる間隔になるように、即ち、各信号線上の電圧で決定される互いに隣接する信号線との間の電位差が大きい場合には、信号線の間隔を大きく、また、各信号線上の電圧で決定される互いに隣接する信号線との間の電位差が小さい場合には、信号線の間隔を小さくしたので、信号線を配置するスペースを大きくすることなく、保護膜に欠陥が生じても信号線の酸化、電食を防止することが可能となる。 40

#### 【0011】

##### 【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

なお、実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

##### 【実施の形態1】

###### 【本発明が適用されるTFT方式の液晶表示モジュールの基本構成】

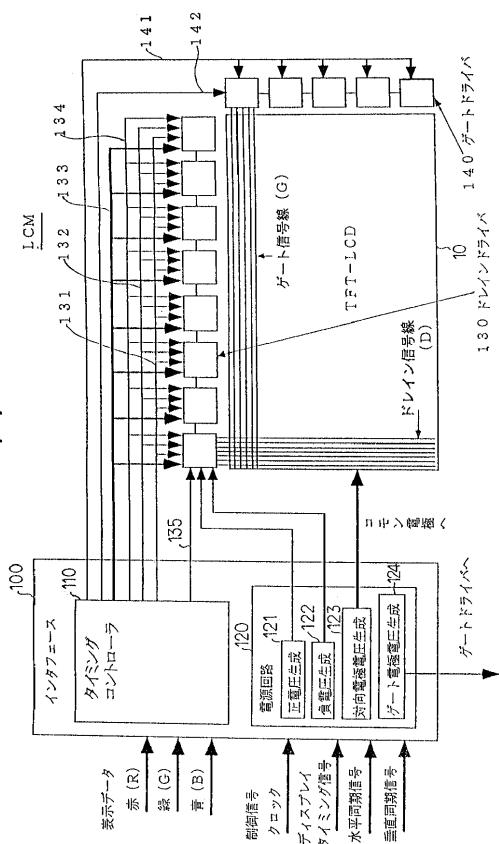

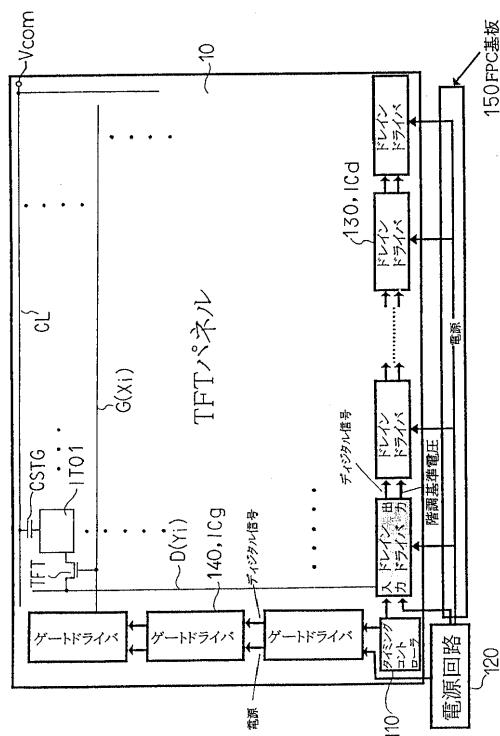

図4は、本発明が適用されるTFT方式の液晶表示モジュールの概略構成を示すブロック図である。

本実施の形態の液晶表示モジュール（LCM）は、液晶表示パネル（TFT-LCD）1 50

0の長辺側の一辺にドレインドライバ130が配置され、また、液晶表示パネル10の短辺側の一辺に、ゲートドライバ140が配置される。

液晶表示パネル10は、画素電極、薄膜トランジスタ等が形成されるTFT基板と、対向電極、カラーフィルタ等が形成されるフィルタ基板とを、所定の間隙を隔てて重ね合わせ、該両基板間の周縁部近傍に枠状に設けたシール材により、両基板を貼り合わせると共に、シール材の一部に設けた液晶封入口から両基板間のシール材の内側に液晶を封入、封止し、さらに、両基板の外側に偏光板を貼り付けて構成される。

#### 【0012】

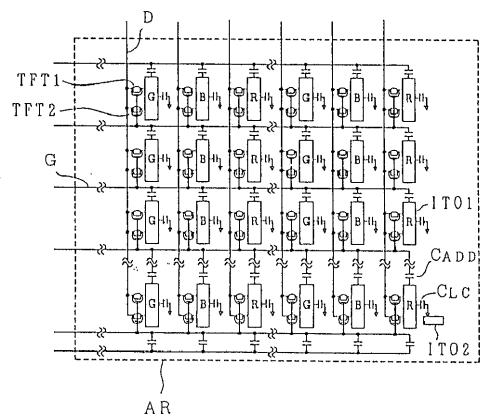

図5は、図4に示す液晶表示パネル10の一例の等価回路を示す図である。

同図に示すように、液晶表示パネル10は、マトリクス状に形成される複数の画素を有する。

10

各画素は、隣接する2本の信号線（ドレイン信号線（D）またはゲート信号線（G））と、隣接する2本の信号線（ゲート信号線（G）またはドレイン信号線（D））との交差領域内に配置される。

各画素は薄膜トランジスタ（TFT1, TFT2）を有し、各画素の薄膜トランジスタ（TFT1, TFT2）のソース電極は、画素電極（ITO1）に接続され、画素電極（ITO1）とコモン電極（または、対向電極）（ITO2）との間に液晶層が設けられるので、画素電極（ITO1）とコモン電極（ITO2）との間には、液晶容量（CLC）が等価的に接続される。

また、画素電極（ITO1）と前段のゲート信号線（G）との間には、附加容量（CADD）

20が接続される。

#### 【0013】

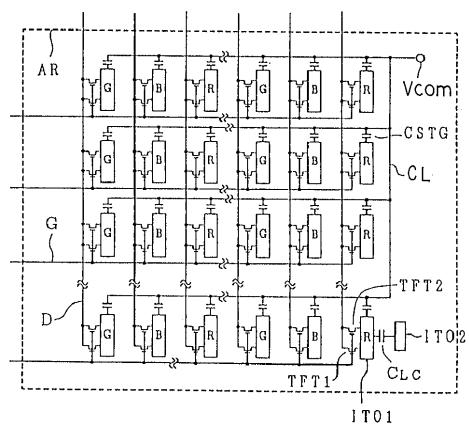

図6は、図4に示す液晶表示パネル10の他の例の等価回路を示す図である。

図5に示す例では、前段のゲート信号線（G）とソース電極との間に附加容量（CADD）が形成されているが、図6に示す例の等価回路では、コモン電極（ITO2）に供給されるVcomの電圧が印加される共通信号線（CL）と画素電極（ITO1）との間に保持容量（CSTG）が形成されている点が異なっている。

なお、図5、図6において、ARは表示領域である。

本発明は、どちらにも適用可能であるが、前者の方式では、前段のゲート信号線（G）パルスが附加容量（CADD）を介して画素電極に飛び込むのに対し、後者的方式では、飛び込みがないため、より良好な表示が可能となる。

30

また、図5、図6は、縦電界方式の液晶表示パネルの等価回路を示しており、さらに、図5、図6は回路図であるが、実際の幾何学的配置に対応して描かれている。

#### 【0014】

図5、図6に示す液晶表示パネル10において、列方向に配置された各画素の薄膜トランジスタ（TFT1, TFT2）のドレイン電極は、それぞれドレイン信号線（D）に接続され、各ドレイン信号線（D）は、列方向の各画素の液晶に階調電圧を印加するドレインドライバ130に接続される。

また、行方向に配置された各画素における薄膜トランジスタ（TFT1, TFT2）のゲート電極は、それぞれゲート信号線（G）に接続され、各ゲート信号線（G）は、1水平走査時間、行方向の各画素の薄膜トランジスタ（TFT1, TFT2）のゲート電極に走査駆動電圧（正のバイアス電圧あるいは負のバイアス電圧）を供給するゲートドライバ140に接続される。

40

#### 【0015】

図4に示すインタフェース部100は、タイミングコントローラ（本発明の表示制御装置）110と電源回路120とから構成される。

タイミングコントローラ110は、1個の半導体集積回路（LSI）から構成され、コンピュータ本体側から送信されてくるクロック信号（CK）、ディスプレイタイミング信号（DTMG）、水平同期信号（H Sync）、垂直同期信号（V Sync）の各表示制御信号および表示用データ（R・G・B）を基に、ドレインドライバ130、および、ゲー

50

トドライバ140を制御・駆動する。

タイミングコントローラ110は、ディスプレイタイミング信号が入力されると、これを表示開始位置と判断し、スタートパルス（表示データ取込開始信号）を信号線135を介して第1番目のドレインドライバ130に出力し、さらに、受け取った単純1列の表示データを、表示データのバスライン133を介してドレインドライバ130に出力する。

その際、タイミングコントローラ110は、ドレインドライバ130のデータラッチ回路に表示データをラッチするための表示制御信号である表示データラッチ用クロック信号（CL2）を信号線131を介して出力する。

本体コンピュータ側からの表示データは、例えば、6ビットあるいは8ビットで、1画素単位、即ち、赤（R）、緑（G）、青（B）の各データを1つの組にして単位時間毎に転送される。10

#### 【0016】

タイミングコントローラ110は、ディスプレイタイミング信号の入力が終了するか、または、ディスプレイタイミング信号が入力されてから所定の一定時間が過ぎると、1水平分の表示データが終了したものとして、ドレインドライバ130の内部のラッチ回路に蓄えていた表示データに基づく階調電圧を、液晶表示パネル10のドレン信号線（D）に出力するための表示制御信号である出力タイミング制御用クロック信号（CL1）を信号線132を介してドレインドライバ130に出力する。

また、タイミングコントローラ110は、垂直同期信号入力後に、第1番目のディスプレイタイミング信号が入力されると、これを第1番目の表示ラインと判断して信号線142を介してゲートドライバ140にフレーム開始指示信号（FLM）を出力する。20

さらに、タイミングコントローラ110は、水平同期信号に基づいて、1水平走査時間毎に、順次液晶表示パネル10の各ゲート信号線（G）に正のバイアス電圧を印加するよう、信号線142を介してゲートドライバ140へ1水平走査時間周期のシフトクロック信号（CL3）を出力する。

これにより、液晶表示パネル10の各ゲート信号線（G）に接続された複数の薄膜トランジスタ（TFT1, TFT2）が、1水平走査時間の間導通し、1表示ラインの画素に階調電圧が書き込まれる。

以上の動作により、液晶表示パネル10に画像が表示される。

#### 【0017】

図4に示す電源回路120は、正電圧生成回路121、負電圧生成回路122、コモン電極（対向電極）電圧生成回路123、ゲート電極電圧生成回路124から構成される。

正電圧生成回路121、負電圧生成回路122は、それぞれ直列抵抗分圧回路で構成され、正電圧生成回路121は、例えば、正極性の5値の階調基準電圧（V"0～V"4）を、負電圧生成回路122は、例えば、負極性の5値の階調基準電圧（V"5～V"9）を出力する。

この正極性の階調基準電圧（例えば、V"0～V"4）、および負極性の階調基準電圧（例えば、V"5～V"9）は、各ドレインドライバ130に供給される。

また、各ドレインドライバ130には、信号線134を介して、タイミングコントローラ110からの交流化信号（交流化タイミング信号；M）も供給される。30

コモン電極電圧生成回路123はコモン電極（ITO2）に印加する駆動電圧を、ゲート電極電圧生成回路124は薄膜トランジスタ（TFT1, TFT2）のゲート電極に印加する駆動電圧（正のバイアス電圧および負のバイアス電圧）を生成する。40

#### 【0018】

##### [本発明の実施の形態1の液晶表示モジュールの構成]

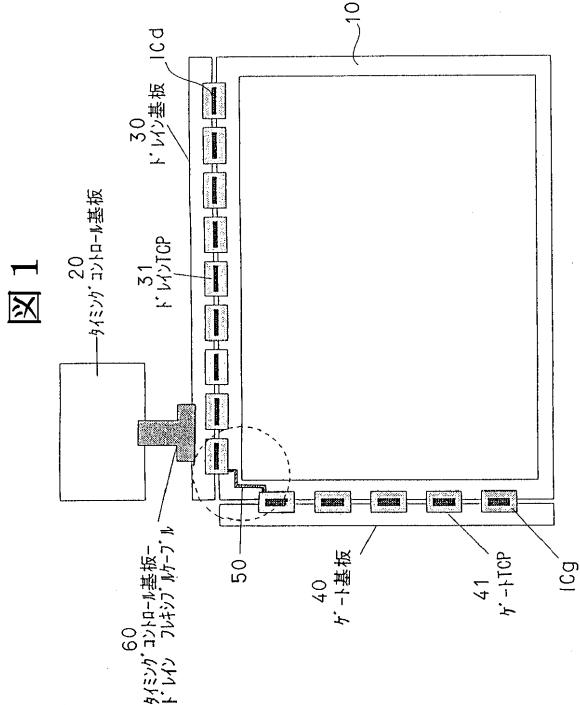

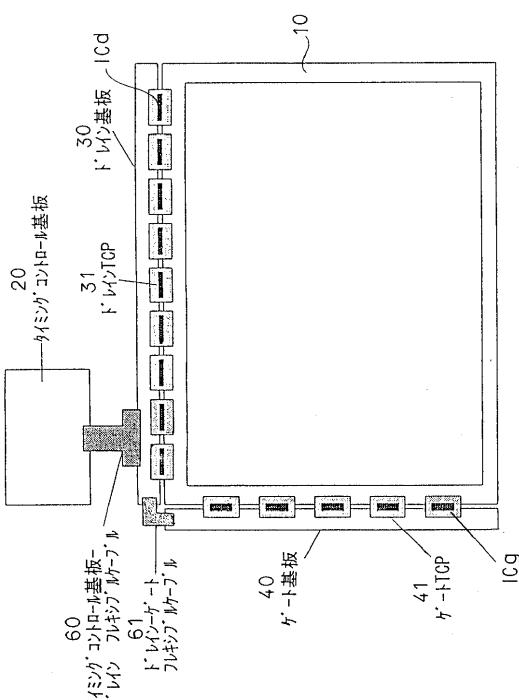

図1は、本発明の実施の形態1の液晶表示モジュールにおける、液晶表示パネル10の周囲にドレインドライバ130およびゲートドライバ140を配置した状態を示す図である。

図1において、31は、液晶表示パネル10の一方のガラス基板（TFT基板側のガラス基板）と、ドレイン基板30との間に実装されるドレイン側TCP（Tape Carrier Packa50

ge)、41は、液晶表示パネル10の一方のガラス基板と、ゲート基板40との間に実装されるゲート側TCPである。

ドレイン側TCP(31)には、ドレインドライバ130を構成する半導体チップ(ICd)が、ゲート側TCP(41)には、ゲートドライバ140を構成する半導体チップ(ICg)が搭載されている。

また、タイミングコントロール基板20には、タイミングコントローラ110および電源回路120が搭載されている。

#### 【0019】

##### [従来の液晶表示モジュールの構成]

図8は、従来の液晶表示モジュールにおける、液晶表示パネル10の周囲にドレインドライバ130およびゲートドライバ140を配置した状態を示す図である。 10

図8に示すように、従来の液晶表示モジュールでは、タイミングコントロール基板20からドレイン基板30に対して出力される電源電圧、および信号は、フレキシブルケーブル60を介してドレイン基板30に送出される。

また、タイミングコントロール基板20からゲート基板40に対して出力される電源電圧、および信号は、フレキシブルケーブル60 ドレイン基板30 フレキシブルケーブル61 ゲート基板40を介して、ゲート基板40に送出される。

#### 【0020】

##### [本発明の実施の形態の液晶表示モジュールの特徴]

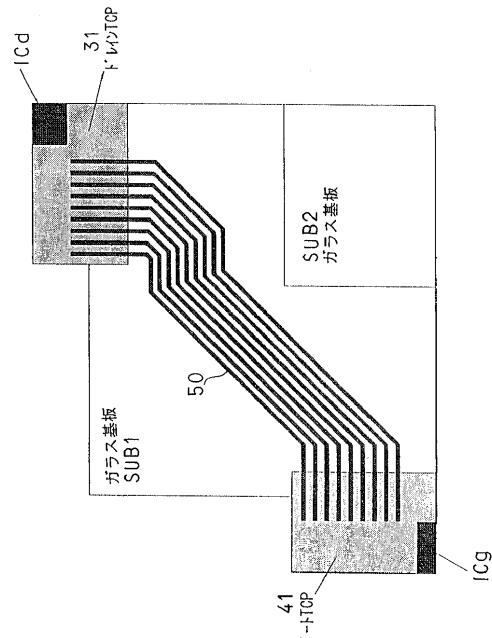

図2は、図1中の点線の円の部分を拡大して示す図である。 20

なお、図2において、SUB1は、TFT基板側のガラス基板、SUB2は、フィルタ基板側のガラス基板である。

本実施の形態では、タイミングコントロール基板20からゲート基板40に送出される電源電圧、および信号は、ドレイン基板30 第1番目のドレイン側TCP(31) ガラス基板(SUB1)上の信号線50 第1番目のゲート側TCP(41) ゲート基板40の順に転送される。

ここで、タイミングコントロール基板20からゲート基板40に送出される電源電圧は、Vcom、VGH、VGL、VccおよびGNDの5種類であり、信号は、クロック(CL3)、FLM(フレーム開始指示信号)、およびOE(アウトプットイネーブル信号)の3種類である。 30

なお、これらの信号線50は、Al(アルミニウム)、Cr(クロム)、あるいはモリブデン(Mo)等で形成され、通常、保護膜などで覆われ、大気と接触しないようにされている。

また、図2中には、信号線は9本図示されているが、1本はダミーの信号線である。

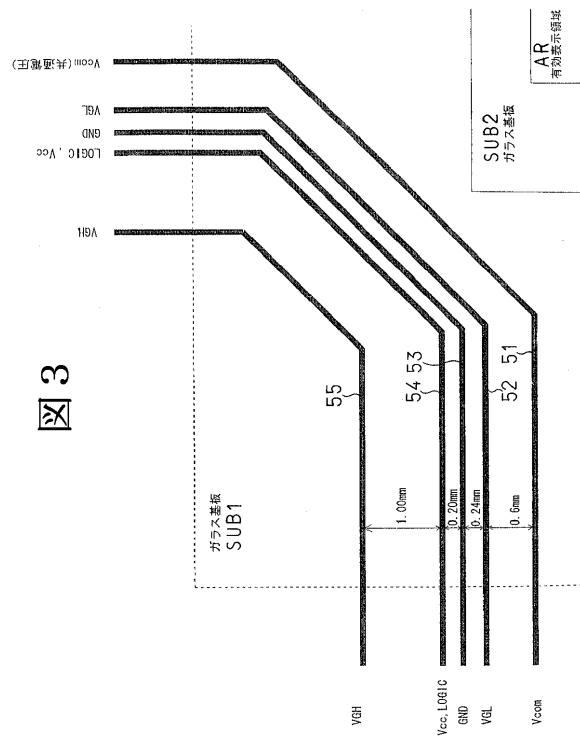

次に、本実施の形態の特徴とする信号線の配線間隔について、図3を用いて説明する。

なお、この図3では、主に、電源電圧(Vcom, VGH, VGL, Vcc, GND)について説明する。

また、これらの電源電圧の電圧値を表1に示す。

#### 【0021】

##### 【表1】

| 電源電圧名 | 信号電圧 (V) | 電位差 (V) | 配線間隔 (mm) |

|-------|----------|---------|-----------|

| V com | 6        | 10      | 0. 60     |

| V GL  | -4       | 4       | 0. 24     |

| GND   | 0        | 3. 3    | 0. 20     |

| V cc  | 3. 3     | 16. 7   | 1. 00     |

| V GH  | 20       |         |           |

10

## 【0022】

なお、V comは、コモン電極（ITO2）に印加する電圧、V GHは、薄膜トランジスタ（TFT1, TFT2）をオンとする電圧、V GLは、薄膜トランジスタ（TFT1, TFT2）をオフとする電圧、V ccは、ゲートドライバ140を構成する半導体チップ内部の論理回路用の電源電圧、GND（またはV ssともいう）は、接地電圧である。

図3に示すように、V comの電圧は、コモン電極（ITO2）に印加する電圧であり、液晶パネル10内部に供給する必要があるため、V comを供給する信号線51は、液晶パネル10の一番内側（有効表示領域ARに一番近い領域）に配置する。

それ以外の信号線（52～55）は、表1に示すように、互いに隣接する信号線との間の電位差が最も小さくなるように配置する。

20

本実施の形態では、図3に示すように、V comを供給する信号線51 V GLを供給する信号線52 GNDを供給する信号線53 V ccを供給する信号線54 V GHを供給する信号線55の順となる。

## 【0023】

そして、本実施の形態では、互いに隣接する信号線間の電位差が最も大きい信号線の間隔（本実施の形態では、V ccを供給する信号線54とV GHを供給する信号線55との間の間隔）を電食が発生しない、電界強度となるように決定する。

本実施の形態では、表1に示すように、このV ccを供給する信号線54とV GHを供給する信号線55との間の間隔1.0mmとした。

したがって、電界強度は、16.7（=16.7/1.0）（V/mm）となる。

30

そして、残りの信号線の間の配線間隔を、前述した電界強度と略等しくなるように決定する。

したがって、本実施の形態では、表1に示すように、V ccを供給する信号線54とGNDを供給する信号線53との間の配線間隔は0.2mm、GNDを供給する信号線53とV GLを供給する信号線52との間の配線間隔は0.24mm、V GLを供給する信号線52とV comを供給する信号線52との間の配線間隔は0.6mmとなる。

## 【0024】

このように、信号線（51ないし55）の配線間隔を決定することにより、電食が発生せず、また他の配置に比べて、最も少ないスペースで配線を配置することが可能となる。

なお、前述の説明では、電食が発生しない電界強度が、16.7（V/mm）である場合について説明したが、この電食が発生しない電界強度は、信号線の材料、保護膜の容量などにより、液晶表示パネル毎に異なるので、各液晶表示パネル毎に電食が発生しない電界強度として最適な電界強度を設定する必要がある。また、前述の説明では、電源電圧（V com, V GH, V GL, V cc, GND）を供給する信号線の配線間隔について説明したが、信号（クロック（CL3）、FLM（フレーム開始指示信号）、OE（アウトプットイネーブル信号））を供給する信号線との間の配線間隔も同様にして決定することができる。

40

但し、これらの信号は、時間の経過とともに電圧値が変化する電圧（所謂、パルス状電圧）であるので、この場合の電圧値は、時間平均をとって規定する必要がある。

## 【0025】

50

**[実施の形態 2]****[本発明の実施の形態の液晶表示モジュールの構成]**

図7は、本発明の実施の形態2の液晶表示モジュールにおける、液晶表示パネル10の周囲にドレインドライバ130およびゲートドライバ140を配置した状態を示す図である。

本実施の形態の液晶表示モジュールでは、タイミングコントローラ110、ドレインドライバ130を構成する半導体チップICd、ゲートドライバ140を構成する半導体チップICgが、液晶表示パネル10のTFT基板側のガラス基板(SUB1)上に実装される。

そして、タイミングコントロール110から、ゲートドライバ140を構成する半導体チップICgに供給される信号、および電源回路120からゲートドライバ140を構成する半導体チップICgに供給される電源電圧は、液晶表示パネル10のTFT基板側のガラス基板(SUB1)上に形成された信号線を介して、ゲートドライバ140を構成する各半導体チップICgに供給される。

10

ここで、電源回路120は、液晶表示パネル10の外部に設置される。

**【0026】**

また、タイミングコントロール110から、ドレインドライバ130を構成する半導体チップICdに供給される信号、および電源回路120からドレインドライバ130を構成する半導体チップICdに供給される階調基準電圧は、液晶表示パネル10のTFT基板側のガラス基板(SUB1)上に形成された信号線を介して、各ドレインドライバ130を構成する半導体チップICdに供給される。

20

但し、ドレインドライバ130を構成する半導体チップ内部の論理回路用の電源電圧は、電源回路120 フレキシブルプリント基板150を介して、各ドレインドライバ130に供給される。

本実施の形態においても、液晶表示パネル10のTFT基板側のガラス基板(SUB1)上に形成される信号線の配線間隔を、前述したような配線間隔とすることにより、信号線を配置するスペースを大きくすることなく、保護膜に欠陥が生じても信号線の酸化、電食を防止することが可能となる。

**【0027】**

なお、本実施の形態において、ドレインドライバ130を構成する半導体チップ内の論理回路用の電源電圧を、液晶表示パネル10のTFT基板側のガラス基板(SUB1)上に形成した信号線を介して、各ドレインドライバ130に供給するようにしてもよい。

30

この場合にも、前述したような配線間隔とすることにより、信号線を配置するスペースを大きくすることなく、保護膜に欠陥が生じても信号線の酸化、電食を防止することが可能となる。

また、前記各実施の形態では、本発明を縦電界方式の液晶表示パネルに適用した場合について説明したが、これに限定されるものではなく、横電界方式の液晶表示パネルにも適用可能である。

また、前記各実施の形態では、本発明をTFT方式の液晶表示装置に適用した場合について説明したが、これに限定されるものではなく、本発明は、STN方式の単純マトリクス形液晶表示装置にも適用可能であることは言うまでもない。

40

以上、本発明者によってなされた発明を、前記発明の実施の形態に基づき具体的に説明したが、本発明は、前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

**【0028】****【発明の効果】**

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記のとおりである。

本発明の液晶表示装置によれば、電源電圧、および信号を供給する信号線を、液晶表示素子の一方の基板上に配置する際に、信号線を配置するスペースを大きくすることなく、保

50

護膜に欠陥が生じても信号線の酸化、電食を防止することが可能となる。

【図面の簡単な説明】

【図1】本発明の実施の形態1の液晶表示モジュールにおける、液晶表示パネルの周囲にドレインドライバおよびゲートドライバを配置した状態を示す図である。

【図2】図1中の点線の円の部分を拡大して示す図である。

【図3】本発明の実施の形態1における、信号線の配線間隔を説明するための図である。

【図4】本発明が適用されるTFT方式の液晶表示モジュールの概略構成を示すブロック図である。

【図5】図4に示す液晶表示パネルの一例の等価回路を示す図である。

【図6】図4に示す液晶表示パネルの他の例の等価回路を示す図である。

【図7】本発明の実施の形態2の液晶表示モジュールにおける、液晶表示パネルの周囲にドレインドライバおよびゲートドライバを配置した状態を示す図である。

【図8】従来の液晶表示モジュールにおける、液晶表示パネルの周囲にドレインドライバおよびゲートドライバを配置した状態を示す図である。

【符号の説明】

10 ... 液晶表示パネル、 20 ... タイミングコントロール基板、 30 ... ドレイン基板、 31 , 41 ... T C P、 40 ... ゲート基板、 50 , 51 ~ 55 , 131 , 132 , 134 , 135 , 141 , 142 ... 信号線、 60 , 61 ... フレキシブルケーブル、 100 ... インタフェース部、 110 ... タイミングコントローラ、 120 ... 電源回路、 121 ... 正電圧生成回路、 122 ... 負電圧生成回路、 123 ... コモン電極（対向電極）電圧生成回路、 124 ... ゲート電極電圧生成回路、 130 ... ドレインドライバ、 133 ... 表示データのバスライン、 140 ... ゲートドライバ、 150 ... フレキシブルプリント配線基板、 A R ... 表示領域、 I TO 1 ... 画素電極、 I TO 2 ... コモン電極、 D ... ドレイン信号線、 G ... ゲート信号線、 TFT 1 , TFT 2 ... 薄膜トランジスタ、 CLC ... 液晶容量、 C ADD ... 付加容量、 CSTG ... 保持容量、 CL ... 共通信号線、 ICd , ICg ... 半導体チップ、 SUB 1 , SUB 2 ... ガラス基板。

10

20

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【 四 5 】

【 6 】

図 5

四 6

【 四 7 】

【図8】

7

8

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 670 J

(72)発明者 鈴木 伸之

千葉県茂原市早野3300番地 株式会社日立製作所 ディスプレイグループ内

(72)発明者 森下 俊輔

千葉県茂原市早野3300番地 株式会社日立製作所 ディスプレイグループ内

(72)発明者 中山 貴徳

千葉県茂原市早野3300番地 株式会社日立製作所 ディスプレイグループ内

審査官 鈴木 俊光

(56)参考文献 特開平11-281994(JP,A)

特開平11-142871(JP,A)

特開平08-122746(JP,A)

特開平09-026593(JP,A)

特開2000-162635(JP,A)

特開平05-143021(JP,A)

特開平10-293286(JP,A)

特開平07-270825(JP,A)

特開平08-234220(JP,A)

特開平09-127540(JP,A)

特開平10-010564(JP,A)

特開平11-065472(JP,A)

特開平07-023104(JP,A)

特開平11-054761(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1345

G02F 1/133