(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7118902号**

**(P7118902)**

(45)発行日 令和4年8月16日(2022.8.16)

(24)登録日 令和4年8月5日(2022.8.5)

(51)国際特許分類

|         |                |         |             |

|---------|----------------|---------|-------------|

| H 0 3 M | 3/02 (2006.01) | H 0 3 M | 3/02        |

| G 0 6 F | 3/041(2006.01) | G 0 6 F | 3/041 5 2 2 |

F I

請求項の数 20 (全24頁)

(21)出願番号 特願2018-567127(P2018-567127)

(86)(22)出願日 平成29年5月8日(2017.5.8)

(65)公表番号 特表2019-531612(P2019-531612

A)

(43)公表日 令和1年10月31日(2019.10.31)

(86)国際出願番号 PCT/US2017/031510

(87)国際公開番号 WO2018/004826

(87)国際公開日 平成30年1月4日(2018.1.4)

審査請求日 令和2年4月7日(2020.4.7)

(31)優先権主張番号 15/199,276

(32)優先日 平成28年6月30日(2016.6.30)

(33)優先権主張国・地域又は機関

米国(US)

前置審査

(73)特許権者 502161508

シナティクス インコーポレイテッド

アメリカ合衆国, 95131 カリフォルニア州, サンノゼ, マッケイ ドラ

イブ 1109

(74)代理人 100205350

弁理士 狩野 芳正

(74)代理人 100117617

弁理士 中尾 圭策

(72)発明者 ボハンノン, エリック スコット

アメリカ合衆国, カリフォルニア州,

サンノゼ, マッケイ ドライヴ 1251

ベル, ジュニア マーシャル ジェイ

アメリカ合衆国, カリフォルニア州,

サンノゼ, マッケイ ドライヴ 1251

最終頁に続く

(54)【発明の名称】 デルタシグマ変調器を備えた入力装置レシーバ

**(57)【特許請求の範囲】****【請求項1】**

複数のセンサ電極を備えた入力装置のための処理システムであって、

前記複数のセンサ電極のうちの第1のセンサ電極からセンサ信号を受信し、前記センサ

信号のミラー電流を出力するように構成された電流コンペアと、

前記ミラー電流をダウンコンバートして、処理された信号を出力するように構成された

混合器と、

デルタシグマ変調器であり、

正入力ノードと、負入力ノードと、を含む、前記処理された信号を受信するように構成さ

れた少なくとも2つの入力ノードと、

前記正入力ノード及び前記負入力ノードと結合され、積分信号を生成するように構成さ

れた積分器と、

前記積分器の出力と結合され、前記積分信号を量子化して、出力値と前記出力値の反

転値を出力するように構成された量子化器と、

前記量子化器から受信した前記出力値及び前記反転値に基づいて制御されたフィード

バックデジタルアナログ変換器(DAC)と、

を備えるデルタシグマ変調器と、

前記デルタシグマ変調器の出力と結合され、前記量子化器の量子化ノイズを低減するよ

うに構成されたデジタルフィルタと、

を備え、

前記積分器は、受動積分器であり、

前記フィードバック D A C が、

第 1 電流源と、

第 2 電流源と、

前記第 1 電流源を、前記出力値に基づいて、前記正入力ノード又は前記負入力ノードに選択的に結合するように構成された第 1 スイッチと、

前記第 2 電流源を、前記反転値に基づいて、前記正入力ノード又は前記負入力ノードに選択的に結合するように構成された第 2 スイッチと、

を備える、

処理システム。

10

【請求項 2】

前記デルタシグマ変調器が、更に、前記正入力ノード及び負入力ノードと結合され、前記電流コンペアによって生成されたコモンモード電流を低減するように構成されたコモンモードフィードバック回路を備える、請求項 1 に記載の処理システム。

【請求項 3】

前記電流コンペアがシングルエンド入力を有し、前記正入力ノード及び前記負入力ノードが完全差動入力である、請求項 1 に記載の処理システム。

【請求項 4】

前記デルタシグマ変調器が、連続時間変調器であり、前記デジタルフィルタが低域フィルタであり、前記量子化器がシングルビット量子化器である、請求項 1 に記載の処理システム。

20

【請求項 5】

前記受動積分器が、2 以上のキャパシタンスを含む、請求項 1 に記載の処理システム。

【請求項 6】

前記受動積分器が、前記第 1 のセンサ電極のキャパシタンスを含む、請求項 1 に記載の処理システム。

【請求項 7】

複数のセンサ電極と、

前記複数のセンサ電極と結合された処理システムと、を備え、

前記処理システムは、

前記複数のセンサ電極のうちの第 1 のセンサ電極からセンサ信号を受信し、前記センサ信号のミラー電流を出力するように構成された電流コンペアと、

30

前記ミラー電流をダウンコンバートして、処理された信号を出力するように構成された混合器と、

デルタシグマ変調器であり、

正入力ノードと、負入力ノードと、を含む、前記処理された信号を受信するように構成された少なくとも 2 つの入力ノードと、

前記正入力ノード及び前記負入力ノードと結合され、積分信号を生成するように構成された積分器と、

前記積分器の出力と結合され、前記積分信号を量子化して、出力値と前記出力値の反転値を出力するように構成された量子化器と、

40

前記量子化器から受信した前記出力値及び前記反転値に基づいて制御されたフィードバックデジタルアナログ変換器 (D A C) と、

を備えるデルタシグマ変調器と、

前記デルタシグマ変調器の出力と結合され、前記量子化器の量子化ノイズを低減するように構成されたデジタルフィルタと、

を備え、

前記積分器は、受動積分器であり、

前記フィードバック D A C が、

第 1 電流源と、

50

第 2 電流源と、

前記第 1 電流源を、前記出力値に基づいて、前記正入力ノード又は前記負入力ノードに選択的に結合するように構成された第 1 スイッチと、

前記第 2 電流源を、前記反転値に基づいて、前記正入力ノード又は前記負入力ノードに選択的に結合するように構成された第 2 スイッチと、

を備える、

入力装置。

**【請求項 8】**

前記デルタシグマ変調器が、更に、前記正入力ノード及び前記負入力ノードと結合され、前記電流コンベアによって生成されたコモンモード電流を低減するように構成されたコモンモードフィードバック回路を備える、請求項 7 に記載の入力装置。 10

**【請求項 9】**

前記電流コンベアがシングルエンド入力を有し、前記正入力ノード及び前記負入力ノードが完全差動入力である、請求項 7 に記載の入力装置。

**【請求項 10】**

前記デルタシグマ変調器が、連続時間変調器であり、前記デジタルフィルタが低域フィルタであり、前記量子化器がシングルビット量子化器である、請求項 7 に記載の入力装置。 20

**【請求項 11】**

前記受動積分器が、2 以上のキャパシタンスを含む、請求項 7 に記載の入力装置。

**【請求項 12】**

前記受動積分器が、前記第 1 のセンサ電極のキャパシタンスを含む、請求項 7 に記載の入力装置。 20

**【請求項 13】**

電流コンベアを使用して、複数のセンサ電極のうちの第 1 のセンサ電極から受信したセンサ信号をミラーリングするステップと、

混合器を使用して、前記センサ信号のミラー電流をダウンコンバートすることにより処理された信号を生成するステップと、

前記処理された信号に基づく信号を積分して、積分信号を生成するステップと、

前記積分信号を量子化して、出力値と前記出力値の反転値を出力するステップと、

量子化された前記積分信号に基づいて、正入力ノードと、負入力ノードと、を含む少なくとも 2 つ入力ノードと結合された、第 1 電流源と第 2 電流源を備えるフィードバックデジタルアナログ変換器 (D A C) を制御するステップと、 30

前記第 1 電流源を、前記出力値に基づいて、前記正入力ノード又は前記負入力ノードに選択的に結合するステップと、

前記第 2 電流源を、前記反転値に基づいて、前記正入力ノード又は前記負入力ノードに選択的に結合するステップと、

デジタルフィルタを使用して、量子化ノイズを低減するステップと、を含み、

前記信号を積分するステップが受動積分器によって実行される、

方法。

**【請求項 14】**

前記正入力ノード及び前記負入力ノードと結合されたコモンモードフィードバック回路を使用して、前記電流コンベアによって生成されたコモンモード電流を低減するステップを更に含む、請求項 13 に記載の方法。 40

**【請求項 15】**

前記電流コンベアがシングルエンド入力を有し、前記正入力ノード及び前記負入力ノードが完全差動入力である、請求項 13 に記載の方法。

**【請求項 16】**

前記センサ信号を受信し、前記信号を積分し、前記積分信号を量子化し、前記フィードバック D A C を制御することが、量子化器を備えるデルタシグマ変調器によって実行され、前記デルタシグマ変調器が、連続時間変調器であり、前記デジタルフィルタが低域フィ 50

ルタであり、前記量子化器がシングルビット量子化器である、

請求項 1 3 に記載の方法。

**【請求項 1 7】**

前記受動積分器が、2 以上のキャパシタンスを含む、請求項 1 3 に記載の方法。

**【請求項 1 8】**

前記電流コンベアによって出力される前記ミラー電流が、1 でない値の係数 A でスケールされている、請求項 1 に記載の処理システム。

**【請求項 1 9】**

前記混合器は、前記ミラー電流を実質的に直流電流 (DC) レベルにダウンコンバートする、請求項 1 に記載の処理システム。

10

**【請求項 2 0】**

前記混合器が、矩形波混合器と、高調波拒絶混合器と、正弦波混合器と、のうち一つを含む、請求項 1 に記載の処理システム。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明の実施形態は、一般に、一体型検出装置を備えた表示装置を有する入力装置を作動させるための技術に関する。

**【背景技術】**

**【0 0 0 2】**

20

近接センサデバイス(一般に、タッチパッド又はタッチセンサデバイスとも呼ばれる)を含む入力装置は、様々な電子システムに広く使用されている。近接センサデバイスは、典型的には、しばしば面によって区分された検出領域を有し、検出領域内で、近接センサデバイスが1つ以上の入力オブジェクトの存在、位置及び/又は動きを決定する。近接センサデバイスは、電子システムのインターフェースを提供するために使用されうる。例えば、近接センサデバイスは、より大きい計算処理システムの入力装置(ノートブック又はデスクトップコンピュータに組み込まれるかその周辺装置の不透明タッチパッドなど)としてしばしば使用される。近接センサデバイスは、しばしばより小さい計算処理システム(携帯電話に組み込まれたタッチスクリーンなど)にも使用される。

**【発明の概要】**

30

**【0 0 0 3】**

本明細書で述べる一実施形態は、複数のセンサ電極を含む入力装置のための処理システムである。処理システムは、複数のセンサ電極のうちの少なくとも第1のセンサ電極から受け取ったセンサ信号に基づいて信号を受け取るように構成された1つ以上の入力ノードと、1つ以上の入力ノードと結合され、積分信号を生成するように構成された積分器とを含むデルタシグマ変調器を含む。デルタシグマ変調器は、更に、積分器の出力と結合され、積分信号を量子化するように構成された量子化器と、量子化器に基づいて制御されたフィードバックデジタルアナログ変換器(DAC)とを含む。処理システムは、更に、デルタシグマ変調器の出力と結合され、量子化器の量子化ノイズを低減するように構成されたデジタルフィルタを含む。

40

**【0 0 0 4】**

本明細書で述べる別の実施形態は、複数のセンサ電極と、複数のセンサ電極と結合された処理システムとを含む入力装置である。処理システムは、複数のセンサ電極のうちの第1のセンサ電極から受け取ったセンサ信号に基づく信号を受け取るように構成された1つ以上の入力ノードを含むデルタシグマ変調器を含む。デルタシグマ変調器は、更に、1つ以上の入力ノードと結合され、積分信号を生成するように構成された積分器と、積分器の出力と結合され、積分信号を量子化するように構成された量子化器と、量子化器に基づいて制御されたフィードバックデジタルアナログ変換器(DAC)とを含む。処理システムは、更に、デルタシグマ変調器の出力と結合され、量子化器の量子化ノイズを低減するように構成されたデジタルフィルタを含む。

50

**【 0 0 0 5 】**

本明細書で述べる別の実施形態は、1つ以上の入力ノードに、複数のセンサ電極のうちの第1のセンサ電極からセンサ信号を受け取ることを含む方法である。この方法は、更に、センサ信号に基づいて信号を積分して積分信号を生成することと、積分信号を量子化することを含む。方法は、更に、積分信号の量子化に基づいてフィードバックデジタルアナログ変換器（D A C）を制御することを含み、フィードバックD A Cが、1つ以上の入力ノードと結合される。方法は、更に、デジタルフィルタを使用して量子化ノイズを低減することを含む。

**【 0 0 0 6 】**

本開示の上記の特徴を詳細に理解できるように、以上に簡潔に要約された本開示のより詳細な記述が実施形態を参照して行われることがあり、その実施形態の幾つかが添付図面に示される。しかしながら、添付図面が、単に典型的な実施形態を示し、したがって、その範囲の限定と見なされるべきでなく、他の等しく有効な実施形態を許容できることに注意されたい。

10

**【図面の簡単な説明】****【 0 0 0 7 】**

【図1】一実施形態による入力装置の概略ブロック図である。

【図2】一実施形態による典型的なセンサ電極機構の一部分を示す図である。

【図3】一実施形態による典型的なセンサ電極機構の一部分を示す図である。

【図4】一実施形態による、典型的入力装置のブロック図を示す。

20

【図5】一実施形態による、典型的入力装置の概略ブロック図である。

【図6】一実施形態による、センサ電極から受け取った信号を処理する典型的方法を示す図である。

**【発明を実施するための形態】****【 0 0 0 8 】**

理解を容易にするため、可能な場合は、図に共通の同一要素を示すために同一参照数字を使用した。一実施形態で開示された要素が、特定の記述なしに他の実施形態で有益に利用されうる。本明細書で参照される図面は、特に断らない限り一定の縮尺で描かれないことを理解されたい。また、図面は、提示と説明を明瞭にするために、しばしば単純化され、詳細又は構成要素が省略される。図面と検討は、後述される原理を説明する役割をし、同じ名称は同じ要素を示す。

30

**【 0 0 0 9 】**

以下の詳細な説明は、単に本質的に例示であり、本開示又は本開示の用途及び使用法を限定するものではない。更に、前述の背景、概要又は以下の詳細な説明に示された如何なる明示又は暗示された理論によっても拘束されるものではない。

**【 0 0 1 0 】**

入力装置がますます複雑になっており、含むセンサ電極の数も増えているため、処理システムに対する処理要求も同様に高まっている。センサ電極から受け取った入力信号を他のシステム制約条件内で適切に処理するために、処理システムは、(1)センサ電極用の付加処理回路のための領域の拡大、(2)所定の領域のための処理回路の縮小、及び(3)受け取った入力信号を処理するための時間の拡大、のうちの少なくとも1つを必要とする傾向がある。しかしながら、入力装置機能が、同じ(又は、より小さい)パッケージング内で高まり続けているので、処理回路に割り当てられた領域を大きくできない場合がある。更に、付加処理回路により多くの領域を提供することは、製造コストを高めうる。更に、一体型表示装置を備えた入力装置の場合、解像度が高い表示装置ほど表示更新に必要な時間が多くなる傾向がある。その結果、場合によっては、センサ電極から受け取った入力信号の処理により多くの時間を割り当てることができない。

40

**【 0 0 1 1 】**

本明細書で述べる実施形態は、一般に、センサ電極から受け取った信号を処理する処理システム及び関連入力装置、並びに方法を含む。より具体的には、処理システムは、積分

50

器、量子化器、フィードバックデジタルアナログ変換器（D A C）、及びコモンモードフィードバック機構を含むデルタシグマ変調器を含む。幾つかの実施形態では、デルタシグマ変調器は、処理システムのアナログフロントエンド（A F E）又は他のレシーバ回路内に含まれる。幾つかの実施形態では、デルタシグマ変調器は、差動一次連続時間受動デルタシグマ変調器を含む。集合的に、デルタシグマ変調器の構成要素は、従来のA F Eよりかなり小さいサイズのA F Eになる。

#### 【0012】

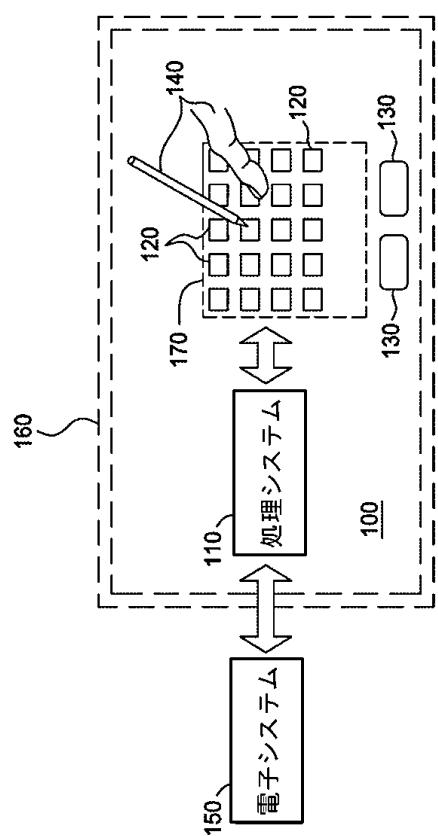

##### 典型的な入力装置の実施態様

図1は、本技術の実施形態による入力装置100の概略ブロック図である。様々な実施形態では、入力装置100は、検出装置と一体化された表示装置を含む。入力装置100は、電子システム150に入力を提供するように構成されうる。本明細書で使用されるとき、用語「電子システム」（又は「電子装置」）は、広義には、情報を電子的に処理できる任意のシステムを指す。電子システムの幾つかの非限定的な例には、デスクトップコンピュータ、ラップトップコンピュータ、ネットブックコンピュータ、タブレット、ウェブブラウザ、電子ブックリーダ及び携帯情報端末（PDA）などの全てのサイズ及び形状のパーソナルコンピュータが含まれる。追加の例示的な電子システムには、入力装置100と、別個のジョイスティック又はキースイッチとを含む物理キー・ボードなどの複合入力装置が含まれる。更に例示的な電子システムには、データ入力装置（リモートコントロールとマウスを含む）やデータ出力装置（表示画面とプリンタを含む）などの周辺装置が含まれる。他の例には、リモート端末、キオスク及びビデオゲーム機（例えば、ビデオゲーム機、携帯ゲーム装置など）が含まれる。他の例には、通信装置（スマートフォンなどの携帯電話を含む）、及びメディア装置（レコーダ、エディタ、並びにテレビ、セットトップボックス、音楽プレーヤ、デジタルフォトフレーム及びデジタルカメラなどのプレーヤを含む）が含まれる。更に、電子システムは、入力装置に対してホストでもスレーブでもよい。

10

#### 【0013】

入力装置100は、電子システムの物理部分として実現されてもよく、電子システムと物理的に別個でもよい。必要に応じて、入力装置100は、バス、ネットワーク、及び他の有線又は無線相互接続のいずれか1つ以上を使用して、電子システムの一部と通信できる。例には、I 2 C、S P I、P S / 2、ユニバーサルシリアルバス（U S B）、B l u e t o o t h、R F 及びI R D Aが含まれる。

20

#### 【0014】

図1では、入力装置100は、検出領域170内の1つ以上の入力オブジェクト140によって提供された入力を検出するように構成された近接センサデバイス（例えば、しばしば「タッチパッド」又は「タッチセンサデバイス」とも呼ばれる）として示される。図1に示されたように、例示的な入力オブジェクトは、指とスタイラスを含む。

30

#### 【0015】

検出領域170は、入力装置100の上、そのまわり、その中、及び／又はその近くに、入力装置100がユーザ入力（例えば、1つ以上の入力オブジェクト140によって提供されたユーザ入力）を検出できる任意の空間を包含する。特定の検出領域のサイズ、形状及び位置は、実施形態により大きく異なりうる。幾つかの実施形態では、検出領域170は、信号対雑音比によって十分に正確なオブジェクト検出が妨げられるまで、入力装置100の表面から空間内に1つ以上の方向に拡張する。この検出領域170が特定の方向に拡張する距離は、約1ミリメートル未満、数ミリメートル、数センチメートル以上でよく、使用される検出技術のタイプと必要精度により大きく異なりうる。したがって、幾つかの実施形態は、入力装置100の任意の面との非接触、入力装置100の入力面（例えば、タッチ面）との接触、ある大きさの印加力又は圧力と結合された入力装置100の入力面との接触、及び／又はこれらの組み合わせを含む入力を検出する。様々な実施形態で、入力面は、例えば、センサ電極が中に存在するケーシングの表面、センサ電極又は任意のケーシングの上に貼り付けられた表面板によって提供されうる。幾つかの実施形態では

40

50

、検出領域 170 は、入力装置 100 の入力面に投影されたときに矩形形状を有する。

【0016】

入力装置 100 は、センサ構成要素と検出技術の任意の組み合わせを利用して、検出領域 170 内のユーザ入力を検出できる。入力装置 100 は、ユーザ入力を検出するための複数のセンサ電極 120 を含む。入力装置 100 は、センサ電極を形成するように組み合わされた 1 つ以上のセンサ電極 120 を含みうる。幾つかの非限定的な例として、入力装置 100 は、容量性、弾性、抵抗性、誘導性、磁性、音響、超音波、及び / 又は光技術を使用しうる。

【0017】

幾つかの実施態様は、一次元、二次元、三次元、又はそれより高次元の空間にわたる画像を提供するように構成される。幾つかの実施態様は、特定の軸又は平面に沿った入力の投射を提供するように構成される。

10

【0018】

入力装置 100 の幾つかの抵抗性実施態様では、柔軟で導電性の第 1 の層が、1 つ以上のスペーサ要素によって導電性の第 2 の層から分離される。動作中、層内に 1 つ以上の電圧勾配が作成される。柔軟な第 1 層を押すと、層間の電気接触を作成するのに十分だけ撓み、その結果、層間の接触を表す電圧出力が生じる。これらの電圧出力は、位置情報を決定するために使用されうる。

【0019】

入力装置 100 の幾つかの誘導性実施態様では、1 つ以上のセンサ電極 120 が、1 つの共振コイル又はコイル対によって生成されるループ電流をピックアップする。次に、電流の大きさ、位相及び周波数の幾つかの組み合わせを使用して位置情報を決定できる。

20

【0020】

入力装置 100 の幾つかの容量性実施態様では、電圧又は電流を印加して電界を作成する。近くの入力オブジェクトは、電界を変化させ、電圧や電流などの変化として検出されうる容量結合の検出可能な変化を生成する。

【0021】

幾つかの容量性実施態様は、配列又は他の規則的若しくは不規則的パターンの容量性センサ電極 120 を利用して電界を作成する。幾つかの容量性実施態様では、個別のセンサ電極 120 をオーム短絡してより大きいセンサ電極を構成できる。幾つかの容量実施態様は、均一な抵抗でよい抵抗シートを利用する。

30

【0022】

前述されたように、幾つかの容量性実施態様は、センサ電極 120 と入力オブジェクトの間の容量結合の変化に基づく「自己キャパシタンス」(又は「絶対容量」)検出方法を利用する。一実施形態では、処理システム 110 は、既知の振幅を有する電圧をセンサ電極 120 上に生成し、センサ電極を駆動電圧まで充電するのに必要な電荷の量を測定するよう構成される。他の実施形態では、処理システム 110 は、既知の電流を生成し、得られた電圧を測定するよう構成される。様々な実施形態では、センサ電極 120 近くの入力オブジェクトは、センサ電極 120 近くの電界を変化させ、したがって、測定された容量結合が変化する。一実施態様では、絶対容量検出方法は、変調信号を使用してセンサ電極 120 を基準電圧(例えば、系統接地)に対して変調し、センサ電極 120 と入力オブジェクト 140 の間の容量結合を検出することによって機能する。

40

【0023】

更に、前述されたように、幾つかの容量性実施態様は、検出電極間の容量結合の変化に基づく「相互キャパシタンス」(又は「トランス容量」)検出方法を利用する。様々な実施形態では、検出電極近くの入力オブジェクト 140 が、検出電極間の電界を変化させ、それにより、測定された容量結合が変化する。一実施態様では、トランス容量検出方法は、以下に更に記載するように、1 つ以上のトランスマッタ検出電極(「トランスマッタ電極」とも)と 1 つ以上のレシーバ検出電極(「レシーバ電極」とも)の間の容量結合を検出することによって機能する。トランスマッタ検出電極は、トランスマッタ信号を伝送す

50

るために基準電圧（例えば、系統接地）に対して変調されうる。レシーバ検出電極は、結果信号の受け取りを容易にするために基準電圧に対して実質的に一定に保持されうる。結果信号は、1つ以上のトランスマッタ信号、及び／又は環境的干渉（例えば、他の電磁気信号）の1つ以上の発生源に対応する影響を含みうる。検出電極は、専用トランスマッタ電極又はレシーバ電極でもよく、送信と受信の両方を行うように構成されうる。

#### 【0024】

図1で、処理システム110は、入力装置100の一部として示される。処理システム110は、入力装置100のハードウェアを動作させて検出領域170の入力を検出するように構成される。処理システム110は、1つ以上の集積回路（IC）及び／又は他の回路構成要素の一部又は全てを含む。例えば、相互キャパシタンスセンサデバイスのための処理システムは、トランスマッタセンサ電極によって信号を送信するように構成されたトランスマッタ回路及び／又はレシーバセンサ電極によって信号を受信するように構成されたレシーバ回路とを有しうる。幾つかの実施態様では、処理システム110は、また、ファームウェアコードやソフトウェアコードなどの電子的に読み取り可能な命令を含みうる。幾つかの実施形態では、処理システム110を構成する構成要素は、入力装置100のセンサ電極120の近くなどに一緒に配置される。他の実施形態では、処理システム110の構成要素は、入力装置100のセンサ電極120の近くに1つ以上の構成要素があり、他の場所に1つ以上の構成要素があるように物理的に別個である。例えば、入力装置100は、デスクトップコンピュータに結合された周辺装置でよく、処理システム110は、デスクトップコンピュータの中央処理ユニット上と、中央処理ユニットとは別個の1つ以上のIC（おそらく関連ファームウェアを有する）上で動作するように構成されたソフトウェアを含みうる。別の例として、入力装置100は、電話に物理的に組み込まれてもよく、処理システム110は、電話の主プロセッサの一部である回路とファームウェアを含んでもよい。幾つかの実施形態では、処理システム110は、入力装置100の実現に専用化される。他の実施形態では、処理システム110は、また、表示画面の動作、触覚アクチュエータの駆動などの他の機能を実行する。

#### 【0025】

処理システム110は、処理システム110の様々な機能を処理する1組のモジュールとして実現されうる。各モジュールは、処理システム110、ファームウェア、ソフトウェア又はこれらの組み合わせの一部である回路を含みうる。様々な実施形態では、モジュールの様々な組み合わせが使用されうる。例示的モジュールには、センサ電極や表示画面などのハードウェアを動作させるためのハードウェア動作モジュール、センサ信号や位置情報などのデータを処理するためのデータ処理モジュール、及び情報を報告するための報告モジュールが含まれる。更に他の例示的モジュールには、センサ電極120を作動させて入力を検出するように構成されたセンサ作動モジュール、モード変更ジェスチャなどのジェスチャを識別するように構成された識別モジュール、及び動作モードを変更するためのモード変更モジュールが含まれる。処理システム110は、また、1つ以上のコントローラを含みうる。

#### 【0026】

幾つかの実施形態では、処理システム110は、1つ以上のアクションを引き起こすことによって、検出領域170内のユーザ入力（又は、ユーザ入力の欠如）に直接応答する。例示的なアクションには、動作モードの変更、並びにカーソル移動、選択、メニューナビゲーション、及び他の機能などのGUIアクションが含まれる。幾つかの実施形態では、処理システム110は、入力（又は、入力がないこと）に関する情報を電子システムのある部分（例えば、処理システム110とは別個の電子システムの中央処理システムがある場合は、その別個の中央処理システム）に提供する。幾つかの実施形態では、電子システムのある部分は、処理システム110から受け取った情報を処理してユーザ入力に作用し、例えば、モード変更アクションとGUIアクションを含むあらゆる種類のアクションを容易にする。

#### 【0027】

10

20

30

40

50

例えば、幾つかの実施形態では、処理システム 110 は、入力装置 100 のセンサ電極 120 を動作させて、検出領域 170 内の入力（又は、入力の欠如）を示す電気信号を生成する。処理システム 110 は、電子システムに提供される情報を作成する際に電気信号に任意の適切な量の処理を実行できる。例えば、処理システム 110 は、センサ電極 120 から得られたアナログ電気信号をデジタル化できる。別の例として、処理システム 110 は、フィルタリング又は他の信号調整を実行できる。更に別の例として、処理システム 110 は、情報が電気信号と基準線との差を反映するように、基準線を減算するか又は他の方法で考慮できる。更に他の例として、処理システム 110 は、位置情報の決定、入力のコマンドとしての認識、手書きの認識などを行える。

#### 【0028】

10

「位置情報」は、本明細書で使用されるとき、絶対位置、相対位置、速度、加速度及び他のタイプの空間情報を広く含む。例示的な「ゼロ次元」位置情報は、近／遠又は接触／非接触情報を含む。例示的な「一次元」位置情報は、軸に沿った位置を含む。例示的な「二次元」位置情報は、平面内の運動を含む。例示的な「三次元」位置情報は、空間内の瞬間又は平均速度を含む。更に他の例は、空間情報の他の表現を含む。また、例えば、ある期間にわたる位置、運動又は瞬間速度を追跡する履歴データを含む、1つ以上のタイプの位置情報に関する履歴データが、決定されかつ／又は記憶されうる。

#### 【0029】

幾つかの実施形態では、入力装置 100 は、処理システム 110 又は他の処理システムによって操作される付加入力構成要素によって実現される。そのような付加入力構成要素は、検出領域 170 内の入力のための冗長機能、又は他の機能を提供できる。図 1 は、入力装置 100 を使用して要素の選択を容易にするために使用されうる、検出領域 170 近くのボタン 130 を示す。他のタイプの付加入力構成要素には、スライダ、ポール、ホイール、スイッチなどが含まれる。これと反対に、幾つかの実施形態では、入力装置 100 は、他の入力構成要素なしに実施されうる。

20

#### 【0030】

30

幾つかの実施形態では、入力装置 100 は、タッチスクリーンインターフェースを含み、検出領域 170 は、表示装置 160 の表示画面のアクティブ領域の少なくとも一部と重なる。例えば、入力装置 100 は、表示画面を覆う実質的に透明なセンサ電極 120 を含み、関連電子システムのためのタッチスクリーンインターフェースを提供できる。表示画面は、ユーザに視覚インターフェースを表示できる任意のタイプの動的表示装置でよく、また任意のタイプの発光ダイオード（LED）、有機 LED（OLED）、陰極線管（CRT）、液晶ディスプレイ（LCD）、プラズマ、エレクトロルミネセンス（EL）、又は他の表示技術を含みうる。入力装置 100 と表示装置 160 は、物理要素を共用できる。例えば、幾つかの実施形態は、表示と検出に同じ電気構成要素の幾つかを利用できる。別の例として、表示画面 160 は、処理システム 110 によって一部分又は全体が操作されうる。

#### 【0031】

40

この技術の多くの実施形態が、完全に機能する装置の文脈で述べられているが、この技術の機構が、プログラム製品（例えば、ソフトウェア）として様々な形態で配布されうることを理解されたい。例えば、この技術の機構は、電子プロセッサによって読み取り可能な情報保持媒体（例えば、処理システム 110 によって読み取り可能な非一時的コンピュータ読み取り可能及び／又は記録可能／書き込み可能情報保持媒体）上のソフトウェアプログラムとして実現され配布されうる。更に、この技術の実施形態は、配布を行うために使用される特定タイプの媒体にかかわらず、等しく適用される。非一時的で電子的に読み取り可能な媒体の例には、様々なディスク、メモリスティック、メモリカード、メモリモジュールなどが含まれる。電子的に読み取り可能な媒体は、フラッシュ、光学、磁気、ホログラフィ又は任意の他の記憶技術に基づきうる。

#### 【0032】

典型的なセンサ電極機構

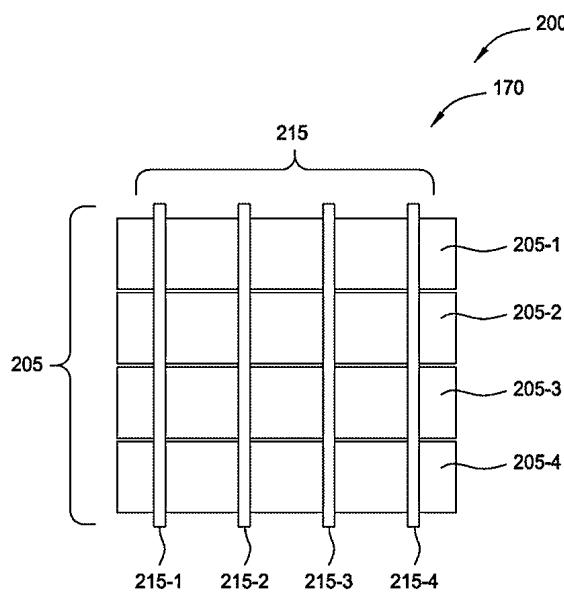

図 2 及び図 3 は、本明細書に記載された実施形態による、典型的センサ電極機構の一部

50

を示す図である。具体的には、機構 200(図2)は、幾つかの実施形態により、センサ電極のパターンと関連付けられた検出領域170内で検出するように構成されたセンサ電極のパターンの一部を示す。説明と記述を分かりやすくするために、図2は、センサ電極を単純な矩形パターンで示し、様々な関連構成要素を示していない。この検出電極パターンは、第1の複数のセンサ電極205(例えば、205-1, 205-2, 205-3, 205-4)と、第2の複数のセンサ電極215(例えば、215-1, 215-2, 215-3, 215-4)とを含む。センサ電極205, 215はそれぞれ、前述されたセンサ電極120の例である。一実施形態では、処理システム110は、第1の複数のセンサ電極205を複数のトランスマッタ電極として、第2の複数のセンサ電極215を複数のレシーバ電極として作動させる。別の実施形態では、処理システム110は、第1の複数のセンサ電極205と第2の複数のセンサ電極215を絶対容量検出電極として作動させる。

#### 【0033】

第1の複数のセンサ電極205と第2の複数のセンサ電極215は、典型的には、互いにオーミック分離される。即ち、1つ以上の絶縁体が、第1の複数のセンサ電極205と第2の複数のセンサ電極215を分離し、それらが互いに電気的に短絡するのを防ぐ。幾つかの実施形態では、第1の複数のセンサ電極205と第2の複数のセンサ電極215が、共通層上に配置されうる。複数のセンサ電極205, 215は、それらの間の交差領域に配置された絶縁材料によって電気的に分離されてもよく、そのような構造では、第1の複数のセンサ電極205及び/又は第2の複数のセンサ電極215は、同一電極の様々な部分を接続するジャンパーで構成されうる。幾つかの実施形態では、第1の複数のセンサ電極205と第2の複数のセンサ電極215は、1つ以上の絶縁材料層によって分離される。幾つかの実施形態では、第1の複数のセンサ電極205と第2の複数のセンサ電極215は、1つ以上の基板によって分離され、例えば、同一基板の両側または積層された異なる基板上に配置されてもよい。

#### 【0034】

複数のセンサ電極205, 215は、任意の所望の形状に形成されうる。更に、センサ電極205のサイズ及び/又は形状は、センサ電極215のサイズ及び/又は形状と異なりうる。更に、基板の同じ側に配置されたセンサ電極205, 215が、異なる形状及び/又はサイズを有してもよい。一実施形態では、第1の複数のセンサ電極205は、第2の複数のセンサ電極215より大きくてよい(例えば、より大きな表面積を有する)が、これは必要条件ではない。他の実施形態では、第1及び第2の複数のセンサ電極205, 215は、類似のサイズ及び/又は形状を有してもよい。

#### 【0035】

一実施形態では、第1の複数のセンサ電極205は、実質的に第1の方向に延在し、第2の複数のセンサ電極215は、実質的に第2の方向に延在する。例えば、図2に示されたように、第1の複数のセンサ電極205は、ある方向に延し、第2の複数のセンサ電極215は、センサ電極205に対して実質的に直角の方向に延在する。他の向き(例えば、平行又は他の相対的な向き)も可能である。

#### 【0036】

幾つかの実施形態では、第1及び第2の複数のセンサ電極205, 215は両方とも、一緒に表示装置160を構成する複数の層(又は表示スタック)の外側に配置される。表示スタックの一例は、レンズ層、1つ以上の偏光子層、カラーフィルタ層、1つ以上の表示電極層、表示材料層、薄膜トランジスタ(TFT)ガラス層、及びバックライト層などの層を含みうる。しかしながら、表示スタックの他の構成が可能である。他の実施形態では、第1及び第2の一方又は両方の複数のセンサ電極205, 215が、表示関連層の一部として含まれるか個別層として含まれるかに関係なく、表示スタック内に配置される。例えば、特定の表示電極層内のVcom電極は、表示更新と容量検出の両方を行うように構成されうる。

#### 【0037】

10

20

30

40

50

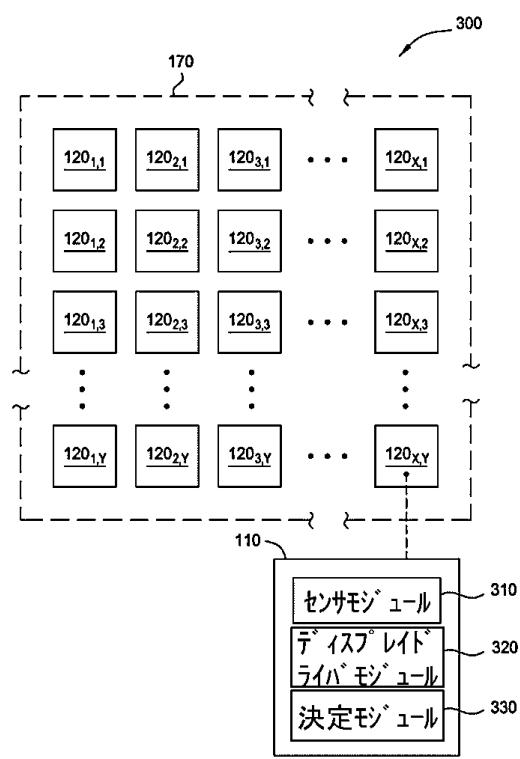

図3の機構300は、幾つかの実施形態による、検出領域170内で検出するように構成されたセンサ電極パターンの一部を示す。例証と記述を分かりやすくするために、図3は、センサ電極120を単純な長方形パターンで示し、他の関連構成要素を示していない。典型的パターンは、X列とY行で配列されたセンサ電極120X, Yの配列を含み、XとYは正整数であるが、XとYの一方はゼロでよい。センサ電極120のパターンは、対極配列、繰り返しパターン、非繰り返しパターン、單一行又は列、あるいは他の適切な配列などの他の構成を有しうる。更に、様々な実施形態では、センサ電極120の数は、行ごと及び/又は列ごとに異なってもよい。一実施形態では、センサ電極120の少なくとも1つの行及び/又は列は、他のものからずらされ、他と異なる少なくとも1つの方向に延在する。センサ電極120は、処理システム110に結合され、検出領域170内の入力オブジェクトの存在(又は、その欠如)を決定するために利用される。

10

#### 【0038】

第1の動作モードで、センサ電極120(1201, 1, 1202, 1, 1203, 1, ... 120X, Y)の配列は、絶対検出技術によって入力オブジェクトの存在を検出するために利用されうる。即ち、処理システム110は、センサ電極120を変調して、変調されたセンサ電極120と入力オブジェクトの間の容量結合の変化の測定値を取得して入力オブジェクトの位置を決定するように構成される。処理システム110は、更に、変調されたセンサ電極120が受け取った結果信号の測定値に基づいて、絶対容量の変化を決定するように構成される。

20

#### 【0039】

幾つかの実施形態では、機構300は、センサ電極120の少なくとも2つの間に配置された1つ以上のグリッド電極(図示せず)を含む。グリッド電極は、複数のセンサ電極120をグループとして少なくとも部分的に区切り、また追加又は代替として、センサ電極120の1つ以上を完全又は部分的に区切ってもよい。一実施形態では、グリッド電極は、複数のアバーチャを有する平面体であり、各アバーチャは、センサ電極120のそれぞれを区切る。他の実施形態では、グリッド電極は、個別又はグループで駆動されうる複数のセグメント又は複数のセグメントを含む。グリッド電極は、センサ電極120と同じように製造されうる。グリッド電極は、センサ電極120と共に、導電性ルーティングトレースを利用しつて入力オブジェクト検出に使用される処理システム110に結合されうる。

30

#### 【0040】

センサ電極120は、典型的には、互いにオーミック分離され、グリッド電極からオーミック分離される。即ち、1つ以上の絶縁体が、センサ電極120とグリッド電極を分離し、それらが互いに電気的に短絡するのを防ぐ。幾つかの実施形態では、センサ電極120とグリッド電極は、絶縁ギャップによって分離され、この絶縁ギャップは、電気絶縁材料が充填されもよく、空気ギャップでもよい。幾つかの実施形態では、センサ電極120とグリッド電極は、1つ以上の絶縁材料層によって垂直方向に分離される。幾つかの他の実施形態では、センサ電極120とグリッド電極は、1つ以上の基板によって分離され、例えば、同じ基板の反対側に配置されてもよく異なる基板上に配置されてもよい。更に他の実施形態では、グリッド電極は、同一基板上又は様々な基板上に、複数の層で構成されてもよい。一実施形態では、第1のグリッド電極が、第1の基板上(又は、基板の第1の側)に形成され、第2のグリッド電極が、第2の基板上(又は、基板の第2の側)に形成されてもよい。例えば、第1のグリッド電極が、表示装置160の薄膜トランジスタ(TFT)層上に配置された1つ以上のコモン電極を含み(図1)、第2のグリッド電極は、表示装置160のカラーフィルタガラス上に配置される。第1及び第2のグリッド電極の寸法は、等しくてもよく少なくとも1つの寸法が異なってもよい。

40

#### 【0041】

第2の動作モードで、センサ電極120(1201, 1, 1202, 1, 1203, 1, ... 120X, Y)は、トランスマッタ信号がグリッド電極に印加されたときにトランスマッタ容量検出技術によって入力オブジェクトの存在を検出するために利用されうる。即ち、処

50

理システム 110 は、トランスマッタ信号によってグリッド電極を駆動し、各センサ電極 120 によって結果信号を受け取るように構成され、結果信号は、入力オブジェクトの位置を決定するために処理システム 110 又は他のプロセッサによって利用され、トランスマッタ信号に対応する影響を含む。

#### 【 0042 】

第 3 の動作モードでは、センサ電極 120 は、トランス容量検出技術によって入力オブジェクトの存在を検出するために利用されるトランスマッタ及びレシーバ電極のグループに分割されうる。即ち、処理システム 110 は、第 1 グループのセンサ電極 120 をトランスマッタ信号によって駆動し、結果信号を第 2 グループのセンサ電極 120 によって受け取ってもよく、結果信号は、トランスマッタ信号に対応する影響を含む。結果信号は、入力オブジェクトの位置を決定するために処理システム 110 又は他のプロセッサによって利用される。

10

#### 【 0043 】

入力装置 100 は、前述されたモードのいずれかで動作するように構成されうる。入力装置 100 は、また、前述されたモードの任意の複数のモード間で切り替わるように構成されうる。

#### 【 0044 】

容量結合の局所的容量検出領域は、「容量性画素」、「タッチ画素」、「ティクセル (pixel)」などと呼ばれうる。容量性画素は、第 1 の動作モードでは個別のセンサ電極 120 と基準電圧の間、第 2 の動作モードではセンサ電極 120 とグリッド電極の間、及びトランスマッタ及びレシーバ電極として使用されるセンサ電極 120 のグループの間に形成されうる（例えば、図 2 の機構 200）。容量結合は、センサ電極 120 と関連付けられた検出領域 170 内の入力オブジェクトの近さと動きにより変化し、したがって、入力装置 100 の検出領域内の入力オブジェクトの存在の指標として使用されうる。

20

#### 【 0045 】

幾つかの実施形態では、センサ電極 120 は、そのような容量結合を決定するために「走査」される。即ち、一実施形態では、センサ電極 120 の 1 つ以上が、トランスマッタ信号を送信するために駆動される。トランスマッタは、1 つのトランスマッタ電極が一度に送信するか複数のトランスマッタ電極が同時に送信するように作動されうる。複数のトランスマッタ電極が同時に送信する場合、複数のトランスマッタ電極は、同じトランスマッタ信号を送信し、それにより実質的により大きいトランスマッタ電極を作成できる。あるいは、複数のトランスマッタ電極が、異なるトランスマッタ信号を送信できる。例えば、複数のトランスマッタ電極は、レシーバ電極の結果信号に対する複合的な影響を個々に決定することを可能にする 1 つ以上の符号化方式により様々なトランスマッタ信号を送信できる。一実施形態では、複数のトランスマッタ電極は、同じトランスマッタ信号を同時に送信でき、レシーバ電極は、影響を受け、走査方式に従って測定される。

30

#### 【 0046 】

レシーバセンサ電極として構成されたセンサ電極 120 は、結果信号を取得するために単独又は複合的に操作されうる。結果信号は、容量性画素における容量結合の測定値を決定するために使用されうる。処理システム 110 は、行われる同時測定の数並びに支持電気構造のサイズを小さくするために、センサ電極 120 によって走査式及び / 又は多重式に受け取るように構成されうる。一実施形態では、1 つ以上のセンサ電極は、マルチプレクサなどのスイッチング要素を介して処理システム 110 のレシーバに結合される。そのような実施形態では、スイッチング要素は、処理システム 110 の内部でもよく、処理システム 110 の外部でもよい。1 つ以上の実施形態では、スイッチング要素は、更に、センサ電極 120 をトランスマッタ又は他の信号及び / 又は電位と結合するように構成されうる。一実施形態では、スイッチング要素は、複数のレシーバ電極を共通レシーバに同時に結合するように構成されうる。

40

#### 【 0047 】

他の実施形態では、そのような容量結合を決定するセンサ電極 120 の「走査」は、セ

50

ンサ電極の1つ以上の変調と、1つ又はセンサ電極の絶対容量の測定を含む。別の実施形態では、センサ電極は、複数のセンサ電極が一度に駆動され受け取られるように作動される。そのような実施形態では、1つ以上のセンサ電極120のそれぞれから絶対容量測定値が同時に得られうる。一実施形態では、センサ電極120のそれぞれが、同時に駆動され受信され、センサ電極120のそれぞれから同時に絶対容量測定値を得る。様々な実施形態では、処理システム110は、センサ電極120の一部分を選択的に変調するよう構成されうる。例えば、センサ電極は、ホストプロセッサ上で動作するアプリケーション、入力装置の状態及び検出装置の動作モードに基づいて（これらに限定されない）選択されうる。様々な実施形態では、処理システム110は、センサ電極120の少なくとも一部分を選択的に遮蔽し、かつ他のセンサ電極120によって選択的に遮蔽又は送信するよう構成されうる。

#### 【0048】

容量性画素からの1組の測定値は、画素における容量結合を表す「容量性イメージ」（「容量フレーム」とも）を構成する。多数の容量性イメージが、多数の期間にわたって取得され、それらの間の差を使用して検出領域内の入力に関する情報を得る。例えば、連続期間にわたって取得された連続する容量性イメージを使用して、検出領域に入る入力オブジェクト、検出領域から出る入力オブジェクト、及び検出領域の中の1つ以上の入力オブジェクトの動きを追跡できる。

#### 【0049】

上記実施形態のいずれにおいても、複数のセンサ電極120は、センサ電極120が同時に変調されるか同時に受け取るように連動されてもよい。前述された方法と比較して、複数のセンサ電極を連動させると、正確な位置情報を識別するために使用できない可能性がある粗い容量性イメージが作成されうる。しかしながら、粗い容量性イメージは、入力オブジェクトの存在を検出するために使用されうる。一実施形態では、粗い容量性イメージは、処理システム110又は入力装置100を「dose」モード又は低消費電力モードから移行するために使用されうる。一実施形態では、粗い容量性イメージは、容量検出ICを「Dose」モード又は低消費電力モードから移行するために使用されうる。別の実施形態では、粗い容量性イメージは、ホストICと表示ドライバの少なくとも一方を「Dose」モード又は低省電力モードでなくすために使用されうる。粗い容量性イメージは、全センサ領域又はセンサ領域の一部分にのみ対応しうる。

#### 【0050】

入力装置100のバックグラウンドキャパシタンスは、検出領域170内に入力オブジェクトがないことと関連付けられた容量性イメージである。バックグラウンドキャパシタンスは、環境及び動作条件により変化し、様々な方法で評価されうる。例えば、幾つかの実施形態は、検出領域170内に入力オブジェクトがないことが決定されたときに「ベースラインイメージ」を取得し、それらのベースラインイメージをそのバックグラウンド容量の評価として使用する。バックグラウンド容量又はベースライン容量は、2つのセンサ電極間の漂遊容量結合に（一方のセンサ電極が、変調信号によって駆動され、他方が、系統接地に対して一定に保持される）、又はレシーバ電極と近傍変調電極の間の漂遊容量結合によって存在しうる。多くの実施形態では、バックグラウンド又はベースライン容量は、ユーザ入力ジェスチャの時間期間にわたって比較的一定でありうる。

#### 【0051】

容量性イメージは、より効率的な処理のために入力装置100のバックグラウンド容量に合わせて調整されうる。幾つかの実施形態は、容量性画素における容量結合の測定値を「ベースライン化」して「ベースライン容量性イメージ」を作成することによってこれを達成する。即ち、幾つかの実施形態は、容量性イメージを構成する測定値を、それらのイメージと関連付けられた「ベースラインイメージ」の適切な「ベースライン値」と比較し、ベースラインイメージからの変化を決定する。

#### 【0052】

10

20

30

40

50

幾つかのタッチスクリーン実施形態では、センサ電極 120 の 1つ以上が、表示画面の表示の更新に使用される 1つ以上の表示電極を含む。表示電極は、セグメント化 Vcom 電極（コモン電極）の 1つ以上のセグメント、ソース駆動線、ゲート線、アノードサブ画素電極、カソード画素電極、又は他の適切な表示要素など、アクティブマトリクスディスプレイの 1つ以上の要素を含みうる。これらの表示電極は、適切な表示画面基板上に配置されうる。例えば、コモン電極は、幾つかの表示画面（例えば、面内スイッチング（IPS）、フリンジ場スイッチング（FFS）、又はプレーントゥライインスイッチング（PLS）有機発光ダイオード（OLED））上の透明基板（ガラス基板、TFT ガラス、又は他の透明材料）上、幾つかの表示画面（例えば、パターン化垂直整列（PVA）又はマルチドメイン垂直整列（MVA））のカラーフィルタガラスの下面上、放出層（OLED）の上などに配置されうる。そのような実施形態では、複数の機能を実行するので、表示電極は、「コンビネーション電極」とも呼ばれうる。様々な実施形態では、センサ電極 120 のそれぞれは、1つ以上のコモン電極を含む。他の実施形態では、少なくとも 2つのセンサ電極 120 が、少なくとも 1つのコモン電極を共用できる。以下の記述は、センサ電極 120 及び / 又はグリッド電極が 1つ以上のコモン電極を含むことについて述べうるが、前述されたような様々な他の表示電極が、コモン電極と共に又はコモン電極の代替として使用されうる。様々な実施形態では、センサ電極 120 とグリッド電極は、コモン電極層全体（Vcom 電極）を含む。

#### 【0053】

様々なタッチスクリーン実施形態では、「容量性フレームレート」（連続容量性イメージが取得されるレート）は、「表示フレームレート」（画面をリフレッシュして同じ画像を再表示することを含む、表示画像が更新されるレート）のものと同じでもよく異なってもよい。様々な実施形態では、容量性フレームレートは、表示フレームレートの整数倍である。他の実施形態では、容量性フレームレートは、表示フレームレートの分数倍である。更に他の実施形態では、容量性フレームレートは、表示フレームレートの分数でも整数倍でもよい。1つ以上の実施形態では、表示フレームレートは、変化することがあるが（例えば、電力を削減するか三次元表示情報などの追加画像データを提供するため）、タッチフレームレートは一定のままである。他の実施形態では、表示フレームレートは、一定のままでよく、タッチフレームレートが増減される。

#### 【0054】

引き続き図 3 を参照すると、センサ電極 120 に結合された処理システム 110 は、センサモジュール 310 と、必要に応じてディスプレイドライバモジュール 320 を含む。センサモジュール 310 は、入力検出が必要とされる期間中の容量検出のためにセンサ電極 120 の少なくとも 1つを駆動するように構成された回路を含む。一実施形態では、センサモジュール 310 は、少なくとも 1つのセンサ電極 120 に変調信号を加えて、少なくとも 1つのセンサ電極と入力オブジェクトの間の絶対容量の変化を検出するように構成される。別の実施形態では、センサモジュール 310 は、少なくとも 1つのセンサ電極 120 にトランスマッタ信号を加えて、少なくとも 1つのセンサ電極と別のセンサ電極 120 との間のトランス容量の変化を検出するように構成される。変調信号とトランスマッタ信号は、一般に、入力検出のために割り当てられた時間期間に複数の電圧遷移を含む様々な電圧信号である。様々な実施形態では、センサ電極 120 及び / 又はグリッド電極が、様々な動作モードで違うふうに駆動されうる。一実施形態では、センサ電極 120 及び / 又はグリッド電極は、位相、振幅及び / 又は形状のいずれか 1つが異なりうる信号（変調信号、トランスマッタ信号及び / 又はシールド信号）によって駆動されうる。様々な実施形態では、変調信号とトランスマッタ信号は、少なくとも 1つの形状、周波数、振幅及び / 又は位相が類似する。他の実施形態では、変調信号とトランスマッタ信号は、周波数、形状、位相、振幅及び位相が異なる。センサモジュール 310 は、センサ電極 120 及び / 又はグリッド電極の 1つ以上に選択的に結合されうる。例えば、センサモジュール 310 は、センサ電極 120 の選択部分と結合され、絶対容量検出モード又はトランス容量検出モードで動作できる。別の例では、センサモジュール 310 は、センサ電極 120 の異

10

20

30

40

50

なる部分でよく、絶対容量検出モード又はトランス容量検出モードで動作できる。更に別の例では、センサモジュール310は、全てのセンサ電極120に結合され、絶対容量検出モード又はトランス容量検出モードで動作できる。

#### 【0055】

センサモジュール310は、グリッド電極を、近くの導体の電気的影響からセンサ電極120を遮蔽できるシールド電極として動作させるように構成される。一実施形態では、処理システムは、グリッド電極を、近くの導体の電気的影響からセンサ電極120を「遮蔽」できるシールド電極として動作させ、またセンサ電極120をグリッド電極から防護してグリッド電極とセンサ電極120の間の寄生容量が少なくとも部分的に減少するよう構成される。一実施形態では、シールド信号が、グリッド電極に加えられる。シールド信号は、系統接地若しくは他の接地などの接地信号又は任意の他の定電圧（即ち、非変調）信号でよい。別の実施形態では、グリッド電極をシールド電極として動作させることは、グリッド電極が電気的に浮動されることを含みうる。一実施形態では、グリッド電極は、他のセンサ電極に対する大きい結合により電極が浮動されている間に有効シールド電極として動作できる。他の実施形態では、シールド信号は、「ガーディング信号」と呼ばれることがあり、ガーディング信号は、センサ電極に加えられる変調信号と類似の位相、周波数及び振幅の少なくとも1つを有する可変電圧信号である。1つ以上の実施形態では、ルーティングトレースは、グリッド電極及び/又はセンサ電極120の下で引き回すことによって入力オブジェクトに対する応答から遮蔽されてもよく、したがって、センサ電極120として示されたアクティブセンサ電極の一部でなくてもよい。

10

#### 【0056】

1つ以上の実施形態では、容量検出（又は、入力検出）と表示更新が、少なくとも部分的に重複する期間に行われうる。例えば、表示更新のためにコモン電極が駆動されるとき、コモン電極は、容量検出のためにも駆動されうる。別の実施形態では、容量検出と表示更新は、非表示更新期間とも呼ばれる非重複期間に行われてもよい。様々な実施形態では、非表示更新期間は、表示フレームの2つの表示ラインのための表示ライン更新期間の間に生じることがあり、少なくとも表示更新期間と同じ時間の長さでよい。そのような実施形態では、非表示更新期間は、「長い水平プランキング期間」、「長いhプランキング期間」又は「分散プランキング期間」と呼ばれることがあり、プランキング期間は、2つの表示更新期間の間に生じ、少なくとも表示更新期間と同じ長さである。一実施形態では、非表示更新期間は、フレームの表示ライン更新期間の間に生じ、トランスミッタ信号の複数の遷移をセンサ電極120に印加することを可能にするのに十分の長さである。他の実施形態では、非表示更新期間は、水平プランキング期間と垂直プランキング期間を含みうる。処理システム110は、様々な非表示更新時間の1つ以上又はその任意の組み合わせの最中に、容量検出のためにセンサ電極120を駆動するように構成されうる。繰り返しコヒーレント周波数及び位相によって重複する表示更新期間と容量検出期間の正確な制御を提供するために、センサモジュール310とディスプレイドライバモジュール320の間で同期信号が共用されうる。一実施形態では、そのような同期信号は、比較的安定した電圧を有する表示更新期間と一致するように、入力検出期間の始めと終わり（例えば、入力積分器リセット時間の終わり近くと表示電荷共用時間の終わり近く）で比較的安定した電圧を可能にするように構成されうる。変調信号又はトランスミッタ信号の変調周波数が、表示ライン更新レートの高調波でよく、その位相は、表示要素からレシーバ電極に、ベースラインイメージの一部でありうるほぼ一定の電荷結合を提供するように決定される。

20

30

#### 【0057】

センサモジュール310は、入力検出が必要とされる期間中の変調信号又はトランスミッタ信号に対応する影響を含む結果信号を、センサ電極120及び/又はグリッド電極によって受け取るように構成された回路を含む。センサモジュール310は、検出領域170内の入力オブジェクトの位置を決定してもよく、結果信号を示す情報を含む信号を、別のモジュール又はプロセッサ（例えば、関連付けられた電子装置150（即ち、ホストプロセッサ）の決定モジュール330又はプロセッサに提供して、検出領域170内の入力

40

50

オブジェクトの位置を決定してもよい。

**【 0 0 5 8 】**

ディスプレイドライバモジュール 320 は、処理システム 110 に含まれてもよく、処理システム 110 と別個でもよい。ディスプレイドライバモジュール 320 は、非検出（例えば、表示更新）期間中に表示装置 160 の表示に表示画像更新情報を提供するように構成された回路を含む。

**【 0 0 5 9 】**

一実施形態では、処理システム 110 は、ディスプレイドライバモジュール 320 と、センサモジュール 310 の少なくとも一部分（例えば、トランスマッタモジュール及び／又はレシーバモジュール）とを含む第 1 の一体型コントローラを含む。別の実施形態では、処理システム 110 は、ディスプレイドライバモジュール 320 を含む第 1 の一体型コントローラと、センサモジュール 310 を含む第 2 の一体型コントローラとを含む。更に別の実施形態では、処理システムは、ディスプレイドライバモジュール 320 とセンサモジュール 310 の第 1 の部分（例えば、トランスマッタモジュールとレシーバモジュールの一方）とを含む第 1 の一体型コントローラと、センサモジュール 310 の第 2 の部分（例えば、トランスマッタとレシーバモジュールのうちの他方の 1 つ）を含む第 2 の一体型コントローラとを含む。複数の一体型回路を含むこれらの実施形態では、これらの間に、表示更新周期、検出期間、トランスマッタ信号、表示更新信号などを同期させるように構成された同期機構が結合されてもよい。

**【 0 0 6 0 】**

前述されたように、幾つかの実施形態では、決定モジュール 330 が、検出領域 170 内の入力オブジェクトの位置を決定するように構成されうる。決定モジュール 330 は、更に、処理システム 110 の様々な構成要素の動作の調整と関連した他の機能を実行するように構成されうる。代替実施形態では、決定モジュール 330 に起因する機能の幾つか又は全ては、処理システム 110 の外部のプロセッサ（例えば、関連電子システムのホストプロセッサ）によって提供されうる。

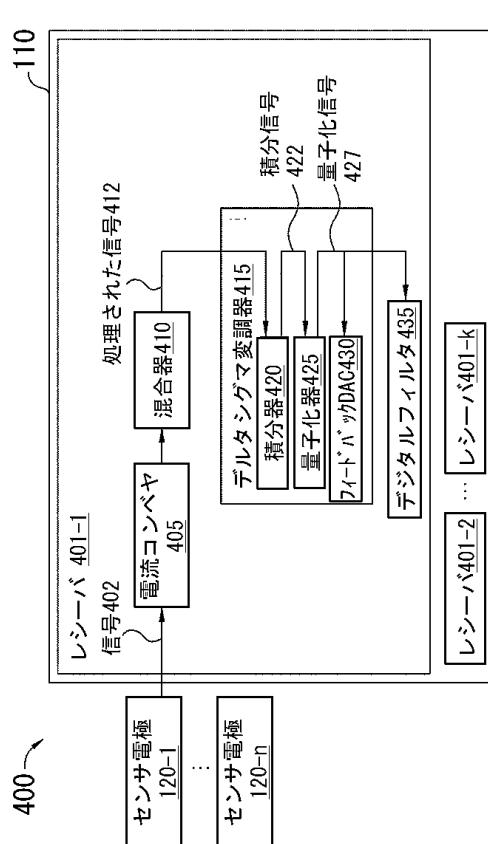

**【 0 0 6 1 】**

デルタシグマ変調器を備えた入力装置レシーバの典型的機構

図 4 は、一実施形態による、典型的入力装置のブロック図を示す。より具体的には、入力装置 400 は、複数のセンサ電極 120 - 1 ~ 120 - n と結合された処理システム 110 を含む。様々な参照番号を使用して述べたが、入力装置 400 が、前述した入力装置 100 の様々な特徴を含みうることに注意されたい。

**【 0 0 6 2 】**

処理システム 110 は、複数の k 個のレシーバ 401 - 1 ~ 401 - k を含み、各レシーバは、センサ電極 120 - 1 ~ 120 - n から信号を受け取るように構成される。図示されたように、レシーバ 401 - 1 は、センサ電極 120 - 1 から信号 402 を受け取るように構成される。幾つかの実施形態では、レシーバ 401 - 1 ~ 401 - k は、処理システム 110 の AFE として提供され、更なる信号調整回路を含みうる。複数のセンサ電極 120 - 1 ~ 120 - n に関して具体的に述べたが、本明細書で述べる技術は、他の構成のセンサ電極（例えば、図 2 の複数のセンサ電極 205, 215）と共に使用されうる。更に、レシーバ 401 - 1 ~ 401 - k は、絶対容量及びトランス容量検出実施態様内で信号を受け取るために使用されうる。

**【 0 0 6 3 】**

レシーバ 401 - 1 は、電流コンベア 405 と混合器 410 を含む。電流コンベア 405 は、信号 402 を受け取り、信号 402 の電流を電流コンベア 405 の出力にミラーリングするように構成される。電流コンベア 405 は、任意の適切な利得値を有しうる。混合器 410 は、電流コンベア 405 からミラー電流を受け取り、その電流を R.F. 周波数からほぼ直流（D.C.）レベル（即ち、実質的に周波数成分を含まない）にダウンコンバートする。混合器 410 は、矩形波混合器、高調波拒絶混合器又は正弦波混合器などの任意の適切な実施態様を有しうる。

10

20

30

40

50

**【 0 0 6 4 】**

電流コンベア 4 0 5 と混合器 4 1 0 は、受け取った信号 4 0 2 に基づいて処理信号 4 1 2 を作成する働きをする。処理信号 4 1 2 は、完全差動出力、疑似差動出力又はシングルエンド出力の形でよい。一実施形態では、センサ電極 1 2 0 - 1 は、シングルエンド信号 4 0 2 を電流コンベア 4 0 5 に提供し、混合器 4 1 0 は、完全差動処理信号 4 1 2 を出力する。

**【 0 0 6 5 】**

レシーバ 4 0 1 - 1 は、更に、デルタシグマ変調器 4 1 5 とデジタルフィルタ 4 3 5 を含む。一般に、デルタシグマ変調器 4 1 5 は、比較的高周波数のデルタシグマ変調を使用して処理信号 4 1 2 を符号化する働きをし、デジタルフィルタ 4 3 5 は、より高い解像度だがより低いサンプル周波数のデジタル出力を形成するために利用される。デジタルフィルタ 4 3 5 は、任意の適切な実施態様を有しうる。例えば、デジタルフィルタ 4 3 5 は、有限インパルス応答 (FIR) フィルタ又は無限インパルス応答 (IIR) フィルタでよく、幾つかの実施形態では、デジタルフィルタ 4 3 5 は低域フィルタである。他の実施形態では、デジタルフィルタ 4 3 5 は、高域フィルタである。更に、シングルビット量子化を有する幾つかの実施形態では、シングルビットストリームを使用して（例えば、ワインドウフーリエ変換を使用して）周波数スペクトルを分析できるので、デジタルフィルタ 4 3 5 は、デシメーションを実行しなくてもよい。有益には、デシメーションを行うための除外回路は、レシーバ 4 0 1 - 1 に必要な領域を低減する。

10

**【 0 0 6 6 】**

幾つかの実施形態では、デルタシグマ変調器 4 1 5 は、コモンモードフィードバックを有する、差動入力、一次、連続時間、受動デルタシグマ変調器である。有益には、デルタシグマ変調器 4 1 5 の一次及び連続時間態様は、より高次及び／又は離散時間実施態様よりも少ない回路を必要とする。例えば、連続時間実施態様は、デルタシグマ変調器 4 1 5 のループの外部にサンプリング回路を含む必要がなく、その結果、実施態様が本質的にアンチエイリアシングになる。しかしながら、代替実施形態では、デルタシグマ変調器 4 1 5 は、離散時間型変調器及び／又は一次より高次を含む。更に、代替実施形態では、デルタシグマ変調器 4 1 5 は、シングルエンド又は擬似差動入力を有しうる。

20

**【 0 0 6 7 】**

デルタシグマ変調器 4 1 5 は、更に、処理信号 4 1 2 を積分して積分信号 4 2 2 を作成するように構成された積分器 4 2 0 を含む。積分器 4 2 0 は、能動又は受動実施態様を有しうる。一般に、受動実施態様は、抵抗、キャパシタンス及び／又はインダクタンスなどの受動回路要素を単独で含む。一般に、能動実施態様は、制御信号に基づいて電子流を制御できる演算増幅器（オペアンプ）又は他の能動素子を含む。幾つかの実施形態では、積分器 4 2 0 は、受動積分器を含み、受動積分器は、能動積分器と比較したとき、必要な領域が少なくかつ改善された線形性能を提供する傾向がある。

30

**【 0 0 6 8 】**

デルタシグマ変調器 4 1 5 は、更に、積分信号 4 2 2 に基づいて量子化信号 4 2 7 を生成するように構成された量子化器 4 2 5 を含む。量子化器 4 2 5 は、任意の適切なシングルビット又はマルチビット実施態様を有してもよく、幾つかの実施形態で、量子化器 4 2 5 は、一般にマルチビット量子化器より少ない領域を必要とするシングルビット量子化器である。デルタシグマ変調器 4 1 5 は、更に、量子化信号 4 2 7 に基づいて制御されたフィードバックデジタルアナログ変換器 (DAC) 4 3 0 を含む。フィードバック DAC 4 3 0 は、ゼロ復帰 (RZ) 又は非ゼロ復帰 (NRZ) DAC などの任意の適切な実施態様を有しうる。更に、フィードバック DAC 4 3 0 は、抵抗実施態様又はスイッチドキャパシタ抵抗器 (SCR) 回路網の実施態様として構成されうる。

40

**【 0 0 6 9 】**

電流コンベア 4 0 5 を有する幾つかの実施形態では、デルタシグマ変調器 4 1 5 は、電流コンベア 4 0 5 によって生成されたコモンモード電流を軽減するように構成されたコモンモードフィードバック機構を含む。しかしながら、幾つかの代替実施形態では、レー

50

バ 4 0 1 - 1 は、電流コンベア 4 0 5 と混合器 4 1 0 を含まない。電流コンベア 4 0 5 (及び、場合によっては、関連コモンモードフィードバック機構) と混合器 4 1 0 を省略すると、レシーバ 4 0 1 - 1 に必要な領域が少なくなる。1 つの非限定的な例では、指紋検出実施態様は、電流コンベア 4 0 5 を省略すると同時にコモンモードフィードバック機構を保持できる。更に、これらの実施形態では、センサ電極 1 2 0 - 1 のキャパシタンスを積分器 4 2 0 として使用でき、これは、更に、レシーバ 4 0 1 - 1 の必要な領域と消費電力を削減できる。一般に、センサ電極 1 2 0 - 1 のキャパシタンスを積分器 4 2 0 に使用すると、同じサンプリング周波数のデルタシグマ変調器 4 1 5 のオーバーサンプリング比が低下する傾向がある。場合によって、デルタシグマ変調器 4 1 5 の性能は、オーバーサンプリング比が低いにもかかわらず、許容可能なままである。一実施形態では、デルタシグマ変調器 4 1 5 は、低いオーバーサンプリング比に起因する低い性能を緩和するために、二次(又は、より高次)実施態様に高められる。

#### 【 0 0 7 0 】

幾つかの実施形態では、レシーバ 4 0 1 - 1 は、指紋検出を行うのに適する。一般に、指紋検出は、干渉に対する性能を改善するために差動センサ測定値を使用して行われ、位置検出は、典型的には、シングルエンドの測定値を使用して行われる。これらの実施形態では、電流コンベア 4 0 5 を含む比較的低インピーダンスの入力段は、高インピーダンスの入力段(例えば、トランスコンダクタ)と交換されうる。例えば、トランスコンダクタは、信号 4 0 2 を受け取るように構成された差動対、差動対の出力電圧を増幅するように構成された利得段、及び増幅出力電圧を混合器 4 1 0 に渡される電流に変換するトランスコンダクタンス増幅器を使用して構成されうる。

#### 【 0 0 7 1 】

図 5 は、一実施形態による、典型的入力装置の概略ブロック図を示す。より具体的には、機構 5 0 0 は、入力装置のレシーバ 4 0 1 の 1 つの可能な実施態様を示す。要素が、前述された入力装置 1 0 0 , 4 0 0 の様々な特徴に基づいて機構 5 0 0 に追加されかつ/又は機構 5 0 0 から除去されうることに注意されたい。

#### 【 0 0 7 2 】

センサ電極 1 2 0 は、レシーバ 4 0 1 と結合される。センサ電極 1 2 0 は、抵抗  $R_{s e n s o r}$  とキャパシタンス  $C_{s e n s o r}$  を含む単極モデルを使用して表わされる。センサ電極 1 2 0 は、実際にはより複雑な挙動を示しうるが、単極モデルは、この記述のためにかなり良好な近似を提供する。センサ電極 1 2 0 は、単位利得を有する増幅器 5 0 2 の逆相端子に信号 4 0 2 を提供する。増幅器 5 0 2 は、電流コンベア 4 0 5 の一部として含まれ、電流コンベア 4 0 5 は、更に、増幅器 5 0 2 の入力電流  $I_{in}$  の複製を作成するように構成された電流ミラー 5 0 4 , 5 0 6 を含む。入力電流  $I_{in}$  は、一般に、増幅器 5 0 2 の非逆相端子に基準電圧  $V_{t x}$  を印加することによって作成され、基準電圧  $V_{t x}$  は、逆相端子における電圧を制御してセンサ電極 1 2 0 の両端に電圧を印加する。入力電流  $n$  は、一般に、センサ電極 1 2 0 に対する入力装置の容量性影響を含む。電流ミラー 5 0 4 , 5 0 6 はそれぞれ、入力電流  $I_{in}$  を係数 A だけ変倍し、変倍電流 (A ·  $I_{in}$ ) が、混合器 4 1 0 に提供される。

#### 【 0 0 7 3 】

混合器 4 1 0 は、変倍電流を無線周波数 (RF) 周波数からほぼ直流 (DC) 値にダウンコンバートすることを可能にするスイッチ 5 0 8 , 5 1 0 を含む。一実施形態では、混合器 4 1 0 は、実質的に、スイッチ 5 0 8 , 5 1 0 に提供される制御信号に応じた極性スイッチング機能を行う。混合器 4 1 0 は、処理信号 4 1 2 をデルタシグマ変調器 4 1 5 の完全差動入力ノードに提供するように構成される。一般に、処理信号 4 1 2 は、デルタシグマ変調器 4 1 5 の正及び負入力ノードにそれぞれ提供された連続時間出力信号  $I_{in+}(t)$  ,  $I_{in-}(t)$  を含む。

#### 【 0 0 7 4 】

図示されたように、デルタシグマ変調器 4 1 5 は、電流コンベア 4 0 5 によって生成されたコモンモード電流を低減するように構成されたコモンモードフィードバック機構 5 1

10

20

30

40

50

2を含む。一般に、コモンモードフィードバック機構512は、入力ノード上の電圧を、コモンモード電圧 $V_{CM}$ を中心とする $V_{inp}(t)$ ,  $V_{inm}(t)$ に維持する働きをする。コモンモードフィードバック機構512は、利得 $G_m$ を有し、デルタシグマ変調器415の正及び負入力ノードと結合されたトランスコンダクタンス増幅器514を含む。幾つかの実施形態では、トランスコンダクタンス増幅器514は、A級増幅器又はAB級増幅器である。トランスコンダクタンス増幅器514は、更に、基準電圧 $V_{ref}$ を受け取るように構成される。幾つかの実施形態では、 $V_{ref}$ は、コモンモード電圧 $V_{CM}$ 又はほぼ $V_{DD}/2$ である。トランスコンダクタンス増幅器514の出力は、電流ミラー $I_{cmp+}(t)$ ,  $I_{cmp-}(t)$ によってそれぞれの正及び負入力ノードに提供される電流を制御する。コモンモードフィードバック機構512は、更に、それぞれの正及び負入力ノードと結合された電流ミラー $I_{cmn+}(t)$ ,  $I_{cmn-}(t)$ を含む。

#### 【0075】

幾つかの実施形態では、コモンモードフィードバック機構512は、更に、電流ミラー $I_{cmp+}(t)$ ,  $I_{cmp-}(t)$ ,  $I_{cmn+}(t)$ ,  $I_{cmn-}(t)$ の低周波数ノイズを軽減するように構成されたチョッピング回路516p, 516nを含む。例えば、チョッピング回路516p, 516nは、電流ミラーの(1/f)ノイズを除去するように構成されてもよいが、より高い周波数ノイズが、典型的には、それより後の段でデジタルフィルタ435によって除去される。幾つかの代替実施形態では、コモンモードフィードバック機構512が省略される。

#### 【0076】

コモンモードフィードバック機構512は、更に、入力ノード $V_{inp}(t)$ ,  $V_{inm}(t)$ 上の電圧がレール電圧に達するのを防ぐように構成されたキャパシタンスC2, C3を含む。キャパシタンスC2, C3は、混合器410から出力された電流( $I_{in+}(t)$ ,  $I_{in-}(t)$ として示された)によって表示されたコモンモードインピーダンスを示す。更に、キャパシタンスC2, C3は、電流コンペア405の出力が、所定の時間にデルタシグマ変調器415の2つの入力ノードの一方にのみ接続されるレシーバ401の機能を可能にする。

#### 【0077】

デルタシグマ変調器415は、更に、正及び負入力ノードと結合された積分器420を含む。図示されたように、積分器420は、キャパシタC0, C1を含み、デルタシグマ変調器415の正及び負入力ノード上の連続時間信号 $I_{in+}(t)$ ,  $I_{in-}(t)$ に基づいて積分信号422を生成するように構成された受動積分器である。リセットスイッチ518は、デルタシグマ変調器415をリセットして、デルタシグマ変調器415が、同じバイアス点から検出周期を始めることを保証するように構成される。積分器420は、シングルビット量子化器425の入力端子と結合される。量子化器425は、比較的大きいオーバーサンプリング比を達成するのに適した周波数を有するクロック信号(CLK)を受け取る。「大きい」オーバーサンプリング比の幾つかの非限定的な例は、500~2,000以上である。オーバーサンプリング比は、十分に大きいとき、量子化器425からの量子化ノイズを、デジタルフィルタ435(例えば、低域デジタルフィルタ)を使用して除去されるように形成される。

#### 【0078】

量子化器425の出力値D(及びその反転値)は、デルタシグマ変調器415のフィードバックデジタルアナログ変換器(DAC)430のスイッチ520p, 520nを制御するために使用される量子化信号427を表わす。このようにして、積分器420、量子化器425及びフィードバックDAC430は、デルタシグマ変調器415のフィードバックループを形成する。フィードバックDAC430は、更に、量子化信号427に基づいてデルタシグマ変調器415の正又は負入力ノードと選択的に結合される電流源 $I_{dfp}$ ,  $I_{dffn}$ を含む。例えば、 $V_{inp}(t)$ ,  $V_{inm}(t)$ の差を含む電圧信号が増大(又は拡大)するとき、量子化信号427は、電流源 $I_{dfp}$ を負入力ノードと接続させ、電流源 $I_{dffn}$ を正入力ノードと結合させる。このようにして、電流源 $I_{dfp}$ は、

10

20

30

40

50

電荷をキャパシタ C<sub>1</sub>の上電極にプッシュし、電圧  $V_{inm}(t)$  を高める。同様に、電流源  $I_{dfn}$  は、電荷をキャパシタ C<sub>0</sub> の上電極からプルし、電圧  $V_{inp}(t)$  が低下し、したがって  $V_{inp}(t)$  と  $V_{inm}(t)$  の間の電圧差が低減される。フィードバック DAC 430 は、更に、電流源  $I_{dfp}$ ,  $I_{dfn}$  が基準電圧  $V_{ref}$  と結合された「リセット」状態を含む。

#### 【0079】

一実施形態では、電流源  $I_{dfp}$ ,  $I_{dfn}$  は、25% のデューティサイクルを有するゼロ復帰 (RZ) 波形を生成し、これは、符号間干渉を減少させるのに有利でありうる。代替実施形態では、電流源  $I_{dfp}$ ,  $I_{dfn}$  は、異なるデューティサイクルを有する RZ 波形、又は非ゼロ復帰 (NRZ) 波形を提供しうる。更に、フィードバック DAC 430 は、抵抗実施態様や S-C-R 回路網実施態様などの代替実施態様を有しうるが、電流源  $I_{dfp}$ ,  $I_{dfn}$  の描かれた実施態様は、一般に、代替実施態様と比較されたときに少ない領域を必要とする。

10

#### 【0080】

前述された様々な技術を使用することにより、レシーバ 401 は、従来のレシーバ回路と比較されたときに、実質的に入力装置のための領域を節約できる。例えば、レシーバ 401 を含む AFE を実現するのに必要な領域は、従来のタッチ検出 AFE に必要な領域の約 4 分の 1 (25%)、又は従来の指紋検出 AFE に必要な領域の約 8 分の 1 (12.5%) でよい。したがって、入力検出性能を改善するために、所定の半導体領域（及びコスト）内により多くの AFE が含まれうる。あるいは、所定数の AFE は、従来の実施態様より少ない半導体領域を必要とする（かつコストを下げる）。

20

#### 【0081】

レシーバ 401 は、また、入力装置の改善された検出性能を提供する。検出フレームを取得するために使用できる期間が限られると仮定すると、所定の半導体領域内により多くのレシーバ 401 を含めて並列に動作させることができるので、レシーバ 401 は、より狭いシステム帯域幅を提供し、干渉性能を改善する。例えば、入力装置が 512 個のセンサ電極と 64 個の「従来」の AFE を含むと仮定する。検出フレームの取得に 2 ミリ秒 (ms) の期間が等しく割り当てられる場合、各 AFE は、検出に最大 250 マイクロ秒 ( $\mu s$ ) ( $2 \text{ ms} \times 64 / 512$ ) が利用できることになる。しかしながら、更に、レシーバ 401 が 4 : 1 の領域節約を提供すると仮定すると、64 個の「従来」の AFE が、256 個の AFE と置き換えられ、これは、検出に最大 1 ms ( $2 \text{ ms} \times 4 \times 64 / 512$ ) を利用できることになる。この検出時間の 4 : 1 の増大は、システム帯域幅の 4 : 1 の減少に対応でき、その結果、干渉性能が改善される。

30

#### 【0082】

更に、レシーバ 410 を実現する AFE は、検出フレームを取得するのに必要な合計時間を短縮でき、これにより、表示更新（例えば、高い表示解像度を可能にする）及び／又は他の処理機能により長い時間が可能になる。例えば、前の例と同じ検出パラメータを仮定し、250  $\mu s$  の検出時間を維持すると、検出フレームの取得に必要な合計時間は 500  $\mu s$  である。したがって、検出に割り当てられた 2 ms のうちの 1.5 ms を表示に戻すことができ、それにより、表示タイミングと信号整定の制約を減少できる。

40

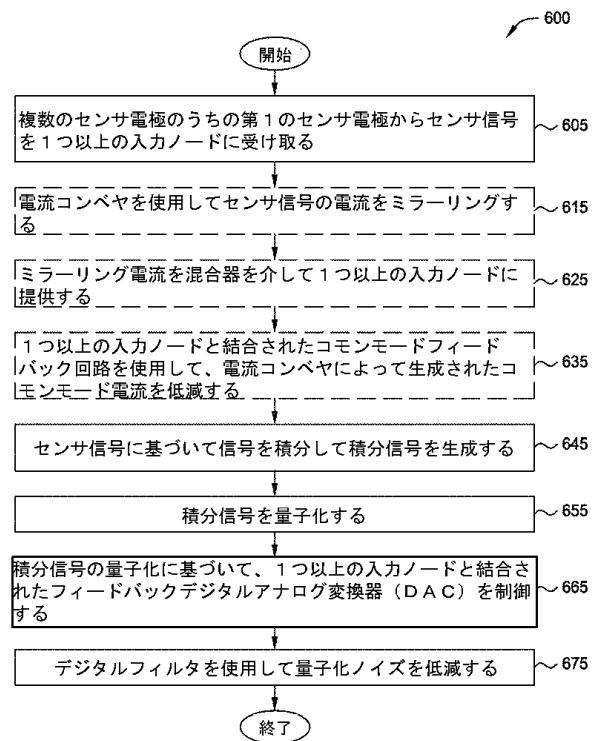

#### 【0083】

図 6 は、一実施形態による、センサ電極から受け取った信号を処理する典型的方法である。方法 600 は、一般に、図 4 に関して前述されたレシーバ 401 の実施形態と関連して実行される。

#### 【0084】

方法 600 は、ブロック 605 で始まり、複数のセンサ電極のうちの第 1 のセンサ電極から 1 つ以上の入力ノードにセンサ信号を受け取る。幾つかの実施形態では、1 つ以上の入力ノードは、レシーバ 401 のデルタシグマ変調器の入力ノードである。他の実施形態では、1 つ以上の入力ノードは、混合器を介してデルタシグマ変調器と結合された電流コンベアの入力ノードである。この場合、センサ信号は、電流コンベアに対するシングルエ

50

ンド入力でよい。

**【 0 0 8 5 】**

電流コンベアと混合器を含む実施形態では、省略可能なブロック 6 1 5 で、センサ信号の電流が、電流コンベアを使用して反射される。幾つかの実施形態では、反射電流は、電流コンベアに含まれる電流ミラーの利得に基づいて変倍される。省略可能なブロック 6 2 5 で、反射電流は、混合器を介して、デルタシグマ変調器の 1 つ以上の入力ノードに提供される。省略可能なブロック 6 3 5 で、1 つ以上の入力ノードと結合されたコモンモードフィードバック回路を使用して、電流コンベアによって作成されたコモンモード電流が低減される。

**【 0 0 8 6 】**

ブロック 6 4 5 で、センサ信号に基づく信号が、積分されて積分信号が生成される。ブロック 6 5 5 で、積分信号が量子化される。ブロック 6 6 5 で、積分信号の量子化に基づいて、1 つ以上の入力ノードと結合されたフィードバックデジタルアナログ変換器 (D A C) が制御される。ブロック 6 7 5 で、デルタシグマ変調器と結合されたデジタルフィルタを使用して量子化ノイズが低減される。方法 6 0 0 は、ブロック 6 7 5 の完了後に終わる。

10

**【 0 0 8 7 】**

したがって、本明細書に示された実施形態及び例は、本発明による実施形態とその特定の応用例を最もよく説明し、それにより当業者が本開示を作成し使用できるようにするために提示された。しかしながら、当業者は、以上の説明及び例が、単に説明と例のために提示されたことを理解するであろう。以上の説明は、網羅的でもなく、開示した厳密な形態に本開示を限定するものでもない。

20

**【 0 0 8 8 】**

以上のことから考慮して、本開示の範囲は、以下の請求項によって決定される。

**【 符号の説明 】**

**【 0 0 8 9 】**

1 0 0 , 4 0 0 入力装置

1 1 0 処理システム

1 2 0 センサ電極

4 1 5 デルタシグマ変調器

30

4 2 0 積分器

4 2 5 量子化器

4 3 0 フィードバックデジタルアナログ変換器 (D A C)

4 3 5 デジタルフィルタ

30

40

50

【図面】

【図 1】

【図 2】

FIG. 1

FIG. 2

【図 3】

FIG. 3

【図 4】

FIG. 4

10

20

30

40

50

【図 5】

【図 6】

FIG. 6

---

フロントページの続き

(72)発明者 ヤング, イーホン

アメリカ合衆国, カリフォルニア州, サンノゼ, マッケイ ドライヴ 1251

審査官 川口 貴裕

(56)参考文献 米国特許出願公開第2016/0126972(US, A1)

米国特許出願公開第2015/0109157(US, A1)

米国特許出願公開第2015/0145535(US, A1)

特開2013-055450(JP, A)

特開2014-045475(JP, A)

特開平11-122909(JP, A)

特開2011-124693(JP, A)

米国特許出願公開第2007/0236374(US, A1)

特表2008-542760(JP, A)

米国特許出願公開第2015/0268760(US, A1)

(58)調査した分野 (Int.Cl., DB名)

H03M 3/02

G06F 3/041