**Demande de brevet déposée pour la Suisse et le Liechtenstein**

Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

## Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

⑫ FASCICULE DE LA DEMANDE A3

11

624 820 G

②1 Numéro de la demande: 12646/78

⑦ Requérant(s):

Kabushiki Kaisha Daini Seikosha, Tokyo (JP)

② Date de dépôt: 12.12.1978

⑦2 Inventeur(s):

Takashi Ishida, Tokyo (JP)

⑩ Priorité(s): 12.12.1977 JP 52-149485

74 Mandataire:

Bovard & Cie., Bern

④2 Demande publiée le: 31.08.1981

56 Rapport de recherche au verso

54 Pièce d'horlogerie électronique, notamment montre-bracelet.

57 Une montre électronique comprend un oscillateur de base de temps (1) suivi d'un diviseur de fréquence (2) dont le rapport de division peut être modifié. Un étage supplémentaire ( $F_{N+1}$ ) permet de faire fonctionner une fois sur deux les autres étages selon un cycle très raccourci. Des moyens de mémorisation de la correction de cycle (6) et des moyens de correction de cycle ou de présélection de diviseur (5) établissent le rapport de division quelques unités au-dessus d'un rapport de division naturel. Des moyens de commande de rapport de division variable (4) actionnent des moyens de présélection une fois par cycle de l'étage complémentaire, et sont aptes à être rendus inopérants de façon que le rapport de division naturel puisse à volonté être rétabli. Des moyens d'affichage (3) fonctionnent en dépendance du cycle de l'étage de division supplémentaire ou du cycle de l'étage précédent, selon que le circuit de commande de correction (4) est en fonction ou est rendu inopérant.

# RAPPORT DE RECHERCHE RECHERCHENBERICHT

Demande de brevet No.:

Patentgesuch Nr.:

CH 12646/78

I.I.B. Nr.:

HO 13 609

## Documents considérés comme pertinents Einschlägige Dokumente

| Catégorie<br>Kategorie | Citation du document avec indication, en cas de besoin, des parties pertinentes.<br>Kennzeichnung des Dokuments, mit Angabe, soweit erforderlich, der massgeblichen Teile                                                                                                                                                                                         | Revendications concernées<br>Betrifft Anspruch Nr.                                          |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                        | <p><u>GB - A - 1 518 221</u> (K.K. SUWA SEIKOSHA)</p> <p>* page 3, lignes 3-49; figure 3 *</p> <p>---</p> <p><u>US - A - 3 922 844</u> (M. SAKAMOTO)</p> <p>* colonne 2, lignes 54-68; colonne 3, lignes 1-20; figure 1 *</p> <p>---</p> <p><u>DE - A - 2 233 800</u> (OMEGA LOUIS BRANDT &amp; FRERES)</p> <p>* page 4, lignes 3-12; figure 2 *</p> <p>-----</p> | 1                                                                                           |

| A                      |                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                           |

|                        |                                                                                                                                                                                                                                                                                                                                                                   | Domaines techniques recherchés<br>Recherchierte Sachgebiete (INT. CL. 2)<br><br>G 04 F 5/00 |

Catégorie des documents cités

Kategorie der genannten Dokumente:

X: particulièrement pertinent von besonderer Bedeutung

A: arrière-plan technologique technologischer Hintergrund

O: divulgation non-écrite nichtschriftliche Offenbarung

P: document intercalaire Zwischenliteratur

T: théorie ou principe à la base de l'invention der Erfindung zugrunde liegende Theorien oder Grundsätze

E: demande faisant interférence kollidierende Anmeldung

L: document cité pour d'autres raisons aus andern Gründen angeführtes Dokument

&: membre de la même famille, document correspondant Mitglied der gleichen Patentfamilie; übereinstimmendes Dokument

## Etendue de la recherche/Umfang der Recherche

Revendications ayant fait l'objet de recherches **ensemble**

Recherchierte Patentansprüche:

Revendications n'ayant pas fait l'objet de recherches

Nicht recherchierte Patentansprüche:

Raison:

Grund:

## REVENDICATIONS

1. Pièce d'horlogerie électronique, notamment montre-bracelet électronique, comprenant un oscillateur qui engendre un signal de temps standard, un diviseur de fréquence à rapport de division variable qui divise la fréquence dudit signal de temps standard, et un dispositif d'affichage qui reçoit et affiche une information de temps basée sur un signal issu dudit diviseur de fréquence, caractérisée en ce qu'elle comprend un circuit de présélection pour préétablir la position d'une partie dudit diviseur de fréquence, et des moyens à mémoire qui emmagasinent des signaux de préétablissement de cette partie de diviseur, la fréquence dudit oscillateur étant quelque peu supérieure à une fréquence standard déterminée pour un rapport de division naturel et ledit diviseur de fréquence ayant un étage diviseur de plus qu'un diviseur qui serait établi pour ce rapport de division naturel.

2. Pièce d'horlogerie électronique selon la revendication 1, caractérisée en ce que ledit diviseur de fréquence à rapport de division variable est agencé pour faire varier son rapport de division en dépendance desdits signaux de préétablissement emmagasinés dans lesdits moyens à mémoire, un circuit de commande de la fonction variable du diviseur étant apte également à prohiber cette fonction variable en provoquant, en réponse à une situation prédéterminée des signaux délivrés par lesdits moyens à mémoire, un fonctionnement naturel du diviseur de fréquence.

La présente invention concerne une pièce d'horlogerie électronique, notamment une montre-bracelet électronique, comprenant un oscillateur engendrant un signal de temps standard et un diviseur de fréquence à rapport de division variable.

Dans les montres électroniques classiques, afin de pouvoir tirer du diviseur une fréquence de précision, la fréquence même de l'oscillateur de temps standard était modifiée, par le biais de modifications intervenant sur des paramètres du circuit de l'oscillateur. Ces modifications de réglage étaient par exemple effectuées à l'aide d'un condensateur trimmer, qui est en fait un genre de condensateur variable. Toutefois, étant donné que les parties mécaniques qui constituent un condensateur trimmer manquent de fiabilité et que les paramètres du circuit de l'oscillateur ne peuvent guère se maintenir à des valeurs constantes, on rencontrait des difficultés dans l'établissement des circuits d'une telle montre classique. Dans d'autres montres électroniques classiques, comprenant un diviseur de fréquence à rapport de division variable, il n'y avait pas une relation directe entre la fréquence sortant du diviseur et la fréquence du signal de temps standard engendrée par l'oscillateur, et la connaissance de cette dernière ne pouvait pas certainement être tirée du signal sortant du diviseur.

Les publications antérieures GB-A-1518221 et US-A-3922844 présentent des pièces d'horlogerie électroniques qui comprennent un oscillateur engendrant un signal de temps standard et un diviseur de fréquence à rapport de division variable. Les agencements de mémoire mémorisent le rapport de division selon le cycle duquel le diviseur de fréquence doit fonctionner. Toutefois, dans ces pièces d'horlogerie antérieurement connues, la fréquence de l'oscillateur est de peu inférieure à une puissance de 2, et le nombre d'étages binaires du diviseur est égal à l'exposant de cette puissance de 2. Ainsi, le diviseur doit fonctionner avec un rapport de division quelque peu inférieur à son rapport de division naturel. Une fréquence supérieure à une fréquence standard déterminée pour un rapport de division naturel, puissance de 2, n'est pas envisagée car elle présente l'inconvénient de nécessiter un flip-flop ou étage de plus dans le diviseur, pour une utilité relativement peu grande, de sorte qu'on préférerait utiliser une fréquence inférieure à la fréquence naturelle. Il s'avère toutefois que certaines fonctions auxiliaires de la

montre ne sont pas possibles en l'absence d'un diviseur ne présentant pas une importante réserve de comptage, ce qui n'est pas le cas des diviseurs à rapport variable dans les pièces d'horlogerie divulguées par les publications antérieures citées. Ces pièces d'horlogerie antérieurement connues présentaient l'inconvénient précédemment cité selon lequel il n'y avait pas, et il ne pouvait pas y avoir de façon sûre, une relation directe entre la fréquence sortant du diviseur et la fréquence du signal de temps standard engendrée par l'oscillateur.

10 De toute façon, des documents constituant l'art antérieur ne fournissent pas un enseignement selon lequel des mesures seraient prises pour qu'un signal sortant d'un diviseur de fréquence à rapport de division variable puisse être en une relation directe et connue avec la fréquence du signal de temps standard engendrée par l'oscillateur, et cela tout particulièrement dans le cas où la fréquence engendrée par l'oscillateur est supérieure à la puissance de 2 qui lui est le plus voisine.

Le but de la présente invention est de fournir une montre électronique ne présentant pas les inconvénients susmentionnés et, 20 notamment, une montre électronique ayant un diviseur de fréquence à rapport de division variable dans laquelle il soit possible, d'une manière certaine, de connaître la fréquence d'oscillation de l'oscillateur en se basant sur la fréquence du signal délivré par le diviseur.

25 Conformément à l'invention, ce but est atteint par la présence des caractères énoncés dans les revendications annexées.

Accessoirement, des formes d'exécution de l'invention visent à faciliter l'établissement des circuits d'une montre électronique, à éviter la présence dans une montre d'un condensateur trimmer et à 30 fournir des moyens avantageux pour mémoriser le rapport de division dans les moyens à mémoire, ce dernier avantage étant obtenu par une forme d'exécution de l'invention dans laquelle le rapport de division du diviseur de fréquence est modifié par le biais de la position de commutateurs présents dans les moyens à 35 mémoire.

Le dessin annexé illustre, à titre d'exemple, une forme d'exécution de l'objet de l'invention; dans ce dessin:

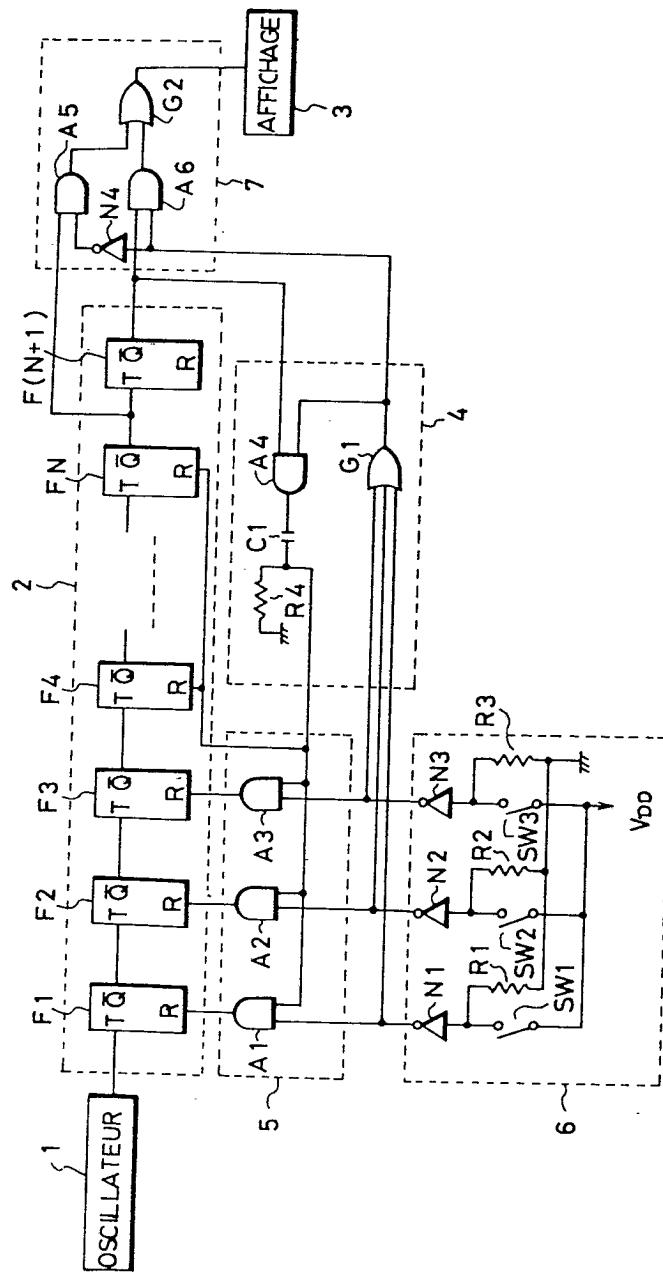

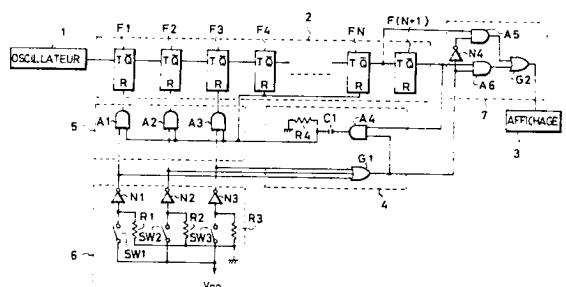

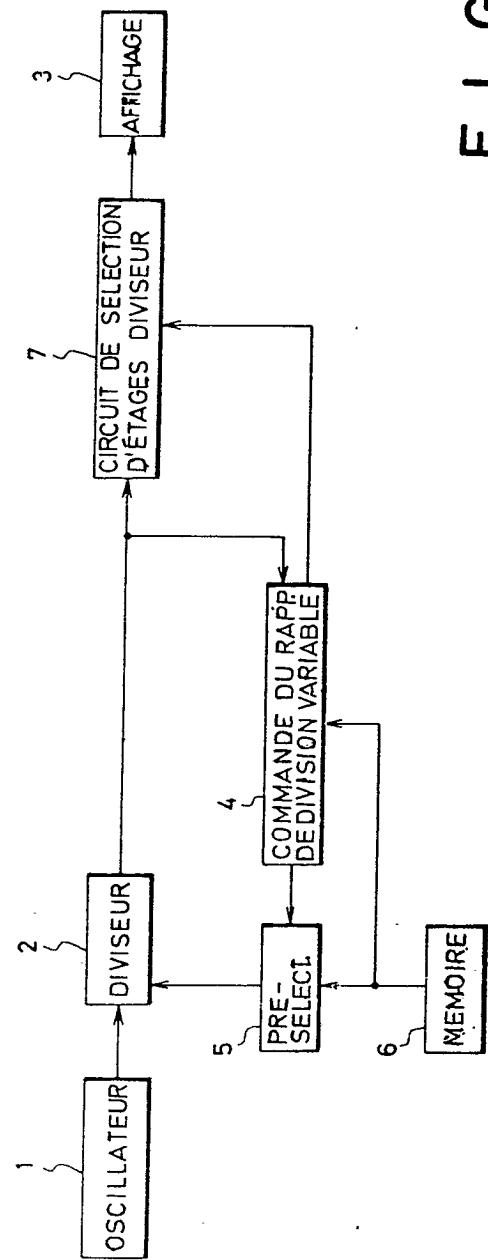

la fig. 1 est un schéma-bloc général d'une montre électronique conforme à l'invention,

40 la fig. 2 est un schéma plus détaillé d'une forme d'exécution selon laquelle le schéma de la fig. 1 peut être réalisé, et

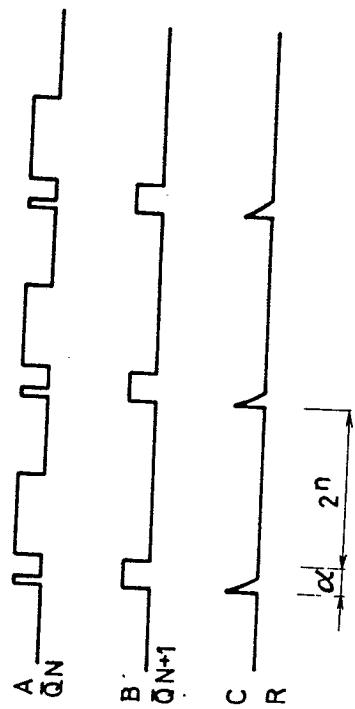

la fig. 3 est un diagramme des niveaux logiques en fonction du temps expliquant le fonctionnement des circuits représentés à la fig. 3.

45 A la fig. 1, on voit que la montre électronique en question comprend un diviseur de fréquence 2 qui divise la fréquence d'un signal délivré par un oscillateur de tension standard 1. Un circuit de présélection 5 est disposé pour permettre la présélection de certains étages déterminés du diviseur 2, et des moyens à mémoire 6 mémorisent les informations de présélection de ces étages du diviseur. Un circuit 4 de commande de rapport de division variable commande l'action de présélection du circuit de présélection 5 en réponse au signal de sortie même du diviseur de fréquence 2, et un circuit 7, de sélection d'étages du diviseur, sélectionne un étage ou un autre du diviseur de fréquence pour fournir la sortie de celui-ci, en dépendance d'un signal délivré par le circuit de commande de rapport de division variable 4. Enfin, un dispositif d'affichage 3 fournit un affichage d'informations horaires sur la base des signaux provenant du diviseur selon la sélection des étages de celui-ci 55 qu'effectue le circuit 7 de sélection d'étages du diviseur.

Il va sans dire que le dispositif d'affichage peut être l'un de ceux que l'on connaît classiquement, notamment un dispositif d'affichage à cristaux liquides comprenant des segments composants d'un caractère 8 ou encore d'autres dispositifs d'indication numériques ou analogiques.

La fig. 2 représente une forme d'exécution d'un circuit réalisant une montre électronique conforme à l'invention. Les moyens de mémoire 6 consistent en trois commutateurs  $SW_1$ ,  $SW_2$  et  $SW_3$ ,

trois résistances  $R_1$ ,  $R_2$  et  $R_3$  et trois inverseurs  $N_1$ ,  $N_2$  et  $N_3$ . Une extrémité de chacun des commutateurs  $SW_1$ - $SW_3$  est connectée à la source de tension positive  $V_{DD}$ , leur autre extrémité étant connectée respectivement à l'entrée d'un des trois inverseurs  $N_1$ - $N_3$  et connectées en même temps à la masse par l'intermédiaire des résistances respectives  $R_1$ - $R_3$ . Le circuit de présélection 5 comprend trois portes ET  $A_1$ ,  $A_2$  et  $A_3$ , à deux entrées, dont les premières entrées sont connectées respectivement aux sorties des trois inverseurs  $N_1$ ,  $N_2$  et  $N_3$ , et dont les secondes entrées sont connectées ensemble de façon à recevoir un même signal d'activation.

Le diviseur de fréquence 2 consiste en une série de flip-flops  $F_1$ - $F_N$  branchés en cascade, et en un flip-flop additionnel  $F_{(N+1)}$ , qui ne se trouve pas dans un circuit diviseur de fréquence classique de montre électronique. La sortie de l'oscillateur de signal de temps standard est connectée au premier étage diviseur  $F_1$  du diviseur et les sorties des trois portes ET  $A_1$ ,  $A_2$ ,  $A_3$  sont connectées respectivement à l'entrée de remise à zéro  $R$  des trois flip-flops  $F_1$ ,  $F_2$  et  $F_3$ . Les entrées  $R$ , de remise à zéro, des autres flip-flops ordinaires du diviseur,  $F_4$ - $F_N$ , sont connectées en commun et sont reliées à la connexion commune des secondes entrées des trois portes ET  $A_1$ - $A_3$ , en un point de circuit qui recevra les impulsions à certains moments, comme cela sera expliqué plus loin. On note que le flip-flop supplémentaire  $F_{(N+1)}$  a son entrée  $R$  de remise à zéro non connectée, ce qui signifie que ce flip-flop-là n'est pas remis à zéro.

On remarque à la fig. 2 que les sorties des flip-flops du diviseur qui actionnent le flip-flop suivant (ou qui délivrent l'information de sortie) sont les sorties  $Q$ . Si l'on part, comme cela est usuel, d'un état de repos où tous les flip-flops sont au niveau bas, on aura un fonctionnement dans lequel la première impulsion d'entrée fera passer tous les flip-flops de l'état 0 à l'état 1, les impulsions suivantes faisant progressivement basculer certains seulement de ces flip-flops, de la manière connue pour un compteur binaire.

Le circuit 4 de commande de rapport de division variable consiste en une porte OU  $G_1$ , une porte ET  $A_4$  et un circuit de différenciation comprenant un condensateur  $C_1$  et une résistance  $R_4$ . Les entrées de la porte OU  $G_1$  sont connectées respectivement aux sorties des trois inverseurs  $N_1$ - $N_3$ , et la sortie de cette porte OU est connectée à une entrée de la porte ET  $A_4$ , de même qu'à l'entrée d'une porte ET  $A_6$  et à l'entrée d'un inverseur  $N_4$  dans le circuit de sélection d'étages du diviseur. L'autre entrée de la porte ET  $A_4$  est connectée à la sortie  $Q$  de l'étage de flip-flop supplémentaire  $F_{(N+1)}$  du diviseur de fréquence 2, et la sortie de cette porte ET  $A_4$  est connectée au condensateur de différenciation  $C_1$  dont l'autre électrode est connectée à la masse par l'intermédiaire de la résistance de différenciation  $R_4$ . Le point de connexion de cette résistance  $R_4$  et du condensateur  $C_1$  est relié au point d'entrée commun où sont connectées les trois secondes entrées des portes  $A_1$ ,  $A_2$ ,  $A_3$  et les entrées  $R$  de remise à zéro des flip-flops  $F_4$ - $F_N$ .

Le circuit 7 de sélection d'étages du diviseur comprend l'inverseur  $N_4$  précédemment mentionné, la porte ET  $A_6$  également déjà mentionnée et une autre porte ET  $A_5$ , de même qu'une porte OU  $G_2$ . Une entrée de la porte ET 5 est connectée à la sortie de l'inverseur  $N_4$  dont l'entrée est connectée à la sortie de la porte OU  $G_1$  dans le circuit de commande de rapport de division variable (ou circuit de correction cyclique) 4. Comme la porte ET  $A_6$  a une entrée connectée directement à la sortie de la porte OU  $G_1$ , tandis que la porte ET  $A_5$  a une entrée connectée à ce même point par l'intermédiaire de l'inverseur  $N_4$ , on aura toujours soit la porte  $A_5$ , soit la porte  $A_6$  qui sera passante, tandis que l'autre sera bloquée. On note que l'autre entrée de la porte ET  $A_5$  est connectée à la sortie  $Q$  du flip-flop  $F_N$ , tandis que l'autre entrée de la porte ET  $A_6$  est connectée à la sortie  $Q$  du flip-flop supplémentaire  $F_{(N+1)}$ . Par ailleurs, les sorties des deux portes ET  $A_5$  et  $A_6$  sont connectées aux deux entrées de la porte OU  $G_2$ , dont la sortie délivre ainsi celui, sélectionné, des deux signaux apparaissant respectivement à la sortie  $Q$  du flip-flop  $F_N$  et à la sortie  $Q$  du flip-flop  $F_{(N+1)}$ .

Le fonctionnement du circuit de la fig. 2 s'explique en considérant la fig. 3. Sur cette dernière, la courbe A représente l'état du dernier flip-flop régulier, c'est-à-dire le flip-flop  $F_N$ , la courbe B représente l'état du flip-flop supplémentaire  $F_{(N+1)}$  et la courbe C 5 représente le signal différencié apparaissant sur le point de connexion du condensateur de différenciation  $C_1$  et de la résistance de différenciation  $R_4$ . Si l'on admet qu'il n'y a pas de remise à zéro par les entrées de remise à zéro  $R$  et si l'on admet que  $N = 15$ , la fréquence de sortie du diviseur, sur le flip-flop  $F_N$ , sera de 1 Hz, si la 10 fréquence de l'oscillateur de temps standard 1 est 32768 Hz, c'est-à-dire  $2^{15}$  Hz. Si l'on compte encore l'étage supplémentaire du diviseur de fréquence 2, on voit que celui-ci totalise seize étages flip-flops.

Au cours du fonctionnement du diviseur binaire 2, il arrive un 15 moment où la sortie du seizième flip-flop  $F_{(N+1)}$  passe du niveau bas au niveau haut (c'est-à-dire que le flip-flop lui-même passe de l'état 1 à l'état 0, puisque l'on considère la sortie inverse), et ce saut est transmis par la porte ET  $A_4$ , pour autant que celle-ci soit pourvue d'un niveau 1 sur son autre entrée. Ce saut est différencié 20 par le condensateur  $C_1$  et la résistance  $R_4$  et fournit une impulsion représentée par la courbe C de la fig. 3. Il va sans dire que l'on admet qu'au moins un des trois commutateurs  $SW_1$  est à l'état ouvert (non passant) de façon qu'au moins une des trois entrées de la porte OU  $G_1$  soit au niveau 1 et que l'autre entrée de la porte ET  $A_4$  soit ainsi au niveau 1. Dans ce cas, on a l'impulsion 25 différenciée représentée à la fig. 3C, laquelle est d'une durée suffisante pour remettre à zéro tous les flip-flops  $F_4$  à  $F_N$ , et ceux des trois flip-flops  $F_1$ ,  $F_2$  et  $F_3$  dont la porte ET correspondante  $A_1$ ,  $A_2$ ,  $A_3$  est à l'état passant. La durée de cette impulsion différenciée, suffisante pour remettre les flip-flops à zéro, est toutefois en tous les 30 cas inférieure à la période des impulsions sortant de l'oscillateur de temps standard 1.

A partir d'un état 0 de tous les flip-flops, une impulsion provoque le passage de tous les flip-flops à l'état 1. Immédiatement 35 après, l'impulsion différenciée fait revenir à l'état 0 presque tous les flip-flops, c'est-à-dire tous les flip-flops autres que le flip-flop supplémentaire  $F_{(N+1)}$  et que ceux des trois premiers flip-flops dont la porte correspondante  $A_1$ ,  $A_2$ ,  $A_3$  est à l'état non passant. En admettant que ces trois portes soient passantes, on aurait donc, 40 pour l'ensemble des flip-flops  $F_1$ - $F_N$ , un cycle de comptage d'un seul pas. Toutefois, puisque le seizième flip-flop,  $F_{(N+1)}$  n'est pas remis à zéro par l'impulsion différenciée, l'impulsion suivante va faire débuter un cycle de comptage normal. Celui-ci commencera par le basculement du seizième flip-flop, mais dans ce sens, celui-ci ne 45 provoque pas d'impulsions différencierées. Après comptage d'un cycle complet, le seizième flip-flop basculera à nouveau dans le sens provoquant une impulsion différenciée et on aura un retour à la 50 position définie par les trois commutateurs  $SW_1$ ,  $SW_2$  et  $SW_3$ . On comprend que lorsque l'un de ces commutateurs est à l'état passant, l'inverseur  $N_1$ ,  $N_2$ ,  $N_3$  correspondant délivre un niveau 0 sur sa sortie et la porte correspondante  $A_1$ ,  $A_2$ ,  $A_3$  est à l'état non passant. De ce fait, l'impulsion différenciée ne peut pas remettre à zéro le flip-flop correspondant  $F_1$ ,  $F_2$ ,  $F_3$ . Celui des flip-flops dont l'interrupteur correspondant est fermé manquera donc d'être remis 55 à zéro, c'est-à-dire qu'il sera laissé à l'état 1. Selon le cas, un nombre d'impulsions situé entre zéro et sept peut être nécessaire pour ramener ces trois flip-flops à l'état 0. On aura là un cycle extrêmement raccourci durant lequel le dernier flip-flop  $F_{(N+1)}$  est à l'état 1, comme le montre la fig. 3B. Ensuite viendra un cycle complet 60 durant lequel ce dernier flip-flop sera à l'état 0, comme le montre également la fig. 3B. Etant donné que l'on prélève la sortie du diviseur à la sortie de ce dernier flip-flop  $F_{(N+1)}$ , le cycle complet du diviseur se composera dudit cycle extrêmement raccourci et d'un cycle normal. La fig. 3A montre que le flip-flop  $F_N$  suit le cycle 65 normal pour moitié à l'état 1 et pour moitié à l'état 0, tandis qu'il effectue le cycle raccourci par une impulsion extrêmement brève de niveau 1 puis une période de niveau 0, correspondant à ce que commandent les trois interrupteurs  $SW_1$ ,  $SW_2$  et  $SW_3$ . Quant à la

fig. 3C, il faut noter qu'elle n'est pas tracée à l'échelle, en réalité les pointes sont d'une durée beaucoup plus faible.

On a vu que les commutateurs  $SW_1$ ,  $SW_2$  et  $SW_3$  commandent la présélection des flip-flops  $F_1$ ,  $F_2$ ,  $F_3$  respectivement, à l'état 1 au début du cycle très court qui commence par l'impulsion de différenciation. Comme ce cycle très court sera suivi d'un cycle normal, on voit que le cycle total, à la sortie du flip-flop supplémentaire, sera égal à  $2^{15} + 1 + X$ ,  $X$  étant donné par les commutateurs  $SW_1$ ,  $SW_2$  et  $SW_3$ , avec les pondérations respectives 1, 2, 4. Si par exemple la fréquence d'oscillation standard est de 32772 Hz (soit  $2^{15} + 1 + 3$ ) le code binaire à établir par les trois commutateurs sera «trois», ce qui amènera à avoir l'interrupteur  $SW_1$  fermé (passant), l'interrupteur  $SW_2$  fermé et l'interrupteur  $SW_3$  ouvert (non passant).

Puisque, même si aucun des trois premiers flip-flops n'est laissé à l'état 1, le cycle de comptage total serait supérieur d'un pas au cycle de comptage naturel, l'adjonction d'un code binaire, par exemple 3, provoque l'adjonction d'un pas de plus que le code (dans l'exemple 4 pas) en plus du cycle naturel. Ainsi, pour une fréquence qui est égale à 32768 Hz + 4, on ne doit prévoir que le code binaire 3 à l'aide des interrupteurs  $SW_1$ ,  $SW_2$ ,  $SW_3$ . Comme on vient de le voir,

le rapport de division du diviseur de fréquence 2 peut être changé en modifiant l'état des trois interrupteurs  $SW_1$ ,  $SW_2$ ,  $SW_3$  dans les moyens de mémorisation 6.

La montre en question présente encore une autre particularité intéressante. Il est en effet possible de connaître directement la fréquence d'oscillation. Lorsque les trois commutateurs  $SW_1$ ,  $SW_2$ ,  $SW_3$  des moyens à mémoire 6 sont tous à l'état fermé (passant), ce qui donnerait un rapport de division « $2^n + 1 + 7$ », la porte OU  $G_1$  délivre un niveau 0 à sa sortie et la porte ET  $A_4$  devient non passante, ce qui fait que l'impulsion différenciée ne se présente pas. En même temps, la porte ET  $A_6$  cesse d'être passante tandis que la porte ET  $A_5$  devient passante, ce qui fait que la sortie de la porte OU  $G_2$  délivre le signal provenant du flip-flop  $F_N$ , et non pas le signal provenant du flip-flop  $F_{(N+1)}$ . Dans ces conditions, le diviseur fonctionne d'une façon naturelle, sa sortie étant prélevée sur le quinzième étage. Les moyens qui augmentaient arbitrairement le cycle de division du diviseur sont en fait inhibés. Dans ce cas, puisque le diviseur 2 agit comme un diviseur ordinaire à rapport fixe, la période et/ou la fréquence d'oscillation pourra être calculée très exactement sur la base d'une mesure exacte de la période et/ou de la fréquence du signal sortant du diviseur 2. Le rapport entre les deux grandeurs sera très exactement de 32768.

F I G. 1

F I G. 3

FIG. 2