(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5464893号

(P5464893)

(45) 発行日 平成26年4月9日(2014.4.9)

(24) 登録日 平成26年1月31日(2014.1.31)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/786 (2006.01)H01L 29/78 618Z

H01L 29/78 618G

H01L 29/78 627G

H01L 29/78 617T

請求項の数 1 (全 40 頁)

(21) 出願番号 特願2009-101238 (P2009-101238)

(22) 出願日 平成21年4月17日 (2009.4.17)

(65) 公開番号 特開2009-278081 (P2009-278081A)

(43) 公開日 平成21年11月26日 (2009.11.26)

審査請求日 平成24年4月9日 (2012.4.9)

(31) 優先権主張番号 特願2008-109657 (P2008-109657)

(32) 優先日 平成20年4月18日 (2008.4.18)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 宮入秀和

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 大力浩二

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 恵木勇司

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 神保安弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

【請求項 1】

ゲート電極と、

前記ゲート電極上のゲート絶縁層と、

前記ゲート絶縁層に接し、非晶質構造の中に複数の結晶領域を含みチャネル形成領域を構成する第1の半導体層と、

一導電型を付与する不純物元素を含み、ソース領域及びドレイン領域を有する第2の半導体層と、を有し、

前記結晶領域は、前記ゲート絶縁層と前記第1の半導体層との界面から離れた位置から、前記第2の半導体層に向かって略放射状に成長した逆錐形状の構造を有し、

前記第1の半導体層は、二次イオン質量分析法によって計測される酸素濃度が、 $5 \times 10^{-18}$  atoms/cm<sup>3</sup> 以下であり、窒素濃度が  $1 \times 10^{-20}$  atoms/cm<sup>3</sup> 乃至  $1 \times 10^{-21}$  atoms/cm<sup>3</sup> であり、前記窒素濃度は、前記ゲート絶縁層と前記第1の半導体層との界面近傍において、二次イオン質量分析法によって計測されるピーク濃度が  $3 \times 10^{-20}$  atoms/cm<sup>3</sup> 乃至  $1 \times 10^{-21}$  atoms/cm<sup>3</sup> であり、該界面近傍から前記第2の半導体層に向かって減少しており、

前記結晶領域は単結晶を含み、

前記単結晶は双晶を含むことを特徴とする半導体装置。

【発明の詳細な説明】

10

20

**【技術分野】****【0001】**

本発明は、薄膜トランジスタおよびその作製方法、並びに該薄膜トランジスタを用いた半導体装置および表示装置に関する。

**【背景技術】****【0002】**

既に液晶ディスプレイの技術分野において、薄膜トランジスタ（以下、「TFT」とも記す。）は広く用いられている。TFTは電界効果トランジスタの一種であり、チャネルを形成する半導体が薄膜で形成されることからこのような命名がされている。現在では、当該半導体の薄膜としてアモルファスシリコン若しくは多結晶シリコンを用いてTFTを製造する技術が実用化されている。 10

**【0003】**

ところで、アモルファスシリコン若しくは多結晶シリコンと並び、微結晶シリコンと呼ばれる半導体材料が古くから知られており、電界効果トランジスタに関するものについての報告もある（例えば、特許文献1を参照）。しかしながら、今日に至るまで微結晶シリコンを用いたTFTは、アモルファスシリコントランジスタと多結晶シリコントランジスタの間に埋もれて実用化が遅れ、学会レベルで報告が散見されるのが実情である（例えば、非特許文献1を参照）。

**【0004】**

微結晶シリコン膜は、プラズマCVD法とよばれる方法により、原料ガスをプラズマ（弱電離プラズマ）により分解してガラス等の絶縁表面を有する基板上に形成することが可能であるが、非平衡状態で反応が進むため、結晶核生成や結晶成長を制御することが難しいと考えられていた。 20

**【0005】**

勿論、さまざまな研究が進められ、一部の説によると、微結晶シリコンの成長メカニズムは、まず、基板上に原子がランダムに配向したアモルファス（非晶質）相が成長し、その後、結晶の核成長がおこると考えられている（非特許文献2を参照）。この場合、微結晶シリコンの核成長が起こるときには、特異なシリコン-水素結合がアモルファス表面に観測されることから、微結晶シリコンの核密度を微結晶シリコン膜形成時の水素ガス濃度により制御できると考えられている。 30

**【0006】**

また、微結晶シリコン膜成長表面における酸素、窒素等の不純物元素が与える影響についても検討されており、不純物濃度を低減することで、微結晶シリコン膜の結晶粒が大粒径化し、欠陥密度（特に、荷電欠陥密度）が低減するという知見がある（非特許文献3を参照）。

**【0007】**

そして、TFTの動作特性を向上させるためには、微結晶シリコン膜の高純度化が必要であるという考え方があり、酸素、窒素及び炭素濃度を、それぞれ $5 \times 10^{-6} \text{ cm}^{-3}$ 、 $2 \times 10^{-8} \text{ cm}^{-3}$ 、 $1 \times 10^{-8} \text{ cm}^{-3}$ として実効移動度の向上を図ったものが報告されている（非特許文献4を参照）。また、プラズマCVD法による成膜温度を150とし、酸素濃度を $1 \times 10^{-6} \text{ cm}^{-3}$ にまで低減させ実効移動度の向上を図ったものが報告されている（非特許文献5を参照）。 40

**【先行技術文献】****【特許文献】****【0008】**

【特許文献1】米国特許第5,591,987号

**【非特許文献】****【0009】**

【非特許文献1】トシアキ・アライ（Toshiaki Araki）他、エス・アイ・ディー-07 ダイジェスト（S I D 07 D I G E S T）、2007、p.1370- 50

1373

【非特許文献2】ヒロユキ・フジワラ(Hirouki Fujiwara)他、ジャパンニーズ・ジャーナル・オブ・アプライド・フィジックス(Jpn. J. Appl. Phys.) Vol. 41、2002、p. 2821-2828

【非特許文献3】トシヒロ・カメイ(Toshihiro Kamei)他、ジャパンニーズ・ジャーナル・オブ・アプライド・フィジックス(Jpn. J. Appl. Phys.) Vol. 37、1998、p. L265-L268

【非特許文献4】C.-H. Lee 他、インターナショナル エレクトロン デバイス ミーティング テクニカル ダイジェスト(Int. Electron Devices Meeting Tech. Digest)、2006、p. 295-298

10

【非特許文献5】Czang-Ho Lee 他、アプライド・フィジックス・レターズ(Appl. Phys. Lett.)、89、2006、p. 252101

#### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0010】

しかしながら、アモルファスシリコン膜を形成した後に、金属材料でなる光熱変換層を設け、レーザ光を照射して微結晶シリコン膜を形成する方法では、結晶性を向上させることはできるが、生産性の観点から、レーザーアニールで作製される多結晶シリコン膜との間に優位性を見いだすことができない。

##### 【0011】

20

微結晶シリコンの核成長が起こるときには、特異なシリコン-水素結合がアモルファス表面に観測されるという知見は有益ではあるが、結局は核生成位置と核生成密度を直接的に制御することができない。

##### 【0012】

また、微結晶シリコン膜の高純度化を図り、不純物濃度を低減することで、微結晶シリコン膜の結晶粒が大粒径化し、欠陥密度(特に荷電欠陥密度)が低減したものが得られるとしても、それは単に微結晶シリコン膜の物性値が変化したことを示すのみで、必ずしもTFTなどの素子特性を改善するものではない。半導体素子は、半導体中を流れる電子又は正孔によるキャリアの流れを意図的に制御して動作させるものであるが、当該キャリアが流れる場所を考慮した上で、その場所における微結晶シリコン膜の膜質を改善できなければ意味がないからである。

30

##### 【0013】

そこで、本発明の一態様は、TFTに代表される半導体素子の動作特性が改善されるように、微結晶半導体膜若しくは結晶粒を含む半導体膜の膜質を制御することを目的とする。或いは、微結晶半導体膜若しくは結晶粒を含む半導体膜の形成過程を制御して、TFTに代表される半導体素子の特性向上を図ることを目的とする。更には本発明の一態様は、薄膜トランジスタのオン電流を向上させることを目的とする。

##### 【課題を解決するための手段】

##### 【0014】

40

本発明の一態様は、非晶質構造の中に複数の結晶領域を含む半導体層の作製において、該結晶領域が生成する起点となる結晶核の生成位置と生成密度を制御することで、該半導体層の膜質を制御することを要旨とする。本発明の一態様は、非晶質構造の中に複数の結晶領域を含む半導体層をチャネル形成領域とする薄膜トランジスタの作製において、該半導体層の該結晶領域が生成する起点となる結晶核の生成位置と生成密度を、キャリアが流れる領域に合わせて制御することを要旨とする。

##### 【0015】

非晶質構造の中に複数の結晶領域を含む半導体層は、微結晶半導体の生成が可能な混合比で半導体材料ガス(例えば、水素化シリコンガス、フッ化シリコンガス又は塩化シリコンガス)と希釈ガスを反応ガスとして用いて形成される。当該反応ガスは、酸素濃度を低減させた超高真空反応室内に導入され、所定の圧力を維持してグロー放電プラズマを生成

50

する。これにより反応室内に置かれた基板に被膜が堆積されるが、堆積初期段階においては結晶核の生成を妨害する不純物元素を反応室中に含ませて被膜の堆積を開始し、当該不純物元素の濃度を低減させていくことで結晶核を生成させ、その核を基に結晶領域を形成する。

【0016】

結晶核の生成を妨害する不純物としては、窒素若しくは窒化物が好ましい。半導体層に窒素を含ませる場合には、該半導体層において、S I M S によって計測される窒素濃度が  $1 \times 10^{20} \text{ cm}^{-3}$  乃至  $1 \times 10^{21} \text{ cm}^{-3}$  とする。該窒素濃度は、ゲート絶縁層と半導体層との界面近傍において、S I M S によって計測されるピーク濃度が  $3 \times 10^{20} \text{ cm}^{-3}$  乃至  $1 \times 10^{21} \text{ cm}^{-3}$  であり、該界面近傍から半導体層の厚さ方向に向けて窒素濃度を減少させることで、結晶領域の成長端となる核生成位置と核生成密度を制御する。

10

【0017】

なお、結晶核の生成を抑制する不純物元素において、シリコン中において、キャリアトラップを生成しない不純物元素（例えば、窒素）を選択する。一方、シリコンのダングリングボンドを生成する不純物元素（例えば、酸素）の濃度は低減させる。すなわち、酸素についてはS I M S によって計測される濃度を  $5 \times 10^{18} \text{ cm}^{-3}$  以下とすることが好ましい。

【0018】

本発明の一態様である薄膜トランジスタは、非晶質構造の中に複数の結晶領域を含む半導体層を有する。該半導体層上には、ソース領域及びドレイン領域を形成する一対の一導電型の不純物元素を含む半導体層が設けられている。

20

【0019】

なお、本明細書中において、濃度は二次イオン質量分析法（Secondary Ion Mass Spectrometry。以下、S I M S という。）によるものである。ただし、他の計測法が挙げられている場合など、特に記載がある場合にはこの限りではない。

【0020】

なお、本明細書中において、オン電流とは、トランジスタがオン状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。

30

【0021】

また、オフ電流とは、トランジスタがオフ状態のときに、ソース電極とドレイン電極の間に流れる電流をいう。例えば、N型のトランジスタの場合には、ゲート電圧がトランジスタの閾値電圧よりも低いときにソース電極とドレイン電極との間に流れる電流である。

【発明の効果】

【0022】

非晶質構造の中に複数の結晶領域を含む半導体層において、結晶領域の発生密度と発生位置を制御することができる。このような半導体層を薄膜トランジスタのチャネル形成領域として、オン電流の向上を図ることができる。

【図面の簡単な説明】

【0023】

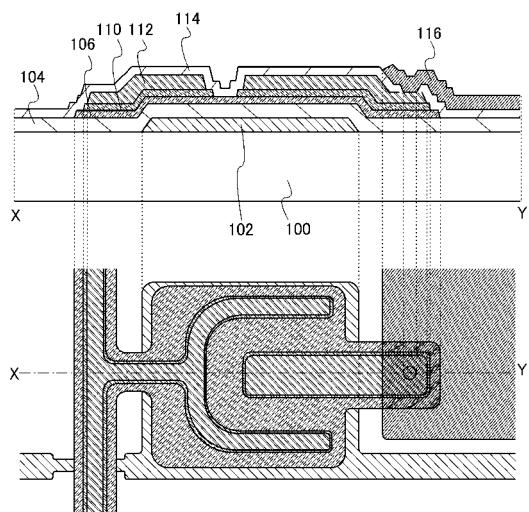

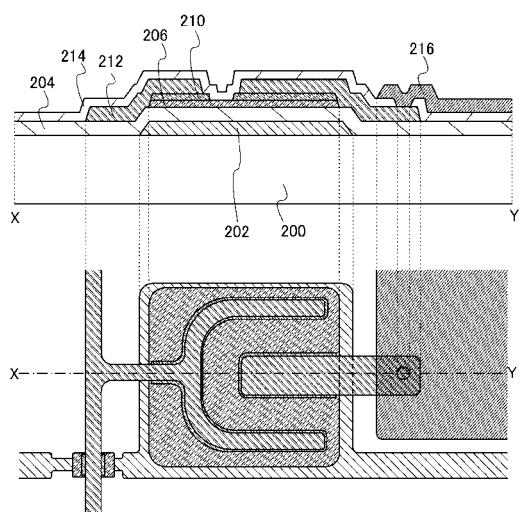

【図1】薄膜トランジスタの一例を説明する図。

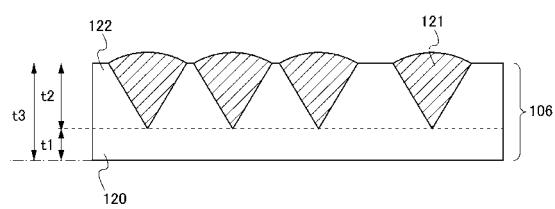

【図2】薄膜トランジスタが有する半導体層を説明する図。

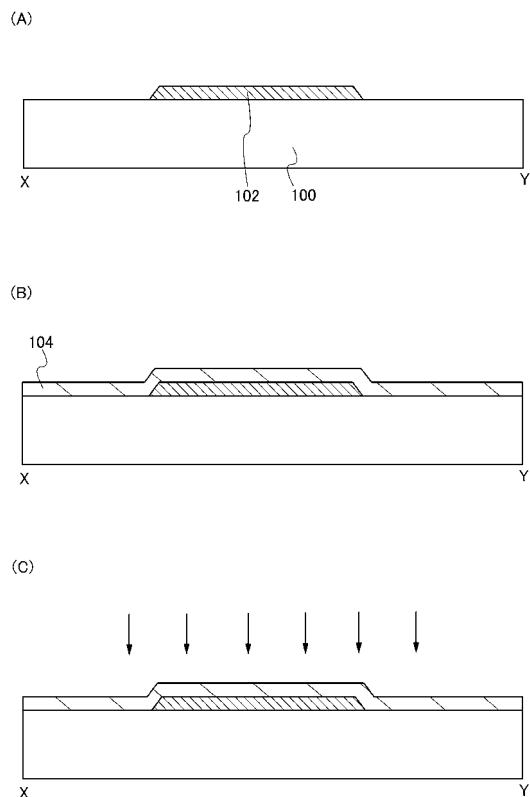

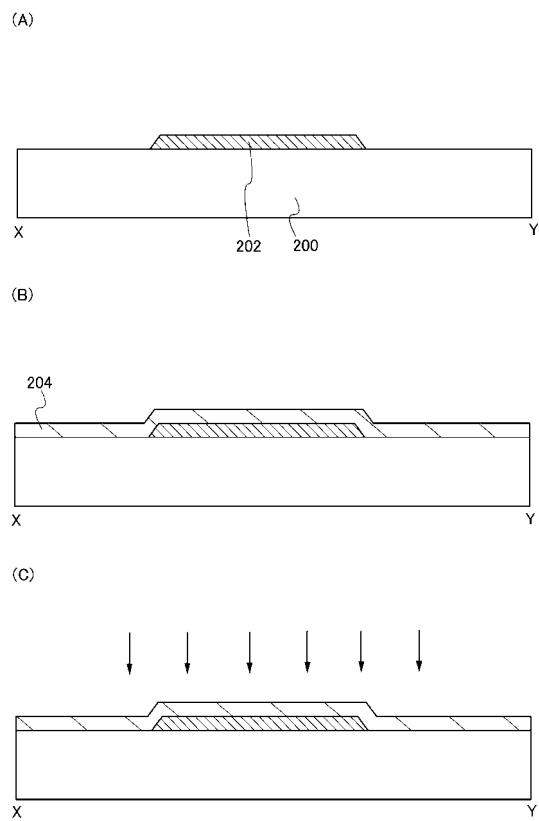

【図3】薄膜トランジスタの作製方法の一例を説明する図。

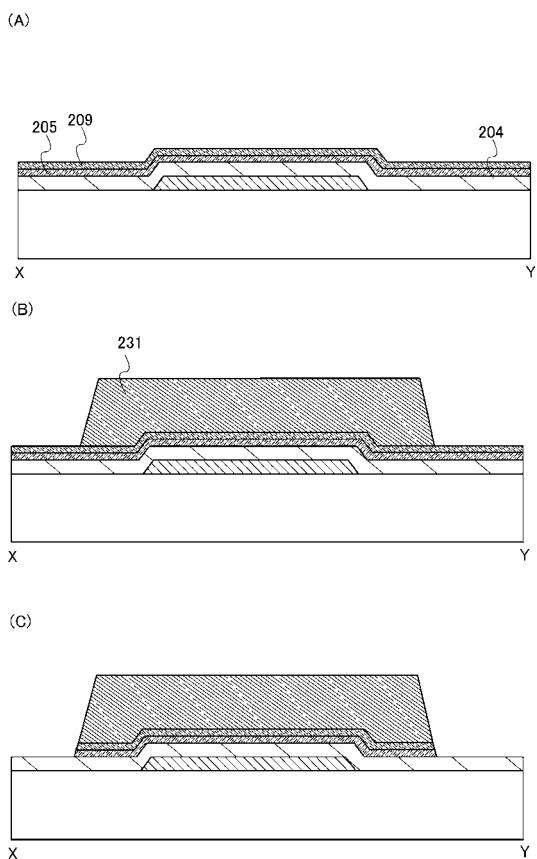

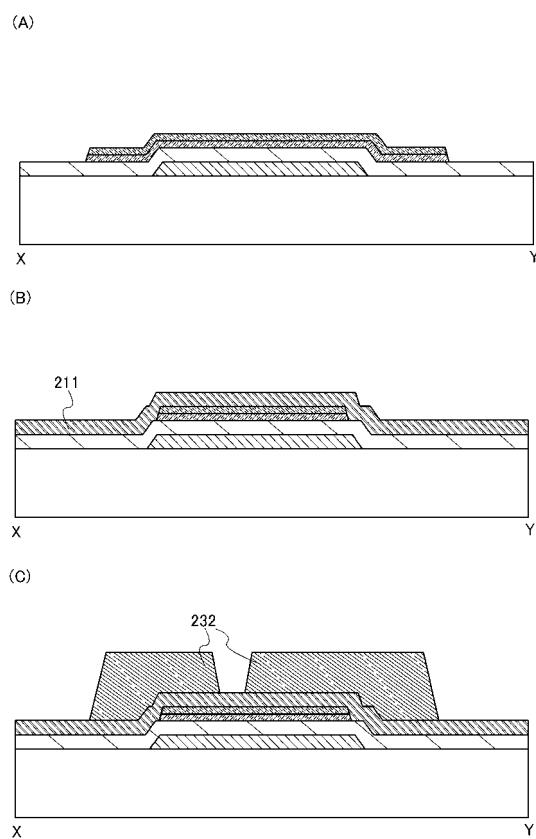

【図4】薄膜トランジスタの作製方法の一例を説明する図。

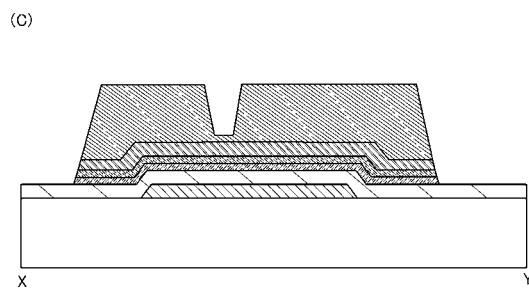

【図5】薄膜トランジスタの作製方法の一例を説明する図。

【図6】薄膜トランジスタの作製方法に適用可能な装置を説明する図。

【図7】薄膜トランジスタの作製方法の一例を説明する図。

【図8】薄膜トランジスタの作製方法の一例を説明する図。

【図9】薄膜トランジスタの作製方法の一例を説明する図。

40

10

20

30

40

50

【図10】薄膜トランジスタの作製方法の一例を説明する図。

【図11】薄膜トランジスタの作製方法の一例を説明する図。

【図12】薄膜トランジスタの一例を説明する図。

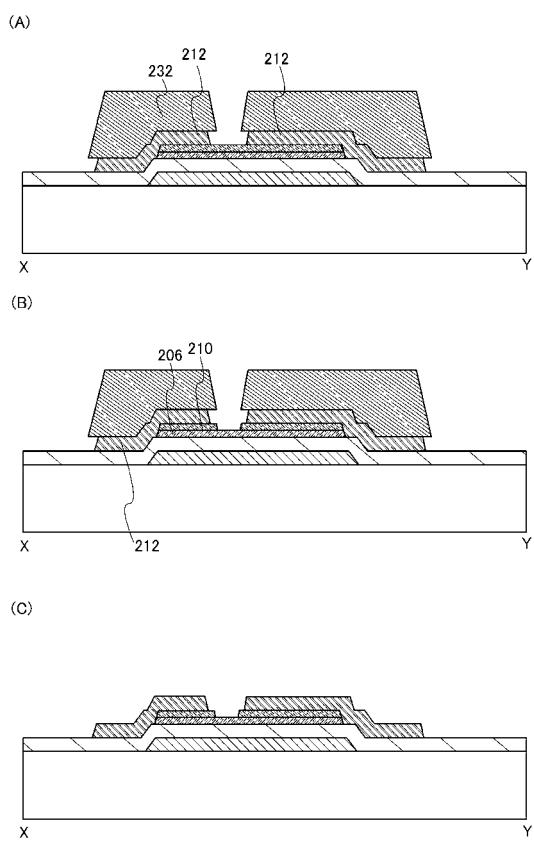

【図13】薄膜トランジスタの作製方法の一例を説明する図。

【図14】薄膜トランジスタの作製方法の一例を説明する図。

【図15】薄膜トランジスタの作製方法の一例を説明する図。

【図16】薄膜トランジスタの作製方法の一例を説明する図。

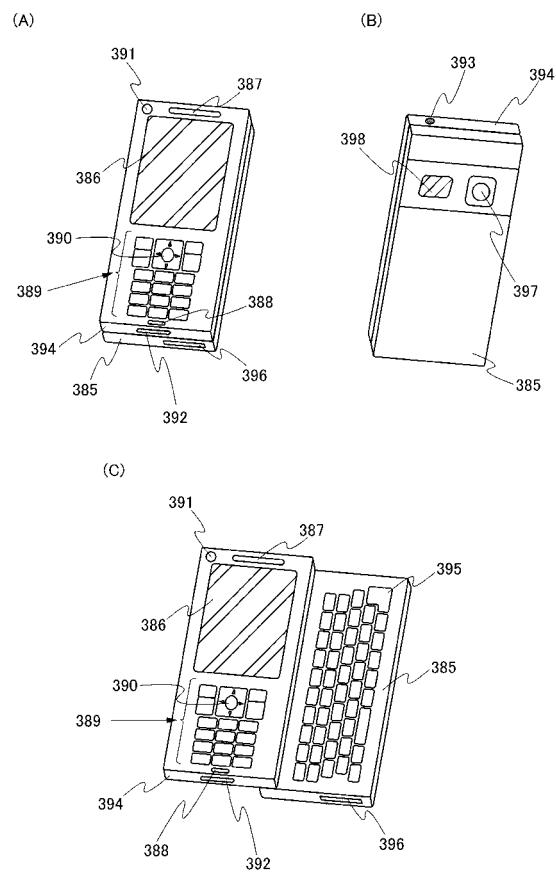

【図17】電子機器等を説明する図。

【図18】電子機器等を説明する図。

【図19】電子機器等を説明する図。

【図20】電子機器等を説明する図。

【図21】電子機器等を説明する図。

【図22】電子機器等を説明する図。

【図23】電子機器等を説明する図。

【図24】電子機器等を説明する図。

【発明を実施するための形態】

【0024】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。また、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0025】

(実施の形態1)

本実施の形態では、薄膜トランジスタの形態の一例について、図面を参照して説明する。

【0026】

図1は、本実施の形態にかかる薄膜トランジスタの上面図及び断面図を示す。図1に示す薄膜トランジスタは、基板100上にゲート電極層102を有し、ゲート電極層102を覆ってゲート絶縁層104を有し、ゲート絶縁層104上に接して半導体層106を有し、半導体層106上の一部に接してソース領域及びドレイン領域110を有する。また、ソース領域及びドレイン領域110上に接して配線層112を有する。配線層112はソース電極及びドレイン電極を構成する。配線層112上には、保護膜として機能する絶縁層114を有する。また、各層は所望の形状にパターン形成されている。

【0027】

なお、図1に示す薄膜トランジスタは、液晶表示装置の画素部に設けられる画素トランジスタに適用することができる。そのため、図示した例では、絶縁層114に開口部が設けられ、絶縁層114上に画素電極層116が設けられ、画素電極層116と配線層112の一方とが接続されている。

【0028】

また、ソース電極及びドレイン電極の一方は、U字型（またはコの字型、馬蹄型）の形状で設けられ、これがソース電極及びドレイン電極の他方を囲い込んでいる。ソース電極とドレイン電極との距離はほぼ一定に保たれている（図1を参照）。

【0029】

薄膜トランジスタのソース電極及びドレイン電極を上記した形状とすることで、該薄膜トランジスタのチャネル幅を大きくすることができます、電流量が増大する。また、電気的特性のばらつきを低減することができる。更には、作製工程におけるマスクパターンのずれによる信頼性の低下を抑制することができる。ただし、これに限定されず、ソース電極及

10

20

30

40

50

びドレイン電極の一方は必ずしもU字型でなくともよい。

【0030】

ここで、図1に示す薄膜トランジスタの主要な特徴の一つである半導体層106について説明する。半導体層106は、薄膜トランジスタのチャネル形成領域として機能する。半導体層106において、結晶質半導体により構成される結晶粒は、非晶質構造を含む半導体層中に離散して存在する(図2を参照)。

【0031】

半導体層106は、第1の領域120及び第2の領域122を有する。第1の領域120は、非晶質構造を有する。第2の領域122は、離散的に存在する複数の結晶粒121と、複数の結晶粒121の間に非晶質構造と、を有する。第1の領域120は、ゲート絶縁層104上に接して、ゲート絶縁層104との界面から厚さt1となる位置まで存在する。第2の領域122は、第1の領域120上に接して、厚さt2となる位置まで存在する。すなわち、結晶粒121の核生成位置は、ゲート絶縁層104の界面からt1の位置となるよう半導体層106の厚さ方向において制御されている。結晶粒121の核生成位置は、半導体層106に含まれる結晶化を抑制する不純物元素の濃度(例えば窒素濃度)により制御されている。

【0032】

結晶粒121の形状は、逆錐形である。ここで、逆錐形とは、(i)多数の平面から構成される面と、(ii)前記面の外周と前記面の外に存在する頂点とを結ぶ線の集合によって作られる立体的形状であって、該頂点が基板側に存在するものをいう。換言すると、後の実施例において説明するように、ゲート絶縁層104と半導体層106との界面から離れた位置から、半導体層106が堆積される方向に向けて、略放射状に成長した形状である。離散的に形成された結晶核のそれぞれが、半導体層の形成と共に結晶の方位に沿って成長することで、結晶粒は、結晶核を起点として結晶の成長方向と垂直な面の面内方向に拡がるように成長する。このように結晶粒を有することで、非晶質半導体よりもオン電流を高くすることができる。また、結晶粒121内には単結晶または双晶を含む。ここで、逆錐形の結晶粒121では、側面は面方位が揃っており、側面の断面形状は一直線である(図2を参照)。そのため、結晶粒121は複数の結晶を含んでいる形態よりも単結晶または双晶を含む形態に近いと考えられる。双晶を含む場合には、複数の結晶を含む場合と比較して、ダングリングボンドが少ないため欠陥数が少なく、オフ電流が小さい。また、複数の結晶を含む場合と比較して、粒界が少なく、オン電流が大きい。なお、結晶粒121には、複数の結晶を含んでいてもよい。

【0033】

なお、双晶とは、結晶粒界において異なる二つの結晶粒が極めて整合性よく接合していることをいう。即ち、結晶粒界において結晶格子が連続的に連なり、結晶欠陥等に起因するトラップ準位を非常に作りにくい構成となっている。従って、この様な結晶構造を有する領域は実質的に結晶粒界が存在しないと見なすことができる。

【0034】

なお、ここで結晶核の生成を抑制する不純物元素は、シリコン中にあってキャリアトラップを生成しない不純物元素(例えば、窒素)を選択する。一方、シリコンのダングリングボンドを生成する不純物元素(例えば酸素)の濃度は低減させる。従って、窒素濃度を低減せずに酸素濃度を低減させるとよい。具体的には、酸素についてはSIMSによって計測される濃度を $5 \times 10^{18} \text{ cm}^{-3}$ 以下とするとよい。

【0035】

また、半導体層106の形成は、ゲート絶縁層104の表面に窒素を存在させて行う。ここで、窒素濃度は核生成位置を決定するため重要である。窒素が存在するゲート絶縁層104上に半導体層106を形成すると、まず、第1の領域120が形成され、その後、第2の領域122が形成される。ここで、第1の領域120と第2の領域122との界面の位置は窒素濃度により決定される。SIMSによって計測される窒素の濃度が $1 \times 10^{20} \text{ cm}^{-3}$ 以上 $1 \times 10^{21} \text{ cm}^{-3}$ 以下、好ましくは $2 \times 10^{20} \text{ cm}^{-3}$ 以上 $7 \times$

10

20

30

40

50

$10^{20} \text{ cm}^{-3}$  以下のときに結晶核を生成し、第2の領域122が形成されることとなる。すなわち、結晶粒121の成長の起点となる結晶核の生成位置において、SIMSによって計測される窒素の濃度は  $1 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下、好ましくは  $2 \times 10^{20} \text{ cm}^{-3}$  以上  $7 \times 10^{20} \text{ cm}^{-3}$  以下となる。換言すると、逆錐形を有する結晶粒121の頂点における、SIMSによって計測される窒素の濃度は  $1 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下、好ましくは  $2 \times 10^{20} \text{ cm}^{-3}$  以上  $7 \times 10^{20} \text{ cm}^{-3}$  以下である。

#### 【0036】

また、窒素濃度は、ゲート絶縁層104との界面から離れるにつれて徐々に低下する。窒素濃度は、 $25 \text{ nm}$  以上  $40 \text{ nm}$  以下の範囲でゲート絶縁層104界面より一桁低下するとよく、好ましくは  $30 \text{ nm}$  以上  $35 \text{ nm}$  以下で一桁低下することが好ましい。

10

#### 【0037】

上記説明したように、結晶粒は離散的に存在する。結晶粒を離散的に存在させるためには、結晶の核生成密度を制御することが必要である。窒素濃度を上記の濃度範囲とすることで、結晶粒の核生成密度を制御し、結晶粒を離散的に存在せしめることが可能である。

#### 【0038】

なお、上記したように結晶核の生成を抑制する不純物元素が高濃度 (SIMSによって計測される不純物元素の濃度が概ね  $1 \times 10^{20} \text{ cm}^{-3}$  以上) に存在すると、結晶成長も抑制するため、半導体層106に含ませる窒素は、半導体層106の被形成面にのみ添加し、またはその膜の形成初期にのみ導入する。

20

#### 【0039】

次に、図1に示す薄膜トランジスタの作製方法について説明する。薄膜トランジスタではp型よりもn型の方が、キャリアの移動度が高い。また、同一の基板上に形成する薄膜トランジスタを全て同じ極性に統一すると、工程数を抑えることができるため好ましい。そのため、本実施の形態では、n型の薄膜トランジスタの作製方法について説明する。

#### 【0040】

まず、基板100上にゲート電極層102を形成する(図3(A)を参照)。

#### 【0041】

基板100としては、ガラス基板、セラミック基板の他、本作製工程の処理温度に耐えうる程度の耐熱性を有するプラスチック基板等を用いることができる。また、基板に透光性を要しない場合には、ステンレス合金等の金属の基板の表面に絶縁層を設けたものを用いてもよい。ガラス基板としては、例えば、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス若しくはアルミニケイ酸ガラス等の無アルカリガラス基板を用いるとよい。基板100がマザーガラスの場合には、第1世代(例えば、 $320 \text{ mm} \times 400 \text{ mm}$ )から第7世代( $1870 \text{ mm} \times 2200 \text{ mm}$ )、第8世代(例えば、 $2200 \text{ mm} \times 2400 \text{ mm}$ )のものを用いることができるのみならず、第9世代(例えば、 $2400 \text{ mm} \times 2800 \text{ mm}$ )、第10世代(例えば、 $2950 \text{ mm} \times 3400 \text{ mm}$ )のものをも用いることができる。

30

#### 【0042】

ゲート電極層102は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属又はこれらを主成分とする合金を用いて、単層で又は積層して形成することができる。アルミニウムを用いる場合には、タンタルを添加して合金化したAl-Ta合金を用いるとヒロックが抑制されるため、好ましい。また、ネオジムを添加して合金化したAl-Nd合金を用いると、抵抗を抑えつつヒロックの発生を抑制することができるため、更に好ましい。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体やAg-Pd-Cu合金を用いてもよい。例えば、アルミニウム層上にモリブデン層が積層された二層の積層構造、または銅層上にモリブデン層を積層した二層構造、または銅層上に窒化チタン層若しくは窒化タンタルを積層した二層構造とすることが好ましい。電気的抵抗が低い層上にバリア層として機能する金属層が積層されることで、電気的抵抗が低く、且つ金属層から半導体層への金属元素の拡

40

50

散を防止することができる。または、窒化チタン層とモリブデン層とから構成される二層の積層構造、または膜厚 50 nm のタンゲステン層と膜厚 500 nm のアルミニウムとシリコンの合金からなる層と膜厚 30 nm の窒化チタン層とを積層した三層の積層構造としてもよい。また、三層の積層構造とする場合には、第 1 の導電層のタンゲステン層に代えて窒化タンゲステン層を用いてもよいし、第 2 の導電層のアルミニウムとシリコンの合金からなる層に代えてアルミニウムとチタンの合金からなる層を用いてもよいし、第 3 の導電層の窒化チタン層に代えてチタン層を用いてもよい。例えば、Al - Nd 合金からなる層上にモリブデン層を積層して形成すると、耐熱性に優れ、且つ電気的に低抵抗な導電層を形成することができる。

## 【0043】

10

ゲート電極層 102 は、基板 100 上に、スパッタリング法又は真空蒸着法等を用いて上記した材料により導電層を形成し、該導電層上にフォトリソグラフィ法又はインクジェット法等によりレジストマスクを形成し、該レジストマスクを用いて導電層をエッチングして形成することができる。また、銀、金又は銅等の導電性ナノペーストをインクジェット法により基板上に吐出し、焼成することで形成することもできる。なお、上記の金属の窒化物層を、基板 100 と、ゲート電極層 102 との間に設けてもよい。ここでは、基板 100 上に導電層を形成し、フォトマスクを用いて形成したレジストマスクによりエッチングする。

## 【0044】

20

なお、ゲート電極層 102 の側面は、テーパー形状とすることが好ましい。ゲート電極層 102 上には、後の工程で半導体層及び配線層等を形成するので、段差の箇所における形成不良を防止するためである。ゲート電極層 102 の側面をテーパー形状にするためには、レジストマスクを後退させつつエッチングを行えばよい。例えば、エッチングガス（例えば、塩素ガス）に酸素ガスを含ませることでレジストを後退させつつエッチングを行うことが可能である。

## 【0045】

30

また、ゲート電極層 102 を形成する工程によりゲート配線（走査線）も同時に形成することができる。更には、画素部が有する容量線も同時に形成することができる。なお、走査線とは画素を選択する配線をいい、容量線とは画素の保持容量の一方の電極に接続された配線をいう。ただし、これに限定されず、ゲート配線及び容量配線の一方又は双方と、ゲート電極層 102 とは別に設けてもよい。

## 【0046】

30

次に、ゲート電極層 102 を覆ってゲート絶縁層 104 を形成する（図 3（B）を参照）。ゲート絶縁層 104 は、CVD 法又はスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン又は窒化酸化シリコンを用いて、単層で又は積層して形成することができる。また、ゲート絶縁層 104 は、高周波数（1 GHz 程度）のマイクロ波プラズマ CVD 装置を用いて形成することが好ましい。マイクロ波プラズマ CVD 装置を用いて高い周波数によりゲート絶縁層 104 を形成すると、ゲート電極と、ドレイン電極及びソース電極との間の耐圧を向上させることができるために、信頼性の高い薄膜トランジスタを得ることができる。また、ゲート絶縁層 104 を酸化窒化シリコンにより形成することで、トランジスタの閾値電圧の変動を抑制することができる。

40

## 【0047】

なお、本明細書中において、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法（RBS : Rutherford Backscattering Spectrometry）及び水素前方散乱法（HFS : Hydrogen Forward Scattering）を用いて測定した場合に、組成範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 1.5 原子%、シリコンが 2.5 ~ 3.5 原子%、水素が 0.1 ~ 1.0 原子% の範囲で含まれるものをいう。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS 及び HFS を用いて測定した場合に、組成範囲として酸素が

50

5～30原子%、窒素が20～55原子%、シリコンが25～35原子%、水素が10～30原子%の範囲で含まれるものという。ただし、酸化窒化シリコン又は窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

【0048】

なお、ゲート絶縁層104を窒化シリコンにより形成した場合には、ゲート絶縁層104上に薄い酸化窒化シリコン層を設けることで、薄膜トランジスタの動作初期に発生する劣化を抑制することができる。ここで、酸化窒化シリコン層は極薄く形成すればよく、1nm以上であればよい。好ましくは1nm以上3nm以下とする。

【0049】

次に、半導体層106の形成方法について説明する。半導体層106は、2nm以上60nm以下、好ましくは10nm以上30nm以下の厚さで形成するとよい。

【0050】

また、上記したように、半導体層106は、逆錐形の結晶粒を有する。逆錐形の結晶粒は、例えば、半導体層106の酸素濃度を低くし、窒素濃度を酸素濃度よりも高くし、窒素濃度が結晶粒の成長方向に従って低下していくことで、結晶粒の核生成を制御しつつ形成することができる。ここで、窒素濃度は酸素濃度よりも一桁以上高いことが好ましい。より具体的には、ゲート絶縁層104と半導体層106の界面における、SIMSによって計測される酸素の濃度を $5 \times 10^{18} \text{ cm}^{-3}$ 以下とし、窒素の濃度を $1 \times 10^{20} \text{ cm}^{-3}$ 以上 $1 \times 10^{21} \text{ cm}^{-3}$ 以下とする。また、酸素濃度を低く抑えて、窒素濃度を酸素濃度よりも高くして形成する。

【0051】

酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くする手段の一は、半導体層106の形成前に、ゲート絶縁層104の表面に多量の窒素を存在させることである。ゲート絶縁層104の表面に多量の窒素を存在させるためには、ゲート絶縁層104の形成後、半導体層106の形成前に、ゲート絶縁層104の表面を、窒素を含むガスによって生成されるプラズマにより処理すればよい。ここで、窒素を含むガスとしては、例えばアンモニア、窒素、塩化窒素、フッ化窒素等が挙げられる。

【0052】

または、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くする異なる手段の一は、半導体層106に接するゲート絶縁層104に、高濃度に窒素を含ませることである。従って、ゲート絶縁層104を窒化シリコンにより形成することである。なお、この手段については実施の形態2にて説明する。

【0053】

または、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くする異なる手段の一は、半導体層106の形成に用いる処理室（チャンバー）の内壁を、高濃度に窒素を含む膜により覆うことである。高濃度に窒素を含む材料として、例えば窒化シリコンが挙げられる。なお、処理室（チャンバー）内壁を覆う高濃度に窒素を含む膜は、ゲート絶縁層104と同時に形成してもよく、工程の簡略化ができるため好ましい。また、この場合には、ゲート絶縁層104の形成に用いる処理室（チャンバー）と半導体層106の形成に用いる処理室（チャンバー）が同一のものとなるため、製造装置が小型化される。なお、この手段については実施の形態3にて説明する。

【0054】

または、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くする異なる手段の一は、半導体層106の形成に用いるガスに含まれる酸素の濃度を低く抑え、窒素の濃度を高くすることである。このとき、窒素は半導体層106となる膜の形成初期に用いるガスにのみ供給し、または供給する窒素の量を減少させていけばよい。なお、この手段については実施の形態4にて説明する。

【0055】

なお、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くするには、上記手段のいず

10

20

30

40

50

れかを用いてもよいし、これらを組み合わせて用いてもよい。本実施の形態では、ゲート絶縁層104は窒化シリコン層上に酸化窒化シリコン層を積層した構造とし、ゲート絶縁層104をアンモニアに曝すことで、ゲート絶縁層104の表面に窒素を供給する。

【0056】

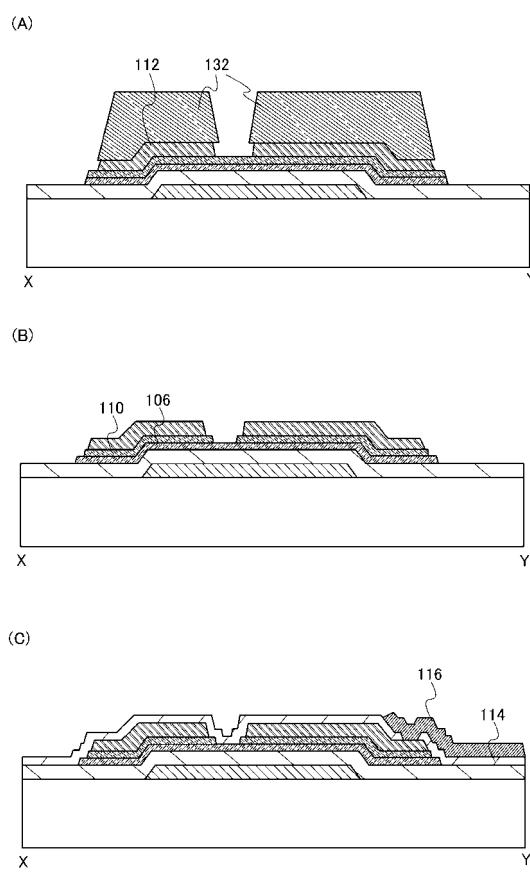

ここで、ゲート絶縁層104、半導体層106並びにソース領域及びドレイン領域110の形成の一例について詳細に説明する。これらの層はCVD法等を用いて形成する。また、ゲート絶縁層104は、窒化シリコン層上に酸化窒化シリコン層を設けた積層構造とする。このような構造とすることで、窒化シリコン層により基板中に含まれる電気的特性に影響を及ぼす元素（基板がガラスである場合にはナトリウム等の元素）が、半導体層106等に侵入することを防止することができる。図6は、これらを形成するに際して用いるCVD装置の模式図を示す。

【0057】

図6に示すプラズマCVD装置161は、ガス供給手段150及び排気手段151に接続されている。

【0058】

図6に示すプラズマCVD装置161は、処理室141と、ステージ142と、ガス供給部143と、シャワープレート144と、排気口145と、上部電極146と、下部電極147と、交流電源148と、温度制御部149と、を具備する。

【0059】

処理室141は剛性のある素材で形成され、内部を真空排気できるように構成されている。処理室141には、上部電極146と下部電極147が備えられている。なお、図6では、容量結合型（平行平板型）の構成を示しているが、異なる二以上の高周波電力を印加して処理室141の内部にプラズマを生成できるものであれば、誘導結合型など他の構成を適用してもよい。

【0060】

図6に示すプラズマCVD装置により処理を行う際には、所定のガスをガス供給部143から導入する。導入されたガスは、シャワープレート144を通って、処理室141に導入される。上部電極146と下部電極147に接続された交流電源148により、高周波電力が印加されて処理室141内のガスが励起されてプラズマが生成される。また、真空ポンプに接続された排気口145によって、処理室141内のガスが排気されている。また、温度制御部149によって、被処理物を加熱しながらプラズマ処理することができる。

【0061】

ガス供給手段150は、反応ガスが充填されるシリンド152、圧力調整弁153、ストップバルブ154、マスフローコントローラ155などで構成されている。処理室141内において、上部電極146と基板100との間には板状に加工され、複数の細孔が設けられたシャワープレートを有する。上部電極146に導入される反応ガスは、内部の中空構造を経て、この細孔から処理室141内に導入される。

【0062】

処理室141に接続される排気手段151には、真空排気と、反応ガスを流す場合において処理室141内を所定の圧力に保持するように制御する機能が含まれている。排気手段151の構成としては、バタフライバルブ156、コンダクタンスバルブ157、ターボ分子ポンプ158、ドライポンプ159などが含まれる。バタフライバルブ156とコンダクタンスバルブ157を並列に配置する場合には、バタフライバルブ156を閉じてコンダクタンスバルブ157を動作させることで、反応ガスの排気速度を制御して処理室141の圧力を所定の範囲に保つことができる。また、コンダクタンスの大きいバタフライバルブ156を開くことで高真空排気が可能となる。

【0063】

なお、処理室141を $10^{-5}$ Paよりも低い圧力まで超高真空排気する場合には、クライオポンプ160を併用することが好ましい。その他、到達真空度として超高真空まで

10

20

30

40

50

排気する場合には、処理室141の内壁を鏡面加工し、内壁からのガス放出を低減するためにベーキング用のヒータを設けても良い。

【0064】

なお、図6に示すように、処理室141の全体を覆って膜が形成（被着）されるようにプレコート処理を行うと、処理室141内壁に付着した不純物元素、または処理室141（チャンバー）内壁を構成する不純物元素の素子への混入を防止することができる。本実施の形態では、プレコート処理はシリコンを主成分とする膜を形成すればよく、例えば、非晶質シリコン等を形成すればよい。ただし、この膜には酸素が含まれないことが好ましい。

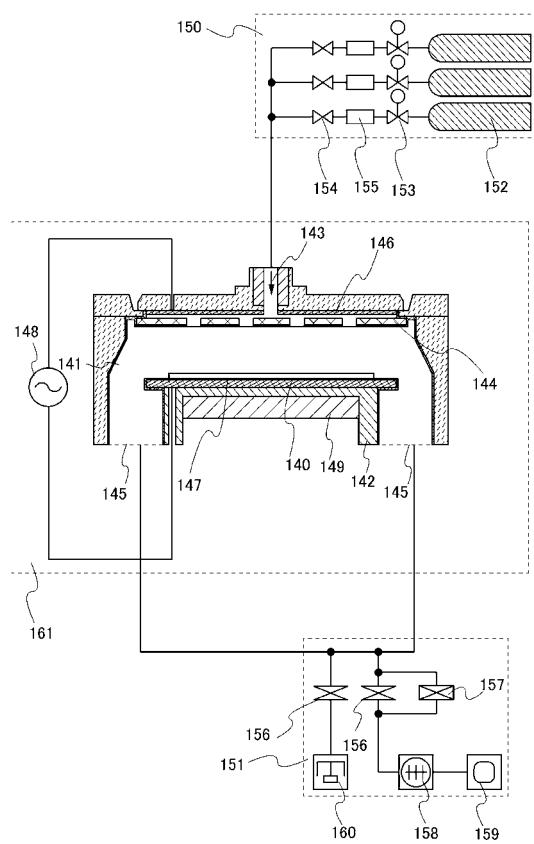

【0065】

ゲート絶縁層104の形成からドナーとなる不純物元素を含む半導体層109（一導電型を付与する不純物元素を含む半導体層ともいう。）の形成までについて、図7を参照して以下に説明する。なお、ゲート絶縁層104は、窒化シリコン層上に酸化窒化シリコン層を積層して形成する。

【0066】

まず、ゲート電極層102が形成された基板をCVD装置の処理室141内にて加熱し、窒化シリコン層を形成するための材料ガスを処理室141内に導入する（図7の予備処理A1）。ここでは、一例として、SiH<sub>4</sub>の流量を40sccm、H<sub>2</sub>の流量を500sccm、N<sub>2</sub>の流量を550sccm、NH<sub>3</sub>の流量を140sccmとして処理室141内に材料ガスを導入して流量を安定させ、処理室141内の圧力を100Pa、基板の温度を280とし、370Wでプラズマ放電を行うことで、約110nmの窒化シリコン層を形成する。その後、SiH<sub>4</sub>の導入のみを停止して数秒後にプラズマの放電を停止させる（図7のSiNx層形成B1）。処理室141内にSiH<sub>4</sub>が存在する状態でプラズマの放電を停止させると、シリコンを主成分とする粒状物又は粉状物が形成されてしまい、歩留まりを低下させる原因となるためである。なお、N<sub>2</sub>ガス及びNH<sub>3</sub>ガスはいずれか一方を用いればよく、これらを混合して用いる場合には流量を適宜調整するとよい。また、H<sub>2</sub>ガスの導入及び流量は適宜調整し、不要な場合には導入しなくてもよい。

【0067】

次に、窒化シリコン層の形成に用いた材料ガスを排気し、酸化窒化シリコン層の形成に用いる材料ガスを処理室141内に導入する（図7のガス置換C1）。ここでは、一例として、SiH<sub>4</sub>の流量を30sccm、N<sub>2</sub>Oの流量を1200sccmとし、材料ガスを導入して流量を安定させ、処理室141内の圧力を40Pa、基板の温度を280として50Wのプラズマ放電を行うことで、約110nmの酸化窒化シリコン層を形成する。その後、窒化シリコン層と同様に、SiH<sub>4</sub>の導入のみを停止し、その数秒後にプラズマの放電を停止させる（図7のSiO<sub>x</sub>N<sub>y</sub>層形成D1）。

【0068】

上記の工程により、ゲート絶縁層104を形成することができる。ゲート絶縁層104の形成後、基板100を処理室141から搬出する（図7のアンロードE1）。

【0069】

基板100を処理室141から搬出した後、処理室141に、例えばNF<sub>3</sub>ガスを導入し、処理室141内をクリーニングする（図7のクリーニング処理F1）。その後、処理室141に非晶質シリコン層を形成する処理を行う（図7のプレコート処理G1）。ここで、非晶質シリコン膜の成膜方法について説明する。成膜に用いる材料ガスを処理室141内に導入する。ここでは、一例として、SiH<sub>4</sub>の流量を280sccm、H<sub>2</sub>の流量を300sccmとして材料ガスを導入して安定させ、処理室141内の圧力を170Pa、基板の温度を280とし、60Wのプラズマ放電を行うことで、約150nmの半導体層を形成することができる。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub>の供給のみを停止し、その数秒後にプラズマの放電を停止させる。その後、これらのガスを排気し、ドナーとなる不純物元素を含む半導体層109の成膜に用いるガスを導入する。この処理により、処理室141の内壁に非晶質シリコン層が形成される。または

10

20

30

40

50

、窒化シリコンによりプレコート処理を行ってもよい。この場合の処理は、ゲート絶縁層 104 を形成する処理と同様である。その後、基板 100 を処理室 141 内に搬入する(図 7 のロード H1)。

【0070】

次に、ゲート絶縁層 104 の表面に窒素を供給する。ここでは、ゲート絶縁層 104 をアンモニアガスに曝すことによって窒素を供給する(図 7 のフラッシュ処理 I1)。また、アンモニアガスには水素を含ませてもよい。ここでは、一例として、処理室 141 内の圧力は概ね 20 Pa ~ 30 Pa、基板の温度は 280 とし、処理時間は 60 秒間とするよい。なお、本工程の処理ではアンモニアガスに曝すのみであるが、プラズマ処理を行ってもよい。その後、上記処理に用いたガスを排気し、半導体層 105 の形成に用いる材料ガスを処理室 141 内に導入する(図 7 のガス置換 J1)。

10

【0071】

次に、窒素が供給されたゲート絶縁層 104 上の全面に半導体層 105 を形成する。半導体層 105 は、後の工程でパターン形成されて半導体層 106 となるものである。まず、半導体層 105 の形成に用いる材料ガスを処理室 141 内に導入する。ここでは、一例として、SiH<sub>4</sub> の流量を 10 sccm、H<sub>2</sub> の流量を 1500 sccm として材料ガスを導入して流量を安定させ、処理室 141 内の圧力を 280 Pa、基板の温度を 280 とし、50 W のプラズマ放電を行うことで、約 50 nm の半導体層を形成する。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub> の導入のみを停止し、その数秒後にプラズマの放電を停止させる(図 7 の半導体層形成 K1)。その後、これらのガスを排気し、ドナーとなる不純物元素を含む半導体層 109 の形成に用いるガスを導入する(図 7 のガス置換 L1)。なお、これに限定されず、ガスの置換は必ずしも行わなくてよい。

20

【0072】

上記の例において、半導体層 105 の形成に用いられる材料ガスでは、SiH<sub>4</sub> の流量に対する H<sub>2</sub> の流量を 150 倍としている。そのため、シリコンは徐々に堆積される。

【0073】

本実施の形態におけるゲート絶縁層 104 の表面には窒素が供給されている。上記したように、窒素はシリコンの結晶核の生成を抑制する。そのため、半導体層 105 の形成の初期段階ではシリコンの結晶核が生成されない。半導体層 105 の形成初期段階で形成されるこの層が、図 2 に示す第 1 の領域 120 となる。半導体層 105 は一の条件により形成するため、第 1 の領域 120 と第 2 の領域 122 は同一の条件により形成されるものである。上記したようにゲート絶縁層 104 の表面に窒素を供給し、該表面上に半導体層 105 を形成することで、窒素を含む半導体層(図 2 に示す第 1 の領域 120)が形成される。半導体層 105 において、窒素の濃度はゲート絶縁膜との界面から離れるにつれて低下し、窒素の濃度が一定の値以下となると、結晶核が生成される。その後、その結晶核が成長し、結晶粒 121 が形成される。

30

【0074】

次に、半導体層 105 上の全面にドナーとなる不純物元素を含む半導体層 109 を形成する。ドナーとなる不純物元素を含む半導体層 109 は、後の工程でパターン形成されてソース領域及びドレイン領域 110 となるものである。まず、ドナーとなる不純物元素を含む半導体層 109 の形成に用いる材料ガスを処理室 141 内に導入する。ここでは、一例として、SiH<sub>4</sub> の流量を 100 sccm、PH<sub>3</sub> を H<sub>2</sub> により 0.5 vol % まで希釈した混合ガスの流量を 170 sccm として材料ガスを導入して流量を安定させ、処理室 141 内の圧力を 280 Pa、基板の温度を 280 とし、60 W のプラズマ放電を行うことで、約 50 nm の半導体層を形成する。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub> の導入のみを停止し、その数秒後にプラズマの放電を停止させる(図 7 の不純物半導体層形成 M1)。その後、これらのガスを排気する(図 7 の排気 N1)。

40

【0075】

以上説明したように、ドナーとなる不純物元素を含む半導体層 109 までを形成することができる(図 4 (A) を参照)。

50

## 【0076】

次に、ドナーとなる不純物元素を含む半導体層109上に導電層111を形成する。

## 【0077】

導電層111は、アルミニウム、銅、チタン、ネオジム、スカンジウム、モリブデン、クロム、タンタル若しくはタングステン等により単層で、又は積層して形成することができる。または、ヒロック防止元素が添加されたアルミニウム合金（ゲート電極層102に用いることができるAl-Nd合金等）により形成してもよい。または、ドナーとなる不純物元素を添加した結晶性シリコンを用いてもよい。ドナーとなる不純物元素が添加された結晶性シリコンと接する側の層を、チタン、タンタル、モリブデン、タングステン又はこれらの元素の窒化物により形成し、その上にアルミニウム又はアルミニウム合金を形成した積層構造としても良い。更には、アルミニウム又はアルミニウム合金を、チタン、タンタル、モリブデン、タングステン又はこれらの元素の窒化物で挟んだ積層構造としてもよい。例えば、導電層111として、アルミニウム層をモリブデン層で挟んだ三層の積層構造とするとよい。

## 【0078】

導電層111は、CVD法、スパッタリング法又は真空蒸着法を用いて形成する。また、導電層111は、銀、金又は銅等の導電性ナノペーストを用いてスクリーン印刷法又はインクジェット法等を用いて吐出し、焼成することで形成しても良い。

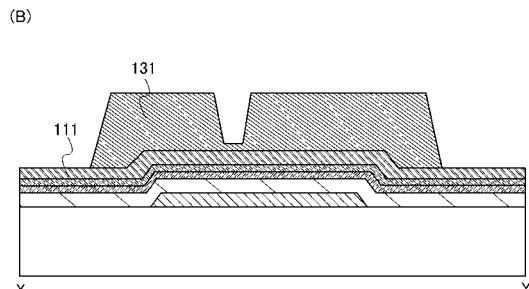

## 【0079】

次に、導電層111上に第1のレジストマスク131を形成する（図4（B）を参照）。第1のレジストマスク131は厚さの異なる二の領域を有し、多階調マスクを用いて形成することができる。多階調マスクを用いることで、使用するフォトマスクの枚数が低減され、作製工程数が減少するため好ましい。本実施の形態において、半導体層105、バッファ層107、ドナーとなる不純物元素を含む半導体層109、及び導電層111のパターンを形成する工程と、ソース領域とドレイン領域を分離する工程において、多階調マスクを用いて形成したレジストマスクを用いることができる。

## 【0080】

多階調マスクとは、多段階の光量で露光を行うことが可能なマスクであり、代表的には、露光領域、半露光領域及び未露光領域の3段階の光量で露光を行う。多階調マスクを用いることで、一度の露光及び現像工程によって、複数（代表的には二種類）の厚さを有するレジストマスクを形成することができる。そのため、多階調マスクを用いることで、フォトマスクの枚数を削減することができる。

## 【0081】

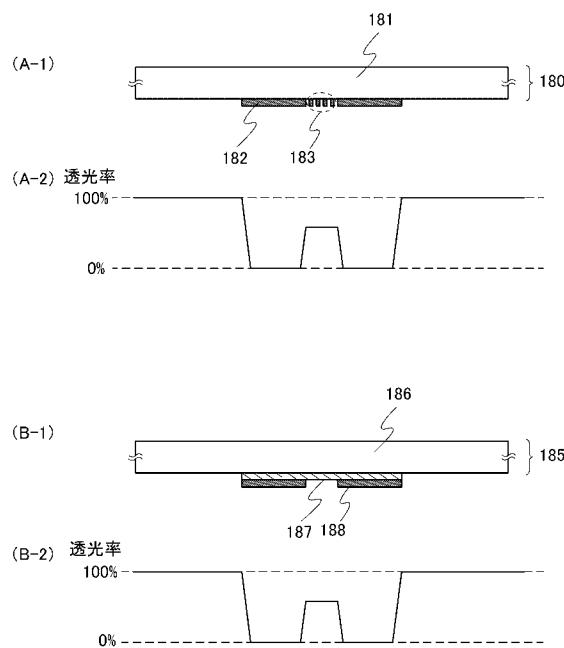

図8（A-1）及び図8（B-1）は、代表的な多階調マスクの断面図を示す。図8（A-1）にはグレートーンマスク180を示し、図8（B-1）にはハーフトーンマスク185を示す。

## 【0082】

図8（A-1）に示すグレートーンマスク180は、透光性を有する基板181上に遮光膜により形成された遮光部182、及び遮光膜のパターンにより設けられた回折格子部183で構成されている。

## 【0083】

回折格子部183は、露光に用いる光の解像度限界以下の間隔で設けられたスリット、ドット又はメッシュ等を有することで、光の透過量を制御する。なお、回折格子部183に設けられるスリット、ドット又はメッシュは周期的なものであってもよいし、非周期的なものであってもよい。

## 【0084】

透光性を有する基板181としては、石英等を用いることができる。遮光部182及び回折格子部183を構成する遮光膜は、金属あるいは金属酸化物を用いて形成すればよく、好ましくはクロム又は酸化クロム等により設けられる。

## 【0085】

グレートーンマスク 180 に露光するための光を照射した場合、図 8 (A - 2) に示すように、遮光部 182 に重畳する領域における透光率は 0 % となり、遮光部 182 又は回折格子部 183 が設けられていない領域における透光率は 100 % となる。また、回折格子部 183 における透光率は、概ね 10 ~ 70 % の範囲であり、回折格子のスリット、ドット又はメッシュの間隔等により調整可能である。

【0086】

図 8 (B - 1) に示すハーフトーンマスク 185 は、透光性を有する基板 186 上に半透光膜により形成された半透光部 187、及び遮光膜により形成された遮光部 188 で構成されている。

【0087】

半透光部 187 は、MoSiN、MoSi、MoSiO、MoSiON、CrSi 等の膜を用いて形成することができる。遮光部 188 は、グレートーンマスクの遮光膜と同様の金属あるいは金属酸化物を用いて形成すればよく、好ましくはクロム又は酸化クロム等により設けられる。

【0088】

ハーフトーンマスク 185 に露光するための光を照射した場合、図 8 (B - 2) に示すように、遮光部 188 に重畳する領域における透光率は 0 % となり、遮光部 188 又は半透光部 187 が設けられていない領域における透光率は 100 % となる。また、半透光部 187 における透光率は、概ね 10 ~ 70 % の範囲であり、形成する材料の種類又は形成する膜厚等により、調整可能である。

10

【0089】

多階調マスクを用いて露光して現像を行うことで、膜厚の異なる領域を有するレジストマスクを形成することができる。

【0090】

次に、第 1 のレジストマスク 131 を用いて半導体層 105、ドナーとなる不純物元素を含む半導体層 109、及び導電層 111 をエッティングする。この工程により、半導体層 105、ドナーとなる不純物元素を含む半導体層 109 及び導電層 111 を素子毎に分離する(図 4 (C) を参照)。

20

【0091】

ここで、第 1 のレジストマスク 131 を後退させて第 2 のレジストマスク 132 を形成する。レジストマスクの後退には、酸素プラズマによるアッシングを用いればよい。

30

【0092】

次に、第 2 のレジストマスク 132 を用いて導電層 111 をエッティングし、配線層 112 を形成する(図 5 (A) を参照)。配線層 112 は、ソース電極及びドレイン電極を構成する。導電層 111 のエッティングは、ウエットエッティングを用いることが好ましい。ウエットエッティングにより、導電層が選択的にエッティングされ、導電層の側面は第 2 のレジストマスク 132 よりも内側に後退し、配線層 112 が形成される。従って、配線層 112 の側面と、エッティングされたドナーとなる不純物元素を含む半導体層 109 の側面は一致せず、配線層 112 の側面の外側に、ソース領域及びドレイン領域 110 の側面が形成されることになる。配線層 112 は、ソース電極及びドレイン電極のみならず信号線としても機能する。ただし、これに限定されず、信号線と配線層 112 とは別に設けてよい。

40

【0093】

次に、第 2 のレジストマスク 132 が形成された状態で、ドナーとなる不純物元素を含む半導体層 109 をエッティングして、ソース領域及びドレイン領域 110 を形成する(図 5 (B) を参照)。

【0094】

次に、第 2 のレジストマスク 132 が形成された状態で、ドライエッティングを行うとい。ここで、ドライエッティングの条件は、露出している半導体層 106 にダメージが入らず、且つ半導体層 106 に対するエッティングレートが低い条件を用いる。つまり、露出し

50

ている半導体層 106 の表面にほとんどダメージを与えることなく露出している半導体層 106 の膜厚がほとんど減少しない条件を用いる。エッティングガスとしては、 $\text{Cl}_2$  ガス等を用いることができる。また、エッティング方法については特に限定はなく、ICP 方式、CCP 方式、ECR 方式、反応性イオンエッティング (RIE: Reactive Ion Etching) 方式等を用いることができる。

#### 【0095】

ここで、用いることのできるドライエッティング条件の一例として、 $\text{Cl}_2$  ガスの流量を 100 sccm、チャンバー内の圧力を 0.67 Pa、下部電極温度を -10 とし、上部電極のコイルに 2000 W の RF (13.56 MHz) 電力を投入してプラズマを生成し、基板 100 側には電力を投入せず 0 W として (すなわち、無バイアスとして)、30 秒間のエッティングを行う。チャンバー内壁の温度は約 80 とすることが好ましい。

#### 【0096】

次に、第 2 のレジストマスク 132 が形成された状態でプラズマ処理を行うとよい。ここで、プラズマ処理は、例えば水プラズマにより行うとよい。

#### 【0097】

水プラズマ処理は、反応空間に水蒸気 ( $\text{H}_2\text{O}$  蒸気) に代表される、水を主成分とするガスを導入し、プラズマを生成して、行うことができる。水プラズマにより第 2 のレジストマスク 132 を除去することができる。また、水プラズマ処理、あるいは、大気に曝した後に水プラズマ処理を行うことで、酸化膜が形成されることもある。

#### 【0098】

なお、水プラズマ処理を用いることなく露出している半導体層 106 にダメージが入らず、且つ半導体層 106 に対するエッティングレートが低い条件でドライエッティングを行ってもよい。

#### 【0099】

上記したように、一対のソース領域及びドレイン領域 110 を形成した後に、半導体層 106 にダメージを与えない条件で更なるドライエッティングを行うことで、露出した半導体層 106 上に存在する残渣などの不純物元素を除去することができる。また、ドライエッティングに続けて水プラズマ処理を行うことで、第 2 のレジストマスク 132 を除去することも可能である。水プラズマ処理を行うことで、ソース領域とドレイン領域との間の絶縁を確実なものにすことができ、完成する薄膜トランジスタのオフ電流を低減し、オン電流を向上させ、電気的特性のばらつきを低減することができる。

#### 【0100】

なお、プラズマ処理等の工程は上記の順番に限定されず、第 2 のレジストマスク 132 を除去した後に、無バイアスでのエッティングや、プラズマ処理を行ってもよい。

#### 【0101】

以上説明したように、本実施の形態に係る薄膜トランジスタを作製することができる (図 5 (B) を参照)。本実施の形態に係る薄膜トランジスタは、液晶表示装置に代表される表示装置の画素に設けられるスイッチングトランジスタに適用することができる。この場合、この薄膜トランジスタを覆って、開口部を有する絶縁層 114 を形成し、該開口部において配線層 112 により構成されるソース電極及びドレイン電極と接続されるように画素電極層 116 を形成する (図 5 (C) を参照)。この開口部は、フォトリソグラフィ法により形成することができる。その後、当該開口部を介して接続されるように、絶縁層 114 上に画素電極層 116 を設ける。このようにして、図 1 に示す表示装置の画素に設けられるスイッチングトランジスタを作製することができる。

#### 【0102】

なお、絶縁層 114 は、ゲート絶縁層 104 と同様に形成することができる。絶縁層 114 は、大気中に浮遊する有機物、金属又は水蒸気等の汚染源となりうる不純物元素の侵入を防ぐことができるよう、緻密な窒化シリコンにより設けることが好ましい。

#### 【0103】

なお、画素電極層 116 は、透光性を有する導電性高分子 (導電性ポリマーともいう。

10

20

30

40

50

)を含む導電性組成物を用いて形成することができる。画素電極層116は、シート抵抗が10000 / cm<sup>2</sup>以下であって、且つ波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。

【0104】

導電性高分子としては、いわゆる 電子共役系導電性高分子を用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、又はこれらの2種以上の共重合体等が挙げられる。

【0105】

画素電極層116は、例えば、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、または酸化シリコンを添加したインジウム錫酸化物等を用いて形成することができる。

【0106】

画素電極層116は、配線層112等と同様に、フォトリソグラフィ法を用いてエッチングを行い、パターン形成すればよい。

【0107】

なお、図示していないが、絶縁層114と画素電極層116との間に、スピンドーティング法等により形成した有機樹脂からなる絶縁層を有していても良い。

【0108】

以上、本実施の形態にて説明したように、オン電流が高い薄膜トランジスタを得ることができる。

【0109】

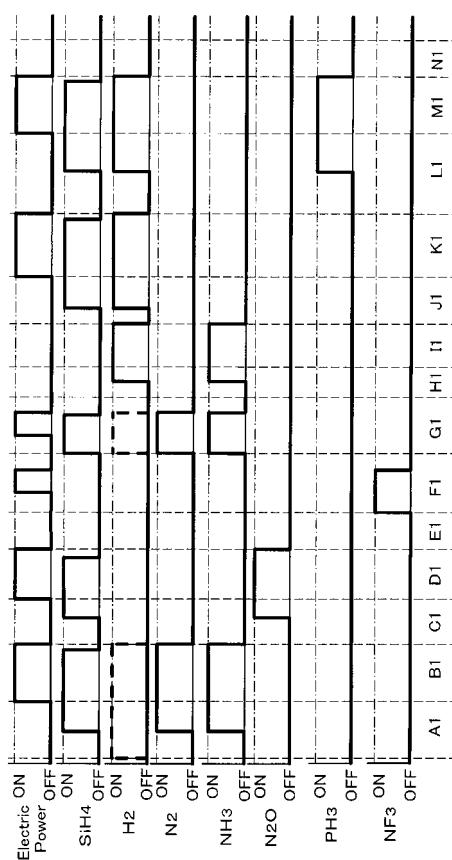

(実施の形態2)

本実施の形態では、図1に示す薄膜トランジスタの作製方法であって、実施の形態1とは異なるものについて説明する。本実施の形態では、実施の形態1と同様に、逆錐形の形状を有する結晶粒を含む半導体層を形成する。ただし、半導体層に窒素を含ませる手段が異なる。

【0110】

本実施の形態では、半導体層に接するゲート絶縁層を窒化シリコンにより形成することで、半導体層の窒素濃度を制御し、逆錐形の形状を有する結晶粒を含む半導体層を形成する。ゲート絶縁層104からドナーとなる不純物元素を含む半導体層109の形成までについて、図9を参照して以下に説明する。

【0111】

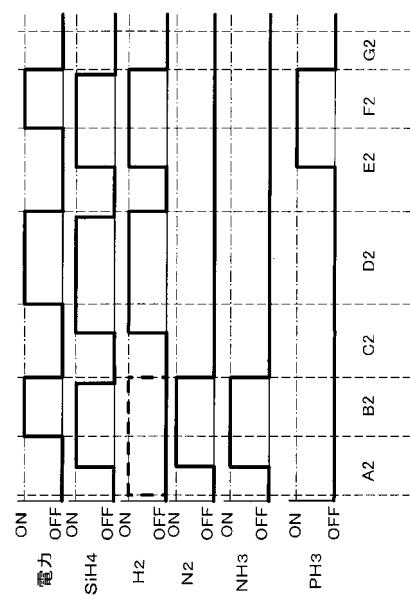

まず、ゲート電極層102が形成された基板をCVD装置の処理室141内にて加熱し、窒化シリコン層の形成に用いる材料ガスを処理室141内に導入する(図9の予備処理A2)。ここでは、一例として、SiH<sub>4</sub>の流量を40sccm、H<sub>2</sub>の流量を500sccm、N<sub>2</sub>の流量を550sccm、NH<sub>3</sub>の流量を140sccmとして材料ガスを導入して流量を安定させ、処理室141内の圧力を100Pa、基板の温度を280とし、370Wのプラズマ放電を行うことで、約300nmの窒化シリコン層を形成する。その後、SiH<sub>4</sub>の導入のみを停止して数秒後にプラズマの放電を停止させる(図9のSiNx層形成B2)。なお、N<sub>2</sub>ガス及びNH<sub>3</sub>ガスはいずれか一方を用いればよく、これらを混合して用いる場合には流量を適宜調整するとよい。また、H<sub>2</sub>ガスの導入及び流量は適宜調整し、不要な場合には導入しなくてもよい。

【0112】

次に、窒化シリコン層の形成に用いた材料ガスを排気し、半導体層105の形成に用いる材料ガスを処理室141内に導入する(図9のガス置換C2)。

【0113】

次に、ゲート絶縁層104上の全面に半導体層105を形成する。半導体層105は、

10

20

30

40

50

後の工程でパターン形成されて半導体層 106 となるものである。まず、半導体層 105 の形成に用いる材料ガスを処理室 141 内に導入する。ここでは、一例として、 $\text{SiH}_4$  の流量を 10 sccm、 $\text{H}_2$  の流量を 1500 sccm として材料ガスを導入して流量を安定させ、処理室 141 内の圧力を 280 Pa、基板の温度を 280 とし、50 W のプラズマ放電を行うことで、約 50 nm の半導体層を形成する。その後、上記した窒化シリコン層等の形成と同様に、 $\text{SiH}_4$  の導入のみを停止し、その数秒後にプラズマの放電を停止させる（図 9 の半導体層形成 D2）。その後、これらのガスを排気し、ドナーとなる不純物元素を含む半導体層 109 の形成に用いるガスを導入する（図 9 のガス置換 E2）。なお、これに限定されず、ガスの置換は必ずしも行わなくてもよい。

## 【0114】

10

上記の例において、半導体層 105 の形成に用いられる材料ガスでは、 $\text{SiH}_4$  の流量に対する $\text{H}_2$  の流量を 150 倍としており、シリコンは徐々に堆積される。

## 【0115】

本実施の形態のゲート絶縁層 104 において、少なくとも半導体層 105 に接する最上層は窒化シリコンで形成されているため、ゲート絶縁層 104 の表面には多量の窒素が存在する。上記したように、窒素はシリコンの結晶の核生成を抑制する。そのため、半導体層 105 の形成の初期段階ではシリコンの結晶核が生成されない。半導体層 105 の形成の初期段階で形成されるこの層が、図 2 に示す第 1 の領域 120 となる。半導体層 105 は一の条件により形成するため、第 1 の領域 120 と第 2 の領域 122 は同じ条件により形成される。上記したようにゲート絶縁層 104 は窒化シリコンで形成されているため、ゲート絶縁層 104 上の半導体層 105 は窒素を含む（図 2 に示す第 1 の領域 120）。半導体層 105 において、窒素の濃度はゲート絶縁層 104 との界面から離れるにつれて低下し、窒素の濃度が一定の値以下となると、結晶核が生成される。その後、その結晶核が成長し、結晶粒 121 が形成される。なお、ここで結晶粒 121 の成長の起点となる結晶核の生成位置において、SIMS によって計測される窒素の濃度は  $1 \times 10^{20} \text{ cm}^{-3}$  以上  $1 \times 10^{21} \text{ cm}^{-3}$  以下、好ましくは  $2 \times 10^{20} \text{ cm}^{-3}$  以上  $7 \times 10^{20} \text{ cm}^{-3}$  以下となる。

20

## 【0116】

30

なお、ここで、結晶核の生成を抑制する不純物元素は、シリコン中にあって、キャリアトラップを生成しない不純物元素（例えば、窒素）を選択する。一方、シリコンのダングリングボンドを生成する不純物元素（例えば、酸素）の濃度は低減させる。従って、窒素濃度を低減させずに酸素濃度を低減させるとよい。具体的には、SIMS によって計測される酸素の濃度が  $5 \times 10^{18} \text{ cm}^{-3}$  以下となるようにするとよい。

## 【0117】

次に、半導体層 105 上の全面にドナーとなる不純物元素を含む半導体層 109 を形成する。ドナーとなる不純物元素を含む半導体層 109 は、後の工程でパターン形成されて、ソース領域及びドレイン領域 110 となるものである。まず、ドナーとなる不純物元素を含む半導体層 109 の形成に用いる材料ガスを処理室 141 内に導入する。ここでは、一例として、 $\text{SiH}_4$  の流量を 100 sccm、 $\text{PH}_3$  を  $\text{H}_2$  により 0.5 vol % まで希釈した混合ガスの流量を 170 sccm として材料ガスを導入して流量を安定させ、処理室 141 内の圧力を 280 Pa、基板の温度を 280 とし、60 W のプラズマ放電を行うことで、約 50 nm のドナーとなる不純物元素を含む半導体層を形成する。その後、上記した窒化シリコン層等の形成と同様に、 $\text{SiH}_4$  の供給のみを停止し、その数秒後にプラズマの放電を停止させる（図 9 の不純物半導体層形成 F2）。その後、これらのガスを排気する（図 9 の排気 G2）。

40

## 【0118】

上記説明したように、少なくとも半導体層に接するゲート絶縁層の最上層を窒化シリコンにより形成することで、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くすることができ、逆錐形の形状を有する結晶粒を含む半導体層を形成することができる。

## 【0119】

50

## (実施の形態 3 )

本実施の形態では、図 1 に示す薄膜トランジスタの作製方法であって、実施の形態 1 及び実施の形態 2 とは異なるものについて説明する。本実施の形態では、実施の形態 1 及び実施の形態 2 と同様に、逆錐形の形状を有する結晶粒を含む半導体層を形成する。ただし、半導体層に窒素を含ませる手段が異なる。

## 【 0 1 2 0 】

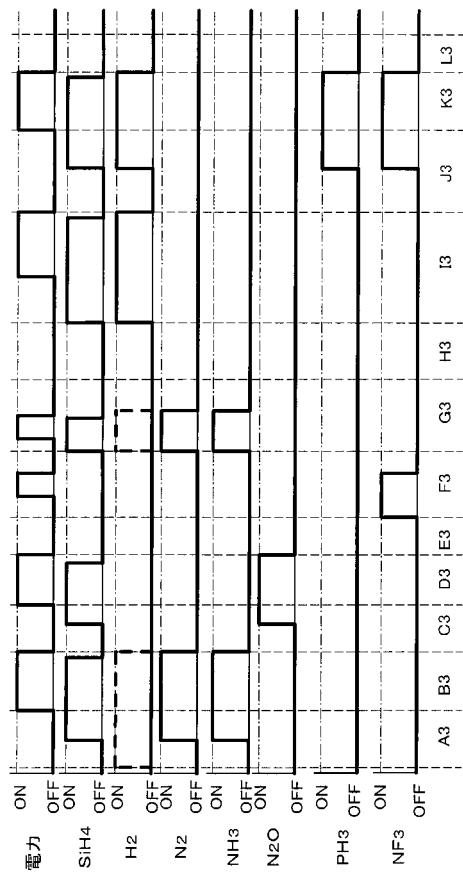

本実施の形態では、半導体層の形成前に処理室 141 内をクリーニングし、その後窒化シリコン層によりチャンバー内壁を覆うことで、半導体層に窒素を含ませて、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くする。ゲート絶縁層 104 の形成からドナーとなる不純物元素を含む半導体層 109 の形成までについて、図 10 を参照して以下に説明する。

10

## 【 0 1 2 1 】

まず、ゲート電極層 102 が形成された基板を CVD 装置の処理室 141 内（チャンバー内）にて加熱し、窒化シリコン層を形成するための材料ガスを処理室 141 内に導入する（図 10 の予備処理 A3）。ここでは、一例として、SiH<sub>4</sub> の流量を 40 sccm、H<sub>2</sub> の流量を 500 sccm、N<sub>2</sub> の流量を 550 sccm、NH<sub>3</sub> の流量を 140 sccm として材料ガスを導入して流量を安定させ、処理室 141 内の圧力を 100 Pa、基板の温度を 280 とし、370 W のプラズマ放電を行うことで、約 110 nm の窒化シリコン層を形成する。その後、SiH<sub>4</sub> の導入のみを停止して数秒後にプラズマの放電を停止させる（図 10 の SiNx 膜形成 B3）。なお、N<sub>2</sub> ガス及び NH<sub>3</sub> ガスはいずれか一方を用いればよく、これらを混合して用いる場合には流量を適宜調整するとよい。また、H<sub>2</sub> ガスの導入及び流量は適宜調整し、不要な場合には導入しなくてもよい。

20

## 【 0 1 2 2 】

次に、窒化シリコン層の形成に用いる材料ガスを排気し、酸化窒化シリコン層の形成に用いる材料ガスを処理室 141 内に導入する（図 10 のガス置換 C3）。ここでは、一例として、SiH<sub>4</sub> の流量を 30 sccm、N<sub>2</sub>O の流量を 1200 sccm とし、材料ガスを導入して安定させ、処理室 141 内の圧力を 40 Pa、基板の温度を 280 として 50 W のプラズマ放電を行うことで、約 110 nm の酸化窒化シリコン層を形成する。その後、窒化シリコン層と同様に、SiH<sub>4</sub> の導入のみを停止し、その数秒後にプラズマの放電を停止させる（図 10 の SiOxNy 層形成 D3）。

30

## 【 0 1 2 3 】

上記の工程により、ゲート絶縁層 104 を形成することができる。ゲート絶縁層 104 の形成後、基板 100 を処理室 141 から搬出する（図 10 のアンロード E3）。

## 【 0 1 2 4 】

基板 100 を処理室 141 から搬出後、処理室 141 に NF<sub>3</sub> ガスを導入し、処理室 141 内をクリーニングする（図 10 のクリーニング処理 F3）。その後、ゲート絶縁層 104 と同様に窒化シリコン層を形成する処理を行う（図 10 のプレコート処理 G3）。この処理により、処理室 141 の内壁が窒化シリコン層により覆われる。その後、基板 100 を処理室 141 に搬入し、半導体層 105 の形成に用いる材料ガスを処理室 141 内に導入する（図 10 のロード H3）。

40

## 【 0 1 2 5 】

次に、ゲート絶縁層 104 上の全面に半導体層 105 を形成する。半導体層 105 は、後の工程でパターン形成されて半導体層 106 となるものである。まず、半導体層 105 の形成に用いる材料ガスを処理室 141 内に導入する。ここでは、一例として、SiH<sub>4</sub> の流量を 10 sccm、H<sub>2</sub> の流量を 1500 sccm として材料ガスを導入して流量を安定させ、処理室 141 内の圧力を 280 Pa、基板の温度を 280 とし、50 W のプラズマ放電を行うことで、約 50 nm の半導体層を形成する。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub> の導入のみを停止し、その数秒後にプラズマの放電を停止させる（図 10 の半導体層形成 I3）。その後、これらのガスを排気し、ドナーとなる不純物元素を含む半導体層 109 の形成に用いるガスを導入する（図 10 のガス置換 J50）。

3)。なお、これに限定されず、ガスの置換は必ずしも行わなくてよい。

【0126】

上記の例において、半導体層105の形成に用いられる材料ガスでは、SiH<sub>4</sub>の流量に対するH<sub>2</sub>の流量を150倍としており、シリコンは徐々に堆積される。

【0127】

本実施の形態では、処理室141の内壁を覆う窒化シリコン層からゲート絶縁層104の表面に窒素が供給される。上記したように、窒素はシリコンの結晶の核生成を抑制する。そのため、半導体層105の形成の初期段階ではシリコンの結晶核が生成されない。半導体層105の形成の初期段階で形成されるこの層が、図2に示す第1の領域120となる。半導体層105は一の条件により形成するため、第1の領域120と第2の領域122は同じ条件により形成されるものである。上記したようにゲート絶縁層104の表面には窒素が供給されているため、窒素を含む半導体層105(図2に示す第1の領域120)が形成される。半導体層105において、窒素の濃度はゲート絶縁層104との界面から離れるにつれて低下し、窒素の濃度が一定の値以下となると、結晶核が生成される。その後、その結晶核が成長し、結晶粒121が形成される。

【0128】

次に、半導体層105上の全面にドナーとなる不純物元素を含む半導体層109を形成する。ドナーとなる不純物元素を含む半導体層109は、後の工程でパターン形成されてソース領域及びドレイン領域110となるものである。まず、ドナーとなる不純物元素を含む半導体層109の成膜に用いる材料ガスを処理室141内に導入する。ここでは、一例として、SiH<sub>4</sub>の流量を100sccm、PH<sub>3</sub>をH<sub>2</sub>により0.5vol%まで希釈した混合ガスの流量を170sccmとして材料ガスを導入して流量を安定させ、処理室141内の圧力を280Pa、基板の温度を280とし、60Wのプラズマ放電を行うことで、約50nmの半導体層を形成する。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub>の供給のみを停止し、その数秒後にプラズマの放電を停止させる(図10のドナーとなる不純物元素を含む半導体層形成K3)。その後、これらのガスを排気する(図10の排気L3)。

【0129】

上記説明したように、少なくとも半導体層105を形成する直前に処理室141の内壁を窒化シリコン層により覆うことで、ゲート絶縁層104中の酸素濃度を低く抑え、ゲート絶縁層104中の窒素濃度を酸素濃度よりも高くすることが可能であり、逆錐形の形状を有する結晶粒を含む半導体層を形成することができる。

【0130】

また、処理室141の内壁を窒化シリコン層により覆うことで、処理室141の内壁を構成する元素等が半導体層に混入することをも防ぐことができる。

【0131】

なお、上記の説明では、窒化シリコン層上に酸化窒化シリコン層を積層してゲート絶縁層104を形成したため、ゲート絶縁層104の形成後にクリーニング処理とプレコート処理を行う形態について説明したが、本実施の形態は、実施の形態2と組み合わせて実施してもよい。すなわち、ゲート絶縁層104を窒化シリコンにより形成し、ゲート絶縁層104の形成がプレコート処理を兼ねていてもよい。ゲート絶縁層104の形成がプレコート処理を兼ねることで、工程が簡略化し、スループットを向上させることができる。

【0132】

(実施の形態4)

本実施の形態では、実施の形態1乃至実施の形態3とは異なる半導体装置の作製方法について説明する。本実施の形態では、実施の形態1と同様に、逆錐形の形状を有する結晶粒を含む半導体層を形成する。ただし、半導体層に窒素を含ませる手段が異なる。

【0133】

本実施の形態では、半導体層の形成初期のガスに窒素を混入させることで、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くする。ゲート絶縁層104からドナーとなる不

10

20

30

40

50

純物元素を含む半導体層 109 の形成までについて、図 11 を参照して以下に説明する。

【0134】

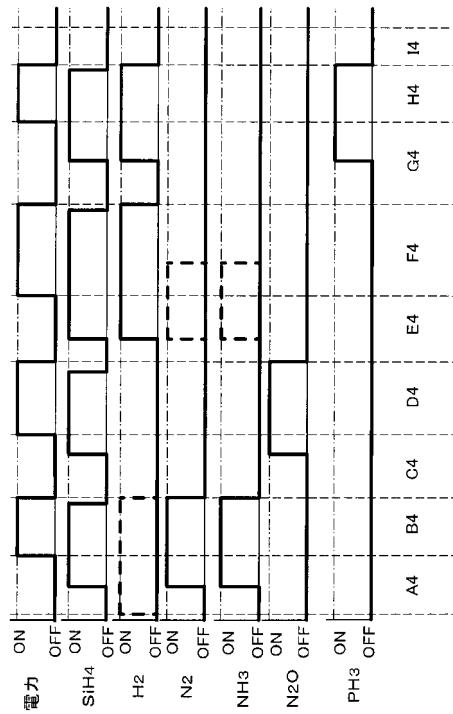

まず、ゲート電極層 102 が形成された基板を CVD 装置の処理室 141 内（チャンバー内）にて加熱し、窒化シリコン層の形成に用いる材料ガスを処理室 141 内に導入する（図 11 の予備処理 A4）。ここでは、一例として、SiH<sub>4</sub> の流量を 40 sccm、H<sub>2</sub> の流量を 500 sccm、N<sub>2</sub> の流量を 550 sccm、NH<sub>3</sub> の流量を 140 sccm として材料ガスを導入して流量を安定させ、処理室 141 内の圧力を 100 Pa、基板の温度を 280 とし、370 W のプラズマ放電を行うことで、約 110 nm の窒化シリコン層を形成する。その後、SiH<sub>4</sub> の導入のみを停止して数秒後にプラズマの放電を停止させる（図 11 の SiNx 層形成 B4）。なお、N<sub>2</sub> ガス及び NH<sub>3</sub> ガスはいずれか一方を用いればよく、これらを混合して用いる場合には流量を適宜調整するとよい。また、H<sub>2</sub> ガスの導入及び流量は適宜調整し、不要な場合には導入しなくてもよい。 10

【0135】

次に、窒化シリコン層の形成に用いる材料ガスを排気し、酸化窒化シリコン層の形成に用いる材料ガスを処理室 141 内に導入する（図 11 のガス置換 C4）。ここでは、一例として、SiH<sub>4</sub> の流量を 30 sccm、N<sub>2</sub>O の流量を 1200 sccm とし、材料ガスを導入して流量を安定させ、処理室 141 内の圧力を 40 Pa、基板の温度を 280 として 50 W のプラズマ放電を行うことで、約 110 nm の酸化窒化シリコン層を形成する。その後、窒化シリコン層と同様に、SiH<sub>4</sub> の導入のみを停止し、その数秒後にプラズマの放電を停止させる（図 11 の SiO<sub>x</sub>N<sub>y</sub> 層形成 D4）。その後、これらのガスを排気し、半導体層 105 の形成に用いるガスを導入する（図 11 のガス置換 E4）。 20

【0136】

次に、ゲート絶縁層 104 上の全面に半導体層 105 を形成する。半導体層 105 は、後の工程でパターン形成されて半導体層 106 となるものである。ここでは、一例として、SiH<sub>4</sub> の流量を 10 sccm、H<sub>2</sub> の流量を 1500 sccm、N<sub>2</sub> の流量を 1000 sccm として材料ガスを導入して流量を安定させ、処理室 141 内の圧力を 280 Pa、基板の温度を 280 とし、50 W のプラズマ放電を行う。その後、N<sub>2</sub> の流量のみを 0 として半導体層を成長させて、約 50 nm の半導体層を形成する。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub> の導入のみを停止し、その数秒後にプラズマの放電を停止させる（図 11 の半導体層形成 F4）。その後、これらのガスを排気し、ドナーとなる不純物元素を含む半導体層 109 の形成に用いるガスを導入する（図 11 のガス置換 G4）。なお、N<sub>2</sub> に代えて NH<sub>3</sub> を用いてもよい。なお、これに限定されず、ガスの置換は必ずしも行わなくてもよい。 30

【0137】

上記の例において、半導体層 105 の形成に用いられる材料ガスでは、SiH<sub>4</sub> の流量に対する H<sub>2</sub> の流量を 150 倍としており、シリコンは徐々に堆積される。

【0138】

本実施の形態における半導体層 105 の形成初期のガスには窒素が含まれている。上記したように、窒素はシリコンの結晶の核生成を抑制する。そのため、半導体層 105 の形成初期の段階ではシリコンの結晶核が生成されない。半導体層 105 の形成初期の段階で形成されるこの層が、図 2 に示す第 1 の領域 120 となる。上記したように半導体層 105 の形成初期のガスには窒素が含まれているので、半導体層 105（図 2 に示す第 1 の領域 120）は窒素を含有する。半導体層 105 において、窒素の濃度はゲート絶縁層 104 との界面から離れるにつれて低下し、窒素の濃度が一定の値以下となると、結晶核が生成される。その後、その結晶核が成長し、結晶粒 121 が形成される。 40

【0139】

次に、半導体層 105 上の全面にドナーとなる不純物元素を含む半導体層 109 を形成する。ドナーとなる不純物元素を含む半導体層 109 は、後の工程でパターン形成されてソース領域及びドレイン領域 110 となるものである。まず、ドナーとなる不純物元素を含む半導体層 109 の形成に用いる材料ガスを処理室 141 内に導入する。ここでは、一 50

例として、SiH<sub>4</sub>の流量を100sccm、PH<sub>3</sub>をH<sub>2</sub>により0.5vol%まで希釈した混合ガスの流量を170sccmとして材料ガスを導入して流量を安定させ、処理室141内の圧力を280Pa、基板の温度を280とし、60Wのプラズマ放電を行うことで、約50nmの半導体層を形成する。その後、上記した窒化シリコン層等の形成と同様に、SiH<sub>4</sub>の導入のみを停止し、その数秒後にプラズマの放電を停止させる(図11の不純物半導体層形成H4)。その後、これらのガスを排気する(図11の排気I4)。

#### 【0140】

上記説明したように、半導体層の形成初期のガスに窒素を含ませることで、酸素濃度を低く抑え、窒素濃度を酸素濃度よりも高くすることが可能であり、逆錐形の形状を有する結晶粒を含む半導体層を形成することができる。

10

#### 【0141】

##### (実施の形態5)

本実施の形態では、薄膜トランジスタの形態の一例について、図面を参照して説明する。本実施の形態では、多階調マスクを用いることなく薄膜トランジスタを形成する。

#### 【0142】

図12は、本実施の形態にかかる薄膜トランジスタの上面図及び断面図を示す。図12に示す薄膜トランジスタは、基板200上にゲート電極層202を有し、ゲート電極層202を覆ってゲート絶縁層204を有し、ゲート絶縁層204上に接して半導体層206を有し、半導体層206上の一端に接してソース領域及びドレイン領域210を有する。また、ゲート絶縁層204、並びにソース領域及びドレイン領域210上に接する配線層212を有する。配線層212はソース電極及びドレイン電極を構成する。配線層212上には、保護膜として機能する絶縁層214を有する。また、各層は所望の形状にパターン形成されている。

20

#### 【0143】

なお、図12に示す薄膜トランジスタは、図1に示す薄膜トランジスタと同様に、液晶表示装置の画素部に設けられる画素トランジスタに適用することができる。そのため、図示した例では、絶縁層214には開口部が設けられ、絶縁層214上には画素電極層216が設けられ、画素電極層216と配線層212とが接続されている。

30

#### 【0144】

また、ソース電極及びドレイン電極の一方は、U字型(またはコの字型)の形状で設けられ、これがソース電極及びドレイン電極の他方を囲い込んでいる。ソース電極とドレイン電極との距離はほぼ一定に保たれている(図12を参照)。

#### 【0145】

薄膜トランジスタのソース電極及びドレイン電極を上記した形状とすることで、該薄膜トランジスタのチャネル幅を大きくすることができ、電流量が増大する。また、電気的特性のばらつきを低減することができる。更には、作製工程におけるマスクパターンのずれによる信頼性の低下を抑制することができる。ただし、これに限定されず、ソース電極及びドレイン電極の一方は必ずしもU字型でなくともよい。

40

#### 【0146】

本実施の形態における半導体層206は、実施の形態1における半導体層106と同様の特徴を有し、同様の材料及び方法により形成することができる。また、実施の形態2乃至実施の形態4にて説明したように形成してもよい。従って、本実施の形態では半導体層206の形成に関する詳細な説明は省略する。

#### 【0147】

図12に示す薄膜トランジスタの作製方法について説明する。薄膜トランジスタではp型よりもn型の方が、キャリアの移動度が高い。また、同一の基板上に形成する薄膜トランジスタを全て同じ極性に統一すると、工程数を抑えることができ、好ましい。そのため、本実施の形態では、n型の薄膜トランジスタの作製方法について説明する。

#### 【0148】

50

まず、基板 200 上にゲート電極層 202 を形成する（図 13（A）を参照）。

【0149】

基板 200 としては、実施の形態 1 における基板 100 と同様のものを用いることができる。

【0150】

ゲート電極層 202 は、実施の形態 1 におけるゲート電極層 102 と同様の材料及び方法により形成することができる。

【0151】

次に、ゲート電極層 202 を覆ってゲート絶縁層 204 を形成する（図 13（B）を参照）。ゲート絶縁層 204 は、実施の形態 1 におけるゲート絶縁層 104 と同様の材料及び方法により形成することができる。10

【0152】

ここで、ゲート絶縁層 204 上に窒素を供給する処理を行ってもよい（図 13（C）を参照）。窒素を供給する処理として、実施の形態 1 にて説明したゲート絶縁層 204 を NH<sub>3</sub> ガスに曝す処理が挙げられる。

【0153】

次に、ゲート絶縁層 204 上に半導体層 205、及びドナーとなる不純物元素を含む半導体層 209 を形成する（図 14（A）を参照）。その後、ドナーとなる不純物元素を含む半導体層 209 上に第 1 のレジストマスク 231 を形成する（図 14（B）を参照）。

【0154】

半導体層 205 は、実施の形態 1 における半導体層 105 と同様に形成することができる。ドナーとなる不純物元素を含む半導体層 209 は、実施の形態 1 におけるドナーとなる不純物元素を含む半導体層 109 と同様に形成することができる。20

【0155】

なお、半導体層 205 は、実施の形態 2 乃至実施の形態 4 にて説明した方法により形成してもよい。

【0156】

次に、第 1 のレジストマスク 231 を用いて半導体層 205、及びドナーとなる不純物元素を含む半導体層 209 をエッティングして島状の半導体層を形成する（図 14（C）を参照）。その後、第 1 のレジストマスク 231 を除去する（図 15（A）を参照）。30

【0157】

次に、エッティングされた半導体層 205、及びドナーとなる不純物元素を含む半導体層 209 を覆って導電層 211 を形成する（図 15（B）を参照）。導電層 211 は、導電層 111 と同様の材料及び方法により形成することができる。その後、導電層 211 上に第 2 のレジストマスク 232 を形成する（図 15（C）を参照）。

【0158】

次に、第 2 のレジストマスク 232 を用いて導電層 211 をエッティングして配線層 212 を形成する。（図 16（A）を参照）。配線層 212 は、ソース電極及びドレイン電極を構成する。導電層 211 のエッティングは、ウエットエッティングを用いることが好ましい。ウエットエッティングにより、導電層が選択的にエッティングされる。その結果、導電層 211 の側面は第 2 のレジストマスク 232 の側面よりも内側に後退し、配線層 212 が形成される。従って、配線層 212 の側面と、エッティングされたドナーとなる不純物元素を含む半導体層 209 の側面は一致せず、配線層 212 の側面の外側に、ソース領域及びドレイン領域の側面が形成される。配線層 212 は、ソース電極及びドレイン電極のみならず信号線としても機能する。ただし、これに限定されず、信号線と配線層 212 とは別に設けてよい。40

【0159】

次に、第 2 のレジストマスク 232 を用いて島状半導体層のドナーとなる不純物元素を含む半導体層 209 をエッティングする（図 16（B）を参照）。ここまでで、半導体層 206、並びにソース領域及びドレイン領域 210 が形成される。50

## 【0160】

次に、実施の形態1と同様に第2のレジストマスク232が形成された状態で、半導体層206にダメージが入らず、且つ半導体層206に対するエッチングレートが低い条件下ドライエッチングを行うとよい。更には、水プラズマ処理により第2のレジストマスク232を除去するとよい(図16(C))。

## 【0161】

以上の工程により本実施の形態に係る薄膜トランジスタを作製することができる。本実施の形態に係る薄膜トランジスタは、実施の形態1にて説明した薄膜トランジスタと同様に、液晶表示装置に代表される表示装置の画素に設けられるスイッチングトランジスタに適用することができる。そのため、この薄膜トランジスタを覆って、絶縁層214を形成する。絶縁層214には、配線層212により構成されるソース電極及びドレイン電極に達するように開口部が形成されている。この開口部は、フォトリソグラフィ法により形成することができる。その後、当該開口部を介して接続されるように、絶縁層214上に画素電極層216を設けると、図12に示す表示装置の画素に設けられるスイッチングトランジスタを作製することができる。

## 【0162】

なお、絶縁層214は、実施の形態1における絶縁層114と同様に形成することができる。また、画素電極層216は、実施の形態1における画素電極層116と同様に形成することができる。

## 【0163】

なお、図示していないが、絶縁層214と画素電極層216との間に、スピンドコーティング法等により形成した有機樹脂膜からなる絶縁層を有しても良い。

## 【0164】

以上、本実施の形態にて説明したように、オン電流が高い薄膜トランジスタを、多階調マスクを用いることなく得ることができる。

## 【0165】

## (実施の形態6)

本実施の形態では、表示装置の一形態として、実施の形態5で示す薄膜トランジスタを有する液晶表示装置について説明する。ここでは、VA(Vertical Alignment)型の液晶表示装置について、図17乃至図19を参照して説明する。VA型とは、液晶パネルの液晶分子の配列を制御する方式の一種をいう。VA型の液晶表示装置では、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く。本実施の形態では、特に画素(ピクセル)をいくつかの領域(サブピクセル)に分け、それぞれ別の方向に液晶分子を倒すよう工夫されている。これをマルチドメインあるいはマルチドメイン設計という。以下の説明では、マルチドメイン設計が考慮された液晶表示装置について説明する。

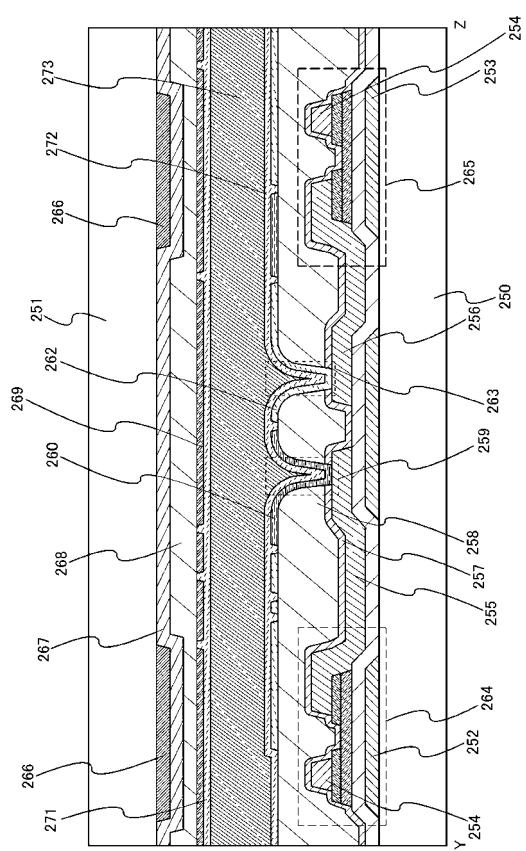

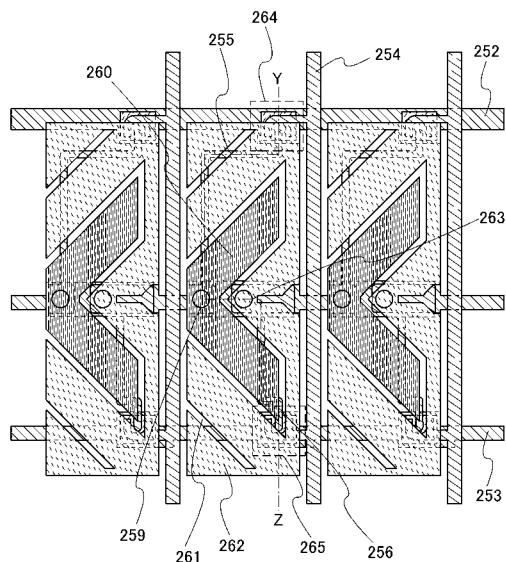

## 【0166】

図17及び図18は、VA型の液晶表示装置の画素構造を示している。図18は本実施の形態で示す画素構造の平面図であり、図18中に示す切断線Y-Zに対応する断面構造を図17に表している。以下の説明では図17及び図18を参照して説明する。

## 【0167】

本実施の形態で示す画素構造は、基板250上に設けられた一つの画素が複数の画素電極を有し、それぞれの画素電極に平坦化膜258及び絶縁層257を介して薄膜トランジスタが接続されている。各薄膜トランジスタは、異なるゲート信号で駆動されるように構成されている。すなわち、マルチドメイン設計された画素において、個々の画素電極に印加する信号を、独立して制御する構成を有している。

## 【0168】

画素電極260は、開口部259において、配線255を介して薄膜トランジスタ264と接続されている。また、画素電極262は、開口部263において、配線256を介して薄膜トランジスタ265と接続している。薄膜トランジスタ264のゲート電極25

10

20

30

40

50

2と、薄膜トランジスタ265のゲート電極253には、異なるゲート信号を与えることができるよう分離されている。一方、データ線として機能する配線254は、薄膜トランジスタ264と薄膜トランジスタ265で共通して用いられている。薄膜トランジスタ264及び薄膜トランジスタ265は実施の形態5で示す方法を用いて作製することができる。

【0169】

画素電極260と画素電極262の形状は異なっており、スリット261によって分離されている。画素電極262は、V字型に広がる画素電極260の外側を囲むように形成されている。画素電極260と画素電極262に印加する電圧のタイミングを、薄膜トランジスタ264及び薄膜トランジスタ265により異ならせることで、液晶の配向を制御している。ゲート電極252とゲート電極253に異なるゲート信号を与えることで、薄膜トランジスタ264と薄膜トランジスタ265の動作タイミングを異ならせることができる。また、画素電極260及び画素電極262上に配向膜272が形成されている。

10

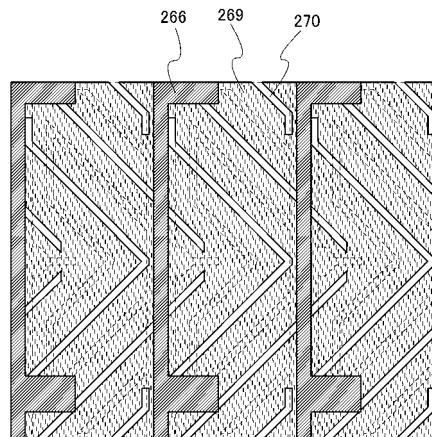

【0170】

対向基板251には、遮光膜266、着色膜267、対向電極269が形成されている。また、着色膜267と対向電極269の間には平坦化膜268が形成され、液晶の配向乱れを防いでいる。また、対向電極269上には配向膜271が形成されている。図19に対向基板251側の画素構造を示す。対向電極269は異なる画素間で共通化され、スリット270を有する。スリット270と、画素電極260及び画素電極262のスリット261とを交互に配置することで、斜め電界を発生させて液晶の配向を制御することができる。その結果、液晶が配向する方向を場所によって異ならせることができ、視野角を拡げることができる。

20

【0171】

ここでは、基板、着色膜、遮光膜、及び平坦化膜で、カラーフィルターを構成する。なお、遮光膜、平坦化膜の何れか一方、または両方は、基板上に形成されていなくともよい。

【0172】

また、着色膜は、可視光の波長範囲のうち、任意の波長範囲の光の成分を優先的に透過させる機能を有する。通常は、赤色波長範囲の光、青色波長範囲の光、及び緑色波長範囲の光のそれぞれを優先的に透過させる着色膜を組み合わせて、カラーフィルターに用いることが多い。しかしながら、着色膜の組み合わせに関しては、これに限定されない。

30

【0173】

画素電極260と対向電極269が液晶層273を挟持することで、第1の液晶素子が形成されている。また、画素電極262と対向電極269が液晶層273を挟持することで、第2の液晶素子が形成されている。また、一画素に第1の液晶素子と第2の液晶素子が設けられたマルチドメイン構造である。

【0174】

なお、ここでは、液晶表示装置として、VA型の液晶表示装置を示したが、これに限定されない。すなわち、実施の形態5に示す薄膜トランジスタを用いて形成した素子基板を、FFS型の液晶表示装置、IPS型の液晶表示装置、TN型の液晶表示装置又はその他の液晶表示装置に用いることができる。

40

【0175】

また、本実施の形態では実施の形態5にて作製した薄膜トランジスタを用いたが、実施の形態1にて作製した薄膜トランジスタを用いてもよい。

【0176】

以上説明したように、液晶表示装置を作製することができる。本実施の形態の液晶表示装置は、オン電流が高い薄膜トランジスタを画素トランジスタとして用いているため、画質が良好（例えば、高コントラスト）であり、且つ消費電力の低い液晶表示装置を作製することができる。

【0177】

50

(実施の形態 7 )

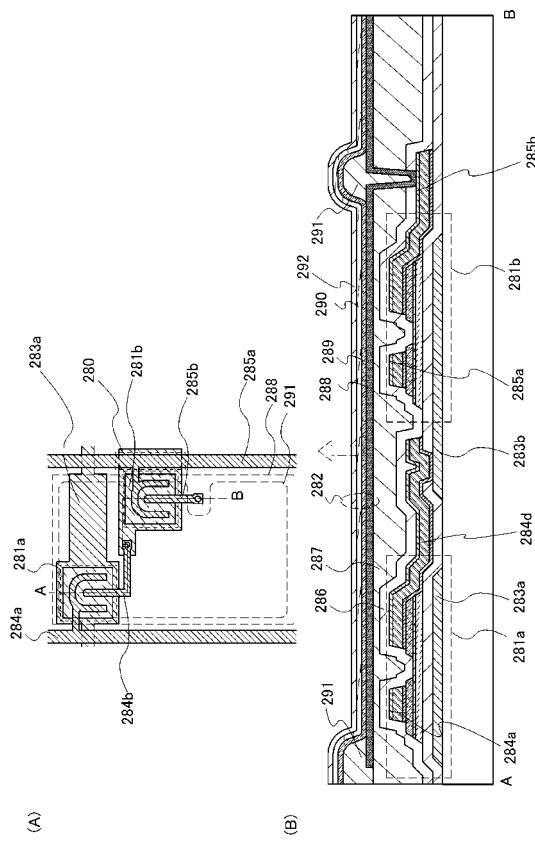

本実施の形態では、表示装置の一形態として、実施の形態 5 で示す薄膜トランジスタを有する発光表示装置について説明する。ここでは、発光表示装置が有する画素の構成の一例について説明する。図 20 ( A ) は画素の平面図を示し、図 20 ( B ) は図 20 ( A ) 中の切断線 A - B に対応する断面構造を示す。

【 0178 】

発光表示装置として、本実施の形態ではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって大別され、一般的に、前者は有機 EL 素子、後者は無機 EL 素子と呼ばれている。また、ここでは、薄膜トランジスタの作製方法として実施の形態 5 を用いたが、これに限定されず、実施の形態 1 に示す作製方法により作製したものであってもよい。

10

【 0179 】

有機 EL 素子は、発光素子に電圧を印加することにより、一対の電極から電子と正孔がそれぞれ発光性の有機化合物を含む層に注入されて、電流が流れる。そして、それらキャリア ( 電子と正孔 ) が再結合することにより、発光性の有機化合物が励起状態を形成し、励起状態が基底状態に緩和する際に発光する。このようなメカニズムから、このような発光素子は電流励起型の発光素子と呼ばれる。

【 0180 】

無機 EL 素子は、素子構成により、分散型無機 EL 素子と薄膜型無機 EL 素子とに分類される。分散型無機 EL 素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー - アクセプター再結合型発光である。薄膜型無機 EL 素子は、発光層を誘電体層で挟み込み、さらに発光層を誘電体層で挟み込んだものを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機 EL 素子を用いて説明する。

20

【 0181 】

図 20 ( A ) 及び ( B ) において、第 1 の薄膜トランジスタ 281a は画素電極への信号の入力を制御するためのスイッチング用の薄膜トランジスタであり、第 2 の薄膜トランジスタ 281b は発光素子 282 への電流または電圧を制御するための駆動用の薄膜トランジスタである。

30

【 0182 】

第 1 の薄膜トランジスタ 281a のゲート電極は走査線 283a に、ソース領域及びドレイン領域の一方は、信号線 284a に接続され、ソース領域及びドレイン領域の他方は配線 284b を介して第 2 の薄膜トランジスタ 281b のゲート電極 283b に接続される。また、第 2 の薄膜トランジスタ 281b のソース領域及びドレイン領域の一方は電源線 285a に接続され、ソース領域及びドレイン領域の他方は配線 285b を介して発光素子の画素電極 ( 陰極 288 ) に接続される。第 2 の薄膜トランジスタ 281b のゲート電極、ゲート絶縁膜、及び電源線 285a で容量素子 280 を構成し、第 1 の薄膜トランジスタ 281a のソース電極及びドレイン電極の他方は容量素子 280 に接続されている。

40

【 0183 】

なお、容量素子 280 は、第 1 の薄膜トランジスタ 281a がオフのときに第 2 の薄膜トランジスタ 281b のゲート電極とソース電極の間の電位差、またはゲート電極とドレイン電極の間の電位差 ( 以下、ゲート電圧という。 ) を保持するための容量素子に相当し、これらは必ずしも設けなくてもよい。

【 0184 】

本実施の形態では、第 1 の薄膜トランジスタ 281a 及び第 2 の薄膜トランジスタ 281b は n チャネル型薄膜トランジスタで形成されるが、これらの方または双方が p チャネル型の薄膜トランジスタで形成されていてもよい。

50

## 【0185】

第1の薄膜トランジスタ281a及び第2の薄膜トランジスタ281b上には絶縁層286が形成され、絶縁層286上に平坦化膜287が形成され、平坦化膜287及び絶縁層286に開口部が形成され、該開口部において配線285bに接続する陰極288が形成されている。平坦化膜287は、アクリル樹脂、ポリイミド、ポリアミドなどの有機樹脂またはシロキサンポリマーを用いて形成することが好ましい。該開口部では、陰極288が凹凸を有するため、陰極が凹凸を有する領域を覆い、且つ開口部を有する隔壁291を設ける。隔壁291の開口部において陰極288と接するように、EL層289が形成され、EL層289を覆うように陽極290が形成され、陽極290及び隔壁291を覆うように保護絶縁膜292が形成される。

10

## 【0186】

ここでは、発光素子として上面射出(トップエミッション)構造の発光素子282を示している。上面射出構造の発光素子282は、第1の薄膜トランジスタ281a及び第2の薄膜トランジスタ281bとEL層が重畠する領域での発光も取り出すことが可能であるため、広い発光面積を確保することが可能である。しかしながら、EL層289の下地が凹凸を有すると、EL層289の膜厚分布が不均一となり、陽極290と陰極288が短絡(ショート)し、表示欠陥を生じてしまうおそれがある。このため、平坦化膜287を設けることが好ましい。平坦化膜287を設けることで、歩留まりを向上させることができる。

## 【0187】

20

陰極288と陽極290でEL層289を挟んでいる領域が発光素子282に相当する。図20に示した画素の場合、発光素子282から発せられる光は、図20(B)に白抜きの矢印で示すように陽極290側に射出する。

## 【0188】

陰極288は仕事関数が小さく、且つ光を反射する導電膜であれば公知の材料を用いることができる。例えば、Ca、MgAg、AlLi等が望ましい。EL層289は、単数の層で構成されていてもよいし、複数の層が積層されて構成されていてもよい。複数の層が積層されて構成されている場合には、陰極288に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層して形成する。電子注入層を用いることで、Alなどの仕事関数の大きい金属を陰極288として用いることもできる。なお、発光層以外の層、例えば電子注入層、電子輸送層、ホール輸送層、ホール注入層の全てを設ける必要はなく、必要に応じて必要な層を適宜設ければよい。陽極290は、光を透過する透光性を有する導電性材料を用いて形成し、例えば酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、ITO、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性導電膜を用いても良い。

30

## 【0189】

ここでは、基板とは逆側の面から発光を取り出す上面射出構造の発光素子について示したが、これに限定されない。すなわち、基板側の面から発光を取り出す下面射出(ボトムエミッション)構造の発光素子や、基板側及び基板とは逆側の面から発光を取り出す両面射出(デュアルエミッション)構造の発光素子を採用してもよい。

40

## 【0190】

また、ここでは、発光素子として有機EL素子について述べたが、発光素子として無機EL素子を用いてもよい。

## 【0191】

なお、本実施の形態では、発光素子の駆動を制御する薄膜トランジスタ(駆動用薄膜トランジスタ)と発光素子が接続されている例を示したが、駆動用薄膜トランジスタと発光素子との間に電流制御用薄膜トランジスタが接続されていてもよい。

## 【0192】

以上説明したように、発光表示装置を作製することができる。本実施の形態の発光表示

50

装置は、オン電流が高い薄膜トランジスタを画素トランジスタとして用いているため、画質が良好（例えば、高コントラスト）であり、且つ消費電力の低い発光表示装置とすることができる。

【0193】

（実施の形態8）

次に、表示装置が有する表示パネルの構成の一例について説明する。

【0194】

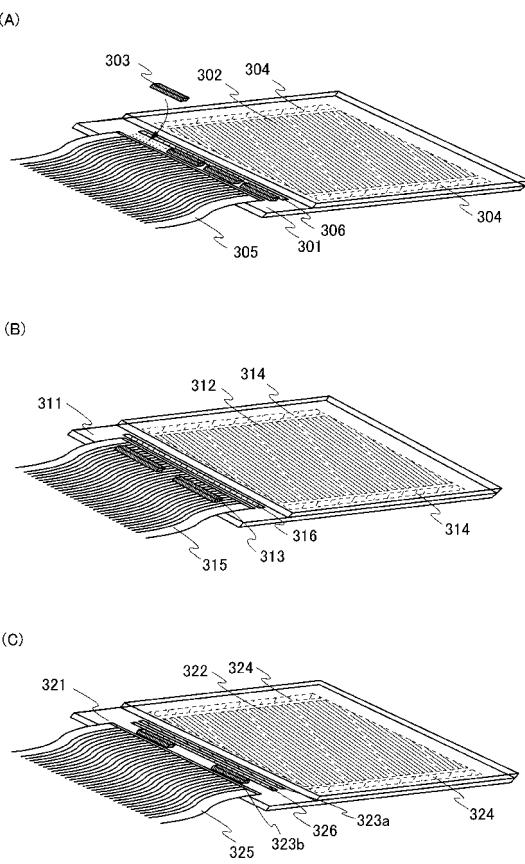

図21(A)は、信号線駆動回路303のみを別途形成し、基板301上に形成された画素部302と接続させた表示パネルの形態を示す。画素部302、保護回路306、及び走査線駆動回路304が形成された素子基板は、実施の形態1等に示す薄膜トランジスタを用いて形成する。信号線駆動回路303は、単結晶半導体を用いたトランジスタ、多結晶半導体を用いたトランジスタ、またはSOI(Silicon On Insulator)を用いたトランジスタにより構成すれば良い。SOIを用いたトランジスタには、ガラス基板上に単結晶半導体層を設けたトランジスタを含む。画素部302と、信号線駆動回路303と、走査線駆動回路304とに、それぞれ電源の電位及び各種信号等が、FPC305を介して供給される。保護回路306は、その他の構造の薄膜トランジスタ、ダイオード、抵抗素子及び容量素子等から選択された1つ又は複数の素子によって設けてもよい。

【0195】

なお、信号線駆動回路303及び走査線駆動回路304を、画素部の画素トランジスタと同じ基板上に形成しても良い。

【0196】

また、駆動回路を別途形成する場合には、必ずしも駆動回路が形成された基板を、画素部が形成された基板上に貼り合わせる必要はなく、例えばFPC上に貼り合わせるようにしても良い。図21(B)は、信号線駆動回路313のみを別途形成し、基板311上に形成された画素部312、保護回路316、及び走査線駆動回路314が形成された素子基板とFPC315が接続している表示パネルの形態を示す。画素部312、保護回路316及び走査線駆動回路314は、上記の実施の形態にて説明した薄膜トランジスタを用いて形成する。信号線駆動回路313は、FPC315及び保護回路316を介して、画素部312に接続されている。画素部312と、信号線駆動回路313と、走査線駆動回路314のそれぞれに、電源の電位及び各種の信号等が、FPC315を介して入力される。

【0197】

また、信号線駆動回路の一部又は走査線駆動回路の一部のみを、上記の実施の形態に示す薄膜トランジスタを用いて画素部と同じ基板上に形成し、残りを別途形成して画素部と電気的に接続するようにしても良い。図21(C)は、信号線駆動回路が有するアナログスイッチ323aを、画素部322及び走査線駆動回路324と同じ基板321上に形成し、信号線駆動回路が有するシフトレジスタ323bを別途異なる基板に形成して貼り合わせる表示パネルの形態を示す。画素部322、保護回路326、及び走査線駆動回路324は、上記の実施の形態に示す薄膜トランジスタを用いて形成する。信号線駆動回路が有するシフトレジスタ323bは、アナログスイッチ323a及び保護回路326を介して画素部322と接続されている。画素部322と、信号線駆動回路と、走査線駆動回路324のそれぞれに、電源の電位及び各種の信号等が、FPC325を介して入力される。

【0198】

図21に示すように、本実施の形態の表示装置では、信号線駆動回路と走査線駆動回路の一部または全部を、画素部と同じ基板上に形成することができる。一部又は全部が画素部と同じ基板上に形成された信号線駆動回路と走査線駆動回路に設けられる薄膜トランジスタは、上記の実施の形態にて説明したように形成することができる。なお、表示装置の構成は上記説明に限定されない。例えば、特に必要のない場合には、保護回路は設けなく

10

20

30

40

50

てもよい。

【0199】

なお、別途回路を形成した基板の接続方法は、特に限定されるものではなく、公知のCOG方式、ワイヤボンディング方式、或いはTAB方式などを用いることができる。また接続する位置は、電気的な接続が可能であるならば、図21に示した位置に限定されない。また、コントローラ、CPU又はメモリ等を別途形成し、接続するようにしても良い。

【0200】

なお、信号線駆動回路は、シフトレジスタとアナログスイッチを有する。または、シフトレジスタとアナログスイッチに加え、バッファ、レベルシフタ、ソースフォロワ等、他の回路を有していても良い。また、シフトレジスタとアナログスイッチは必ずしも設ける必要はなく、例えばシフトレジスタの代わりにデコーダ回路のような信号線の選択ができる別の回路を用いても良いし、アナログスイッチの代わりにラッチ等を用いても良い。

【0201】

(実施の形態9)

上記実施の形態の薄膜トランジスタで構成される素子基板及びこれを用いた表示装置等は、アクティブマトリクス型の表示装置パネルに適用することができる。更には、これらを表示部に組み込んだ電子機器に適用することもできる。

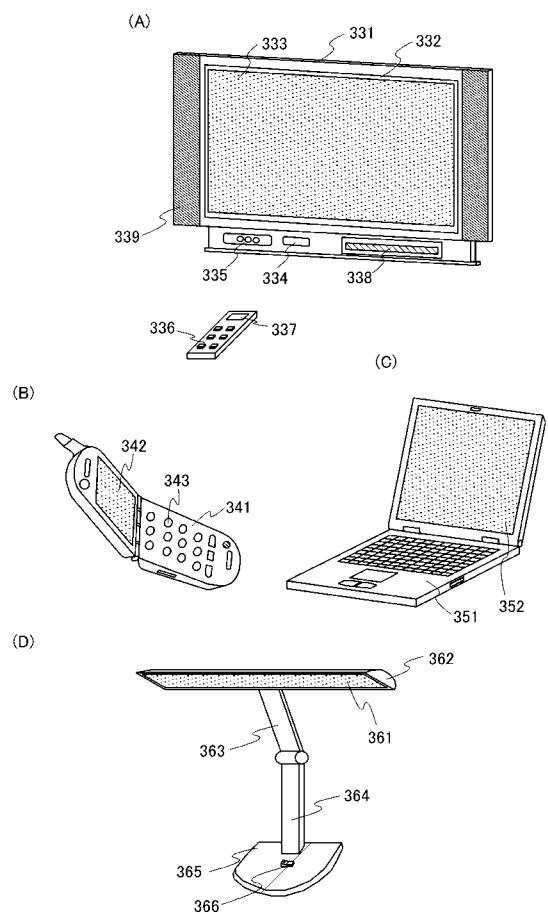

【0202】

その様な電子機器としては、ビデオカメラ及びデジタルカメラ等のカメラ、ヘッドマウントディスプレイ（ゴーグル型ディスプレイ）、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話または電子書籍等）などが挙げられる。それらの一例を図22に示す。

【0203】

図22(A)はテレビジョン装置である。上記の実施の形態を適用した表示パネルを筐体に組みこんで、テレビジョン装置を完成させることができる。表示パネルにより主画面333が形成され、その他付属設備としてスピーカ部339及び操作スイッチなどが備えられている。

【0204】

図22(A)に示すように、筐体331に表示素子を利用した表示パネル332が組みこまれ、受信機335により一般的のテレビ放送の受信をはじめ、モデム334を介して有線又は無線による通信ネットワークに接続することにより片方向（送信者から受信者）又は双方向（送信者と受信者間、又は受信者間同士）の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又はリモコン操作機336により行うことが可能であり、このリモコン装置にも出力する情報を表示する表示部337が設けられていても良く、表示部337に実施の形態1等の薄膜トランジスタが設けられていてもよい。また、主画面333の他にサブ画面338を第2の表示パネルで形成し、チャンネルや音量などを表示する構成が付加されていても良い。この構成において、主画面333及びサブ画面338の一方又は双方に実施の形態1等の薄膜トランジスタを適用することができる。

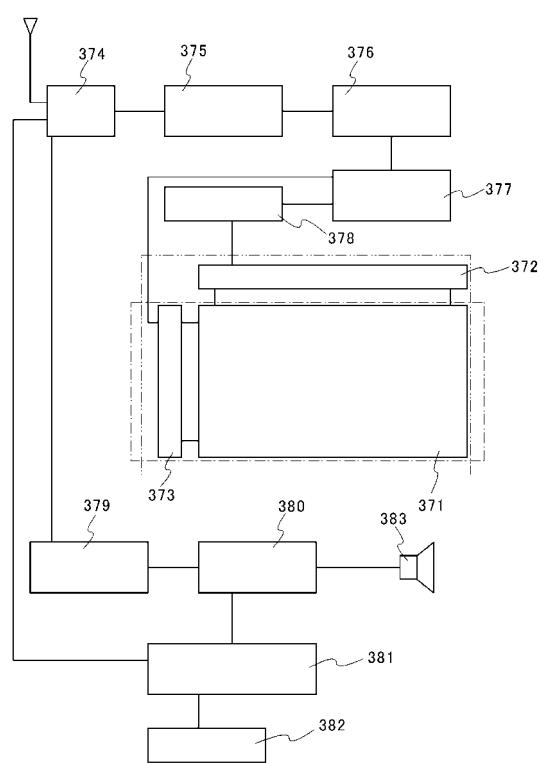

【0205】

図23は、テレビ装置の主要な構成を説明するブロック図を示している。表示パネルには、画素部371が形成されている。信号線駆動回路372と走査線駆動回路373は、表示パネルにCOG方式により実装されていても良い。

【0206】

また、その他の外部回路の構成として、映像信号の入力側には、チューナ374で受信した信号のうち、映像信号を増幅する映像信号増幅回路375と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路376と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路377等が設けられている。コントロール回路377は、走査線側と信号線側にそれぞれ信号を出力する。デジタル駆動する場合には、信号線側に信号分割回路378を設け、入力デジタル信号をm個

10

20

30

40

50

に分割して入力する構成としても良い。

【0207】

チューナ374で受信した信号のうち、音声信号は、音声信号增幅回路379に送られ、その出力は音声信号処理回路380を経てスピーカ383に入力される。制御回路381は受信局（受信周波数）や音量の制御情報を入力部382から受け、チューナ374や音声信号処理回路380に信号を送出する。

【0208】

勿論、テレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表示媒体に適用してもよい。

10

【0209】

以上説明したように、主画面333及びサブ画面338の一方又は双方に実施の形態1等で説明した薄膜トランジスタを適用することで、画質が高く、消費電力の低いテレビ装置を作製することができる。

【0210】

図22（B）は、携帯電話機341の一例を示している。携帯電話機341は、表示部342、操作部343等により構成されている。表示部342に実施の形態1等で説明した薄膜トランジスタを適用することで、画質を向上させ、消費電力を低減させることができる。

【0211】

図22（C）に示す携帯型のコンピュータは、本体351、表示部352等を含んでいる。表示部352に、実施の形態1等で説明した薄膜トランジスタを適用することで、画質を向上させ、消費電力を低減させることができる。

20

【0212】

図22（D）は卓上照明器具であり、照明部361、傘362、可変アーム363、支柱364、台365、電源366を含む。上記の実施の形態で説明した発光表示装置を照明部361に用いることにより作製される。照明部361に実施の形態1等で説明した薄膜トランジスタを適用することで、消費電力を低減させることができる。

【0213】

図24は携帯電話機の構成の一例を示しており、例えば表示部に実施の形態1等で示した薄膜トランジスタを有する素子基板及びそれを有する表示装置が適用される。図24（A）が正面図、図24（B）が背面図、図24（C）が展開図である。図24に示す携帯電話機は、筐体394及び筐体385の二つの筐体で構成されている。図24に示す携帯電話機は、携帯電話と携帯情報端末の双方の機能を備えており、コンピュータを内蔵し、音声通話以外にも様々なデータ処理が可能であり、スマートフォンとも呼ばれる。

30

【0214】

筐体394においては、表示部386、スピーカ387、マイクロフォン388、操作キー389、ポインティングディバイス390、表面カメラ用レンズ391、外部接続端子ジャック392、イヤホン端子393等を備え、筐体385においては、キーボード395、外部メモリスロット396、裏面カメラ397、ライト398等により構成されている。また、アンテナは筐体394に内蔵されている。

40

【0215】

また、上記の構成に加えて、非接触ICチップ又は小型記録装置等を内蔵していくてもよい。

【0216】

図24（A）では筐体394と筐体385が重なり合っており、図24（A）の状態から筐体394と筐体385がスライドし、図24（C）のように展開する。表示部386には、実施の形態1等における表示装置を組み込むことが可能であり、使用形態に応じて表示の方向が適宜変化する。なお、表示部386と同一面に表面カメラ用レンズ391を備えているため、テレビ電話が可能である。また、表示部386をファインダーとして裏

50

面カメラ 397 及びライト 398 で静止画及び動画の撮影が可能である。

【0217】

スピーカ 387 及びマイクロフォン 388 は音声通話に限らず、テレビ電話、音声の録音及び再生等の用途に使用できる。操作キー 389 では、電話の発着信、電子メール等の簡単な情報入力、画面のスクロール及びカーソル移動等が可能である。

【0218】

また、書類の作成、携帯情報端末としての使用等、取り扱う情報が多い場合は、キーボード 395 を用いると便利である。重なり合った筐体 394 と筐体 385 ( 図 24 ( A ) ) はスライドでき、図 24 ( C ) のように展開して携帯情報端末として使用できる。また、キーボード 395 及びポインティングディバイス 390 を用いることで、円滑な操作でマウスの操作が可能である。外部接続端子ジャック 392 は A C アダプタ及び U S B ケーブル等の各種ケーブルと接続可能であり、これを介して充電やパーソナルコンピュータ等とのデータ通信が可能である。また、外部メモリスロット 396 に記録媒体を挿入して使用することで、大量のデータの保存及び移動が可能である。

10

【0219】

筐体 385 の裏面 ( 図 24 ( B ) ) には、裏面カメラ 397 及びライト 398 を備えており、表示部 386 をファインダーとして静止画及び動画の撮影が可能である。

【0220】

また、上記の構成に加えて、赤外線通信機能、 U S B ポート、テレビワンセグ受信機能、非接触 I C チップ、イヤホンジャック等を備えていてもよい。

20

【0221】

実施の形態 1 等で説明した薄膜トランジスタを画素に適用することで、画質を向上させ、消費電力を低減させることができる。

【符号の説明】

【0222】

|     |                    |    |

|-----|--------------------|----|

| 100 | 基板                 | 30 |

| 102 | ゲート電極層             |    |

| 104 | ゲート絶縁層             |    |

| 105 | 半導体層               |    |

| 106 | 半導体層               |    |

| 109 | ドナーとなる不純物元素を含む半導体層 |    |

| 110 | ソース領域及びドレイン領域      |    |

| 111 | 導電層                |    |

| 112 | 配線層                |    |

| 114 | 絶縁層                |    |

| 116 | 画素電極層              |    |

| 120 | 第 1 の領域            |    |

| 121 | 結晶粒                |    |

| 122 | 第 2 の領域            |    |

| 131 | 第 1 のレジストマスク       | 40 |

| 132 | 第 2 のレジストマスク       |    |

| 141 | 処理室                |    |

| 142 | ステージ               |    |

| 143 | ガス供給部              |    |

| 144 | シャワープレート           |    |

| 145 | 排気口                |    |

| 146 | 上部電極               |    |

| 147 | 下部電極               |    |

| 148 | 交流電源               |    |

| 149 | 温度制御部              | 50 |

|       |                    |    |

|-------|--------------------|----|

| 1 5 0 | ガス供給手段             |    |

| 1 5 1 | 排気手段               |    |

| 1 5 2 | シリンド               |    |

| 1 5 3 | 圧力調整弁              |    |

| 1 5 4 | ストップバルブ            |    |

| 1 5 5 | マスフローコントローラ        |    |

| 1 5 6 | バタフライバルブ           |    |

| 1 5 7 | コンダクタンスバルブ         |    |

| 1 5 8 | ターボ分子ポンプ           |    |

| 1 5 9 | ドライポンプ             | 10 |

| 1 6 0 | クライオポンプ            |    |

| 1 6 1 | プラズマ CVD 装置        |    |

| 1 8 0 | グレートーンマスク          |    |

| 1 8 1 | 基板                 |    |

| 1 8 2 | 遮光部                |    |

| 1 8 3 | 回折格子部              |    |

| 1 8 5 | ハーフトーンマスク          |    |

| 1 8 6 | 基板                 |    |

| 1 8 7 | 半透光部               |    |

| 1 8 8 | 遮光部                | 20 |

| 2 0 0 | 基板                 |    |

| 2 0 2 | ゲート電極層             |    |

| 2 0 4 | ゲート絶縁層             |    |

| 2 0 5 | 半導体層               |    |

| 2 0 6 | 半導体層               |    |

| 2 0 9 | ドナーとなる不純物元素を含む半導体層 |    |

| 2 1 0 | ソース領域及びドレイン領域      |    |

| 2 1 1 | 導電層                |    |

| 2 1 2 | 配線層                |    |

| 2 1 4 | 絶縁層                | 30 |

| 2 1 6 | 画素電極層              |    |

| 2 3 1 | 第1のレジストマスク         |    |

| 2 3 2 | 第2のレジストマスク         |    |

| 2 5 0 | 基板                 |    |

| 2 5 1 | 対向基板               |    |

| 2 5 2 | ゲート電極              |    |

| 2 5 3 | ゲート電極              |    |

| 2 5 4 | 配線                 |    |

| 2 5 5 | 配線                 |    |

| 2 5 6 | 配線                 | 40 |

| 2 5 7 | 絶縁層                |    |

| 2 5 8 | 平坦化膜               |    |

| 2 5 9 | 開口部                |    |

| 2 6 0 | 画素電極               |    |

| 2 6 1 | スリット               |    |

| 2 6 2 | 画素電極               |    |

| 2 6 3 | 開口部                |    |

| 2 6 4 | 薄膜トランジスタ           |    |

| 2 6 5 | 薄膜トランジスタ           |    |

| 2 6 6 | 遮光膜                | 50 |

|         |          |    |

|---------|----------|----|

| 2 6 7   | 着色膜      |    |

| 2 6 8   | 平坦化膜     |    |

| 2 6 9   | 対向電極     |    |

| 2 7 0   | スリット     |    |

| 2 7 1   | 配向膜      |    |

| 2 7 2   | 配向膜      |    |

| 2 7 3   | 液晶層      |    |

| 2 8 0   | 容量素子     |    |

| 2 8 1 a | 薄膜トランジスタ | 10 |

| 2 8 1 b | 薄膜トランジスタ |    |

| 2 8 2   | 発光素子     |    |

| 2 8 3 a | 走査線      |    |

| 2 8 3 b | ゲート電極    |    |

| 2 8 4 a | 信号線      |    |

| 2 8 4 b | 配線       |    |

| 2 8 5 a | 電源線      |    |

| 2 8 5 b | 配線       |    |

| 2 8 6   | 絶縁層      |    |

| 2 8 7   | 平坦化膜     |    |

| 2 8 8   | 陰極       | 20 |

| 2 8 9   | E L 層    |    |

| 2 9 0   | 陽極       |    |

| 2 9 1   | 隔壁       |    |

| 2 9 2   | 保護絶縁膜    |    |

| 3 0 1   | 基板       |    |

| 3 0 2   | 画素部      |    |

| 3 0 3   | 信号線駆動回路  |    |

| 3 0 4   | 走査線駆動回路  |    |

| 3 0 5   | F P C    |    |

| 3 0 6   | 保護回路     | 30 |

| 3 1 1   | 基板       |    |

| 3 1 2   | 画素部      |    |

| 3 1 3   | 信号線駆動回路  |    |

| 3 1 4   | 走査線駆動回路  |    |

| 3 1 5   | F P C    |    |

| 3 1 6   | 保護回路     |    |

| 3 2 1   | 基板       |    |

| 3 2 2   | 画素部      |    |

| 3 2 3 a | アナログスイッチ |    |

| 3 2 3 b | シフトレジスタ  | 40 |

| 3 2 4   | 走査線駆動回路  |    |

| 3 2 5   | F P C    |    |

| 3 2 6   | 保護回路     |    |

| 3 3 1   | 筐体       |    |

| 3 3 2   | 表示パネル    |    |

| 3 3 3   | 主画面      |    |

| 3 3 4   | モデル      |    |

| 3 3 5   | 受信機      |    |

| 3 3 6   | リモコン操作機  |    |

| 3 3 7   | 表示部      | 50 |

|       |              |    |

|-------|--------------|----|

| 3 3 8 | サブ画面         |    |

| 3 3 9 | スピーカ部        |    |

| 3 4 1 | 携帯電話機        |    |

| 3 4 2 | 表示部          |    |

| 3 4 3 | 操作部          |    |

| 3 5 1 | 本体           |    |

| 3 5 2 | 表示部          |    |

| 3 6 1 | 照明部          |    |

| 3 6 2 | 傘            |    |

| 3 6 3 | 可変アーム        | 10 |

| 3 6 4 | 支柱           |    |

| 3 6 5 | 台            |    |

| 3 6 6 | 電源           |    |

| 3 7 1 | 画素部          |    |

| 3 7 2 | 信号線駆動回路      |    |

| 3 7 3 | 走査線駆動回路      |    |

| 3 7 4 | チューナ         |    |

| 3 7 5 | 映像信号增幅回路     |    |

| 3 7 6 | 映像信号処理回路     |    |

| 3 7 7 | コントロール回路     | 20 |

| 3 7 8 | 信号分割回路       |    |

| 3 7 9 | 音声信号增幅回路     |    |

| 3 8 0 | 音声信号処理回路     |    |

| 3 8 1 | 制御回路         |    |

| 3 8 2 | 入力部          |    |

| 3 8 3 | スピーカ         |    |

| 3 8 5 | 筐体           |    |

| 3 8 6 | 表示部          |    |

| 3 8 7 | スピーカ         |    |

| 3 8 8 | マイクロフォン      | 30 |

| 3 8 9 | 操作キー         |    |

| 3 9 0 | ポインティングディバイス |    |

| 3 9 1 | 表面カメラ用レンズ    |    |

| 3 9 2 | 外部接続端子ジャック   |    |

| 3 9 3 | イヤホン端子       |    |

| 3 9 4 | 筐体           |    |

| 3 9 5 | キーボード        |    |

| 3 9 6 | 外部メモリスロット    |    |

| 3 9 7 | 裏面カメラ        |    |

| 3 9 8 | ライト          | 40 |

【図1】

【図3】

【図2】

【図5】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

## 【図18】

【図19】

【図20】

### 【図21】

【図22】

【図23】

【図24】

---

フロントページの続き

(72)発明者 伊佐 敏行

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 大橋 達也

(56)参考文献 特開2005-045269 (JP, A)

特表2004-504721 (JP, A)

特開2001-102587 (JP, A)

特開平07-094749 (JP, A)

鶴飼 育弘, 薄膜トランジスタ技術のすべて 構造, 特性, 製造プロセスから次世代TFTまで

, 日本, 株式会社工業調査会, 2007年10月25日, 第74~79ページ

T. EHARA, Electron spin resonance study of nitrogen-doped microcrystalline silicon and

amorphous silicon, Applied Surface Science, 1997年, Vol.113, p.126-129

H. FUJIWARA et al., Stress-Induced Nucleation of Microcrystalline Silicon from Amorphous Phase, Japanese Journal of Applied Physics, 2002年, Vol.41, p.2811-2828

恵原 貴志 他, 窒素ドープ微結晶及びSiO<sub>2</sub>埋め込み微粒子シリコンの構造特性, 応用物理学関係連合講演会講演予稿集1997, (社)応用物理学会, 1997年, 第855ページ

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786