(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-501524

(P2007-501524A)

(43) 公表日 平成19年1月25日(2007.1.25)

| (51) Int.C1.                  | F 1        | テーマコード (参考) |

|-------------------------------|------------|-------------|

| <b>HO1L 29/786 (2006.01)</b>  | HO1L 29/78 | 613A        |

| <b>HO1L 21/8234 (2006.01)</b> | HO1L 27/08 | 102A        |

| <b>HO1L 27/088 (2006.01)</b>  | HO1L 27/08 | 331E        |

| <b>HO1L 27/08 (2006.01)</b>   | HO1L 29/78 | 613Z        |

|                               | HO1L 29/78 | 618C        |

審査請求 未請求 予備審査請求 未請求 (全 25 頁) 最終頁に続く

|               |                              |          |                                                                                                                                                                                                    |

|---------------|------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2006-522626 (P2006-522626) | (71) 出願人 | 591016172<br>アドバンスト・マイクロ・ディバイシズ・<br>インコーポレイテッド<br>ADVANCED MICRO DEVI<br>CES INCORPORATED<br>アメリカ合衆国、94088-3453<br>カリフォルニア州、サニィベイル、ビィ・<br>オウ・ボックス・3453、ワン・エイ・<br>エム・ディ・プレイス、メイル・ストップ<br>・68 (番地なし) |

| (86) (22) 出願日 | 平成16年7月28日 (2004.7.28)       | (74) 代理人 | 100099324<br>弁理士 鈴木 正剛                                                                                                                                                                             |

| (85) 翻訳文提出日   | 平成18年3月22日 (2006.3.22)       | (74) 代理人 | 100111615<br>弁理士 佐野 良太                                                                                                                                                                             |

| (86) 國際出願番号   | PCT/US2004/024590            |          |                                                                                                                                                                                                    |

| (87) 國際公開番号   | W02005/034207                |          |                                                                                                                                                                                                    |

| (87) 國際公開日    | 平成17年4月14日 (2005.4.14)       |          |                                                                                                                                                                                                    |

| (31) 優先権主張番号  | 10/633,504                   |          |                                                                                                                                                                                                    |

| (32) 優先日      | 平成15年8月5日 (2003.8.5)         |          |                                                                                                                                                                                                    |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                                                                                                                    |

最終頁に続く

(54) 【発明の名称】全般的な設計目標を達成すべく、半導体デバイス中のキャリア移動度の可変な半導体デバイス

## (57) 【要約】

半導体デバイス(100)は、基板(110)、およびこの基板(110)上に形成される絶縁層(120)とを含む。第1デバイス(710)は第1フィン(130)を含む絶縁層(120)上に形成される。この第1フィン(130)は、絶縁層(120)上に形成され、第1アスペクト比を有する。第2デバイス(720)は、第2フィン(130)を含む絶縁層(120)上に形成される。この第2フィン(130)は、絶縁層(120)上に形成され、第1アスペクト比と異なる第2アスペクト比を有する。

**【特許請求の範囲】****【請求項 1】**

基板(110)と、

前記基板(110)上に形成される絶縁層(120)と、

前記絶縁層(120)上に形成されるとともに、第1フィンアスペクト比を有する第1フィン(130)を含む、前記絶縁層(120)上に形成される第1デバイス(710)と、

前記絶縁層(120)上に形成されるとともに、前記第1フィンアスペクト比と異なる第2フィンアスペクト比を有する第2フィン(130)を含む、前記絶縁層(120)上に形成される第2デバイス(720)と、

を含む、半導体デバイス(100)。

**【請求項 2】**

前記第1デバイス(710)はN M O Sデバイスであり、前記第2デバイス(720)はP M O Sデバイスである、請求項1記載の半導体デバイス(100)。

**【請求項 3】**

前記第1デバイス(710)および前記第2デバイス(720)は、単一の回路素子に含まれる、請求項1記載の半導体デバイス(100)。

**【請求項 4】**

前記第1デバイス(710)の前記第1フィン(130)の第1キャリア移動度は、前記第2デバイス(720)の前記第2フィン(130)の第2キャリア移動度と異なる、

請求項1記載の半導体デバイス(100)。

**【請求項 5】**

前記第1デバイス(710)は、

前記第1フィン(130)の少なくとも3つの面上に形成される第1ゲート絶縁層(410)(510)(610)と、

前記第1フィン(130)の少なくとも3つの面上に形成される第1ゲート材料層(420)(520)(620)と、

をさらに含んでおり、

前記第2デバイス(720)は、

前記第2フィン(130)の少なくとも3つの面上に形成される第2ゲート絶縁層(410)(510)(610)と、

前記第2フィン(130)の少なくとも3つの面上に形成される第1ゲート材料層(420)(520)(620)と、

をさらに含む、請求項1記載の半導体デバイス(100)。

**【請求項 6】**

前記第1ゲート絶縁層(610)と前記第1ゲート材料層(620)は、前記第1フィン(130)の4つの面上に形成される、請求項5記載の半導体デバイス(100)。

**【請求項 7】**

前記第2ゲート絶縁層(610)と前記第2ゲート材料層(620)は、前記第2フィン(130)の4つの面上に形成される、請求項6記載の半導体デバイス(100)。

**【請求項 8】**

絶縁層(120)と、

前記絶縁層(120)上に形成され、第1高さおよび第1幅を有する第1フィン(130)、前記第1フィン(130)の少なくとも3つの面上に形成される第1ゲート絶縁層(410)(510)(610)、および前記第1ゲート絶縁層(410)(510)(610)に隣接する第1ゲート(430)(530)(630)を含む、前記絶縁層(120)上に形成される第1デバイス(710)と、

前記絶縁層(120)上に形成され、第2高さおよび第2幅を有する第2フィン(130)、前記第2フィン(130)の少なくとも3つの面上に形成される第2ゲート絶縁層(410)(510)(610)、および前記第2ゲート絶縁層(410)(510)(610)を含む、前記絶縁層(120)上に形成される第2デバイス(720)。

610)に隣接する第2ゲート(430)(530)(630)を含む、前記絶縁層(120)上に形成される第2デバイス(720)と、

を含み、前記第1高さと前記第1幅の第1比は、前記第2高さと前記第2幅の第2比と異なる、

半導体デバイス(100)。

【請求項9】

前記絶縁層(120)上に形成され、第3高さおよび第3幅を有する第3フィン(130)、前記第3フィン(130)の少なくとも3つの面上に形成される第3ゲート絶縁層(410)(510)(610)、および前記第3ゲート絶縁層(410)(510)(610)に隣接する第3ゲート(430)(530)(630)を含む、前記絶縁層(120)上に形成される第3デバイス(730)をさらに含んでおり、

前記第3高さと前記第3幅の第3比は、前記第1比および前記第2比と異なる、請求項8記載の半導体デバイス(100)。

【請求項10】

絶縁層(120)と、

前記絶縁層(120)上に形成され、第1高さおよび第1幅を有する第1フィン(130)を含む、前記絶縁層(120)上に形成されるN型デバイス(710)と、

前記絶縁層(120)上に形成され、第2高さおよび第2幅を有する第2フィン(130)を含む、前記絶縁層(120)上に形成されるP型デバイス(720)と、

を含んでおり、

前記第2幅は、前記第1幅の所定倍であり、

前記N型デバイス(710)のキャリア移動度が前記P型デバイス(720)のキャリア移動度とほぼ等しいように、前記第1高さおよび前記第2高さが形成される、

半導体デバイス(100)。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイス、および半導体デバイスを製造する方法に関する。本発明は特に、ダブルゲートデバイスに適用することができる。

【背景技術】

【0002】

超々大規模集積回路の半導体デバイスに関する密度の高さ、性能の高さに対する拡大する要求は、100ナノメータ(nm)未満のゲート長のような構造的要素、高い信頼性、および製造処理能力の向上を要求する。構造的要素を100nm未満に減少することは、従来の方法の限界に挑むこととなる。

【0003】

例えば、従来のプレーナ型のMOS電界効果トランジスタ(MOSFET)のゲート長を100nm未満にスケーリングした場合、ソースおよびドレイン間の過度の漏れ電流のような短チャネル効果に関連する問題を克服することができます困難になる。さらに、移動度低下および多くのプロセス問題によって、さらに小さなデバイス構造を含めるように従来のMOSFETをスケーリングすることが困難になる。

したがって、FET性能を改善するとともにさらなるデバイス・スケーリングを可能とすべく、新規なデバイス構造が求められている。

【0004】

ダブルゲートMOSFETは、既存のプレーナ型のMOSFETに代わる候補となっている新規なデバイスである。いくつかの点において、ダブルゲートMOSFETは従来のバルクシリコンMOSFETよりも優れた特性を呈する。

これらの優れた特性は、ダブルゲートMOSFETが従来のMOSFETのようにチャネルの片側だけではなくチャネルの2つの側にゲート電極を有することから生ずる。

2つのゲートがある場合、ドレインによって生成される電界はチャネルのソース端から

10

20

30

40

50

より遮断される。また、2つのゲートはシングルゲートのおよそ2倍の電流を制御することができ、これによりスイッチング信号がより強くなる。

【0005】

FinFETは、短チャネル耐性に優れている最近のMOSFET構造である。

FinFETは、バーティカルフィン(vertical fin)中に形成されるバーティカルチャネルを含んでいる。このFinFET構造は、従来のプレーナ型のMOSFETで使用されるのと同様のレイアウトや製造技術を使用して製造することができる。

【発明の開示】

【0006】

本発明の一形態は、第1フィン・アスペクト比を有する第1FinFETデバイスと、10 第2フィン・アスペクト比を有する第2FinFETデバイスとを提供する。

【0007】

本発明のさらなる利点および他の構造は、以下の詳細な説明で記載される。そしてその一部は、以下の検討に基づいて当業者に明白になるであろう。または本発明を実行することによって認識できる。本発明の利点および構造は、添付された請求項で特に指摘されるように理解され、達成される。

【0008】

本発明によれば、前述およびその他の利点の一部は、基板と、この基板上に形成された絶縁層を含む半導体デバイスによって達成される。

絶縁層上に、第1フィンを含む第1デバイスを形成してもよい。この第1フィンは、絶縁層上に形成され第1フィン・アスペクト比を有し得る。絶縁層上に、第2フィンを含む第2デバイスを形成してもよい。この第2フィンは、絶縁層上に形成され第1フィン・アスペクト比と異なる第2フィン・アスペクト比を有し得る。20

【0009】

本発明の他の態様によれば、半導体デバイスは、絶縁層、およびこの絶縁層上に形成される第1デバイスを含んでいてもよい。

この第1デバイスは、絶縁層上に形成され、第1高さおよび第1幅を有する第1フィンを含むことができる。この第1デバイスはまた、第1フィンの少なくとも3つの側面に形成される第1絶縁層、および第1ゲートを含み得る。

第2デバイスは絶縁層上に形成される。この第2デバイスは、絶縁層上に形成される。この第2デバイスは、絶縁層上に形成され、第2高さおよび第2幅を有している第2フィンを含んでいる。この第2デバイスはまた、第2フィンの少なくとも3つの側面に形成される第2絶縁層、およびこの第2絶縁層に隣接する第2ゲートを含み得る。30

第1高さおよび第1幅の第1比は、第2高さおよび第2幅の第2比と異なる。

【0010】

本発明のさらなる態様によれば、半導体デバイスは、絶縁層、およびこの絶縁層上に形成されるN型デバイスを含んでいてもよい。

このN型デバイスは、絶縁層上に形成され、第1高さおよび第1幅を有する第1フィンを含み得る。P型デバイスは、絶縁層上に形成され得る。このP型デバイスは、絶縁層上に形成され、第2高さおよび第2幅を有している第2フィンを含み得る。第2幅は、第1幅の所定倍であり得る。N型デバイスのキャリア移動度がP型のデバイスのキャリア移動度とほぼ等しいように、第1高さおよび第2高さを形成してもよい。40

【0011】

本発明の他の利点および構成は、以下の詳細な説明から、当業者に容易に明白になるであろう。図示および記載した実施形態は、本発明を実行するために熟考された最良のモードの例として、記載されている。本発明は、この発明内のすべての様々な明白な点における修正例ができる。このように、図面は、本来例示的なものであって、制限的なものではないとみなされる。

同じ参照符号を有する要素は類似の要素を示している、添付した図面を参照する。

【発明を実施するための最良の形態】

## 【0012】

以下、添付の図面に言及して本発明の実施形態を詳細に記載する。異なる図面における同一の参照符号は、同一又は類似の要素を示す。また、以下の詳細な記載は本発明を制限するものではない。代わりに、本発明の範囲は添付の請求項および均等物によって定義される。

## 【0013】

本発明による実施形態は異なるフィン・アスペクト比を有する異なるFinFETを提供する。これらの異なるフィン・アスペクト比はFinFETデバイスの全体的なキャリア移動度を調整するのに使用することができる。

## 【0014】

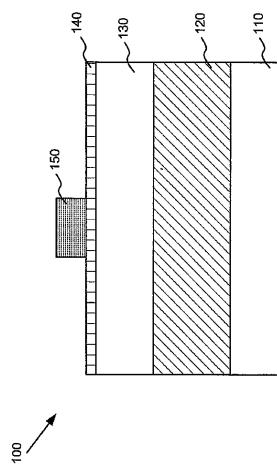

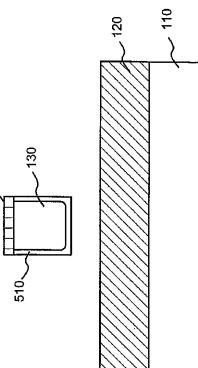

図1は、本発明の実施形態に従って形成された半導体デバイス100の断面図である。

図1等においては1つのデバイス100を示すが、半導体分野における当業者は、ここに記載されるプロセスを使用して、半導体デバイス100と同時に同じウェーハ（またはウェーハの一部、チップ等）上に他のデバイス（例えば、図7の半導体デバイス710、720等）を形成してもよいことを理解するであろう。

図1を参照して、半導体デバイス100は、シリコン基板110、埋込酸化膜120、および埋込酸化膜120上のシリコン層130を含んだSOI（silicon on insulator）構造を含んでいてもよい。埋込酸化膜120およびシリコン層130を、従来の方法により基板110上に形成してもよい。

## 【0015】

例示的な実施形態においては、埋込酸化膜120は酸化シリコンを含んでおり、約1000から約3000の範囲の厚みを有し得る。

シリコン層130は、約300から約1500の範囲の厚みを有する多結晶シリコン、または単結晶シリコンを含んでいてもよい。

以下に詳述するように、シリコン層130は、ダブルゲート・トランジスタデバイスのフィン構造を形成するのに使用される。

## 【0016】

本発明の他の実施形態では、基板110および層130は、ゲルマニウムのような他の半導体材料、またはシリコンゲルマニウムのような半導体材料の組合せを含んでいてもよい。埋込酸化膜120もまた、他の絶縁材料を含んでいてもよい。

## 【0017】

後のエッティングプロセスの間に保護キャップとしての役割を果たすシリコン窒化物層または酸化シリコン層（例えばSiO<sub>2</sub>）のようなトップ絶縁層140を、シリコン層130上に形成することができる。

例示的な実施形態においては、絶縁層140は約150から約700の範囲の厚みでたい積することができる。次に、後の処理のためのフォトレジストマスク150を形成すべく、フォトレジスト材料をたい積してパターン化してもよい。このフォトレジスト材料は、任意の従来方法によりたい積すると共にパターン化することができる。

## 【0018】

その後、半導体デバイス100をエッティングすることができる。例示的な実施形態の1つにおいては、従来の方法で絶縁層140およびシリコン層130をエッティングするとともにこのエッティングを埋込酸化膜120の上で停止させ、フィンを形成してもよい。その後、フォトレジストマスク150を除去してもよい。

このフィンを形成した後、（例えば半導体材料のたい積またはエピタキシャル成長によって）フィンの各端部に隣接するソースおよびドレイン領域を形成することができる。

例えば、例示的な実施形態の一例では、ソースおよびドレイン領域を形成すべく、シリコン、ゲルマニウム、またはシリコンとゲルマニウムを組合せた層を従来の方法でたい積し、パターン化し、エッティングしてもよい。

あるいは、フィンを形成するのと同じフォトリソグラフィプロセスでこのソースおよびドレイン領域を形成してもよい。

10

20

30

40

50

## 【0019】

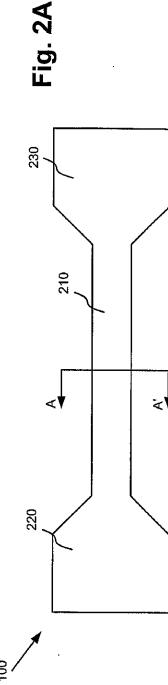

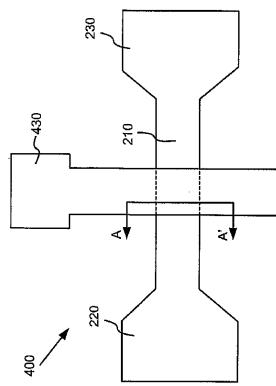

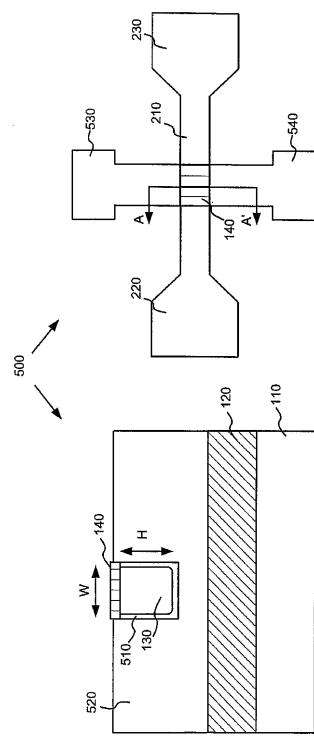

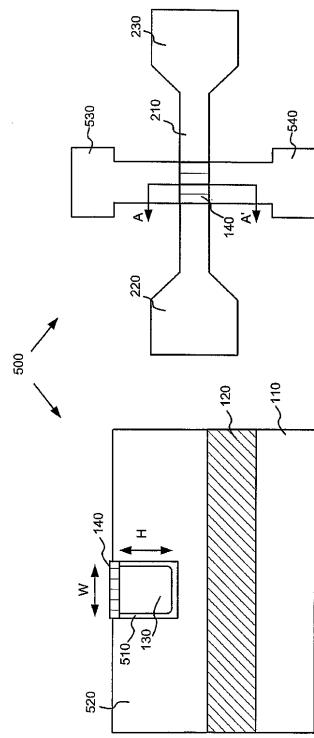

図2Aは、このような方法で形成された半導体100上のフィン構造の概略的な上面図である。

本発明の例示的な実施形態によれば、ソース領域220およびドレイン領域230は、埋込酸化膜120上のフィン構造210の端部に隣接するように形成することができる。

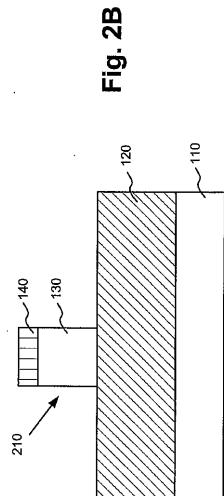

## 【0020】

図2Bは、本発明の例示的な実施形態によるフィン構造210の構成を示す図2AのA-A'線に沿った断面図である。上述したように、構造210を形成すべく、絶縁層140およびシリコン層130をエッティングすることができる。この構造210は、シリコン130および絶縁性のキャップ140を含んでいてもよい。例示的な実施形態においては、シリコンフィン130の幅は約100から約1000の範囲とすることができます。

## 【0021】

ソース/ドレイン領域220、230は、この時点でもまたは後のプロセス段階で（例えばゲートの形成後）ドープすることができる。例えば、n型またはp型不純物をソース/ドレイン領域220、230に注入してもよい。特定の端末装置の必要条件に基づき、特定の注入量およびエネルギーを選択してもよい。当業者は、回路必要条件に基づいてソース/ドレイン注入プロセスを最適化することができるであろう。また、このようなステップは本発明の要旨を過度に不明瞭にしないようにすべく、ここに開示しない。

その後、ソース/ドレイン領域220、230を活性化すべく、活性アニーリングを実行することができる。

## 【0022】

異なる構成の様々なFinFETデバイスを、図2Aおよび図2Bに示したデバイス100から形成することができる。このような異なるFinFETデバイスには、（1）ダブルゲートFinFET、（2）ゲートFinFET、（3）uゲートFinFET、および（または）（4）ラウンドゲートFinFETが含まれる。FinFETのこれら4つの例示的なタイプのデバイスを、以下、本発明の趣旨に沿って記載する。

## 【0023】

## &lt;ダブルゲートFinFET&gt;

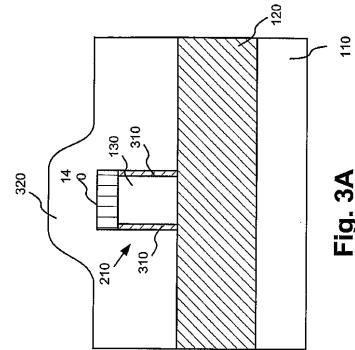

図3Aは、例示的な実施形態による図2Aおよび図2Bの構造210からのダブルゲートFinFET300の形成を示す断面図である。

図3Aに示すように、フィン130の露出した側面上に比較的薄いゲート酸化膜310を形成することができる。例えば、ゲート酸化膜310をフィン130上に熱成長させてよい。ゲート酸化膜310を、フィン130の側面上に約50から約150の厚さに成長させてよい。

## 【0024】

ゲート酸化膜310を形成した後、ゲート材料層320をフィン構造210上にたい積することができる。

例示的な実施形態の一例においては、ゲート材料層320は、従来の化学蒸着法(CVD)またはその他周知の技術を使用してたい積されたポリシリコンを含んでいてもよい。あるいは、ゲルマニウムまたはシリコンおよびゲルマニウムの組合せのよう他の半導体材料、または様々な金属を、層320のゲート材料として使用してもよい。

## 【0025】

図3Bの上面図に記載するように、ゲート材料層320にゲートをパターン化するとともにエッティングして、フィン210のチャネル領域を横切って広がるゲート構造330を形成してもよい。

生成されたデバイス300を、広く「ダブルゲートFinFET」と呼ぶことができる。

## 【0026】

ゲート構造330はリソグラフィ（例えばフォトリソグラフィ）によってゲート材料層320に形成することができる。

10

20

30

40

50

図3Aおよび図3Bには示していないが、ゲート材料層320のエッチングを容易にすべく、ゲート材料層320をプレーナ化してもよいし、底反射防止膜(BARC)および場合によってはトップ反射防止(TAR)膜(図示しない)をプレーナ化したゲート材料層320にたい積してもよい。

半導体分野における当業者に理解されるであろうように、プレーナ化したゲート材料層320およびBARC層は、上に重なるフォトレジスト層をより正確にパターン化することを容易にすることができます。

その結果、約20nmから約50nm程の小さい寸法を有するゲート構造330のクリティカルディメンション(CD)(すなわち、ゲート寸法のような最小フィーチャサイズ)を形成することができる。

10

#### 【0027】

ゲート構造330は、フィン210の側面に隣接するゲート部分と、フィン210から離れるように配置されたより大きな電極部分を含んでいてもよい。

ゲート構造330の電極部分は、ゲート部分をバイアスする、またはゲート部分を制御する、アクセス可能な電気コンタクトを提供してもよい。

#### 【0028】

再度図3Aを参照すると(図3BのA-A'線の断面)、ダブルゲートFinFET300のフィン130のチャネルは、ゲート酸化膜310に隣接するフィン130の2つの側壁に沿って存在することができる。

フィン130の上面にある比較的厚い絶縁キャップ140により、フィン130の上面にチャネルが形成されないようになっている。

フィン130の2つの側壁に沿ったゲート材料320が、フィン130の側壁に沿った2つのチャネルを制御する2つのゲート(すなわち"ダブルゲート")を構成するので、フィン130の側壁に沿った2つのチャネルは、ダブルゲートFinFET300の「ダブルゲート」という呼び方がされる。

#### 【0029】

このフィン130の2つの側壁は共通の結晶配向(例えば、配向<110>)を有し得る。

フィン130の側壁の結晶配向が共通かつ垂直であるので、ダブルゲートFinFET300のフィン130の幅を変更しても、フィン130の多数キャリアのモビリティ(すなわちN型デバイスにおける電子、P型デバイスにおけるホール)に影響を与えない。

多数キャリアのモビリティは、ダブルゲートFinFET300のフィン130の2つの側壁の共通の結晶配向(例えば、配向<110>)によってもっぱら決定される。

#### 【0030】

##### <ゲートFinFET>

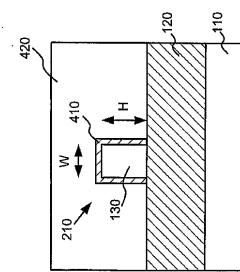

図4Aは、本発明の実施形態による図2Aおよび図2Bの構造210からのゲート(バイゲート)FinFET400の形成を示す断面図である。

まず、(例えば選択エッチングによって)フィン130上の絶縁キャップ140を除去し、埋込酸化膜120上に被覆されていないフィン130を残す。

図4Aに示すように、フィン130の露出した上面および側面に比較的薄いゲート酸化膜410を形成することができる。例えば、ゲート酸化膜410をフィン130上に熱成長させてもよい。ゲート酸化膜410を、フィン130の上面および側面上に約50から約150の厚さに成長させてもよい。

#### 【0031】

ゲート酸化膜410を形成した後、ゲート材料層420をフィン構造210上にたい積することができる。

例示的な実施形態の一例においては、ゲート材料層420は、従来の化学蒸着法(CVD)またはその他周知の技術を使用してたい積されたポリシリコンを含んでいてもよい。あるいは、ゲルマニウムまたはシリコンおよびゲルマニウムの組合せのような他の半導体材料、または様々な金属を、層420のゲート材料として使用してもよい。

40

50

図3Aでは示されていないが、上述したように、後のゲート形成を容易にすべく、図4Aに示すようにゲート材料層420をプレーナ化してもよい。

【0032】

図4Bの上面図に記載するように、ゲート材料層420にゲートをパターン化するとともにエッチングして、フィン210のチャネル領域を横切って広がるゲート構造430を形成してもよい。

生成されたデバイス400を、広く「ゲートFinFET」と呼ぶことができる。

【0033】

ゲート構造430はリソグラフィ（例えばフォトリソグラフィ）によってゲート材料層420に形成することができる。

図4Aおよび図4Bには示していないが、ゲート材料層420のエッチングを容易にすべく、底反射防止膜（BARC）および場合によってはトップ反射防止（TAR）膜（図示しない）をプレーナ化したゲート材料層420にたい積してもよい。

上述したように、プレーナ化したゲート材料層420およびBARC層は、下位ゲートCDを形成し易くする。

【0034】

ゲート構造430は、フィン210の側面に隣接するゲート部分と、フィン210から離れるように配置されたより大きな電極部分を含んでいてもよい。

ゲート構造430の電極部分は、ゲート部分をバイアスする、またはゲート部分を制御する、アクセス可能な電気コンタクトを提供してもよい。

【0035】

再度図4Aを参照すると（図4BのA-A'線の断面）、ゲートFinFET400のフィン130におけるチャネルは、ゲート酸化膜410に隣接するフィン130の2つの側壁に沿って存在することができる。

フィン130の2つの側壁と上面に沿ったゲート材料420が、フィン130の側壁および上面に沿った3つのチャネルを制御する3つのゲート（すなわち、型に）を構成するので、フィン130の2つの側壁と上面に沿った3つのチャネルは、ゲートFinFET400の「ゲート」という呼び方がされる。

【0036】

ゲートFinFET400のフィン130の2つの側壁は共通の結晶配向（例えば、配向<110>）を有しており、フィン130の上面は異なる結晶配向（例えば、配向<100>）を有し得る。

フィン130のチャネルの結晶配向が異なるので、ダブルゲートFinFET300と異なり、ゲートFinFET400のフィン130の幅および（または）高さを変更すると、フィン130の多数キャリアのモビリティに影響を与える。

この点に関して、フィン130についての「フィン・アスペクト比」をH/W（Hがフィン130の高さで、Wがフィン130の幅）として形成することが有用である。図4Aには、ゲートFinFET400のフィン130の高さHと幅Wを示される。

【0037】

多数キャリアについてのキャリアの移動度は、他の結晶の配向（例えば、配向<110>）よりも、ある結晶の配向（例えば、配向<100>）の方が高くなり得る。

2つの異なる結晶方向に沿ったチャネルを有するフィン130については、全体的なキャリア移動度は、フィン130の側面および上面のキャリア移動度の「平均」であり得る。

ここで使用される「平均」という用語は、フィン130の側壁および上面のキャリア移動度を重み付けして組み合わせることをも意味するように緩やかに解釈されるべきであつて、厳密な数学的な平均ではないことを注目すべきである。

このフィン130の全体的なモビリティは、フィン130の側面のチャネルとフィン130の上面のチャネルの端部とが近いとなつた様々な物理的原因により正確な数学的定義ができない可能性がある。

10

20

30

40

50

## 【0038】

しかしながら、フィン・アスペクト比  $H/W$  (すなわち)、フィン 130 の幅  $W$  に対する高さ  $H$  の比率) を変えることによって、フィン 130 の全体的なキャリア移動度を調整することができる。

このフィン 130 の全体的なキャリア移動度は、その結晶配向によりフィン 130 の上面と側面のどちらがより高いキャリア移動度を有するかにより、フィン・アスペクト比  $H/W$  が増加するにつれて増加または低減する。

しかしながら、ここでの開示に基づき、ゲート FinFET 400 のフィン 130 の所望する全体的なキャリア移動度を達成するための、フィン 130 のフィン・アスペクト比  $H/W$  に対する適切な調整 (すなわち、どちらの方向をどれだけ高くするか、または低くするか) を、当業者であれば特段の実験をすることなくできるであろう。

例えば、フィン 130 のフィン・アスペクト比  $H/W$  に対する適切な調節は、使用される特定の製造プロセス / 材料に基づくものであってもよいし、様々なテストデバイスの構築および (または) デバイス・モデリングにより、不要な実験をしないで決定してもよい。

## 【0039】

## &lt;UゲートFinFET&gt;

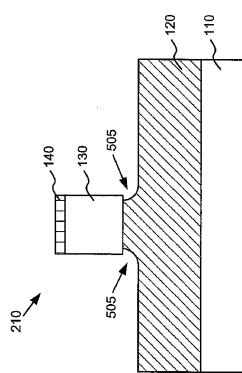

図 5A は、本発明の実施形態による図 2A および図 2B の構造 210 からの U ゲート FinFET 500 の形成を示す断面図である。

図 5A に示すように、埋込酸化膜 120 の部分を除去するのに従来のエッティングケミストリを使用することができる。このエッティングの間、フィン 130 の下の埋込酸化膜 120 の部分を除去することができる。フィン 130 より下の側面のアンダーカットは、フィン 130 より下の埋込酸化膜 120 をさらにエッティングする後のプロセスを促進するに使用することができる。

## 【0040】

その後、フィン 130 より下の埋込酸化膜 120 の一部を貫通する横方向のエッティングを実行すべく、第 2 のエッティングを実行してもよい。

図 3B に示すように、フィン 130 より下に位置する埋込酸化膜 120 を貫通する横方向のエッティングを実行すべく、典型的な実施形態の 1 つにおいては、例えば高圧力の HBr を使用する等方性エッティングを実行してもよい。

フィン 130 は、図 5B に示す断面の埋込酸化膜 120 の上に、実質的にサスペンド (浮遊) されている。

しかしながら、フィン 130 の端部はまだ埋込酸化膜 120 に付着しており、図 5B に示すフィン 210 のサスペンドされた部分は、ソース / ドレイン領域 220、230 のそれぞれと隣接するフィン 210 の端部において埋込酸化膜 120 に支持される。

## 【0041】

その後、ゲート絶縁層をたい積することができる。例えば、図 5C に示すように、ゲート絶縁層として働く薄い酸化膜 510 をフィン 130 の露出した側面および底面に熱成長させてもよい。酸化膜 510 は、約 10 から約 30 の厚さに成長させてもよい。一方、フィン 130 の上面は、絶縁キャップ 140 により保護される。

## 【0042】

その後、図 5C に示すように、フィン構造 210 の周りにゲート材料層 520 をたい積することができる。

ゲート材料層 520 は、後に形成されるゲート電極のゲート材料を含んでいるとともに、従来の化学蒸着法 (CVD) を使用して、約 500 から約 1000 の範囲の厚みにたい積されたポリシリコンを含んでいてもよい。あるいは、ゲルマニウムまたはシリコンおよびゲルマニウムの組合せのような他の半導体材料、または様々な金属を、層 320 のゲート材料として使用してもよい。

## 【0043】

その後、ゲート材料層 520 をプレーナ化することができる。例えば、図 5C に示すよ

10

20

30

40

50

うに、ゲート材料の鉛直方向における高さが絶縁キャップ 140 と等しいまたはほとんど等しくなるように、化学的機械的研磨 (C M P) を実行してもよい。

図 5 C に示すように、フィン 130 のチャネル領域のゲート材料層 520 の断面は U 字型である。またゲート材料は、フィン 130 の 2 つの側面および下面において、フィン 130 を取り囲む。

一方、フィン 130 の上面は、絶縁キャップ 140 によって被覆される。

#### 【0044】

その後、u ゲート F i n F E T 500 のゲート電極 530、540 を形成すべく、ゲート材料層 520 をパターン化し、エッチングしてもよい。

例えば、図 5 D は、ゲート電極 530、540 を形成した後の、本発明の u ゲート F i n F E T 500 の上面図を示す。

10

図示のように、u ゲート F i n F E T 500 は、フィン 130 の側面および底面を囲むゲート材料 520 (図 5 C)、およびゲート電極 530、540 を有する構造を含んでいる。簡略化のため、フィン 210 の側面および下面を取り囲むゲート絶縁膜 410 は、図 7 に図示していない。

#### 【0045】

再度図 5 C を参照すると (図 5 D の A - A' 線の断面)、u ゲート F i n F E T 500 のフィン 130 におけるチャネルは、ゲート酸化膜 510 に隣接するフィン 130 の 2 つの側壁および底面に沿って存在することができる。

フィン 130 の 2 つの側壁と底面に隣接するゲート材料 520 が、フィン 130 の側壁および底面に沿った 3 つのチャネルを制御する 3 つのゲート (すなわち、U 型に) を構成するので、フィン 130 の 2 つの側壁と底面に沿った 3 つのチャネルは、u ゲート F i n F E T 500 の「u ゲート」という呼び方がされる。

20

#### 【0046】

u ゲート F i n F E T 500 のフィン 130 の 2 つの側壁は共通の結晶配向 (例えば、配向 <110>) を有しており、フィン 130 の底面は異なる結晶配向 (例えば、配向 <100>) を有し得る。

フィン 130 のチャネルの結晶配向が異なるので、ゲート F i n F E T 400 と同様に、u ゲート F i n F E T 500 のフィン 130 のアスペクト比 H / W を変更すると、フィン 130 の多数キャリアのモビリティに影響を与える。

30

実際上、アスペクト比 H / W に基づく u ゲート F i n F E T 500 のフィン 130 の全体的なモビリティは、(必ずしも一致しないが) 上述した ゲート F i n F E T 400 のフィン 130 の全体的なモビリティとの関連性が高い。

この類似性は、第 3 チャネルがフィン 130 の上面または底面に位置するかの違いを有する、I 型ゲートと u 型ゲートの間の構造の類似によるものである。

#### 【0047】

ゲート F i n F E T 400 と同様に、u ゲート F i n F E T 500 のフィン 130 の全体的なモビリティは、フィン・アスペクト比 H / W を変化することにより調整することができる。

このフィン 130 の全体的なキャリア移動度は、その結晶配向によりフィン 130 の底面と側面のどちらがより高いキャリア移動度を有するかにより、フィン・アスペクト比 H / W が増加するにつれて増加または低減する。

40

しかしながら、ここでの開示に基づき、u ゲート F i n F E T 500 のフィン 130 の所望する全体的なキャリア移動度を達成するための、フィン 130 のフィン・アスペクト比 H / W に対する適切な調整を、当業者であれば特段の実験をすることなくできるであろう。

#### 【0048】

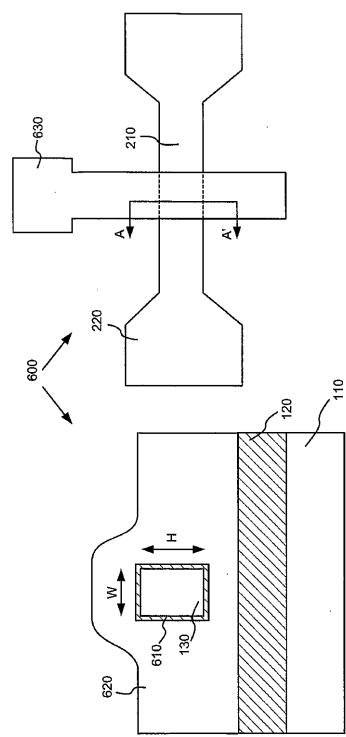

<ラウンドゲート F I N F E T >

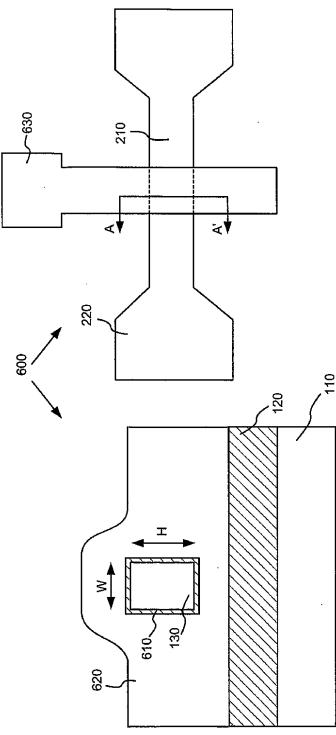

図 6 A は、本発明の実施形態による図 2 A および図 2 B の構造 210 からのラウンドゲート F i n F E T 600 の形成を示す断面図である。

図 5 A について上述したように、埋込酸化膜 120 の部分を除去するのに従来のエッチングケミストリを使用することができる。

その後、フィン 130 より下の埋込酸化膜 120 の一部を横にエッチングすべく、第 2 のエッチングを実行してもよい。

図 5 B に示すように、フィン 130 より下に位置する埋込酸化膜 120 を貫通する横方向のエッチングを実行すべく、典型的な実施形態の 1 つにおいては、例えば高圧力の HBr を使用する等方性エッチングを実行してもよい。

フィン 130 は、図 5 B に示す断面の埋込酸化膜 120 の上に、実質的にサスペンド(浮遊)されている。

#### 【0049】

図 5 B と異なり、ラウンドゲート FinFET 600 を形成する際、(例えば選択エッチングによって)フィン 130 上の絶縁キャップ 140 を除去し、埋込酸化膜 120 上に被覆されていないフィン 130 を残す。

次に、フィン 130 上にゲート絶縁層を形成することができる。例えば、図 6 に示すように、ゲート絶縁層として働く薄いゲート酸化膜 610 を、フィン 130 の露出した全面に熱成長させてもよい。ゲート酸化膜 610 を、約 10 から約 30 の厚さに成長させてもよい。一方、フィン 130 の上面は、絶縁キャップ 140 により保護される。

#### 【0050】

その後、図 6 A に示すように、フィン構造 210 の周りにゲート材料層 620 をたい積することができる。

ゲート材料層 620 は、後に形成されるゲート電極のゲート材料を含んでいるとともに、従来の化学蒸着法 (CVD) を使用して、約 500 から約 1000 の範囲の厚みにたい積されたポリシリコンを含んでいてもよい。あるいは、ゲルマニウムまたはシリコンおよびゲルマニウムの組合せのよう他の半導体材料、または様々な金属をゲート材料として使用してもよい。

#### 【0051】

その後、ラウンドゲート FinFET 600 のゲート電極 630 を形成すべく、ゲート材料層 620 をパターン化し、エッチングしてもよい。

例えば、図 6 B は、ゲート電極 630 を形成した後の、本発明のラウンドゲート FinFET 600 の上面図を示す。

図示のように、ラウンドゲート FinFET 600 は、フィン 130 の 4 つの全ての側面を囲むゲート材料 620 (図 6 A)、およびゲート電極 630 を有する構造を含んでいる。

#### 【0052】

再度図 6 A を参照すると (図 6 B の A - A' 線の断面)、ラウンドゲート FinFET 600 のフィン 130 におけるチャネルは、ゲート酸化膜 610 に隣接するフィン 130 の 2 つの側壁、上面、および底面に沿って存在することができる。

フィン 130 の 2 つの側壁、上面、および底面に隣接するゲート材料 620 が、フィン 130 の側壁および底面に沿った 4 つのチャネルを制御するフィン 130 を "取り囲む (around)" 4 つのゲートを構成するので、フィン 130 の 2 つの側壁、上面、および底面に沿った 4 つのチャネルは、ラウンドゲート FinFET 600 の「ラウンドゲート」という呼び方がされる。

#### 【0053】

ラウンドゲート FinFET 600 のフィン 130 の 2 つの側壁は共通の結晶配向 (例えば、配向 <110>) を有しており、フィン 130 の上面および底面は異なる共通の結晶配向 (例えば、配向 <100>) を有し得る。

フィン 130 のチャネルの結晶配向が異なるので、ゲート FinFET 400 および u ゲート FinFET 500 と同様に、ラウンドゲート FinFET 600 のフィン 130 のアスペクト比 H / W を変更すると、フィン 130 の多数キャリアのモビリティに影響を与える。

10

20

30

40

50

実際上、アスペクト比H / Wに基づくラウンドゲートFinFET600のフィン130の全体的なモビリティは、少なくとも、ラウンドゲートのFinFET600のフィン130が ゲートFinFET400およびuゲートFinFET500より1つ多い水平方向のチャネルを有するので、 ゲートFinFET400およびuゲートFinFET500と多少異なる振る舞いをする可能性がある。

#### 【0054】

ゲートFinFET400と同様に、ラウンドゲートFinFET600のフィン130の全体的なモビリティは、フィン・アスペクト比H / Wを変化することにより調整することができる。

このフィン130の全体的なキャリア移動度は、その結晶配向によりフィン130の上面／底面と側面のどちらがより高いキャリア移動度を有するかにより、フィン・アスペクト比H / Wが増加するにつれて増加または低減する。

しかしながら、ここでの開示に基づき、ラウンドゲートFinFET600のフィン130の所望する全体的なキャリア移動度を達成するための、フィン130のフィン・アスペクト比H / Wに対する適切な調整を、当業者であれば特段の実験をすることなくできるであろう。

#### 【0055】

<異なるキャリア移動度を有する例示的な実施形態>

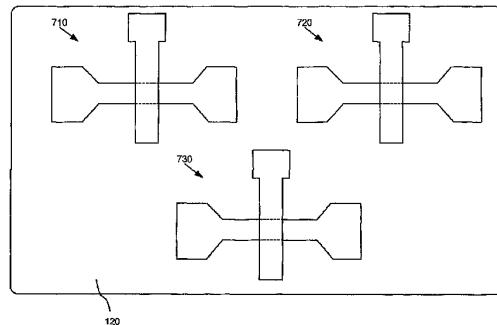

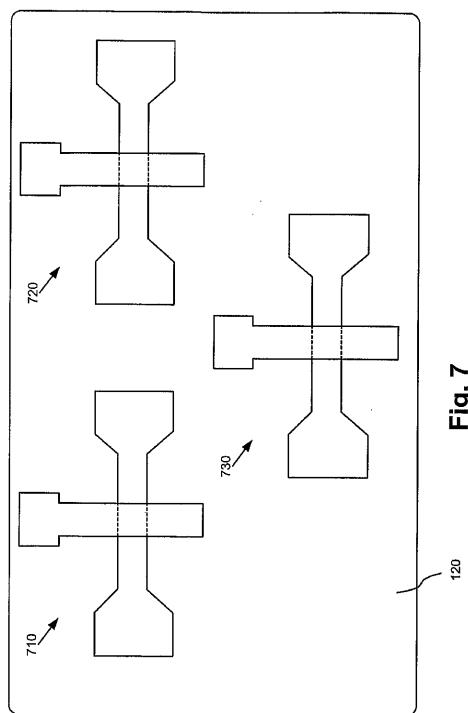

図7は、本発明の例示的な実施例によるFinFETデバイス710、720および730を含むウェーハの概略的な上面図である。

埋込酸化膜120はウェーハ（またはチップ）を示す。このウェーハの上には図示の3つのデバイス710、720および730が形成される。

デバイス710、720および730のうち少なくとも2つのデバイスの全体的なキャリア移動度が異なり得る。

デバイス710、720および730はすべて ゲートFinFET400、uゲートFinFET500、およびラウンドゲートFinFET600のいずれかのタイプのデバイスとすることができます。

あるいは、デバイス710、720および730は、ダブルゲートFinFET300、 ゲートFinFET400、uゲートFinFET500およびラウンドゲートFinFET600のうち、複数の異なるタイプのデバイスを含み得る。

例えば、ダブルゲートFinFET300と、 ゲートFinFET400、uゲートFinFET500およびラウンドゲートFinFET600の1つは同じフィンアスペクト比H / Wを有し得るが、それにも関わらず、FinFET400 / 500 / 600のさらなる垂直方向のチャネルにより、これらの全体的なキャリア移動度はどれも異なる。

#### 【0056】

さらに、デバイス710、720および730のすべてをN型MOS（NMOS）デバイス、P型MOS（PMOS）デバイス、またはNMOSデバイスとPMOSデバイスの組み合わせ（例えばCMOS（complementary MOS））としてもよい。デバイス710、720および730は他のデバイスと接続または相互接続され得るが、本発明を明確にするため、これらの接続については図7に示していない。

#### 【0057】

ここでの開示を考慮して、様々な設計上の理由により、異なるデバイス（例えばデバイス710および720）を、（異なるフィン・アスペクト比H / Wにより）全体的なキャリア移動度が異なるように形成することができることを当業者は理解するであろう。

例えば、全体的なキャリア移動度は、デバイス710 / 720のタイプに基づき異なり得る。

本発明の実施形態の一例においては、NMOSデバイスを、選択されたフィン・アスペクト比による全体的なキャリア移動度を有するようにし、同じウェーハ／チップ上のPMOSデバイスは、これとは異なるように選択されたフィン・アスペクト比による全体的なキャリア移動度を備えるものとする。これにより、NMOSデバイスのキャリア移動度が

10

20

20

30

40

50

PMOSデバイスのキャリア移動度よりも大きさにおいて（すなわち、絶対値）より大きくなるように形成することができる。

あるいは、PMOSデバイスを、同じウェーハ／チップ上のNMOSデバイスの全体的なキャリア移動度より絶対値においてより大きい全体的なキャリア移動度で形成してもよい。

あるいは、デバイスの全体的なキャリア移動度がほぼ等しくなるように、NMOSデバイス（例えばデバイス710）およびPMOSデバイス（例えばデバイス720）のフィン・アスペクト比を選択してもよい。

#### 【0058】

また、与えられた回路素子（例えばインバータ、NANDゲート、メモリエレメント、NORゲートなど）内のフィン・アスペクト比H/Wを変化することは有利である。 10

例えば単一の回路素子内において、1つのFinFETデバイス710は第1フィン・アスペクト比H/W<sub>1</sub>を持ち得る。

回路素子内の他のFinFETデバイス720は、デバイス710/720間の駆動電流のバランスをとるために、第2フィン・アスペクト比H/W<sub>2</sub>を持ち得る。

本発明のある実施形態においては、（例えば図7のデバイス710のソース／ドレイン領域をデバイス720のドレイン／ソースに接続することによって）回路素子のデバイス710および720の異なるアスペクトのフィンを、電気的に接続してもよい。

#### 【0059】

これに変えて、またはさらに、フィン・アスペクト比H/Wを回路素子間において変化させてもよい。 20

例えば、1つの回路素子は1つ以上のFinFETデバイスを含んでいてもよい。また、FinFETデバイス710は第1フィン・アスペクト比H/W<sub>1</sub>を有し、このアスペクト比により定まる第1の全体的なキャリア移動度を有する。

分離した回路素子は、第2フィン・アスペクト比H/W<sub>2</sub>を有し、このアスペクト比により定まる第2の全体的なキャリア移動度を有する1つ以上のFinFETデバイス720を含み得る。

#### 【0060】

さらに、ここに示した本発明のデバイス710ないし730のフィン・アスペクト比を変えることによって、様々な設計上の制約に応えることができる。 30

例えば、デバイス710および720は、それぞれCMOSデバイスのNMOSとPMOSの構成部分であり得る。

さらに、PMOSチャネル幅がNMOSチャネル幅に対して2:1の比率を有するよう（単なる例示である）、既存のデザイン・ルールが存在していることがあるので、この方法により配置される、典型的な、プレーナMOSFETデバイスの駆動電流は、既存の関係を有している。

デバイス710および720の駆動電流の既存の関係を維持している一方で、デバイス710および720のフィン・アスペクト比を調整することにより、チャネル幅の比率を（例えば3:2に）異なるようにすることができる。

すなわち、デバイス710および720のそれぞれの幅W<sub>1</sub>、W<sub>2</sub>が3:2の比率を持つようにすることができ、デバイス710および720のそれぞれの高さH<sub>1</sub>およびH<sub>2</sub>を調整し、それぞれのフィン・アスペクト比H<sub>1</sub>/W<sub>1</sub>およびH<sub>2</sub>/W<sub>2</sub>が既存の駆動電流関係を得られるようにしてもよい。 40

#### 【0061】

あるいは、デバイス710および720の駆動電流の新しい関係を生成する一方で、デバイス710および720のフィン・アスペクト比を調整することにより、同じチャネル幅の比率（例えば2:1）となるようにすることができる。

すなわち、デバイス710および720のそれぞれの幅W<sub>1</sub>、W<sub>2</sub>が2:1の比率を有するようにすることができ、デバイス710および720のそれぞれの高さH<sub>1</sub>およびH<sub>2</sub>を調整し、それぞれのフィン・アスペクト比H<sub>1</sub>/W<sub>1</sub>およびH<sub>2</sub>/W<sub>2</sub>が新しい駆動 50

電流関係（例えばデバイス 710 / 720 間の駆動電流が等しい関係）を生成するようにしてよい。

【0062】

当業者は、パターン化に使用するマスク（例えば図 2B のフィン 130 を形成するのに使用される図 1 のフォトレジストマスク 150）を調整することにより、異なるデバイス 710 / 720 のフィン幅（例えば、幅  $W_1$  および  $W_2$ ）が選択されることを認識するであろう。

同様に、フィン 130 の選択的なマスキングおよび露出している他のフィン 130 をエッチングしてこれらの高さを低くすることにより、異なるデバイス 710 / 720 のフィンの高さ（例えば、高さ  $H_1$  および  $H_2$ ）が選択され得る。

10

【0063】

このように、本発明によれば、異なるフィン・アスペクト比を有する、異なる Fin FET デバイス 710 / 720 / 730 を形成することができる。これらの異なるデバイス 710 / 720 / 730 を同じウェーハまたはチップ上に形成することができるとともに、同一の全体的なキャリア移動度または異なるキャリア移動度を呈することができる。

生成した構造は、短チャネル耐性に優れているので有利である。さらに、本発明はフレキシビリティを増加すると共に、従来のプロセスに容易に統合することができる。

【0064】

＜他の実施形態＞

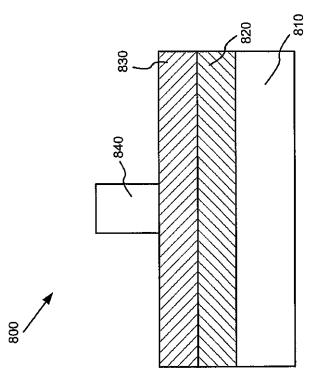

いくつかの実施形態においては、上述した他のものとは異なるラウンドゲート Fin FET を形成することが望ましい。

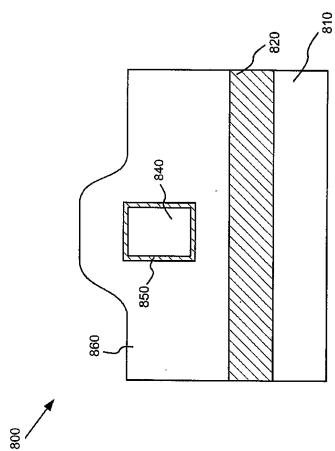

図 8A ないし図 8C は、本発明の他の実施形態によるラウンドゲート Fin FET 80 の形成を示す断面図である。

図 8A は、（図 2B と同じように）フィンを形成した後のプロセス段階を示す断面図である。第 1 絶縁層 830、第 2 絶縁層 820、および基板 810 上にシリコン・フィン 840 を形成することができる。図 8A には示していないが、（図 2A と同じように）フィン 840 の一方の端部はソース及びドレイン領域と接続されている。

【0065】

その後、図 8B に示すように、選択エッチングを実行して、フィン 840 より下の第 1 絶縁層 830 の部分を除去してもよい。

30

フィン 840 は、第 2 絶縁層 820 上に、実質的にサスペンド（浮遊）されている。

しかしながら、フィン 840 の端部はまだ第 1 絶縁層 830 に付着しており、図 8B に示すフィン 840 のサスペンドされた部分は、図示しないソース／ドレイン領域に隣接するフィン 840 の端部において第 1 絶縁層 830 に支持される。

【0066】

その後、フィン 840 上にゲート絶縁層をたい積することができる。例えば、図 8C に示すように、ゲート絶縁層として働く薄い酸化膜 850 をフィン 840 の全ての露出面に熱成長させてもよい。酸化膜 850 は、約 10 から約 30 の厚さに成長させてもよい。

40

【0067】

その後、図 6A に示すように、フィン構造 840 の周りにゲート材料層 860 をたい積することができる。

ゲート材料層 860 は、後に形成されるゲート電極のゲート材料を含んでいるとともに、従来の化学蒸着法（CVD）を使用して、約 500 から約 1000 の範囲の厚みにたい積されたポリシリコンを含んでいてもよい。あるいは、ゲルマニウムまたはシリコンおよびゲルマニウムの組合せのよう他の半導体材料、または様々な金属を、層 320 のゲート材料として使用してもよい。

その後、ここに記載したように、ゲート材料層 860 をラウンドゲート Fin FET 800 のゲートおよびゲート電極にパターン化することができる。

【0068】

50

前記記載においては、本発明について理解し易いように、特定の材料、構造、化学薬品、プロセス等のような多数の特定の詳細を記載している。

しかしながら、特にここに記載した詳細によることなく、本発明を実行することができる。その他、不必要に本発明の内容を不明瞭にしないように、周知のプロセス構造は詳細に記載していない。

#### 【0069】

本発明による、半導体デバイスを製造するのに使用される絶縁層および導電層は、従来のたい積技術によってたい積してもよい。例えば、低圧CVD (LPCVD) およびエンハンストCVD (ECD) を含んだ様々な種類のCVDプロセスのようなメタライゼーション技術を使用することができる。

10

#### 【0070】

本発明は、様々な種類の半導体デバイスの形成に適用可能である。したがって、不必要に本発明の内容を不明瞭にしないようにその詳細は記載しない。本発明を実行する際に、従来のたい積技術、フォトリソグラフィ技術、およびエッチング技術を使用してもよい。なお、このような技術の詳細についてはここでは詳述していない。

#### 【0071】

さらに、FinFETデバイス400/500/600の側面は結晶配向<110>を有するとともに、上面/下面是結晶配向<100>を有するものとして記載したが、これらのデバイスを製造することで、側面は結晶配向<100>となり、上面/下面是他の結晶配向<110>または<111>となる場合もある。

20

#### 【0072】

本発明の好ましい実施形態およびその多様性のうちのいくつかの例のみが、本発明において開示されると共に記載される。本発明は、様々な他の組合せおよび環境において使用できると共に、ここに記載されるような本発明の概念の範囲内の変形または修正することができるものとして理解される。

#### 【0073】

明示がない場合には、本出願の詳細な説明の中で使用されるどの要素、指示またはステップも本発明に重要または本質的なものとして解釈すべきではない。

ここに使用される、「ある(a)」と言う言葉は、1つ以上のものを含むように意図される。1つのものを示すような場合には「1つの(one)」またはこれに類する言葉を使用している。本発明の範囲は、請求の範囲およびこれらの均等物によって定義される。

30

#### 【図面の簡単な説明】

#### 【0074】

【図1】本発明の実施形態によるFinの形成に使用される例示的な層を示す断面図。

【図2A】本発明の例示的な実施形態によるFin構造の概略的な上面図。

【図2B】本発明の例示的な実施形態による図2AのFin構造の形成を示す断面図。

【図3A】本発明の例示的な実施形態による図2BのデバイスからのダブルゲートFinFETの形成を示す断面図。

【図3B】本発明の例示的な実施形態による図2BのデバイスからのダブルゲートFinFETの形成を示す上面図。

40

【図4A】本発明の例示的な実施形態による図2BのデバイスからのゲートFinFETの形成を示す断面図。

【図4B】本発明の例示的な実施形態による図2BのデバイスからのゲートFinFETの形成を示す上面図。

【図5A】本発明の例示的な実施形態による図2BのデバイスからのuゲートFinFETの形成を示す断面図。

【図5B】本発明の例示的な実施形態による図2BのデバイスからのuゲートFinFETの形成を示す断面図。

【図5C】本発明の例示的な実施形態による図2BのデバイスからのuゲートFinFETの形成を示す断面図。

50

【図 5 D】本発明の例示的な実施形態による図 2 B のデバイスからの u ゲート F i n F E T の形成を示す上面図。

【図 6 A】本発明の例示的な実施形態による図 2 B のデバイスからのラウンドゲート F i n F E T の形成を示す断面図。

【図 6 B】本発明の例示的な実施形態による図 2 B のデバイスからのラウンドゲート F i n F E T の形成を示す上面図。

【図 7】本発明の例示的な実施形態による図 3 A ないし図 6 B のデバイスのいずれかを含むウェーハの上面図。

【図 8 A】本発明の他の例示的な実施形態によるラウンドゲート F i n F E T の形成を示す断面図。

【図 8 B】本発明の他の例示的な実施形態によるラウンドゲート F i n F E T の形成を示す断面図。

【図 8 C】本発明の他の例示的な実施形態によるラウンドゲート F i n F E T の形成を示す断面図。

10

【図 1】

Fig. 1

【図 2 A】

Fig. 2A

【図 2 B】

Fig. 2B

【図 3 A】

Fig. 3A

【図 4 A】

Fig. 4A

【図 4 B】

Fig. 4B

【図 5 A】

Fig. 5A

【図 5 B】

Fig. 5B

【図 5 C】

FIG. 5C

【図 5 D】

FIG. 5D

【図 6 A】

Fig. 6A

【図 6 B】

Fig. 6B

【図7】

Fig. 7

【図8A】

Fig. 8A

【図8B】

Fig. 8B

【図8C】

Fig. 8C

**【手続補正書】**

【提出日】平成17年7月1日(2005.7.1)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】****【特許請求の範囲】****【請求項1】**

基板(110)と、

前記基板(110)上に形成される絶縁層(120)と、

前記絶縁層(120)上に形成されるとともに、第1フィンアスペクト比を有する第1フィン(130)を含む、前記絶縁層(120)上に形成される第1デバイス(710)と、

前記絶縁層(120)上に形成されるとともに、前記第1フィンアスペクト比と異なる第2フィンアスペクト比を有する第2フィン(130)を含む、前記絶縁層(120)上に形成される第2デバイス(720)と、

を含む、半導体デバイス(100)。

**【請求項2】**

前記第1デバイス(710)はNMOSデバイスであり、前記第2デバイス(720)はPMOSデバイスである、請求項1記載の半導体デバイス(100)。

**【請求項3】**

前記第1デバイス(710)および前記第2デバイス(720)は、単一の回路素子に含まれる、請求項1記載の半導体デバイス(100)。

**【請求項4】**

前記第1デバイス(710)の前記第1フィン(130)の第1キャリア移動度は、前記第2デバイス(720)の前記第2フィン(130)の第2キャリア移動度と異なる、請求項1記載の半導体デバイス(100)。

**【請求項5】**

前記第1デバイス(710)は、

前記第1フィン(130)の少なくとも3つの面上に形成される第1ゲート絶縁層(410)(510)(610)と、

前記第1フィン(130)の少なくとも3つの面上に形成される第1ゲート材料層(420)(520)(620)と、

をさらに含んでおり、

前記第2デバイス(720)は、

前記第2フィン(130)の少なくとも3つの面上に形成される第2ゲート絶縁層(410)(510)(610)と、

前記第2フィン(130)の少なくとも3つの面上に形成される第1ゲート材料層(420)(520)(620)と、

をさらに含む、請求項1記載の半導体デバイス(100)。

**【請求項6】**

前記第1ゲート絶縁層(610)と前記第1ゲート材料層(620)は、前記第1フィン(130)の4つの面上に形成される、請求項5記載の半導体デバイス(100)。

**【請求項7】**

前記第2ゲート絶縁層(610)と前記第2ゲート材料層(620)は、前記第2フィン(130)の4つの面上に形成される、請求項6記載の半導体デバイス(100)。

**【請求項8】**

前記第1フィン(130)は、第1高さおよび第1幅を有しており、

前記第1デバイスは、前記第1フィン(130)の少なくとも3つの面上に形成される

第1絶縁層(410)(510)(610)と、前記第1絶縁層(410)(510)(610)に隣接する第1ゲート(430)(530)(630)と、をさらに含んでおり

、前記第2フィン(130)は、第2高さおよび第2幅を有しており、

前記第2デバイスは、前記第2フィン(130)の少なくとも3つの面上に形成される第2絶縁層(410)(510)(610)と、前記第2ゲート絶縁層(410)(510)(610)に隣接する第2ゲート(430)(530)(630)と、をさらに含んでおり、

前記第1高さと前記第1幅の第1比は、前記第2高さと前記第2幅の第2比と異なる、請求項1記載の半導体デバイス(100)。

#### 【請求項9】

前記絶縁層(120)上に形成され、第3高さおよび第3幅を有する第3フィン(130)、前記第3フィン(130)の少なくとも3つの面上に形成される第3ゲート絶縁層(410)(510)(610)、および前記第3ゲート絶縁層(410)(510)(610)に隣接する第3ゲート(430)(530)(630)を含む、前記絶縁層(120)上に形成される第3デバイス(730)をさらに含んでおり、

前記第3高さと前記第3幅の第3比は、前記第1比および前記第2比と異なる、請求項8記載の半導体デバイス(100)。

#### 【請求項10】

前記第1デバイス(710)は、前記絶縁層(120)上に形成され、第1高さおよび第1幅を有する第1フィン(130)を含む、N型デバイスであり、

前記第2デバイス(720)は、前記絶縁層(120)上に形成され、第2高さおよび第2幅を有する第2フィン(130)を含む、P型デバイスであり、

前記N型デバイス(710)のキャリア移動度が前記P型デバイス(720)のキャリア移動度とほぼ等しいように、前記第1高さおよび前記第2高さが形成される、

請求項1記載の半導体デバイス(100)。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | International Application No<br>PCT/US2004/024590                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 H01L29/786 H01L21/336 H01L27/12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H01L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

| Electronic data base consulted during the International search (name of data base and, where practical, search terms used)<br>EPO-Internal, INSPEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                        | Relevant to claim No.                                                          |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | US 2002/011612 A1 (HIEDA KATSUHIKO)<br>31 January 2002 (2002-01-31)<br>page 23, paragraph 418 – paragraph 420<br>-----<br>F. Daugé, J. Pretet, A. Vandooren, L.<br>Mathew, B.-Y. Nguyen, J. Jomaah, S.<br>Cristoloveanu: "Channels Separation in<br>FINFETs", ULIS'2003 Workshop, Udine, 20-21<br>March 2003<br><a href="http://www.diegm.uniud.it/ulis2003/presentazioni/116_Dauge.pdf">http://www.diegm.uniud.it/ulis2003/presentazioni/116_Dauge.pdf</a><br>XP002321769<br>the whole document<br>----- | 1-10                                                                           |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -----<br>US 5 391 506 A (TADA ET AL)<br>21 February 1995 (1995-02-21)<br>the whole document<br>-----                                                                                                                                                                                                                                                                                                                                                                                                      | 1-10                                                                           |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -----<br>-----                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-10                                                                           |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| <p>* Special categories of cited documents :</p> <p>*A* document defining the general state of the art which is not considered to be of particular relevance</p> <p>*E* earlier document but published on or after the International filing date</p> <p>*L* document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)</p> <p>*O* document referring to an oral disclosure, use, exhibition or other means</p> <p>*P* document published prior to the international filing date but later than the priority date claimed</p> <p>*T* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</p> <p>*X* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</p> <p>*Y* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.</p> <p>*&amp;* document member of the same patent family</p> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                |

| Date of the actual completion of the international search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Date of mailing of the international search report                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                |

| 21 March 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 05/04/2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL – 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Authorized officer<br>Hoffmann, N                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                |

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US2004/024590

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                                 |                       |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                              | Relevant to claim No. |

| Y                                                    | N.H.E. WESTE, K. ESHRAGHIAN: "Principles of CMOS VLSI Design"<br>1988, ADDISON-WESLEY , XP002321770<br>page 140 - page 141<br>-----                                                                                                                                                                             | 1-10                  |

| A                                                    | LEMME M ET AL: "Influence of channel width on n- and p-type nano-wire-MOSFETs on silicon on insulator substrate"<br>MICROELECTRONIC ENGINEERING, ELSEVIER<br>PUBLISHERS BV., AMSTERDAM, NL,<br>vol. 67-68, June 2003 (2003-06), pages<br>810-817, XP004428954<br>ISSN: 0167-9317<br>the whole document<br>----- | 1-10                  |

| A                                                    | PARK J-T ET AL: "PI-GATE SOI MOSFET"<br>IEEE ELECTRON DEVICE LETTERS, IEEE INC.<br>NEW YORK, US,<br>vol. 22, no. 8, August 2001 (2001-08),<br>pages 405-406, XP001099966<br>ISSN: 0741-3106<br>the whole document<br>-----                                                                                      | 7,8                   |

| A                                                    | US 2003/102497 A1 (FRIED DAVID M ET AL)<br>5 June 2003 (2003-06-05)<br>the whole document<br>-----                                                                                                                                                                                                              | 1-10                  |

| P, X                                                 | US 2004/110331 A1 (YEO YEE-CHIA ET AL)<br>10 June 2004 (2004-06-10)<br>the whole document<br>-----                                                                                                                                                                                                              | 1-5,8-10              |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

|                              |

|------------------------------|

| International Application No |

| PCT/US2004/024590            |

| Patent document cited in search report |    | Publication date |    | Patent family member(s) |  | Publication date |

|----------------------------------------|----|------------------|----|-------------------------|--|------------------|

| US 2002011612                          | A1 | 31-01-2002       | JP | 2002118255 A            |  | 19-04-2002       |

| US 5391506                             | A  | 21-02-1995       | JP | 5218415 A               |  | 27-08-1993       |

|                                        |    |                  | JP | 5218416 A               |  | 27-08-1993       |

|                                        |    |                  | JP | 5343679 A               |  | 24-12-1993       |

| US 2003102497                          | A1 | 05-06-2003       | US | 2004038464 A1           |  | 26-02-2004       |

| US 2004110331                          | A1 | 10-06-2004       | TW | 591797 B                |  | 11-06-2004       |

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 1 7 K |

| H 01 L | 29/78 | 6 1 7 N |

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,M,A,MD,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(74)代理人 100108604

弁理士 村松 義人

(72)発明者 ピン ユ

アメリカ合衆国、カリフォルニア州 95014、キュパーティノ、ポピー ウェイ 1373

(72)発明者 シブリー エス. アーメド

アメリカ合衆国、カリフォルニア州 95134、サン ノゼ、ナンバー105、エラン ビレッジ レイン 350

(72)発明者 ハイホン ワン

アメリカ合衆国、カリフォルニア州 95035、ミルピタス、アパートメント ティー303、ミルモント ドライブ 1775

F ターム(参考) 5F048 AC01 AC03 BA16 BB01 BB04 BB05 BC01 BD06 CB08

|       |      |      |      |      |      |      |      |      |      |      |

|-------|------|------|------|------|------|------|------|------|------|------|

| 5F110 | AA07 | AA30 | BB04 | CC10 | DD05 | DD13 | EE09 | EE22 | EE45 | FF02 |

| FF23  | GG01 | GG02 | GG03 | GG12 | GG13 | GG17 | GG24 | GG25 | HJ23 |      |

| NN78  |      |      |      |      |      |      |      |      |      |      |