(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

G11C 16/12 (2006.01)

(45) 공고일자

2007년08월03일

(11) 등록번호

10-0746292

(24) 등록일자

2007년07월30일

(21) 출원번호

(22) 출원일자

심사청구일자

10-2006-0062626

2006년07월04일

2006년07월04일

(65) 공개번호

(43) 공개일자

(73) 특허권자

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

유현기

경기 수원시 영통구 영통동 신나무실 극동아파트 615-1402

류지도

경기 수원시 권선구 권선동 주공아파트 331동 1002호

서보영

경기 안양시 동안구 호계3동 967-47 안양빌라 가동 306호

전창민

서울 양천구 신월1동 134-17 태형APT 1103호

전희석

경기 수원시 권선구 권선동 우남아파트 2차 231동 606호

최성곤

경기 오산시 오산동 현대아파트 101동 804호

한정우

경기 수원시 권선구 금곡동 LG빌리지 아파트 309동 1004호

(74) 대리인

권영규

윤재석

한지희

(56) 선행기술조사문현

JP2002289705 A

KR1019970008201 A

US5663923 A

JP2004031920 A

KR1020010061501 A

심사관 : 조명관

전체 청구항 수 : 총 9 항

(54) 비휘발성 메모리 장치

## (57) 요약

비휘발성 메모리 장치가 개시된다. 본 발명에 따른 비휘발성 메모리 장치는 메모리셀 블록, 제1 및 제2 스위칭 블록을 구비한다. 메모리셀 블록에는 메모리셀들이 다수개 배열되며, 메모리셀들은 각각 부동 게이트와 제어 게이트를 구비하며 로컬 비트 라인에 접속되는 메모리 트랜지스터 및 상기 메모리 트랜지스터에 직렬로 연결되며 소스 라인에 접속되는 선택 트랜지스터를 포함한다. 제1 스위칭 블록은 글로벌 비트 라인을 로컬 비트 라인에 선택적으로 접속하고, 제2 스위칭 블록은 메모리셀 블록 내의 메모리셀들을 소정 비트수 단위로 제어한다. 제1 스위칭 블록은 글로벌 비트 라인과 로컬 비트 라인 사이에 병렬로 연결되는 적어도 두 개의 스위칭 소자를 구비한다.

## 내용

도 1

### 특허청구의 범위

#### 청구항 1.

부동 게이트와 제어 게이트를 구비하며 로컬 비트 라인에 접속되는 메모리 트랜지스터 및 상기 메모리 트랜지스터에 직렬로 연결되며 소스 라인에 접속되는 선택 트랜지스터를 포함하는 메모리셀들이 다수개 배열되는 메모리셀 블록;

글로벌 비트 라인을 상기 로컬 비트 라인에 선택적으로 접속하는 제1 스위칭 블록; 및

상기 메모리셀 블록 내의 메모리셀들을 소정 비트수 단위로 제어하는 제2 스위칭 블록을 구비하며,

상기 제1 스위칭 블록은

상기 글로벌 비트 라인과 상기 로컬 비트 라인 사이에 병렬로 연결되는 적어도 두 개의 스위칭 소자를 구비하는 비휘발성 메모리 장치.

#### 청구항 2.

제 1 항에 있어서, 상기 병렬로 연결되는 적어도 두 개의 스위칭 소자 각각은

NMOS, PMOS, 또는 CMOS 소자인 비휘발성 메모리 장치.

#### 청구항 3.

제 1 항에 있어서, 상기 병렬로 연결되는 적어도 두 개의 스위칭 소자 각각은

상기 선택 트랜지스터와 실질적으로 동일하게 구현되는 것을 특징으로 하는 비휘발성 메모리 장치.

#### 청구항 4.

제 1 항에 있어서, 상기 소정 비트수는

8인 비휘발성 메모리 장치.

### 청구항 5.

제 1 항에 있어서,

상기 메모리 트랜지스터의 제어 게이트는 로컬 센스 라인에 연결되고,

상기 제2 스위칭 블록은 글로벌 센스 라인을 상기 로컬 센스 라인에 선택적으로 접속시키는 비휘발성 메모리 장치.

### 청구항 6.

각각이 메모리 트랜지스터와 선택 트랜지스터를 구비하는 메모리 셀을 다수개 포함하는 메모리 섹터;

글로벌 비트라인;

글로벌 센스 라인;

상기 다수의 섹터들 중 대응하는 섹터로 비트라인 전압을 인가하기 위한 로컬 비트라인;

소정 비트수 단위로 메모리 트랜지스터들의 제어 게이트들을 상호 접속하는 로컬 센스 라인;

상기 글로벌 비트 라인을 상기 로컬 비트 라인에 선택적으로 접속하는 제1 스위칭 소자; 및

상기 글로벌 센스 라인을 상기 로컬 센스 라인에 선택적으로 접속하는 제2 스위칭 소자를 구비하며,

상기 제1 스위칭 소자는

상기 글로벌 비트 라인과 상기 로컬 비트 라인 사이에 병렬로 연결되는 적어도 두 개의 스위칭 트랜지스터들을 구비하는 비휘발성 메모리 장치.

### 청구항 7.

제 6 항에 있어서, 상기 스위칭 트랜지스터들 각각은

NMOS, PMOS, 또는 CMOS 소자인 비휘발성 메모리 장치.

### 청구항 8.

제 6 항에 있어서, 상기 스위칭 트랜지스터들 각각은

상기 선택 트랜지스터와 실질적으로 동일하게 구현되는 것을 특징으로 하는 비휘발성 메모리 장치.

### 청구항 9.

제 6 항에 있어서, 상기 소정 비트수는

8인 비휘발성 메모리 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

##### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 반도체 메모리 장치에 관한 것으로, 보다 상세하게는 2-T(transistor) FN(Fowler-Nordheim) 타입의 EEPROM 메모리셀을 구비하는 비휘발성 메모리 장치에 관한 것이다.

비휘발성 메모리 장치(Non-volatile memory device)는 전원이 공급되지 않으면 데이터가 지워지는 DRAM, SRAM 소자와는 달리 전원이 공급되지 않아도 데이터가 지워지지 않는 메모리 소자이다.

비휘발성 메모리 소자 중 대표적인 것이 전기적으로 프로그램 및 소거가 가능한 EEPROM이다.

EEPROM은 영구적인 코드를 저장하기 위해 사용되고, 통상적으로, 바이트(byte) 단위로 프로그래밍되고, 블록이나 셱터 단위로 소거된다. 그러나, 최근에는 바이트 단위로 소거 가능한 플래시 메모리가 제안되고 있으며, 바이트 단위로 소거 가능한 플래시 메모리로는 2T FN 타입의 EEPROM 이 주로 사용된다.

2T FN 타입 EEPROM이란 2개의 트랜ジ스터로 하나의 메모리셀을 구성하며, FN 터널링 방식에 의해 프로그램 및 소거가 이루어지는 EEPROM을 말한다. 메모리 셀을 구성하는 2개의 트랜ジ스터는 직렬로 연결되며, 하나는 FLOTOX(Floating gate Tunnel Oxide) 형 메모리 트랜지스터이고, 다른 하나는 선택 트랜지스터이다.

한편, EEPROM 장치의 메모리 용량이 증가함에 따라 단위 메모리셀의 크기(cell Size)가 계속 줄어들어 메모리셀의 액티브 폭(Active Width)이 감소되고 메모리셀의 커패시턴스 값이 작아지는 추세이다. 이에 따라 메모리셀의 프로그램과 소거 효율이 떨어진다. 따라서, 온셀(on-cell) 메모리 트랜지스터의 문턱전압이 증가되어 온셀(On-cell) 전류 측면에서는 계속 불리해지고 있다. "온셀"이란 메모리 트랜지스터의 부유 게이트(floating gate)로부터 전자가 빠져나와 문턱 전압이 낮아진 상태(예를 들어 1V 이하)의 메모리셀로서, "소거된 셀"이라고도 한다. 이에 반해, "오프셀"이란 메모리 트랜지스터의 부유 게이트(floating gate)에 전자가 축적되어 문턱전압이 높아진 상태(예를 들어 +5V 이상)의 메모리셀로서, "프로그램된 셀"이라고도 한다.

온셀의 문턱전압이 높아지면, 온셀 전류량은 줄어든다. 특히, 데이터를 저장하고 지우는 반복적인 작업으로 인하여 온셀(On Cell)의 문턱전압(Vth)이 증가하고, 이에 따라 온셀 전류량이 줄어들면, 온셀/오프셀을 판별하기 어려운 상태에 이를 수 있다. 온셀/오프셀의 판별이 어려워지면 판독 오류 등이 발생할 수 있다.

이를 개선하기 위해서 전자가 터널링(Tunneling)되는 터널 영역(tunnel oxide)의 품질을 향상시키는 공정 등 공정면에서 개선 방법이 강구되어 왔다. 그러나, 공정 측면에서도 여러 제약이 존재함에 따라, 공정 측면에서의 개선 방안 외에, EEPROM 셀의 온셀 전류를 향상시키는 새로운 방안이 요구된다.

##### 발명이 이루고자 하는 기술적 과제

따라서 본 발명이 이루고자 하는 기술적인 과제는 EEPROM 메모리셀의 전류 특성, 특히 온셀 전류 특성을 개선하여 판독 속도(Read Speed)를 빠르게 하고 판독 오류 가능성을 감소시키는 비휘발성 메모리 장치를 제공하는 것이다.

#### 발명의 구성

상기 기술적 과제를 달성하기 위한 본 발명의 일 측면에 따른 비휘발성 메모리 장치는 메모리셀 블록, 그리고 제1 및 제2 스위칭 블록을 구비한다.

상기 메모리 셀 블록에는 메모리 셀들이 다수개 배열되며, 메모리 셀들은 각각 부동 게이트와 제어 게이트를 구비하며 로컬 비트 라인에 접속되는 메모리 트랜지스터 및 상기 메모리 트랜지스터에 직렬로 연결되며 소스 라인에 접속되는 선택 트랜지스터를 포함한다.

상기 제1 스위칭 블록은 글로벌 비트 라인을 상기 로컬 비트 라인에 선택적으로 접속하고, 상기 제2 스위칭 블록은 상기 메모리 셀 블록 내의 메모리 셀들을 소정 비트수 단위로 제어한다. 상기 제1 스위칭 블록은 상기 글로벌 비트 라인과 상기 로컬 비트 라인 사이에 병렬로 연결되는 적어도 두 개의 스위칭 소자를 구비한다.

상기 병렬로 연결되는 적어도 두 개의 스위칭 소자 각각은 NMOS, PMOS, 또는 CMOS 소자일 수 있다.

상기 병렬로 연결되는 적어도 두 개의 스위칭 소자 각각은 상기 선택 트랜지스터와 실질적으로 동일하게 구현될 수 있다.

상기 기술적 과제를 달성하기 위한 본 발명의 다른 일 측면에 따른 비휘발성 메모리 장치는, 각각이 메모리 트랜지스터와 선택 트랜지스터를 구비하는 메모리 셀을 다수개 포함하는 메모리 섹터, 글로벌 비트라인, 상기 다수의 섹터들 중 대응하는 섹터로 비트라인 전압을 인가하기 위한 로컬 비트라인, 글로벌 센스 라인, 소정 비트수(예를 들어, 8) 단위로 메모리 트랜지스터들의 제어 게이트들을 상호 접속하는 로컬 센스 라인, 상기 글로벌 비트 라인을 상기 로컬 비트 라인에 선택적으로 접속하는 제1 스위칭 소자, 및 상기 글로벌 센스 라인을 상기 로컬 센스 라인에 선택적으로 접속하는 제2 스위칭 소자를 구비한다.

상기 제1 스위칭 소자는, 상기 글로벌 비트 라인과 상기 로컬 비트 라인 사이에 병렬로 연결되는 적어도 두 개의 스위칭 트랜지스터들을 구비한다.

본 발명과 본 발명의 동작상의 이점 및 본 발명의 실시에 의하여 달성되는 목적을 충분히 이해하기 위해서는 본 발명의 바람직한 실시예를 예시하는 첨부 도면 및 첨부 도면에 기재된 내용을 참조하여야만 한다.

이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시예를 설명함으로써, 본 발명을 상세히 설명한다. 각 도면에 제시된 동일한 참조부호는 동일한 부재를 나타낸다.

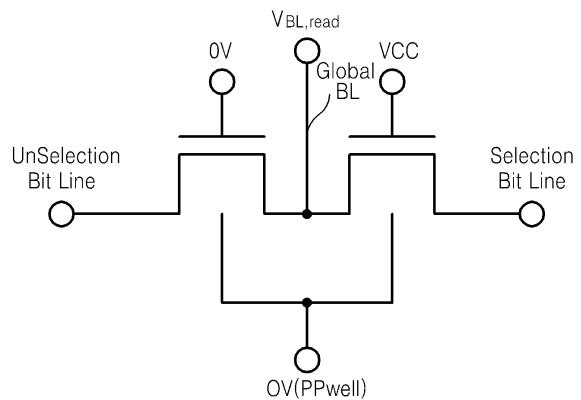

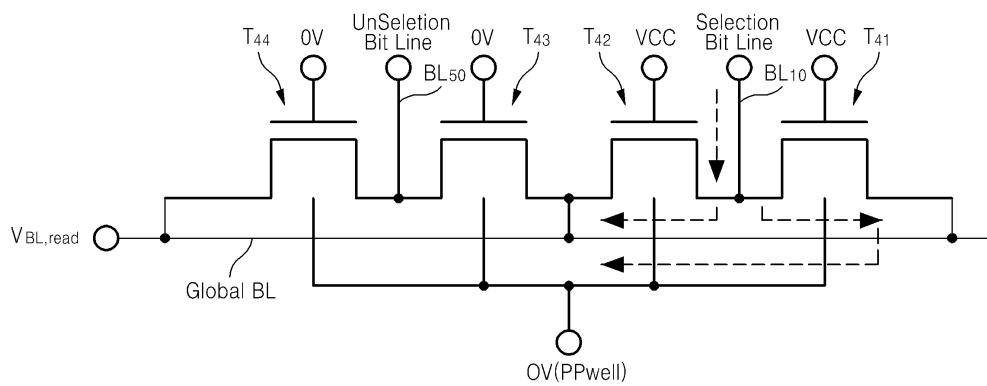

도 1은 본 발명의 일 실시예에 따른 비휘발성 메모리 장치의 메모리 어레이의 일부분을 나타내는 회로도이다.

도 1을 참조하면, 본 발명의 일 실시예에 따른 비휘발성 메모리 장치는, 다수의 메모리 셀 블록(MCBi, 예를 들어, MCB1, MCB2, "섹터"라고 칭하기도 함), 섹터 선택 스위칭 블록(SSBi, 예를 들어, SSB1, SSB2), 바이트 선택 스위칭 블록을 포함한다.

메모리 셀 블록(MCBi)은 로우(row) 방향과 칼럼(column) 방향으로 배열된 다수의 메모리 셀들(MC)을 포함한다.

메모리 셀(MC)은 두개의 트랜지스터, 즉 메모리 트랜지스터( $T_1$ )와 선택 트랜지스터( $T_2$ )로 구성될 수 있다. 메모리 트랜지스터( $T_1$ )는 "1"이나 "0"레벨로 데이터를 보존하는 역할을 하며, 선택 트랜지스터( $T_2$ )는 메모리 비트를 선택하는 역할을 한다. 이러한 메모리 트랜지스터( $T_1$ )는 부유 게이트(Floating Gate, FG)와 제어 게이트(Control Gate, CG)를 구비하는 FLOTOX (Floating gate Tunnel Oxide) 형 트랜지스터이며, 선택 트랜지스터( $T_2$ )는 선택 게이트(Selection Gate, SG)를 포함한다. 이러한 메모리 셀(MC)이 다수개 모여 메모리 셀 블록(MCBi)을 이룬다.

메모리 셀 블록(MCBi) 내에 위치하는 다수의 메모리 트랜지스터( $T_1$ )의 제어 게이트(CG)는 행마다 로컬 센스 라인(local sense line,  $SL_{in}$ , 예를 들어  $SL_{11}, SL_{12}, SL_{1m}$ )에 의해 상호 접속되고, 선택 트랜지스터( $T_2$ )의 선택 게이트는 행마다 워드 라인(WL<sub>i</sub>, 예를 들어 WL1, WL2)에 의해 상호 접속된다. 또한, 다수의 선택 트랜지스터( $T_2$ )는 공통 소오스 라인( $SO_i$ , 예를 들어  $SO_1, SO_2$ )에 상호 접속된다. 이를 공통 소오스 라인( $SO_i$ )은 행마다, 열마다, 섹터마다 또는 전체 메모리를 위해 구성될 수 있다. 도 1에서는 공통 소오스 라인( $SO_i$ )의 모든 상호 접속이 도시되어 있지는 않다.

메모리 셀 블록(MCBi)의 주위에는 섹터 선택 스위칭 블록(SSBi)와 바이트 선택 스위칭 블록이 위치한다.

섹터 선택 스위칭 블록(SSBi)은 섹터 단위로 메모리 셀을 선택하는 역할을 하는 다수의 섹터 선택 스위칭 소자들( $T_{41}$ ,  $T_{42}$ ,  $T_{43}$ ,  $T_{44}$ )을 포함한다. 섹터 선택 스위칭 소자들( $T_{41}$ ,  $T_{42}$ ,  $T_{43}$ ,  $T_{44}$ )은, 칼럼 방향으로 소정 개수(예를 들어, 64개)의 메모리 셀마다 스위칭 트랜지스터 형태로 구현될 수 있다.

섹터 선택 스위칭 소자들( $T_{41}$ ,  $T_{42}$ ,  $T_{43}$ ,  $T_{44}$ )은 각각 글로벌 비트라인(global bit line, BL<sub>i</sub>, 예를 들어 BL<sub>0</sub>, BL<sub>17</sub>, BL<sub>8</sub>)을 하나의 섹터에 걸쳐 뻗어있는 로컬 비트 라인(BL<sub>in</sub>, 예를 들어 BL<sub>10</sub>, SL<sub>17</sub>, SL<sub>50</sub>)과 선택적으로 연결하고, 워드 라인(WL<sub>i</sub>)에 대해 평행하게 뻗어있는 섹터 선택 게이트 라인(SSGi, 예를 들어, SSG1, SSG2, SSG3, SSG4)에 의해 제어된다. 본 발명의 일 실시예에서는, 각 글로벌 비트라인과 이에 대응하는 로컬 비트 라인 사이에는 적어도 두 개의 섹터 선택 스위칭 트랜지스터가 병렬로 연결된다.

섹터 선택 스위칭 소자들( $T_{41}$ ,  $T_{42}$ ,  $T_{43}$ ,  $T_{44}$ )은 메모리 셀(MC)과 동일한 도전형의 영역에 위치하게 된다. 예를 들어 메모리 셀(MC)이 제 1 도전형 영역(140)에 위치한다면 선택 스위칭 소자들( $T_{41}$ ,  $T_{42}$ ,  $T_{43}$ ,  $T_{44}$ ) 역시 제 1 도전형 영역(140)에 위치하게 된다. "제 1 도전형"과 "제 2 도전형"은 P형 또는 N형과 같이 서로 반대되는 도전형을 가리킨다. 도전형 영역은 웰(well)이거나, 반도체 기판 일 수 있다. 또한, 섹터 선택 스위칭 소자들( $T_{41}$ ,  $T_{42}$ ,  $T_{43}$ ,  $T_{44}$ )은 예를 들어 PMOS, NMOS 또는 CMOS 일 수 있다.

본 발명의 일 실시예에서는, 섹터 선택 스위칭 소자들( $T_{41}$ ,  $T_{42}$ ,  $T_{43}$ ,  $T_{44}$ )은 각각 N형 트랜지스터로 구현된다.

바이트 선택 스위칭 블록은 선택된 섹터 중에서 바이트 단위로 메모리 셀을 선택하는 역할을 하는 바이트 선택 스위칭 소자( $T_3$ )를 포함한다. 바이트 선택 스위칭 소자( $T_3$ )는 1 바이트 메모리 셀마다 스위칭 트랜지스터 형태로 구현될 수 있다.

바이트 선택 스위칭 소자( $T_3$ )는 글로벌 센스 라인(global sense line, SL<sub>i</sub>, 예를 들어 SL<sub>1</sub>, SL<sub>2</sub>)을 하나의 바이트(또는 워드)에 걸쳐 뻗어있는 로컬 센스 라인(SL<sub>in</sub>, 예를 들어 SL<sub>11</sub>, SL<sub>12</sub>, SL<sub>1m</sub>)과 선택적으로 연결하고, 비트 라인(BL<sub>i</sub>)에 대해 평행하게 뻗어있는 바이트 선택 게이트 라인(BSG<sub>i</sub>, 예를 들어 BSG<sub>0</sub>, BSG<sub>1</sub>, BSG<sub>2</sub>, BSG<sub>3</sub>)에 의해 제어된다.

바이트 선택 스위칭 소자( $T_3$ )는 메모리 셀(MC)과는 다른 도전형의 영역에 위치하게 된다. 예를 들어 메모리 셀(MC)이 제 1 도전형 영역(140)에 위치한다면 바이트 선택 스위칭 소자( $T_3$ )는 제 2 도전형 영역(150)에 위치하게 된다. 이때, 도전형 영역은 웰(well)이거나, 반도체 기판 일 수 있다. 또한, 바이트 선택 스위칭 소자( $T_3$ )는 예를 들어 PMOS, NMOS 또는 CMOS 일 수 있다. 본 발명의 일 실시예에서는, 바이트 선택 스위칭 소자( $T_3$ )는 P형 트랜지스터로 구현된다.

본 실시예에서는, 로우 방향으로 2바이트 메모리 셀들과 칼럼 방향으로 n(예를 들어 64)개 메모리 셀들이 모여 하나의 섹터(MCBi)를 형성한다. 각 섹터(MCBi)의 상단 혹은 하단에는 섹터 선택 스위칭 블록(SSBi)이 위치하고, 각 섹터(MCBi)의 좌 혹은 후측에는 바이트 선택 스위칭 소자( $T_3$ )가 위치한다.

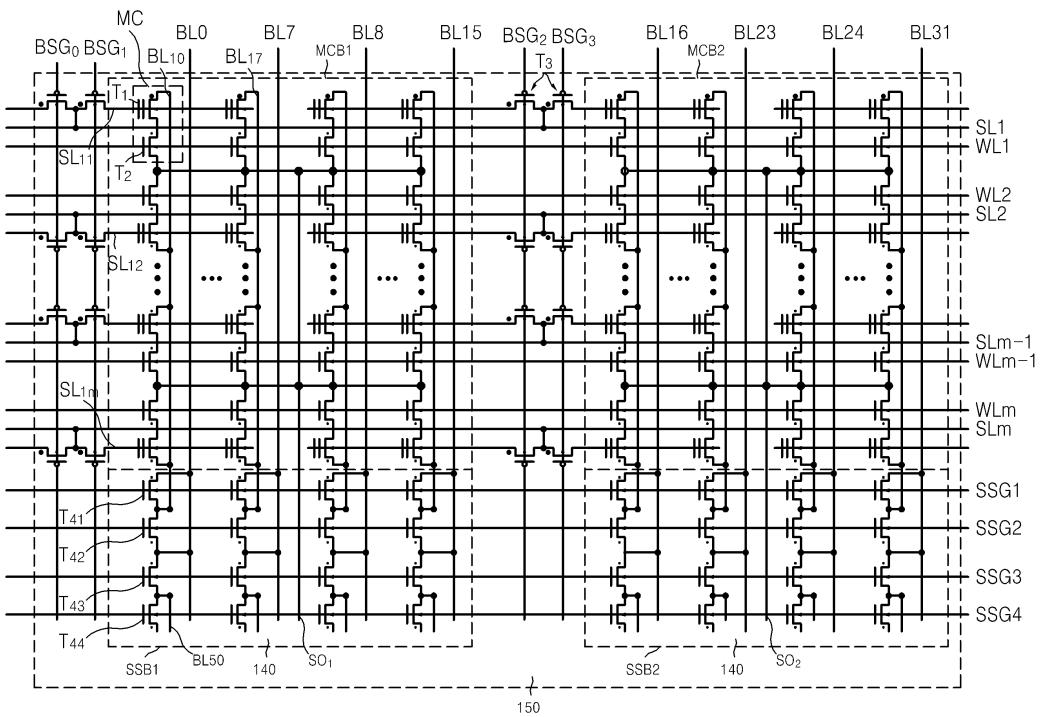

도 2는 본 발명의 일 실시예에 따른 메모리 장치의 메모리 셀의 개략적으로 도시한 단면도이다.

도 2에 도시한 바와 같이, 본 발명의 일 실시예에 따른 비휘발성 메모리 소자의 메모리 셀(MC)은 P형 반도체 기판(미도시) 내의 딥 N형 웰(DNwell, 150)에 형성된 포켓 P형 웰(PPwell, 140)에 형성되는 메모리 트랜지스터( $T_1$ )와 선택 트랜지스터( $T_2$ )를 포함한다.

메모리 트랜지스터( $T_1$ )는 포켓 P형 웰(PPwell)에 부유 게이트(floating gate, 21), 부유 게이트(21) 상부의 게이트간 절연막(22), 게이트간 절연막(22) 상부의 제어 게이트(control gate, 23)를 구비한다. 또한, 포켓 P형 웰(PPwell)과 부유 게이트(21) 사이에는 게이트 절연막(11)이 개재되어 있으며, 게이트 절연막(11)은 상대적으로 얇은 두께를 갖는 터널링 영역을 포함한다. 터널링 영역은 메모리 셀(MC)의 프로그램과 소거시 FN 터널링이 가능한 두께로 형성될 수 있으며, 이러한 터널링 영역을 통하여 전하가 부유 게이트(21)로 이동된다.

메모리 트랜지스터( $T_1$ )의 일 단자(예를 들어, 드레인 영역(N))는 비트라인에 접속된다. 선택 트랜지스터( $T_2$ )는 선택 게이트(30)를 구비하며, 공정 단순화 측면에서, 메모리 트랜지스터( $T_1$ )와 유사하게, 절연막 패턴(31) 및 유사 게이트(32)를 구비할 수 있다. 선택 트랜지스터( $T_2$ )의 일 단자(예를 들어, 소오스 영역)는 공통 소오스 라인(SO)에 접속된다. 또한, 포켓 P형 웰(PPwell)과 선택 게이트(30) 사이에는 게이트 절연막(12)이 개재되어 있다.

도 2에 도시된 바와 같이, 비트 라인과 메모리 트랜지스터( $T_1$ )가 인접하게 위치함에 따라, 메모리 트랜지스터( $T_1$ )는 비트 라인 전압에 따라 지속적인 스트레스로 교란을 받을 수 있다. 이로 인해, 메모리 트랜지스터의 온셀 전류는 열화될 수 있다.

한편, 섹터 선택 스위칭 소자를 이용하여 선택된 섹터에 대해서만 비트라인 전압이 인가됨으로써, 비트라인 전압에 따른 교란(disturbance)은 줄어들 수 있으나, 집적도 증가 및 섹터 구조로 인하여 단위 메모리셀 면적은 더욱 제한된다. 이에 따라 셀 유닛 피치(cell unit pitch)에 맞게 메모리 트랜지스터( $T_1$ )를 형성해야 한다. 그러므로, 메모리 트랜지스터( $T_1$ )의 액티브 폭(active width)이 제한되어 온셀전류가 더욱 제한된다.

온셀 전류를 향상시키기 위하여, 본 발명의 일 실시예에서는, 섹터 선택 스위칭 소자( $T_{41}, T_{42}, T_{43}, T_{44}$ )는 병렬 구조( $T_{41}$  및  $T_{42}, T_{43}$  및  $T_{44}$ )로 구현된다. 섹터 선택 스위칭 소자의 전류량은 섹터 선택 스위칭 트랜지스터( $T_{41}, T_{42}, T_{43}, T_{44}$ )의 액티브 폭을 늘이면 되나, 셀 유닛 피치에서 로우 방향(워드라인 방향의 피치(Cell X Pitch)가 칼럼 방향(비트라인 방향의 피치(Cell Y Pitch)보다 상대적으로 작아 섹터 선택 스위칭 트랜지스터의 액티브 폭을 늘이는 데는 한계가 있다. 또한 섹터 선택 스위칭 트랜지스터( $T_{41}, T_{42}, T_{43}, T_{44}$ )는 선택 트랜지스터( $T_2$ )와 실질적으로 동일하게 구현되는 것이 바람직하므로, 섹터 선택 스위칭 트랜지스터의 액티브 폭을 증가시키기 어렵다. 이러한 제한에도 불구하고, 섹터 선택 스위칭 트랜지스터는 단위 메모리셀 전류 이상의 전류 드라이빙 능력이 있어야 하며, 비트 라인 전류의 병목(Bottleneck)으로 작용해선 안된다.

따라서, 본 발명의 일 실시예에서는, 섹터 선택 스위칭 트랜지스터( $T_{41}, T_{42}, T_{43}, T_{44}$ )의 전류 드라이빙 능력을 향상시키기 위하여, 도 1에 도시된 바와 같이, 각 글로벌 비트 라인과 이에 대응하는 로컬 비트라인 사이에 두 개의 스위칭 소자( $T_{41}$  및  $T_{42}, T_{43}$  및  $T_{44}$ )가 병렬로 연결된다.

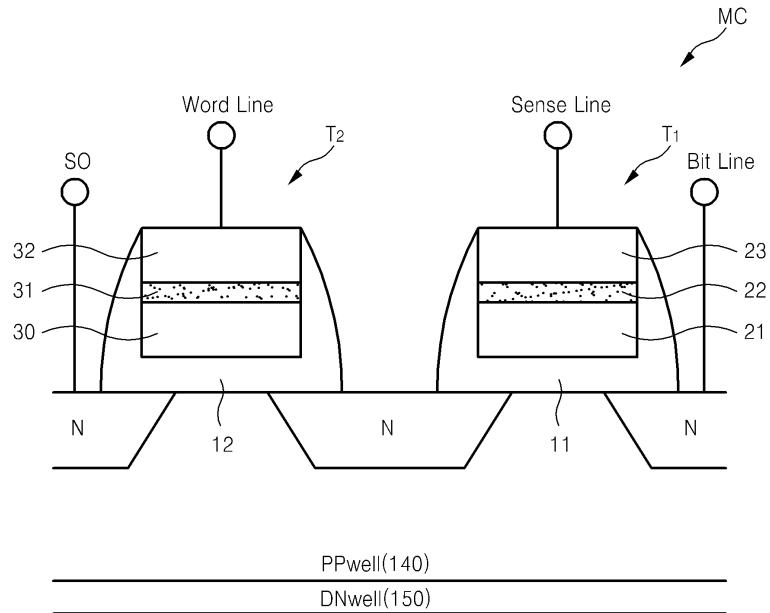

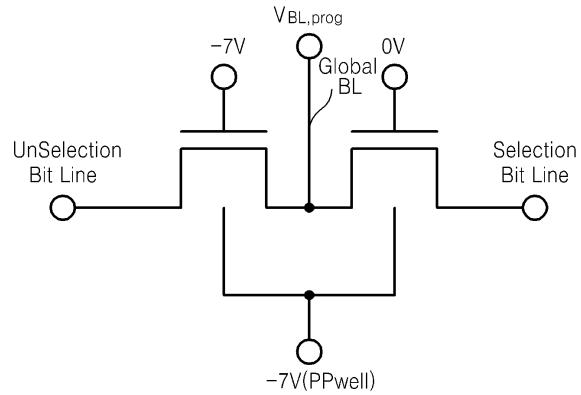

도 3a 및 도 3b는 본 발명의 일 실시예에 따른 메모리 장치의 섹터 선택 스위칭 소자의 동작을 설명하기 위한 도면이다.

도 3a를 참조하여, 프로그램(기록)시의 섹터 선택 스위칭 소자( $T_{41}, T_{42}, T_{43}, T_{44}$ )의 동작을 설명한다.

두 개의 섹터 선택 스위칭 소자( $T_{41}, T_{42}$ )는 하나의 섹터에 걸쳐 뻗어있는 로컬 비트 라인( $BL_{in}$ , 예를 들어  $BL_{10}$ )과 글로벌 비트 라인(Global BL, 예를 들어, BL0) 사이에 병렬로 연결되어, 로컬 비트 라인( $BL_{in}$ )과 글로벌 비트라인(BLi)을 선택적으로 연결한다.

두 개의 섹터 선택 스위칭 소자( $T_{43}, T_{44}$ )는 다른 하나의 섹터에 걸쳐 뻗어있는 로컬 비트 라인(예를 들어  $BL_{50}$ )과 글로벌 비트 라인(Global BL, 예를 들어, BL0) 사이에 병렬로 연결되어, 로컬 비트 라인( $BL_{in}$ )과 글로벌 비트라인(BLi)을 선택적으로 연결한다.

여기서,  $BL_{10}$ 는 선택된 로컬 비트 라인이고,  $BL_{50}$ 는 선택되지 않은 로컬 비트 라인인 것으로 가정한다. 즉, 제1 메모리 블록(MCB1)이 선택되고, 나머지 메모리 블록(예를 들어, MCB2)는 선택되지 않은 것으로 가정한다.

이 경우, 포켓 P웰(PPwell)에는  $Vni$ (예를 들어, -7V)가 인가되고, 섹터 선택 스위칭 소자( $T_{41}, T_{42}$ )의 제어 게이트에는 0V가 인가되고, 섹터 선택 스위칭 소자( $T_{43}, T_{44}$ )의 제어 게이트에는  $Vni$ (예를 들어, -7V)가 인가된다. 이에 따라, 섹터 선택 스위칭 소자( $T_{43}, T_{44}$ )는 턴오프되고, 섹터 선택 스위칭 소자( $T_{41}, T_{42}$ )는 턴온되어, 글로벌 비트라인(예를 들어,

BL0)과 선택된 로컬 비트 라인(BL<sub>10</sub>)은 전기적으로 연결된다. 섹터 선택 스위칭 소자(T<sub>41</sub>, T<sub>42</sub>)에 의하여 선택된 섹터(제1 메모리 블록, MCB1)에 상응하는 로컬 비트라인들은 각각 대응하는 글로벌 비트라인과 연결된다. 반면, 선택되지 않은 섹터(예를 들어, 제2 메모리 블록, MCB2)에 상응하는 로컬 비트 라인들은 대응하는 글로벌 비트라인에 접속되지 않는다.

따라서, 메모리셀의 프로그램시에, 글로벌 비트라인으로부터 섹터 선택 스위칭 소자(T<sub>41</sub>, T<sub>42</sub>)를 통해 선택된 로컬 비트라인으로 비트라인 프로그램 전압(V<sub>BL,prog</sub>)이 인가된다. 따라서, 프로그램시 전류는 도 3a에서 점선으로 도시된 바와 같이, 글로벌 비트라인으로부터 두 개의 섹터 선택 스위칭 소자(T<sub>41</sub>, T<sub>42</sub>)를 통해 선택된 로컬 비트라인으로 제공될 수 있다. 따라서, 프로그램 속도가 빨라질 수 있다.

비트라인 프로그램 전압(V<sub>BL,prog</sub>)은 표 1에 나타난 바와 같이 프로그램의 경우, 프로그램 금지(program inhibit)의 경우 각각 Vni, 0V이다. 본 발명의 일 실시예에 따른 비휘발성 메모리 소자의 프로그램(program)시의 전압 조건은 표 1과 같다.

[표 1]

|     | BL    | SL  | WL    | S0 | SSG | BSG | PPwell | DNwell |

|-----|-------|-----|-------|----|-----|-----|--------|--------|

| 선택  | Vni/0 | Vpp | Vni/0 | F1 | 0   | 0   | Vni    | Vpp    |

| 비선택 | F1    | 0   | Vnn/0 | F1 | Vni | Vpp | 0      | Vpp    |

(Vpp: positive high voltage, Vpi: positive intermediate voltage, Vnn: negative high voltage, Vni: negative intermediate voltage, F1: floating, 0: ground)

Vpp, Vpi, Vnn, Vni은 각각 예를 들어, 10, 7, -10, -7V 일 수 있다.

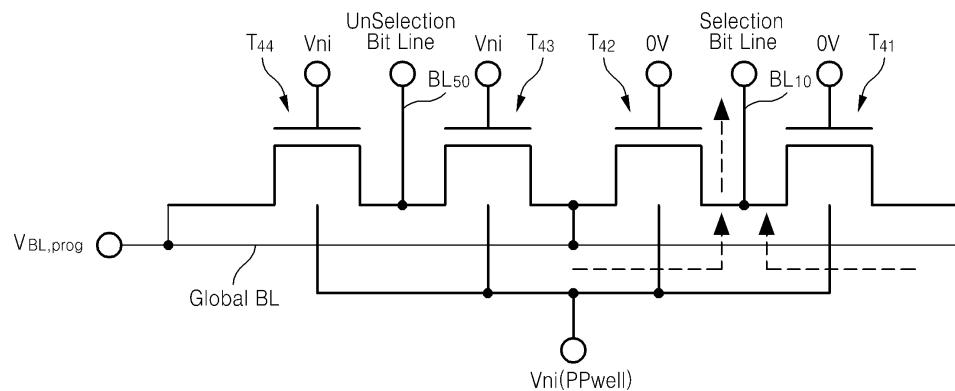

도 3b를 참조하여 판독(read)시의 섹터 선택 스위칭 소자(T<sub>41</sub>, T<sub>42</sub>, T<sub>43</sub>, T<sub>44</sub>)의 동작을 설명한다.

글로벌 비트라인(Global BL, 예를 들어, BL0), 로컬 비트라인들(BL<sub>10</sub>, BL<sub>50</sub>) 및 섹터 선택 스위칭 소자(T<sub>41</sub>, T<sub>42</sub>, T<sub>43</sub>, T<sub>44</sub>)의 연결 관계는 도 3a에 도시된 바와 같다. 다만, 메모리 셀의 판독시의 전압 조건은 도 3a에 도시된 프로그램시의 전압 조건과 다르다.

본 발명의 일 실시예에 따른 비휘발성 메모리 소자의 판독시의 전압 조건은 표 2와 같다.

[표 2]

|     | BL    | SL | WL | S0 | SSG | BSG | PPwell | DNwell |

|-----|-------|----|----|----|-----|-----|--------|--------|

| 선택  | Vcc/0 | Vr | Vr | 0  | Vcc | 0   | 0      | Vcc    |

| 비선택 | 0     | Vr | 0  | 0  | 0   | Vcc | 0      | Vcc    |

(Vpp: positive high voltage, Vpi: positive intermediate voltage, Vnn: negative high voltage, Vni: negative intermediate voltage, Vr: read voltage, 0: ground)

여기서도,  $BL_{10}$ 는 선택된 로컬 비트 라인이고,  $BL_{50}$ 는 선택되지 않은 로컬 비트 라인인 것으로 가정한다. 즉, 제1 메모리 블록(MCB1)이 선택되고, 나머지 메모리 블록(예를 들어, MCB2)은 선택되지 않은 것으로 가정한다.

이 경우, 포켓 P웰(PPwell)에는 0V가 인가되고, 섹터 선택 스위칭 소자( $T_{41}, T_{42}$ )의 제어 게이트에는 Vcc가 인가되고, 섹터 선택 스위칭 소자( $T_{43}, T_{44}$ )의 제어 게이트에는 0V가 인가되며, 글로벌 비트라인에는 비트라인 판독 전압( $V_{BL,read}$ )이 인가된다. 이에 따라, 섹터 선택 스위칭 소자( $T_{43}, T_{44}$ )는 턴오프되고, 섹터 선택 스위칭 소자( $T_{41}, T_{42}$ )는 턴온되어, 글로벌 비트라인과 선택된 로컬 비트 라인( $BL_{10}$ )은 연결된다. 비트라인 판독 전압( $V_{BL,read}$ )은 Vcc, 0 혹은 0과 Vcc 사이의 적절한 전압레벨(예를 들어, 0.5V)로 설정될 수 있다.

선택된 메모리셀이 온셀인 경우, 도 3b에서 점선으로 도시된 바와 같이, 선택된 로컬 비트라인( $BL_{10}$ )으로부터 두 개의 섹터 선택 스위칭 소자( $T_{41}, T_{42}$ )를 통해 글로벌 비트라인(BL0)으로 온셀 전류가 흐른다. 두 개의 섹터 선택 스위칭 소자( $T_{41}, T_{42}$ )를 글로벌 비트라인과 해당 로컬 비트라인 사이에 병렬로 연결함으로써, 트랜지스터 폭이 증가되는 효과를 얻는다. 따라서, 로컬 비트라인에 흐르는 온셀 전류가 섹터 선택 스위칭 소자( $T_{41}, T_{42}$ )에 의해 제한되지 않고 글로벌 비트라인으로 제공되며, 글로벌 비트라인과 연결되는 센스 앰프에서 온셀 전류를 오류없이 감지할 수 있다. 또한, 판독 속도가 빨라질 수 있다.

따라서, 본 발명의 일 실시예에 의하면, 섹터 선택 스위칭 소자의 전류 드라이빙 능력이 향상되어, 비트라인 전류, 특히 온셀 전류의 특성이 개선될 수 있다.

도 4a 및 도 4b는 본 발명의 비교예에 따른 섹터 선택 스위칭 소자의 동작을 설명하기 위한 도면이다.

도 4a를 참조하여, 본 발명의 일 비교예에 따른 메모리 장치의 프로그램시의 섹터 선택 스위칭 소자의 동작을 살펴보면 다음과 같다.

도 4a에 도시된 예에서는, 글로벌 비트 라인은 하나의 섹터 선택 트랜지스터를 통하여 대응하는 로컬 비트라인과 연결된다. 따라서, 글로벌 비트 라인과 선택된 로컬 비트라인을 연결하는 섹터 선택 트랜지스터가 턴온되는 경우, 비트라인 프로그램 전압( $V_{BL,prog}$ )은 글로벌 비트 라인으로부터 하나의 섹터 선택 트랜지스터를 통하여 선택된 로컬 비트라인으로 인가된다.

도 4b를 참조하면, 선택된 로컬 비트라인에 연결된 섹터 선택 스위칭 소자의 제어 게이트에는 Vcc가 인가되고, 선택되지 않은 로컬 비트라인에 연결된 섹터 선택 스위칭 소자의 제어 게이트에는 0V가 인가된다. 제어 게이트에 Vcc가 인가된 섹터 선택 스위칭 소자가 턴온되어, 글로벌 비트라인과 선택된 로컬 비트 라인은 연결된다.

선택된 메모리셀이 온셀인 경우, 선택된 로컬 비트라인으로부터 하나의 섹터 선택 스위칭 소자를 통해 글로벌 비트라인으로 온셀 전류가 흐른다. 그런데, 섹터 선택 스위칭 소자는 종래기술에서 상술한 바와 같이, 셀 유닛 피치에 맞게 형성된 트랜지스터로 구현되므로 액티브폭이 제한되어, 셀 전류를 제한하는 병목(bottleneck)으로 작용할 수 있다.

반면, 본 발명에서는, 글로벌 비트라인과 각 로컬 비트라인을 선택적으로 연결하는 스위칭 소자를 두 라인 사이에 병렬로 구성되는 둘 이상의 섹터 선택 스위칭 소자로 구현함으로써, 섹터 선택 스위칭 소자의 전류 드라이빙 능력이 향상된다. 이에 따라 온셀 전류 특성이 개선된다.

본 발명은 도면에 도시된 일 실시 예를 참고로 설명되었으나 이는 예시적인 것에 불과하며, 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호 범위는 첨부된 등록청구범위의 기술적 사상에 의해 정해져야 할 것이다.

### 발명의 효과

상술한 바와 같이 본 발명에 의하면, EEPROM 메모리셀의 전류 특성, 특히 온셀 전류 특성이 개선된다. 이에 따라, 판독 속도(Read Speed)가 빨라지고, 온셀/오프셀의 판별이 용이하여 판독 오류 가능성은 감소되는 효과가 있다.

## 도면의 간단한 설명

본 발명의 상세한 설명에서 인용되는 도면을 보다 충분히 이해하기 위하여 각 도면의 간단한 설명이 제공된다.

도 1은 본 발명의 일 실시예에 따른 비휘발성 메모리 장치의 메모리 어레이의 일부분을 나타내는 회로도이다.

도 2는 본 발명의 일 실시예에 따른 메모리 장치의 메모리 셀의 개략적으로 도시한 단면도이다.

도 3a 및 도 3b는 본 발명의 일 실시예에 따른 메모리 장치의 섹터 선택 스위칭 소자의 동작을 설명하기 위한 도면이다.

도 4a 및 도 4b는 본 발명의 비교예에 따른 메모리 장치의 섹터 선택 스위칭 소자의 동작을 설명하기 위한 도면이다.

### 도면

도면1

도면2

도면3a

도면3b

도면4a

도면4b