(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6520085号

(P6520085)

(45) 発行日 令和1年5月29日(2019.5.29)

(24) 登録日 令和1年5月10日(2019.5.10)

(51) Int.Cl.

F 1

H01G 4/33 (2006.01)

H01G 4/30 (2006.01)H01G 4/33

H01G 4/30102

541

請求項の数 4 (全 13 頁)

(21) 出願番号 特願2014-246925 (P2014-246925)

(22) 出願日 平成26年12月5日 (2014.12.5)

(65) 公開番号 特開2016-111182 (P2016-111182A)

(43) 公開日 平成28年6月20日 (2016.6.20)

審査請求日 平成29年8月2日 (2017.8.2)

(73) 特許権者 000003067

TDK株式会社

東京都中央区日本橋二丁目5番1号

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100113435

弁理士 黒木 義樹

(74) 代理人 100124062

弁理士 三上 敬史

(72) 発明者 浪川 達男

東京都港区芝浦三丁目9番1号 TDK株式会社内

(72) 発明者 青谷 淳司

東京都港区芝浦三丁目9番1号 TDK株式会社内

最終頁に続く

(54) 【発明の名称】薄膜キャパシタ

## (57) 【特許請求の範囲】

## 【請求項 1】

下地電極上に誘電体層および上部電極層を順次積層した積層体と、少なくとも前記下地電極の一部、前記誘電体層および前記上部電極層を被覆するとともに、前記下地電極に達する第一の貫通孔と、前記上部電極層に達する第二の貫通孔とを、それぞれ備えた保護層と、

前記下地電極上の前記保護層にある前記第一の貫通孔を通して前記下地電極と電気的に接続する第一の引出電極と、

前記上部電極層上の前記保護層にある前記第二の貫通孔を通して前記上部電極層と電気的に接続する第二の引出電極と、

前記第一の引出電極を介して前記下地電極を外部回路と接続する第一の端子電極と、

前記第二の引出電極を介して前記上部電極層を外部回路と接続する第二の端子電極と、を備え、

前記保護層と前記第一の端子電極との間、および前記保護層と前記第二の端子電極との間に、それぞれ開口部を備えた絶縁層を有し、

前記第一の端子電極は前記第一の引出電極と、前記第二の端子電極は前記第二の引出電極と、それぞれの前記絶縁層に設けられた前記開口部を通じて接続されており、

前記絶縁層の成膜領域が、前記第一の端子電極および前記第二の端子電極の面積よりも広く、

前記保護層の縦弾性係数(ヤング率)が、0.1 GPa以上2.0 GPa以下であるこ

10

20

とを特徴とする薄膜キャパシタ。

【請求項 2】

前記保護層は、前記上部電極層上端からの膜厚が3.0 μm以上7.0 μm以下であることを特徴とする請求項1に記載の薄膜キャパシタ。

【請求項 3】

前記絶縁層の縦弾性係数(ヤング率)が、3.0 GPa以上であることを特徴とする請求項1又は2に記載の薄膜キャパシタ。

【請求項 4】

前記下地電極は、Ni箔であることを特徴とする請求項1から3のいずれか一項に記載の薄膜キャパシタ。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、薄膜キャパシタに関するものである。

【背景技術】

【0002】

薄膜キャパシタは、下部電極層、誘電体層および上部電極層を順次積層したキャパシタ素子を、保護層により被覆した構造を有する。保護層には、下部電極層あるいは上部電極層を端子電極と接続するための露出部が設けられる(特許文献1および2参照)。

20

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003-109844号公報

【特許文献2】特開2003-347157号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

保護層の機能の一つに、キャパシタ素子と外部回路とを接続する端子電極を保持する機能がある。ここで、キャパシタ素子には誘電体層の電歪効果に基づく変形が生じる。保護層は、このようなキャパシタ素子の変形を端子電極に波及させないものであることが望ましい。薄膜キャパシタは、積層セラミックキャパシタと比較してキャパシタ素体が薄い。そのため、薄膜キャパシタは端子電極の形成および端子電極の接触維持が困難である。薄膜キャパシタにおいて、保護層がキャパシタ素子の変形を端子電極に波及させない機能を有することは重要である。

30

【0005】

しかし、本発明者らの検討によれば、従来公知の保護層では、キャパシタ素子の変形が端子電極に及ぼす影響が解消されない場合が多い。例えば、特許文献1および2に記載の薄膜キャパシタを試作したところ、継続的に端子電極の接続強度が低下する傾向が認められた。

【0006】

40

本発明は、上記問題点を鑑みてなされたものであり、端子電極の接続強度を維持し、外部回路との接続をより安定化しうる薄膜キャパシタの提供を目的とする。

【課題を解決するための手段】

【0007】

上記課題は、本発明に係る薄膜キャパシタによって解決される。本発明に係る薄膜キャパシタは、下地電極上に誘電体層および上部電極層を順次積層した積層体と、少なくとも下地電極の一部、誘電体層および上部電極層を被覆するとともに、下地電極に達する第一の貫通孔と、上部電極層に達する第二の貫通孔とを、それぞれ備えた保護層と、下地電極上の保護層にある第一の貫通孔を通して下地電極と電気的に接続する第一の引出電極と、上部電極層上の保護層にある第二の貫通孔を通して上部電極層と電気的に接続する第二の引

50

出電極と、第一の引出電極を介して下地電極を外部回路と接続する第一の端子電極と、第二の引出電極を介して上部電極層を外部回路と接続する第二の端子電極と、を備える。このとき、保護層の縦弾性係数（一般に「ヤング率」と称する。以下、単に「ヤング率」という。）を0.1 GPa以上、2.0 GPa以下とする。この構成によって、端子電極の機械的強度が維持され、もって薄膜キャパシタの外部回路との接続を安定化させることができる。ヤング率が2.0 GPaよりも大きくなると、キャパシタの使用を通じて発生する誘電体層の電歪効果に基づく変形が保護層によって吸収されにくくなり、端子電極へ波及することによって、端子電極と外部回路との接続維持が困難となってしまう。また、ヤング率が0.1 GPaよりも小さい場合は、端子電極の固定が不安定になってしまう。

## 【0008】

10

本発明に係る薄膜キャパシタの保護層は、下地電極上に誘電体層および上部電極層を順次積層した積層体の上端からの厚みが3.0 μm以上7.0 μm以下とすることができる。この構成によって、端子電極を構成する金属層を誘電体層から離間させることができ、キャパシタの使用を通じて発生する誘電体層の電歪効果に基づく変形をより効率的に吸収できる。その結果、薄膜キャパシタの外部回路との接続をより安定化させることができる。この厚みが3.0 μmよりも薄い場合、キャパシタの使用を通じて発生する誘電体層の電歪効果に基づく変形が端子電極に波及してしまう場合がある。また、7.0 μmよりも厚い場合は、端子電極の固定が不安定になってしまう傾向がある。

## 【0009】

20

本発明に係る薄膜キャパシタは、保護層に加えて絶縁層を有した構造とすることができる。この絶縁層は、端子電極直下の保護層を被覆するものである。具体的には、保護層と第一の端子電極との間、および保護層と第二の端子電極との間に開口部を備えた絶縁層を設けることができる。この絶縁層の成膜領域が、第一の端子電極および第二の端子電極の面積よりも広い面積を有した構造としてもよい。その際、端子電極直下およびその周辺の保護層のみを被覆するものであってもよいし、保護層全域を被覆するものであってもよい。絶縁層のヤング率は3.0 GPa以上とすることができる。この構成によって、端子電極の固定を、さらに安定化させることができる。絶縁層のヤング率の上限値は、絶縁層の後工程の有無や種類によって規定の必要が生じる場合がある。しかし、端子電極の固定をより安定化させる効果という観点では、必ずしも上限値を設ける必要はない。

## 【0010】

30

本発明の薄膜キャパシタの下地電極は、Ni箔とすることができる。Ni箔は耐酸化性と低電気抵抗を有する材料であり、他の代表的な導電材料（CuやAlなどの金属）に比して高い硬度とヤング率とを有する。そのため、下地電極が保護層の形状維持に寄与し、本発明の効果である端子電極をさらに安定して固定させることができる。

## 【発明の効果】

## 【0011】

本発明に係る薄膜キャパシタによれば、外部回路との接続をより安定化させた薄膜キャパシタを提供することが可能となる。

## 【図面の簡単な説明】

## 【0012】

40

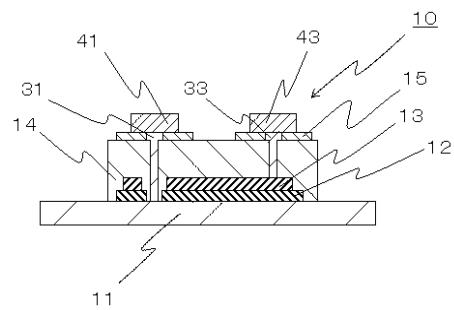

【図1】本発明の一実施形態に係る薄膜キャパシタの構造を示す概略断面図である。

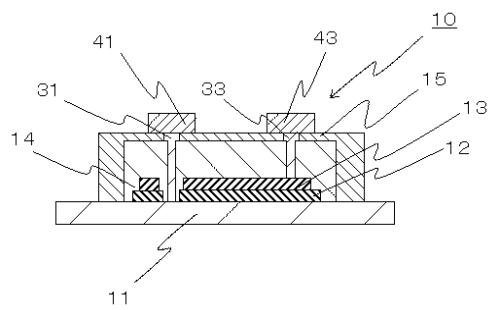

【図2】本発明の別の実施形態に係る薄膜キャパシタの構造を示す概略断面図である。

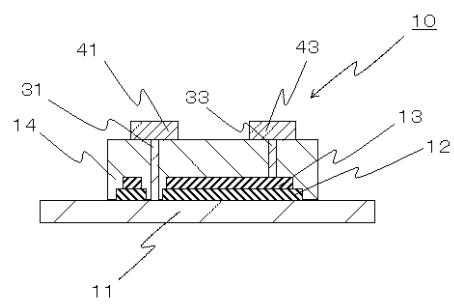

【図3】本発明のさらに別の実施形態に係る薄膜キャパシタの構造を示す概略断面図である。

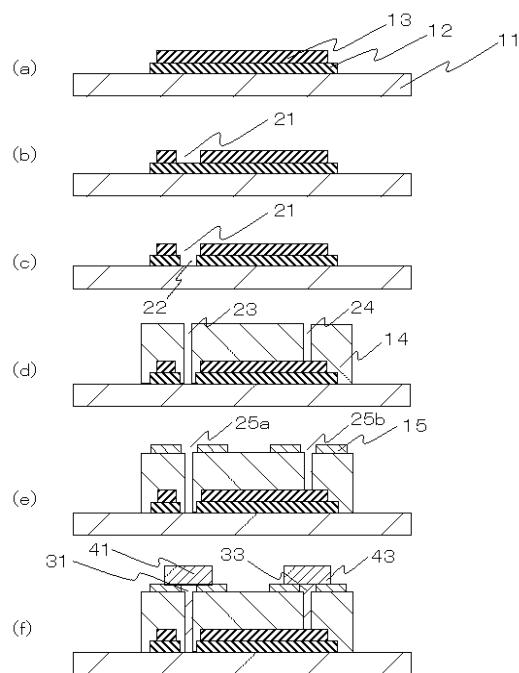

【図4】本発明の一実施形態に係る薄膜キャパシタの製造方法を示す概略断面図である。

## 【発明を実施するための形態】

## 【0013】

以下、本発明の好適な実施形態について説明する。但し、本発明は以下の実施形態に限定されるものではない。なお、同一又は同等の要素については同一の符号を付し、説明が重複する場合にはその説明を省略する。

50

## 【0014】

図1は、本実施形態に係る薄膜キャパシタの構造を示す概略断面図である。薄膜キャパシタ10は、下地電極11と、この下地電極11の上に積層された誘電体層12と、誘電体層12の上に積層された上部電極層13と、誘電体層12および上部電極層13を被覆するとともに下地電極11上に第一の貫通孔(図中の符号表示なし)を、上部電極層13上に第二の貫通孔(図中の符号表示なし)を、それぞれ備えた保護層14と、保護層14内の第一の貫通孔を通して下地電極11と電気的に接続する第一の引出電極31と、保護層14内の第二の貫通孔を通して上部電極層13と電気的に接続する第二の引出電極33と、第一の引出電極31を介して下地電極11を外部回路と接続する第一の端子電極41と、第二の引出電極33を介して上部電極層13を外部回路と接続する第二の端子電極43と、第一の端子電極41および第二の端子電極43直下の保護層14を被覆する絶縁層15と、を備えて構成されている。

## 【0015】

下地電極11は、導電性を有する材料であれば特に制限されない。金属、酸化物、有機導電材料等を適宜選択することができる。高い電気伝導性を有する材料として、例えば、Ni、Pt、Pd、Ir、Ru、Rh、Re、Os、Au、Ag、Cu、IrO<sub>2</sub>、RuO<sub>2</sub>、SrRuO<sub>3</sub>、およびLaNiO<sub>3</sub>の少なくともいずれか1つを含むように構成してもよい。下地電極11の膜厚は、電気伝導度と機械的強度との観点から、50～2000nmであることが好ましい。50nmを下回る場合、下地電極11の電気抵抗が大きくなり薄膜キャパシタの電気特性を低下させる場合がある。2000nmを超える場合、下地電極11の内部応力が誘電体層12に及ぼす圧力が顕著となる傾向がある。下地電極11は、Siやアルミナなどの基板(図示せず)の上に設けられていてもよいが、下地電極11が基板の機能を兼ねていてもよい。この場合、下地電極11と基板とは同一の材料となる。例えば、Ni、Cu、Al等の卑金属またはこれらの合金を主成分とした箔や板、ステンレス鋼、インコネル(登録商標)等の板や箔を好適に用いることができる。特にNi箔は、高い伝導性を有するとともに高い硬度とヤング率とを有し、保護層14と絶縁層15との形状維持に寄与するため好ましい。下地電極11と基板を同一材料とした場合の下地電極11の厚さは5μm～500μmであることが好ましい。下地電極11の厚さが5μmを下回る場合は、下地電極11の機械的強度が保護層14と絶縁層15との形状を維持できる大きさを下回る場合がある。逆に下地電極11の厚さが500μmを超える場合は、薄膜キャパシタ製造工程に不可避な熱履歴に起因する歪の蓄積量が大きくなり、保護層14と絶縁層15との形状維持に悪影響を及ぼす場合がある。本実施形態では、下地電極11にNi箔を用いた態様を示す。Ni箔である下地電極11は、誘電体層12や上部電極層13等を保持する保持部材としての機能と、下部電極層としての機能と、を兼ね備えている。なお、基板/電極膜構造を用いる形態の場合は、基板/電極膜を組合せた構造体を本実施形態の下地電極11に対応させて、本発明の実施形態とすることができる。

## 【0016】

誘電体層12は、チタン酸バリウム(BaTiO<sub>3</sub>、以下「BT」という。)、チタン酸バリウムストロンチウム((BaSr)TiO<sub>3</sub>、以下「BST」という。)、チタン酸ストロンチウム(SrTiO<sub>3</sub>、以下「ST」という。)、ジルコン酸カルシウム(CaZrO<sub>3</sub>、(BaSr)(TiZr)O<sub>3</sub>、以下「CZ」という。)、BaTiZrO<sub>3</sub>などのペロブスカイト型酸化物が好適に用いられる。誘電体層12は、これらの酸化物のうち一つ以上を含む複合材料であってもよいし、複数の誘電体層の積層体であってもよい。誘電体層12の膜厚は、誘電体素子の機能と機械的強度保持の観点から100～1000nm程度とすることができます。誘電体層12の形成方法は特に制限されず、公知の誘電体薄膜作成方法を適宜選択して用いることができる。例えば、スパッタリング法や蒸着法等の物理的気相成長法を用いてもよいし、プラズマCVD法等の化学的気相成長法を用いてもよい。あるいは、出発原料を含む溶液を塗布して焼成する溶液法を用いてもよい。

## 【0017】

上部電極層13は、導電性を有する材料であれば特に制限されない。金属、酸化物、有機

10

20

30

40

50

導電材料等を適宜選択することができる。高い電気伝導性を有する材料として、例えば、Ni、Pt、Pd、Ir、Ru、Rh、Re、Os、Au、Ag、Cu、IrO<sub>2</sub>、RuO<sub>2</sub>、SrRuO<sub>3</sub>、およびLaNiO<sub>3</sub>の少なくともいずれか1つを含むように構成してもよい。特に、Cu、Ni、Pt、Pd、Ir、Ru、Rh、Re、Os、Au、Agを主成分として構成される導電性材料が好ましく、中でもNiを主成分として構成される導電性材料が電気的特性と機械的強度との観点から好ましい。上部電極層13はNiを単体で用いる必要はなく、たとえばNi/Cuのような積層構造としてもよい。この場合、上部電極層13のNi層側を誘電体層12側にコンタクトさせ、Cu側を外部とすることができます。さらに、CuはNiに比して導電性が高いため、Cuの厚みをNiに比して増すことにより上部電極層13の導電性を高めることができる。

10

#### 【0018】

保護層14は、ヤング率が0.1GPa以上2.0GPa以下の材料を適宜選択して用いることができる。例えば、ポリイミド系樹脂、エポキシ系樹脂、フェノール系樹脂、ベンゾシクロブテン系樹脂、ポリアミド系樹脂、フッ素系樹脂などの絶縁樹脂を好適に用いることができる。特に、ポリイミド系樹脂は吸湿率および吸水率が小さいという点で好ましい。これら材料のヤング率は、高分子材料の機械的特性を調整する公知の手段を適宜用いて調整することができる。例えば、(1)側鎖もしくは分子鎖へのアルキル基の導入、(2)分子鎖へのイオウの導入(加硫)、(3)架橋点の削減(分子鎖の酸素基を水素終端に変える、など)、(4)反応途中での重合禁止剤の投入による重合反応の制限、のような手段を用いることができる。

20

#### 【0019】

保護層14のヤング率は、ナノインデンテーション法により求めることができる。ナノインデンテーション法に用いられるナノインデンターは、圧子の押し込みによって薄膜の機械的特性を評価する手法として知られているところ、薄膜自身の機械的強度評価には下地の影響を受けない程度の最大押し込み深さで荷重-変位曲線を得る必要がある。上述した保護層14のヤング率は、下地の影響を考慮して最大押し込み深さを保護層14の膜厚の1/5から1/3程度として得られた荷重-変位曲線から算出された結果であることが望ましい。具体的には、荷重20mNから100mN程度の低荷重で予備測定を行っておくことが望ましい。

#### 【0020】

30

絶縁層15を設ける場合は、ヤング率が3.0GPa以上の材料を適宜選択して用いることができる。例えば、ポリイミド系樹脂、エポキシ系樹脂、フェノール系樹脂、ベンゾシクロブテン系樹脂、ポリアミド系樹脂、フッ素系樹脂などの絶縁樹脂などを好適に用いることができる。絶縁層15の材料のヤング率も、保護層14の場合と同様に、高分子材料の機械的特性を調整する公知の手段を適宜用いて調整することができる。改めて例示するならば、(1)側鎖もしくは分子鎖へのアルキル基の導入、(2)分子鎖へのイオウの導入(加硫)、(3)架橋点の削減(分子鎖の酸素基を水素終端に変える、など)、(4)反応途中での重合禁止剤の投入による重合反応の制限、のような手段である。絶縁層15のヤング率も、保護層14と同様にナノインデンテーション法を用いて求めることができる。

40

#### 【0021】

絶縁層15の形成は、いくつかの態様によって行うことができる。絶縁層15は、図1に示すように、後述する第一の端子電極41ならびに第二の端子電極43の直下およびその周辺の保護層14のみを被覆するものであってもよい。また、図2に示す本発明の別の実施形態のように、必ずしもに絶縁層15の形成を必須としなくてもよい。反対に、図3に示す本発明のさらに別の実施形態のように、絶縁層15により保護層14全域を被覆する態様であってもよい。

#### 【0022】

第一の引出電極31ならびに第二の引出電極33は、導電性の高い材料を適宜選択して用いることができる。例えば、Au、Ag、Pt、Cuなどを用いることができる。機械的

50

特性と電気伝導性の両立という観点から、Cuを主成分として構成されるのが好ましい。

【0023】

第一の端子電極41ならびに第二の端子電極43は、導電性の高い材料を適宜選択して用いることができる。例えば、Au、Ag、Pt、Cuなどを用いることができる。機械的特性と電気伝導性の両立という観点から、Cuを主成分として構成されるのが好ましい。第一の端子電極41ならびに第二の端子電極43の外層には、Au、Ni、Sn、Pdなどの層を設けてもよい。

【0024】

次に、図4を参照して、薄膜キャパシタ10の製造方法を説明する。

【0025】

まず、図4(a)に示すように、下地電極11上に誘電体層12の成膜及び上部電極層13の成膜を行い、積層体を形成する。

10

【0026】

次に、図4(b)に示すように、上部電極層13の一部に対して下地電極11方向にウェットエッティングを施し、開口部21を形成する。上部電極層13をエッティングするときは、フォトリソグラフィによるパターニングを実施した後、塩化第二鉄等のエッティング液(エッチャント)を用いる。

【0027】

次に、図4(c)に示すように、開口部21にて露出した誘電体層12の一部を、積層体における下地電極11の反対側に位置する表面から下地電極11方向にウェットエッティングを施し、開口部22を形成する。誘電体層12をエッティングするときは、誘電体材料はエッティングするが電極層の材料はエッティングしないエッティング液(エッチャント)を用いる。具体的には、例えば誘電体層12がBT、BST、STの場合、好ましいエッチャントは塩酸+フッ化アンモニウム水溶液である。また、誘電体層12がCZの場合、好ましいエッチャントは硫酸+フッ化アンモニウム水溶液である。

20

【0028】

次に、図4(d)に示すように、保護層14を形成する。この際、開口部22の内部に保護層の開口部23を、ならびに開口部21以外の領域に存在する上部電極層13上に保護層の開口部24を設ける。

【0029】

30

次に、図4(e)に示すように、絶縁層15を形成する。この際、保護層の開口部23の直上に絶縁層の開口部25aを、ならびに保護層の開口部24の直上に絶縁層の開口部25bを設ける。これら図4(d)および(e)の工程によって、第一の貫通孔(23~25a)および第二の貫通孔(24~25b)が形成される。絶縁層15を設けない場合は、第一の貫通孔は保護層の開口部23のみで構成され、第二の貫通孔は保護層の開口部24のみで形成される。

【0030】

そして、シード成膜およびめっき処理を行って、第一の貫通孔(23~25a)を通して下地電極11と接続するように第一の引出電極31および第一の端子電極41を、ならびに第二の貫通孔(24~25b)を通して上部電極層13と接続するように第二の引出電極33および第二の端子電極43を形成する(図4(f))。

40

【0031】

このように、本実施形態に係る薄膜キャパシタ10によれば、保護層14のヤング率が2.0GPa以下であることにより、キャパシタの使用を通じて発生する誘電体層12の電歪効果に基づく変形を保護層14によって吸収させることができ、第一の端子電極41ならびに第二の端子電極43と外部回路との接触を安定して維持できる。また、保護層14のヤング率が0.1GPa以上であることにより、保護層14上に第一の端子電極41ならびに第二の端子電極43を安定して固定できる。さらに、第一の端子電極41ならびに第二の端子電極43直下の保護層14を被覆する位置に、ヤング率が3.0GPa以上である絶縁層15を設けることによって、第一の端子電極41ならびに第二の端子電極43

50

の固定をより安定化させることができる。

【0032】

以下、実施例および比較例を挙げて、本発明についてより具体的に説明する。ただし、本発明は以下の実施例に限定されるものではない。

【0033】

図1から図3のいずれかに示す断面形状を有する薄膜キャパシタ10を、実施例1～33、および比較例1～3として作製し評価した。

【0034】

(実施例1～9)

下地電極11として厚み100μmのNi箔を用意し、その片面に誘電体層12であるBT層を誘電率1000、膜厚900nmとなるようにスパッタリング法で形成した。誘電体層12上には、上部電極層13(下層、誘電体層12側)であるNi層をスパッタリング法で形成し、Ni層上に上部電極層13(上層)であるCu層をスパッタリング法で形成した。その際、容量が約8000pF(8nF)となるように、上部電極層13の面積及びパターン形状と、誘電体層12の厚みと、を設定した(図4(a)参照)。

【0035】

誘電体層12及び上部電極層13の形成後、熱処理を行った。熱処理後の上部電極層13に対して、下地電極11との接続を行う位置に開口部21を有するレジスト層を形成した。開口部21の形状はマスクパターン上で正方形とし、サイズはマスクパターン上で150μm×150μmとした。その後、開口部21の上部電極層13を塩化第二鉄溶液によりエッティング除去した。その後レジスト層を剥離した(図4(b)参照)。

【0036】

開口部21の位置に露出した誘電体層12に対して、さらに開口部22を有するレジスト層を形成した。開口部22の形状はマスクパターン上で正方形とし、サイズはマスクパターン上で100×100μmとした。その後、開口部22の誘電体層12を塩酸とフッ化アンモニウム水溶液の混合液を用いてエッティングを行なった。その後レジスト層を剥離した後、熱処理を行った(図4(c)参照)。

【0037】

感光性を有するポリイミド樹脂を用いて保護層14を形成した。ポリイミド樹脂の材料には、(1)通常のポリイミドモノマーと、(2)アルキル基を結合させたポリイミドモノマーと、を混合させた材料を用いた。これらモノマー(1)とモノマー(2)との混合比を変えて予備試験片を作成し、ヤング率を求めた。予備試験の結果を基に、実施例に係る保護層14のヤング率が三水準で得られるよう形成を試みた。得られた保護層14のヤング率を、ナノインデンテーションシステム(Hysitron社製)を用いて求めた。測定は、最大荷重20mNの条件で荷重-変位曲線を一試料あたり100回求め、ヤング率を算出して平均値を求めた。なお、最大変位量は保護層14の膜厚に対して表面から約1/4以下であり、下地電極11の影響は認められなかった。測定の結果、保護層14のヤング率は、0.1GPa、1.0GPa、2.0GPaの三水準となっていることを確認した。三水準のヤング率を有する保護層14について、それぞれ膜厚を3.0μm、5.0μm、7.0μmとして、それらの組み合わせにより計九水準の保護層14を形成した。形成された保護層14に対し、フォトリソグラフィによって開口部22の内部にさらに保護層の開口部23を、および上部電極層13上の開口部21の無い部位に保護層の開口部24を設けた。保護層の開口部23および保護層の開口部24の形状はマスクパターン上で正方形とし、サイズはマスクパターン上で50×50μmとした。(図4(d)参照)。

【0038】

感光性を有するポリイミド樹脂を用いて絶縁層15を形成した。絶縁層15の膜厚は2μmとした。保護層14の場合と同じ要領でモノマーの混合比を変え、ヤング率が3.0GPaである絶縁層15を得た。フォトリソグラフィによって保護層の開口部23の直上に絶縁層の開口部25aを、保護層の開口部24の直上に絶縁層の開口部25bをそれぞれ

設け、第一の貫通孔（23～25a）および第二の貫通孔（24～25b）とした。絶縁層の開口部25aおよび絶縁層の開口部25bの形状はマスクパターン上で正方形とし、サイズはマスクパターン上で $75 \times 75 \mu\text{m}$ とした。また、後述する第一の端子電極41ならびに第二の端子電極43の直下およびその周辺のみ絶縁層15が残留するようパターンを形成した。（図4（e）参照）。

#### 【0039】

以上の手順で、九水準（実施例1～9）に対応。各水準は表1を参照。）に保護層14のヤング率および膜厚を変化させた計270個（一水準あたり30個）の薄膜キャパシタ素体を得た。薄膜キャパシタ素体に対し、Cuシード成膜およびCuめっき処理にて第一の引出電極31および第一の端子電極41、ならびに第二の引出電極33および第二の端子電極43を形成した。その際、第一の引出電極31および第一の端子電極41は第一の貫通孔（23～25a）を通じて下地電極11と接続させ、第二の引出電極33および第二の端子電極43は第二の貫通孔（24～25b）を通じて上部電極層13と接続させた。さらに、第一の端子電極41ならびに第二の端子電極43は、絶縁層15よりも狭い領域に存在する形状で作製した（図4（f）参照）。

10

#### 【0040】

ダイシングによって幅0.8mm、長さ1.6mmの形状に薄膜キャパシタ素体を個片化して、270個の薄膜キャパシタ10を得た。得られた薄膜キャパシタ10について、JIS C 60068-2-21:2009に基づいた、厚さ0.8mmの耐基板曲げ性試験用プリント配線基板上に実装したうえで1Vrms、1kHz、室温条件下で静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.05nF、標準偏差は0.2nFとなった。また、絶縁抵抗値を測定したところ、 $1.0 \sim 2.0 \times 10^{11}$ の範囲内であった。

20

#### 【0041】

薄膜キャパシタ10に対して耐基板曲げ性試験をおこなった。薄膜キャパシタ10を実装したプリント配線基板に対して、JIS C 60068-2-21:2009に基づき、1.0mm/sの加圧速度で4.0mmまで曲げ、20秒間保持した。その後曲げ力を緩めてから、1Vrms、1kHz、室温条件下で静電容量を測定し、耐基板曲げ性試験を実施する前の静電容量値に対して1/1000以下となった薄膜キャパシタ10をNGと判断し、NG個数をカウントして評価結果とした。

30

#### 【0042】

薄膜キャパシタ10に対して耐湿動作試験をおこなった。耐湿動作試験では、プリント配線基板上に実装した薄膜キャパシタ10を60、90%RHに調節した恒温槽内に入れ、交流電圧4Vrms、1kHzを1000時間印加した。1000時間経過後の薄膜キャパシタ10に対して再度静電容量および絶縁抵抗を測定し、絶縁抵抗値が恒温槽に入れる前の絶縁抵抗値に対して1/100以下となった薄膜キャパシタ10をNGと判断し、NG個数をカウントして評価結果とした。

#### 【0043】

薄膜キャパシタ10に対して、再び同条件で耐基板曲げ性試験をおこなった。曲げ力を緩めてから、1Vrms、1kHz、室温条件下で静電容量を測定し、耐基板曲げ性試験を実施する前の静電容量値に対して1/1000以下となった薄膜キャパシタ10をNGと判断し、NG個数をカウントして評価結果とした。

40

#### 【0044】

##### （実施例10～12）

保護層14のヤング率を0.1GPa、1.0GPa、2.0GPaの三水準、保護層14の膜厚を5.0μmの一水準として、絶縁層15を保護層14の全域被覆としたこと以外は、実施例1～9と同様の手順で薄膜キャパシタ10を作製し、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.05nF、標準偏差は0.17nFとなった。また、絶縁抵抗値を測定したところ、 $1.0 \sim 2.0 \times 10^{11}$ の範囲内であった。

50

## 【0045】

## (実施例13～18)

保護層14のヤング率を0.1GPa、1.0GPa、2.0GPaの三水準、保護層14の膜厚を5.0μmの一水準として、絶縁層15のヤング率を1.0GPa、2.8GPaの二水準としたこと以外は、実施例1～9と同様の手順で薄膜キャパシタ10を作製し、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.05nF、標準偏差は0.18nFとなった。また、絶縁抵抗値を測定したところ、 $1.0 \sim 2.0 \times 10^{11}$ の範囲内であった。

## 【0046】

10

## (実施例19～21)

保護層14のヤング率を0.1GPa、1.0GPa、2.0GPaの三水準、保護層14の膜厚を5.0μmの一水準として、絶縁層15を設けなかったこと、および、第一の端子電極41ならびに第二の端子電極43を保護層14上に設けたこと以外は、実施例1～9と同様の手順で薄膜キャパシタ10を作製し、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.01nF、標準偏差は0.21nFとなった。また、絶縁抵抗値を測定したところ、 $1.0 \sim 2.0 \times 10^{11}$ の範囲内であった。

## 【0047】

20

## (実施例22～24)

下地電極11を、500μm厚みのアルミナ基板上に厚み600nmのNi薄膜を形成したものとしたこと、保護層14のヤング率を1.0GPa、膜厚を5.0μmの一水準に固定したこと、絶縁層15については、それぞれ第一の端子電極41ならびに第二の端子電極43の周辺のみとしてヤング率を3.0GPaとした（実施例22）、保護層14の全域被覆としてヤング率を3.0GPaとした（実施例23）、第一の端子電極41ならびに第二の端子電極43の周辺のみとしてヤング率を2.8GPaとした（実施例24）、こと以外は、実施例1～9と同様の手順で薄膜キャパシタ10を作製し、耐基板曲げ性試験の曲げ量を2.0mmとしたこと以外は、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.06nF、標準偏差は0.14nFとなった。また、絶縁抵抗値を測定したところ、 $1.0 \sim 2.0 \times 10^{11}$ の範囲内であった。

30

## 【0048】

## (実施例25)

下地電極11を、500μm厚みのアルミナ基板上に厚み600nmのNi薄膜を形成したものとしたこと、保護層14のヤング率を1.0GPa、膜厚を5.0μmの一水準に固定したこと、絶縁層15を設けなかったこと、および、第一の端子電極41ならびに第二の端子電極43を保護層14上に設けたこと以外は、実施例1～9と同様の手順で薄膜キャパシタ10を作製し、耐基板曲げ性試験の曲げ量を2.0mmとしたこと以外は、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.02nF、標準偏差は0.14nFとなった。また、絶縁抵抗値を測定したところ、 $1.0 \sim 2.0 \times 10^{11}$ の範囲内であった。

40

## 【0049】

## (実施例26～27)

保護層14のヤング率を1.0GPaの一水準に固定したこと、保護層14の膜厚を2.5μm（実施例26）、7.5μm（実施例27）の二水準としたこと以外は、実施例1～9と同様の手順で薄膜キャパシタ10を作製し、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.04nF、標準偏差は0.23nFとなった。また、絶縁抵抗値を測定したところ、 $1.0 \sim 2.0 \times 10^{11}$ の範囲内であった。

50

## 【0050】

## (実施例28～29)

保護層14のヤング率を1.0GPaの一水準に固定したこと、保護層14の膜厚を2.5μm(実施例26)、7.5μm(実施例27)の二水準としたこと、絶縁層15のヤング率を2.8GPaの一水準に固定したこと以外は、実施例1～9と同様の手順で薄膜キャパシタ10を作製し、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.04nF、標準偏差は0.22nFとなった。また、絶縁抵抗値を測定したところ、1.0～2.0×10<sup>11</sup>の範囲内であった。

## 【0051】

10

## (実施例30～31)

保護層14のヤング率を1.0GPaの一水準に固定したこと、保護層14の膜厚を2.5μm(実施例26)、7.5μm(実施例27)の二水準としたこと、絶縁層15を設けなかったこと、および、第一の端子電極41ならびに第二の端子電極43を保護層14上に設けたこと以外は、実施例1～9と同様の手順で薄膜キャパシタ10を作製し、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.01nF、標準偏差は0.22nFとなった。また、絶縁抵抗値を測定したところ、1.0～2.0×10<sup>11</sup>の範囲内であった。

## 【0052】

20

## (実施例32～33)

下地電極11を、500μm厚みのアルミナ基板上に厚み600nmのNi薄膜を形成したものとしたこと、保護層14のヤング率を1.0GPaの一水準に固定したこと、保護層14の膜厚を2.5μm(実施例26)、7.5μm(実施例27)の二水準としたこと、絶縁層15を設けなかったこと、および、第一の端子電極41ならびに第二の端子電極43を保護層14上に設けたこと以外は、実施例1～9と同様の手順で薄膜キャパシタ10を作製し、耐基板曲げ性試験の曲げ量を2.0mmとしたこと以外は、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は7.99nF、標準偏差は0.21nFとなった。また、絶縁抵抗値を測定したところ、1.0～2.0×10<sup>11</sup>の範囲内であった。

30

## 【0053】

## (比較例1～3)

保護層14のヤング率を0.05GPa(比較例1)、2.5GPa(比較例2)、3.0GPa(比較例3)とし、保護層14の膜厚を5.0μmの一水準に固定したこと以外は、実施例1～9と同様に薄膜キャパシタ10を作製し、実施例1～9と同様の評価を行った。得られた薄膜キャパシタ10の静電容量を測定し、その平均値及び標準偏差を算出したところ、平均値は8.00nF、標準偏差は0.15nFとなった。また、絶縁抵抗値を測定したところ、1.0～2.0×10<sup>11</sup>の範囲内であった。

## 【0054】

40

以上の実施例1～3及び比較例1～3について、耐湿信頼性試験と、その前後に実施した耐基板曲げ性試験の結果を表1に示す。

## 【0055】

【表1】

|       | 保護層14<br>ヤング率<br>[GPa] | 保護層14<br>膜厚<br>[μm] | 絶縁層15<br>有無 | 絶縁層15の<br>設置領域 | 絶縁層15<br>ヤング率<br>[GPa] | 下地電極<br>材料および構造  | 耐基板曲げ性試験<br>曲げ量<br>[mm] | 耐基板曲げ性試験<br>耐温動作試験前<br>(NG個数/母数) | 耐温動作試験後<br>(NG個数/母数) | 耐基板曲げ性試験<br>耐温動作試験後<br>(NG個数/母数) |

|-------|------------------------|---------------------|-------------|----------------|------------------------|------------------|-------------------------|----------------------------------|----------------------|----------------------------------|

| 実施例1  | 0.1                    | 3.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例2  | 1.0                    | 3.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例3  | 2.0                    | 3.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例4  | 0.1                    | 5.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例5  | 1.0                    | 5.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例6  | 2.0                    | 5.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例7  | 0.1                    | 7.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例8  | 1.0                    | 7.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例9  | 2.0                    | 7.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例10 | 0.1                    | 5.0                 | 有           | 保護層14全域被覆      | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例11 | 1.0                    | 5.0                 | 有           | 保護層14全域被覆      | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例12 | 2.0                    | 5.0                 | 有           | 保護層14全域被覆      | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 0/30                             |

| 実施例13 | 0.1                    | 5.0                 | 有           | 端子電極周辺まで       | 1.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 2/30                             |

| 実施例14 | 1.0                    | 5.0                 | 有           | 端子電極周辺まで       | 1.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 3/30                             |

| 実施例15 | 2.0                    | 5.0                 | 有           | 端子電極周辺まで       | 1.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 3/30                             |

| 実施例16 | 0.1                    | 5.0                 | 有           | 端子電極周辺まで       | 2.8                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 1/30                             |

| 実施例17 | 1.0                    | 5.0                 | 有           | 端子電極周辺まで       | 2.8                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 2/30                             |

| 実施例18 | 2.0                    | 5.0                 | 有           | 端子電極周辺まで       | 2.8                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 2/30                             |

| 実施例19 | 0.1                    | 5.0                 | 無           | —              | —                      | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 5/30                             |

| 実施例20 | 1.0                    | 5.0                 | 無           | —              | —                      | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 4/30                             |

| 実施例21 | 2.0                    | 5.0                 | 無           | —              | —                      | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 5/30                             |

| 実施例22 | 1.0                    | 5.0                 | 有           | 端子電極周辺まで       | 3.0                    | アルミ基板/Ni層(600nm) | 2.0                     | 0/30                             | 0/30                 | 5/30                             |

| 実施例23 | 1.0                    | 5.0                 | 有           | 保護層14全域被覆      | 3.0                    | アルミ基板/Ni層(600nm) | 2.0                     | 0/30                             | 0/30                 | 4/30                             |

| 実施例24 | 1.0                    | 5.0                 | 有           | 端子電極周辺まで       | 2.8                    | アルミ基板/Ni層(600nm) | 2.0                     | 0/30                             | 0/30                 | 6/30                             |

| 実施例25 | 1.0                    | 5.0                 | 無           | —              | —                      | アルミ基板/Ni層(600nm) | 2.0                     | 0/30                             | 0/30                 | 8/30                             |

| 実施例26 | 1.0                    | 2.5                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 3/30                             |

| 実施例27 | 1.0                    | 7.5                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 4/30                             |

| 実施例28 | 1.0                    | 2.5                 | 有           | 端子電極周辺まで       | 2.8                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 6/30                             |

| 実施例29 | 1.0                    | 7.5                 | 有           | 端子電極周辺まで       | 2.8                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 7/30                             |

| 実施例30 | 1.0                    | 2.5                 | 無           | —              | —                      | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 8/30                             |

| 実施例31 | 1.0                    | 7.5                 | 無           | —              | —                      | Ni箔(100μm)       | 4.0                     | 0/30                             | 0/30                 | 9/30                             |

| 実施例32 | 1.0                    | 2.5                 | 無           | —              | —                      | アルミ基板/Ni層(600nm) | 2.0                     | 0/30                             | 0/30                 | 8/30                             |

| 実施例33 | 1.0                    | 7.5                 | 無           | —              | —                      | アルミ基板/Ni層(600nm) | 2.0                     | 0/30                             | 0/30                 | 10/30                            |

| 比較例1  | 0.05                   | 5.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 2/30                 | 28/28                            |

| 比較例2  | 2.5                    | 5.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 1/30                 | 29/29                            |

| 比較例3  | 3.0                    | 5.0                 | 有           | 端子電極周辺まで       | 3.0                    | Ni箔(100μm)       | 4.0                     | 0/30                             | 3/30                 | 27/27                            |

## 【0056】

表1に示すように、本発明の実施により得られる薄膜キャパシタは、端子電極の接続強度が維持され、外部回路との接続がより安定化されていることが確認された。

## 【符号の説明】

## 【0057】

1 0 · · · 薄膜キャパシタ、1 1 · · · 下地電極、1 2 · · · 誘電体層、1 3 · · · 上部電極層、1 4 · · · 保護層、1 5 · · · 絶縁層、2 1 · · · 上部電極層の開口部、2 2 · · · 誘電体層の開口部、2 3 · · · 下地電極までの保護層の開口部(1 5を設けた場合は2 5aと共に第一の貫通孔を構成する)、2 4 · · · 上部電極層までの保護層の開口部(1 5を設けた場合は2 5bと共に第二の貫通孔を構成する)、2 5a · · · 下地電極までの絶縁層の開口部(2 3と共に第一の貫通孔を構成する)、2 5b · · · 上部電極層までの絶縁層の開口部(2 4と共に第二の貫通孔を構成する)、3 1 · · · 下地電極からの引出電極(第一の引出電極)、3 3 · · · 上部電極層からの引出電極(第二の引出電極)、4 1 · · · 下地電極と接続する端子電極(第一の端子電極)、4 3 · · · 上部電極層と接続する端子電極(第二の端子電極)

10

20

30

40

【図1】

【図3】

【図2】

【図4】

---

フロントページの続き

(72)発明者 倉知 克行

東京都港区芝浦三丁目9番1号 TDK株式会社内

(72)発明者 油川 祐基

東京都港区芝浦三丁目9番1号 TDK株式会社内

(72)発明者 田中 成明

東京都港区芝浦三丁目9番1号 TDK株式会社内

審査官 上谷 奈那

(56)参考文献 特開2004-152884(JP, A)

特開2011-108886(JP, A)

米国特許出願公開第2008/0145996(US, A1)

国際公開第2007/046173(WO, A1)

特開2013-172075(JP, A)

特開2005-191604(JP, A)

特開平11-220069(JP, A)

特開2010-258406(JP, A)

特開2006-210776(JP, A)

特開2009-038241(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01G 4/33

H01G 4/30