(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

30 August 2007 (30.08.2007)

PCT

(10) International Publication Number

WO 2007/097918 A1

## (51) International Patent Classification:

H04N 3/15 (2006.01)

AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

## (21) International Application Number:

PCT/US2007/003332

## (22) International Filing Date: 7 February 2007 (07.02.2007)

## (25) Filing Language: English

## (26) Publication Language: English

## (30) Priority Data:

11/354,444 15 February 2006 (15.02.2006) US

## (71) Applicant (for all designated States except US): EASTMAN KODAK COMPANY [US/US]; 343 State Street, Rochester, New York 14650-2201 (US).

## (72) Inventor; and

## (75) Inventor/Applicant (for US only): XU, Weize [CN/US]; 155 Crandon Way, Rochester, New York 14618 (US).

## (74) Common Representative: EASTMAN KODAK COMPANY; 343 State Street, Rochester, New York 14650-2201 (US).

## (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM,

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

## Published:

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

## (54) Title: A/D CONVERTER USING RAMPED TRANSFER GATE CLOCKS

(57) **Abstract:** An image sensor includes a photosensitive region that accumulates charge corresponding to received incident light; a transfer gate for transferring charge from the photosensitive region; a voltage supply having an increasing voltage over time; a floating diffusion for receiving the charge from the photosensitive region and converting the charge to a voltage; an amplifier for receiving and amplifying a signal from the floating diffusion; a comparator for comparing a voltage from the amplifier to a reference voltage; and a counter for counting clock cycles between initiation of the increasing voltage until a signal is received from the comparator indicating charge transfer from the photosensitive region to the floating diffusion; wherein a digital signal is generated that represents an unfilled capacity of the photosensitive region.

WO 2007/097918 A1

## **A/D CONVERTER USING RAMPED TRANSFER GATE CLOCKS**

### **FIELD OF THE INVENTION**

The invention relates generally to the field of image sensors, and

5 more particularly, to such CMOS image sensors in which the image signal is converted into a digital signal immediately after output from the pixel array.

### **BACKGROUND OF THE INVENTION**

Presently known CMOS image sensors all have the same or

10 substantially the same structures. They typically include the photosensitive devices, like a photodiode or photogate, in the pixel array to convert the optical signal to charge; a floating diffusion capacitor for converting the charge to a voltage; and a pixel amplifier buffering the floating diffusion capacitance from the large output bus capacitance and sending the electrical signal out of the pixel

15 array. The pixel output signals are stored by a sample/hold circuit array followed by an analog signal processing chain and an analog-to-digital converter.

The drawbacks for this present CMOS image sensor is the high noise, low speed and high power. These problems can be addressed by moving the analog-to-digital conversion to earlier stages and then processing the signal in the

20 digital domain. One such prior art for processing in digital domain in an earlier stage is disclosed in IEEE Journal of Solid-State Circuits, Vol. 36, No. 12, December 2001 (page 2049). This prior art includes a ramped voltage applied to a comparator independently of the pixel. This independence can cause pixel-to-pixel non-uniformities at the output.

25 Consequently, a need exists for addressing the high noise, low speed and high power of the image sensors having the latter stage analog-to-digital conversion circuits and the pixel-to-pixel non-uniformities of the image sensors having earlier stage analog-to-digital conversion circuits. This pixel-to-pixel non-uniformities is addressed in the present invention in which the transfer gate

adjacent the photodiode is ramped, and the reference voltage is from the pixel reset.

### **SUMMARY OF THE INVENTION**

The present invention is directed to overcoming one or more of the problems set forth above. Briefly summarized, according to one aspect of the present invention, the invention resides in an image sensor comprising (a) a photosensitive region that accumulates charge corresponding to received incident light; (b) a transfer gate for transferring charge from the photosensitive region; (c) a voltage supply having a ramped voltage over time; (d) a floating diffusion for receiving the charge from the photosensitive region and converting the charge to a voltage; (e) an amplifier for receiving and amplifying a signal from the floating diffusion; (f) a comparator for comparing a voltage from the amplifier to a reference voltage; and (g) a counter for counting clock cycles between initiation of the increasing voltage until a signal is received from the comparator indicating charge transfer from the photosensitive region to the floating diffusion.

The above and other objects of the present invention will become more apparent when taken in conjunction with the following description and drawings wherein identical reference numerals have been used, where possible, to designate identical elements that are common to the figures.

20

### **Advantageous Effect Of The Invention**

The present invention has the advantage of high-speed processing, lower power dissipation and low noise. It further eliminates the effects of non-linearity and threshold variations in the pixel amplifier.

25

### **BRIEF DESCRIPTION OF THE DRAWINGS**

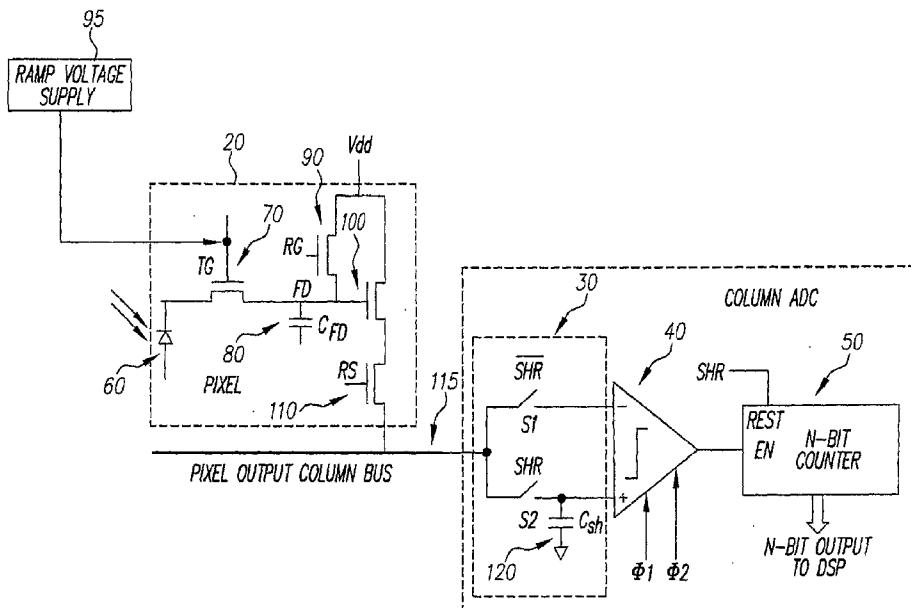

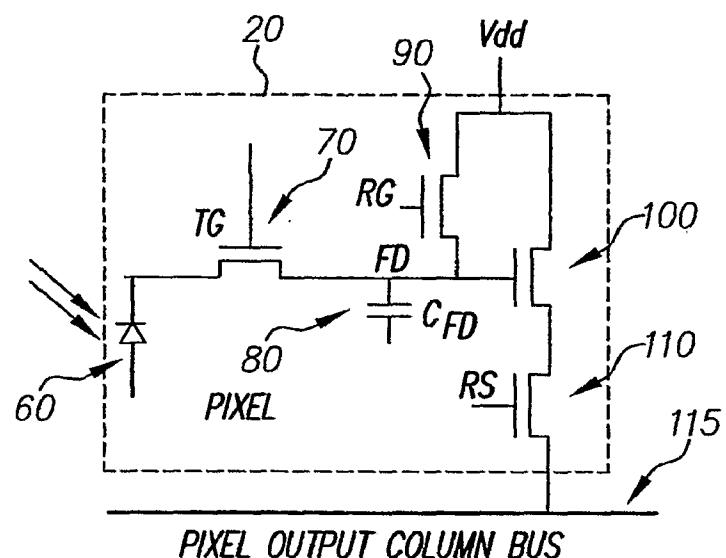

Fig. 1 is a block diagram of the image sensor of the present invention;

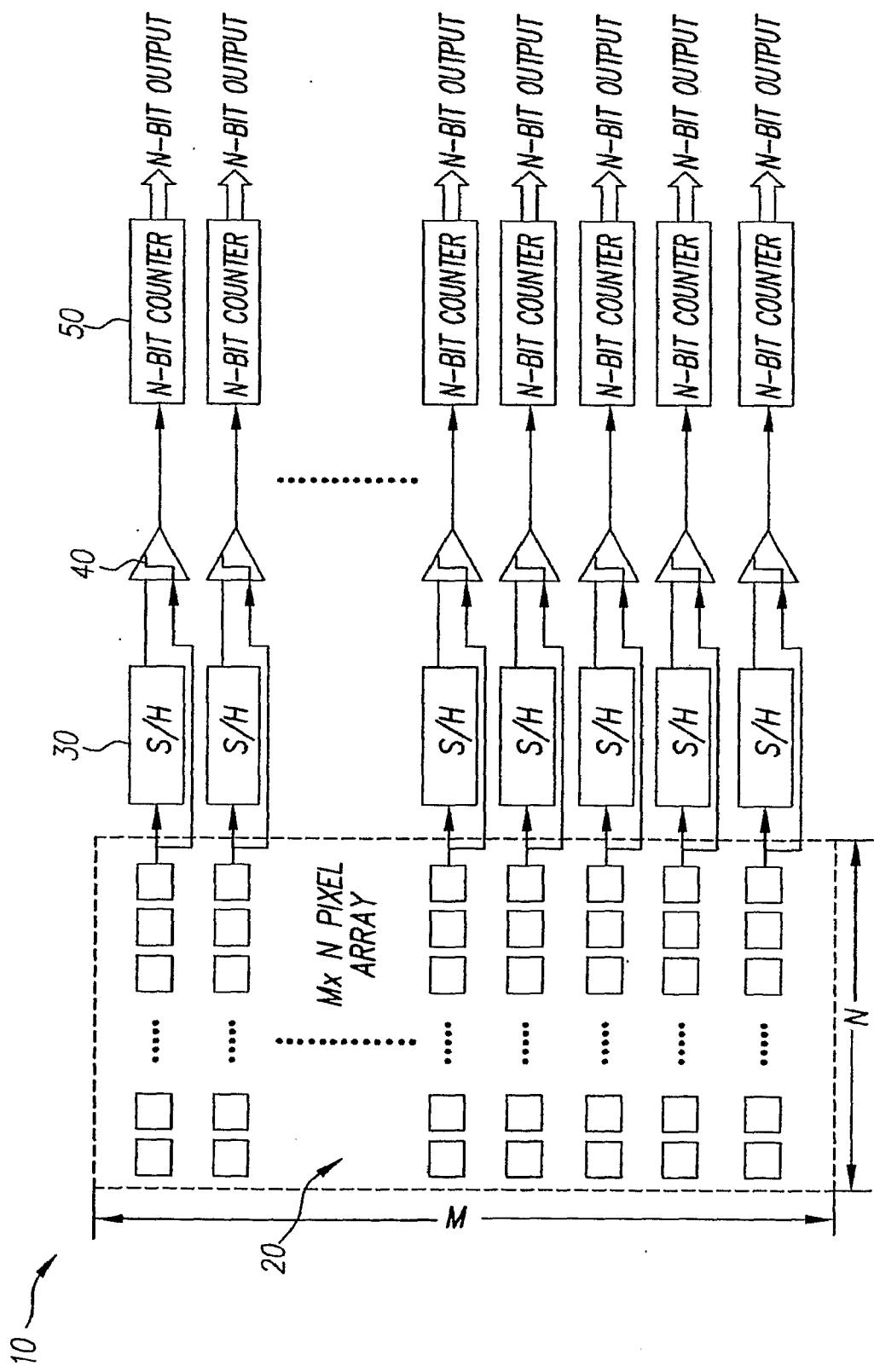

Fig. 2 is a schematic diagram of Fig. 1;

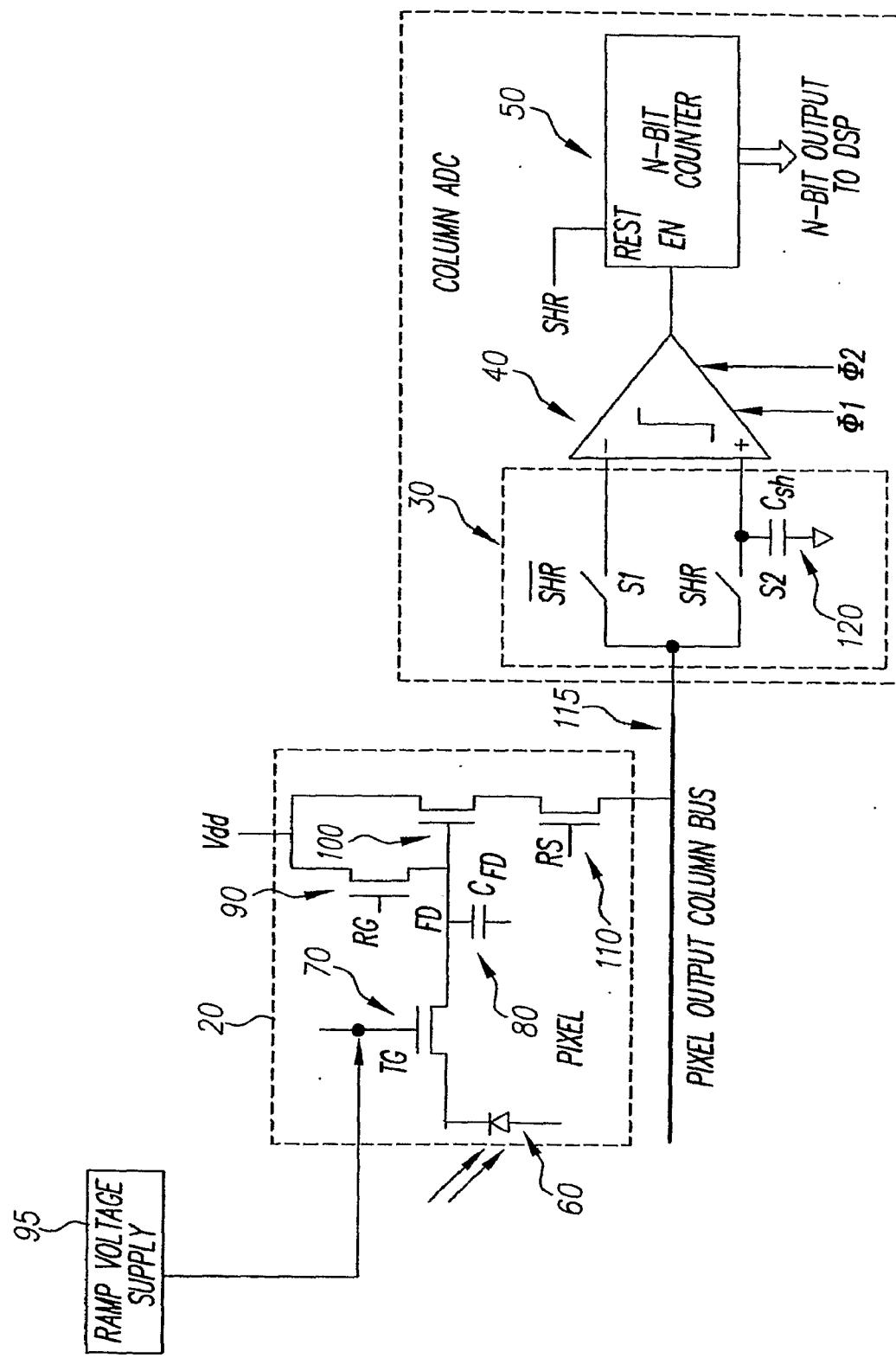

30 Fig. 3 is a timing diagram for Fig 2;

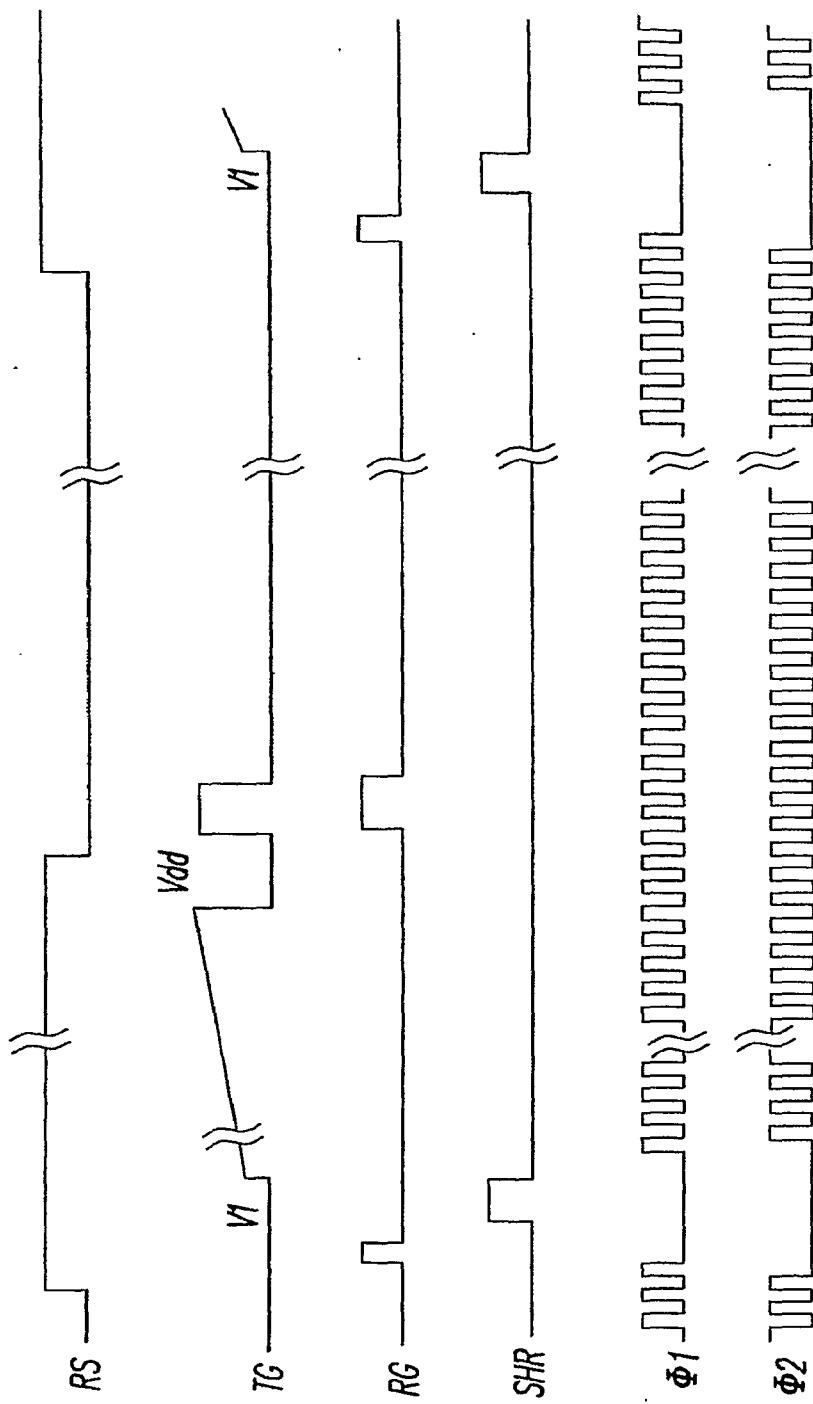

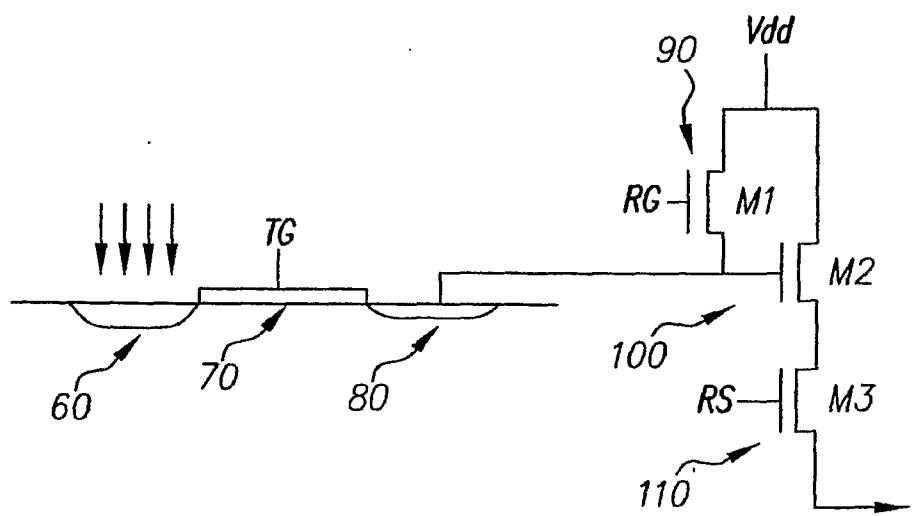

Fig. 4a illustrates the image sensor of the present invention in schematic form;

Fig. 4b illustrates a cross section of the present invention;

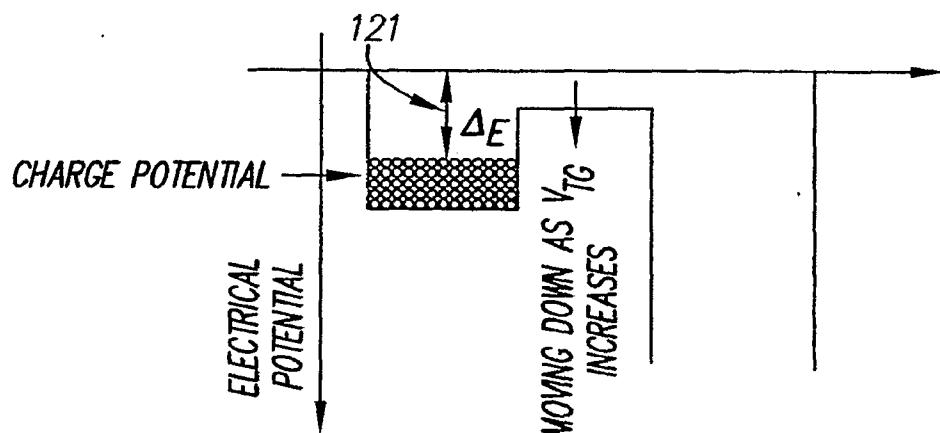

Fig. 4c illustrates a well potential diagram for Fig. 4b for clearly 5 illustrating the concept of the present invention; and

Fig. 5 is a digital camera of the present invention for illustrating a typical commercial embodiment for the image sensor of the present invention.

#### **DETAILED DESCRIPTION OF THE INVENTION**

10 Referring to Fig. 1, there is shown a image sensor 10 of the present invention having a plurality of pixels 20 and a plurality of sample and hold circuits 30 for receiving and storing the signals from the plurality of pixels 20 in a predetermined manner. A plurality of comparators 40 are respectively connected to the output of each sample and hold circuit 30, and a plurality of counters 50 are 15 respectively connected to the plurality of comparators 40.

For clarity of understanding, it is noted that the above-described apparatus of the present invention limits the analog circuit usage (for the purpose of noise reduction) and maximally utilizes the advantages of digital circuits. It is also noted that Fig. 2 illustrates only one pixel and its associated circuitry of the 20 present invention for illustrating a representative pixel of the plurality of pixels of the present invention for clarity of understanding. It is understood that the present invention includes a plurality of such pixels; for example, the pixel array 20 as shown in Fig. 1. Referring to Fig. 2, the pixel 20 is composed of a photosensitive region or photodiode 60 that accumulates charge in response to incident light. A 25 transfer gate 70 receives a ramped voltage over time (preferably an increasing voltage over time) from a voltage supply 95 which causes transfer of charge from the photodiode 60 to a charge-to-voltage conversion region or floating diffusion 80, which converts charge to a voltage signal. The increasing voltage is supplied by a voltage supply 95 which is preferably on-chip but outside the pixel array 20. 30 The voltage supply 95 may optionally be located off-chip in an alternative embodiment. A reset transistor 90 sets a reference voltage for both the floating

diffusion 80 and the sample and hold circuit 30, which (in the case of the sample and hold circuit 30) will be subsequently used by the comparator 40, as will be described in detail hereinbelow. An amplifier or amplifier transistor 100 receives and amplifies the signal from the floating diffusion 80. A row select transistor 110 5 selects the particular row of pixels for output to the sample and hold circuit 30.

Fig. 3 includes the preferred timing for Fig. 2 and includes common timing signal acronyms for the timing signal to be applied to a component referred to in Fig. 2 - RS, TG, RG and SHR. Referring now to Figs. 2 and 3, an image is captured by the plurality of photodiodes 60 during integration, and after 10 integration, a row of pixels in the pixel array is selected for readout by applying a “high” to the gate of row select transistor 110. A pulse voltage is then applied to the gate of the reset transistor 90 to clear charge from the floating diffusion (FD) capacitor 80 and to then reset the floating diffusion 80 to the reference voltage. The voltage at FD 80 is amplified by the amplifier 100 and sent out to the column 15 bus. With the reference signal at the output node 115, clock SHR goes from “low” to “high” to close switch S2 and open switch S1. The reference voltage is sampled onto the capacitor (Csh) 120. The SHR clock also resets the counter 50. Following the SHR pulse, a ramped or an increasing voltage over time is applied onto the transfer gate 70 to create a potential underneath the transfer gate 70 for 20 transferring the signal from the photodiode 60 to the floating diffusion 80. Then SHR changes from high to low, switch S1 closes and S2 opens which puts the comparator 40 in the comparing state, and the counter 50 starts counting clock cycles until the comparator 40 signals the counter 50 to terminate counting. The comparator 50 compares the pixel output voltage to the sampled reset voltage in 25 each column.

When the ramped TG voltage generates a sufficient potential underneath the TG gate 70, charge accumulated in photodiode 60 begins to flow from photodiode 60 to floating diffusion 80. It is noted that the present invention uses the floating diffusion 80 to sense the “beginning” or “initiation” of charge 30 transfer from the photodiode 60, as opposed to sensing the “entire” charge on the photodiode as in the prior art. Returning to the present invention discussion, a

voltage change is created at the floating diffusion 80 upon initiation of charge transfer, and the voltage change is sent out through the pixel amplifier 100 to the column comparator 40. This voltage change triggers the comparator 40 to change output states. The "enable" input of the counter 50 senses the change in output 5 from the comparator 40 and then stops counting. The content of the column counter 50 is the raw pixel digital output.

A digital calibration function is included in the A/D conversion operation by sampling incident light in darkness which is stored in memory (on or off-chip). This calibration signal will be subtracted from the digital signal 10 representing the captured image. The pixel noise and pixel amplifier offset are removed or greatly reduced.

Referring to Figs. 4a-4c, it is noted for clarity that the prior art detects the number of electrons. In contrast, the image sensor of the present invention detects the electrical charge potential of the photodiode, or in other 15 words, it detects the depth of the unfilled potential well of the photodiode. With the presence of the light on the photodiode 60 in the pixel array 20, electrical charges are generated and accumulated in an electrical potential well 121 in the photodiode 60. There is a transfer gate 70 in the pixel in between the photodiode 60 and a floating diffusion 80, which floating diffusion 80 is used to convert the 20 charge to voltage. The voltage applied on the gate of the transfer gate 70 controls the potential underneath the gate and creates a conductive channel when the voltage is higher the threshold voltage of the transfer gate 70. The potential well 121 of the photodiode 60 and the floating diffusion area 80 are connected by this created channel of the transfer gate 70. With the increase of this gate voltage, the 25 electrical potential underneath the gate is lowered. When the potential underneath the transfer gate 70 is equal to the electrical potential of the well 121 of the photodiode 60, charge accumulated in the photodiode 60 starts to move from photodiode 60 to the diffusion area 80 through the transfer gate 70. The move of charge from photodiode 60 to the floating diffusion 80 will generate a voltage 30 signal at the floating diffusion area 80 which is then sent to the input of the pixel amplifier 100. The circuit in the column sample-and-hold array 30 compares the

voltage signal at the pixel amplifier output 115 to a previously generated reference voltage when the transfer gate voltage is applied. The move of the electrons from photodiode 60 to the floating diffusion 80 will trigger the comparator 40 in the sample-and-hold circuit 30 to change its output state. This change of comparator 5 40 output state stops the counter 50 and a digital code is generated at the counter 50 output. This digital code or the digital signal represents the image signal created by the pixel.

Referring to Fig. 5, there is shown a digital camera 125 in which the image sensor 10 of the present invention is disposed for illustrating a preferred 10 commercial embodiment of the present invention.

**PARTS LIST**

- 10 image sensor

- 20 plurality of pixels

- 5 30 sample and hold circuits

- 40 comparators

- 50 counters

- 60 photodiode

- 70 transfer gate

- 10 80 floating diffusion

- 90 reset transistor

- 95 voltage supply

- 100 amplifier transistor

- 110 row select transistor

- 15 115 output node or pixel amplifier output

- 120 capacitor (Csh)

- 121 electrical potential well

- 125 digital camera

**CLAIMS:**

1. An image sensor comprising:

- (a) a photosensitive region that accumulates charge corresponding to received incident light;

- (b) a transfer gate for transferring all or a portion of the charge from the photosensitive region;

- (c) a voltage supply having a ramped voltage over time that is applied to the transfer gate;

- (d) a floating diffusion for receiving all or a portion of the charge from the photosensitive region and converting the charge to a voltage;

- (e) an amplifier for receiving and amplifying a signal from the floating diffusion;

- (f) a comparator for comparing a voltage from the amplifier to a reference voltage; and

- (g) a counter for counting clock cycles between initiation of the increasing voltage until a signal is received from the comparator which indicates initiation of charge transfer from the photosensitive region to the floating diffusion.

- 20 2. The image sensor as in claim 1, wherein the ramped voltage is an increasing voltage over time.

- 25 3. The image sensor as in claim 1 further comprising a reset transistor for generating the reference voltage.

4. The image sensor as in claim 1 further comprising a capacitor electrically connected to the comparator for holding the reference voltage.

- 30 5. The image sensor as in claim 1, wherein the photosensitive region is a photodiode.

6. The image sensor as in claim 1 further comprising a row select transistor electrically connected to the amplifier for enabling readout.

7. An imaging device comprising:

- 5 (a) a photosensitive region that accumulates charge corresponding to received incident light;

- (b) a transfer gate for transferring all or a portion of the charge from the photosensitive region;

- (c) a voltage supply having a ramped voltage over time that is applied to the transfer gate;

- (d) a floating diffusion for receiving all or a portion of the charge from the photosensitive region and converting the charge to a voltage;

- (e) an amplifier for receiving and amplifying a signal from the floating diffusion;

- 15 (f) a comparator for comparing a voltage from the amplifier to a reference voltage; and

- (g) a counter for counting clock cycles between initiation of the increasing voltage until a signal is received from the comparator which indicates initiation of charge transfer from the photosensitive region to the floating diffusion.

20

8. The imaging device as in claim 7, wherein the ramped voltage is an increasing voltage over time.

25

9. The imaging device as in claim 7 further comprising a reset

transistor for generating the reference voltage.

10. The imaging device as in claim 7 further comprising a capacitor electrically connected to the comparator for holding the reference voltage.

30

11. The imaging device as in claim 7, wherein the photosensitive region is a photodiode.

12. The imaging device as in claim 7 further comprising a row select transistor electrically connected to the amplifier for enabling readout.

5 13. An image sensor comprising:

- (a) a photosensitive region having a capacity in which charge accumulates that corresponds to received incident light;

- (b) a transfer gate for transferring all or a portion of the charge from the photosensitive region;

- 10 (c) a voltage supply having a ramped voltage over time that is applied to the transfer gate;

- (d) a charge collection portion for receiving all or a portion of the charge from the photosensitive region and converting the charge to a voltage; and

- (e) a circuit which indicates initiation of charge transfer from the

15 photosensitive region to the charge collection portion.

14. The image sensor as in claim 13, wherein the ramped voltage is an increasing voltage over time.

20 15. The image sensor as in claim 13, wherein the charge collection region is a floating diffusion.

16. The image sensor as in claim 13, wherein the photosensitive region is a photodiode.

25 17. The image sensor as in claim 16, wherein the charge collection region is a floating diffusion.

18. An imaging device comprising:

30 (a) a photosensitive region having a capacity in which charge accumulates which corresponds to received incident light;

(b) a transfer gate for transferring all or a portion of the charge from the photosensitive region;

(c) a voltage supply having a ramped voltage over time that is applied to the transfer gate;

5 (d) a charge collection portion for receiving all or a portion of the charge from the photosensitive region and converting the charge to a voltage; and

(e) a circuit which indicates initiation of charge transfer from the photosensitive region to the charge collection portion.

10 19. The imaging device as in claim 18, wherein the ramped voltage is an increasing voltage over time.

15 20. The imaging device as in claim 18, wherein the charge collection region is a floating diffusion.

20 21. The imaging device as in claim 18, wherein the photosensitive region is a photodiode.

25 22. The imaging device as in claim 21, wherein the charge collection region is a floating diffusion.

23. A method of operating an image sensor, the method comprising the steps of:

25 (a) accumulating charge corresponding to received incident light by a photosensitive region having a capacity;

(b) transferring all or a portion of the charge from the photosensitive region by a transfer gate;

(c) applying a ramped voltage over time to the transfer gate;

(d) receiving all or a portion of the charge from the photosensitive 30 region and converting the charge to a voltage by a charge collection portion; and

(e) indicating initiation of charge transfer from the photosensitive region to the charge collection portion.

24. The method as in claim 23 further comprising the step of

5 providing an increasing voltage over time as the ramped voltage.

25. The method as in claim 23 further comprising the step of

providing the charge collection region as a floating diffusion.

10 26. The method as in claim 23 further comprising the step of

providing the photosensitive region as a photodiode.

27. The method as in claim 26 further comprising the step of

providing the charge collection region as a floating diffusion.

15

1/5

FIG. 1

2/5

FIG. 2

3/5

FIG. 3

4/5

FIG. 4a

FIG. 4b

5/5

FIG. 4C

FIG. 5

# INTERNATIONAL SEARCH REPORT

International application No

PCT/US2007/003332

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H04N3/15

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H04N

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                    | Relevant to claim No. |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2005/083421 A1 (BEREZIN VLADIMIR [US] ET AL) 21 April 2005 (2005-04-21)<br>paragraphs [0028], [0031]; figure 5                                                     | 13-27                 |

| A         | WO 2005/120046 A (COUNCIL CENT LAB RES COUNCILS [GB]; CROOKS JAMIE [GB]; TOWRIE MIKE [GB] 15 December 2005 (2005-12-15)<br>page 2, line 26 - page 3, line 8; figure 2 | 1,7                   |

| A         | US 2003/058360 A1 (LIU XINQIAO [US] ET AL) 27 March 2003 (2003-03-27)<br>paragraph [0091]; figures 1,4                                                                | 1,7                   |

| A         | US 2002/067417 A1 (TAN CHARLES M C [US] ET AL) 6 June 2002 (2002-06-06)<br>paragraph [0024]; figures 1,2                                                              | 1,7                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

Date of the actual completion of the international search

22 June 2007

Date of mailing of the international search report

04/07/2007

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Bequet, Thierry

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2007/003332

| Patent document cited in search report | Publication date | Patent family member(s) |               | Publication date |

|----------------------------------------|------------------|-------------------------|---------------|------------------|

| US 2005083421                          | A1               | 21-04-2005              | NONE          |                  |

| WO 2005120046                          | A                | 15-12-2005              | EP 1762088 A2 | 14-03-2007       |

| US 2003058360                          | A1               | 27-03-2003              | NONE          |                  |

| US 2002067417                          | A1               | 06-06-2002              | NONE          |                  |