(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-147477

(P2010-147477A)

(43) 公開日 平成22年7月1日(2010.7.1)

(51) Int.Cl.

F 1

テーマコード (参考)

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 652H |

| HO1L 29/739 | (2006.01) | HO1L 29/78 | 653A |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 655B |

| HO1L 29/06  | (2006.01) | HO1L 29/78 | 658G |

|             |           | HO1L 29/78 | 658F |

審査請求 未請求 請求項の数 26 O L (全 13 頁) 最終頁に続く

(21) 出願番号 特願2009-286443 (P2009-286443)

(22) 出願日 平成21年12月17日 (2009.12.17)

(31) 優先権主張番号 12/317,297

(32) 優先日 平成20年12月20日 (2008.12.20)

(33) 優先権主張国 米国(US)

(71) 出願人 501315784

パワー・インテグレーションズ・インコーポレーテッド

アメリカ合衆国・95138・カリフォルニア州・サンホゼ・ヘリヤー・アベニュー

5245

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

最終頁に続く

(54) 【発明の名称】シリコンウェハ上にパワートランジスタデバイスを製造する方法

(57) 【要約】 (修正有)

【課題】パワー半導体デバイス構造と、高電圧トランジスタを製造するためのプロセスを提供する。

【解決手段】エピタキシャル層13はバッファ層11に分離され、バッファ層11まで垂直方向に一定であるドーピング濃度を有する。間隔を空けて配置された1対のトレンチは、エピタキシャル層13において、当該エピタキシャル層13の上面から下方の少なくともバッファ層12にまで形成される。誘電材料が、トレンチにおいて第1および第2の側壁部分の上に形成される。ソース/コレクタおよびボディ領域14はエピタキシャル層13の上部に形成される。ボディ領域14は、ボディ領域14からバッファ層12にまで延在するエピタキシャル層13のドリフト領域から柱のソース/コレクタ領域を分離している。ボディ領域14に隣接し、ボディ領域14から絶縁されたトレンチの各々において絶縁ゲート部材17が形成される。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

パワートランジスタデバイスを製造する方法であって、

第1の導電型のバッファ層を、前記第1の導電型とは逆の第2の導電型の基板上に形成するステップを含み、前記バッファ層は、上面、第1の厚さおよび第1のドーピング濃度を有し、前記方法はさらに、

前記バッファ層の上に前記第1の導電型のエピタキシャル層を形成するステップを含み、前記エピタキシャル層は、上面、および、前記第1の厚さよりも厚い第2の厚さを有し、前記方法はさらに、

前記エピタキシャル層において、前記エピタキシャル層を含む柱を規定する、間隔を空けて配置された1対のトレンチを形成するステップを含み、前記柱は、第1および第2の側壁部分ならびに第1の横方向の幅を有し、前記トレンチは、前記エピタキシャル層の上面から下方に垂直方向に延在して、前記バッファ層の上面を越えて延在する底部にまで達し、前記トレンチは第2の横方向の幅を有し、前記方法はさらに、

前記第1および第2の側壁部分の各々を、少なくともボディ領域の下から下方向の前記底部まで覆う誘電材料を前記トレンチに形成するステップと、

第2の導電型のボディ領域を前記柱に形成するステップと、

第1の導電型の第1の領域を前記柱に形成するステップとを含み、前記第1の領域は、前記第1の導電型であり、前記上面に配置され、前記ボディ領域は、前記ボディ領域から前記バッファ層にまで延在するドリフト領域から前記柱の前記第1の領域を分離しており、前記方法はさらに、

前記上面において、または、前記上面付近において前記トレンチの各々にゲート部材を形成するステップを含み、前記ゲート部材は前記ボディ領域に隣接して配置され、前記ボディ領域から絶縁されている、方法。

## 【請求項 2】

前記基板はエミッタを含み、前記第1の領域はバイポーラトランジスタのコレクタを含み、前記第1の領域はまたソースを含み、前記ドリフト領域は、電界効果トランジスタの拡張ドレイン領域を含み、前記ゲート部材に電位を印加することにより、前記パワートランジスタデバイスがオン状態であるときに前記エミッタと前記コレクタとの間において入力される順方向導通を制御する、請求項1に記載の方法。

## 【請求項 3】

前記エピタキシャル層の第2の厚さが前記バッファ層の第1の厚さよりも約3～5倍厚い、請求項1に記載の方法。

## 【請求項 4】

前記第1の横方向の幅は前記第2の横方向の幅と実質的に等しい、請求項1に記載の方法。

## 【請求項 5】

前記エピタキシャル層は、前記上面から実質的に垂直方向に一定である第2のドーピング濃度を有し、前記第2のドーピング濃度は実質的に前記第1のドーピング濃度未満である、請求項1に記載の方法。

## 【請求項 6】

前記第1の導電型はn型であり、前記第2の導電型はp型である、請求項1に記載の方法。

## 【請求項 7】

前記誘電材料は酸化物を含む、請求項1に記載の方法。

## 【請求項 8】

前記トレンチの底部は、垂直方向に延在して前記基板にまで達する、請求項1に記載の方法。

## 【請求項 9】

前記第1のドーピング濃度は、前記パワートランジスタデバイスがオフ状態であるとき

10

20

30

40

50

に前記基板へのパンチスルーを防ぐように、第2のドーピング濃度と比べて十分に高く、前記基板は、前記第1の領域に対して少なくとも600Vの電位である、請求項5に記載の方法。

【請求項10】

パワートランジスタデバイスを製造する方法であって、

第1の導電型の半導体材料を、前記第1の導電型とは逆の第2の導電型の基板上に形成するステップを含み、前記半導体材料は、エピタキシャル層およびバッファ層を含み、前記バッファ層は、前記エピタキシャル層を前記基板から分離し、前記エピタキシャル層は、上面および第1の厚さを有し、前記方法はさらに、

前記エピタキシャル層において、前記半導体材料からなる柱を規定する、間隔を空けて配置された1対のトレンチを形成するステップを含み、前記柱は、第1および第2の側壁部分ならびに第1の横方向の幅を有し、前記トレンチは、前記エピタキシャル層の上面から下方に垂直方向に延在して少なくとも前記バッファ層にまで達し、前記トレンチは第2の横方向の幅を有し、前記方法はさらに、

前記第1および第2の側壁部分の各々を覆う誘電材料を前記トレンチに形成するステップと、

前記第2の導電型のボディ領域を前記柱に形成するステップと、

前記第1の導電型の第1の領域を前記柱に形成するステップとを含み、前記第1の領域は、前記第1の導電型であり、前記上面に配置され、前記ボディ領域は、前記ボディ領域から前記バッファ層にまで延在する前記エピタキシャル層のドリフト領域から前記柱の前記第1の領域を分離しており、前記方法はさらに、

前記上面において、または、前記上面付近において前記トレンチの各々にゲート部材を形成するステップを含み、前記ゲート部材は、前記ボディ領域に隣接して配置され、前記ボディ領域から絶縁されている、方法。

【請求項11】

前記エピタキシャル層は、前記バッファ層まで下方に垂直方向に実質的に一定である第1のドーピング濃度を有し、前記バッファ層は、前記エピタキシャル層の第1のドーピング濃度よりも少なくとも1桁大きい第2のドーピング濃度を有する、請求項10に記載の方法。

【請求項12】

前記ゲート部材を形成するステップは、

マスキング層において、第1および第2のトレンチ上にそれぞれ配置された第1および第2の開口部を形成するステップを含み、前記マスキング層は、前記柱を覆う部分を前記第1の開口部と前記第2の開口部との間に備え、前記部分は、前記柱の上面と重なる前記第1および第2の側壁部分の各端縁を越えた距離だけ重なっており、前記ゲート部材を形成するステップはさらに、

前記第1および第2の開口部をそれぞれ通る前記トレンチにおいて前記誘電材料を異方的にエッチングして、第1および第2のゲートトレンチを作成するステップと、

前記第1および第2のゲートトレンチにおける第1および第2の誘電体領域を等方的にエッチングして、前記第1および第2の側壁部分の各々のうち、前記上面から前記ボディ領域の底部まで延在する区域から誘電材料を除去するステップとを含む、請求項10に記載の方法。

【請求項13】

前記区域上にわたってゲート酸化物を形成するステップと、

前記第1および第2のトレンチの各々において前記ゲート部材を形成するステップとを含み、前記ゲート部材は、前記ゲート酸化物によって前記区域から絶縁されている、請求項12に記載の方法。

【請求項14】

前記誘電材料だけが、前記ドリフト領域に隣接したトレンチに存在している、請求項10に記載の方法。

10

20

30

40

50

**【請求項 15】**

前記誘電材料は酸化物を含む、請求項 12 に記載の方法。

**【請求項 16】**

前記エピタキシャル層の第1の厚さは、前記バッファ層の第2の厚さよりも約3～5倍厚い、請求項 10 に記載の方法。

**【請求項 17】**

前記第1の横方向の幅は、前記第2の横方向の幅と実質的に等しい、請求項 10 に記載の方法。

**【請求項 18】**

前記第1および第2の横方向の幅は各々、約2 μm である、請求項 17 に記載の方法。 10

**【請求項 19】**

前記第1の導電型はn型であり、前記第2の導電型はp型である、請求項 10 に記載の方法。

**【請求項 20】**

前記トレンチは垂直方向に延在して前記基板にまで達する、請求項 10 に記載の方法。

**【請求項 21】**

少なくとも4ミルの厚さを有するシリコンウェハ上にパワートランジスタデバイスを製造する方法であって、

前記シリコンウェハの基板上にバッファ層を形成するステップを含み、前記バッファ層は、第1の厚さを有し、第1の導電型であり、前記基板は前記第1の導電型とは逆の第2の導電型であり、前記方法はさらに、 20

前記バッファ層上に前記第1の導電型のエピタキシャル層を形成するステップを含み、前記エピタキシャル層は、前記第1の厚さよりも少なくとも3倍厚い第2の厚さを有し、前記エピタキシャル層は、全体にわたって実質的に一定のドーピング濃度を有し、前記バッファ層は、前記エピタキシャル層の実質的に一定のドーピング濃度よりも少なくとも1桁大きいドーピング濃度を有し、前記方法はさらに、

トレンチを前記シリコンウェハに垂直方向にエッチングするステップを含み、前記トレンチは、前記エピタキシャル層の上面から下方に延在して少なくとも前記バッファ層にまで達し、前記トレンチは複数の柱を規定し、各々の柱は、第1および第2の側壁ならびに第1の横方向の幅を有し、前記第2の厚さと前記第1の横方向の幅との比は少なくとも10：1 であり、各々の縦型トレンチは第2の横方向の幅を有し、前記方法はさらに、 30

前記トレンチを、前記第1および第2の側壁を覆う誘電材料で充填するステップと、

前記柱において前記第2の導電型のボディ領域を形成するステップとを含み、前記ボディ領域は、前記第1の側壁と前記第2の側壁との間ににおいて前記柱の第1の横方向の幅にわたって延在し、前記ボディ領域は前記バッファ層から前記ボディ領域を分離するドリフト領域を規定し、前記方法はさらに、

前記柱において前記第1の導電型の第1の領域を形成するステップを含み、前記ボディ領域は前記ドリフト領域から前記第1の領域を分離し、前記方法はさらに、

前記トレンチにおける前記誘電材料をエッチングして、ゲートトレンチを形成するステップと、 40

前記ゲートトレンチの各々において絶縁ゲート部材を形成するステップとを含み、前記絶縁ゲート部材は、前記ボディ領域に隣接して配置され、前記ボディ領域から絶縁される、方法。

**【請求項 22】**

前記第1の領域はソースを含み、前記絶縁ゲート部材はゲートを含み、前記ドリフト領域は、前記パワートランジスタデバイスの電界効果トランジスタの拡張ドレイン領域を含み、前記第1の領域はまた、前記パワートランジスタデバイスのバイポーラトランジスタのコレクタを含み、前記基板は、前記パワートランジスタデバイスのバイポーラトランジスタのエミッタを含む、請求項 21 に記載の方法。

**【請求項 23】**

前記トレンチは垂直方向に延在して前記基板にまで達する、請求項 2 1 に記載の方法。

【請求項 2 4】

前記第 2 の横方向の幅は約  $2 \mu m$  である、請求項 2 1 に記載の方法。

【請求項 2 5】

前記第 1 の横方向の幅は約  $2 \mu m$  である、請求項 2 1 に記載の方法。

【請求項 2 6】

前記誘電材料だけが、前記ドリフト領域に隣接したトレンチに存在している、請求項 2 1 に記載の方法。

【発明の詳細な説明】

【技術分野】

10

【0 0 0 1】

この開示は、パワー半導体デバイス構造、および高電圧トランジスタを製造するためのプロセスに関する。

【背景技術】

【0 0 0 2】

背景

20

高電圧の電界効果トランジスタ (H V F E T) および他のさまざまな高電圧パワー半導体デバイスは、半導体技術において周知である。多くの H V F E T が採用しているデバイス構造は、当該デバイスが「オフ」状態であるときに印加された高電圧（たとえば、数百ボルト）をサポートまたは阻止する低ドープ拡張ドレイン領域を備える。高抵抗エピタキシャル層があるために、高電圧（たとえば  $500 \sim 700 V$  以上）で動作する通常の M O S F E T パワーデバイスが有する「オン」状態のドレイン・ソース抵抗 ( $R_{DS(on)}$ ) は、典型的には、特に高ドレイン電流では大きくなる。たとえば、従来のパワー M O S F E T においては、典型的には、トランジスタが有するオン状態抵抗全体のうち 95 % が、ドリフトゾーンとも称される低ドープの拡張ドレイン領域によって引起される。

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 3】

30

導通損失の問題に取組むために、さまざまな代替的設計構造が提案してきた。たとえば、縦型の薄いシリコン (V T S) M O S F E T の場合、導通損失を低下させるには、近接する厚い酸化物に埋込まれたフィールドプレートによって空乏化される薄いシリコン層において、傾斜したドーピングプロファイルが用いられる。しかしながら、V T S 構造についての問題として、比較的大きな出力容量 (C o s s) がある。これは、（ソース端子に結合された）大きなフィールドプレートが（ドレイン端子に結合された）シリコン柱に重なることによってもたらされるものである。この比較的大きな出力容量により、デバイスの高周波スイッチング性能が制限されてしまう。従来の V T S M O S F E T 構造についての別の欠点は、ドリフト領域を垂直方向に通る直線的に傾斜したドーピングプロファイルが必要とされる点であり、これは、大抵の場合、制御するのが困難で、製造に費用がかかってしまう。

【0 0 0 4】

40

C o o l M O S <sup>TM</sup> 概念として公知である別の方策の場合、導通損失は N - および P - 表面電界緩和 (R E S U R F (reduced surface field)) 層を交互にすることによって低減される。C o o l M O S <sup>TM</sup> デバイスにおいては、電気伝導性は多数キャリアによってのみもたらされる。すなわち、バイポーラの電流（少数キャリア）は寄与しない。C o o l M O S <sup>TM</sup> の高電圧パワー M O S F E T 設計が大型のトレンチフィールドプレート構造を有していないために、比較的低い C o s s からも利点が得られる。それにもかかわらず、いくつかの応用例においては、C o o l M O S <sup>TM</sup> 設計では、依然として容認できないほど高い導電性損失をこうむる。

【0 0 0 5】

絶縁ゲートバイポーラトランジスタまたは I G B T は、少数キャリアパワー半導体デバ

50

イスであり、単一のデバイス構造においてバイポーラパワースイッチングトランジスタと組合されて IGBT 制御入力により比較的低い導通損失を達成する。しかしながら、IGBT 設計の主要な欠点は、エピタキシャルドリフト領域に少数キャリアが蓄積することによって起こる特徴的な「テール電流」のせいで、スイッチング周波数が典型的には 60 KHz 以下に制限されることである。言い方を換えれば、より高い周波数 (100 KHz 以上) で不十分なスイッチング性能によって引起されるスイッチング損失は解決されないままである。IGBT 設計のスイッチング速度の向上を目指した試みには、極薄のウェハ (~75 μm 以下) の非パンチスルーフ構造の使用が含まれる。しかし、極薄ウェハの処理には大幅なコストの追加が伴い、製造処理がさらに複雑になる。

【課題を解決するための手段】

10

【0006】

この開示は、以下の詳細な説明および添付の図面からより十分に理解されるであろうが、本発明を図示される具体的な実施例に限定するものではなく、説明および理解だけを目的としたものとみなされるべきである。

【図面の簡単な説明】

【0007】

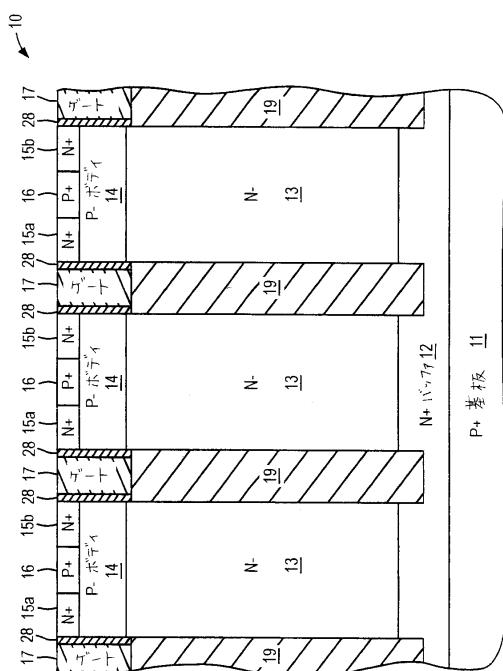

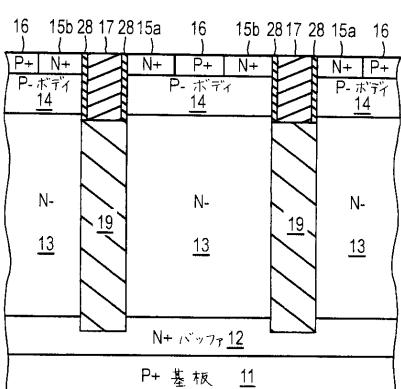

【図 1】深いトレンチ絶縁ゲートバイポーラトランジスタ (IGBT) 構造を示す例示的な側断面図である。

20

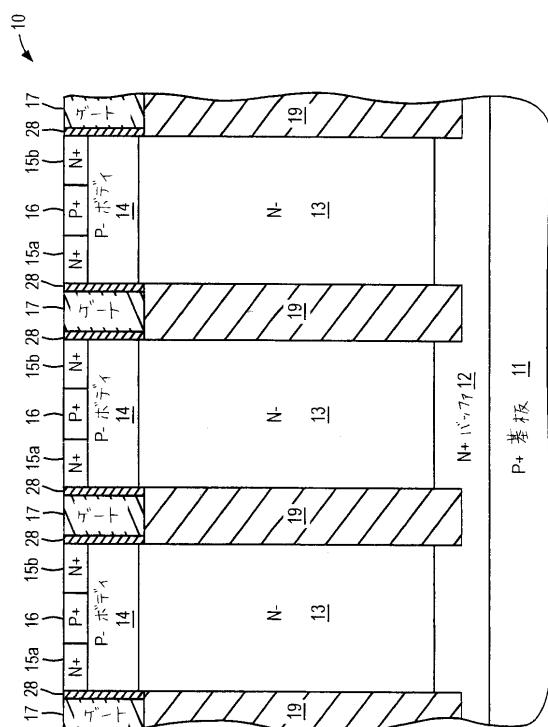

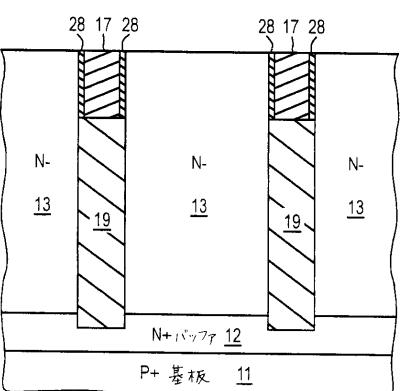

【図 2】別の深いトレンチ絶縁ゲートバイポーラトランジスタ (IGBT) 構造を示す例示的な側断面図である。

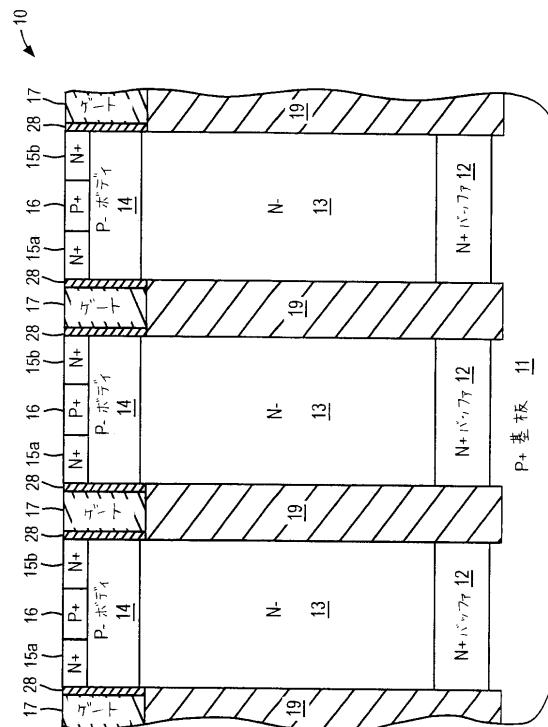

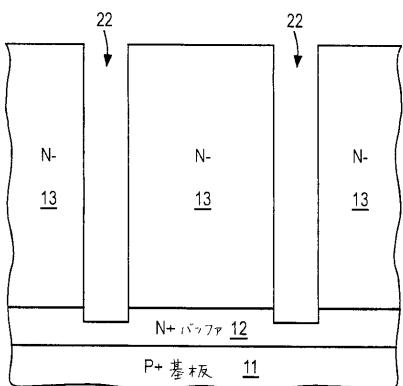

【図 3 A】P+ 基板上に N- ドープエピタキシャル層を形成する最初の工程後の製造プロセスにおける深いトレンチ IGBT 構造を示す例示的な側断面図である。

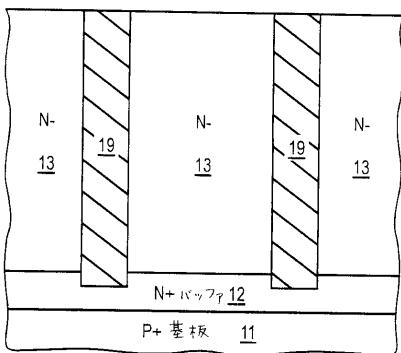

【図 3 B】縦型の深いトレンチエッチング後における図 3 A の例示的なデバイス構造を示す図である。

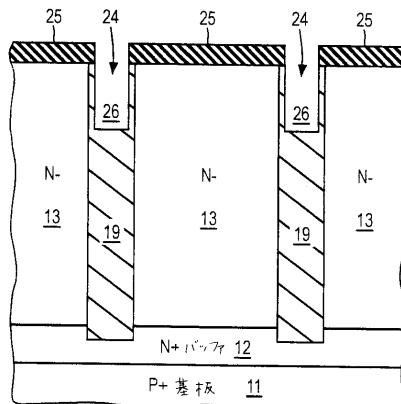

【図 3 C】深い縦型トレンチを充填する誘電体領域の形成後における図 3 B の例示的なデバイス構造を示す図である。

【図 3 D】シリコン基板の上面をマスキングし、次いで第 1 の誘電体エッチングを行った後における図 3 C の例示的なデバイス構造を示す図である。

30

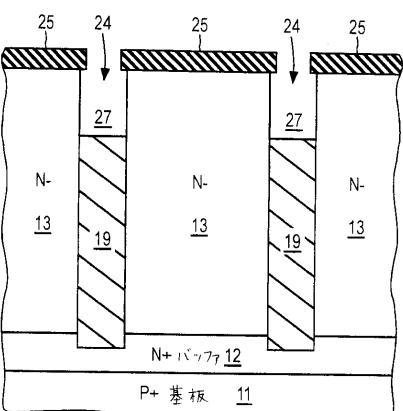

【図 3 E】ゲートトレンチを形成する第 2 の誘電体エッチング後における図 3 D の例示的なデバイス構造を示す図である。

【図 3 F】ゲートトレンチにおけるトレンチゲート構造の形成後における図 3 E の例示的なデバイス構造を示す図である。

【図 3 G】ソース (コレクタ) およびボディ領域の形成後における図 3 F の例示的なデバイス構造を示す図である。

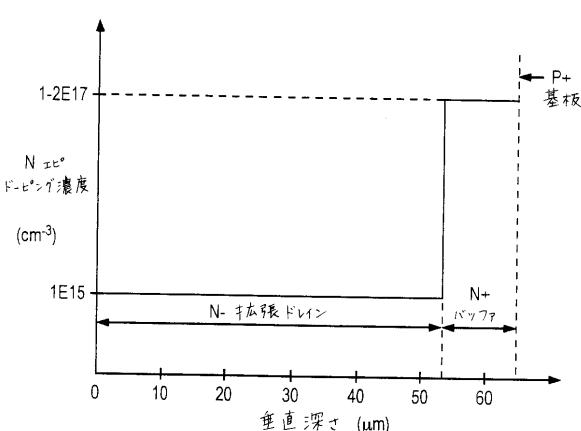

【図 4】図 1 に示されるような例示的な深いトレンチ IGBT デバイス構造のためのエピタキシャル層ドーピングプロファイル対正規化距離についてのプロットを示す図である。

【発明を実施するための形態】

【0008】

詳細な説明

以下の説明においては、この発明の完全な理解を助けるために、材料の種類、寸法、構造特徴、処理工程などの具体的な詳細を述べる。しかしながら、当業者であれば、これらの具体的な詳細がなくてもこの発明が実施可能であることを認識するだろう。図中の要素が具象的なものであり、明瞭にするために縮尺通りには描かれていないことも理解されるはずである。

40

【0009】

図 1 は、深いトレンチ IGBT 10 の例示的な側断面図を示しており、深いトレンチ IGBT 10 は、P+ ドープシリコン基板 11 の上方に形成された N 型シリコンの、分離された複数の拡張ドレイン領域 13 を含む構造を有する。図 1 の例においては、拡張ドレイン領域 13 は、高濃度ドープ N+ バッファ層 12 によって P+ 基板 11 から分離される。一実施例においては、拡張ドレイン領域 13 は、N+ バッファ層 12 からシリコンウ

50

エハの上面まで延在するエピタキシャル層の一部をなす。基板 11 を高濃度にドープすることにより、完成したデバイスにおいて基板 11 の底に位置するドレイン電極にまで流れる電流に対する抵抗が最小限にされる。

【0010】

深いトレンチ IGBT 10 はまた P - ボディ領域 14 を含む。各々の P - ボディ領域 14 の上方にあるウェハのエピタキシャル層の上面において、一対の N + ドープソース領域 15a および 15b が P 型領域 16 によって横方向に分離される。図から分かるように、各 P - ボディ領域 14 は、拡張ドレイン領域 13 のうち対応する領域の真上に配置されており、当該対応する領域を N + ソース領域 15a および 15b ならびに P 型領域 16 から垂直に分離している。図 1 のデバイス構造はさらに、(たとえば、ポリシリコンで構成される) ゲート 17 を有するトレンチゲート構造と、ゲート 17 を、隣接する側壁 P - ボディ領域 14 から絶縁するゲート絶縁層 28 とを含む。ゲート絶縁層 28 は熱成長した二酸化珪素または別の適切な誘電絶縁材料を含んでいてもよい。製造完了したデバイスにおいては、ゲート 17 に適切な電位を印加することにより、P - ボディ領域 14 の垂直な側壁部分に沿って導電性チャネルが形成される。このため、電流が半導体材料を通って垂直に流れ得る。すなわち、P + 基板 11 から上昇してバッファ層 12 および拡張ドレイン領域 13 を通り、垂直に形成された導電性チャネルを通って、ソース領域 15 が配置されているシリコンウェハの上面まで流れ得る。

10

【0011】

別の実施例においては、(図 1 に図示のとおり) 半導体柱の横方向の幅にわたって N + ソース領域 15a と 15b との間に P + 領域 16 を配置する代りに、各柱の横方向の長さ(すなわち、例示した図のページの内外)にわたって各柱の上部に N + ソース領域 15 および P + 領域を交互に形成してもよい。言い換えれば、図 1 に示されるような所与の断面図は、断面をどこで取るかに応じて、柱 17 の横方向の幅全体にわたって延在する N + ソース領域 15 または P + 領域 16 を有することとなる。このような実施例においては、各々の N + ソース領域 15 は、(柱の横方向の長さに沿って) 両側が P + 領域 16 に隣接している。同様に、各々の P + 領域 16 は、(柱の横方向の長さに沿って) 両側が N + ソース領域 15 に隣接している。

20

【0012】

当業者であれば、P + 基板 11 が縦型の PNP バイポーラ接合トランジスタの P + エミッタ層としても機能することを認識するだろう。基本的な用語で表現すれば、深いトレンチ IGBT 10 が備える半導体デバイスは、上述のトレンチゲート MOSFET 構造によって制御される交互になった PNPN 導電型 (P + 基板 11 · N + バッファ層 12 および N - 拡張ドレイン領域 13 · P - ボディ領域 14 · N + ソース領域 15) からなる 4 つの層を備える。当業者であれば、N + バッファ層 12 を含めることにより、ドリフト領域 13 に形成されたオフ状態空乏層が高電圧阻止中に P + エミッタ(基板)層 11 に達するものが有利に防止されることをさらに認識するだろう。

30

【0013】

拡張ドレイン領域 13、P - ボディ領域 14、ソース領域 15a および 15b、ならびに P + 領域 16 は、図 1 の例示的なデバイス構造にシリコン材料からなるメサまたは柱(これらの用語はともに本願においては同義的に用いられる)を集合的に含む。図 3A ~ 図 3F に関連付けて以下に説明するように、柱は、各々の柱またはメサの両側にある半導体材料の領域を選択的に除去することによって形成される縦型トレンチによって規定される。各柱の高さおよび幅、ならびに隣接する縦型トレンチ間の間隔は、デバイスの降伏電圧要件によって決定されてもよい。さまざまな実施例においては、柱は、約 30 μm ~ 120 μm 厚の範囲の垂直高さ(厚さ)を有する。たとえば、寸法がほぼ 1 mm × 1 mm のダイ上に形成された深いトレンチ IGBT が有する柱は、約 60 ~ 65 μm の垂直厚さを備え、N - 拡張ドレイン領域 13 は、垂直厚さが全体で約 50 μm であり、N + バッファ層 12 は、垂直厚さが全体で約 10 ~ 15 μm であり得る。さらなる一例として、約 2 mm ~ 4 mm のダイ上に形成されたトランジスタ構造は、各々の側部に、約 30 μm の厚さを

40

50

もつ柱構造を有し得る。いくつかの実施例においては、各柱の横方向の幅は、非常に高い降伏電圧（たとえば、600～800V）を達成するために、可能な限り確実に狭くなるよう（たとえば、約0.4μm～0.8μmの幅）に製造される。

【0014】

さらに別の代替的な実施例においては、N+バッファ層をデバイス構造から省いてよい。しかしながら、N+バッファ層12を省くということは、所要の阻止電圧をサポートするためにN-拡張ドレイン領域13の垂直厚さ（柱の高さ）を実質的に増やす（たとえば、100～120μm）必要があるかもしだれることを意味していることに留意する。

【0015】

（N-拡張ドレイン領域13を含む）隣接する対の柱は、深いトレンチ誘電体領域19によって横方向に分離された状態で示されている。誘電体領域19は二酸化珪素、窒化珪素または他の好適な誘電材料を含んでいてもよい。深いトレンチの形成後、誘電体領域19は、熱成長および化学気相成長を含むさまざまな周知の方法を用いて形成され得る。図1の例においては、誘電体領域19の各々は、ゲート17のすぐ下から下方に延在してN+バッファ層12にまで達する。言い換えれば、図示される実施例においては、誘電体領域19は、ドリフト領域13の垂直方向の厚さ全体を通じて実質的に垂直に延在する。

【0016】

図2に示される実施例においては、誘電体領域19は、N+バッファ領域12を通じて垂直に延在してP+基板11にまで達する。

【0017】

一実施例においては、隣接したドリフト領域13の側壁を分離する各誘電体領域19の横方向の幅は、約2μmである。具体的な実施例においては、各ドリフト領域および各誘電体領域の横方向の幅は、1:1の幅比で、2μmに等しくなる。代替的な実施例は、0.2～6.0の範囲の幅比（ドリフト領域対誘電体領域）で製造されてもよい。

【0018】

当業者であれば、順方向（オン状態）導通の間に、バイポーラデバイスのP+エミッタ層11からドリフト領域13に少数キャリア（正孔）を注入することによってN-ドリフト領域13の抵抗が著しく低減されることを理解するだろう。これらの注入された少数キャリアは、典型的には、深いトレンチIGBTをオンやオフに切換えるときにドリフト領域13に出入りする（再結合する）のに時間を要する。図1および図2に示される例示的なデバイス構造においては、少数キャリアの再結合（「ライフタイム・キリング(lifetime killing)」とも称される）は、誘電体（たとえば酸化物）領域19とのN-ドリフト領域13の界面によって形成される大きな側壁領域に沿って作り出される多数の界面トラップを介して達成される。たとえば、デバイスがオン状態（順方向導通）からオフ状態（阻止電圧）に切換えられると、N-ドリフト領域13の側壁区域に沿った界面トラップは、ドリフト領域13から少数キャリアを速やかに一掃するのを有効に支援し、これにより、デバイスの高速切換え性能を向上させる。

【0019】

深いトレンチIGBTデバイス構造が誘電体領域19内に導電性のフィールドプレートを含んでいないので、すなわち、トレンチが酸化物または他の何らかの好適な誘電体で完全に充填されているので、N-ドリフト領域13のドーピングプロファイルが実質的に一定になり得ると認識されるはずである。

【0020】

図3A～図3Gの各々は、例示的な製造プロセスにおけるさまざまな段階で得られる例示的な深いトレンチIGBT構造を示す側断面図である。これらの図によって示されるこの製造プロセスは、図1のデバイスだけではなく、図2に示される深いトレンチIGBTデバイス構造をも形成するのに用いられてもよい。まず、図3Aには、P+シリコン基板11の上にN-ドープ層12および13を形成する最初の工程後の製造プロセスにおける深いトレンチIGBT構造の例示的な側断面図が示される。一実施例においては、N+バッファ層12は、約10～15μmの範囲の垂直厚さを有する。N+層11を高濃度にド

10

20

30

40

50

ープすることにより、完成したデバイスにおいて基板の底に位置するドレイン（エミッタ）電極を通って流れる電流に対する抵抗が最小限にされる。N+バッファ層12を高濃度にドープすることによっても、逆バイアス電圧阻止中におけるP+基板11へのパンチスルーが防止される。層12は、その層の形成中にドープされてもよい。N-エピタキシャル層13も、その層の形成中にドープされてもよい。

【0021】

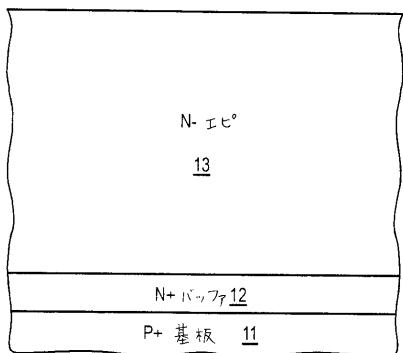

図4は、図1に示されるような例示的な深いトレンチIGBTデバイス構造のためのエピタキシャル層ドーピングプロファイル対正規化距離についてのプロットを示す。図から分かるように、N型エピタキシャル層のドーピングプロファイル濃度は、約 $1 \times 10^{15} \text{ cm}^{-3}$ の比較的低濃度で実質的に平坦になっている。約 $54 \mu\text{m}$ の垂直深さでN+バッファ層が始まっており、ここでは、ドーピングプロファイル濃度が、約 $2 \times 10^{17} \text{ cm}^{-3}$ の濃度へと急激に増大（段階的に増大）している。

10

【0022】

層12および13が形成された後、半導体ウェハの上面が適切にマスクされ、次いで、深い縦型トレンチ22がN-エピタキシャル層13にエッチングされる。図3Bは、深いトレンチ22によって分離されたN-ドープ半導体材料からなるシリコン柱またはメサを形成する縦型トレンチエッチング後の製造プロセスにおける深いトレンチIGBTの例示的な側断面図を示す。各々の柱の高さおよび幅、ならびに隣接する縦型トレンチ22間の間隔は、デバイスの降伏電圧要件によって決定され得る。上述のとおり、エピタキシャル材料13のこれらの分離された柱は、最終的には、最終深さのトレンチIGBTデバイス構造を有するドリフト領域またはN型拡張ドレインを形成する。

20

【0023】

さまざまな実施例においては、各々の柱が（ページの内外への）直交する方向にかなりの横方向距離にわたって延在し得ることが理解されるはずである。いくつかの実施例においては、各柱によって形成されたN型ドリフト領域の横方向の幅は、非常に高い降伏電圧（たとえば、600～800V）を達成するために、可能な限り確実に狭くなるよう製造される。

20

【0024】

さらに、図1の例は、分離された3つのN-ドリフト領域を含む半導体材料からなる3本の柱または列を備えた断面を示しているが、このデバイス構造が、完成したデバイスの半導体ダイの上で両横方向に何度も繰り返され得るかまたは再現され得ることが理解されるはずである。他の実施例は、任意には、付加的なまたはより少数の半導体領域を含んでもよい。たとえば、いくつかの代替的な実施例は、上部から底部までの間で変化するドーピングプロファイルを有するドリフト領域を備えていてもよい。他の実施例では、分離された柱（たとえばN-ドリフト領域）を形成する半導体材料の横方向の幅が複数回にわたって急激に（すなわち、段階的に）変動し得る。たとえば、ドリフト領域13は、シリコンウェハの上面付近でより広く、また、N+バッファ層12に最も近いところでより広くなるよう製造されてもよい。

30

【0025】

図3Cは、トレンチ22を誘電材料（たとえば酸化物）で充填し、これにより誘電体領域19を形成した後における図3Bの例示的なデバイス構造を示す。誘電材料は、エピタキシャル層柱の各々の側壁を覆い、トレンチ22の各々を完全に充填している。誘電体層は好ましくは二酸化珪素を含んでいるが、窒化珪素または他の好適な誘電材料が用いられてもよい。誘電体領域19は、熱成長および化学気相成長を含むさまざまな周知の方法を用いて形成されてもよい。領域19の形成後、シリコン基板の上面は、化学機械研磨などの従来技術を利用して平坦化されてもよい。

40

【0026】

図3Dは、シリコン基板の上面をマスキングした後の図3Cの例示的なデバイス構造を示す。この例においては、マスキング層25はフォトレジストの層からなり、酸化物領域19上で中心に位置決めされた開口部24が設けられている。なお、マスキング層25の

50

うち、エピタキシャル領域13の各柱の真上にある部分は、柱の側壁部分の端縁を越えてわずかな距離だけ延在するかまたは重なることに留意されたい。これにより、酸化物領域19の第1および第2の側壁部分を覆う側壁酸化物の薄い層を残す効果が得られる。すなわち、各々のN-エピ柱13に最も近い各開口部24の端縁は、側壁とは重ならず、むしろ、開口部24は、各開口部24の最も近接する端縁が、対応する柱の側壁からわずかな距離だけ離れるように意図的にオフセットにされる。一実施例においては、重なり合う距離は約0.2μm～0.5μmである。

## 【0027】

ゲートトレンチ26は、開口部24のすぐ下の区域における領域19の誘電材料を除去する第1の誘電体エッチングによって形成される。一実施例においては、第1の誘電体エッチングは実質的に異方性のプラズマエッチングである。第1の誘電体エッチングは、所望または目標の深さ、一実施例においては約3μmの深さ、にまで施される。たとえば、プラズマエッチングのためにC<sub>4</sub>F<sub>8</sub>/CO/Ar/O<sub>2</sub>ガスの混合物を使用してもよい。なお、第1のエッチングがもつ異方性により、ゲートトレンチに実質的に垂直な側壁プロファイルがもたらされるが、これは、各柱13の側壁にまでは延在または貫通しないことに留意されたい。別の言い方をすれば、マスキング層25は、開口部24を通る異方性エッチングがN-エピ柱13の側壁に侵食しないような距離だけ重ねられる。むしろ、酸化物領域19を含む誘電材料の一部は、第1の誘電体エッチング後でも依然として柱13の側壁区域を覆ったままとなる。

## 【0028】

図3Eは、ゲートトレンチにおけるN-エピ柱13の側壁を覆う酸化物の除去後における図3Dの例示的なデバイス構造を示す。第2の誘電体エッチングは、N-エピ柱の側壁上の残りの酸化物を完全に除去するよう、マスキング層25の開口部24を通じて行われてもよい。一実施例においては、第2の誘電体エッチングは、本来は実質的に等方性である（たとえば、バッファードフッ酸を用いる）ウェットエッチングである。結果として、1対のゲートトレンチ開口部27が設けられて、柱またはメサの側壁に沿ってエピタキシャルシリコン材料を露出させる。

## 【0029】

図示される実施例においては、第2の誘電体エッチングは極めて選択的であり、これは、シリコンをエッチングする場合よりもはるかに高速で誘電材料をエッチングすることを意味する。このプロセスを用いると、各側壁のシリコン表面は損傷を受けることがなく、このため、引続き、高品質のゲート酸化物を側壁表面に成長させることができる。加えて、第2の誘電体エッチングが実質的に等方性であるため、ゲートトレンチは、垂直方向および横方向のどちらにも同様の速さでエッチングされる。しかしながら、第2の誘電体エッチングを用いて、シリコンメサの側壁上に残っている10分の数ミクロンの二酸化珪素を除去するので、トレンチゲート開口部27のアスペクト比に対する全体的な影響は比較的些細なものとなる。一実施例においては、各ゲートトレンチ開口部27の横方向の幅は約1.5μmであり、最終深さは約3.5μmとなる。

## 【0030】

図3Fは、マスキング層25を除去し、N-エピ柱13の露出した側壁部分を覆う高品質で薄い（たとえば、～500）ゲート酸化物層28を形成し、次いでゲートトレンチを充填した後の図3Eの例示的なデバイス構造を示す。一実施例においては、ゲート酸化物層28は熱成長して、100～1000の範囲の厚さになる。マスキング層25を除去してからゲート酸化物28を形成する。各ゲートトレンチの残りの部分は、完成した深いトレンチIGBTデバイス構造においてゲート部材17を形成するドープポリシリコンまたは別の好適な材料で充填される。一実施例においては、各々のゲート部材17は、横方向の幅が約1.5μmで、深さが約3.5μmとなる。

## 【0031】

マスキング層は、マスクのミスアライメント誤差が起こる最悪の場合でも、各々のN-エピ柱13の側壁に対して結果として得られるマスキング層25の重なりによって、対向

10

20

30

40

50

する柱の側壁のいずれかに沿ったシリコン材料へのプラズマエッティングの侵食が依然として防止されるほど十分に長い距離だけ重ねられなければならないことを、当業者であれば認識するだろう。同様に、マスキング層 25 は、マスクのミスアライメントが起こる最悪の場合でも、側壁 19 のいずれかに残っている酸化物が適度な第 2 の誘電体エッティングによっても除去できないほどに長く重ねられるべきではない。

### 【0032】

図 3G は、各々の N - ドリフト領域 13 の上部付近に N + ソース (コレクタ) 領域 15a および 15b ならびに P - ボディ領域 14 を形成した後における図 3F の例示的なデバイス構造を示す。ソース領域 15 および P - ボディ領域 14 は各々、通常の堆積、拡散および / または注入処理技術を用いて形成されてもよい。N + ソース領域 15 の形成後、トランジスタデバイスは、(明瞭にするために図示されない) 従来の製造方法を用いてデバイスのそれぞれの領域 / 材料に電気的に接続するソース (コレクタ)、ドレイン (エミッタ)、および M O S F E T ゲート電極を形成することによって完成させてもよい。

10

### 【0033】

特定のデバイスタイプに関連付けて上述の実施例を説明してきたが、当業者であれば、多数の変形例および代替例が十分にこの発明の範囲内に収まることを認識するだろう。たとえば、さまざまな深いトレンチ I G B T を説明してきたが、図示される方法、レイアウトおよび構造は、ショットキー (Schottky)、ダイオード、M O S およびバイポーラの構造を含む他の構造およびデバイスタイプに等しく適用可能である。したがって、明細書および図面は、限定的なものとしてではなく、例示的なものとみなされるべきである。

20

### 【符号の説明】

### 【0034】

10 深いトレンチ I G B T 、 11 P + 基板、 12 N + バッファ層、 13 拡張ドレイン領域、 14 P - ボディ領域、 15a 、 15b N + ソース領域、 16 P + 領域、 17 ゲート。

### 【図 1】

### 【図 2】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図3G】

【図3F】

【図4】

## フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

H 01 L 29/06 301D

(74)代理人 100109162

弁理士 酒井 將行

(74)代理人 100111246

弁理士 荒川 伸夫

(74)代理人 100124523

弁理士 佐々木 真人

(72)発明者 ビジエイ・パルササラシー

アメリカ合衆国、94040 カリフォルニア州、マウンテン・ビュー、ボニータ・アベニュー、1

055

(72)発明者 スジット・バネルジー

アメリカ合衆国、95125 カリフォルニア州、サンノゼ、ハクスリー・コート、1901