(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6571071号

(P6571071)

(45) 発行日 令和1年9月4日(2019.9.4)

(24) 登録日 令和1年8月16日(2019.8.16)

(51) Int.Cl.

H03F 1/02 (2006.01)

H03F 3/24 (2006.01)

F 1

H03F 1/02

H03F 3/24

1 1 1

請求項の数 15 (全 24 頁)

(21) 出願番号 特願2016-518386 (P2016-518386)

(86) (22) 出願日 平成26年6月2日 (2014.6.2)

(65) 公表番号 特表2016-521102 (P2016-521102A)

(43) 公表日 平成28年7月14日 (2016.7.14)

(86) 國際出願番号 PCT/US2014/040561

(87) 國際公開番号 WO2014/197399

(87) 國際公開日 平成26年12月11日 (2014.12.11)

審査請求日 平成29年5月9日 (2017.5.9)

(31) 優先権主張番号 13/911,902

(32) 優先日 平成25年6月6日 (2013.6.6)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】可変ブースト電源電圧を用いたエンベロープトラッカー

## (57) 【特許請求の範囲】

## 【請求項 1】

装置であって、前記装置は下記を備える、

エンベロープ信号と可変ブースト電源電圧とを受け、出力電圧と出力電流とを与えるよう構成された増幅器と、

バッテリー電圧と、前記エンベロープ信号に基づいて決定された少なくとも1つの信号とを受け、前記バッテリー電圧と前記少なくとも1つの信号とに基づいて前記可変ブースト電源電圧を生成するように構成されたブーストコンバータと、

前記エンベロープ信号または前記出力電圧に基づいて前記ブーストコンバータのための前記少なくとも1つの信号を生成するように構成されたブーストコントローラ、ここで、前記ブーストコントローラが、

前記増幅器から前記ブーストコントローラへの出力電流に基づいてヘッドルームを決定するように構成されたコンバータと、

前記ヘッドルームと前記エンベロープ信号または前記出力電圧を加算し、加算電圧を与えるように構成された加算器と、

前記加算電圧のピークを検出し、前記検出されたピーク電圧を与えるように構成されたピーク検出器と、

を備える。

## 【請求項 2】

前記ブーストコントローラが、前記エンベロープ信号または前記出力電圧に基づいてイ

10

20

ネーブル信号を生成するように構成され、前記少なくとも1つの信号が前記イネーブル信号を備え、前記ブーストコンバータが、前記イネーブル信号に基づいて有効または無効にされる、請求項1に記載の装置。

**【請求項3】**

前記ブーストコントローラが、前記エンベロープ信号または前記出力電圧に基づいて前記ブーストコンバータのためのしきい値電圧を生成するように構成され、前記少なくとも1つの信号が前記しきい値電圧を備え、前記ブーストコンバータが、前記バッテリー電圧と前記しきい値電圧とに基づいて前記可変ブースト電源電圧を生成するように構成された、請求項1に記載の装置。

**【請求項4】**

前記増幅器から前記ブーストコントローラへの前記出力電流が、前記増幅器からの前記出力電流のプログラム可能な比率に応じて調整された検知出力電流である、請求項1に記載の装置。

**【請求項5】**

前記ブーストコントローラが、前記加算電圧の前記検出されたピークに基づいてイネーブル信号を生成するように構成され、前記少なくとも1つの信号が前記イネーブル信号を備え、前記ブーストコンバータが、前記イネーブル信号に基づいて有効または無効にされる、請求項1に記載の装置。

**【請求項6】**

前記ブーストコントローラは、前記加算電圧の前記検出されたピークが前記バッテリー電圧を超えるときに前記ブーストコンバータを有効にし、前記加算電圧の前記検出されたピークが前記バッテリー電圧を下回るときに前記ブーストコンバータを無効にするための前記イネーブル信号を生成するように構成された、請求項5に記載の装置。

**【請求項7】**

前記ブーストコントローラは、前記加算電圧の前記検出されたピークが所定の時間量の間、または所定の量だけ、または両方、前記バッテリー電圧を下回るときに前記ブーストコンバータを無効にするための前記イネーブル信号を生成するように構成された、請求項6に記載の装置。

**【請求項8】**

前記ブーストコントローラは、

前記検出されたピーク電圧に基づいてしきい値電圧を決定するように構成された制御回路をさらに備え、ここにおいて、前記少なくとも1つの信号が前記しきい値電圧を備え、ここにおいて、前記ブーストコンバータが、前記バッテリー電圧と前記しきい値電圧とに基づいて前記可変ブースト電源電圧を生成するように構成される、請求項1に記載の装置。

。

**【請求項9】**

前記制御回路が、前記検出されたピーク電圧に基づいてイネーブル信号を決定するように構成され、前記少なくとも1つの信号が前記イネーブル信号を備え、前記ブーストコンバータが、前記イネーブル信号に基づいて有効または無効にされる、請求項8に記載の装置。

**【請求項10】**

方法であって、前記方法は下記を備える、

バッテリー電圧と、エンベロープ信号に基づいて決定された少なくとも1つの信号とに基づいて可変ブースト電源電圧をブーストコンバータによって生成することと、

出力電圧と出力電流とを得るために前記可変ブースト電源電圧を用いて前記エンベロープ信号を増幅することと、

前記エンベロープ信号または前記出力電圧に基づいて前記ブーストコンバータのための前記少なくとも1つの信号をブーストコントローラによって生成すること、ここで、前記ブーストコントローラが、コンバータと、加算器と、ピーク検出器とを備える、

前記方法は、さらに下記を備える、

10

20

30

40

50

前記増幅器から前記ブーストコントローラへの出力電流に基づいてヘッドルームを前記コンバータによって決定することと、

前記ヘッドルームと前記エンベロープ信号または前記出力電圧を前記加算器によって加算し、加算電圧を与えることと、

前記加算電圧のピークを前記ピーク検出器によって検出し、前記検出されたピーク電圧を与えること。

【請求項 1 1】

前記エンベロープ信号または前記出力電圧に基づいてイネーブル信号を生成することをさらに備え、ここにおいて、前記少なくとも 1 つの信号が前記イネーブル信号を備え、ここにおいて、前記可変ブースト電源電圧の生成が、前記イネーブル信号に基づいて有効または無効にされる、請求項 1 0 に記載の方法。 10

【請求項 1 2】

前記エンベロープ信号または前記出力電圧に基づいてしきい値電圧を生成することをさらに備え、ここにおいて、前記少なくとも 1 つの信号が前記しきい値電圧を備え、ここにおいて、前記可変ブースト電源電圧が、前記バッテリー電圧と前記しきい値電圧とに基づいて生成される、請求項 1 0 に記載の方法。

【請求項 1 3】

前記しきい値電圧を前記生成することが、前記ヘッドルームにさらにに基づいて前記しきい値電圧を生成することを備える、請求項 1 2 に記載の方法。

【請求項 1 4】 20

前記しきい値電圧を前記生成することが、前記加算電圧の前記検出されたピークに基づいて前記しきい値電圧を決定することを備える、請求項 1 2 に記載の方法。

【請求項 1 5】

非一時的コンピュータ可読記憶媒体は下記を備える、

少なくとも 1 つのコンピュータに、請求項 1 0 から 1 4 のいずれか一項に記載の方法を実行させるためのコード。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

関連出願の相互参照

[0001]本開示は、すべての目的のために、その内容全体が参照により本明細書に組み込まれる、2013年6月6日に出願された米国非仮出願第13/911,902号の優先権を主張する。 30

【0 0 0 2】

[0002]本開示は、一般に電子工学に関し、より詳細には、増幅器および／または他の回路のための電源電圧を生成するための技法に関する。

【背景技術】

【0 0 0 3】

[0003]通信システムでは、送信機は、データを処理（たとえば、符号化および変調）して、出力サンプルを生成し得る。送信機は、出力サンプルをさらに調整（たとえば、アナログ変換、フィルタ処理、周波数アップコンバート、および増幅）して、出力無線周波（R F）信号を生成し得る。送信機は、次いで、通信チャネルを介して出力 R F 信号を受信機に送信し得る。受信機は、送信された R F 信号を受信し、送信されたデータを復元するために、受信した R F 信号に対して補足的処理を実行し得る。 40

【0 0 0 4】

[0004]送信機は、一般に、出力 R F 信号のための高い送信電力を与えるための電力増幅器（P A）を含む。電力増幅器は、高い送信電力を与えることができ、高い電力付加効率（P A E : power-added efficiency）を有するべきである。さらに、電力増幅器は、低いバッテリー電圧の場合でも良好な性能と高い P A E を有することが要求され得る。

【発明の概要】 50

## 【0005】

[0005] 増幅器および／または他の回路のための可変ブースト電源電圧 (variable boosted supply voltage) を効率的に生成するための技法が本明細書で開示される。例示的な設計では、装置（たとえば、集積回路、ワイヤレスデバイス、または回路モジュール）は、増幅器と、ブーストコンバータ（boost converter）とを含み得る。増幅器は、エンベロープ信号（envelope signal）と可変ブースト電源電圧とを受け、出力電圧と出力電流とを与え得る。エンベロープ信号は、送信されているRF信号のエンベロープに従い得る。可変ブースト電源電圧は増幅器のための電源電圧として使用され得る。ブーストコンバータは、電源電圧（たとえば、バッテリー電圧）と、エンベロープ信号に基づいて決定された少なくとも1つの信号とを受け得、電源電圧と少なくとも1つの信号とにに基づいて可変ブースト電源電圧を生成し得る。可変ブースト電源電圧は、電源電圧よりも大きくなり得、調整可能であり得る。

## 【0006】

[0006] 本装置は、エンベロープ信号および／または出力電圧に基づいてブーストコンバータのための少なくとも1つの信号を生成し得る、ブーストコントローラをさらに含み得る。ブーストコントローラは、エンベロープ信号および／または出力電圧に基づいてイネーブル信号を生成し得る。代替または追加として、ブーストコントローラは、エンベロープ信号および／または出力電圧に基づいて、場合によってはヘッドルーム（たとえば、ヘッドルーム電圧またはヘッドルーム電流）にさらにに基づいて、ブーストコンバータのためのしきい値電圧を生成し得る。ヘッドルームは増幅器からの出力電流に依存し得る。少なくとも1つの信号はイネーブル信号および／またはしきい値電圧を含み得る。ブーストコンバータは、イネーブル信号に基づいて有効または無効にされ得る。ブーストコンバータは、電源電圧としきい値電圧とにに基づいて可変ブースト電源電圧を生成し得る。たとえば、しきい値電圧は、可変であり、エンベロープ信号とヘッドルームとの和に基づいて決定され得る（たとえば、和に等しくなり得る）。可変ブースト電源電圧はしきい値電圧に等しいかまたはそれに比例し得る。

## 【0007】

[0007] 本開示の様々な態様および特徴について以下でさらに詳細に説明する。

## 【図面の簡単な説明】

## 【0008】

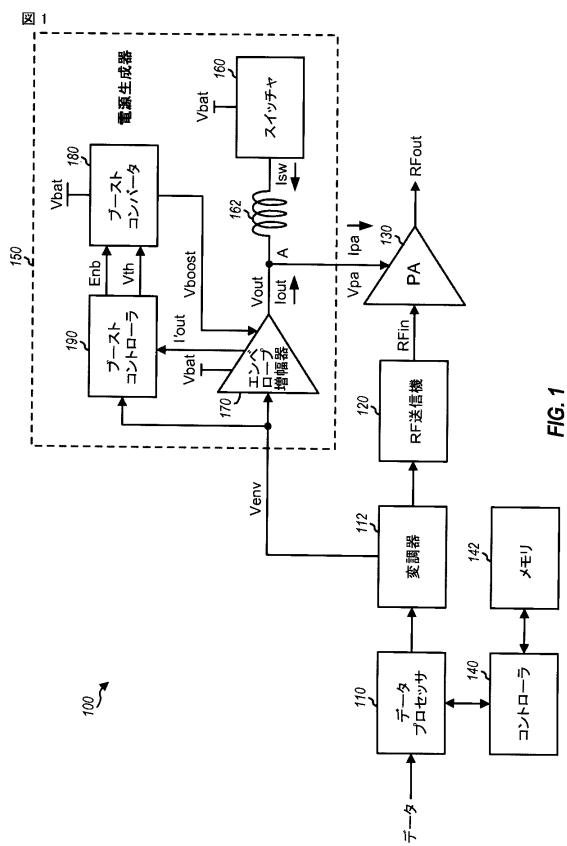

【図1】[0008] ワイヤレス通信デバイスのブロック図。

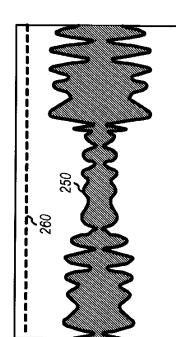

【図2 A】[0009] 固定バッテリー電圧に基づいて電力増幅器を動作させる図。

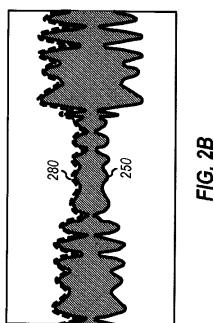

【図2 B】エンベロープトラッキングを用いた可変電源電圧に基づいて電力増幅器を動作させる図。

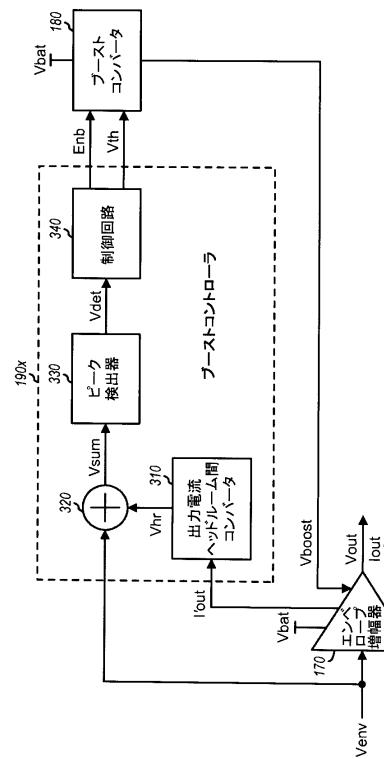

【図3】[0010] ブーストコントローラのブロック図。

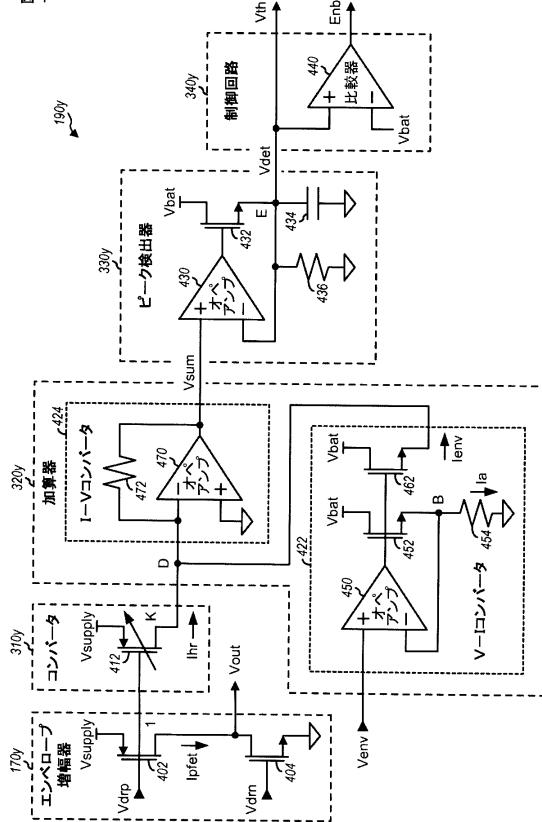

【図4】[0011] ブーストコントローラの概略図。

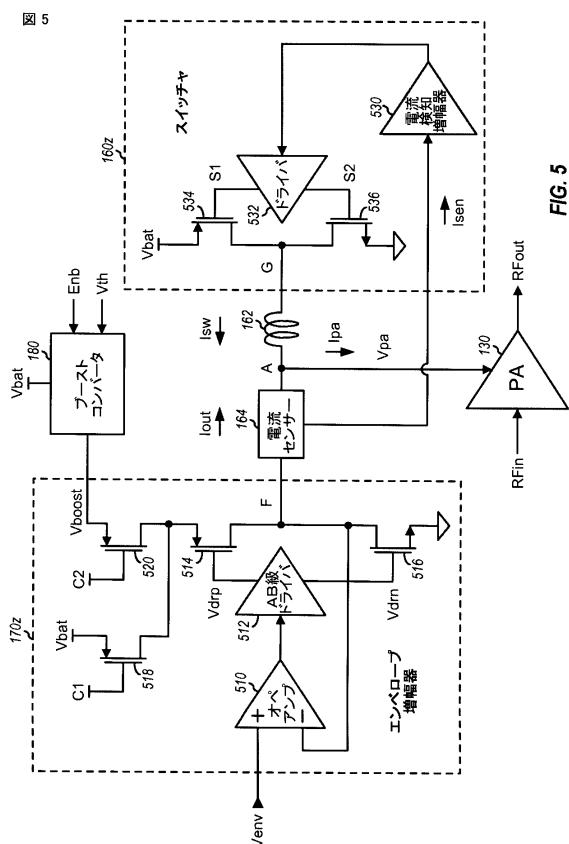

【図5】[0012] スイッチャ（switcher）とエンベロープ増幅器との概略図。

【図6】[0013] ブーストコンバータの概略図。

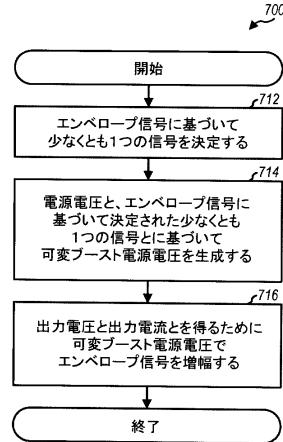

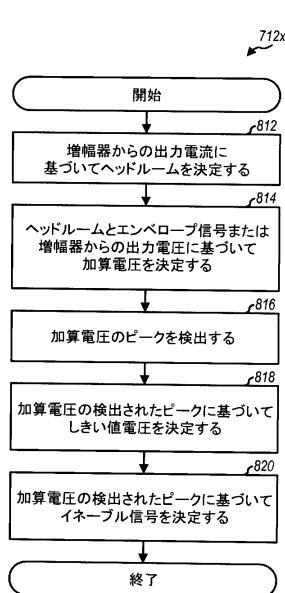

【図7】[0014] 可変ブースト電源電圧を生成するためのプロセスを示す図。

【図8】[0015] ブーストコンバータを制御するための信号を生成するためのプロセスの例示的な設計を示す図。

## 【発明を実施するための形態】

## 【0009】

[0016] 以下に示す発明を実施するための形態は、本開示の例示的な設計を説明するものであり、本開示が実施され得る唯一の設計を表すものではない。「例示的」という用語は、本明細書では、「例、事例、または例示の働きをすること」を意味するために使用する。「例示的」として本明細書で説明するいかなる設計も、必ずしも他の設計よりも好ましいまたは有利であると解釈されるべきであるとは限らない。発明を実施するための形態は、本開示の例示的な設計の完全な理解を与えるための具体的な詳細を含む。本明細書で説明する例示的な設計はこれらの具体的な詳細なしに実施され得ることが当業者には明らか

10

20

30

40

50

であろう。いくつかの事例では、本明細書で提示する例示的な設計の新規性を不明瞭にしないように、よく知られている構造およびデバイスをブロック図の形式で示す。

#### 【0010】

[0017] 増幅器および／または他の回路のための可変ブースト電源電圧を生成するための技法が本明細書で開示される。本技法は、電力増幅器、ドライバ増幅器、バッファなどの様々なタイプの増幅器のために使用され得る。本技法はまた、ワイヤレス通信デバイス、セルラーフォン、携帯情報端末（PDA）、ハンドヘルドデバイス、ワイヤレスモードム、ラップトップコンピュータ、コードレスフォン、Bluetooth（登録商標）デバイス、コンシューマー電子デバイスなど、様々な電子デバイスのために使用され得る。明快のために、ワイヤレス通信デバイス中のエンベロープ増幅器のための可変ブースト電源電圧を生成する技法の使用について以下で説明する。10

#### 【0011】

[0018] 図1に、ワイヤレス通信デバイス100の例示的な設計のブロック図を示す。明快のために、ワイヤレスデバイス100の送信機部分のみが図1に示されており、受信機部分は図1に示されていない。ワイヤレスデバイス100内で、データプロセッサ110は、送信されるべきデータを受信し、データを処理（たとえば、符号化、インターリーブ、シンボルマッピング）し、データシンボルを与え得る。データプロセッサ110はまた、パイロットを処理し、パイロットシンボルを与え得る。データプロセッサ110は、符号分割多元接続（CDMA）、時分割多元接続（TDMA）、周波数分割多元接続（FDMA）、直交FDMA（OFDMA）、シングルキャリアFDMA（SC-FDMA）および／またはいくつかの他の多重化方式のためのデータシンボルおよびパイロットシンボルをさらに処理し得、出力シンボルを与え得る。20

#### 【0012】

[0019] 変調器112は、データプロセッサ110から出力シンボルを受け、直交変調、極変調、または何らかの他のタイプの変調を実行し、出力サンプルを与え得る。変調器112はまた、出力サンプルのエンベロープを決定し得る。例示的な設計では、エンベロープは次のように決定され得る。

#### 【数1】

$$e(t) = \text{avg} \left( \sqrt{I^2(t) + Q^2(t)} \right), \quad \text{式(1)}$$

30

上式で、 $I(t)$ は、サンプル期間 $t$ における同相( $I$ )出力サンプルを示し、

$Q(t)$ は、サンプル期間 $t$ における直交( $Q$ )出力サンプルを示し、

$e(t)$ はエンベロープ信号を示し、

「avg」は平均演算を示す。

#### 【0013】

[0020] 式(1)に示された設計では、変調器112は、各複素数値の出力サンプルの大きさを計算し、出力サンプルにわたって大きさを平均化することによって、エンベロープ信号を決定する。変調器112は、他の様式で、たとえば、 $I$ および $Q$ 出力サンプルの他の関数に基づいてエンベロープ信号を決定し得る。たとえば、出力サンプルの複数のストリームが（たとえば、キャリアアグリゲーションのための複数のキャリア上で）同時に送信され得、変調器112は、(i)

40

## 【数2】

$$P_k(t) = I_k^2(t) + Q_k^2(t)$$

として各出力サンプルストリームの電力を計算することと、ここで、 $I_k(t)$  および  $Q_k(t)$  は  $I$  サンプルおよび  $Q$  サンプルを示し、 $P_k(t)$  はサンプル期間  $t$  における  $k$  番目の出力サンプルストリームの電力を示す、そして、(i i) 全電力を得るためにすべての出力サンプルストリームの電力を加算すること、すなわち

## 【数3】

$$P(t) = \sum_k P_k(t)$$

と、そして、(i i i) エンベロープ信号を得るために全電力の平方根を取ること（場合によっては結果を平均すること）、すなわち

## 【数4】

$$e(t) = \sqrt{P(t)}$$

とによって、エンベロープ信号を決定し得る。概して、変調器 112 は、出力サンプルのエンベロープの何らかの関数に基づいてエンベロープ信号を与え得る。エンベロープ信号は電力トラッキング信号とも呼ばれ得る。

## 【0014】

[0021] RF 送信機 120 は、変調器 112 からの出力サンプルを処理（たとえば、アナログ変換、増幅、フィルタ処理、周波数アップコンバート）し、入力 RF 信号（RF in）を与え得る。電力増幅器（PA）130 は、入力 RF 信号を増幅して、所望の送信電力レベルを取得し、出力 RF 信号（RF out）を与え得、出力 RF 信号はアンテナ（図 1 に図示せず）を介して送信され得る。RF 送信機 120 は、エンベロープ信号を生成するために変調器 112 を使用する代わりに、エンベロープ信号を生成するための回路を含み得る。

## 【0015】

[0022] 電源生成器 150 は、変調器 112 からエンベロープ信号（Env）を受け、電力増幅器 130 のための電源電圧を生成し得、それは、PA 電源電圧と呼ばれ、Vpa として示され得る。電源生成器 150 はエンベロープトラッカー（envelope tracker）と呼ばれることもある。図 1 に示された設計では、電源生成器 150 は、スイッチャ 160 と、エンベロープ増幅器（Env Amp）170 と、ブーストコンバータ 180 と、ブーストコントローラ 190 と、インダクタ 162 とを含む。スイッチャ 160 は、スイッチングモード電源（SMPs : switching-mode power supply）、バックコンバータ（buck converter）などと呼ばれることもある。スイッチャ 160 は、バッテリー電圧（Vbat）を受け、ノード A において直流（DC）および低周波成分を備える第 1 の供給電流（Is w）を与える。インダクタ 162 は、スイッチャ 160 からの電流を蓄積し、蓄積された電流を交互サイクルでノード A に与える。ブーストコンバータ 180 は、Vbat

10

20

30

40

50

電圧としきい値電圧 ( $V_{th}$ ) とを受け、イネーブル (Enb) 信号によって有効にされたとき、 $V_{bat}$  電圧よりも高いブースト電源電圧 ( $V_{boost}$ ) を生成する。 $V_{boost}$  電圧は、可変であり得、 $V_{th}$  電圧に依存し得る(たとえば、 $V_{boost} \propto V_{th}$  である)。ブーストコントローラ 190 は、 $V_{env}$  信号と  $I_{out}$  電流(または  $I_{out}$  電流の比率に応じて調整された(scaled)バージョン)とに基づいて  $V_{th}$  電圧と Enb 信号とを生成する。電源生成器 150 中の回路について以下でさらに詳細に説明する。

#### 【0016】

[0023] エンベロープ増幅器 170 は、その信号入力において  $V_{env}$  信号を受け、その 2 つの供給入力において  $V_{bat}$  電圧と  $V_{boost}$  電圧とを受け、ノード A において高周波成分を備える出力電流 ( $I_{out}$ ) と出力電圧 ( $V_{out}$ ) とを与える。電力増幅器 130 に与えられた PA 供給電流 ( $I_{pa}$ ) は、スイッチャ 160 からの  $I_{sw}$  電流と、エンベロープ増幅器 170 からの  $I_{out}$  電流とを含む。エンベロープ増幅器 170 はまた、電力増幅器 130 のための PA 電源電圧として  $V_{out}$  電圧を与える。概して、電圧は固定値(たとえば、 $V_{bat}$ )または可変値(たとえば、 $V_{out}$ )を有し得る。電圧は、経時的に変動し得、信号と見なされ得る。

#### 【0017】

[0024] コントローラ 140 は、ワイヤレスデバイス 100 内の様々なユニットの動作を制御し得る。メモリ 142 は、コントローラ 140 および / またはワイヤレスデバイス 100 内の他のユニットのためのプログラムコードとデータとを記憶し得る。データプロセッサ 110、変調器 112、コントローラ 140、およびメモリ 142 は、1 つまたは複数の特定用途向け集積回路 (ASIC) および / または他の IC 上に実装され得る。

#### 【0018】

[0025] 図 1 に、ワイヤレスデバイス 100 の例示的な設計を示す。ワイヤレスデバイス 100 は、他の様式でも実装され得、図 1 に示されている回路とは異なる回路を含み得る。RF 送信機 120、電力増幅器 130、および電源生成器 150 の全部または一部分が、1 つまたは複数のアナログ集積回路 (IC)、RF IC (RFIC)、混合信号 IC などの上に実装され得る。

#### 【0019】

[0026] 図 2A に、電力増幅器 130 のための固定バッテリー電圧の使用を示す。(RF in 信号に後続する) RF out 信号は、時間変動するエンベロープを有し、プロット 250 によって示されている。バッテリー電圧は、プロット 260 によって示されており、電力増幅器 130 からの RF out 信号をクリッピングすることを回避するために、時間変動するエンベロープの最も大きい振幅よりも高い。バッテリー電圧と RF out 信号のエンベロープとの間の差は、出力負荷に送達される代わりに電力増幅器 130 によって放散される浪費される電力を表す。

#### 【0020】

[0027] 図 2B に、電源生成器 150 を用いた電力増幅器 130 のための可変電源電圧の生成を示す。電源生成器 150 は、RF out 信号のエンベロープを示すエンベロープ信号を受け、エンベロープ信号に基づいて電力増幅器 130 のための(プロット 280 によって示される)PA 電源電圧を生成する。PA 電源電圧は、経時的に RF out 信号のエンベロープを厳密に追跡する。したがって、PA 電源電圧と RF out 信号のエンベロープとの間の差が小さくなり、その結果、浪費される電力が少なくなる。電力増幅器 130 は、PA 効率を改善するためにすべての RF 信号振幅について飽和状態で動作させられ得る。

#### 【0021】

[0028] 電源生成器 150 は、電力増幅器 130 に与えられる RF in 信号のエンベロープを追跡するように PA 電源電圧を効率的に生成することができ、それによって、電力増幅器 130 に与えられる PA 電源電圧が適切な大きさ / 電圧を有し、電力増幅器 130 の PAE が改善されることができる。さらに、電源生成器 150 は、低いバッテリー電圧で

10

20

30

40

50

P A 電源電圧を生成することができる。ワイヤレスデバイス 100 は、電力消費を削減し、バッテリー寿命を延長し、および / または他の利点を得るために、低いバッテリー電圧で動作し得る。しかしながら、電力増幅器 130 は、バッテリー電圧よりも高い P A 電源電圧を用いて動作する必要があり得る。たとえば、バッテリー電圧は 2.5 ボルト (V) であり得、必要とされる P A 電源電圧は 3.2 V であり得る。より高い P A 電源電圧を得るためにバッテリー電圧をブーストするためにブーストコンバータが使用され得る。しかしながら、P A 電源電圧を直接与えるためにブーストコンバータを使用することにより、コストと電力消費とが増加し得、その両方とも望ましくないことがある。

#### 【0022】

[0029] 電源生成器 150 は、電力増幅器 130 の P A E を改善するために可変 V boost 電圧を用いて P A 電源電圧を効率的に生成し、P A 電源電圧を直接与えるためにブーストコンバータを使用することの不利益を回避することができる。これは、(i) 電力増幅器 130 への供給電流の DC および低周波成分を備える第 1 の供給電流 (I<sub>ind</sub>) を生成する効率的なスイッチャ 160 と、(ii) 電力増幅器 130 への供給電流の高周波成分を備える第 2 の供給電流 (I<sub>env</sub>) を生成する線形エンベロープ増幅器 170 との組合せを使用することによって達成され得る。スイッチャ 160 は、バッテリー電圧を用いて動作し得、電力増幅器 130 のための電力の大部分を与え得る。エンベロープ増幅器 170 は、可変 V<sub>boost</sub> 電圧 (必要な場合) またはバッテリー電圧 (可能な場合) を用いて動作し得、電力増幅器 130 に残りの供給電流を与え得る。ブーストコンバータ 180 は、V<sub>th</sub> 電圧に基づいてエンベロープ増幅器 170 のための所望の大きさ / 電圧の可変 V<sub>boost</sub> 電圧を生成し得る。電源生成器 150 は、適切な大きさ / 電圧の P A 電源電圧が電力増幅器 130 に与えられるように、電力増幅器 130 に与えられた R F in 信号のエンベロープを追跡するための P A 電源電圧を生成することができる。10

#### 【0023】

[0030] 図 3 に、図 1 中の電源生成器 150 内のブーストコントローラ 190 の 1 つの例示的な設計である、ブーストコントローラ 190 x のブロック図を示す。エンベロープ増幅器 170 は、その出力において電力増幅器 130 に V<sub>out</sub> 電圧と I<sub>out</sub> 電流とを与え得る。エンベロープ増幅器 170 は、I<sub>out</sub> 電流を検知し、検知出力電流 (I'<sub>out</sub>) を与えることができる検知回路を含み得る。I'<sub>out</sub> 電流は、I<sub>out</sub> 電流に等しくなり得る (たとえば、I'<sub>out</sub> = I<sub>out</sub> である) か、または I<sub>out</sub> 電流の比率に応じて調整されたバージョンであり得る (たとえば、I'<sub>out</sub> = K \* I<sub>out</sub> であり、ただし、K > 1 である)。20

#### 【0024】

[0031] ブーストコントローラ 190 x は、エンベロープ増幅器 170 に与えられた V<sub>env</sub> 電圧と、エンベロープ増幅器 170 からの I'<sub>out</sub> 電流とを受け得る。ブーストコントローラ 190 内で、出力電流ヘッドルーム間コンバータ 310 は、I'<sub>out</sub> 電流を受け、ヘッドルーム電圧 (V<sub>hr</sub>) を与え得る。加算器 320 は、V<sub>env</sub> 電圧と V<sub>hr</sub> 電圧とを受け、加算し得、加算電圧 (V<sub>sum</sub>) を与え得る。ピーク検出器 330 は、加算器 320 からの V<sub>sum</sub> 電圧のピークを検出し得、検出されたピーク電圧 (V<sub>det</sub>) を与え得る。制御回路 340 は、V<sub>det</sub> 電圧を受け得、V<sub>det</sub> 電圧に基づいて V<sub>th</sub> 電圧を与え得る。V<sub>th</sub> 電圧は、V<sub>det</sub> 電圧に等しくなり得る (たとえば、V<sub>th</sub> = V<sub>det</sub> である) か、あるいは V<sub>det</sub> 電圧の比率に応じて調整されたおよび / またはシフトバージョンであり得る (たとえば、V<sub>th</sub> = Q \* V<sub>det</sub> + V<sub>os</sub> であり、ただし、Q は任意のスケーリングファクタであり得、V<sub>os</sub> は任意のオフセット電圧であり得る)。30

#### 【0025】

[0032] 制御回路 340 はまた、V<sub>det</sub> 電圧に基づいて E<sub>nb</sub> 制御信号を生成し得る。例示的な設計では、制御回路 340 は、(i) V<sub>th</sub> 電圧が V<sub>batt</sub> 電圧よりも大きい (すなわち V<sub>th</sub> > V<sub>batt</sub> である) ときにブーストコンバータ 180 を有効にするか、または (ii) V<sub>th</sub> 電圧が V<sub>batt</sub> 電圧よりも小さい (すなわち V<sub>th</sub> < V<sub>batt</sub> である) ときにブーストコンバータ 180 を無効にするための E<sub>nb</sub> 制御信号を生成し得る。制40

御回路 340 はまた、ブーストコンバータ 180 を有効にすることと無効にすることとの間を継続的にトグルすることを回避するために、ヒステリシスを用いた E n b 制御信号を生成し得る。たとえば、制御回路 340 は、( i ) V t h 電圧が、ある最小持続時間の間 V b a t 電圧よりも小さく、および / または ( i i ) V t h 電圧が、少なくともある最小量だけ V b a t 電圧よりも小さいとき、ブーストコンバータ 180 を無効にするための E n b 制御信号を生成し得る。

#### 【 0 0 2 6 】

[0033] エンベロープ増幅器 170 は、V e n v 信号を増幅すべきであり、圧縮すべきでない。これは、( i ) 必要なときはいつでも電源電圧として V b o o s t 電圧で V e n v 信号を増幅することと、( i i ) エンベロープ増幅器 170 の出力における V o u t 電圧のピークにいくらかのヘッドルームを加えたものよりも高くなるように V b o o s t 電圧を生成することと、によって保証され得る。V t h 電圧は、V e n v 電圧のピークに V h r 電圧を加えたものに基づいて生成され得る。V b o o s t 電圧は、V t h 電圧に基づいて生成され得(たとえば、V b o o s t = V t h であり)、それにより、エンベロープ増幅器 170 が圧縮を回避することができることを保証し得る。10

#### 【 0 0 2 7 】

[0034] 図 3 に、( i ) 可変 V h r 電圧が I ' o u t 電流に基づいて生成され、( i i ) V t h 電圧が可変 V h r 電圧に基づいて生成される例示的な設計を示す。この設計では、V h r 電圧は、より大きい I o u t 電流の場合により高くなり得、より小さい I o u t 電流の場合により低くなり得る。この設計により、( i ) より大きい I o u t 電流の場合にエンベロープ増幅器 170 のためのより大きいヘッドルームが生じ、これにより線形性が向上し得るか、または( i i ) より小さい I o u t 電流の場合にエンベロープ増幅器 170 のためのより小さいヘッドルームが生じ、これにより電力消費を削減し得る。別の例示的な設計では、V t h 電圧は、固定された V h r 電圧に基づいて生成され得る。固定された V h r 電圧は、関係する様々な V o u t 電圧に対して良好な性能を与えるように選択され得る。20

#### 【 0 0 2 8 】

[0035] 図 3 に、V s u m 電圧を得るために加算器 320 によって V e n v 電圧が V h r 電圧と加算される例示的な設計を示す。別の例示的な設計では、V s u m 電圧を得るために加算器 320 によって V o u t 電圧が V h r 電圧と加算され得る。V o u t 電圧は、V b a t 電圧または V b o o s t 電圧に依存し得、V b a t 電圧または V b o o s t 電圧が十分に高くないとき、ひずみ得る。したがって、( V o u t 電圧の代わりに) V e n v 電圧を V h r 電圧と加算することにより、より正確な V s u m 電圧となり得る。30

#### 【 0 0 2 9 】

[0036] 別の例示的な設計では、(電圧の代わりに) 電流が加算器 320 によって加算され得る。この設計では、コンバータ 310 は(ヘッドルーム電圧の代わりに) ヘッドルーム電流を与え得、V e n v 電圧は、エンベロープ電流に変換され、加算器 320 によってヘッドルーム電流と加算され得、加算電流は加算電圧に変換され得る。

#### 【 0 0 3 0 】

[0037] 図 3 に、図 1 中のブーストコントローラ 190 の例示的な設計を示す。ブーストコントローラ 190 は他の様式でも実装され得る。別の例示的な設計では、ブーストコントローラ 190 は、固定された V h r 電圧に基づいて V t h 電圧を生成し得、コンバータ 310 は、省略されるかまたは固定電圧生成器と交換され得る。また別の例示的な設計では、ピーク検出器 330 は(加算器 320 の後の代わりに) エンベロープ増幅器 170 と加算器 320 との間に配置され得る。この設計では、V t h 電圧を得るために、V h r 電圧は検出されたピーク電圧と加算され得る。また別の例示的な設計では、ピーク検出器 330 は省略され得、(V d e t 電圧の代わりに) V s u m 電圧が制御回路 340 に与えられ得る。40

#### 【 0 0 3 1 】

[0038] 図 1 中のブーストコントローラ 190 および図 3 中のブーストコントローラ 1950

$0 \times$  内の回路は様々な様式で実装され得る。ブーストコントローラ中の回路の例示的な設計について以下で説明する。この設計では、加算電流を得るために（電圧の代わりに）電流が加算される。

#### 【0032】

[0039] 図4に、図1中のブーストコントローラ190と図3中のブーストコントローラ190 $\times$ との例示的な設計である、ブーストコントローラ190yの概略図を示す。図4は、図1および図3中のエンベロープ増幅器170の例示的な設計である、エンベロープ増幅器170yは、Pチャネル金属酸化物半導体（PMOS）トランジスタ402と、Nチャネル金属酸化物半導体（NMOS）トランジスタ404とを含む。PMOSトランジスタ402は、そのソースが電源電圧（V<sub>suppl</sub>）に結合され、そのゲートが第1の駆動信号（V<sub>d rp</sub>）を受ける。V<sub>suppl</sub>電圧はV<sub>bat</sub>電圧またはV<sub>boost</sub>電圧であり得る。NMOSトランジスタ404は、そのソースが回路接地に結合され、そのゲートが第2の駆動信号（V<sub>d rn</sub>）を受ける。トランジスタ402および404のドレインは、互いに結合され、V<sub>out</sub>電圧を与える。他の例示的な設計では、PMOSトランジスタ402はNMOSトランジスタまたはカスコード構造と置き換えられ得る。10

#### 【0033】

[0040] 図4に示された例示的な設計では、ブーストコントローラ190yは、変換器310yと、加算器320yと、ピーク検出器330yと、制御回路340yとを含み、それらは、図3中の変換器310と、加算器320と、ピーク検出器330と、制御回路340との1つの例示的な設計である。コンバータ310yは、そのソースがV<sub>suppl</sub>電圧に結合され、そのゲートがV<sub>d rp</sub>信号を受け、そのドレインがノードDにヘッドルーム電流（I<sub>hr</sub>）を与えるPMOSトランジスタ412を含む。20

#### 【0034】

[0041] 加算器320yは、電圧電流（V - I）コンバータ422と、電流電圧（I - V）コンバータ424とを含む。V - Iコンバータ422内で、演算増幅器（オペアンプ）450は、その非反転入力がV<sub>env</sub>信号を受け、その反転入力がノードBに結合され、その出力がNMOSトランジスタ452および462のゲートに結合される。NMOSトランジスタ452は、そのドレインがV<sub>bat</sub>電圧に結合され、そのソースがノードBに結合される。NMOSトランジスタ462は、そのドレインがV<sub>bat</sub>電圧に結合され、そのソースがノードBにエンベロープ電流（I<sub>env</sub>）を与える。抵抗器454はノードBと回路接地との間に結合される。I - Vコンバータ424内で、オペアンプ470は、その非反転入力が回路接地に結合され、その反転入力がノードDに結合され、その出力がV<sub>sum</sub>電圧を与える。オペアンプ470はまた、その非反転入力が、回路接地の代わりに基準電圧に結合され得る。抵抗器472は、オペアンプ470の反転入力と出力との間に結合される。30

#### 【0035】

[0042] ピーク検出器330yは、その非反転入力が加算器320yの出力に結合され、その反転入力がノードEに結合され、その出力がNMOSトランジスタ432のゲートに結合されたオペアンプ430を含む。NMOSトランジスタ432は、そのドレインがV<sub>bat</sub>電圧に結合され、そのソースが、ノードEにおけるV<sub>det</sub>電圧を与え、それがピーク検出器330yの出力である。キャパシタ434および抵抗器436はノードEと回路接地との間に結合される。40

#### 【0036】

[0043] 制御回路340yは、ピーク検出器330yの出力に結合された非反転入力と、V<sub>bat</sub>電圧を受ける反転入力と、E<sub>nb</sub>信号を与える出力とを有する比較器（Comp）440とを含む。制御回路340yはまた、V<sub>th</sub>電圧としてV<sub>det</sub>電圧を与える。

#### 【0037】

[0044] エンベロープ増幅器170yは、エンベロープ増幅器170yの出力におけるV<sub>out</sub>電圧がエンベロープ増幅器170yの入力におけるV<sub>env</sub>信号を追跡するよう50

、 $V_{env}$ 信号に基づいて $V_{drn}$ および $V_{dnp}$ 信号を生成する。エンベロープ増幅器170yは、それが可能であるときに所望の $I_{out}$ 電流を与える。エンベロープ増幅器170yは、AB級増幅器であり得、それは良好な線形性と低電力消費との間の良好なトレードオフを与える。AB級増幅器の場合、PMOSトランジスタ402またはNMOSトランジスタ404のいずれかが所与の瞬間に負荷電流を導通し得る。負荷電流を導通するMOSトランジスタは、 $I_{out}$ 電流ならびに負荷電流を導通しないMOSトランジスタのためのバイアス電流を与えることになる。したがって、PMOSトランジスタ402が導通し、 $I_{out}$ 電流を与えるとき、PMOSトランジスタ402のドレイン電流( $I_{prefet}$ )は、エンベロープ増幅器170yによって与えられる $I_{out}$ 電流にほぼ等しくなり、すなわち $I_{prefet} = I_{out}$ になる。

10

## 【0038】

[0045]ブーストコントローラ190yは次のように動作する。コンバータ310yは、(i) PMOSトランジスタ402のドレイン電流の比率に応じて調整されたバージョンであり、(ii) エンベロープ増幅器170yによって与えられる $I_{out}$ 電流に比例する、ヘッドルーム電流( $I_{hr}$ )を与える。エンベロープ増幅器170y内のPMOSトランジスタ402はW/Lの次元を有し、ただし、WはPMOSトランジスタ402の幅であり、Lは長さである。コンバータ310y内のPMOSトランジスタ412は $K^*W/L$ の次元を有し得、ただし、Kは任意の値であり得る。Kは、1に等しいか、または1よりも大きいか、または1よりも小さくなり得る。たとえば、Kは、 $I_{hr}$ 電流が $I_{out}$ 電流のごく一部であるように、0.01または0.001に等しくなり得る。Kは固定値またはプログラムできる値であり得る。コンバータ310yからの $I_{hr}$ 電流は次のように表され得る。

20

## 【数5】

$$I_{hr} \approx K * I_{out} \quad . \quad \text{式(2)}$$

## 【0039】

[0046]式(2)に示された設計では、 $I_{hr}$ 電流は $I_{out}$ 電流に比例する。したがって、より大きい $I_{out}$ 電流はより大きいヘッドルームを生じ、その逆も同様である。

30

## 【0040】

[0047]加算器320y内のV-Iコンバータ422は、 $V_{env}$ 信号を受け、 $I_{env}$ 電流を与える。オペアンプ450とNMOSトランジスタ452とは、ノードBにおける電圧を $V_{env}$ 電圧にほぼ等しく維持するフィードバックループで結合される。NMOSトランジスタ452のソースによって与えられる電流( $I_a$ )は、

## 【数6】

$$I_a \approx \frac{V_{env}}{R_s}$$

40

として与えられ得、ただし、 $R_s$ は抵抗器454の抵抗値である。NMOSトランジスタ452および462は、同じゲート電圧を受け、同じ次元を有し、ほぼ等しいソース電流を与える。したがって、NMOSトランジスタ462のソース電流は次のように表され得る。

## 【数7】

$$I_{env} \approx \frac{V_{env}}{R_s} . \quad \text{式(3)}$$

## 【0041】

[0048] コンバータ310yからのIhr電流とV-Iコンバータ422からのIenv電流とは、ノードDにおいて加算される。加算電流(Isum)は次のように表され得る。

10

## 【数8】

$$I_{sum} = I_{hr} + I_{env} . \quad \text{式(4)}$$

## 【0042】

[0049] 加算器320y内のI-Vコンバータ424は、ノードDからIsum電流を受け、ピーク検出器330yに加算電圧(Vsum)を与える。Isum電流は抵抗器472を通って流れ、Vsum電圧は、Isum電流による抵抗器472の両端間の電圧降下によって決定される。Vsum電圧は次のように表され得る。

20

## 【数9】

$$V_{sum} = R_f * I_{sum} , \quad \text{式(5)}$$

上式で、Rfは抵抗器472の抵抗値である。

## 【0043】

[0050] ピーク検出器330yはVsum電圧のピークを検出する。ピーク検出器330y内で、オペアンプ430とNMOSトランジスタ432とはフィードバックループで結合される。Vsum電圧がVdet電圧を超えたとき、オペアンプ430は高い電圧を出力し、NMOSトランジスタ432はオンにされる。この場合、キャパシタ434は、NMOSトランジスタ432を介してより高い電圧まで充電される。逆に、Vsum電圧がVdet電圧を下回ったとき、オペアンプ430は低い電圧を出力し、NMOSトランジスタ432はオフにされる。この場合、キャパシタ434は抵抗器436を介して緩やかに放電され、キャパシタ434の両端間の電圧はゆっくり降下する。Vdet電圧は、したがって、(i)上昇するVsum電圧に従って急速に増加し、(ii)下降するVsum電圧に対して緩やかに減少する。

30

## 【0044】

[0051] 制御回路340yは、Vdet電圧を受け、Vth電圧とEnv信号とを与える。制御回路340y内で、比較器440は、Vdet電圧をVth電圧と比較し、Vdet電圧がVbat電圧を超えたときにEnv信号上で論理高(「1」)を出力し、Vdet電圧がVbat電圧を下回ったときにEnv信号上で論理低(「0」)を出力する。制御回路340yはまた、上記で説明したように、時間および/または電圧レベルのヒステリシスを伴ったEnv信号を生成し得る。

40

## 【0045】

[0052] 図4に、ブーストコントローラ190y内の回路の例示的な設計を示す。ブーストコントローラ中の回路は他の様式でも実装され得る。概して、ブーストコントローラ190は、エンベロープ増幅器170によってVout信号を圧縮することを回避し、バッ

50

テリー電力を温存するために、ブーストコンバータ180の動作を制御し得る。ブーストコントローラ190は、たとえば、図3および図4に示すように、I<sub>out</sub>電流とV<sub>env</sub>信号とに基づいてV<sub>th</sub>電圧とE<sub>nb</sub>信号とを生成し得る。ブーストコントローラ190は、V<sub>batt</sub>電圧が十分に高くないときにブーストコンバータ180を有効にするためのE<sub>nb</sub>信号を生成し得る。さらに、ブーストコントローラ190は、V<sub>boost</sub>電圧が(i)V<sub>out</sub>信号の圧縮を回避するために十分に高いが、(ii)電力消費を削減するために高過ぎないように、V<sub>th</sub>電圧を与える。V<sub>th</sub>電圧は、V<sub>out</sub>信号のピークにエンベロープ増幅器170のための十分なヘッドルームを加えたものよりも高くなり得る。ヘッドルームはエンベロープ増幅器170からの出力電流の閾数であり得る。

## 【0046】

10

[0053]エンベロープ増幅器170の出力電流に基づいてヘッドルームを調整することは、様々な動作シナリオにおける良好な性能を保証し得る。たとえば、ロングタームエボリューション(LTE:Long Term Evolution)システムでは、ワイヤレスデバイス100は、1.44~20MHzの範囲内にあるシステム帯域幅内の180KHz中の12個のサブキャリアをカバーし得る、1つのリソースブロック(RB)上でアップリンク信号を送信し得る。アップリンク信号のための1-RB波形は、極めて遅いピークを有し得る。この場合、インダクタ162は電流を使い果たし得、エンベロープ増幅器170が、負荷電流のすべてを瞬間に与えなければならないことがある。より多くの電圧ヘッドルームは、エンベロープ増幅器170が(i)1-RB波形の遅いピークの場合でも負荷電流のすべてを与えることができ、(ii)より速い波形の場合に良好な効率を維持することができることを保証し得る。

## 【0047】

20

[0054]図5に、それぞれ、図1中のスイッチャ160とエンベロープ増幅器170との例示的な設計である、スイッチャ160zとエンベロープ増幅器170zとの概略図を示す。エンベロープ増幅器170z内で、オペアンプ510はその非反転入力がV<sub>env</sub>信号を受け、その反転入力が(ノードFである)エンベロープ増幅器170zの出力に結合され、その出力がAB級ドライバ512の入力に結合される。ドライバ512は、(i)その第1の出力が、PMOSトランジスタ514のゲートに結合され、V<sub>drip</sub>信号を与え、(ii)その第2の出力が、NMOSトランジスタ516のゲートに結合され、V<sub>drn</sub>信号を与える。NMOSトランジスタ516は、そのドレインがノードFに結合され、そのソースが回路接地に結合される。PMOSトランジスタ514は、そのドレインがノードFに結合され、そのソースがPMOSトランジスタ518および520のドレインに結合される。PMOSトランジスタ518は、そのゲートがC1制御信号を受け、そのソースがV<sub>batt</sub>電圧を受ける。PMOSトランジスタ520は、そのゲートがC2制御信号を受け、そのソースがV<sub>boost</sub>電圧を受ける。

30

## 【0048】

[0055]図5に示された例示的な設計では、電流センサー164は、ノードFとノードAとの間に結合され、エンベロープ増幅器170zによって与えられたI<sub>out</sub>電流を検知する。センサー164は、I<sub>out</sub>電流の大部分をノードAに流し、スイッチャ160zに小さい検知電流(I<sub>sen</sub>)を与える。I<sub>sen</sub>電流はエンベロープ増幅器170zからのI<sub>out</sub>電流のごく一部である。別の例示的な設計では、電流センサー164は、たとえば、図4中のPMOSトランジスタ412と同様に、PMOSトランジスタ514と並列に結合され、V<sub>drip</sub>信号を受ける、PMOSトランジスタを用いて実装され得る。

40

## 【0049】

[0056]スイッチャ160z内で、電流検知増幅器530は、その入力が電流センサー164に結合され、その出力がスイッチャドライバ532の入力に結合される。ドライバ532は、その第1の出力(S1)がPMOSトランジスタ534のゲートに結合され、その第2の出力(S2)がNMOSトランジスタ536のゲートに結合される。NMOSトランジスタ536は、そのドレインが(ノードGである)スイッチャ160zの出力に結合され、そのソースが回路接地に結合される。PMOSトランジスタ534は、そのドレ

50

インがノード G に結合され、そのソースが V<sub>b a t</sub> 電圧を受ける。インダクタ 162 はノード A とノード G との間に結合される。

#### 【0050】

[0057] スイッチャ 160z は次のように動作する。スイッチャ 160z は、電流センサー 164 がエンベロープ増幅器 170z からの高い出力電流を検知し、低い検知電圧をドライバ 532 に与えるとき、オン状態にある。ドライバ 532 は、次いで、PMOSトランジスタ 534 のゲートに低い電圧を与える。NMOSトランジスタ 536 のゲートに低い電圧を与える。PMOSトランジスタ 534 は、オンにされ、V<sub>b a t</sub> 電圧からのエネルギーを蓄積するインダクタ 162 に V<sub>b a t</sub> 電圧を結合する。インダクタ 162 を通る電流はオン状態中に上昇し、上昇のレートは、(i) V<sub>b a t</sub> 電圧とノード A における V<sub>p a</sub> 電圧との間の差と、(ii) インダクタ 162 のインダクタンスとに依存する。逆に、スイッチャ 160z は、電流センサー 164 がエンベロープ増幅器 170z からの低い出力電流を検知し、高い検知電圧をドライバ 532 に与えるとき、オフ状態にある。ドライバ 532 は、次いで、PMOSトランジスタ 534 のゲートに高い電圧を与える。NMOSトランジスタ 536 はオンにされ、インダクタ 162 はノード A と回路接地との間に結合される。インダクタ 162 を通る電流はオフ状態中に低下し、低下のレートは、ノード A における V<sub>p a</sub> 電圧とインダクタ 162 のインダクタンスとに依存する。したがって、V<sub>b a t</sub> 電圧は、オン状態中にインダクタ 162 を介して電力増幅器 130 に電流を与え、インダクタ 162 は、オフ状態中にその蓄積されたエネルギーを電力増幅器 130 に与える。上記で説明した 1 - R<sub>B</sub> 波形の場合、インダクタ 162 における電流はピーク中にゼロまで低下し得、エンベロープ増幅器 170z は負荷電流のすべてを与える。この場合、十分に大きいヘッドルームが、エンベロープ増幅器 170z が所望の負荷電流を与えることができることを保証し得る。10

#### 【0051】

[0058] エンベロープ増幅器 170z は、効率を改善するために、必要なときのみ V<sub>b o o s t</sub> 電圧に基づいて動作し、残りの時間 V<sub>b a t</sub> 電圧に基づいて動作し得る。たとえば、エンベロープ増幅器 170z は、V<sub>b a t</sub> 電圧に基づいて電力のほぼ 85% を与え、V<sub>b o o s t</sub> 電圧に基づいて電力のほぼ 15% のみを与える。R<sub>F o u t</sub> 信号の大きいエンベロープにより、電力増幅器 130 のために高い V<sub>p a</sub> 電圧が必要とされるとき、E<sub>n b</sub> 信号は論理高（たとえば、V<sub>b a t</sub>）にあり、C1 制御信号は論理高（たとえば、V<sub>b a t</sub>）にあり、C2 制御信号は論理低（たとえば、0V）にある。この場合、ブーストコンバータ 180 は有効にされ、V<sub>b o o s t</sub> 電圧を生成し、PMOSトランジスタ 520 はオンにされ、PMOSトランジスタ 514 のソースに V<sub>b o o s t</sub> 電圧を与え、PMOSトランジスタ 518 はオフにされる。逆に、電力増幅器 130 のために高い V<sub>p a</sub> 電圧が必要とされないとき、E<sub>n b</sub> 信号は論理低にあり、C1 制御信号は論理低にあり、C2 制御信号は論理高にある。この場合、ブーストコンバータ 180 は無効にされ、PMOSトランジスタ 520 はオフにされ、PMOSトランジスタ 518 はオンにされ、PMOSトランジスタ 514 のソースに V<sub>b a t</sub> 電圧を与える。C1 および C2 制御信号は、E<sub>n b</sub> 制御信号に基づいて生成され、たとえば、C1 = E<sub>n b</sub> であり、C2 = 反転された E<sub>n b</sub> であり得る。30

#### 【0052】

[0059] エンベロープ増幅器 170z は次のように動作する。エンベロープ信号が増加したとき、オペアンプ 510 の出力は増加し、V<sub>d r p</sub> 信号は減少し、NMOSトランジスタ 516 がほぼオフにされるまで V<sub>d r n</sub> 信号は減少し、エンベロープ増幅器 170z の出力は増加する。エンベロープ信号が減少したとき、逆が真である。エンベロープ増幅器 170z の出力からオペアンプ 510 の反転入力までの負のフィードバックにより、エンベロープ増幅器 170z は単位利得を有する。したがって、エンベロープ増幅器 170z の出力はエンベロープ信号に従い、V<sub>p a</sub> 電圧はエンベロープ信号にほぼ等しくなり得る。MOSトランジスタ 514 および 516 のためのバイアス電流が小さい場合でも、大き4050

い出力電流が供給され得るように、ドライバ 512 は、効率を改善するために A B 級増幅器を用いて実装され得る。

#### 【0053】

[0060] 図 5 に、図 1 中のスイッチャ 160 およびエンベロープ増幅器 170 の例示的な設計を示す。スイッチャ 160 およびエンベロープ増幅器 170 は他の様式でも実装され得る。たとえば、スイッチャ 160 は、 $I_{sen}$  電流とオフセット電流とを受け、加算し、加算電流を電流検知増幅器 530 に与える、加算器を含み得る。スイッチャ 160 がより長い時間期間の間オンにされ、電力増幅器 130 のためのより大きい  $I_{ind}$  電流を与えることができるよう、加算電流は  $I_{sen}$  電流よりもオフセット電流だけ低くなり得る。エンベロープ増幅器 170 は、2001 年 10 月 9 日に発行された「Apparatus and Method for Efficiently Amplifying Wideband Envelope Signals」と題する米国特許第 6,300,826 号に記載されているように実装され得る。

10

#### 【0054】

[0061] スイッチャ 160z は、高効率を有し、電力増幅器 130 のための供給電流の大部分を送達する。エンベロープ増幅器 170z は、線形段階として動作し、比較的高い帯域幅（たとえば、MHz 範囲内）を有する。スイッチャ 160z は、エンベロープ増幅器 170z からの出力電流を低減するように動作し、それにより総合効率が改善される。

#### 【0055】

[0062] 図 6 に、図 1 中のブーストコンバータ 180 の例示的な設計である、ブーストコンバータ 180z の概略図を示す。ブーストコンバータ 180z 内で、インダクタ 612 は一方の端部が  $V_{bat}$  電圧を受け、他方の端部がノード H に結合される。NMOS ランジスタ 614 は、そのソースが回路接地に結合され、そのゲートが  $C_b$  制御信号を受信し、そのドレインがノード H に結合される。ダイオード 616 は、そのアノードがノード H に結合され、そのカソードがブーストコンバータ 180z の出力に結合される。キャパシタ 618 は、一方の端部が回路接地に結合され、他方の端部がブーストコンバータ 180z の出力に結合される。ブーストコントローラ 620 は、 $V_{th}$  電圧と、 $V_{boost}$  電圧と、NMOS ランジスタ 614 のドレインにおける検知電流とを受ける。ブーストコントローラ 620 は、 $V_{th}$  電圧と  $V_{boost}$  電圧と検知電流とに基づいて  $C_b$  制御信号を生成する。 $C_b$  制御信号は、NMOS ランジスタ 614 をオンまたはオフにする。

20

#### 【0056】

[0063] ブーストコンバータ 180z は次のように動作する。オン状態では、NMOS ランジスタ 614 は閉じられ、インダクタ 612 は  $V_{bat}$  電圧と回路接地との間に結合され、インダクタ 612 を介する電流は増加する。オフ状態では、NMOS ランジスタ 614 は開かれ、インダクタ 612 からの電流は、ダイオード 616 を介して、キャパシタ 618 と、ブーストコンバータ 180（図 6 に図示せず）の出力における負荷とに流れれる。 $V_{boost}$  電圧は次のように表され得る。

30

#### 【数 10】

40

$$V_{boost} = V_{bat} \cdot \frac{1}{1 - \text{Duty\_Cycle}} , \text{ および} \quad \text{式(6)}$$

## 【数11】

$$\text{Duty\_Cycle} = \left(1 - \frac{V_{\text{bat}}}{V_{\text{boost}}}\right), \quad \text{式(7)}$$

上式で、Duty\_Cycleは、N M O Sトランジスタ614がオンにされるデューティサイクルである。

## 【0057】

[0064]ブーストコントローラ620は、所望のV<sub>boost</sub>電圧を得、ブーストコンバータ180の適切な動作を保証するために、適切なデューティサイクルをもつC<sub>b</sub>制御信号を生成する。ブーストコントローラ620は、V<sub>boost</sub>電圧をV<sub>th</sub>電圧と比較し、V<sub>boost</sub>電圧がV<sub>th</sub>電圧に一致するようにC<sub>b</sub>制御信号を生成し得る。ブーストコントローラ620は比較器および／または他の回路を含み得る。検知電流は制御ループの安定性を保証し得る。10

## 【0058】

[0065]例示的な設計では、たとえば、図1に示されているように、装置（たとえば、集積回路、ワイヤレスデバイス、回路モジュールなど）は増幅器とブーストコンバータとを含み得る。増幅器（たとえば、エンベロープ増幅器170）は、エンベロープ信号と可変ブースト電源電圧とを受け、出力電圧と出力電流とを与え得る。ブーストコンバータ（たとえば、ブーストコンバータ180）は、電源電圧（たとえば、バッテリー電圧）と、エンベロープ信号に基づいて決定された少なくとも1つの信号とを受け得、電源電圧と少なくとも1つの信号とにに基づいて可変ブースト電源電圧を生成し得る。20

## 【0059】

[0066]本装置は、エンベロープ信号および／または出力電圧に基づいてブーストコンバータのための少なくとも1つの信号を生成し得るブーストコントローラ（たとえば、ブーストコントローラ190）をさらに含み得る。ブーストコントローラは、エンベロープ信号および／または出力電圧に基づいてイネーブル信号を生成し得る。代替または追加として、ブーストコントローラは、エンベロープ信号および／または出力電圧に基づいてブーストコンバータのためのしきい値電圧を生成し得る。少なくとも1つの信号はイネーブル信号および／またはしきい値電圧を備え得る。ブーストコンバータは、イネーブル信号に基づいて有効または無効にされ得る。ブーストコンバータは、電源電圧としきい値電圧に基づいて可変ブースト電源電圧を生成し得る。30

## 【0060】

[0067]例示的な設計では、ブーストコントローラは、ヘッドルーム電圧またはヘッドルーム電流であり得るヘッドルームにさらにに基づいて、しきい値電圧を生成し得る。ブーストコントローラは、増幅器からの出力電流、または出力電流のプログラム可能な比率に応じて調整されたバージョン、または何らかの他の量に基づいてヘッドルームを決定し得る。ブーストコントローラは、ヘッドルームおよびエンベロープ信号および／または出力電圧に基づいて加算電圧を決定し、加算電圧のピークを検出し、加算電圧の検出されたピークに基づいてしきい値電圧を決定し得る。ブーストコントローラはまた、加算電圧の検出されたピークに基づいてイネーブル信号を生成し得る。たとえばブーストコントローラは、（i）加算電圧の検出されたピークが電源電圧を超えるときにブーストコンバータを有効にするか、または（ii）加算電圧の検出されたピークが電源電圧を下回るときにブーストコンバータを無効にするためのイネーブル信号を生成し得る。ブーストコントローラはまた、加算電圧の検出されたピークが所定の時間量の間および／または所定の量だけ電源電圧を下回るときにブーストコンバータを無効にするためのイネーブル信号を生成し得る。40

## 【0061】

[0068]例示的な設計では、ブーストコントローラは、コンバータと、加算器と、ピーク

50

検出器と、制御回路とを含み得る。コンバータ（たとえば、図3中のコンバータ310）は、出力電流に基づいてヘッドルームを決定し得る。加算器（たとえば、加算器320）は、ヘッドルームとエンベロープ信号または出力電圧を加算し、加算電圧を与え得る。ピーク検出器（たとえば、ピーク検出器330）は、加算電圧のピークを検出し、検出されたピーク電圧を与え得る。制御回路（たとえば、制御回路340）は、検出されたピーク電圧に基づいてしきい値電圧および／またはイネーブル信号を決定し得る。

#### 【0062】

[0069]図7に、可変ブースト電源電圧を生成するためのプロセス700の例示的な設計を示す。エンベロープ信号に基づいて少なくとも1つの信号を決定する（ブロック712）。電源電圧と、エンベロープ信号に基づいて決定された少なくとも1つの信号とに基づいて可変ブースト電源電圧を生成する（ブロック714）。出力電圧と出力電流とを得るために可変ブースト電源電圧を用いてエンベロープ信号を増幅する（ブロック716）。

10

#### 【0063】

[0070]例示的な設計では、エンベロープ信号および／または出力電圧に基づいてイネーブル信号が生成され得る。代替または追加として、エンベロープ信号および／または出力電圧に基づいてしきい値電圧が生成され得る。しきい値電圧はまた、さらにヘッドルームに基づいて生成され得る。少なくとも1つの信号はイネーブル信号および／またはしきい値電圧を備え得る。可変ブースト電源電圧は、電源電圧およびしきい値電圧に基づいて生成され得る。可変ブースト電源電圧の生成は、イネーブル信号に基づいて有効または無効にされ得る。

20

#### 【0064】

[0071]図8に、ブーストコンバータを制御するための少なくとも1つの信号を生成するためのプロセス712xの例示的な設計を示す。プロセス712xは、図7中のステップ712のために使用され得る。増幅器の出力電流に基づいてヘッドルームを決定する（ブロック812）。ヘッドルームおよび増幅器に与えられたエンベロープ信号および／または増幅器からの出力電圧に基づいて加算電圧を決定する（ブロック814）。加算電圧のピークを検出する（ブロック816）。加算電圧の検出されたピークに基づいてしきい値電圧を決定する（ブロック818）。また、加算電圧の検出されたピークに基づいてイネーブル信号を生成する（ブロック820）。

30

#### 【0065】

[0072]本明細書で説明した回路（たとえば、エンベロープ増幅器、ブーストコンバータ、ブーストコントローラなど）は、I C、アナログI C、RF I C、混合信号I C、A S I C、プリント回路板（P C B）、電子デバイスなどの上で実装され得る。回路はまた、相補型金属酸化物半導体（C M O S）、N M O S、P M O S、バイポーラ接合トランジスタ（B J T）、バイポーラC M O S（B i C M O S）、シリコンゲルマニウム（S i G e）、ガリウムヒ素（G a A s）、ヘテロ接合バイポーラトランジスタ（H B T）、高電子移動度トランジスタ（H E M T）、シリコンオンインシュレータ（S O I）など、様々なI Cプロセス技術を用いて作製され得る。

#### 【0066】

[0073]本明細書で説明した回路を実装する装置は、スタンドアロンデバイスであり得るか、またはより大きいデバイスの一部であり得る。デバイスは、（i）スタンドアロンI C、（i i）データおよび／または命令を記憶するためのメモリI Cを含み得る1つまたは複数のI Cのセット、（i i i）R F受信機（R F R）またはR F送信機／受信機（R T R）などのR F I C、（i v）移動局モデル（M S M）などのA S I C、（v）他のデバイス内に埋め込まれ得るモジュール、（v i）受信機、セルラーフォン、ワイヤレスデバイス、ハンドセット、またはモバイルユニット、（v i i）その他であり得る。

40

#### 【0067】

[0074]1つまたは複数の例示的な設計では、説明した機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せで実装され得る。ソフトウェアで実装される場合、機能は、1つまたは複数の命令またはコードとしてコンピュータ可読媒体

50

上に記憶されるか、あるいはコンピュータ可読媒体を介して送信され得る。コンピュータ可読媒体は、ある場所から別の場所へのコンピュータプログラムの転送を可能にする任意の媒体を含む、コンピュータ記憶媒体とコンピュータ通信媒体の両方を含む。記憶媒体は、コンピュータによってアクセスされ得る任意の利用可能な媒体であり得る。限定ではなく例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM（登録商標）、CD-ROMまたは他の光ディスクストレージ、磁気ディスクストレージまたは他の磁気ストレージデバイス、あるいは命令またはデータ構造の形態の所望のプログラムコードを搬送または記憶するために使用され得、コンピュータによってアクセスされ得る、任意の他の媒体を備えることができる。また、いかなる接続もコンピュータ可読媒体と適切に呼ばれる。たとえば、ソフトウェアが、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線（DSL）、または赤外線、無線、およびマイクロ波などのワイヤレス技術を使用して、ウェブサイト、サーバ、または他のリモートソースから送信される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、DSL、または赤外線、無線、およびマイクロ波などのワイヤレス技術は、媒体の定義に含まれる。本明細書で使用するディスク（disk）およびディスク（disc）は、コンパクトディスク（disc）（CD）、レーザーディスク（登録商標）（disc）、光ディスク（disc）、デジタル多用途ディスク（disc）（DVD）、フロッピー（登録商標）ディスク（disk）およびbulley-ray（登録商標）ディスク（disc）を含み、ディスク（disk）は、通常、データを磁気的に再生し、ディスク（disc）は、データをレーザーで光学的に再生する。上記の組合せもコンピュータ可読媒体の範囲内に含めるべきである。

10

20

## 【0068】

[0075]本開示についての以上の説明は、いかなる当業者も本開示を作成または使用することができるよう与えたものである。本開示への様々な修正は当業者には容易に明らかとなり、本明細書で定義した一般原理は、本開示の範囲から逸脱することなく他の変形形態に適用され得る。したがって、本開示は、本明細書で説明した例および設計に限定されるものではなく、本明細書で開示した原理および新規の特徴に合致する最も広い範囲を与えられるべきである。

以下に本願の出願当初の特許請求の範囲に記載された発明を付記する。

## [C 1]

装置であって、前記装置は下記を備える、

30

エンベロープ信号と可変ブースト電源電圧とを受け、出力電圧と出力電流とを与えるように構成された増幅器と、

電源電圧と、前記エンベロープ信号に基づいて決定された少なくとも1つの信号とを受け、前記電源電圧と前記少なくとも1つの信号とに基づいて前記可変ブースト電源電圧を生成するように構成されたブーストコンバータ。

## [C 2]

前記エンベロープ信号または前記出力電圧に基づいて前記ブーストコンバータのための前記少なくとも1つの信号を生成するように構成されたブーストコントローラをさらに備える、C 1に記載の装置。

## [C 3]

前記ブーストコントローラが、前記エンベロープ信号または前記出力電圧に基づいてイネーブル信号を生成するように構成され、前記少なくとも1つの信号が前記イネーブル信号を備え、前記ブーストコンバータが、前記イネーブル信号に基づいて有効または無効にされる、C 2に記載の装置。

40

## [C 4]

前記ブーストコントローラが、前記エンベロープ信号または前記出力電圧に基づいて前記ブーストコンバータのためのしきい値電圧を生成するように構成され、前記少なくとも1つの信号が前記しきい値電圧を備え、前記ブーストコントローラが、前記電源電圧と前記しきい値電圧とに基づいて前記可変ブースト電源電圧を生成するように構成された、C 2に記載の装置。

50

[ C 5 ]

前記ブーストコントローラが、ヘッドルームにさらに基づいて前記しきい値電圧を生成するように構成された、C 4 に記載の装置。

[ C 6 ]

前記ブーストコントローラが、前記増幅器からの前記出力電流に基づいて前記ヘッドルームを決定するように構成された、C 5 に記載の装置。

[ C 7 ]

前記ブーストコントローラが、前記増幅器からの前記出力電流のプログラム可能な比率に応じて調整されたバージョンに基づいて前記ヘッドルームを決定するように構成された、C 5 に記載の装置。

10

[ C 8 ]

前記ブーストコントローラが、前記ヘッドルームおよび前記エンベロープ信号または前記出力電圧に基づいて加算電圧を決定し、前記加算電圧のピークを検出し、前記加算電圧の前記検出されたピークに基づいて前記しきい値電圧を決定するように構成された、C 5 に記載の装置。

[ C 9 ]

前記ブーストコントローラが、前記加算電圧の前記検出されたピークに基づいてイネーブル信号を生成するように構成され、前記少なくとも1つの信号が前記イネーブル信号を備え、前記ブーストコンバータが、前記イネーブル信号に基づいて有効または無効にされる、C 8 に記載の装置。

20

[ C 10 ]

前記ブーストコントローラは、前記加算電圧の前記検出されたピークが前記電源電圧を超えるときに前記ブーストコンバータを有効にし、前記加算電圧の前記検出されたピークが前記電源電圧を下回るときに前記ブーストコンバータを無効にするための前記イネーブル信号を生成するように構成された、C 9 に記載の装置。

[ C 11 ]

前記ブーストコントローラは、前記加算電圧の前記検出されたピークが所定の時間量の間、または所定の量だけ、または両方、前記電源電圧を下回るときに前記ブーストコンバータを無効にするための前記イネーブル信号を生成するように構成された、C 10 に記載の装置。

30

[ C 12 ]

前記ブーストコントローラが、

前記出力電流に基づいてヘッドルームを決定するように構成されたコンバータと、

前記ヘッドルームと前記エンベロープ信号または前記出力電圧を加算し、加算電圧を与えるように構成された加算器と、

前記加算電圧のピークを検出し、検出されたピーク電圧を与えるように構成されたピーク検出器と、を備える、C 2 に記載の装置。

[ C 13 ]

前記ブーストコントローラは、

前記検出されたピーク電圧に基づいてしきい値電圧を決定するように構成された制御回路をさらに備え、ここにおいて、前記少なくとも1つの信号が前記しきい値電圧を備え、ここにおいて、前記ブーストコンバータが、前記電源電圧と前記しきい値電圧とに基づいて前記可変ブースト電源電圧を生成するように構成される、C 12 に記載の装置。

40

[ C 14 ]

前記制御回路が、前記検出されたピーク電圧に基づいてイネーブル信号を決定するように構成され、前記少なくとも1つの信号が前記イネーブル信号を備え、前記ブーストコンバータが、前記イネーブル信号に基づいて有効または無効にされる、C 13 に記載の装置

。

[ C 15 ]

方法であって、前記方法は下記を備える、

50

電源電圧と、エンベロープ信号に基づいて決定された少なくとも1つの信号とともに可変ブースト電源電圧を生成することと、

出力電圧と出力電流とを得るために前記可変ブースト電源電圧を用いて前記エンベロープ信号を增幅すること。

[C 16]

前記エンベロープ信号または前記出力電圧に基づいてイネーブル信号を生成することをさらに備え、ここにおいて、前記少なくとも1つの信号が前記イネーブル信号を備え、ここにおいて、前記可変ブースト電源電圧の生成が、前記イネーブル信号に基づいて有効または無効にされる、C 15に記載の方法。

[C 17]

10

前記エンベロープ信号または前記出力電圧に基づいてしきい値電圧を生成することをさらに備え、ここにおいて、前記少なくとも1つの信号が前記しきい値電圧を備え、ここにおいて、前記可変ブースト電源電圧が、前記電源電圧と前記しきい値電圧とに基づいて生成される、C 15に記載の方法。

[C 18]

前記しきい値電圧を前記生成することが、ヘッドルームにさらに基づいて前記しきい値電圧を生成することを備える、C 17に記載の方法。

[C 19]

20

前記しきい値電圧を前記生成することが、

前記出力電流に基づいてヘッドルームを決定することと、

前記ヘッドルームおよび前記エンベロープ信号または前記出力電圧に基づいて加算電圧を決定することと、

前記加算電圧のピークを検出することと、

前記加算電圧の前記検出されたピークに基づいて前記しきい値電圧を決定することとを備える、C 17に記載の方法。

[C 20]

装置であって、前記装置は下記を備える、

電源電圧と、エンベロープ信号に基づいて決定された少なくとも1つの信号とともに可変ブースト電源電圧を生成するための手段と、

出力電圧と出力電流とを得るために前記可変ブースト電源電圧を用いて前記エンベロープ信号を増幅するための手段。

30

[C 21]

前記エンベロープ信号または前記出力電圧に基づいてイネーブル信号を生成するための手段をさらに備え、ここにおいて、前記少なくとも1つの信号が前記イネーブル信号を備え、ここにおいて、前記可変ブースト電源電圧の生成が、前記イネーブル信号に基づいて有効または無効にされる、C 20に記載の装置。

[C 22]

40

前記エンベロープ信号または前記出力電圧に基づいてしきい値電圧を生成するための手段をさらに備え、ここにおいて、前記少なくとも1つの信号が前記しきい値電圧を備え、ここにおいて、前記可変ブースト電源電圧が前記電源電圧と前記しきい値電圧とに基づいて生成される、C 20に記載の装置。

[C 23]

前記しきい値電圧を生成するための前記手段が、ヘッドルームにさらに基づいて前記しきい値電圧を生成するための手段を備える、C 22に記載の装置。

[C 24]

前記しきい値電圧を生成するための前記手段が、

前記出力電流に基づいてヘッドルームを決定するための手段と、

前記ヘッドルームおよび前記エンベロープ信号または前記出力電圧に基づいて加算電圧を決定するための手段と、

前記加算電圧のピークを検出するための手段と、

50

前記加算電圧の前記検出されたピークに基づいて前記しきい値電圧を決定するための手段と、を備える、C 2 2 に記載の装置。

[ C 2 5 ]

非一時的コンピュータ可読媒体を備えるコンピュータプログラム製品であつて、前記非一時的コンピュータ可読媒体は下記を備える、

少なくとも 1 つのコンピュータに、電源電圧と、エンベロープ信号に基づいて決定された少なくとも 1 つの信号とに基づいて可変ブースト電源電圧の生成を指示させるためのコードと、

前記少なくとも 1 つのコンピュータに、出力電圧と出力電流とを得るために前記可変ブースト電源電圧を用いて前記エンベロープ信号の増幅を指示させるためのコード。

10

【図 1】

【図 2A】

FIG. 2A

【図 2B】

図 2B

FIG. 2B

【図 3】

図 3

FIG. 3

【図 4】

図 4

FIG. 4

【図 5】

図 5

FIG. 5

【図6】

図6

【図7】

図7

【図8】

図8

---

フロントページの続き

(72)発明者 マセ、レナート・カール - アクセル

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 シ、ユンフェイ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 小林 正明

(56)参考文献 米国特許出願公開第2012/0326783(US, A1)

特開2008-061231(JP, A)

特開2011-250166(JP, A)

国際公開第2005/104352(WO, A1)

米国特許出願公開第2009/0004981(US, A1)

米国特許出願公開第2002/0030543(US, A1)

(58)調査した分野(Int.Cl., DB名)

H03F 1/02 - 3/68